CN102272925B - 用于制造照明用具的方法 - Google Patents

用于制造照明用具的方法 Download PDFInfo

- Publication number

- CN102272925B CN102272925B CN200980153425.3A CN200980153425A CN102272925B CN 102272925 B CN102272925 B CN 102272925B CN 200980153425 A CN200980153425 A CN 200980153425A CN 102272925 B CN102272925 B CN 102272925B

- Authority

- CN

- China

- Prior art keywords

- subregion

- chip installation

- solder flux

- layer

- structuring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 16

- 229910000679 solder Inorganic materials 0.000 claims abstract description 78

- 238000009434 installation Methods 0.000 claims description 96

- 230000004907 flux Effects 0.000 claims description 89

- 238000000034 method Methods 0.000 claims description 44

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 claims description 31

- 239000000463 material Substances 0.000 claims description 26

- 229910052751 metal Inorganic materials 0.000 claims description 21

- 239000002184 metal Substances 0.000 claims description 21

- 229910052759 nickel Inorganic materials 0.000 claims description 17

- 229910052737 gold Inorganic materials 0.000 claims description 14

- 239000010931 gold Substances 0.000 claims description 14

- 230000001846 repelling effect Effects 0.000 claims description 14

- 229910052802 copper Inorganic materials 0.000 claims description 11

- 239000010949 copper Substances 0.000 claims description 11

- 230000003647 oxidation Effects 0.000 claims description 11

- 238000007254 oxidation reaction Methods 0.000 claims description 11

- 239000012634 fragment Substances 0.000 claims description 7

- 238000001704 evaporation Methods 0.000 claims description 6

- 229910052709 silver Inorganic materials 0.000 claims description 6

- 239000004332 silver Substances 0.000 claims description 6

- 230000008569 process Effects 0.000 claims description 4

- 239000004411 aluminium Substances 0.000 claims description 3

- 229910052782 aluminium Inorganic materials 0.000 claims description 3

- 230000001678 irradiating effect Effects 0.000 claims description 3

- 239000004020 conductor Substances 0.000 claims description 2

- 230000005693 optoelectronics Effects 0.000 abstract description 3

- 239000010410 layer Substances 0.000 description 65

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 21

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 13

- 238000009826 distribution Methods 0.000 description 8

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 5

- 230000008020 evaporation Effects 0.000 description 5

- 230000005855 radiation Effects 0.000 description 5

- 239000000758 substrate Substances 0.000 description 5

- 239000000919 ceramic Substances 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 238000005401 electroluminescence Methods 0.000 description 4

- 238000005286 illumination Methods 0.000 description 3

- 238000009413 insulation Methods 0.000 description 3

- 238000003475 lamination Methods 0.000 description 3

- 229910000480 nickel oxide Inorganic materials 0.000 description 3

- GNRSAWUEBMWBQH-UHFFFAOYSA-N oxonickel Chemical compound [Ni]=O GNRSAWUEBMWBQH-UHFFFAOYSA-N 0.000 description 3

- 239000004033 plastic Substances 0.000 description 3

- 229920003023 plastic Polymers 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- ZBTDWLVGWJNPQM-UHFFFAOYSA-N [Ni].[Cu].[Au] Chemical compound [Ni].[Cu].[Au] ZBTDWLVGWJNPQM-UHFFFAOYSA-N 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 2

- 230000001070 adhesive effect Effects 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 239000011248 coating agent Substances 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 239000012141 concentrate Substances 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000001465 metallisation Methods 0.000 description 2

- 150000002815 nickel Chemical class 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 229920002120 photoresistant polymer Polymers 0.000 description 2

- 238000005476 soldering Methods 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 239000012876 carrier material Substances 0.000 description 1

- 238000007385 chemical modification Methods 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000000608 laser ablation Methods 0.000 description 1

- 230000002045 lasting effect Effects 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 239000012044 organic layer Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 230000008439 repair process Effects 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 238000004062 sedimentation Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 238000003466 welding Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/16—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different main groups of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. forming hybrid circuits

- H01L25/167—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different main groups of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. forming hybrid circuits comprising optoelectronic devices, e.g. LED, photodiodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/005—Processes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/483—Containers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/64—Heat extraction or cooling elements

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0201—Thermal arrangements, e.g. for cooling, heating or preventing overheating

- H05K1/0203—Cooling of mounted components

- H05K1/021—Components thermally connected to metal substrates or heat-sinks by insert mounting

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/182—Printed circuits structurally associated with non-printed electric components associated with components mounted in the printed circuit board, e.g. insert mounted components [IMC]

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/0058—Laminating printed circuit boards onto other substrates, e.g. metallic substrates

- H05K3/0061—Laminating printed circuit boards onto other substrates, e.g. metallic substrates onto a metallic substrate, e.g. a heat sink

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/075—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00

- H01L25/0753—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L33/00 the devices being arranged next to each other

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/1015—Shape

- H01L2924/10155—Shape being other than a cuboid

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10007—Types of components

- H05K2201/10106—Light emitting diode [LED]

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/20—Details of printed circuits not provided for in H05K2201/01 - H05K2201/10

- H05K2201/2081—Compound repelling a metal, e.g. solder

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/03—Metal processing

- H05K2203/0315—Oxidising metal

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by soldering

- H05K3/341—Surface mounted components

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Led Device Packages (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

Abstract

一种用于制造照明用具的方法提出提供用作为热沉的载体,该载体包括平面芯片安装区域。为了产生第一子区域和至少一个第二子区域对该平面芯片安装区域进行结构化。在此第一子区域在结构化以后具有排斥焊剂的特征。接着在该平面芯片安装区域上施加焊剂,从而焊剂交联所述至少一个第二子区域。在至少一个第二子区域中利用焊剂将至少一个光电体紧固在载体上。最后构造接触部以将电能引导到光电照明体。

Description

本专利申请要求德国专利申请102008063325.9的优先权,该德国专利申请的公开内容通过引用结合于此。

技术领域

本发明涉及一种用于制造照明用具的方法并且尤其是涉及一种用于制造具有光电器件的组件的方法。

背景技术

利用光电器件的应用越来越重要。除了如灯的简单照明用具以外,属于此的还有背景照明,例如用于LCD屏幕或监视器的背景照明。在此,概念“光电器件”表示这样的元件,即该元件在运行中在被供给电能时发光。除了基于半导体的发光二极管以外,属于此的还有有机发光二极管、由有机的和适于发光的无机连接构成的组合、以及其他发光器件。

在一些应用中,需要非常高的光功率,例如用于投影仪。在此首先使用以不同颜色发光的发光体,从而得出白色的混合光。

为了达到尽可能高的亮度(Leuchtdichte),常常将不同的光电器件安置在共同的芯片上并且接着通过相应的引线操控以及供给能量。划分到各个不同的芯片所具有的优点是,一方面可以更好地调节光度(Leuchtkraft)和颜色,并且另一方面减小故障概率或改进修理可能。与此相对地,可能由于不准确地安置而得出不均匀的光分布和亮度,这可能是干扰性地可察觉的。

因此存在如下需要:在制造这样的照明用具时提供一种方法,在这种方法的情况下可达到更高的和更均匀的亮度。

发明内容

该任务利用独立的方法权利要求的主题来解决。

本发明的改进方案和扩展方式是从属权利要求的主题。

根据所提出的原理,亮度和均匀性——也简称为集光率——通过对平面芯片安装区域进行适当的结构化来改进,在该平面芯片安装区域上施加各个照明体。

为此目的在一个扩展方案中提供用作为热沉的载体,该载体包括平面芯片安装区域。该载体可以具有金属芯、具有这样的平面芯片安装区域的金属衬底。同样地,作为载体可以提供具有金属化的芯片安装区域的陶瓷衬底、具有平面的必要时金属化的芯片安装区域的PCB(Printed Circuit Board,印刷电路板)、或者具有这样的区域的引线框架。根据相应的载体,可以对稍后的芯片安装区域进行预处理、例如金属化。每种具有SMT能力的衬底都适合作为载体,使得能够在子区域中被金属化,以便构成平面芯片安装区域。

对平面芯片安装区域进行结构化以产生第一子区域和至少一个第二子区域。所述结构化这样进行,即第一子区域在结构化以后具有排斥焊剂的特征。可替换地,通过对芯片安装区域的结构化,第一子区域变得排斥焊剂,使得芯片安装区域在第一子区域中是排斥焊剂的并且在第二子区域中是吸引焊剂的。

概念“排斥焊剂的”或者“排斥焊剂的特征”被理解为第一子区域的特征,该特征导致在稍后施加焊剂或者焊料时,所述焊剂或者焊料不交联或者几乎不交联第一子区域。因此,在平面芯片安装区域上施加焊剂以后,焊剂主要集中在第二子区域中并且交联该第二子区域。

接着,在所述至少一个第二子区域中将光电体、优选光电半导体器件施加到焊剂上并且与载体固定连接。通过结构化以及产生排斥焊剂的第一子区域,施加在焊剂上的光电体因此在第二子区域中固定。在焊剂的液态状态时进行制造器件,在焊剂上游动的光电体“跟随”焊剂到第二子区域中,因为只有在该子区域中焊剂才交联芯片安装区域。

因此,将平面芯片安装区域结构化为具有排斥焊剂和吸引焊剂或交联特征的子区域允许构造如下子区域:在所述子区域中,一个或多个光电体被固定并且通过预先施加的焊剂与芯片安装区域连接。

接着可以构造电接触部,该电接触部适合于将电能引导到光电照明体。

在一个扩展方案中,与此相关地适宜的是,将用作为热沉的载体已经构造为电极或将平面芯片安装区域构造为电极。在该情况下,平面芯片安装区域不再用作为热沉的部分,而是也用作为到光电器件的电接触。

在一个扩展方案中,第二子区域中的平面芯片安装区域包括至少一个金属的、能被焊剂至少部分地交联的子层。该子层例如可以包括金、银或者另一非氧化的材料。在一个实施方式中,平面安装区域包括不同的彼此相叠布置的子层,这些子层由不同金属构成。所述金属例如可以包括镍、铜、铝、银、金、钛或者钨。在此,可以将金层施加在镍层之上,以便阻止金扩散到位于其下方的例如由铜构成的子层中。

在所述方法的一个扩展方式中提出,为了对芯片安装区域进行结构化和生成第一子区域,去除芯片安装区域内的金层的部分并且对位于其下方的镍层进行氧化。通过氧化位于其下方的层、尤其是镍层,生成第一子区域,该第一子区域具有排斥焊剂的特征,从而施加在其上的焊剂不交联该子区域或者仅仅非常小地交联该子区域。

在一个扩展方案中,通过提供光学光源、优选激光器来实现这样的结构化。接着,为了产生对平面芯片安装区域的结构化,用光学光源照射该平面芯片安装区域的第一字区域并且因此氧化金属子层中的至少一个。在一个实施例中,通过照射表面材料使第一子区域熔化或者蒸发并且氧化位于其下方的暴露出来的材料。该位于下方的被氧化的材料具有排斥焊剂的特征。所述表面材料例如可以是金、铝或者银,该表面材料通过照射、优选借助于激光器被蒸发。构成另一子层的、位于下方的材料被暴露出来。该材料例如可以包括镍。被暴露出来的材料然后例如借助于光学辐射源被氧化,但是也可以通过其他的物理或化学方法被氧化。

在暴露出镍层的情况下,该镍层通过激光射线被氧化并且这样氧化的镍是排斥焊剂的。

一般为了产生具有排斥焊剂的特征的材料,平面芯片安装区域的表面材料可以通过物理或化学方法被化学改变并且可以进行连接。

在另一扩展方案中,对平面芯片安装区域进行结构化,所通过的方式是在平面芯片安装区域上施加止焊层。该止焊层同样是排斥焊剂的。接着为了产生第一和第二子区域对该止焊层结构化并且在第二子区域中去除该止焊层,使得芯片安装区域的第二子区域的位于下面的表面再次暴露出来。对止焊层的结构化例如可以通过合适的掩膜方法和曝光来进行。其余的止焊层保留在芯片安装区域上的第一子区域的构造下面。

在另一扩展方案中,止焊层被直接选择性地施加到平面芯片安装区域上,并且即为第一子区域定义的芯片安装区域。在此,止焊层也是排斥焊剂的。这样的施加可以例如通过模板方法或焊剂分发法来进行。只要需要,就接着通过暴露和/或处理第二子区域的片段而使该第二子区域不具有不期望地施加的止焊层,从而该第二子区域再次包括能被焊剂交联的表面。

为了施加焊剂到第二子区域内的平面芯片安装区域上,提供一种焊剂分发法。这在芯片安装区域在载体内比包围其的区域更深地被放置时是有其有利的,该区域例如可以包含引线和其他电接触部。

在另一扩展方案中,用作为热沉的载体以平面芯片安装区域来提供并且在该平面芯片安装区域上施加接触层。该载体可以是PCB、陶瓷衬底、金属核、塑料或者由这些载体材料构成的组合。

在芯片安装区域以外,将介电层平面地施加到载体上,以便避免与芯片安装区域的短路。在该介电层上现在蒸镀、沉积或者以其他方式施加印制导线和接触焊盘(Kontaktpad)以及其他需要的元件。此外为了产生第一或第二子区域,对芯片安装区域进行相应地结构化,并且接着将焊剂材料例如借助于焊剂分发法沉积到至少一个第二子区域上。通过对平面芯片安装区域的结构化,焊剂被强迫到至少一个第二子区域中并且交联该第二子区域。接着可以将不同的光电器件安放在至少一个第二子区域中的焊剂上并且通过加热焊剂使其与芯片安装区域紧密连接。在最后一个步骤中,进行电接触以引导电能。

电接触例如可以通过线接合来进行,其中接合线一方面与光电发光体连接并且另一方面与芯片安装区域之外的接触焊盘连接。

在本发明的另一扩展方案中,芯片安装区域被划分成不同的第二子区域,其中分别两个相邻的第二子区域被第一子区域的片段分开。通过这种方式,多个光电发光体可以在芯片安装区域上在空间容易分开、但是间隔非常紧的区域中被紧固。例如可以将被实施用于发射不同波长的光的光电发光体如此布置在芯片安装区域上,即使得产生期望的总照明模式。尤其是例如白色的混合色可以通过在芯片安装区域上布置不同的发光体来实现。在此可以通过对两个第二子区域之间的第一子区域进行适当地薄地结构化来达到不同光电发光体的基本上无缝隙的相互接合。

附图说明

下面参照附图根据多个实施例详细地进一步阐释本发明。

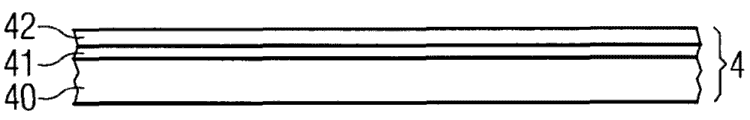

图1示出根据所提出的原理制造的照明用具的截面图,

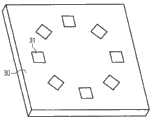

图2示出根据所提出的原理的照明用具的平面芯片安装区域的俯视图,

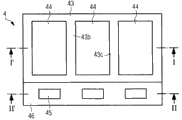

图3示出可替换实施方式中的芯片安装区域的俯视图,

图4A至4E示出用于阐释该方法的实施例的截面图以及俯视图,

图5A至5D以俯视图示出用于制造照明用具的该方法的另一实施例。

具体实施方式

在下面的实施例和图中,相同的或者作用相同的构件可以配备相同的附图标记。图和尺寸关系,尤其是还有各个子区域和层相互之间的尺寸关系,原则上不应被看作为按照比例的。更确切地说,它们用于表明本发明的各个方面。为了更好的理解或者更好的可展示性,这些尺寸关系可以被表示为夸张地大或厚的。

图1以截面图示出照明用具的一个片段,该照明用具是按照根据所提出的原理的方法制造的。对此,照明用具1被施加在用作为热沉的载体10a上。该载体包括连续的铜芯10,该铜芯10具有足够的稳定性并且其热容量足够大,以便能够引出在运行时由照明体100所产生的热。铜芯10除此之外所具有的优点是,该铜芯10可以用作为照明体100的背侧电极。

可替换地,还可以使用陶瓷衬底作为具有金属化的芯片安装区域的载体。

在铜芯10上,为了更好地固定光电器件100,附加地施加子层11和12。这使得稍后施加的焊剂能够良好地交联,照明体100被固定在该焊剂上。各个子层在该实施例中包括由镍构成的子层11以及薄薄地施加在上面的金层12。金层12阻止位于下方的层的不希望的氧化并且因此延长使用期限。

在通过镍子层11与铜芯10导电接触的金层12上,在子区域中施加介电层13。在该介电层13上蒸镀有接触焊片(Kontaktfahne)14,该接触焊片14稍后通过接合线117实现与照明体100的接触。

在芯片安装区域A中,子层11和12在各个子区域17中被结构化,以便保证将照明体100固定在焊剂15上。焊剂15被施加在第二子区域12a中,该第二子区域12a被结构化的子区域17包围。如可认识到的那样,焊剂不交联结构化的子区域17,而是仅仅交联芯片安装区域的第二子区域12a。因此,施加和固定在焊剂上的光电器件被固定在第二子区域12a中。例如发光二极管形式的照明体100包括布置在背侧的镜层115以改进光输出耦合。另外,照明体100包含一个或多个子层42,其中这些子层中的至少一个具有适用于发光的层。在一个实施方式中,照明体可以被构造为薄膜发光二极管。这样的照明体的相应的制造方式对于专业人员是公知的,从而放弃重新阐述。

在该实施例中,照明体100在其表面上具有接触部116,该接触部116通过接合线117与相应的接触焊盘和接触焊片14在照明用具和介电层13的表面上固定。

该结构化的第一子区域17被用薄的氧化镍层16覆盖。该通过去除金层并且接着去除氧化所产生的氧化镍层是排斥焊剂的,从而在芯片安装区域上涂敷焊剂材料时该子区域不被交联。接着,不同的附着力将施加在焊剂上的照明体拉到具有最多焊剂的子区域中。由此,通过在子区域17和12a中对芯片安装区域进行结构化,可以准确地确定照明体在芯片安装区域内的位置。

为了制造这样的照明用具,在该实施例中通过激光去除金层12a。为此将激光射线对准芯片安装区域并且沿着该芯片安装区域引导,从而激光射线所扫过的位置处的子层12蒸发并且因此定义了子区域17。附加地通过激光射线引入的能量同时利用氧对位于下方的镍层11进行氧化,该镍层11然后具有排斥焊剂的特征。在稍后施加焊剂时应当注意,所使用的熔剂不再度使结构化的子区域17中的氧化镍层16减小,并且因此结构化再次取消。

在结构化之后例如通过焊剂分发法来施加焊剂。所施加的照明体100通过焊剂被固定到第二子区域12a上并且在其上被紧固。接着,可以通过接合线法进行接触线117到照明体或光电器件100的电接触。

图2示出用于阐述不同的结构化可能的俯视图。该图示示出芯片安装区域的俯视图,该芯片安装区域可以构成更大的载体的一部分。该芯片安装区域包括两个主区域,这两个主区域分别单独地来看有结构化成第一和第二子区域。在第一主区域中,芯片安装区域通过环绕的子区域24被结构化,从而其中存在暴露的面23。该面23构成第二子区域。在该面上可以通过分发法、沉积法或者印刷法来施加焊剂材料。而环绕的子区域24具有排斥焊剂的特征,从而焊剂材料基本上集中在区域23中。

结构化的芯片安装区域的第二主区域划分成两个第二子区域22a和22b,这两个子区域22a和22b分别通过结构化的桥被相互分隔开。在这里,子区域22a和22b也完全地被排斥焊剂的第一子区域21a环绕。在两个第二子区域22a和22b中沉积的焊剂材料通过结构化的桥21b保持分隔,从而在该实施方式中例如可以将两个分隔开的光电器件安置在各个子区域22a和22b上。

子区域23以及22a和22b的表面是金属的,从而所施加的焊剂材料一方面用于光电器件运行中的散热并且另一方面可以同时形成背面的电接触。

所提出的对芯片安装区域的结构化允许提供不同几何布置的子区域,在这些子区域中可以位置准确地安置光电器件。由此可以在整体上改进光辐射的集光率和均匀性。

图3与此相关地示出更复杂的芯片安装区域的片段,其中结构化有矩形的子区域31。这些子区域31基本上以圆形方式布置在共同的中点周围。通过载体上的适当接线,可以单个地操控光电器件并且因此实现不同的光应用。

子区域的不同尺寸和形状允许提供不同的光电器件并且同时考虑到这些光电器件的不同的辐射特性。因此例如也可以产生混合颜色,所通过的方式是,为了以不同的波长发光,彼此相邻地布置合适的器件。因为芯片安装区域的在结构化以后具有排斥焊剂的特征的第一子区域可以包括非常小的线宽,所以器件也可以被足够近地并排安置,而不会在运行中导致光功率或者辐射质量的减小。在此甚至可能的是,通过适当地选择排斥焊剂的第一子区域的宽度,两个相邻的第二子区域分隔开,直接并排地对光电器件以小于第一子区域的厚度的间隔进行布置和紧固。

同时可以单个地操控不同的光电器件,以便因此也实现不同的应用。对芯片安装区域的结构化允许对更小的光电器件的使用,这些更小的光电器件恰好在制造中更加地容错并且比相应大面积的部件的故障频率更小。

图4A至4E示出用于制造具有光电器件的组件的方法的实施例。

在根据图4A的第一步骤中,提供用作为热沉的载体4。该载体4在这里包括铜芯40,该铜芯40主要用作为热沉,但是载体4还可以包含其他材料。在铜芯40上施加绝缘的介电层41,该介电层41应当阻止铜芯40与位于其上的导电层42之间的短路。介电层41在这里同样具有足够的导热性。

层42包括多个金属化层,这些金属化层在这里由于清楚原因不详细示出。例如在介电层41上首先施加由铜构成的金属化层。在该由铜构成的金属化层上接着蒸镀镍并且然后又为了阻止氧化而施加薄的金层。在铜与金之间布置的镍层是必要的,以便避免金扩散到铜层中以及铜层接着被氧化。替代于这里提到的铜镍金镀层,还额可以使用其他的材料。例如由铜和银或镍和银构成的子层对于紧固稍后施加的照明体也是适用的。

介电层41为几微米厚,位于其上的铜金属化层可以具有35μm至70μm或者更多的厚度,镍层为大约10μm至20μm厚。

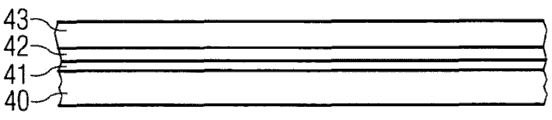

为了对芯片安装区域进行结构化以及划分成第一和第二子区域,其中第一子区域应当起到排斥焊剂的作用,现在大面积地在子层42上沉积出止焊层。结果在图4B中示出。接着借助于光掩膜方法对该止焊层进行结构化并且划分成各个第一子区域43a、43b和43c。例如特别不敏感的光刻胶或者另一有机层也适合作为止焊层。所述止焊层应当至少如此持久,直到对器件的制造结束。

在各个子区域43a、43b和43c之间去除起止焊层作用的光刻胶层的现在未被曝光的部分并且因此定义第二子区域44。在去除未被曝光的区域以后,金属化层42的表面又暴露出来。

图4D以俯视图示出载体的片段以图示各个结构化的第一和第二子区域43a、43b、43c和44。沿着轴I’-I的段对应于根据图4C的截面图。在第二子区域44中,金属表面暴露出来。

在该俯视图的下方区域中暴露有附加的接触焊盘45,这些接触焊盘45被介电保护层46包围。在图4E中示出沿着线II’-II的截面图。在金属化层42上为了电绝缘施加有另一介电层47。可替换地,该层47也可以由止焊层来构成,只要该止焊层起到电绝缘的作用。在该介电层47上沉积出接触元件45作为接触焊片和接触焊盘。为了阻止接触焊盘的氧化和减小短路概率,这些接触元件由另一介电保护层46包围。用于将电能引导到接触焊盘45的接触焊片在所示实施例中被保护层46覆盖。

因此仅仅接触焊盘45暴露出来,这些接触焊盘45例如通过接合线连接与子区域44中的光电器件连接。在载体4的这里未示出的片段中,在介电层47中提供有接触孔,这些接触孔实现与金属层42并且由此与子区域44中的光电器件的电接触。

图5A至5D示出用于制造照明用具的方法的另一实施例。在该方法中,用作为热沉的载体50——例如铜芯、陶瓷芯、PCB、引线框架或者类似的载体——以高的导热性在芯片安装区域51中以及在线接合区域52中被用金属导电层覆盖。在此,线接合区域52和芯片安装区域51导电接触。在用作为热沉的载体上存在的另外的空缺是紧固元件,利用这些紧固元件可以将稍后制造的器件紧固在另外的元件上。

图5B示出通过层压技术的用于模块化构造的薄印刷电路板,该薄印刷电路板具有相应的空缺。该薄印刷电路板50a包括塑料,以一层或多层将不同的接触接触线55或58加入到该塑料中。在该薄印刷电路板的表面上布置有接触元件54、54a、56、56a和57。这些接触元件是暴露的,而为了防止损害可以用薄的保护层对接触线55进行覆盖。接触元件例如包括铜层或薄的铜镍金金属化层。接触焊片57中的一些通过引线55与接触焊片54连接。此外提供有中央空缺53,该中央空缺53实现稍后对根据图5A的结构化的芯片安装区域51以及结构化的线结合区域52的接入。另外的接触元件56a、56和57可以通过SMD技术装配不同的器件。

在下一步骤中,该薄印刷电路板被紧固、例如被层压在用作为热沉的载体50上。对此适宜的是,在层压以前在载体50上在芯片安装区域51和线接合区域52的空缺的下方施加薄的漆层。通过将印刷电路板层压在载体上,实现了薄印刷电路板与载体的紧密连接。同时载体继续起热沉作用。

接触元件54现在现在被布置为与空缺和结构化的芯片安装区域51相邻。另一接触部54a位于与载体50的结构化的线结合区域52相邻。

在图5D中示出的另一步骤中,现在借助于焊剂分发法在结构化的芯片安装区域51上施加焊膏。焊剂的流散通过芯片安装区域的结构化以及到第一和第二子区域的划分而受到阻止,其中芯片安装区域的第一子区域具有排斥焊剂的特征。由此,所施加的焊剂材料仅仅交联第二子区域。接着将半导体器件60布置在芯片安装区域上。焊膏通过附着力迫使各个光电器件到相应的第二子区域中,由此得出在图5D中示出的规则布置。

在该实施例中,在施加焊剂和光电器件以前对薄膜板进行层压。但是这不是强制性的。同样可以首先借助于不同的方法——例如焊剂分发法或者印刷法——将焊剂材料施加到芯片安装区域上并且由此紧固光电器件。接着然后将薄印刷电路板紧固在载体上。

在图5A至5D的实施例中,在芯片安装区域中紧固6个单个的“2*3”形式的光电器件。相应地,该芯片安装区域被划分成6个矩形的第二子区域。各个接触焊盘54通过接合线与光电器件60上的接触焊盘连接。结构化的线接合区域52通过接触线连接到层压板载体上的接触焊盘54a。

接着,可以借助于焊剂分发法在另外的接触焊盘上沉积出焊剂材料并且稍后紧固SMD器件59c、59b或芯片模块59a。所施加的护环61包围接触焊盘54、54a和具有芯片安装区域的空缺区域以及线接合区域51或52。通过护环61还可以替代于利用焊剂分发法还另外地利用丝网印刷或者模板印刷来施加用于接触焊盘56、57和56a的焊剂。

通过对芯片安装区域进行结构化以划分成第一和第二子区域,可以借助于焊剂材料将光电器件以及一般来说照明体紧固在预先良好定义的位置上。由此在大面积的芯片安装区域内改进各个器件的定位。

为此目的,第一子区域在结构化以外为排斥焊剂的,也就是说所施加的焊剂材料不交联该子区域。相应地,在焊剂材料上布置光电器件时,这些光电器件被焊机材料拉到第二子区域中并且在那里被固定。结构化例如可以通过相应地施加止焊层来进行。可替换地,还可以去除或氧化已经位于芯片安装区域中的用作为热沉的载体上的金属层,从而该金属层具有排斥焊剂的特征。恰好是后者在使用激光结构化方法的情况下实现了特别细微和窄的结构。

Claims (12)

1.用于制造照明用具的方法,包括:

—提供用作为热沉的载体(10a、4、50),该载体包括平面芯片安装区域(20、51);

—对所述平面芯片安装区域(51、20)进行结构化以产生第一子区域(17、24、21a、43)和至少一个第二子区域(12a、22a、22b、23、44),其中第一子区域(17、24、21a、43)在结构化以后为排斥焊剂的;

—在所述平面芯片安装区域(51、20)上施加焊剂,从而焊剂交联所述至少一个第二子区域(12a、22a、22b、23、44);

—在所述至少一个第二子区域(12a、22a、22b、23、44)中的焊剂上施加至少一个光电器件(100、60);

—构造适合于将电能引导到光电器件(100、60)的电接触;

—构造具有空缺的薄印刷电路板(50a)、至少一个金属印制导线(55)和至少一个接触区域(54);

—在载体上这样施加薄印刷电路板(50a),使得所述空缺位于芯片安装区域上方,其中施加至少一个光电器件(60)在施加薄印刷电路板(50a)之前或之后进行。

2.根据权利要求1的方法,其中第二子区域(12a、22a、22b、23、44)中的平面芯片安装区域(51、20)包括至少一个金属的、能被焊剂至少部分地交联的子层(12、42)。

3.根据权利要求1至2之一的方法,其中对所述平面芯片安装区域的结构化包括:

—在平面芯片安装区域(51、20)上施加止焊层(43),其中所述止焊层是排斥焊剂的;

—对止焊层进行结构化以产生第一和第二子区域(44);

—去除第二子区域(44)中的止焊层。

4.根据权利要求1至2之一的方法,其中对所述平面芯片安装区域的结构化包括:

—在平面芯片安装区域的第一子区域上施加止焊层,其中所述止焊层是排斥焊剂的;

—根据情况暴露和/或处理第二子区域的片段,从而该第二子区域具有能被焊剂交联的表面。

5.根据权利要求1至2之一的方法,其中对所述平面芯片安装区域的结构化包括:

—提供光学光源,优选激光器;

—通过照射平面芯片安装区域的第一子区域(17)来对平面芯片安装区域进行结构化以产生第二子区域(12a)。

6.根据权利要求5的方法,其中通过照射第一子区域使第一子区域的表面材料熔化或者蒸发并且使因此暴露的位于下方的材料氧化,其中被氧化的材料具有排斥焊剂的特征。

7.根据权利要求1至2之一的方法,其中所述提供用作为热沉的载体(50)包括提供具有芯片安装区域的载体,该芯片安装区域包括由至少两个子层构成的层序列(11、12),其中至少一个子层包括下列材料中的至少一种:

—镍;

—铜;

—铝;

—银;

—金;

—钛;

—钨。

8.根据权利要求1至2之一的方法,其中第一子区域至少沿着所述芯片安装区域的边缘延伸。

9.根据权利要求1至2之一的方法,其中至少两个相邻的第二子区域被第一子区域分隔开。

10.根据权利要求1至2之一的方法,其中所述构造电接触包括:

—将接触线接合到位于芯片安装区域之外的接触焊盘;

—将接触线接合到光电器件上的接触焊盘,其中所述接触焊盘电接触适于发光的层序列的子层。

11.根据权利要求1至2之一的方法,其中所述光电器件在其朝向焊剂那侧具有反射层。

12.根据权利要求1至2之一的方法,其中所述光电器件在其背对焊剂那侧具有接触焊盘。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102008063325.9 | 2008-12-30 | ||

| DE102008063325A DE102008063325A1 (de) | 2008-12-30 | 2008-12-30 | Verfahren zur Fertigung von Leuchtmitteln |

| PCT/DE2009/001693 WO2010075831A1 (de) | 2008-12-30 | 2009-11-27 | Verfahren zur fertigung von leuchtmitteln |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN102272925A CN102272925A (zh) | 2011-12-07 |

| CN102272925B true CN102272925B (zh) | 2014-01-01 |

Family

ID=41725366

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN200980153425.3A Active CN102272925B (zh) | 2008-12-30 | 2009-11-27 | 用于制造照明用具的方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US8809082B2 (zh) |

| EP (2) | EP2371000B1 (zh) |

| JP (1) | JP5766122B2 (zh) |

| KR (1) | KR101681343B1 (zh) |

| CN (1) | CN102272925B (zh) |

| DE (1) | DE102008063325A1 (zh) |

| WO (1) | WO2010075831A1 (zh) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102008063325A1 (de) | 2008-12-30 | 2010-07-01 | Osram Opto Semiconductors Gmbh | Verfahren zur Fertigung von Leuchtmitteln |

| US8816481B2 (en) * | 2011-11-04 | 2014-08-26 | Panasonic Corporation | Semiconductor device having a porous nickel plating part |

| DE102012215705B4 (de) * | 2012-09-05 | 2021-09-23 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Gehäuse für ein optisches bauelement, baugruppe, verfahren zum herstellen eines gehäuses und verfahren zum herstellen einer baugruppe |

| ITTR20120012A1 (it) * | 2012-11-20 | 2013-02-19 | Tecnologie E Servizi Innovativi T S I S R L | Mpcb-led-sink20 - circuito stampato su base metallica con trasferimento diretto del calore dal pad termico dei led di potenza allo strato metallico della mpcb con capacita' di abbassare la temperatura della giunzione del led di ulteriori 20 °c rispet |

| DE102013201775A1 (de) * | 2013-02-04 | 2014-08-07 | Osram Gmbh | Beleuchtungsmodul und Verfahren zur Herstellung eines Beleuchtungsmoduls |

| DE102013101262A1 (de) | 2013-02-08 | 2014-08-14 | Osram Opto Semiconductors Gmbh | Optoelektronisches Leuchtmodul, optoelektronische Leuchtvorrichtung und Kfz-Scheinwerfer |

| US9215794B2 (en) * | 2013-05-06 | 2015-12-15 | Shenzhen China Star Optoelectronics Technology Co., Ltd. | Circuit board and display device |

| DE102013215588A1 (de) * | 2013-08-07 | 2015-02-12 | Brose Fahrzeugteile GmbH & Co. Kommanditgesellschaft, Würzburg | Leiterplattenanordnung, Steuervorrichtung für ein Kühlerlüftermodul und Verfahren |

| JP2015176975A (ja) * | 2014-03-14 | 2015-10-05 | パナソニックIpマネジメント株式会社 | 半導体装置 |

| CN109188631B (zh) * | 2018-09-26 | 2022-06-24 | 昂纳信息技术(深圳)有限公司 | 一种尾纤的防脱落方法及光学装置 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101154656A (zh) * | 2006-09-30 | 2008-04-02 | 香港微晶先进封装技术有限公司 | 多芯片发光二极管模组结构及其制造方法 |

| DE102008001221A1 (de) * | 2007-04-24 | 2008-10-30 | Ceramtec Ag | Bauteil mit einem keramischen Körper mit metallisierter Oberfläche |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE2528000B2 (de) * | 1975-06-24 | 1979-12-20 | Licentia Patent-Verwaltungs-Gmbh, 6000 Frankfurt | Verfahren zur Herstellung einer Lötfläche relativ großer Abmessungen |

| US6546620B1 (en) * | 2000-06-29 | 2003-04-15 | Amkor Technology, Inc. | Flip chip integrated circuit and passive chip component package fabrication method |

| US6660559B1 (en) * | 2001-06-25 | 2003-12-09 | Amkor Technology, Inc. | Method of making a chip carrier package using laser ablation |

| DE10351120A1 (de) | 2003-11-03 | 2005-06-09 | eupec Europäische Gesellschaft für Leistungshalbleiter mbH | Lötstopbarriere |

| DE102004016697B4 (de) * | 2004-02-27 | 2007-10-11 | Osram Opto Semiconductors Gmbh | Verfahren zum Herstellen von Halbleiterchips umfassend ein Verbindungsverfahren, das Löten mit einem Lot umfasst, und Halbleiterchip |

| EP1575084B1 (en) * | 2004-03-01 | 2010-05-26 | Imec | Method for depositing a solder material on a substrate |

| DE102005031336B4 (de) | 2005-05-13 | 2008-01-31 | Osram Opto Semiconductors Gmbh | Projektionseinrichtung |

| CN100571353C (zh) | 2005-05-13 | 2009-12-16 | 奥斯兰姆奥普托半导体有限责任公司 | 投影设备 |

| KR100658939B1 (ko) | 2005-05-24 | 2006-12-15 | 엘지전자 주식회사 | 발광 소자의 패키지 |

| US20060289887A1 (en) * | 2005-06-24 | 2006-12-28 | Jabil Circuit, Inc. | Surface mount light emitting diode (LED) assembly with improved power dissipation |

| KR100699161B1 (ko) | 2005-10-06 | 2007-03-22 | 엘지전자 주식회사 | 발광 소자 패키지 및 그의 제조 방법 |

| KR20080007961A (ko) | 2006-07-19 | 2008-01-23 | 알티전자 주식회사 | 엘이디 모듈의 냉각 장치 및 그 제조 방법 |

| DE102006059127A1 (de) * | 2006-09-25 | 2008-03-27 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung einer Anordnung optoelektronischer Bauelemente und Anordnung optoelektronischer Bauelemente |

| JP5145729B2 (ja) | 2007-02-26 | 2013-02-20 | 富士電機株式会社 | 半田接合方法およびそれを用いた半導体装置の製造方法 |

| DE102008063325A1 (de) | 2008-12-30 | 2010-07-01 | Osram Opto Semiconductors Gmbh | Verfahren zur Fertigung von Leuchtmitteln |

-

2008

- 2008-12-30 DE DE102008063325A patent/DE102008063325A1/de not_active Withdrawn

-

2009

- 2009-11-27 KR KR1020117017729A patent/KR101681343B1/ko active IP Right Grant

- 2009-11-27 WO PCT/DE2009/001693 patent/WO2010075831A1/de active Application Filing

- 2009-11-27 US US13/142,391 patent/US8809082B2/en active Active

- 2009-11-27 EP EP09771691.4A patent/EP2371000B1/de active Active

- 2009-11-27 CN CN200980153425.3A patent/CN102272925B/zh active Active

- 2009-11-27 JP JP2011543974A patent/JP5766122B2/ja active Active

- 2009-11-27 EP EP12186956A patent/EP2544234A1/de not_active Withdrawn

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101154656A (zh) * | 2006-09-30 | 2008-04-02 | 香港微晶先进封装技术有限公司 | 多芯片发光二极管模组结构及其制造方法 |

| DE102008001221A1 (de) * | 2007-04-24 | 2008-10-30 | Ceramtec Ag | Bauteil mit einem keramischen Körper mit metallisierter Oberfläche |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2544234A1 (de) | 2013-01-09 |

| EP2371000A1 (de) | 2011-10-05 |

| DE102008063325A1 (de) | 2010-07-01 |

| JP5766122B2 (ja) | 2015-08-19 |

| KR20110100307A (ko) | 2011-09-09 |

| KR101681343B1 (ko) | 2016-11-30 |

| CN102272925A (zh) | 2011-12-07 |

| US20120107973A1 (en) | 2012-05-03 |

| WO2010075831A1 (de) | 2010-07-08 |

| US8809082B2 (en) | 2014-08-19 |

| JP2012514340A (ja) | 2012-06-21 |

| EP2371000B1 (de) | 2016-10-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN102272925B (zh) | 用于制造照明用具的方法 | |

| US9012926B2 (en) | Radiation-emitting semiconductor component | |

| TWI378554B (en) | Optoelectronic headlight, its manufacturing method and light-emitting diode chip | |

| US7683539B2 (en) | Light emitting device package and method for manufacturing the same | |

| EP1913436B1 (en) | Light emitting diode package and method of fabricating the same | |

| JP5372009B2 (ja) | オプトエレクトロニクス部品およびその製造方法 | |

| TWI300276B (en) | Substrate for mounting light-emitting element, light-emitting element module, and illumination apparatus | |

| KR101911707B1 (ko) | 배선 기판 및 배선 기판의 제조 방법 | |

| CN102165588B (zh) | 具有支承衬底和多个发射辐射的半导体器件的光电子模块及其制造方法 | |

| JP2011009572A (ja) | フリップチップ実装型led及びフリップチップ実装型ledの製造方法。 | |

| TWI809246B (zh) | 固晶結構及其製造方法 | |

| CN101904022B (zh) | 光电子器件 | |

| WO2013175990A1 (ja) | 照明装置 | |

| CN108133951A (zh) | 使用有机发光二极管的照明装置及其制造方法 | |

| CN108260259B (zh) | 使用有机发光器件的照明装置及其制造方法 | |

| US10217731B2 (en) | Method of producing optoelectronic modules and an assembly having a module | |

| CN103716991A (zh) | 用于led的pcb及其制造方法、发光装置及灯具 | |

| US11499688B2 (en) | Light device, headlight and method | |

| US20180138382A1 (en) | Method for manufacturing light emitting diode package | |

| JP4964638B2 (ja) | 照明装置及び照明装置の製造方法 | |

| TWI393243B (zh) | 變光發光元件及其製作方法 | |

| WO2017010818A1 (ko) | 발광 다이오드 패키지 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant |