CN100511405C - Integrated circuit device and electronic instrument - Google Patents

Integrated circuit device and electronic instrument Download PDFInfo

- Publication number

- CN100511405C CN100511405C CNB2006100903282A CN200610090328A CN100511405C CN 100511405 C CN100511405 C CN 100511405C CN B2006100903282 A CNB2006100903282 A CN B2006100903282A CN 200610090328 A CN200610090328 A CN 200610090328A CN 100511405 C CN100511405 C CN 100511405C

- Authority

- CN

- China

- Prior art keywords

- circuit

- data

- sub

- block

- integrated circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Elimination Of Static Electricity (AREA)

Abstract

The invention provides an integrated circuit device and electronic equipment including the same capable of reducing the circuit area. The integrated circuit device includes a driver macrocell in which a plurality of circuit blocks are integrated into a macrocell. The driver macrocell includes a data driver block DB for driving data lines, a memory block MB which stores image data, and a pad block PDB in which pads for electrically connecting output lines of the data driver block DB with the data lines are disposed. The data driver block DB and the memory block MB are disposed along a direction D1 , and the pad block PDB is disposed on the D2 side of the data driver block DB and the memory block MB.

Description

Technical field

The present invention relates to integrated circuit (IC) apparatus and electronic equipment.

Background technology

In the prior art, the integrated circuit (IC) apparatus as driving display panels such as liquid crystal panel has a kind of display driver (lcd driver).In this display driver,, require the size of dwindling chip in order to reduce cost.

But the size that is assembled in the display panel in pocket telephone etc. is roughly constant.Therefore, if the only simple integrated circuit (IC) apparatus that adopts trickle operation to dwindle display driver reaches the purpose of dwindling chip size, will bring a series of problems such as difficulty is installed.

Patent documentation: TOHKEMY 2001-222249 communique

Summary of the invention

The present invention has overcome above-mentioned technical matters, and purpose is to provide a kind of can realize the integrated circuit (IC) apparatus of circuit area downsizing and the electronic equipment that comprises this integrated circuit (IC) apparatus.

The present invention relates to a kind of integrated circuit (IC) apparatus, this integrated circuit (IC) apparatus comprises a plurality of circuit blocks by at least one driver macroelement of macroelementization, and described driver macroelement comprises: data driving block is used for driving data lines; Storage block, storage is used for the view data that described data driving block drives described data line; And pad piece, dispose and be used to be electrically connected the output line of described data driving block and the pad of described data line, wherein, described data driving block and described storage block dispose along first direction, will be with the direction of described first direction quadrature during as second direction, described pad piece be configured in the described second direction side of described data driving block and described storage block.

In the present invention, data driving block, storage block and pad piece are turned to the driver macroelement by integrated ground macroelement.And in this driver macroelement, data driving block and storage block dispose along first direction, and the pad piece is configured in the second direction side of data driving block and storage block.If macroelement data driving block, pad piece etc. like this can use the piece of distribution of for example finishing the output line of the data driving block on pad by manual layout as the driver macroelement.Therefore, can dwindle the distribution zone of output line, realize the small sizeization of integrated circuit (IC) apparatus.And, because not only the zone of the second direction side of data driving block can be used as the pad configuration district, and the zone of the second direction side of storage block also can be used as the pad configuration district and is used, thus can be not lavishly with pad configuration on the pad piece, improve positioning efficiency.By macroelementization, do not need each data driving block is made independent pad piece, thereby can shorten design time.

And, in the present invention, also can with described data driving block the width on the described first direction be made as WDB, described storage block be made as WMB at the width on the described first direction, when the width of described pad piece on described first direction is made as WPB, WDB+WMB≤WPB.

If this relation is set up, just can lavishly pad be arranged in the pad piece, thus the small sizeization of realization integrated circuit (IC) apparatus.

And, in the present invention, also can WDB, the width of described storage block on described first direction be made as WMB, the width of described additional circuit blocks on described first direction was made as number that the solder pad space length of described pad on described first direction in WAB, the described pad piece be made as PP, pad when being made as NP when described driver macroelement comprised adjunct circuit in that described data driving block is made as at the width on the described first direction, (NP-1) * PP<WDB+WMB+WAB<(NP+1) * PP.

If this relation is set up,, can arrange pad with the solder pad space length of equalization just can not produce the useless space of vacating.

And, in the present invention, also can WDB+WMB+WAB≤NP * PP.

And in the present invention, described additional circuit blocks also can be the forwarding piece that comprises impact damper, and wherein, described impact damper is exported to described storage block after the write data signal at least that transfers to described storage block is carried out buffer memory again.

If design this forwarding piece,, can realize the correct data of storage block are write just can reduce the rising waveform of the write data signal that transfers to storage block and weakening of falling waveform as additional circuit blocks.

And, in the present invention, also can comprise a plurality of described driver macroelements, and described a plurality of driver macroelements dispose along described first direction.

Like this, as long as along first direction configuration driven device macroelement, pad piece, data driving block, storage block are disposed along first direction, thereby can realize integrated circuit (IC) apparatus layout efficiently.And, by macroelementization, need not each data driving block is made independent pad piece, thereby can shorten design time.

And, in the present invention, described data driving block also can comprise a plurality of sub-pixel driver elements, each described sub-pixel driver element output is corresponding to the data-signal of the view data of a sub-pixel, and, in described data driving block, when a plurality of described sub-pixel driver elements disposed along described first direction, a plurality of described sub-pixel driver elements disposed along described second direction.

If the antithetical phrase pixel drive unit is carried out matrix configuration like this, can carry out topological design flexibly according to the specification of data driver.

And, the invention still further relates to a kind of following integrated circuit (IC) apparatus, this integrated circuit (IC) apparatus comprises at least one data driving block that is used for driving data lines, described data driving block comprises a plurality of sub-pixel driver elements, each described sub-pixel driver element output is corresponding to the data-signal of the view data of a sub-pixel, when will be along the long side direction of described sub-pixel driver element as first direction, with the direction of described first direction quadrature during as second direction, in described data driving block, when a plurality of described sub-pixel driver elements dispose along described first direction, a plurality of described sub-pixel driver elements dispose along described second direction, and, be used to be electrically connected the described second direction side of the pad configuration of the output line of described data driving block and described data line in described data driving block.

In the present invention, when a plurality of sub-pixel driver elements dispose along the first direction as its long side direction, dispose along second direction with the first direction quadrature.And the second direction side configuration at the sub-pixel driver element of matrix configuration like this is used to be electrically connected the output line of data driving block (sub-pixel driver element) and the pad of data line.So, because the sub-pixel driver element is along the first direction stack arrangement as its long side direction, thereby can dwindle width as the data driving block on the second direction of the short side direction of sub-pixel driver element.And can effectively utilize the zone of vacating of second direction side of the sub-pixel driver element of matrix configuration to dispose pad.Thus, realized the small sizeization of integrated circuit (IC) apparatus.

And in the present invention, each the sub-pixel driver element in described a plurality of sub-pixel driver elements also can comprise: dispose first circuit region with the circuit of the power work of first voltage level; With the second circuit district that disposes with the circuit of the power work of second voltage level that is higher than first voltage level, and described a plurality of sub-pixel driver elements are configured to: between the described second circuit district of each sub-pixel driver element or between described first circuit region along described first direction adjacency.

So, compare with the method for second circuit district adjacency, can dwindle the width of data driving block on first direction, realize the small sizeization of integrated circuit (IC) apparatus with making first circuit region.

And, in the present invention, also can dispose the latch cicuit that latchs view data at described first circuit region, dispose the D/A converter that carries out the D/A conversion of view data with gray scale voltage in described second circuit district.

And, in the present invention, also can comprise at least one storage block of storing image data, described first circuit region of described storage block and described sub-pixel driver element is in abutting connection with configuration.

So since with first circuit region of the storage block of the power work of first voltage level and sub-pixel driver element in abutting connection with configuration, thereby can improve positioning efficiency.

And, in the present invention, described sub-pixel driver element also can comprise the D/A converter that carries out the D/A conversion of view data with gray scale voltage, be used for providing the gray scale voltage supply line of described gray scale voltage to stride across a plurality of described sub-pixel driver elements, along described second direction distribution to described D/A converter.

So, by can be efficiently along the gray scale voltage supply line of second direction distribution providing gray scale voltage, thereby improve positioning efficiency to D/A converter along a plurality of sub-pixel driver elements of second direction configuration.

And, in the present invention, described gray scale voltage supply line also can be on the configuring area of described D/A converter distribution.

In addition, comprise at D/A converter under the situation of gray scale voltage selector switch etc. for example, preferably distribution gray scale voltage supply line on the configuring area of this gray scale voltage selector switch.

And, in the present invention, also can be in the configuring area of the described D/A converter of described sub-pixel driver element, along described second direction configuration N transistor npn npn zone, P transistor npn npn zone, in the configuring area of the circuit except that described D/A converter of described sub-pixel driver element, along described first direction configuration N transistor npn npn zone, P transistor npn npn zone.

So, can be to being connected the gray scale voltage supply line jointly along the N transistor npn npn in the N transistor npn npn zone of second direction configuration and the P transistor npn npn in P transistor npn npn zone, thus improve positioning efficiency.On the other hand, if along N transistor npn npn zone, the P transistor npn npn zone of the circuit outside first direction and the row arrangement D/A converter, just can carry out along the layout efficiently of the flow direction of signal.

And, the invention still further relates to a kind of following electronic equipment, this electronic equipment comprises above arbitrary described integrated circuit (IC) apparatus and the display panel that is driven by described integrated circuit (IC) apparatus.

Description of drawings

Fig. 1 (A), (B), (C) are the key diagrams of the comparative example of present embodiment.

Fig. 2 (A), (B) are the mounting list figure of integrated circuit (IC) apparatus.

Fig. 3 is the synoptic diagram of configuration example of the integrated circuit (IC) apparatus of present embodiment.

Fig. 4 is the synoptic diagram of the example of various types of display drivers and built-in circuit block thereof.

Fig. 5 (A), (B) are the synoptic diagram of plane figure example of the integrated circuit (IC) apparatus of present embodiment.

Fig. 6 (A), (B) are the synoptic diagram of example of the cut-open view of integrated circuit (IC) apparatus.

Fig. 7 is the synoptic diagram of the circuit configuration example of integrated circuit (IC) apparatus.

Fig. 8 (A), (B), (C) are the synoptic diagram of the configuration example of data driver, scanner driver.

Fig. 9 (A), (B) are the synoptic diagram of the configuration example of power circuit, gray scale voltage generative circuit.

Figure 10 (A), (B), (C) are the synoptic diagram of the configuration example of D/A change-over circuit, output circuit.

Figure 11 (A), (B) are the key diagrams of the macroelement method of present embodiment.

Figure 12 (A), (B) also are the key diagrams of the macroelement method of present embodiment.

Figure 13 is a configuration example of transmitting piece.

Figure 14 (A), (B) are the key diagrams of the piece dividing method of storer, data driver.

Figure 15 is a key diagram of repeatedly reading the view data method in the horizontal scan period.

Figure 16 is the synoptic diagram of the configuration example of data driver, driver element.

Figure 17 is the synoptic diagram of the configuration example of sub-pixel driver element.

Figure 18 is the synoptic diagram of the configuration example of sensor amplifier, storage unit.

Figure 19 is the synoptic diagram of the structure example of sub-pixel driver element.

Figure 20 is the synoptic diagram of the configuration example of D/A converter.

Figure 21 (A), (B), (C) are the truth table of sub-decoder of D/A converter and the key diagram of D/A converter layout.

Figure 22 is the key diagram to the wiring method of pad.

Figure 23 (A), (B) are the synoptic diagram of the configuration example of electronic equipment.

Embodiment

Below, describe the preferred embodiment of the invention in detail.And below Shuo Ming present embodiment is not limited to described year content of the present invention of claimed scope, and also not limiting the illustrated formation of present embodiment is necessary solution of the present invention all.

1. comparative example

Fig. 1 (A) expression is as the integrated circuit (IC) apparatus 500 of the comparative example of present embodiment.The integrated circuit (IC) apparatus 500 of Fig. 1 (A) comprises storage block MB (video data RAM) and data driving block DB.And storage block MB and data driving block DB dispose along the D2 direction.In addition, storage block MB, data driving block DB's is in a ratio of long super flat piece along the length of D1 direction and width in the D2 direction.

View data from host computer side is written into storage block MB.Then, data driving block DB is transformed to the data voltage of simulation to the Digital Image Data of writing into storage block MB, drives the data line of display panel then.Like this, picture signal stream is the D2 direction in Fig. 1 (A).Therefore, in Fig. 1 (A) comparative example, according to this signal flow, storage block MB and data driving block DB dispose along the D2 direction.So, between the input and output short path, can optimize the delay of signal, can the good signal of transfer efficiency.

Yet,, have following technological deficiency for the comparative example of Fig. 1 (A).

The first, with regard to integrated circuit (IC) apparatus such as driver,, require the size of dwindling chip for cost degradation., if adopt microfabrication, and, be not only short side direction, and company commander's edge direction is also reduced by dwindling integrated circuit (IC) apparatus 500 merely to dwindle chip size.So, cause the installation difficult technologies defective shown in Fig. 2 (A).That is to say that even preferably export spacing for example more than or equal to 22 μ m,, because the spacing after the dwindling merely as Fig. 2 (A) shown in for example has only 17 μ m, spacing is too narrow, becomes difficult so install.Moreover the instrument bezel of display panel broadens, and the peek of glass reduces, and causes cost to increase.

The second, in display driver, according to technical specification of kind (amorphism TFT, low temperature polycrystalline silicon TFT), pixel count (QCIF, QVGA, VGA) and the product of display panel etc., the formation of storer and data driver changes to some extent.So, with regard to the comparative example of Fig. 1 (A), even the product that has is shown in Fig. 1 (B), the unit interval of its solder pad space length, storer is consistent with the unit interval of data driver, as long as the formation of storer and data driver changes, shown in Fig. 1 (C), their spacing is also just inconsistent.And, shown in Fig. 1 (C),, between circuit block,, have to form unnecessary distribution zone in order to absorb the inconsistent of spacing if spacing is inconsistent.Particularly, for the comparative example that at D1 direction piece is flat Fig. 1 (A), it is bigger to be used to absorb the inconsistent unnecessary distribution of spacing zone.Consequently, the width W of the D2 direction of integrated circuit (IC) apparatus 500 increases, and chip area increases, and causes the increase of cost.

On the other hand, for fear of this class state of affairs, for solder pad space length and unit interval being evened up change the layout of storer and data driver, this causes the construction cycle to prolong again, and the result causes cost to increase.That is to say that for the comparative example of Fig. 1 (A), the circuit of each circuit block constitutes and layout all designs separately, adjust the operation of spacing again, thereby generate unnecessary dummy section, and cause designing problem such as poor efficiencyization.

2. the formation of integrated circuit (IC) apparatus

Fig. 3 illustrates the formation of the integrated circuit (IC) apparatus 10 of the present embodiment that can solve above-mentioned technological deficiency.With regard to present embodiment, from the minor face of integrated circuit (IC) apparatus 10 promptly the first limit SD1 towards the direction of the 3rd limit SD3 on opposite as first direction D1, the opposite direction of D1 as third direction D3.From the long limit of integrated circuit (IC) apparatus 10 promptly the second limit SD2 towards the direction of the 4th limit SD4 on opposite as second direction D2, the opposite direction of D2 as the four directions to D4.In addition, in Fig. 3, though the left side of integrated circuit (IC) apparatus 10 is the first limit SD1, the right is the 3rd limit SD3,, also can be that the left side is that the 3rd limit SD3, the right are the first limit SD1.

As shown in Figure 3, the integrated circuit (IC) apparatus 10 of present embodiment comprises along the first~the N the circuit block CB1~CBN (N is the integer more than or equal to 2) of D1 direction configuration.That is in the comparative example of Fig. 1 (A), circuit block is arranged along the D2 direction, and in the present embodiment, circuit block CB1~CBN arranges along the D1 direction.And each circuit block is super flat piece unlike the comparative example of Fig. 1 (A), but relatively near square piece.

In addition, integrated circuit (IC) apparatus 10 is included in the D2 direction side of circuit block CB1~CBN of the first~the N along outgoing side I/F district 12 (broad sense is first interface area) that limit SD4 is provided with.And comprise the input side I/F district 14 (broad sense is second interface area) that is provided with along limit SD2 in the D4 direction side of the first~the N circuit block CB1~CBN.More particularly, outgoing side I/F district 12 (first I/O district) is configured in D2 direction one side of circuit block CB1~CBN, and not by for example other circuit block.And input side I/F district 14 (second I/O district) also directly is not configured in D4 direction one side of circuit block CB1~CBN by for example other circuit block.That is only there is a circuit block (data driving block) in the part that exists in data driving block in the D2 direction at least.In addition, in that (Intellectual Property: intellecture property) core is used, and when being assembled in other integrated circuit (IC) apparatus, also can form the formation that is not provided with in the I/F district 12,14 at least one as IP integrated circuit (IC) apparatus 10.

Outgoing side (display panel side) I/F district 12 is and display panel forms the zone of interface, and the output that comprise pad, is connected in pad is with various elements such as transistor and protecting components.Specifically, comprise to the data line outputting data signals, to the output of sweep trace output scanning signal with transistor etc.In addition, when display panel is touch panel etc., also can comprise the input transistor.

Input side (host computer side) I/F district 14 is and main frame (MPU, image process controller, baseband engine) forms the zone of interface, and input (I/O with) transistor, output that can comprise pad, is connected in pad is with various elements such as transistor and protecting components.Specifically, the input that comprises the signal (digital signal) that is used to import from main frame with transistor, be used for to the output of main frame output signal with transistor etc.

In addition, also can be provided with along minor face is outgoing side or the input side I/F district of limit SD1, SD3.In addition, also can be arranged on I/F (interface) district 12,14, also can be arranged on zone beyond it (the first~the N circuit block CB1~CBN) as the projection of external connection terminals etc.During regional beyond being located at I/ F district 12,14, can adopt the small-sized protruding technology (is the protruding technology of core with the resin) beyond the metal bump to realize.

The first~the N circuit block CB1~CBN can comprise the circuit block (circuit block that possesses difference in functionality) that two (perhaps three) are different at least.With integrated circuit (IC) apparatus 10 is that the situation of display driver is an example, and circuit block CB1~CBN can comprise as two circuit blocks in data driver, storer, scanner driver, logical circuit, grayscale voltage generation circuit and the power circuit at least.More particularly, circuit block CB1~CBN can comprise data driving block and logic circuit block at least, and, can comprise the grayscale voltage generation circuit piece.In addition, under the situation of internal memory, can also comprise storage block.

For example, Fig. 4 represents the example of the circuit block of various types of display drivers and built-in display driver.(Thin FilmTransistor: thin film transistor (TFT)) panel is with regard to display driver, and circuit block CB1~CBN comprises storer, data driver (source electrode driver), scanner driver (gate drivers), logical circuit (gate-array circuit), grayscale voltage generation circuit (checking gamma circuit) and these circuit blocks of power circuit with regard to the amorphism TFT of internal memory (RAM).On the other hand, with regard to low temperature polycrystalline silicon (LTPS) the TFT panel of memory built-in is used display driver,, can omit the scan drive circuit piece because can on glass substrate, form scanner driver.And, can omit storage block for the non-built-in amorphism TFT panel of storer, for the non-built-in low temperature polycrystalline silicon TFT panel of storer, can omit the circuit block of storer and scanner driver.In addition, with regard to CSTN (Color Super Twisted Nematic) panel, TFD (Thin Film Diode: thin film diode) with regard to the panel, then can omit the grayscale voltage generation circuit piece.

The example of the plane figure of the display-driver Ics device 10 of Fig. 5 (A), Fig. 5 (B) expression present embodiment.Fig. 5 (A), Fig. 5 (B) are the examples that the amorphism TFT panel of memory built-in is used, and for example Fig. 5 (A) is target with QCIF, 32 rank with display driver, and Fig. 5 (B) is target with QVGA, 64 rank with display driver then.

With regard to Fig. 5 (A), (B), its first~the N circuit block CB1~CBN comprises first~the 4th storage block MB1~MB4 (broad sense is the first~the I storage block, and I is the integer more than or equal to 2).Corresponding with each first~the 4th storage block MB1~MB4, comprise along the D1 direction its separately in abutting connection with the configuration first~the 4th data driving block DB1~DB4 (broad sense is the data driving block of the first~the I).Specifically, storage block MB1 and data driving block DB1 be along D1 direction disposed adjacent, storage block MB2 then with data driving block DB2 along D1 direction disposed adjacent.And data driving block DB1 is used for the storage block MB1 storage of the view data (video data) of driving data lines by adjacency, and data driving block DB2 is used for the view data of driving data lines and is then stored by the storage block MB2 of adjacency.

In Fig. 5 (A), (broad sense is the J storage block to the MB1 in storage block MB1~MB4, the DB1 (broad sense be J data driving block) of D3 direction one side of 1≤J<I) in configuration data drive block DB1~DB4.In addition, in the D1 of storage block MB1 direction one side in abutting connection with configuration store piece MB2 (broadly being the storage block of J+1).Then, in the D1 of storage block MB2 direction one side in abutting connection with configuration data drive block DB2 (broadly being the data driving block of J+1).The configuration of storage block MB3, MB4, data driving block DB3, DB4 also is the same.Like this, in Fig. 5 (A), with respect to the boundary line of MB1, MB2, MB1, DB1 and MB2, DB2 dispose symmetrically, and with respect to the boundary line of MB3, MB4, MB3, DB3 and MB4, DB4 dispose symmetrically.In addition, in Fig. 5 (A), though DB2 and DB3 in abutting connection with configuration,, not in abutting connection with and to dispose other circuit block betwixt also passable.

On the other hand, among Fig. 5 (B), for D3 direction one side of the MB1 among storage block MB1~MB4 (broadly the being the J storage block) DB1 (J data driving block) in configuration data drive block DB1~DB4.In addition, the D1 of storage block MB1 direction one side in abutting connection with the configuration DB2 (data driving block of J+1).The D1 of DB2 direction one side in abutting connection with the configuration MB2 (storage block of J+1).DB3, MB3, DB4, MB4 dispose too.In addition, though MB1 and DB2, MB2 and DB3, MB3 and DB4 are respectively in abutting connection with configuration in Fig. 5 (B),, not in abutting connection with and to dispose other circuit block betwixt also passable.

According to the configuration of Fig. 5 (A), has the advantage of (between the storage block of J, J+1) common column address decoder between storage block MB1 and MB2 and MB3 and MB4.On the other hand, according to the configuration of Fig. 5 (B), the wiring closet that can make the data-signal output line from data driving block DB1~DB4 to outgoing side I/F district 12 has the advantage that can improve wiring efficiency apart from homogenising.

The layout of the integrated circuit (IC) apparatus 10 of present embodiment is not to be defined in Fig. 5 (A), (B).For example, the number of blocks of storage block and data driving block also can be 2,3 or more than or equal to 5, also can storage block and data driving block not carried out cutting apart of piece and is constituted.And, also can implement the non-conterminous embodiment of storage block and data driving block.And, be not fine even do not establish such formations such as storage block, scanner driver piece, power circuit piece or grayscale voltage generation circuit piece yet.Between circuit block CB1~CBN and outgoing side I/F district 12 or input side I/F district 14, also can be arranged on the extremely narrow circuit block (smaller or equal to the elongated circuit block of WB) of width on the D2 direction.In addition, circuit block CB1~CBN can also comprise the circuit block of different circuit blocks in the multistage arrangement of D2 direction.For example, also can be scan drive circuit and power circuit as a circuit block.

The integrated circuit (IC) apparatus 10 of Fig. 6 (A) expression present embodiment is along the example of the sectional view of D2 direction.W1, WB, W2 are respectively outgoing side I/F district 12, circuit block CB1~CBN, input side I/F district 14 width in the D2 direction among the figure.In addition, W is the width of integrated circuit (IC) apparatus 10 in the D2 direction.

For present embodiment, shown in Fig. 6 (A), on the D2 direction, can be not between circuit block CB1~CBN (data driving block DB) and outgoing side, input side I/ F district 12,14, do not sandwich other circuit block and constitute.So, just can make W1+WB+W2≤W<W1+2 * WB+W2, can realize elongated integrated circuit (IC) apparatus.Specifically, the width W<2mm of D2 direction can be made, more specifically, W<1.5mm can be made.And consider the inspection and the assembling of chip, preferred W〉0.9mm.In addition, the length L D of long side direction then can accomplish 15mm<LD<27mm.The shape of chip can be accomplished SP than SP=LD/W〉10, more particularly, and SP〉12.

Width W 1, WB, the W2 of Fig. 6 (A) is respectively the width of the transistor formation region (body region, active region) in outgoing side I/F district 12, circuit block CB1~CBN, input side I/F district 14.That is the transistor of transistor and electrostatic protection element etc. is used in 12,14 formation outputs with transistor, I/O with transistor, input in the I/F district.In addition, form the transistor of forming circuit in circuit block CB1~CBN zone.And, determine W1, WB, W2 with well region and the diffusion region that forms this transistorlike as benchmark.For example, in order to realize more elongated integrated circuit (IC) apparatus, hope is also to form projection (active face projection) on the transistor of circuit block CB1~CBN.Concrete, (active region) forms with resin and forms its core, forms the resin core projection of metal level etc. on the surface of resin on transistor.And this projection (external connection terminals) is connected on the pad that is configured in I/F district 12,14 by metal wiring.The W1 of present embodiment, WB, W2 are not the width in the formation zone of such projection, but the width in the transistor formation region territory that below projection, forms.

The width of each comfortable D2 direction of circuit block CB1~CBN for example can be unified for wide.At this moment, as long as the width of each circuit block is identical in fact just passable, the difference that several μ m~20 μ m (tens of μ m) degree is for example arranged is in permissible range.And when having the different circuit block of width in circuit block CB1~CBN, width W B can be a maximum width in the width of circuit block CB1~CBN.The breadth extreme of this moment can be the width in the D2 direction of data driving block for example.Perhaps, under the situation of the integrated circuit (IC) apparatus of memory built-in, can be the width in the D2 direction of storage block.The dummy section of for example wide 20~30 μ m degree can be set between circuit block CB1~CBN and I/ F district 12,14 in addition.

With regard to present embodiment, in outgoing side I/F district 12, can be configured in the pad of the progression of D2 direction for one or more levels.So if consider pad width (for example 0.1 μ m) and solder pad space length, the width W 1 in the D2 direction in outgoing side I/F district 12 can be accomplished 0.13mm≤W1≤0.4mm.In addition, because can be configured in the pad of the progression of D2 direction in input side I/F district 14, so the width W 2 in input side I/F district 14 just can be accomplished 0.1mm≤W2≤0.2mm for one or more levels.In order to realize elongated integrated circuit (IC) apparatus, need to form from the logical signal of logic circuit block, from the gray scale voltage signal of grayscale voltage generation circuit piece and the distribution of power supply by global lines on circuit block CB1~CBN, the total width of this class distribution is for example in the degree of 0.8~0.9mm.Thereby, considering these situations, the width W B of circuit block CB1~CBN can accomplish 0.65≤WB≤1.2mm.

And even W1=0.4mm, W2=0.2mm is because of 0.65≤WB≤1.2mm, so WB〉the W1+W2 establishment.In addition, all be under the situation of minimum value at W1, WB, W2, i.e. W1=0.13mm, WB=0.65mm, W2=0.1mm, the width of integrated circuit (IC) apparatus is W=0.88mm.So W=0.88mm<2 * WB=1.3mm sets up.At W1, WB, W2 all is under the peaked situation, W1=0.4mm, WB=1.2mm, W2=0.2mm, and then the width of integrated circuit (IC) apparatus is the degree of W=1.8mm.So W=1.8mm<2 * WB=2.4mm sets up.Therefore, relational expression W<2 * WB sets up, and can realize elongated integrated circuit (IC) apparatus.

For the comparative example of Fig. 1 (A), shown in Fig. 6 (B), dispose plural a plurality of circuit block along the D2 direction.In addition, in the D2 direction, be formed with the distribution zone between the circuit block and between circuit block and I/F district.So integrated circuit (IC) apparatus 500 just broadens in the width W of D2 direction (short side direction), can not realize tall and thin elongated chips.Thereby even utilize microfabrication that chip is shunk, still, shown in Fig. 2 (A), because the length L D of D1 direction (long side direction) shortens, the output spacing becomes thin space, so, cause installing difficulty.

At this technological deficiency, shown in Fig. 3, Fig. 5 (A), Fig. 5 (B), in the present embodiment, dispose a plurality of circuit block CB1~CBN along the D1 direction.In addition, shown in Fig. 6 (A), can be configured in following (the active face projection) of pad (projection) to transistor (circuit component).By the global lines that the upper strata (lower floor of pad) in the local line of the inner distribution of circuit block forms, also can form between the circuit block or the signal wire between circuit block and the I/F zone etc.So, shown in Fig. 2 (B), can the width W of D2 direction be narrowed down in integrated circuit (IC) apparatus 10, realize super tall and thin elongated chips.The result is, the output spacing is for example maintained more than or equal to 22 μ m, can easily install.。

And, in the present embodiment, owing to dispose a plurality of circuit block CB1~CBN along the D1 direction, so can easily tackle the change of product specification.That is, because can be with the product of public platform design all size, so can improve design efficiency.For example in Fig. 5 (A), (B), having to increase at the pixel count of display panel or grey exponent number has under the situation about subtracting, and only needs the piece number of increase and decrease storage block and data driving block, the reading times etc. of view data just can correspondence in a horizontal scan period.In addition, though Fig. 5 (A), (B) are the amorphism TFT panel examples of memory built-in,, at the low temperature polycrystalline silicon TFT panel of exploitation memory built-in with under the situation of product, as long as from circuit block CB1~CBN, remove the scanner driver piece.And for example, under the situation of the non-built-in product of exploitation storer, as long as remove storage block.And, as mentioned above, even remove circuit block according to specification, in the present embodiment, because the influence that other circuit block is produced can be suppressed to minimum, so can improve design efficiency.

In the present embodiment, can be unified in for example width (highly) of data driving block and storage block to each circuit block CB1~CBN at the width (highly) of D2 direction.And, have under the situation of increase and decrease at the transistor of each circuit block, owing to can adjust in the length of D1 direction, design further high efficiency so can make by increasing and decreasing each circuit block.For example, in Fig. 5 (A), (B), under the situation that formation changes, number of transistors increases and decreases of grayscale voltage generation circuit piece and power circuit piece, also can come corresponding in the length of D1 direction by increase and decrease grayscale voltage generation circuit piece and power circuit piece.

In addition,, it is also conceivable that following collocation method: for example, on the D1 direction, data driving block is slenderly disposed, in the D4 of data driving block direction one side, along other a plurality of circuit blocks such as D1 direction configuration store pieces as second comparative example.But,,,, be difficult to realize tall and thin elongated chips so integrated circuit (IC) apparatus broadens in the width W of D2 direction because the data driving block of amplitude broad sandwiches between other circuit block such as storage block and the outgoing side I/F zone for this second comparative example.And, between data driving block and memory drives piece, produced unnecessary distribution zone, just enlarged width W more.Under the situation that the formation of data driving block or storage block changes, appear at inconsistent problem of spacing of explanation among Fig. 1 (B), (C), can't improve design efficiency.

As the 3rd comparative example of present embodiment, only it is also conceivable that circuit block (for example data driving block) to same function carries out cutting apart of piece and along the method for D1 direction alignment arrangements.But,,, can not realize the expansion of multiple product owing to can only make integrated circuit (IC) apparatus have same function (for example data driver function) for the 3rd comparative example.At this problem, in the present embodiment, circuit block CB1~CBN comprises the circuit block that has two difference in functionalitys at least.So, shown in Fig. 4, Fig. 5 (A), Fig. 5 (B), have the advantage that can provide corresponding to the multimachine kind integrated circuit (IC) apparatus of all kinds display panel.

3. circuit constitutes

Fig. 7 represents that the circuit of integrated circuit (IC) apparatus 10 constitutes.And the circuit of integrated circuit (IC) apparatus 10 constitutes the example that is not limited to Fig. 7, can implement various distortion.Storer 20 (video data RAM) is used for storing image data.Memory cell array 22 comprises a plurality of storage unit, stores the view data of a frame (width of cloth picture) at least.At this moment, a pixel is made of three sub-pixels (3 points) such as for example R, G, B, and each sub-pixel is for example being stored the view data of six (k positions).Row address decoder 24 (a few CD row address decoder of MPU) is carried out the decoding of relevant row address and is handled the selection processing of the word line of the line storage unit of going forward side by side array 22.Column address decoder 26 (MPU column address decoder) is then carried out the decoding of relevant column address and is handled the selection processing of the bit line of the line storage unit of going forward side by side array 22.Writing/Reading circuit 28 (MPU Writing/Reading circuit) carries out the processing of view data write storage unit array 22 and reads the processing of view data from memory cell array 22.With for example with start address and end address for the rectangle on summit being come the accessing zone of define storage units array 22.That is, define accessing zone, the access of the line storage of going forward side by side with the column address of start address and the column address and the row address of row address and end address.

Logical circuit 40 (for example disposing wiring circuit automatically) generates to be used to control and shows control signal constantly and be used for control data processing control signal constantly etc.This logical circuit 40 can be formed by automatic configuration distributions such as for example gate arrays (G/A).Control circuit 42 generates various control signals, carries out the control of device integral body.Specifically, to the adjustment data (γ correction data) of grayscale voltage generation circuit 110 output gray-level characteristics (γ characteristic), and the voltage of control power circuit 90 generates.In addition, the storer that has used row address decoder 24, column address decoder 26, Writing/Reading circuit 28 is carried out the control that Writing/Reading is handled.Showing constantly that control circuit 44 generates to be used to control shows various control signals constantly, the reading of the view data of control from the storer to the display panel side.46 pairs of each visits from main frame of main frame (MPU) interface circuit generate internal pulses, realize the main interface that storer is conducted interviews.Rgb interface circuit 48 is by the rgb interface of Dot Clock realization with the RGB writing data into memory of animation.And, also can be any one the formation that only is provided with in master interface circuit 46, the rgb interface circuit 48.

In Fig. 7, conduct interviews to storer 20 with a pixel unit from master interface circuit 46, rgb interface circuit 48.On the other hand, according to showing constantly with master interface circuit 46, rgb interface circuit 48 are independently inner, each line period with the specified capable unit of row address to data driver 50 transport picture data.

Grayscale voltage generation circuit (checking gamma circuit) the 110th is used to generate the circuit of gray scale voltage, and its formation is shown in Fig. 9 (B).Select to select with voltage VS0~VS255 (broad sense is R and selects to use voltage) according to high-tension supply voltage VDDH, the VSSH output that generates by power circuit 90 with voltage generation circuit 112 (bleeder circuit).Specifically, select to comprise the ladder resistor circuit of a plurality of resistive elements with series connection with voltage generation circuit 112.And, will VDDH, VSSH voltage after partial be exported with voltage VS0~VS255 as selecting by this ladder resistor circuit.Gray scale voltage selects circuit 114 according to the adjustment data that are set in the gray-level characteristic of adjusting register 116 by logical circuit 40, from selecting, for example under the situation on 64 rank, select 64 (broadly to be S with voltage VS0~VS255, R〉S) voltage, as gray scale voltage V0~V63 output.Like this, can generate the gray scale voltage of the preferred gray-level characteristic (γ correcting feature) that is adapted to display panel.And under the situation that reversal of poles drives, also the ladder resistor circuit used of the ladder resistor circuit that can use positive polarity and negative polarity is arranged on and selects with in the voltage generation circuit 112.In addition, the resistance of each resistive element of ladder resistor circuit also can be according to adjusting the adjustment data change that register 116 is set.It also can be the formation that impedance inverter circuit (operational amplifier that connects voltage follower) is set in selecting with voltage generation circuit 112 or gray scale voltage selection circuit 114.

Figure 10 (A) expression comprises the configuration example of each DAC (Digital Analog Converter, digital to analog converter) of the D/A change-over circuit 54 of Fig. 8 (A).Each DAC of Figure 10 (A) can be provided with by each sub-pixel (perhaps each pixel), and is made of ROM code translator etc.And, according to six bit digital view data D0~D5 and reversal data XD0~XD5 thereof from storer 20, select among the gray scale voltage V0~V63 of grayscale voltage generation circuit 110 any, thus, D0~D5 converts aanalogvoltage to view data.And, the analog voltage signal DAQ of gained (DAQR, DAQG, DAQB) is outputed to output circuit 56.

Display driver of using for low temperature polycrystalline silicon TFT etc., R is carried out being delivered to after the multipath conversion with data-signal with, B with, G under the situation of display driver (under the situation of Figure 10 (C)), can carry out D/A conversion with, G with the pictorial data that, B uses to R with a public DAC.In this case, each DAC of Figure 10 (A) is provided with by each pixel.

Figure 10 (B) illustrates the formation of each contained output SQ of the output circuit 56 of Fig. 8 (A).Each output SQ of Figure 10 (B) can be provided with by each pixel.Each output SQ comprises R (red) usefulness, G (green) usefulness, B (indigo plant) impedance inverter circuit OPR, OPG, OPB (operational amplifier that connects voltage follower), carry out signal DAQR, the DAQG from DAC, the impedance conversion of DAQB, and data-signal DATAR, DATAG, DATAB are outputed to R, G, B data-signal output line.For example under the situation of low temperature polycrystalline silicon TFT panel, on-off element (switch transistor) SWR, SWG, SWB shown in Figure 10 (C) also can be set, and the data-signal DATA behind the data-signal that multiplexing R uses, G uses, B uses is exported by impedance inverter circuit OP.In addition, also can be in a plurality of pixels the multiplex data signal.And, can also be the impedance inverter circuit shown in Figure 10 (B), (C) not to be set and the formation of only establishing on-off element etc. at output SQ.

4. macroelementization

4.1 driver macroelement

The integrated circuit (IC) apparatus of present embodiment comprises that a plurality of circuit blocks shown in Figure 11 (A) are by at least one driver macroelement (driver macro block) of macroelementization (grandization, macro blockization).This driver macroelement for example is that distribution and circuit unit dispose be immobilized grand firmly.Particularly, for example the configuration of distribution or circuit unit is carried out according to manual layout.In addition, also can robotization carry out distribution, the configuration of a part.

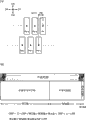

The driver macroelement of Figure 11 (A) comprises: be used for the data driving block DB of driving data lines (source electrode line) and the storage block MB of storing image data.And, also comprise the pad piece PDB of a plurality of pads of the data line that disposes the output line that is used to be electrically connected data driving block DB and display panel.Comprise among this pad piece PDB that in each pad row, pad (pad metal) is arranged along the D1 direction along two interconnected row (broadly, multirow) pad row of D2 direction.

In Figure 11 (A), data driving block DB and storage block MB are along the configuration of D1 direction, and pad piece PDB is configured in the D2 direction side of data driving block DB and storage block MB.Particularly, data driving block DB and storage block MB are along D1 direction adjacency, and data driving block DB and pad piece PDB and storage block MB and pad piece PDB are along D2 direction adjacency.In addition, also can adopt the distortion that other adjunct circuit is set between data driving block DB and storage block MB to implement or make the driver macroelement not comprise that the distortion of storage block MB implements.

Generally speaking, the quantity of the pad that output line connected of data driver is very many.Therefore, if use the automatic wiring instrument that the output line of data driver is connected data driver with on the pad time, will increase the distribution zone of output line, the width of the integrated circuit (IC) apparatus on the D2 direction is increased, thereby be difficult to realize miniature elongated chips.

Just in this point, in Figure 11 (A), data driving block DB and pad piece PDB are as the integrated formation of macroelement.Therefore, the piece of distribution of for example having finished the output line of the data driver on pad efficiently according to manual layout can be registered as the driver macroelement uses.Therefore, and the method that the output line of data driver carries out distribution is compared, can be dwindled the distribution zone of output line by the automatic wiring instrument.Finally, can dwindle the width of the integrated circuit (IC) apparatus on the D2 direction, thereby realize miniature elongated chips.

And, if shown in Figure 11 (A) such macroelementization, so as long as along D1 direction configuration driven device arranged side by side macroelement, just can realize the integrated circuit (IC) apparatus of layout shown in Fig. 5 (A), (B), thereby can carry out the operation of circuit design and layout efficiently.For example, even under the altered situation of specification of the pixel count of display panel, as long as change the number of the driver macroelement of configuration, just can be corresponding therewith and need not again the output line of data driver is carried out distribution, therefore can improve operating efficiency.

And in Figure 11 (A), not only the zone of the D2 direction side of data driving block DB can effectively be applied flexibly and is the pad configuration district, and the zone of the D2 direction side of storage block MB also can effectively be applied flexibly and is the pad configuration district.That is vacating the zone and also can dispose pad, in the D2 of storage block MB direction side.Therefore, be the pad piece PDB of WPB for width, can dispose pad not lavishly, improve positioning efficiency.

And, for example in the comparative example of Fig. 1 (A) because the flow direction of storage block MB and data driving block DB and signal is consistent along D2 direction configuration, so the miniature elongated chips of very difficult realization as short side direction.And, if the specification of the pixel count of display panel, display driver, the structure of storage unit etc. change, and storage block MB or data driving block DB change at width on the D2 direction or the length on the D1 direction, its influence can feed through to other circuit block, causes designing inefficiency.

To this, in Figure 11 (A), data driving block DB and storage block MB in abutting connection with configuration, thereby not only can dwindle the width of the integrated circuit (IC) apparatus on the D2 direction along the D1 direction, and can also make the design high efficiency.

And in the comparative example of Fig. 1 (A), because word line WL disposes along the D1 direction as long side direction, so the signal delay on the word line WL increases, the reading speed of view data is slack-off.Especially, because the word line WL that is connected on the storage unit is formed by polysilicon layer, cause the problem of this signal delay particularly serious.

To this, among Figure 11 (A), in storage block MB, can along as the D2 direction of short side direction to word line WL distribution, and can be along D1 direction pairs of bit line BL distribution as long side direction.And in the present embodiment, the width W of the integrated circuit (IC) apparatus on the D2 direction is shorter.Therefore, not only can dwindle the length of the word line WL in the storage block MB, and can reduce the signal delay on the WL.In addition, in the comparative example of Fig. 1 (A),, cause power consumption to increase owing to when main frame carries out access to a part of access section of storer, also selected longer and parasitic word line WL capacious on the D1 direction.To this, in Figure 11 (A), during the main frame access, can only select word line WL, thereby can realize low-power consumption corresponding to the storage block of memory block.

4.2 the width of driver macroelement

In Figure 11 (A), (B), when the width on the D1 direction of tentation data drive block DB, storage block MB, pad piece PDB was respectively WDB, WMB, WPB, for example the relation of WDB+WMB≤WPB also can be set up.

That is, in Figure 11 (A), the width that the width W PB on the D1 direction of pad piece PDB and width W MB addition with the width W DB of data driving block DB and storage block MB obtain about equally, WDB+WMB=WPB for example.On the other hand, in Figure 11 (B), disposed forwarding piece RP as adjunct circuit.This forwarding piece RP is the circuit block that comprises impact damper, and wherein, impact damper is carried out buffer memory to the write data signal at least (perhaps address signal, storer control signal) that transfers to storage block MB, and then exports to storage block MB.So, under the situation of Figure 11 (B), WDB+WMB<WPB.

If the relation of WDB+WMB=WPB is set up, so with a plurality of driver macroelements when the D1 direction disposes side by side, adjacent pad interblock can not produced useless vacate the zone and in this wise along D1 direction a plurality of pad pieces that are arranged side by side.Therefore, data driver also can have no to be arranged in lavishly on the D1 direction with pad, thereby can dwindle the width on the D1 direction of integrated circuit (IC) apparatus.

And, if the relation of WDB+WMB<WPB is set up, can dispose the forwarding piece RP shown in Figure 11 (B) so, and can also improve positioning efficiency as adjunct circuit.That is, be subjected to the restriction of solder pad space length, it is big that the width W PB of pad piece PDB becomes, and the next door of storage block MB or data driving block DB produces when vacating the zone, adjunct circuit can be configured in this and vacate the zone.In addition, be configured in this adjunct circuit of vacating the zone and be not limited to transmit piece RP.For example, also can dispose the gray scale voltage generative circuit the part, the output line of data driver is set in adjunct circuits such as the circuit of predetermined potential or electrostatic discharge protective circuit.

The configuration example of the pad (pad metal) shown in Figure 12 (A) on the pad piece PDB.In Figure 12 (A), the pad that is arranged in the row of first on the D1 direction is listed as and is arranged in the capable pad row of second on the D1 direction and is stacked on the D2 direction, and interconnected.That is, suppose that the D1 direction is that X-axis, D2 direction are Y-axis, the configuration of staggering of the X coordinate of the X coordinate of the center of the pad of first row and the center of the second capable pad.So in Figure 12 (A), the spacing PP of pad on the D1 direction is X coordinate poor of the center of pad.For example, the difference of the X coordinate of the center of pad Pn and Pn+1 is solder pad space length PP (for example 20~22 μ m).

In Figure 12 (B), suppose that as the width on the D1 direction of the forwarding piece RP of additional circuit blocks be WAB, the pad number on the pad piece PDB is NP.So for example the relation of (NP-1) * PP<WDB+WMB+WAB<(NP+1) * PP is set up.

If this relation is set up, so when being configured in a plurality of driver macroelements on the D1 direction side by side, can not can producing and useless vacate the zone and on the D1 direction, arrange a plurality of pad pieces, and arrange pad (pad) along the D1 direction with the solder pad space length of equalization.If arrange pad with the solder pad space length of equalization, when using projection (hump) etc. to be installed in integrated circuit (IC) apparatus on the glass substrate, stress can be applied to the pad configuration zone equably, can prevent loose contact so.And, vacate the zone in case between pad, produced, owing to this vacates the reason in zone, the flow direction of the binding material of anisotropic conductive materials such as meeting change ACF, may come in contact situations such as bad, if but arrange pad with the solder pad space length of equalization, just can prevent the generation of this situation.And then, the relation of WDB+WMB+WAB≤NP * PP is set up.Like this, can make the solder pad space length equalization on the D1 direction further, to realize the impartial more of stress.

In addition, not disposing under the situation of transmitting the such adjunct circuit of piece RP, can suppose WAB=0.And, on pad piece PDB, also can dispose except that the data driver with the virtual pad the pad (projection, do not connect the pad of welding wire etc.), at this moment, also data driver can be made as the number NP of pad with the number summation of pad and virtual pad.

4.3 forwarding piece

Transmit the configuration example of piece shown in Figure 13.This transmit piece for example can with storage block in abutting connection with configuration.For example, in Fig. 5 (B), the storer that is used to send write data signal from logic circuit block LB, address signal, storer control signal with global lines along D1 direction distribution at circuit block, these signals supply to each storage block MB1~MB4 from logic circuit block LB.In this case, if these signals are not carried out buffer memory, the rising waveform of signal or falling waveform can die down so, and the write time that exists data to write storage block prolongs or take place the danger of write error.

For this point, if in for example D1 of each storage block direction side in abutting connection with configuration forwarding piece shown in Figure 13, these write data signals, address signal, storer control signal are input to each storage block again after transmitting block cache so.Its result can reduce the rising waveform of signal or the falling waveform degree that dies down, and realizes the correct data of storage block are write.

In Figure 13, behind impact damper BFA1 by constituting of the write data signal (WD0, WD1...) of logic circuit block LB, BFA2... buffer memory, export to the forwarding piece of next stage by two phase inverters.Particularly, in Fig. 5 (B), the signal behind buffer memory is transmitted piece output from the forwarding piece of the D1 direction side that is configured in storage block MB4 to the next stage of the D1 direction side that is configured in storage block MB3.And, from the write data signal of logic circuit block LB by impact damper BFB1, BFB2... buffer memory after, export to storage block.Particularly, in Fig. 5 (B), the signal behind buffer memory is exported to storage block MB4 from the forwarding piece of the D1 direction side that is configured in storage block MB4.Like this, in the present embodiment,, not only be provided with impact damper BFA1, the BFA2... of the forwarding piece that is used to output it to next stage, but also be provided with impact damper BFB1, the BFB2... that each storage block is used for write data signal.Like this, can prevent effectively because the parasitic capacity of the storage unit of storage block former thereby cause the waveform of write data signal to die down and the write time prolongs and write error etc. takes place.

And, by behind the impact damper BFC1... buffer memory, export to the forwarding piece of storage block and next stage from the address signal (CPU column address, CPU row address, LCD row address etc.) of logic circuit block LB.And by behind the impact damper BFD1... buffer memory, export to the forwarding piece of storage block and next stage from the storer control signal (read/write switching signal, CPU enable signal, bank selection signal etc.) of logic circuit block LB.

And, in the forwarding piece of Figure 13, also be provided with the impact damper of using from the reading data signal of storage block.Particularly, select signal BANKM (H level) if activate bank, and select this storage block, then from the reading data signal of this storage block behind impact damper BFE1, BFE2... buffer memory, export to read data line RD0L, RD1L....On the other hand, do not select signal BANKM (L level) if activate bank, the output state of impact damper BFE1, BFE2... is a high impedance status so.Thus, can be correctly the reading data signal of other storage block of selecting signal to activate from bank be exported to logic circuit block LB.

5.1 piece is cut apart

Shown in Figure 14 (A), display panel is the QVGA panel of pixel count HPN=240 of pixel count VPN=320, the horizontal scan direction (scan-line direction) of vertical scanning direction (data line direction).In addition, R, G, the B of the figure place PDB of the image of a pixel part (demonstration) data respectively are 6, and the PDB=18 position.In the case, a frame of display panel shows figure place VPN * HPN * PDB=320 * 240 * 18 of needed view data.So the storer of integrated circuit (IC) apparatus needs to store 320 * 240 * 18 view data at least.And data driver is exported each horizontal scan period (time of a sweep trace scanning) HPN=240 single data signal (corresponding to the data-signal of 240 * 18 view data) to display panel.

And in Figure 14 (B), data driver is divided into DBN=4 data drive block DB1~DB4.And storer also is divided into MBN=DBN=4 storage block MB1~MB4.That is for example four driver macroelement DMC1, DMC2, DMC3, the DMC4 that data driving block, storage block, pad piece are carried out macroelementization disposes along the D1 direction.So each driver piece DB1~DB4 exports HPN/DBN=240/4=60 single data signal in each horizontal scan period to display panel.In addition, each storage block MB1~MB4 storage (view data of VPN * HPN * PDB)/MBN=(320 * 240 * 18)/4.

5.2 repeatedly reading of a horizontal scan period

In Figure 14 (B), each data driving block DB1~DB4 is at the data-signal of 60 of horizontal scan period outputs (if R, G, B is 3, then 60 * 3=180 root).So each horizontal scan period must read 240 view data corresponding to data-signal from the storage block MB1~MB4 corresponding to DB1~DB4.

Yet, if the figure place of the view data that each horizontal scan period reads increases, storage unit (sensor amplifier) number of arranging on the D2 direction will take place to need to increase.Consequently, the width W of integrated circuit (IC) apparatus D2 direction increases, and overslaugh makes chip tall and thin.In addition, bring that word line WL is elongated, the problem of the signal delay of WL.

So in the present embodiment, adopt following method: a horizontal scan period, the view data that will be stored in each storage block MB1~MB4 from each storage block MB1~MB4 many times (RN time) reads data driving block DB1~DB4.

For example, in Figure 15, shown in A1, A2, a horizontal scan period, only at RN=2, storage access signal MACS (signal is selected in word select) is for activating (high level).Thus, a horizontal scan period, RN=2 time from each storage block to each data driving block reads image data.Like this, the contained data-latching circuit of first, second data driver DRa, DRb that is arranged at the Figure 16 in the data driving block latchs the view data that reads according to latch signal LATa, the LATb shown in A3, the A4.And, the D/A conversion of the view data that the contained D/A change-over circuit of first, second data driver DRa, DRb then is latched, the contained output circuit of DRa, DRb exports data-signal DATAa, DATAb by D/A conversion gained to the data-signal output line shown in A5, A6.Afterwards, shown in A7, the sweep signal SCSEL of grid of TFT of each pixel that is input to display panel is for activating, and data-signal is input to each pixel, and is kept.

And in Figure 15, in first horizontal scan period, twice reads image data in same first horizontal scan period, exports data-signal DATAa, DATAb to the data-signal output line.But, also can be that at first horizontal period twice reads image data DATAa, DATAb and latch, in ensuing second horizontal period, data-signal DATAa, the DATAb of the view data that correspondence is latched export the data-signal output line to.In addition, the situation of expression reading times RN=2 still, also can be RN 〉=3 among Figure 15.

According to the method for Figure 15, as shown in figure 16, read view data corresponding to 30 data-signal from each storage block, each data driver DRa, DRb then export 30 data-signal.Thus, export 60 data-signal from each data driving block.So, in Figure 15, if the view data that reads corresponding to 30 data-signal from each storer by once reading gets final product.So, compare a horizontal scan period and only read once method, can reduce the storage unit of the D2 direction of Figure 16, the number of sensor amplifier.Consequently, the width of integrated circuit (IC) apparatus D2 direction can be reduced, super tall and thin elongated chips can be realized.Particularly, the length of a horizontal scan period is the level of 52 μ sec under the situation of QVGA.On the other hand, for example be the level of 40nsec the readout time of storer, compares very short with 52 μ sec.So, even in the reading times of a horizontal scan period from once being increased to repeatedly, there is no great influence for display characteristic.

And Figure 14 (A) is the display panel of QVGA (320 * 240), if make the reading times RN=4 of a horizontal scan period, also can be adapted to VGA (640 * 480) display panel, thereby can increase the degree of freedom of design.

And, also can realize that a horizontal scan period repeatedly reads with first method, that is: the many different word lines in each storage block are selected a horizontal scan period by row address decoder (word line selection circuit); Also can realize that a horizontal scan period repeatedly reads, that is: the identical word line in each storage block repeatedly be selected a horizontal scan period by row address decoder with second method; Perhaps, also can realize by the combination of first, second method.

5.3 the configuration of data driver, driver element

The examples of configurations of data driver and the contained driver element of data driver is shown in Figure 16.As shown in figure 16, data driving block is included in a plurality of data driver DRa, the DRb (the first~the m data driver) that the D1 direction is piled up.In addition, each data driver DRa, DRb comprise the individual driver element DRC1~DRC30 of a plurality of 30 (broadly being Q) again.

Storage block word line WL1a be selected and shown in the A1 of Figure 15 when storage block reads for the first time view data, the first data driver DRa latchs the view data of reading according to the latch signal LATa shown in the A3.And, be latched the D/A conversion of view data, and shown in A5, exporting the data-signal output line corresponding to the data-signal DATAa of the view data that reads for the first time like that to.

On the other hand, storage block word line WL1b be selected and shown in the A2 of Figure 15 when storage block reads secondary view data, the second data driver DRb latchs the view data of reading according to the latch signal LATa shown in the A4.And, be latched the D/A conversion of view data, and shown in A6, exporting the data-signal output line corresponding to the data-signal DATAb of the view data that reads for the second time like that to.

As mentioned above, 30 data-signal of corresponding 30 pixels of each data driver DRa, DRb output is exported 60 data-signal corresponding to 60 pixels altogether.

As shown in Figure 16, if along D1 direction configuration (accumulation) a plurality of data driver DRa, DRb, then can prevent to cause making the width W condition of enlarged of integrated circuit (IC) apparatus D2 direction owing to the size of data driver scale.In addition, data driver adopts various formations according to the type of display panel.Under these circumstances, as long as, just can arrange the data driver of various formations expeditiously according to the method for a plurality of data drivers along the configuration of D1 direction.In addition, the situation the when configured number that Figure 16 shows data driver on the D1 direction is two, but configurable number also can be more than or equal to 3.

And each data driver DRa, DRb comprise 30 (Q) driver element DRC1~DRC30 along D2 direction alignment arrangements among Figure 16.Here, driver element DRC1~DRC30 receives the view data of a pixel respectively.And, carry out the D/A conversion of the view data of a pixel, the data-signal of the corresponding pixel image data of output.Each unit of this driver element DRC1~DRC30 can comprise the latch cicuit of data, DAC (DAC of 1 pixel), Figure 10 (B) of Figure 10 (A) and the output SQ of Figure 10 (C).

And, in Figure 16, the pixel count of display panel horizontal scan direction (is being shared by a plurality of integrated circuit (IC) apparatus and is being driven under the situation of data line of display panel, the pixel count of the horizontal scan direction that each integrated circuit (IC) apparatus is born) is HPN, the piece number (piece is cut apart number) of data driving block is DBN, is IN a horizontal scan period to the input number of times of driver element input image data.And IN equals the view data reading times RN of an illustrated horizontal scan period of Figure 15.In this case, the number of the driver element DRC1~DRC30 that arranges along the D2 direction can be expressed as Q=HPN/ (DBN * IN).Under the situation of Figure 16, because HPN=240, DBN=4, IN=2, so Q=240/ (4 * 2)=30.

And, at the width (spacing) of the D2 of driver element DRC1~DRC30 direction is that the width of the D2 direction of the contained peripheral circuit part of WD, data driving block (buffer circuit, distribution zone etc.) is under the situation of WPCB, and the width W B (breadth extreme) of the D2 direction of the first~the N circuit block CB1~CBN can be expressed as Q * WD≤WB<(Q+1) * WD+WPCB.In addition, be under the situation of WPC at the width of the D2 direction of the contained peripheral circuit of storage block part (row address decoder RD, distribution zone), can be expressed as Q * WD≤WB<(Q+1) * WD+WPC.

And, the pixel count of display panel horizontal scan direction be the figure place of the view data of HPN, 1 pixel be the piece number of PDB, storage block be MBN (=DBN), be RN from the reading times of storage block reads image data a horizontal scan period.At this moment, the number P of the sensor amplifier of arranging along the D2 direction in sensor amplifier piece SAB (exporting the sensor amplifier of bit image data) can be expressed as P=(HPN * PDP)/(MBN * RN).Under the situation of Figure 16, because HPN=240, PDP=18, MBN=4, RN=2, so, P=(240 * 18)/(4 * 2)=54.And number P is the effective sensor amplifier number corresponding with the effective storage unit number, does not comprise the number of pseudo-storage unit with non-effective sensor amplifiers such as sensor amplifiers.

And when the width (spacing) of the D2 direction of each sensor amplifier that sensor amplifier piece SAB is contained was WS, the width W SAB of the D2 direction of sensor amplifier piece SAB (storage block) can be expressed as WSAB=P * WS.And when the width of the D2 direction of the contained peripheral circuit of storage block part was WPC, the width W B (breadth extreme) of the D2 direction of circuit block CB1~CBN can be expressed as P * WS≤WB<(P+PDB) * WS+WPC.

5.4 the layout of data driving block

The layout that data driving block is more detailed is shown in Figure 17 for example.In Figure 17, data driving block comprises a plurality of sub-pixel driver element SDC1~SDC180 of the data-signal of the view data that it exports a corresponding sub-pixel separately.And, with regard to this data driving block, in the time of along a plurality of sub-pixel driver element of D1 direction (along the direction on the long limit of sub-pixel driver element) configuration, also dispose a plurality of sub-pixel driver elements along D2 direction perpendicular to D1.That is sub-pixel driver element SDC1~SDC180 is the matrix form configuration.And, be used for realizing that pad that the data driving block output line is electrically connected with the data line of display panel then is configured in the D2 direction side of data driving block.

For example, the driver element DRC1 of the data driver DRa of Figure 16 is made of sub-pixel driver element SDC1, SDC2, the SDC3 of Figure 17.Here, SDC1, SDC2, SDC3 are respectively that R (red) uses, G (green) uses, the sub-pixel driver element of B (orchid) usefulness, import R, G, the B view data (R1, G1, B1) of the corresponding first single data signal from storage block.And sub-pixel driver element SDC1, SDC2, SDC3 carry out the D/A conversion to these view data (R1, G1, B1), first R, G, B data-signal (data voltage) are exported to R, G, the B pad of corresponding first data lines.

Equally, driver element DRC2 is made of sub-pixel driver element SDC4, SDC5, the SDC6 that R uses, G uses, B uses.Import R, G, the B view data (R2, G2, B2) of the corresponding second single data signal from storage block.And sub-pixel driver element SDC4, SDC5, SDC6 carry out the D/A conversion to these view data (R2, G2, B2), second R, G, B data-signal (data voltage) are exported to R, G, the B pad of corresponding second data lines.Other sub-pixel driver element also is the same.

And the number of sub-pixel is not limited to three, also can be more than or equal to four.In addition, the configuration of sub-pixel driver element also is not limited to Figure 17, also can be for example R to be piled up configuration with the sub-pixel driver element along the D2 direction with, B with, G.

5.5 the layout of storage block

The layout of storage block is shown in Figure 18 for example.Figure 18 represents in the storage block part corresponding to a pixel (R, G, B respectively are 6, add up to 18) in detail.

Part corresponding to a pixel in the sensor amplifier piece comprises R sensor amplifier SAR0~SAR5, G sensor amplifier SAG0~SAG5, B sensor amplifier SAB0~SAB5.In addition, in Figure 18, pile up two (broad sense is a plurality of) sensor amplifiers of configuration (and impact damper) along the D1 direction.And, in the 2 line storage units row that the D1 direction side of the sensor amplifier SAR0~SAR1 that piles up configuration is arranged along the D1 direction on the bit line of column of memory cells of skidding for example be connected in SAR0, the bit line of the column of memory cells of following skidding for example is connected in SAR1.And SAR0, SAR1 amplify the signal of the view data that reads from storage unit, thus, export 2 bit image data from SAR0, SAR1.The relation of other sensor amplifier and storage unit also is the same.

Under the situation of the formation of Figure 18, repeatedly reading of a horizontal scan period view data as shown in figure 15 can realize as following.That is, select word line WL1a earlier in first horizontal scan period (first scan line selection), carry out the first time of view data and read, shown in the A5 of Figure 15, output is data-signal DATAa for the first time.In the case, R, G, the B view data from sensor amplifier SAR0~SAR5, SAG0~SAG5, SAB0~SAB5 inputed to sub-pixel driver element SDC1, SDC2, SDC3 respectively.Then, select word line WL1b in same first horizontal scan period, carry out the second time of view data and read, shown in the A6 of Figure 15, output is data-signal DATAb for the second time.In the case, from R, the G of sensor amplifier SAR0~SAR5, SAG0~SAG5, SAB0~SAB5, sub-pixel driver element SDC91, SDC92, the SDC93 that the B view data is inputed to Figure 17 respectively.In addition,, select word line WL2a earlier, carry out the first time of view data and read, and export primary data-signal DATAa in ensuing second horizontal scan period (second scan line selection).Then,, select word line WL2b, carry out the second time of view data and read, and export secondary data-signal DATAb in same second horizontal scan period.

And, also can implement not pile up the distortion of configuration sensor amplifier in the D1 direction.And, also can switch the column of memory cells that is connected in each sensor amplifier with array selecting signal.In this case, by in storage block, repeatedly select same word line, can realize repeatedly reading of a horizontal scan period a horizontal scan period.

5.6 the layout of sub-pixel driver element