KR20250071663A - 적층형 전자 부품 - Google Patents

적층형 전자 부품 Download PDFInfo

- Publication number

- KR20250071663A KR20250071663A KR1020230158445A KR20230158445A KR20250071663A KR 20250071663 A KR20250071663 A KR 20250071663A KR 1020230158445 A KR1020230158445 A KR 1020230158445A KR 20230158445 A KR20230158445 A KR 20230158445A KR 20250071663 A KR20250071663 A KR 20250071663A

- Authority

- KR

- South Korea

- Prior art keywords

- gallium

- side margin

- dielectric layer

- electronic components

- cover portion

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/224—Housing; Encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/30—Stacked capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G2/00—Details of capacitors not covered by a single one of groups H01G4/00-H01G11/00

- H01G2/12—Protection against corrosion

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/005—Electrodes

- H01G4/008—Selection of materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/005—Electrodes

- H01G4/012—Form of non-self-supporting electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/018—Dielectrics

- H01G4/06—Solid dielectrics

- H01G4/08—Inorganic dielectrics

- H01G4/12—Ceramic dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/018—Dielectrics

- H01G4/06—Solid dielectrics

- H01G4/08—Inorganic dielectrics

- H01G4/12—Ceramic dielectrics

- H01G4/1209—Ceramic dielectrics characterised by the ceramic dielectric material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/018—Dielectrics

- H01G4/06—Solid dielectrics

- H01G4/08—Inorganic dielectrics

- H01G4/12—Ceramic dielectrics

- H01G4/1209—Ceramic dielectrics characterised by the ceramic dielectric material

- H01G4/1218—Ceramic dielectrics characterised by the ceramic dielectric material based on titanium oxides or titanates

- H01G4/1227—Ceramic dielectrics characterised by the ceramic dielectric material based on titanium oxides or titanates based on alkaline earth titanates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/018—Dielectrics

- H01G4/06—Solid dielectrics

- H01G4/08—Inorganic dielectrics

- H01G4/12—Ceramic dielectrics

- H01G4/1272—Semiconductive ceramic capacitors

- H01G4/1281—Semiconductive ceramic capacitors with grain boundary layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/228—Terminals

- H01G4/232—Terminals electrically connecting two or more layers of a stacked or rolled capacitor

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E60/00—Enabling technologies; Technologies with a potential or indirect contribution to GHG emissions mitigation

- Y02E60/13—Energy storage using capacitors

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Ceramic Engineering (AREA)

- Inorganic Chemistry (AREA)

- Materials Engineering (AREA)

- Fixed Capacitors And Capacitor Manufacturing Machines (AREA)

- Ceramic Capacitors (AREA)

- Coils Or Transformers For Communication (AREA)

Abstract

본 발명의 일 실시형태에 따른 적층형 전자 부품은, 유전체층 및 내부 전극을 포함하는 바디; 상기 바디 상에 배치되는 외부 전극; 및 상기 바디 상에 배치되는 사이드 마진부; 를 포함하고, 상기 커버부 및 사이드 마진부는 티타늄(Ti) 및 갈륨(Ga)을 포함하며, 상기 커버부에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(A)에 대한, 상기 사이드 마진부에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(B)의 비율(B/A)은 1.5 ≤ B/A 를 만족할 수 있다.

Description

본 발명은 적층형 전자 부품에 관한 것이다.

적층형 전자 부품의 하나인 적층 세라믹 커패시터(MLCC: Multi-Layered Ceramic Capacitor)는 액정 표시 장치(LCD: Liquid Crystal Display) 및 플라즈마 표시 장치 패널(PDP: Plasma Display Panel) 등의 영상 기기, 컴퓨터, 스마트폰 및 휴대폰 등 여러 전자 제품의 인쇄회로기판에 장착되어 전기를 충전시키거나 또는 방전시키는 역할을 하는 칩 형태의 콘덴서이다.

이러한 적층 세라믹 커패시터는 소형이면서 고용량이 보장되고 실장이 용이하다는 장점으로 인하여 다양한 전자 장치의 부품으로 사용될 수 있다. 컴퓨터, 모바일 기기 등 각종 전자 기기가 소형화, 고출력화되면서 적층 세라믹 커패시터에 대한 소형화 및 고용량화의 요구가 증대되고 있다.

소형화 및 고용량화가 진행됨에 따라 용량을 형성하는 영역을 보호할 필요성이 높아지고 있는데, 이는 용량을 형성하는 영역을 둘러싸는 마진영역을 추가하여 이를 개선하고 있다. 다만, 소형화 및 고용량화를 달성하기 위해 구조적인 설계를 지속적으로 변경함에 따라, 용량을 형성하는 영역은 커지고 용량을 형성하는 영역을 보호하는 마진영역이 줄어들면서, 적층 세라믹 커패시터의 내습 신뢰성 및 강도가 취약해지는 문제점이 발생할 우려가 있다.

본 발명이 해결하고자 하는 여러 과제 중 하나는 내습 신뢰성이 향상된 적층형 전자 부품을 제공하기 위함이다.

본 발명이 해결하고자 하는 여러 과제 중 하나는 기계적 특성이 향상된 적층형 전자 부품을 제공하기 위함이다.

다만, 본 발명이 해결하고자 하는 여러 과제는 상술한 내용에 한정되지 않으며, 본 발명의 구체적인 실시형태를 설명하는 과정에서 보다 쉽게 이해될 수 있을 것이다.

본 발명의 일 실시형태에 따른 적층형 전자 부품은, 유전체층 및 상기 유전체층과 제1 방향으로 번갈아 배치되는 내부 전극을 포함하는 용량 형성부, 및 상기 용량 형성부의 상기 제1 방향 양 단면(end-surface)에 배치되는 커버부를 포함하고, 상기 제1 방향으로 서로 마주보는 제1 및 제2 면, 상기 제1 및 제2 면과 연결되고 제2 방향으로 서로 마주보는 제3 및 제4 면, 상기 제1 내지 제4 면과 연결되고 제3 방향으로 서로 마주보는 제5 및 제6 면을 포함하는 바디; 상기 제3 및 제4 면에 배치되는 외부 전극; 및 상기 제5 및 제6 면에 배치되는 사이드 마진부; 를 포함하고, 상기 커버부 및 사이드 마진부는 티타늄(Ti) 및 갈륨(Ga)을 포함하며, 상기 커버부에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(A)에 대한, 상기 사이드 마진부에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(B)의 비율(B/A)은 1.5 ≤ B/A 를 만족할 수 있다.

본 발명의 여러 효과 중 하나는 적층형 전자 부품의 내습 신뢰성이 향상된 것이다.

본 발명의 여러 효과 중 하나는 적층형 전자 부품의 기계적 특성이 향상된 것이다.

다만, 본 발명의 다양하면서도 유익한 장점과 효과는 상술한 내용에 한정되지 않으며, 본 발명의 구체적인 실시형태를 설명하는 과정에서 보다 쉽게 이해될 수 있을 것이다.

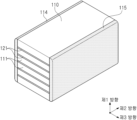

도 1은 본 발명의 일 실시형태에 따른 적층형 전자 부품의 사시도를 개략적으로 도시한 것이다.

도 2는 도 1의 적층형 전자 부품에서 외부 전극을 제외한 사시도를 개략적으로 도시한 것이다.

도 3은 도 1의 적층형 전자 부품에서 외부 전극 및 사이드 마진부를 제외한 사시도를 개략적으로 도시한 것이다.

도 4는 내부 전극의 적층 구조를 나타낸 분리사시도를 개략적으로 도시한 것이다.

도 5는 도 1의 I-I'에 따른 단면도를 개략적으로 도시한 것이다.

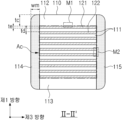

도 6은 도 1의 II-II'에 따른 단면도를 개략적으로 도시한 것이다.

도 7a 및 도 7b는 비교예에 있어서 도 6의 M1 및 M2 영역을 주사전자현미경(SEM)으로 촬영한 이미지이고, 도 7c 및 도 7d는 실시예에 있어서 도 6의 M1 및 M2 영역을 주사전자현미경(SEM)으로 촬영한 이미지이다.

도 8a는 비교예의 커버부 단면을 주사전자현미경(SEM)의 HAADF 모드로 촬영한 이미지이며, 도 8b는 도 8a의 영역에서 EDS 분석을 진행하여 알루미늄(Al) 원소를 맵핑(mapping)한 이미지이고, 도 8c는 도 8a의 영역에서 EDS 분석을 진행하여 규소(Si) 원소를 맵핑(mapping)한 이미지이다.

도 9a는 실시예의 커버부 단면을 주사전자현미경(SEM)의 HAADF 모드로 촬영한 이미지이며, 도 9b는 도 9a의 영역에서 EDS 분석을 진행하여 알루미늄(Al) 원소를 맵핑(mapping)한 이미지이고, 도 9c는 도 9a의 영역에서 EDS 분석을 진행하여 규소(Si) 원소를 맵핑(mapping)한 이미지이며, 도 9d는 도 9a의 영역에서 EDS 분석을 진행하여 갈륨(Ga) 원소를 맵핑(mapping)한 이미지이다.

도 10a는 비교예의 사이드 마진부 단면을 주사전자현미경(SEM)의 HAADF 모드로 촬영한 이미지이며, 도 10b는 도 10a의 영역에서 EDS 분석을 진행하여 알루미늄(Al) 원소를 맵핑(mapping)한 이미지이고, 도 10c는 도 10a의 영역에서 EDS 분석을 진행하여 규소(Si) 원소를 맵핑(mapping)한 이미지이다.

도 11a는 실시예의 사이드 마진부 단면을 주사전자현미경(SEM)의 HAADF 모드로 촬영한 이미지이며, 도 11b는 도 11a의 영역에서 EDS 분석을 진행하여 알루미늄(Al) 원소를 맵핑(mapping)한 이미지이고, 도 11c는 도 11a의 영역에서 EDS 분석을 진행하여 규소(Si) 원소를 맵핑(mapping)한 이미지이며, 도 11d는 도 11a의 영역에서 EDS 분석을 진행하여 갈륨(Ga) 원소를 맵핑(mapping)한 이미지이다.

도 12a 및 도 12b는 비교예의 내습 신뢰성 평가 그래프이고, 도 12c 및 도 12d는 실시예의 내습 신뢰성 평가 그래프이다.

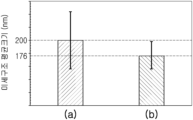

도 13a는 비교예의 결정립 미세구조 크기에 관한 그래프이고, 도 13b는 실시예의 결정립 미세구조 크기에 관한 그래프이다.

도 2는 도 1의 적층형 전자 부품에서 외부 전극을 제외한 사시도를 개략적으로 도시한 것이다.

도 3은 도 1의 적층형 전자 부품에서 외부 전극 및 사이드 마진부를 제외한 사시도를 개략적으로 도시한 것이다.

도 4는 내부 전극의 적층 구조를 나타낸 분리사시도를 개략적으로 도시한 것이다.

도 5는 도 1의 I-I'에 따른 단면도를 개략적으로 도시한 것이다.

도 6은 도 1의 II-II'에 따른 단면도를 개략적으로 도시한 것이다.

도 7a 및 도 7b는 비교예에 있어서 도 6의 M1 및 M2 영역을 주사전자현미경(SEM)으로 촬영한 이미지이고, 도 7c 및 도 7d는 실시예에 있어서 도 6의 M1 및 M2 영역을 주사전자현미경(SEM)으로 촬영한 이미지이다.

도 8a는 비교예의 커버부 단면을 주사전자현미경(SEM)의 HAADF 모드로 촬영한 이미지이며, 도 8b는 도 8a의 영역에서 EDS 분석을 진행하여 알루미늄(Al) 원소를 맵핑(mapping)한 이미지이고, 도 8c는 도 8a의 영역에서 EDS 분석을 진행하여 규소(Si) 원소를 맵핑(mapping)한 이미지이다.

도 9a는 실시예의 커버부 단면을 주사전자현미경(SEM)의 HAADF 모드로 촬영한 이미지이며, 도 9b는 도 9a의 영역에서 EDS 분석을 진행하여 알루미늄(Al) 원소를 맵핑(mapping)한 이미지이고, 도 9c는 도 9a의 영역에서 EDS 분석을 진행하여 규소(Si) 원소를 맵핑(mapping)한 이미지이며, 도 9d는 도 9a의 영역에서 EDS 분석을 진행하여 갈륨(Ga) 원소를 맵핑(mapping)한 이미지이다.

도 10a는 비교예의 사이드 마진부 단면을 주사전자현미경(SEM)의 HAADF 모드로 촬영한 이미지이며, 도 10b는 도 10a의 영역에서 EDS 분석을 진행하여 알루미늄(Al) 원소를 맵핑(mapping)한 이미지이고, 도 10c는 도 10a의 영역에서 EDS 분석을 진행하여 규소(Si) 원소를 맵핑(mapping)한 이미지이다.

도 11a는 실시예의 사이드 마진부 단면을 주사전자현미경(SEM)의 HAADF 모드로 촬영한 이미지이며, 도 11b는 도 11a의 영역에서 EDS 분석을 진행하여 알루미늄(Al) 원소를 맵핑(mapping)한 이미지이고, 도 11c는 도 11a의 영역에서 EDS 분석을 진행하여 규소(Si) 원소를 맵핑(mapping)한 이미지이며, 도 11d는 도 11a의 영역에서 EDS 분석을 진행하여 갈륨(Ga) 원소를 맵핑(mapping)한 이미지이다.

도 12a 및 도 12b는 비교예의 내습 신뢰성 평가 그래프이고, 도 12c 및 도 12d는 실시예의 내습 신뢰성 평가 그래프이다.

도 13a는 비교예의 결정립 미세구조 크기에 관한 그래프이고, 도 13b는 실시예의 결정립 미세구조 크기에 관한 그래프이다.

이하, 구체적인 실시형태 및 첨부된 도면을 참조하여 본 발명의 실시형태를 설명한다. 그러나, 본 발명의 실시형태는 여러 가지 다른 형태로 변형될 수 있으며, 본 발명의 범위가 이하 설명하는 실시형태로 한정되는 것은 아니다. 또한, 본 발명의 실시형태는 통상의 기술자에게 본 발명을 더욱 완전하게 설명하기 위해서 제공되는 것이다. 따라서, 도면에서의 요소들의 형상 및 크기 등은 보다 명확한 설명을 위해 과장될 수 있으며, 도면상의 동일한 부호로 표시되는 요소는 동일한 요소이다.

그리고 도면에서 본 발명을 명확하게 설명하기 위해서 설명과 관계없는 부분은 생략하고, 도면에서 나타난 각 구성의 크기 및 두께는 설명의 편의를 위해 임의로 나타내었으므로, 본 발명이 반드시 도시된 바에 한정되지 않는다. 또한, 동일한 사상의 범위 내의 기능이 동일한 구성요소는 동일한 참조부호를 사용하여 설명한다. 나아가, 명세서 전체에서, 어떤 부분이 어떤 구성요소를 "포함"한다고 할 때, 이는 특별히 반대되는 기재가 없는 한 다른 구성요소를 제외하는 것이 아니라 다른 구성요소를 더 포함할 수 있는 것을 의미한다.

도면에서, 제1 방향은 적층 방향 또는 두께(T) 방향, 제2 방향은 길이(L) 방향, 제3 방향은 폭(W) 방향으로 정의될 수 있다.

적층형

전자 부품

도 1은 본 발명의 일 실시형태에 따른 적층형 전자 부품의 사시도를 개략적으로 도시한 것이다.

도 2는 도 1의 적층형 전자 부품에서 외부 전극을 제외한 사시도를 개략적으로 도시한 것이다.

도 3은 도 1의 적층형 전자 부품에서 외부 전극 및 사이드 마진부를 제외한 사시도를 개략적으로 도시한 것이다.

도 4는 내부 전극의 적층 구조를 나타낸 분리사시도를 개략적으로 도시한 것이다.

도 5는 도 1의 I-I'에 따른 단면도를 개략적으로 도시한 것이다.

도 6은 도 1의 II-II'에 따른 단면도를 개략적으로 도시한 것이다.

이하, 도 1 내지 도 6을 참조하여, 본 발명의 일 실시형태에 따른 적층형 전자 부품에 대하여 상세히 설명한다. 다만, 적층형 전자 부품의 일례로서 적층 세라믹 커패시터에 대하여 설명하나, 본 발명은 유전체 조성물을 이용하는 다양한 전자 제품, 예를 들어, 인덕터, 압전체 소자, 바리스터, 또는 서미스터 등에도 적용될 수 있을 것이다.

본 발명의 일 실시형태에 따른 적층형 전자 부품(100)은, 유전체층(111) 및 상기 유전체층(111)과 제1 방향으로 번갈아 배치되는 내부 전극(121, 122)을 포함하는 용량 형성부(Ac), 및 상기 용량 형성부(Ac)의 상기 제1 방향 양 단면(end-surface)에 배치되는 커버부(112, 113)를 포함하고, 상기 제1 방향으로 서로 마주보는 제1 및 제2 면(1, 2), 상기 제1 및 제2 면(1, 2)과 연결되고 제2 방향으로 서로 마주보는 제3 및 제4 면(3, 4), 상기 제1 내지 제4 면(1, 2, 3, 4)과 연결되고 제3 방향으로 서로 마주보는 제5 및 제6 면(5, 6)을 포함하는 바디(110); 상기 제3 및 제4 면(3, 4)에 배치되는 외부 전극; 및 상기 제5 및 제6 면(5, 6)에 배치되는 사이드 마진부(114, 115); 를 포함하고, 상기 커버부(112, 113) 및 사이드 마진부(114, 115)는 티타늄(Ti) 및 갈륨(Ga)을 포함하며, 상기 커버부(112, 113)에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(A)에 대한, 사이드 마진부(114, 115)에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(B)의 비율(B/A)은 1.5 ≤ B/A 를 만족할 수 있다.

바디(110)는 유전체층(111) 및 내부 전극(121, 122)이 교대로 적층 되어있을 수 있다.

보다 구체적으로, 바디(110)는 바디(110)의 내부에 배치되며, 유전체층(111)을 사이에 두고 서로 마주보도록 번갈아 배치되는 제1 내부 전극(121) 및 제2 내부 전극(122)을 포함하여 용량을 형성하는 용량 형성부(Ac)를 포함할 수 있다.

바디(110)의 구체적인 형상에 특별히 제한은 없지만, 도시된 바와 같이 바디(110)는 육면체 형상이나 이와 유사한 형상으로 이루어질 수 있다. 소성 과정에서 바디(110)에 포함된 세라믹 입자의 수축으로 인하여, 바디(110)는 완전한 직선을 가진 육면체 형상은 아니지만 실질적으로 육면체 형상을 가질 수 있다.

바디(110)는 제1 방향으로 서로 마주보는 제1 및 제2 면(1, 2), 제1 및 제2 면(1, 2)과 연결되고 제2 방향으로 서로 마주보는 제3 및 제4 면(3, 4), 제1 내지 제4 면(1, 2, 3, 4)과 연결되며 제3 방향으로 서로 마주보는 제5 및 제6 면(5, 6)을 가질 수 있다.

바디(110)를 형성하는 복수의 유전체층(111)은 소성된 상태로서, 인접하는 유전체층(111) 사이의 경계는 주사전자현미경(Scanning Electron Microscope, SEM)을 이용하지 않고서는 확인하기 곤란할 정도로 일체화될 수 있다.

유전체층(111)을 형성하는 원료는 충분한 정전 용량을 얻을 수 있는 한 제한되지 않는다. 일반적으로 페로브스카이트(ABO3)계 재료를 사용할 수 있으며, 예를 들어, 티탄산바륨계 재료, 납 복합 페로브스카이트계 재료 또는 티탄산스트론튬계 재료 등을 사용할 수 있다. 티탄산바륨계 재료는 BaTiO3계 세라믹 입자를 포함할 수 있으며, 세라믹 입자의 예시로 BaTiO3, BaTiO3에 Ca(칼슘), Zr(지르코늄) 등이 일부 고용된 (Ba1 - xCax)TiO3 (0<x<1), Ba(Ti1-yCay)O3 (0<y<1), (Ba1 - xCax)(Ti1 - yZry)O3 (0<x<1, 0<y<1) 또는 Ba(Ti1-yZry)O3 (0<y<1) 등을 들 수 있다.

또한, 유전체층(111)을 형성하는 원료는 티탄산바륨(BaTiO3) 등의 입자에 본 발명의 목적에 따라 다양한 세라믹 첨가제, 유기용제, 결합제, 분산제 등이 첨가될 수 있다.

또한, 유전체층(111)은 티탄산바륨(BaTiO3)과 같은 유전체 물질을 이용하여 형성될 수 있으므로, 소성 후 유전체 미세구조를 포함할 수 있다. 유전체 미세구조는, 복수의 결정립, 상기 인접한 결정립 사이에 배치되는 결정립계, 및 상기 결정립계가 3 개 이상 접하는 지점에 배치되는 삼중점을 포함할 수 있으며, 각각 복수 개를 포함할 수 있다.

본 발명에서는, 후술하는 커버부(112, 113) 및 사이드 마진부(114, 115)에 포함되는 유전체층과 구분하기 위해, 용량 형성부(Ac)에 포함된 유전체층(111)은 제1 유전체층(111)이라고 정의할 수 있고, 커버부(112, 113)에 포함된 유전체층은 제2 유전체층이라고 정의할 수 있으며, 사이드 마진부(114, 115)에 포함되는 유전체층은 제3 유전체층이라고 정의할 수 있다.

본 발명의 일 실시형태에 있어서, 용량 형성부(Ac)의 유전체층(111)은 갈륨(Ga)을 포함하지 않을 수 있다.

여기서, 용량 형성부(Ac)의 유전체층(111)이 갈륨(Ga)을 포함하지 않는다는 것은, 유전체층(111)을 소성하기 전, 유전체 슬러리(slurry) 또는 유전체 그린 시트 상태가 갈륨(Ga)을 포함하지 않는다는 것을 의미할 수 있으며, 용량 형성부(Ac)의 중앙부 영역에 위치한 유전체층(111)은 갈륨(Ga)을 포함하지 않는다는 것을 의미할 수 있다.

즉, 후술하는 커버부(112, 113) 또는 사이드 마진부(114, 115)에 포함된 갈륨(Ga)이 고온 열처리 등의 소성 과정이 진행됨에 따라, 용량 형성부(Ac) 중 커버부(112, 113) 또는 사이드 마진부(114, 115)와 인접한 용량 형성부(Ac)의 유전체층(111)의 영역으로 갈륨(Ga)이 확산될 수도 있으나, 용량 형성부(Ac)의 중앙부 영역에 위치한 유전체층(111)은 갈륨(Ga)을 포함하지 않는 것을 의미할 수 있다.

예를 들어, 바디(110)의 제3 방향 중심에서 제1 및 제2 방향 단면(cross-section)을 기준으로, 제1 및 제2 방향 중심부에 위치한 10 μm × 10 μm 영역을 주사전자현미경(SEM)의 에너지 분산 X선 분광법(Energy Dispersive X-ray Spectrometer, EDS) 모드로 관찰하였을 때, 갈륨(Ga)이 검출되지 않거나, 갈륨(Ga)이 0.1 at% 미만으로 검출되는 것을 의미할 수 있다.

유전체층(111)의 두께(td)는 특별히 한정할 필요는 없다.

다만, 적층형 전자 부품의 고용량화를 달성하기 위해서 유전체층(111)의 두께는 3.0 μm 이하일 수 있으며, 적층형 전자 부품의 소형화 및 고용량화를 보다 용이하게 달성하기 위하여 유전체층(111)의 두께는 1.0 μm 이하일 수 있으며, 바람직하게는 0.6 μm 이하일 수 있고, 보다 바람직하게는 0.4 μm 이하일 수 있다.

여기서, 유전체층(111)의 두께(td)는 제1 및 제2 내부 전극(121, 122) 사이에 배치되는 유전체층(111)의 두께(td)를 의미할 수 있다.

한편, 유전체층(111)의 두께(td)는 유전체층(111)의 제1 방향 크기를 의미할 수 있다. 또한, 유전체층(111)의 두께(td)는 유전체층(111) 평균 두께(td)를 의미할 수 있으며, 유전체층(111)의 제1 방향 평균 크기를 의미할 수 있다.

유전체층(111)의 제1 방향 평균 크기는 바디(110)의 제1 및 제2 방향 단면(cross-section)을 1만 배율의 주사전자현미경(SEM)으로 이미지를 스캔하여 측정할 수 있다. 보다 구체적으로, 하나의 유전체층(111)의 제1 방향 평균 크기는 스캔된 이미지에서 하나의 유전체층(111)을 제2 방향으로 등간격인 30개의 지점에서 제1 방향 크기를 측정하여 계산한 평균값을 의미할 수 있다. 상기 등간격인 30개의 지점은 용량 형성부(Ac)에서 지정될 수 있다. 또한, 이러한 평균값 측정을 10개의 유전체층(111)으로 확장하여 평균값을 측정하면, 유전체층(111)의 제1 방향 평균 크기를 더욱 일반화할 수 있다.

내부 전극(121, 122)은 유전체층(111)과 교대로 적층될 수 있다.

내부 전극(121, 122)은 제1 내부 전극(121) 및 제2 내부 전극(122)을 포함할 수 있으며, 제1 및 제2 내부 전극(121, 122)은 바디(110)를 구성하는 유전체층(111)을 사이에 두고 서로 마주하도록 번갈아 배치되며, 바디(110)의 제3 및 제4 면(3, 4)으로 각각 노출될 수 있다.

보다 구체적으로, 제1 내부 전극(121)은 제4 면(4)과 이격되며 제3 면(3)을 통해 노출될 수 있고, 제2 내부 전극(122)은 제3 면(3)과 이격되며 제4 면(4)을 통해 노출될 수 있다. 바디(110)의 제3 면(3)에는 제1 외부 전극(131)이 배치되어 제1 내부 전극(121)과 연결되고, 바디(110)의 제4 면(4)에는 제2 외부 전극(132)이 배치되어 제2 내부 전극(122)과 연결될 수 있다.

즉, 제1 내부 전극(121)은 제2 외부 전극(132)과는 연결되지 않고 제1 외부 전극(131)과 연결되며, 제2 내부 전극(122)은 제1 외부 전극(131)과는 연결되지 않고 제2 외부 전극(132)과 연결될 수 있다. 이때, 제1 및 제2 내부 전극(121, 122)은 중간에 배치된 유전체층(111)에 의해 서로 전기적으로 분리될 수 있다.

한편, 바디(110)는 제1 내부 전극(121)이 인쇄된 세라믹 그린 시트와 제2 내부 전극(122)이 인쇄된 세라믹 그린 시트를 번갈아 적층한 후, 소성하여 형성될 수 있다.

내부 전극(121, 122)을 형성하는 재료는 특별히 제한되지 않으며, 전기 전도성이 우수한 재료를 사용할 수 있다. 예를 들어, 내부 전극(121, 122)은 니켈(Ni), 구리(Cu), 팔라듐(Pd), 은(Ag), 금(Au), 백금(Pt), 주석(Sn), 텅스텐(W), 티타늄(Ti) 및 이들의 합금 중 하나 이상을 포함할 수 있다.

또한, 내부 전극(121, 122)은 니켈(Ni), 구리(Cu), 팔라듐(Pd), 은(Ag), 금(Au), 백금(Pt), 주석(Sn), 텅스텐(W), 티타늄(Ti) 및 이들의 합금 중 하나 이상을 포함하는 내부 전극용 도전성 페이스트를 세라믹 그린 시트에 인쇄하여 형성할 수 있다. 상기 내부 전극용 도전성 페이스트의 인쇄 방법은 스크린 인쇄법 또는 그라비아 인쇄법 등을 사용할 수 있으나, 본 발명이 이에 한정되는 것은 아니다.

한편, 내부 전극(121, 122)의 두께(te)는 특별히 한정할 필요는 없다.

다만, 적층형 전자 부품의 고용량화를 달성하기 위해서 내부 전극(121, 122)의 두께는 1.0 μm 이하일 수 있으며, 적층형 전자 부품의 소형화 및 고용량화를 보다 용이하게 달성하기 위하여 내부 전극(121, 122)의 두께는 0.6 μm 이하일 수 있고, 보다 바람직하게는 0.4 μm 이하일 수 있다.

여기서, 내부 전극(121, 122)의 두께(te)는 내부 전극(121, 122)의 제1 방향 크기를 의미할 수 있다. 또한, 내부 전극(121, 122)의 두께(te)는 내부 전극(121, 122)의 평균 두께(te)를 의미할 수 있으며, 내부 전극(121, 122)의 제1 방향 평균 크기를 의미할 수 있다.

내부 전극(121, 122)의 제1 방향 평균 크기는 바디(110)의 제1 및 제2 방향 단면(cross-section)을 1만 배율의 주사전자현미경(SEM)으로 이미지를 스캔하여 측정할 수 있다. 보다 구체적으로, 하나의 내부 전극의 제1 방향 평균 크기는 스캔된 이미지에서 하나의 내부 전극을 제2 방향으로 등간격인 30개의 지점에서 제1 방향 크기를 측정하여 계산한 평균값일 수 있다. 상기 등간격인 30개의 지점은 용량 형성부(Ac)에서 지정될 수 있다. 또한, 이러한 평균값 측정을 10개의 내부 전극(121, 122)으로 확장하여 평균값을 측정하면, 내부 전극(121, 122)의 제1 방향 평균 크기를 더욱 일반화할 수 있다.

한편, 본 발명의 일 실시예에 있어서, 복수의 유전체층(111) 중 적어도 하나의 평균 두께(td)와 복수의 내부 전극(121, 122) 중 적어도 하나의 평균 두께(te)는 2×te < td 를 만족할 수 있다.

다시 말해, 유전체층(111) 하나의 평균 두께(td)는 내부 전극(121, 122) 하나의 평균 두께(te)의 2 배 보다 더 클 수 있다. 바람직하게는, 복수의 유전체층(111)의 평균 두께(td)는 복수의 내부 전극(121, 122)의 평균 두께(te)의 2 배 보다 더 클 수 있다.

일반적으로 고전압 전장용 전자 부품은, 고전압 환경 하에서 절연파괴전압(Breakdown Voltage, BDV)의 저하에 따른 신뢰성 문제가 주요한 이슈이다.

이에, 고전압 환경 하에서 절연파괴전압의 저하를 막기 위하여 유전체층(111)의 평균 두께(td)를 내부 전극(121, 122)의 평균 두께(te)의 2 배 보다 더 크게 함으로써, 내부 전극 간 거리인 유전체층의 두께를 증가시킬 수 있고, 절연파괴전압 특성을 향상시킬 수 있다.

유전체층(111)의 평균 두께(td)가 내부 전극(121, 122) 평균 두께(te)의 2 배 이하일 경우에는, 내부 전극 간 거리인 유전체층의 평균 두께가 얇아 절연파괴전압이 저하될 수 있으며, 내부 전극 간 단락이 발생할 수 있다.

고전압 전자 부품에서, 내부 전극의 평균 두께(te)는 1 μm 이하일 수 있으며, 유전체층의 평균 두께(td)는 3.0 μm 이하일 수 있으나, 반드시 이에 제한되는 것은 아니다.

한편, 바디(110)는 용량 형성부(Ac)의 제1 방향 양 단면(end-surface) 상에 배치되는 커버부(112, 113)를 포함할 수 있다.

구체적으로, 용량 형성부(Ac)의 제1 방향 일면에 배치되는 제1 커버부(112) 및 용량 형성부(Ac)의 제1 방향 타면에 배치되는 제2 커버부(113)를 포함할 수 있으며, 보다 구체적으로, 용량 형성부(Ac)의 제1 방향 상부에 배치되는 상부 커버부(112) 및 용량 형성부(Ac)의 제1 방향 하부에 배치되는 하부 커버부(113)를 포함할 수 있다.

상부 커버부(112) 및 하부 커버부(113)는 단일 제2 유전체층 또는 2개 이상의 제2 유전체층을 용량 형성부(Ac)의 상하면에 각각 제1 방향으로 적층하여 형성할 수 있으며, 기본적으로 물리적 또는 화학적 스트레스에 의한 내부 전극(121, 122)의 손상을 방지하는 역할을 수행할 수 있다.

상부 커버부(112) 및 하부 커버부(113)는 내부 전극(121, 122)을 포함하지 않으며, 제1 유전체층(111)과 동일한 유전체 물질을 포함할 수 있다. 즉, 상부 커버부(112) 및 하부 커버부(113)는 세라믹 재료를 포함할 수 있으며, 예를 들어 티탄산바륨(BaTiO3)계 세라믹 재료를 포함할 수 있다.

다만, 제2 유전체층의 조성은 제1 유전체층(111)의 조성과 상이할 수 있으며, 예를 들어, 제2 유전체층은 갈륨(Ga)을 포함할 수 있다.

즉, 커버부(112, 113)는 갈륨(Ga)을 포함할 수 있다.

커버부(112, 113)가 갈륨(Ga)을 포함함으로써, 소성 온도를 저하시켜 기공(P) 수를 감소시킬 수 있으며, 이에 따라 커버부(112, 113)의 치밀도가 향상되어 내습 신뢰성이 향상될 수 있다. 또한, 외부로부터 충격을 받더라도 크랙(crack)이 생성되는 것을 억제할 수 있어 기계적 특성이 향상될 수 있다.

또한, 제2 유전체층은 티탄산바륨(BaTiO3)과 같은 유전체 물질을 이용하여 형성될 수 있으므로, 소성 후 유전체 미세구조를 포함할 수 있다. 유전체 미세구조는, 복수의 결정립, 상기 인접한 결정립 사이에 배치되는 결정립계, 및 상기 결정립계가 3 개 이상 접하는 지점에 배치되는 삼중점을 포함할 수 있으며, 각각 복수 개를 포함할 수 있다.

한편, 커버부(112, 113)의 두께(tc)는 특별히 한정할 필요는 없다.

다만, 적층형 전자 부품의 소형화 및 고용량화를 보다 용이하게 달성하기 위하여 커버부(112, 113)의 두께(tc)는 100 μm 이하일 수 있고, 바람직하게는 30 μm 이하일 수 있으며, 초소형 제품에서는 보다 바람직하게 20 μm 이하일 수 있다.

여기서, 커버부(112, 113)의 두께(tc)는 커버부(112, 113)의 제1 방향 크기를 의미할 수 있다. 또한, 커버부(112, 113)의 두께(tc)는 커버부(112, 113)의 평균 두께(tc)를 의미할 수 있으며, 커버부(112, 113)의 제1 방향 평균 크기를 의미할 수 있다.

커버부(112, 113)의 제1 방향 평균 크기는 바디(110)의 제1 및 제2 방향 단면을 1만 배율의 주사전자현미경(SEM)으로 이미지를 스캔하여 측정할 수 있다. 보다 구체적으로, 하나의 커버부를 스캔한 이미지에서 제2 방향으로 등간격인 30개의 지점에서 제1 방향 크기를 측정하여 계산한 평균값일 수 있다.

또한, 전술한 방법으로 측정한 커버부의 제1 방향 평균 크기는, 바디(110)의 제1 및 제3 방향 단면(cross-section)에 있어서, 커버부의 제1 방향 평균 크기와 실질적으로 동일한 크기를 가질 수 있다.

한편, 적층형 전자 부품(100)은 바디(110)의 제3 방향 양 단면(end-surface) 상에 배치되는 사이드 마진부(114, 115)를 포함할 수 있다.

보다 구체적으로, 사이드 마진부(114, 115)는 바디(110)의 제5 면(5)에 배치된 제1 사이드 마진부(114) 및 제6 면(6)에 배치된 제2 사이드 마진부(115)를 포함할 수 있다. 즉, 사이드 마진부(114, 115)는 바디(110)의 제3 방향 양 단면(end-surface)에 배치될 수 있다.

사이드 마진부(114, 115)는 도시된 바와 같이, 바디(110)의 제1 및 제3 방향 단면(cross-section)을 기준으로, 제1 및 제2 내부 전극(121, 122)의 제3 방향 양 끝단과 바디(110)의 경계면 사이의 영역을 의미할 수 있다.

사이드 마진부(114, 115)는 기본적으로 물리적 또는 화학적 스트레스에 의한 내부 전극(121, 122)의 손상을 방지하는 역할을 수행할 수 있다.

사이드 마진부(114, 115)는 세라믹 그린시트 상에 사이드 마진부(114, 115)가 형성될 곳을 제외하고 도전성 페이스트를 도포하여 내부 전극(121, 122)을 형성하고, 내부 전극(121, 122)에 의한 단차를 억제하기 위하여, 적층 후의 내부 전극(121, 122)이 바디(110)의 제5 및 제6 면(5, 6)으로 노출되도록 절단한 후, 단일 제3 유전체층 또는 2 개 이상의 제3 유전체층을 용량 형성부(Ac)의 제3 방향 양 단면(end-surface)에 제3 방향으로 적층하여 형성할 수도 있다.

제1 사이드 마진부(114) 및 제2 사이드 마진부(115)는 내부 전극(121, 122)을 포함하지 않으며, 제1 유전체층(111)과 동일한 유전체 물질을 포함할 수 있다. 즉, 제1 사이드 마진부(114) 및 제2 사이드 마진부(115)는 세라믹 재료를 포함할 수 있으며, 예를 들어 티탄산바륨(BaTiO3)계 세라믹 재료를 포함할 수 있다.

다만, 제3 유전체층의 조성은 제1 유전체층(111)의 조성과 상이할 수 있으며, 예를 들어, 제3 유전체층은 갈륨(Ga)을 포함할 수 있다.

즉, 사이드 마진부(114, 115)는 갈륨(Ga)을 포함할 수 있다.

사이드 마진부(114, 115)가 갈륨(Ga)을 포함함으로써, 소성 온도를 저하시켜 기공(P) 수를 감소시킬 수 있으며, 이에 따라 사이드 마진부(114, 115)의 치밀도가 향상되어 내습 신뢰성이 향상될 수 있다. 또한, 외부로부터 충격을 받더라도 크랙(crack)이 생성되는 것을 억제할 수 있어 기계적 특성이 향상될 수 있다.

또한, 제3 유전체층은 티탄산바륨(BaTiO3)과 같은 유전체 물질을 이용하여 형성될 수 있으므로, 소성 후 유전체 미세구조를 포함할 수 있다. 유전체 미세구조는, 복수의 결정립, 상기 인접한 결정립 사이에 배치되는 결정립계, 및 상기 결정립계가 3 개 이상 접하는 지점에 배치되는 삼중점을 포함할 수 있으며, 각각 복수 개를 포함할 수 있다.

한편, 제1 및 제2 사이드 마진부(114, 115)의 폭(wm)은 특별히 한정할 필요는 없다.

다만, 적층형 전자 부품(100)의 소형화 및 고용량화를 보다 용이하게 달성하기 위하여 제1 및 제2 사이드 마진부(114, 115)의 폭(wm)은 100 μm 이하일 수 있고, 바람직하게는 30 μm 이하일 수 있으며, 초소형 제품에서는 보다 바람직하게 20 μm 이하일 수 있다.

여기서, 사이드 마진부(114, 115)의 폭(wm)은 사이드 마진부(114, 115) 각각의 제3 방향 크기를 의미할 수 있다. 또한, 사이드 마진부(114, 115)의 폭(wm)은 사이드 마진부(114, 115)의 평균 폭(wm)을 의미할 수 있으며, 사이드 마진부(114, 115)의 제3 방향 평균 크기를 의미할 수 있다.

사이드 마진부(114, 115)의 제3 방향 평균 크기는 바디(110)의 제1 및 제3 방향 단면(cross-section)을 1만 배율의 주사전자현미경(SEM)으로 이미지를 스캔하여 측정할 수 있다. 보다 구체적으로, 하나의 사이드 마진부를 스캔한 이미지에서 제1 방향으로 등간격인 10개의 지점에서 제3 방향 크기를 측정하여 계산한 평균값을 의미할 수 있다.

이하에서, 본 발명의 일 실시형태에 대해 보다 구체적으로 설명하기로 한다.

본 발명의 일 실시형태에 있어서, 커버부(112, 113)에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(A)에 대한, 사이드 마진부(114, 115)에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(B)의 비율(B/A)은 1.5 ≤ B/A 를 만족할 수 있다.

커버부(112, 113)와 사이드 마진부(114, 115)에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수에 관한 비율(B/A)이 1.5 ≤ B/A 를 만족함으로써, 커버부(112, 113) 및 사이드 마진부(114, 115)의 소성 온도를 저하시켜 기공(P) 수를 감소시킬 수 있으며, 이에 따라 커버부(112, 113) 및 사이드 마진부(114, 115)의 치밀도가 향상되어 내습 신뢰성이 향상될 수 있다. 또한, 외부로부터 충격을 받더라도 크랙(crack)이 생성되는 것을 억제할 수 있어 기계적 특성이 향상될 수 있다.

또한, 갈륨(Ga)은 저온 소성을 가능하게 하므로, 결정립의 비입성장을 억제하여, 결정립의 크기를 작게하고 균일한 성장을 가능하게 하여, 결정립 크기 분포도를 개선시킬 수 있다. 이에 의해, 기공(P)의 수가 감소할 수 있으며, 전계집중현상으로 인한 절연파괴전압(BDV)을 개선시킬 수 있다.

한편, 기공(P)의 수를 제어하기 위해서라면, 커버부(112, 113) 및 사이드 마진부(114, 115)에 포함된 갈륨(Ga)의 비율(B/A)의 상한 값은 특별히 제한되지 않으나, 10.0 이하일 수 있으며, 다시 말해, B/A ≤ 10.0 을 만족할 수 있다.

커버부(112, 113)와 사이드 마진부(114, 115)에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수에 관한 비율(B/A)이 B/A < 1.5 인 경우, 목표로 하는 기공(P)의 수가 많아져 내습 신뢰성이 열위해질 우려가 있으며, 기계적 강도가 저하되어 용량을 형성하는 내부 전극(121, 122)을 충분히 보호하지 못할 우려가 있다.

이때, 커버부(112, 113)에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(A)는 0 몰 초과 1.0 몰 이하일 수 있다. 다시 말해, 0 몰 < A ≤ 1.0 몰을 만족할 수 있다.

커버부(112, 113)에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(A)가 0 몰 < A ≤ 1.0 몰을 만족함으로써, 커버부(112, 113)의 소성 온도를 저하시켜 기공(P) 수를 감소시킬 수 있으며, 이에 따라 커버부(112, 113)의 치밀도가 향상되어 내습 신뢰성이 향상될 수 있다. 또한, 외부로부터 충격을 받더라도 크랙(crack)이 생성되는 것을 억제할 수 있어 기계적 특성이 향상될 수 있다.

한편, 커버부(112, 113)에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(A)가 1.0 몰 초과(1.0 몰 < A)인 경우, 갈륨(Ga)의 과량 첨가로 인해 응집물이 발생하여 절연파괴전압(BDV)이 저하되거나, 결정립의 성장이 과하게 억제되어 치밀도가 저하되고 기계적 강도가 저하되는 부효과가 발생할 우려가 있다.

한편, 사이드 마진부(114, 115)에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(B)는 0 몰 초과 1.0 몰 이하일 수 있다. 다시 말해, 0 몰 < B ≤ 1.0 몰을 만족할 수 있다.

사이드 마진부(114, 115)에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(B)가 0 몰 < B ≤ 1.0 몰을 만족함으로써, 사이드 마진부(114, 115)의 소성 온도를 저하시켜 기공(P) 수를 감소시킬 수 있으며, 이에 따라 사이드 마진부(114, 115)의 치밀도가 향상되어 내습 신뢰성이 향상될 수 있다. 또한, 외부로부터 충격을 받더라도 크랙(crack)이 생성되는 것을 억제할 수 있어 기계적 특성이 향상될 수 있다.

한편, 사이드 마진부(114, 115)에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(B)가 1.0 몰 초과(1.0 몰 < B)인 경우, 갈륨(Ga)의 과량 첨가로 인해 응집물이 발생하여 절연파괴전압(BDV)이 저하되거나, 결정립이 성장이 과하게 억제되어 치밀도가 저하되고 기계적 강도가 저하되는 부효과가 발생할 우려가 있다.

본 발명의 일 실시형태에 있어서, 커버부(112, 113)는 갈륨(Ga)을 포함한 이차상(secondary-phase)을 포함할 수 있으며, 이때 이차상은 커버부(112, 113)의 삼중점에 배치될 수 있다.

커버부(112, 113)에 포함된 이차상이 갈륨(Ga)을 포함함으로써, 커버부(112, 113)의 기공(P) 수가 감소하고 치밀도가 향상되어 내습 신뢰성이 향상될 수 있으며, 외부로부터 충격을 받더라도 크랙(crack)이 생성되는 것을 억제할 수 있어 기계적 특성이 향상될 수 있다.

또한, 사이드 마진부(114, 115)는 갈륨(Ga)을 포함한 이차상(secondary-phase)을 포함할 수 있으며, 이때 이차상은 사이드 마진부(114, 115)의 삼중점에 배치될 수 있다.

사이드 마진부(114, 115)에 포함된 이차상이 갈륨(Ga)을 포함함으로써, 사이드 마진부(114, 115)의 기공(P) 수가 감소하고 치밀도가 향상되어 내습 신뢰성이 향상될 수 있으며, 외부로부터 충격을 받더라도 크랙(crack)이 생성되는 것을 억제할 수 있어 기계적 특성이 향상될 수 있다.

본 발명에서 「이차상(secondary-phase)」이란, 페로브스카이트계(ABO3) 유전체 입자와는 상이한 조성을 가지는 입자 또는 편석(segregation)을 의미할 수 있다. 구체적으로, 이차상 입자 중의 바륨(Ba)의 원자 백분율(at%)은 30.0 at% 이하, 이차상 입자 중의 티타늄(Ti)의 원자 백분율(at%)은 30.0 at% 이하, 이차상 입자 중의 규소(Si)의 원자 백분율(at%)은 15.0 at% 이하, 이차상 입자 중의 알루미늄(Al)의 원자 백분율(at%)은 15.0 a% 이하일 수 있으며, 상기 바륨(Ba), 티타늄(Ti), 규소(Si), 및 알루미늄(Al)의 원자 백분율(at%) 조건들을 모두 만족하는 입자를 의미할 수 있다.

본 발명에서, 적층형 전자 부품(100)의 각 구성에 포함된 원소의 함량을 측정하는 보다 구체적인 방법의 일 예로서, 파괴 공법의 경우, 주사전자현미경(SEM)의 EDS 모드, 투과전자현미경(Transmission Electron Microscope, TEM)의 EDS 모드, 또는 주사투과전자현미경(Scanning Transmission Electron Microscope, STEM)의 EDS 모드를 이용해 성분을 분석할 수 있다. 먼저, 소결이 완료된 바디 또는 사이드 마진부의 단면(cross-section) 중 유전체 미세구조를 포함하는 영역에서 집속이온빔(Focused Ion Beam, FIB) 장비를 이용하여 박편화된 분석시료를 준비한다. 그리고 박편화된 시료를 제논(Xe) 또는 아르곤(Ar) 이온 밀링을 이용하여 표면의 데미지층을 제거하고, 이후 SEM-EDS, TEM-EDS, 또는 STEM-EDS를 이용하여 얻어진 이미지에서 측정하고자 하는 각 성분을 맵핑(mapping)하여 정성/정량 분석을 진행한다. 이 경우, 각 성분의 정성/정량 분석 그래프는 각 원소의 질량 백분율(wt%), 원자 백분율(at%), 또는 몰 백분율(mol%)로 환산하여 나타낼 수도 있다.

또 다른 방법으로는, 칩을 분쇄하여 유전체 미세구조가 포함된 영역을 선별하고, 이렇게 선별된 유전체 미세구조가 포함된 부분을 유도결합플라즈마 분광분석기(ICP-OES), 유도결합플라즈마 질량분석기(ICP-MS) 등의 장치를 이용하여 유전체 미세구조가 포함된 영역의 성분을 분석할 수 있다.

그리고, 본 발명의 일 실시형태에 있어서, 커버부(112, 113)에 포함된 이차상은 글래스(glass)를 포함할 수 있으며, 예를 들어, 규소(Si)계 글래스(glass)를 포함할 수 있고, 또는 알루미늄(Al)-규소(Si)계 글래스를 포함할 수 있다.

커버부(112, 113)에 포함된 이차상이 글래스를 포함함으로써, 글래스로 인한 이차상의 형성이 보다 용이하고, 갈륨(Ga)이외의 원소들, 예를 들어, 규소(Si)를 더 포함하거나, 알루미늄(Al)을 더 포함할 수 있으며, 갈륨(Ga)이외의 원소들, 예를 들어, 디스프로슘(Dy)과 같은 희토류 원소나, 마그네슘(Mg), 주석(Sn) 원소 등과 같은 부성분이 티탄산바륨(BaTiO3)계 유전체 물질에 고용되지 않고, 이차상에 포함될 수 있다.

또한, 사이드 마진부(114, 115)에 포함된 이차상은 글래스(glass)를 포함할 수 있으며, 예를 들어, 규소(Si)계 글래스(glass)를 포함할 수 있고, 또는 알루미늄(Al)-규소(Si)계 글래스를 포함할 수 있다.

사이드 마진부(114, 115)에 포함된 이차상이 글래스를 포함함으로써, 글래스로 인한 이차상의 형성이 보다 용이하고, 갈륨(Ga)이외의 원소들, 예를 들어, 규소(Si)를 더 포함하거나, 알루미늄(Al)을 더 포함할 수 있으며, 갈륨(Ga)이외의 원소들, 예를 들어, 디스프로슘(Dy)과 같은 희토류 원소나, 주석(Sn) 원소 등이 티탄산바륨(BaTiO3)계 유전체 물질에 고용되지 않고, 이차상에 포함될 수 있다.

본 발명의 일 실시형태에 있어서, 커버부(112, 113)에 포함된 결정립계는 갈륨(Ga)을 포함할 수 있다.

커버부(112, 113)의 결정립계가 갈륨(Ga)을 포함함으로써, 소성 온도를 저하시켜 기공(P) 수를 감소시킬 수 있으며, 이에 따라 커버부(112, 113)의 치밀도가 향상되어 내습 신뢰성이 향상될 수 있다. 또한, 외부로부터 충격을 받더라도 크랙(crack)이 생성되는 것을 억제할 수 있어 기계적 특성이 향상될 수 있다.

이때, 커버부(112, 113)의 결정립계는 갈륨(Ga)의 원자 백분율(at%)이 2.0 at% 이상인 영역을 포함할 수 있으며, 상한 값은 특별히 제한되는 것은 아니나, 예를 들어, 4.0 at% 이하일 수 있다.

커버부(112, 113)의 결정립계가 갈륨(Ga)의 원자 백분율(at%)이 2.0 at% 이상인 영역을 포함함으로써, 소성 온도를 저하시켜 기공(P) 수를 감소시킬 수 있으며, 이에 따라 커버부(112, 113)의 치밀도가 향상되어 내습 신뢰성이 향상될 수 있다. 또한, 외부로부터 충격을 받더라도 크랙(crack)이 생성되는 것을 억제할 수 있어 기계적 특성이 향상될 수 있다.

또한, 커버부(112, 113)의 결정립계에 포함된 갈륨(Ga)의 평균 원자 백분율(at%)이 0.5 at% 이상 2.0 at% 이하일 수 있다.

커버부(112, 113)의 결정립계에 포함된 갈륨(Ga)의 평균 원자 백분율(at%)이 0.5 at% 이상 2.0 at% 이하를 만족함으로써, 소성 온도를 저하시켜 기공(P) 수를 감소시킬 수 있으며, 이에 따라 커버부(112, 113)의 치밀도가 향상되어 내습 신뢰성이 향상될 수 있다. 또한, 외부로부터 충격을 받더라도 크랙(crack)이 생성되는 것을 억제할 수 있어 기계적 특성이 향상될 수 있다.

여기서, 커버부(112, 113)의 결정립계에 포함된 갈륨(Ga)의 원자 백분율(at%)을 측정하는 방법은, 특별히 제한되는 것은 아니나, 전술한 바와 같이 EDS 분석방법을 이용할 수 있다. EDS 분석 위치는 결정립계의 지점들(points)을 측정하여 확인하거나, 결정립계에 수직한 방향으로 라인-프로파일(line-profile)을 이용하여 구할 수 있으며, 측정된 라인-프로파일에서 갈륨(Ga)의 원자 백분율(at%)을 확인할 수 있다.

마찬가지로, 본 발명의 일 실시형태에 있어서, 사이드 마진부(114, 115)에 포함된 결정립계는 갈륨(Ga)을 포함할 수 있다.

사이드 마진부(114, 115)의 결정립계가 갈륨(Ga)을 포함함으로써, 소성 온도를 저하시켜 기공(P) 수를 감소시킬 수 있으며, 이에 따라 사이드 마진부(114, 115)의 치밀도가 향상되어 내습 신뢰성이 향상될 수 있다. 또한, 외부로부터 충격을 받더라도 크랙(crack)이 생성되는 것을 억제할 수 있어 기계적 특성이 향상될 수 있다.

이때, 사이드 마진부(114, 115)의 결정립계는 갈륨(Ga)의 원자 백분율(at%)이 2.0 at% 이상인 영역을 포함할 수 있으며, 상한 값은 특별히 제한되는 것은 아니나, 예를 들어, 4.0 at% 이하일 수 있다.

사이드 마진부(114, 115)의 결정립계가 갈륨(Ga)의 원자 백분율(at%)이 2.0 at% 이상인 영역을 포함함으로써, 소성 온도를 저하시켜 기공(P) 수를 감소시킬 수 있으며, 이에 따라 사이드 마진부(114, 115)의 치밀도가 향상되어 내습 신뢰성이 향상될 수 있다. 또한, 외부로부터 충격을 받더라도 크랙(crack)이 생성되는 것을 억제할 수 있어 기계적 특성이 향상될 수 있다.

또한, 사이드 마진부(114, 115)의 결정립계에 포함된 갈륨(Ga)의 평균 원자 백분율(at%)이 0.5 at% 이상 2.0 at% 이하일 수 있다.

사이드 마진부(114, 115)의 결정립계에 포함된 갈륨(Ga)의 평균 원자 백분율(at%)이 0.5 at% 이상 2.0 at% 이하를 만족함으로써, 소성 온도를 저하시켜 기공(P) 수를 감소시킬 수 있으며, 이에 따라 사이드 마진부(114, 115)의 치밀도가 향상되어 내습 신뢰성이 향상될 수 있다. 또한, 외부로부터 충격을 받더라도 크랙(crack)이 생성되는 것을 억제할 수 있어 기계적 특성이 향상될 수 있다.

여기서, 사이드 마진부(114, 115)의 결정립계에 포함된 갈륨(Ga)의 원자 백분율(at%)을 측정하는 방법은, 특별히 제한되는 것은 아니나, 전술한 바와 같이 EDS 분석방법을 이용할 수 있다. EDS 분석 위치는 결정립계의 지점들(points)을 측정하여 확인하거나, 결정립계에 수직한 방향으로 라인-프로파일(line-profile)을 측정하여 구할 수 있으며, 측정된 라인-프로파일의 원소(들) 중에서 갈륨(Ga)의 원자 백분율(at%)을 확인할 수 있다.

본 발명의 일 실시형태에 있어서, 커버부(112, 113)는 단면(cross-section)을 기준으로 1 μm2에 포함된 기공(P)의 수가 0.30 개 이하일 수 있고, 바람직하게는 1 μm2에 포함된 기공(P)의 수가 0.25 개 이하일 수 있으며, 보다 바람직하게는 1 μm2에 포함된 기공(P)의 수가 0.21 개 이하일 수 있다.

기공(P)의 수를 측정하는 방법은 특별히 제한되는 것은 아니나, 도 6을 예로 들어 설명하면, 적층형 전자 부품(100)의 제1 및 제3 방향 단면(cross-section)을 기준으로, 제1 커버부(112)의 단면(cross-section)을 포함하는 M1 영역을 주사전자현미경(SEM)을 통해 이미지를 촬영한 후, 기공(P)을 측정할 수 있는 프로그램을 통해 기공(P)의 수를 측정할 수 있다.

그리고, 본 발명의 일 실시형태에 있어서, 사이드 마진부(114, 115)는 단면(cross-section)을 기준으로 1 μm2에 포함된 기공(P)의 수가 0.22 개 이하일 수 있고, 바람직하게는 1 μm2에 포함된 기공(P)의 수가 0.21 개 이하일 수 있다.

기공(P)의 수를 측정하는 방법은 특별히 제한되는 것은 아니나, 도 6을 예로 들어 설명하면, 적층형 전자 부품(100)의 제1 및 제3 방향 단면(cross-section)을 기준으로, 제2 사이드 마진부(115)의 단면(cross-section)을 포함하는 M2 영역을 주사전자현미경(SEM)을 통해 이미지를 촬영한 후, 기공(P)을 측정할 수 있는 프로그램을 통해 기공(P)의 수를 측정할 수 있다.

본 발명의 일 실시형태에서는 세라믹 전자 부품(100)이 2 개의 외부 전극(131, 132)을 갖는 구조를 설명하고 있지만, 외부 전극(131, 132)의 개수나 형상 등은 내부 전극(121, 122)의 형태나 기타 다른 목적에 따라 바뀔 수 있을 것이다.

외부 전극(131, 132)은 바디(110) 상에 배치되어 내부 전극(121, 122)과 연결될 수 있다.

보다 구체적으로, 외부 전극(131, 132)은 바디(110)의 제3 및 제4 면(3, 4)에 각각 배치되며, 제1 및 제2 내부 전극(121, 122)과 각각 연결되는 제1 및 제2 외부 전극(131, 132)을 포함할 수 있다. 즉, 제1 외부 전극(131)은 바디의 제3 면(3)에 배치되어 제1 내부 전극(121)과 연결될 수 있으며, 제2 외부 전극(132)은 바디의 제4 면(4)에 배치되어 제2 내부 전극(122)과 연결될 수 있다.

또한, 외부 전극(131, 132)은 바디(110)의 제1 및 제2 면(1, 2) 상의 일부에 연장되어 배치될 수 있고, 또는 바디(110)의 제5 및 제6 면(5, 6) 상의 일부에 연장되어 배치될 수 있다. 즉, 제1 외부 전극(131)은 바디(110)의 제1, 제2, 제5, 제6 면(1, 2, 5, 6) 상의 일부, 및 바디(110)의 제3 면(3) 상에 배치될 수 있고, 제2 외부 전극(132)은 바디(110)의 제1, 제2, 제5, 제6 면(1, 2, 5, 6) 상의 일부, 및 바디(110)의 제3 면(3) 상에 배치될 수 있다.

한편, 외부 전극(131, 132)은 금속 등과 같이 전기 전도성을 갖는 것이라면 어떠한 물질을 사용하더라도 형성될 수 있고, 전기적 특성, 구조적 안정성 등을 고려하여 구체적인 물질이 결정될 수 있으며, 나아가 다층 구조를 가질 수 있다.

예를 들어, 외부 전극(131, 132)은 바디(110)에 배치되는 전극층 및 전극층 상에 배치되는 도금층을 포함할 수 있다.

전극층에 대한 보다 구체적인 예를 들면, 전극층은 제1 도전성 금속 및 글라스를 포함한 소성 전극층인 제1 전극층(131a, 132a)을 포함할 수 있으며, 제2 도전성 금속 및 수지를 포함한 수지계 전극인 제2 전극층(131b, 132b)을 포함할 수 있다.

여기서, 제1 도전성 금속은 제1 전극층(131a, 132a)에 포함된 도전성 금속을 의미할 수 있으며, 제2 도전성 금속은 제2 전극층(131b, 132b)에 포함된 도전성 금속을 의미할 수 있다. 이때, 제1 도전성 금속 및 제2 도전성 금속은 동일하거나 상이할 수 있고, 복수의 금속 물질을 포함할 경우, 적어도 하나의 금속 물질이 동일할 수 있으나, 특별히 이에 제한되는 것은 아니다.

또한, 전극층(131a, 132a, 131b, 132b)은 바디 상에 제1 전극층(131a, 132a) 및 제2 전극층(131b, 132b) 이 순차적으로 형성된 형태일 수 있으며, 바디 상에 도전성 금속을 포함한 시트를 전사하는 방식으로 형성되거나, 소성 전극 상에 도전성 금속을 포함한 시트를 전사하는 방식으로 형성된 것일 수 있다.

전극층(131a, 132a, 131b, 132b)에 포함되는 제1 및 제2 도전성 금속으로 전기 전도성이 우수한 재료를 사용할 수 있으며, 예를 들어, 제1 및 제2 도전성 금속은 니켈(Ni), 구리(Cu), 팔라듐(Pd), 은(Ag), 금(Au), 백금(Pt), 주석(Sn), 텅스텐(W), 티타늄(Ti) 및 이들의 합금으로 이루어진 군으로부터 선택된 하나 이상을 포함할 수 있으나, 특별히 이에 한정되지 않는다.

본 발명의 일 실시형태에 있어서, 전극층(131a, 132a, 131b, 132b)은 제1 전극층(131a, 132a) 및 제2 전극층(131b, 132b)을 포함하는 2 층의 구조를 가질 수 있으며, 이에 따라 외부 전극(131, 132)은 도전성 금속 및 글라스를 포함하는 제1 전극층(131a, 132a) 및 상기 제1 전극층(131a, 132a) 상에 배치되며 도전성 금속 및 수지를 포함하는 제2 전극층(131b, 132b)을 포함할 수 있다.

제1 전극층(131a, 132a)은 글라스를 포함함에 따라 바디(110)와의 접합성을 향상시키는 역할을 수행할 수 있고, 제2 전극층(131b, 132b)은 수지를 포함함에 따라 휨 강도를 향상시키는 역할을 수행할 수 있다.

제1 전극층(131a, 132a)에 사용되는 도전성 금속은 정전 용량 형성을 위해 상기 내부 전극(121, 122)과 전기적으로 연결될 수 있는 재질이면 특별히 제한되지 않으며, 예를 들어, 니켈(Ni), 구리(Cu), 팔라듐(Pd), 은(Ag), 금(Au), 백금(Pt), 주석(Sn), 텅스텐(W), 티타늄(Ti) 및 이들의 합금으로 이루어진 군으로부터 선택된 하나 이상을 포함할 수 있다. 제1 전극층(131a, 132a)은 상기 도전성 금속 입자에 글라스 프릿을 첨가하여 마련된 도전성 페이스트를 도포한 후 소성함으로써 형성될 수 있다.

제2 전극층(131b, 132b)에 포함되는 도전성 금속은 제1 전극층(131a, 132a)과 전기적으로 연결되도록 하는 역할을 수행할 수 있다.

제2 전극층(131b, 132b)에 포함되는 도전성 금속은 전극층(131a, 132a)과 전기적으로 연결될 수 있는 재질이면 특별히 제한되지 않으며, 니켈(Ni), 구리(Cu), 팔라듐(Pd), 은(Ag), 금(Au), 백금(Pt), 주석(Sn), 텅스텐(W), 티타늄(Ti) 및 이들의 합금으로 이루어진 군으로부터 선택된 하나 이상을 포함할 수 있다.

제2 전극층(131b, 132b)에 포함되는 도전성 금속은 구형 입자 및 플레이크형 입자 중 1 이상을 포함할 수 있다. 즉, 도전성 금속은 플레이크형 입자로만 이루어지거나, 구형 입자로만 이루어질 수 있고, 플레이크형 입자와 구형 입자가 혼합된 형태일 수도 있다. 여기서, 구형 입자는 완전한 구형이 아닌 형태도 포함할 수 있으며, 예를 들어 장축과 단축의 길이 비율(장축/단축)이 1.45 이하인 형태를 포함할 수 있다. 플레이크형 입자는 납작하면서 길쭉한 형태를 가진 입자를 의미하며, 특별히 제한되는 것은 아니나, 예를 들어 장축과 단축의 길이 비율(장축/단축)이 1.95 이상일 수 있다. 상기 구형 입자 및 플레이크형 입자의 장축과 단축의 길이는 적층형 전자 부품의 제3 방향의 중앙부에서 절단한 제1 및 제2 방향 단면(cross-section)을 주사전자현미경(SEM)으로 스캔하여 얻은 이미지로부터 측정할 수 있다.

제2 전극층(131b, 132b)에 포함되는 수지는 접합성 확보 및 충격 흡수 역할을 수행할 수 있다. 제2 전극층(131b, 132b)에 포함되는 수지는 접합성 및 충격흡수성을 가지고, 도전성 금속 입자와 혼합하여 페이스트를 만들 수 있는 것이면 특별히 제한되지 않으며, 예를 들어 에폭시계 수지를 포함할 수 있다.

또한, 제2 전극층(131b, 132b)은 복수의 금속 입자, 금속간 화합물 및 수지를 포함할 수 있다. 상기 금속간 화합물을 포함함에 따라 제1 전극층(131a, 132a)과의 전기적 연결성을 보다 향상시킬 수 있다. 상기 금속간 화합물은 복수의 금속 입자를 연결하여 전기적 연결성을 향상시키는 역할을 하며, 복수의 금속 입자를 둘러싸 서로 연결하는 역할을 수행할 수 있다.

이때, 상기 금속간 화합물은 수지의 경화 온도 보다 낮은 융점을 가진 금속을 포함할 수 있다. 즉, 상기 금속간 화합물이 수지의 경화 온도보다 낮은 융점을 가진 금속을 포함하기 때문에, 수지의 경화 온도보다 낮은 융점을 가진 금속이 건조 및 경화 공정을 거치는 과정에서 용융되고, 금속 입자의 일부와 금속간 화합물을 형성하여 금속 입자를 둘러싸게 된다. 이때, 금속간 화합물은 바람직하게 300˚C 이하의 저융점 금속을 포함할 수 있다.

예를 들어, 213~220˚C의 융점을 가지는 Sn을 포함할 수 있다. 건조 및 경화 공정을 거치는 과정에서 Sn이 용융되며, 용융된 Sn이 Ag, Ni 또는 Cu와 같은 고융점의 금속 입자를 모세관 현상에 의해 적시게 되고, Ag, Ni 또는 Cu 금속 입자의 일부와 반응하여 Ag3Sn, Ni3Sn4, Cu6Sn5, Cu3Sn 등의 금속간 화합물을 형성하게 된다. 반응에 참여하지 않은 Ag, Ni 또는 Cu는 금속 입자 형태로 남게 된다.

따라서, 상기 복수의 금속 입자는 Ag, Ni 및 Cu 중 하나 이상을 포함하고, 상기 금속간 화합물은 Ag3Sn, Ni3Sn4, Cu6Sn5 및 Cu3Sn 중 하나 이상을 포함할 수 있다.

도금층(131c, 132c)은 실장 특성을 향상시키는 역할을 수행할 수 있다.

도금층(131c, 132c)의 종류는 특별히 한정하지 않으며, 도면에서는 단일한 층의 도금층(131c, 132c)만을 도시하고 있으나, 이에 제한되는 것은 아니며, 니켈(Ni), 주석(Sn), 팔라듐(Pd) 및 이들의 합금 중 하나 이상을 포함하는 단일한 층의 도금층(131c, 132c)일 수 있고, 복수의 층으로 형성될 수 있다.

도금층(131c, 132c)에 대한 보다 구체적인 예를 들면, 도금층(131c, 132c)은 Ni 도금층 또는 Sn 도금층일 수 있으며, 전극층 상에 Ni 도금층 및 Sn 도금층이 순차적으로 형성된 형태일 수 있고, Sn 도금층, Ni 도금층 및 Sn 도금층이 순차적으로 형성된 형태일 수 있다. 또한, 도금층(131c, 132c)은 복수의 Ni 도금층 및/또는 복수의 Sn 도금층을 포함할 수도 있다.

적층형 전자 부품(100)의 사이즈는 특별히 한정할 필요는 없다.

다만, 소형화 및 고용량화를 동시에 달성하기 위해서는 유전체층 및 내부 전극의 두께를 얇게 하여 적층수를 증가시켜야 하기 때문에, 1005 (길이×폭: 1.0mm×0.5mm) 이하의 사이즈를 가지는 적층형 전자 부품(100)에서 본 발명에 따른 효과가 보다 현저해질 수 있다.

이하, 실시예를 통하여 본 발명을 더욱 상세히 설명하지만, 이는 발명의 구체적인 이해를 돕기 위한 것으로 본 발명의 범위가 실시예에 의해 한정되는 것은 아니다.

(실시예)

비교예는 커버부 및 사이드 마진부를 포함하는 적층형 전자 부품으로 제작하였으며, 커버부 및 사이드 마진부에 갈륨(Ga)을 첨가하지 않은 적층형 전자 부품으로 제작하였다.

실시예는 커버부 및 사이드 마진부에 갈륨(Ga)을 각각 1 몰 이하로 첨가한 것 외에는 비교예와 동일한 방법으로 적층형 전자 부품을 제작하였다. 이때, 커버부에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(A)에 대한, 사이드 마진부에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(B)의 비율(B/A)은 1.5 ≤ B/A 를 만족하도록 제작하였다.

이하의 다양한 비교예 및 실시예는 하나의 적층형 전자 부품에 대한 설명은 아니나, 전술한 제조 방법을 만족하는 비교예 및 실시예에 해당한다.

도 7a 및 도 7b는 비교예 1에 있어서, 도 6의 M1 및 M2 영역을 주사전자현미경(SEM)으로 촬영한 이미지이고, 도 7c 및 도 7d는 실시예 1에 있어서 도 6의 M1 및 M2 영역을 주사전자현미경(SEM)으로 촬영한 이미지이다.

보다 구체적으로, 도 7a는 비교예 1에 있어서, 제1 커버부의 제1 및 제3 방향 단면을 주사전자현미경(SEM)으로 촬영한 이미지이며, 제1 커버부의 단면 중 547 μm2에 포함된 기공(P)의 수는 229 개로 측정되었다. 도 7b는 비교예 1에 있어서 제2 사이드 마진부의 제1 및 제3 방향 단면을 주사전자현미경(SEM)으로 촬영한 이미지이며, 제2 사이드 마진부의 단면 중 190 μm2에 포함된 기공(P)의 수는 45 개로 측정되었다.

도 7c는 실시예 1에 있어서 제1 커버부의 제1 및 제3 방향 단면을 주사전자현미경(SEM)으로 촬영한 이미지이며, 제1 커버부의 단면 중 547 μm2에 포함된 기공(P)의 수는 110 개로 측정되었다. 도 7d는 실시예 1에 있어서 제2 사이드 마진부의 제1 및 제3 방향 단면을 주사전자현미경(SEM)으로 촬영한 이미지이며, 제2 사이드 마진부의 단면 중 190 μm2에 포함된 기공(P)의 수는 39 개로 측정되었다.

이로부터, 커버부에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(A)에 대한, 사이드 마진부에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(B)의 비율(B/A)이 1.5 ≤ B/A 을 만족하는 경우, 커버부 및 사이드 마진부에 포함된 기공(P)의 수가 감소하는 것을 알 수 있다.

도 8a는 비교예 2에 있어서, 제1 커버부의 제1 및 제3 방향 단면을 주사전자현미경(SEM)의 HAADF 모드로 촬영한 이미지이며, 도 8b는 도 8a의 영역에서 EDS 분석을 진행하여 알루미늄(Al) 원소를 맵핑(mapping)한 이미지이고, 도 8c는 도 8a의 영역에서 EDS 분석을 진행하여 규소(Si) 원소를 맵핑(mapping)한 이미지이다.

도 9a는 실시예 2에 있어서, 제1 커버부의 단면을 주사전자현미경(SEM)의 HAADF 모드로 촬영한 이미지이며, 도 9b는 도 9a의 영역에서 EDS 분석을 진행하여 알루미늄(Al) 원소를 맵핑(mapping)한 이미지이고, 도 9c는 도 9a의 영역에서 EDS 분석을 진행하여 규소(Si) 원소를 맵핑(mapping)한 이미지이며, 도 9d는 도 9a의 영역에서 EDS 분석을 진행하여 갈륨(Ga) 원소를 맵핑(mapping)한 이미지이다.

도 10a는 비교예 3의 사이드 마진부 단면을 주사전자현미경(SEM)의 HAADF 모드로 촬영한 이미지이며, 도 10b는 도 10a의 영역에서 EDS 분석을 진행하여 알루미늄(Al) 원소를 맵핑(mapping)한 이미지이고, 도 10c는 도 10a의 영역에서 EDS 분석을 진행하여 규소(Si) 원소를 맵핑(mapping)한 이미지이다.

도 11a는 실시예 3의 사이드 마진부 단면을 주사전자현미경(SEM)의 HAADF 모드로 촬영한 이미지이며, 도 11b는 도 11a의 영역에서 EDS 분석을 진행하여 알루미늄(Al) 원소를 맵핑(mapping)한 이미지이고, 도 11c는 도 11a의 영역에서 EDS 분석을 진행하여 규소(Si) 원소를 맵핑(mapping)한 이미지이며, 도 11d는 도 11a의 영역에서 EDS 분석을 진행하여 갈륨(Ga) 원소를 맵핑(mapping)한 이미지이다.

비교예 2 및 비교예 3 과 실시예 2 및 실시예 3으로부터, 커버부 및 사이드 마진부에 갈륨(Ga)이 포함된 경우, 결정립계 및 삼중점에 갈륨(Ga)이 배치되는 것을 확인할 수 있으며, 규소(Si) 및 알루미늄(Al)이 검출되는 영역에 갈륨(Ga)이 함께 배치되는 것으로부터, 규소(Si) 및 알루미늄(Al)을 포함한 이차상(secondary-phase)에 갈륨(Ga)이 포함된 것을 알 수 있다.

다음으로, 비교예 4 및 비교예 5와, 실시예 4 및 실시예 5에 대해 20 개의 샘플 칩(chip)이 장착된 채널(channel)을 각각 20 개씩 제작하여, 내습 신뢰성 평가를 진행하였다.

도 12a는 비교예 4의 내습 신뢰성 평가 그래프이고, 도 12b는 비교예 5의 내습 신뢰성 평가 그래프이다. 그리고, 도 12c는 실시예 4의 내습 신뢰성 평가 그래프이고, 도 12d는 실시예 5의 내습 신뢰성 평가 그래프이다.

내습 신뢰성 평가는 온도조건 85˚C, 상대습도조건 85%에서, 정격전압 1.0Vr을 8시간 동안 인가하였을 때, 절연 저항(IR) 값이 105 Ω 이하로 떨어진 채널을 불량이라고 평가하였다.

비교예 4 및 비교예 5의 경우, 불량으로 판정된 채널이 각각 1 개씩 존재하였던 반면, 실시예 4 및 실시예 5의 경우, 불량으로 판정된 채널이 없었으며 초기 절연 저항(IR0) 대비 절연 저항(IR)이 저하된 채널도 측정되지 않았다.

이로부터, 커버부에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(A)에 대한, 사이드 마진부에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(B)의 비율(B/A)이 1.5 ≤ B/A 을 만족하는 경우, 적층형 전자 부품의 내습 신뢰성이 향상되는 것을 알 수 있다.

도 13a는 비교예 6의 결정립 미세구조 크기에 관한 그래프이고, 도 13b는 실시예 6의 결정립 미세구조 크기에 관한 그래프이다.

결정립 미세구조는 각 시험예의 제1 커버부의 제1 및 제3 방향 단면(cross-section)의 일부 영역에 포함된 결정립을 의미한다. 도 13a 및 도 13b에서 막대 그래프는 미세구조의 평균크기를 의미하며, 'I' 자형 직선 그래프는 결정립 크기의 분포도를 의미한다.

비교예 6의 일부 영역에 포함된 결정립들의 평균 값은 200 nm 였고, 실시예 7의 일부 영역에 포함된 결정립들의 평균 값은 176 nm 였다. 또한, 결정립들의 크기 분포도는 비교예가 실시예보다 넓게 측정되었다.

이로부터, 커버부에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(A)에 대한, 사이드 마진부에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(B)의 비율(B/A)이 1.5 ≤ B/A 을 만족하는 경우, 결정립의 크기가 감소하는 것을 알 수 있고, 크기 분포도도 개선되는 것을 알 수 있으며, 이로부터 전계집중현상으로 인한 절연파괴전압(BDV)이 개선될 것임을 예측할 수 있다.

이상에서 본 발명의 실시 형태에 대하여 상세하게 설명하였지만 본 발명은 상술한 실시형태 및 첨부된 도면에 의해 한정되는 것이 아니며, 첨부된 청구범위에 의해 한정하고자 한다. 따라서, 청구범위에 기재된 본 발명의 기술적 사상을 벗어나지 않는 범위 내에서 당 기술분야의 통상의 지식을 가진 자에 의해 다양한 형태의 치환, 변형 및 변경이 가능할 것이며, 이 또한 본 발명의 범위에 속한다고 할 것이다.

또한, 본 명세서에서 사용된 '일 실시예'라는 표현은 서로 동일한 실시예를 의미하지 않으며, 각각 서로 다른 고유한 특징을 강조하여 설명하기 위해서 제공된 것이다. 그러나, 상기 제시된 일 실시예들은 다른 일 실시예의 특징과 결합되어 구현되는 것을 배제하지 않는다. 예를 들어, 특정한 일 실시예에서 설명된 사항이 다른 일 실시예에서 설명되어 있지 않더라도, 다른 일 실시예에서 그 사항과 반대되거나 모순되는 설명이 없는 한, 다른 일 실시예에 관련된 설명으로 이해될 수 있다.

본 명세서에서 사용된 용어는 단지 일 실시예를 설명하기 위해 사용된 것으로, 본 개시를 한정하려는 의도가 아니다. 이때, 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다.

100: 적층형 전자 부품

110: 바디

111: 유전체층

112, 113: 커버부

114, 115: 사이드 마진부

121, 122: 내부 전극

131, 132: 외부 전극

P: 기공

110: 바디

111: 유전체층

112, 113: 커버부

114, 115: 사이드 마진부

121, 122: 내부 전극

131, 132: 외부 전극

P: 기공

Claims (13)

- 유전체층 및 상기 유전체층과 제1 방향으로 번갈아 배치되는 내부 전극을 포함하는 용량 형성부, 및 상기 용량 형성부의 상기 제1 방향 양 단면(end-surface)에 배치되는 커버부를 포함하고, 상기 제1 방향으로 서로 마주보는 제1 및 제2 면, 상기 제1 및 제2 면과 연결되고 제2 방향으로 서로 마주보는 제3 및 제4 면, 상기 제1 내지 제4 면과 연결되고 제3 방향으로 서로 마주보는 제5 및 제6 면을 포함하는 바디;

상기 제3 및 제4 면에 배치되는 외부 전극; 및

상기 제5 및 제6 면에 배치되는 사이드 마진부; 를 포함하고,

상기 커버부 및 사이드 마진부는 티타늄(Ti) 및 갈륨(Ga)을 포함하며,

상기 커버부에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(A)에 대한, 상기 사이드 마진부에 포함된 티타늄(Ti) 100 몰 대비 갈륨(Ga)의 몰 수(B)의 비율(B/A)은

1.5 ≤ B/A 를 만족하는

적층형 전자 부품.

- 제1항에 있어서,

0 몰 < B ≤ 1.0 몰을 만족하는

적층형 전자 부품.

- 제1항에 있어서,

0 몰 < A ≤ 1.0 몰을 만족하는

적층형 전자 부품.

- 제1항에 있어서,

상기 유전체층은 갈륨(Ga)을 포함하지 않는

적층형 전자 부품.

- 제1항에 있어서,

상기 용량 형성부의 유전체층을 제1 유전체층이라고 할 때, 상기 커버부는 제2 유전체층을 포함하고, 상기 사이드 마진부는 제3 유전체층을 포함하며,

상기 제1 유전체층의 조성은, 상기 제2 유전체층 및 제3 유전체층 중 적어도 하나의 조성과 상이한

적층형 전자 부품.

- 제1항에 있어서,

상기 커버부 및 사이드 마진부 중 적어도 하나는 갈륨(Ga)을 포함한 이차상(secondary-phase)을 포함하는

적층형 전자 부품.

- 제6항에 있어서,

상기 커버부, 및 사이드 마진부 중 적어도 하나는,

복수의 결정립, 상기 인접한 결정립 사이에 배치되는 결정립계, 및 상기 결정립계가 3 개 이상 접하는 지점에 배치되는 삼중점을 포함하며,

상기 적어도 하나의 삼중점에 상기 이차상이 배치되는

적층형 전자 부품.

- 제6항에 있어서,

상기 이차상은 규소(Si)를 더 포함하는

적층형 전자 부품.

- 제1항에 있어서,

상기 커버부, 및 사이드 마진부 중 적어도 하나는 복수의 결정립, 및 인접한 결정립 사이에 배치되는 결정립계를 포함하며,

상기 결정립계는 갈륨(Ga)을 포함하는

적층형 전자 부품.

- 제9항에 있어서,

상기 결정립계는 갈륨(Ga)의 원자 백분율(at%)이 2.0 at% 이상인 영역을 포함하는

적층형 전자 부품.

- 제9항에 있어서,

상기 결정립계는 갈륨(Ga)의 평균 원자 백분율(at%)이 0.5 at% 이상 2.0 at% 이하인

적층형 전자 부품.

- 제1항에 있어서,

상기 커버부의 상기 제1 및 제3 방향 단면을 기준으로 1μm2 에 포함된 기공의 수는 0.30 개 이하인

적층형 전자 부품.

- 제1항에 있어서,

상기 사이드 마진부의 상기 제1 및 제3 방향 단면을 기준으로 1μm2 에 포함된 기공의 수는 0.22 개 이하인

적층형 전자 부품.

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020230158445A KR20250071663A (ko) | 2023-11-15 | 2023-11-15 | 적층형 전자 부품 |

| US18/826,966 US20250157733A1 (en) | 2023-11-15 | 2024-09-06 | Multilayer electronic component |

| EP24199253.6A EP4557332A1 (en) | 2023-11-15 | 2024-09-09 | Multilayer ceramic capacitor |

| JP2024157202A JP2025081221A (ja) | 2023-11-15 | 2024-09-11 | 積層型電子部品 |

| CN202411625787.0A CN120015528A (zh) | 2023-11-15 | 2024-11-14 | 多层电子组件 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020230158445A KR20250071663A (ko) | 2023-11-15 | 2023-11-15 | 적층형 전자 부품 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20250071663A true KR20250071663A (ko) | 2025-05-22 |

Family

ID=92712207

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020230158445A Pending KR20250071663A (ko) | 2023-11-15 | 2023-11-15 | 적층형 전자 부품 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20250157733A1 (ko) |

| EP (1) | EP4557332A1 (ko) |

| JP (1) | JP2025081221A (ko) |

| KR (1) | KR20250071663A (ko) |

| CN (1) | CN120015528A (ko) |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2022068525A (ja) | 2020-10-22 | 2022-05-10 | Tdk株式会社 | 積層セラミック電子部品 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013173626A (ja) * | 2012-02-23 | 2013-09-05 | Tdk Corp | 誘電体磁器組成物及びセラミック電子部品 |

| CN110246689B (zh) * | 2018-03-09 | 2022-05-24 | 三星电子株式会社 | 陶瓷电介质及其制造方法和陶瓷电子组件及电子设备 |

| US11322307B2 (en) * | 2019-12-27 | 2022-05-03 | Murata Manufacturing Co., Ltd. | Multilayer ceramic capacitor |

| KR102624590B1 (ko) * | 2020-12-07 | 2024-01-12 | 한국과학기술원 | 유전체 세라믹, 이의 제조 방법, 및 이를 포함하는 적층형 전자 부품 |

-

2023

- 2023-11-15 KR KR1020230158445A patent/KR20250071663A/ko active Pending

-

2024

- 2024-09-06 US US18/826,966 patent/US20250157733A1/en active Pending

- 2024-09-09 EP EP24199253.6A patent/EP4557332A1/en active Pending

- 2024-09-11 JP JP2024157202A patent/JP2025081221A/ja active Pending

- 2024-11-14 CN CN202411625787.0A patent/CN120015528A/zh active Pending

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2022068525A (ja) | 2020-10-22 | 2022-05-10 | Tdk株式会社 | 積層セラミック電子部品 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20250157733A1 (en) | 2025-05-15 |

| CN120015528A (zh) | 2025-05-16 |

| JP2025081221A (ja) | 2025-05-27 |

| EP4557332A1 (en) | 2025-05-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20130258546A1 (en) | Multilayer ceramic electronic component and fabrication method thereof | |

| KR20240091624A (ko) | 적층형 전자 부품 | |

| KR20220081633A (ko) | 적층형 전자 부품 및 유전체 조성물 | |

| KR102900301B1 (ko) | 적층형 전자 부품 | |

| KR20250071663A (ko) | 적층형 전자 부품 | |

| US20250174403A1 (en) | Multilayer electronic component | |

| US20260045412A1 (en) | Multilayer electronic component | |

| EP4557333A1 (en) | Multilayer ceramic capacitor | |

| US20250166916A1 (en) | Multilayer electronic component | |

| US20250166922A1 (en) | Multilayer electronic component | |

| US20250166915A1 (en) | Multilayer electronic component | |

| US20240274361A1 (en) | Multilayer electronic component | |

| US20240274355A1 (en) | Multilayer electronic component | |

| US12488945B2 (en) | Multilayer electronic component | |

| KR20250083918A (ko) | 적층형 전자 부품 | |

| EP4421834A2 (en) | Multilayer electronic component | |

| US20250218672A1 (en) | Multilayer electronic component | |

| US20240274363A1 (en) | Multilayer electronic component | |

| KR20250027168A (ko) | 적층형 전자 부품 | |

| KR20250075093A (ko) | 적층형 전자 부품 | |

| KR20240164342A (ko) | 적층형 전자 부품 | |

| KR20250074931A (ko) | 적층형 전자 부품 | |

| KR20250094360A (ko) | 적층형 전자 부품 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

Patent event code: PA01091R01D Comment text: Patent Application Patent event date: 20231115 |

|

| PG1501 | Laying open of application |