KR20180127379A - 프로세서-기반 시스템들 내의 로드 경로 이력에 기반한 어드레스 예측 테이블들을 사용하는 로드 어드레스 예측들의 제공 - Google Patents

프로세서-기반 시스템들 내의 로드 경로 이력에 기반한 어드레스 예측 테이블들을 사용하는 로드 어드레스 예측들의 제공 Download PDFInfo

- Publication number

- KR20180127379A KR20180127379A KR1020187028217A KR20187028217A KR20180127379A KR 20180127379 A KR20180127379 A KR 20180127379A KR 1020187028217 A KR1020187028217 A KR 1020187028217A KR 20187028217 A KR20187028217 A KR 20187028217A KR 20180127379 A KR20180127379 A KR 20180127379A

- Authority

- KR

- South Korea

- Prior art keywords

- load

- address prediction

- address

- prediction table

- processor

- Prior art date

Links

- 238000000034 method Methods 0.000 claims description 39

- 230000004044 response Effects 0.000 claims description 34

- 238000004891 communication Methods 0.000 claims description 8

- 230000001413 cellular effect Effects 0.000 claims description 2

- 230000001052 transient effect Effects 0.000 claims description 2

- 230000003247 decreasing effect Effects 0.000 claims 1

- 239000008188 pellet Substances 0.000 claims 1

- 238000005457 optimization Methods 0.000 description 14

- 238000012545 processing Methods 0.000 description 10

- 238000010586 diagram Methods 0.000 description 5

- 230000001419 dependent effect Effects 0.000 description 4

- 238000013461 design Methods 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 238000012549 training Methods 0.000 description 3

- 238000004590 computer program Methods 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 230000008901 benefit Effects 0.000 description 1

- 238000011010 flushing procedure Methods 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 239000006249 magnetic particle Substances 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 229920001690 polydopamine Polymers 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3802—Instruction prefetching

- G06F9/3804—Instruction prefetching for branches, e.g. hedging, branch folding

- G06F9/3806—Instruction prefetching for branches, e.g. hedging, branch folding using address prediction, e.g. return stack, branch history buffer

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0875—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches with dedicated cache, e.g. instruction or stack

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/3004—Arrangements for executing specific machine instructions to perform operations on memory

- G06F9/30043—LOAD or STORE instructions; Clear instruction

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3824—Operand accessing

- G06F9/383—Operand prefetching

- G06F9/3832—Value prediction for operands; operand history buffers

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3836—Instruction issuing, e.g. dynamic instruction scheduling or out of order instruction execution

- G06F9/3842—Speculative instruction execution

- G06F9/3848—Speculative instruction execution using hybrid branch prediction, e.g. selection between prediction techniques

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/45—Caching of specific data in cache memory

- G06F2212/452—Instruction code

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Software Systems (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Advance Control (AREA)

- Memory System Of A Hierarchy Structure (AREA)

Abstract

발명을 실시하기 위한 구체적인 내용에 개시된 양상들은, 프로세서-기반 시스템들 내의 로드 경로 이력에 기반한 어드레스 예측 테이블들을 사용하여 로드 어드레스 예측들을 제공하는 것을 포함한다. 일 양상에서, 로드 어드레스 예측 엔진은 다수의 로드 어드레스 예측 테이블 엔트리들을 포함하는 로드 어드레스 예측 테이블을 제공한다. 각각의 로드 어드레스 예측 테이블 엔트리는 로드 명령에 대한 예측기 태그 필드 및 메모리 어드레스 필드를 포함한다. 로드 어드레스 예측 엔진은, 검출된 로드 명령에 대한 식별자 및 로드 경로 이력에 기반하여 테이블 인덱스 및 예측기 태그를 생성한다. 테이블 인덱스는 대응하는 로드 어드레스 예측 테이블 엔트리를 룩업하는 데 사용된다. 예측기 태그가 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드와 매칭하면, 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드는 로드 명령에 대한 예측된 메모리 어드레스로서 제공된다.

Description

[0001] 본 출원은, 발명의 명칭이 "PROVIDING LOAD ADDRESS PREDICTIONS USING ADDRESS PREDICTION TABLES BASED ON LOAD PATH HISTORY IN PROCESSOR-BASED SYSTEMS"으로 2016년 3월 31일자로 출원된 미국 특허 출원 시리얼 넘버 제 15/087,069호를 우선권으로 주장하며, 그 특허 출원은 그 전체가 인용에 의해 본 명세서에 포함된다.

[0002] 본 개시내용의 기술은 일반적으로, 프로세서-기반 시스템들에 의한 컴퓨터 프로그램의 실행 동안 로드 명령들의 실행 레이턴시를 개선시키는 것에 관한 것으로, 더 상세하게는 프로세서에서 로드 명령들 및 로드-종속 명령들의 실행을 가속화시키는 것에 관한 것이다.

[0003] 종래의 프로세서들은 모든 각각의 프로세서 클록 사이클 동안 수개의 프로그램 명령들을 페칭(fetch) 및 실행할 수 있다. 프로그램 명령들의 정확한 실행을 보장하기 위해, 프로세서는 프로그램 명령들 사이의 어드레스 및 데이터 종속성들을 모니터링, 검출, 및 충족시키려고 시도한다. 예컨대, 프로세서는, 생산자-소비자 관계가 로드 명령과 후속 저장 명령 사이에 존재한다고 결정할 수 있으며, 따라서, 로드 명령에 의해 생성된 결과가 저장 명령이 실행되게 허용하기 전에 이용가능함을 보장하는 것을 추구할 수 있다.

[0004] 로드 명령들이 프로세서에 의해 실행되는 프로그램 명령들의 총 수의 상당한 부분을 표현할 수 있으므로, 데이터 종속성들의 충족을 보장하는 것은 로드 명령들에 대해 특히 중요하다. 그러나, 로드 명령들에 대한 데이터 종속성들을 충족시키는 것은 그러한 로드 명령들의 실행 레이턴시에 부정적인 영향을 줄 수 있다. 로드 명령이 실행될 수 있는 속도는 종종, 수요가-많은(sought-after) 데이터가 프로세서-기반 시스템의 메모리 계층에(예컨대, 비-제한적인 예들로서, 레벨 1(L1) 캐시, 레벨 2(L2) 캐시, 및/또는 시스템 메모리에) 로케이팅되는 장소에 의존하여 변할 수 있다. 일반적인 원리로서, 데이터가 저장되는 프로세서에 가까울수록, 데이터를 요구하는 로드 명령이 더 신속하게 실행될 수 있다. 결과적으로, 데이터 액세스 시간의 이러한 가변성은 종속적인 로드 명령(즉, 이전의 로드 명령에 의해 생성된 데이터 값을 소비하는 명령)의 실행 레이턴시에 부정적인 영향을 줄 수 있는데, 그 이유는, 이전의 로드 명령이 실행될 때까지 종속적인 로드 명령이 대기해야 하기 때문이다.

[0005] 이러한 데이터 액세스 레이턴시 가변성 때문에, 종래의 프로세서 최적화들은 (예컨대, 데이터 프리페칭(prefetching)을 통해) 로드 명령들의 실행을 가속화시키는 것 및/또는 (예컨대, 데이터 값 예측을 통해) 종속적인 로드 명령들의 실행을 가속화시키는 것에 포커싱되었다. 데이터 프리페칭은, 로드 명령이 더 시기적절한 방식으로 실행될 수 있게 하기 위해, 상위 캐시 레벨(예컨대, L1 캐시)로의 로드 명령에 의해 참조되는 것으로 예상 또는 예측되는 데이터 값을 리트리브하는 것을 수반한다. 데이터 값 예측은, 이전의 로드 명령에 의해 생성될 데이터 값을 예측함으로써 종속적인 로드 명령의 실행을 가속화시키려고 시도하고, 종속적인 로드 명령이 예측된 데이터 값을 사용하여 실행되게 허용하는 기법이다. 로드 명령의 후속 실행 시에, 예측된 데이터 값은 유효한 것으로 확인되거나 또는 잘못 예측된 것으로 부정(disconfirm)될 수 있다. 예측된 데이터 값이 잘못 예측된 것으로 결정되면, 잘못 예측된 데이터 값을 사용하여 명령들을 플러싱(flush)하고 재실행하는 것을 포함하는 복원 액션들이 수행된다.

[0006] 데이터 프리페칭 및/또는 데이터 값 예측 뿐만 아니라 다른 최적화들의 사용이 상당한 성능 이득을 초래할 수 있지만, 그러한 최적화들의 성능을 추가로 개선시키는 메커니즘들을 제공하는 것이 바람직할 수 있다.

[0007] 발명을 실시하기 위한 구체적인 내용에 개시된 양상들은, 프로세서-기반 시스템들 내의 로드 경로 이력에 기반한 어드레스 예측 테이블들을 사용하여 로드 어드레스 예측들을 제공하는 것을 포함한다. 그러한 프로세서-기반 시스템들은 비-제한적인 예로서 수퍼스칼라(superscalar) 프로세서-기반 시스템들을 포함할 수 있다. 이와 관련하여, 예시적인 일 양상에서, 프로세서의 실행 파이프라인의 전단 명령 파이프라인에서 검출된 로드 명령의 타겟일 수 있는 메모리 어드레스를 예측하기 위해 로드 어드레스 예측 엔진이 제공된다. 로드 어드레스 예측 엔진은 복수의 로드 어드레스 예측 테이블 엔트리들을 포함하는 로드 어드레스 예측 테이블을 포함한다. 로드 어드레스 예측 테이블 엔트리들 각각은 검출된 로드 명령에 대응하며, 예측기 태그 필드 및 메모리 어드레스 필드를 포함한다. 로드 명령을 수신할 시에, 로드 어드레스 예측 엔진은, 로드 명령에 대한 식별자(이를테면, 프로그램 카운터) 및 로드 명령에 대한 로드 경로 이력 둘 모두에 기반하여 테이블 인덱스 및 예측기 태그를 생성한다. 테이블 인덱스는 로드 어드레스 예측 테이블 내의 대응하는 로드 어드레스 예측 테이블 엔트리를 룩업(look up)하는 데 사용된다. 예측기 태그가 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드와 매칭하면, 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드는 로드 명령에 대한 예측된 메모리 어드레스로서 제공된다.

[0008] 이러한 방식으로, 로드 어드레스 예측 엔진은 로드 명령들에 대한 메모리 어드레스 예측들을 제공함으로써 프로세서 성능을 개선시킬 수 있다. 몇몇 양상들에서, 예측된 메모리 어드레스는 시스템 데이터 캐시에 액세스하는 데 사용될 수 있다. 캐시 히트(hit)가 시스템 데이터 캐시 상에서 초래되면, 예측된 메모리 어드레스에 대한 데이터 값이 시스템 데이터 캐시로부터 판독되고, 데이터 값 예측을 수행하는 데 사용될 수 있으며, 따라서 개선된 프로세서 성능을 초래한다. 몇몇 양상들은 또한, 예측된 메모리 어드레스가 메모리 명확성을 보조하기 위해 프로세서의 실행 파이프라인의 후단 명령 파이프라인에 제공될 수 있다는 것을 제공할 수 있다. 따라서, 이러한 방식으로, 로드 어드레스 예측 엔진은 종래의 프로세서 최적화들의 효율을 향상시킬 수 있다. 몇몇 양상들은 또한, 로드 어드레스 예측 테이블 내의 각각의 로드 어드레스 예측 테이블 엔트리가 캐시 방식(그 캐시 방식으로, 예측된 메모리 어드레스에 대응하는 메모리 블록이 시스템 데이터 캐시 내에 존재하는 것으로 예상됨)을 표현하는 캐시 방식 표시자를 포함한다는 것을 제공할 수 있다. 캐시 방식 표시자를 제공함으로써, 시스템 데이터 캐시 내의 모든 캐시 방식들에 액세스하는 것을 회피하기 위한 필요성이 회피되며, 따라서 시스템 전력 소비를 감소시킨다.

[0009] 몇몇 양상들에서, 로드 어드레스 예측 테이블 내의 각각의 로드 어드레스 예측 테이블 엔트리는 또한 신뢰도 값 필드를 포함할 수 있다. 신뢰도 값 필드는, 예측된 메모리 어드레스가 대응하는 로드 명령에 대해 정확하다는, 로드 어드레스 예측 엔진에 의해 제공되는 신뢰도 임계치 값 필드에 대한 신뢰도의 레벨을 표현할 수 있다. 예측된 메모리 어드레스가 로드 명령에 대해 정확한 것으로 확인되는 경우, 신뢰도 값 필드가 증분될 수 있다. 예측된 메모리 어드레스가 로드 명령에 대해 부정확한 것으로 결정되면 또는 로드 어드레스 예측 테이블 상의 미스(miss)가 발생하고 로드 명령에 대한 기존의 로드 어드레스 예측 테이블 엔트리에 대한 신뢰도 값이 높다면, 신뢰도 값 필드는 감분될 수 있다.

[0010] 다른 양상에서, 로드 어드레스 예측 엔진이 제공된다. 로드 어드레스 예측 엔진은, 예측기 태그 필드 및 메모리 어드레스 필드를 각각 포함하는 복수의 로드 어드레스 예측 테이블 엔트리들을 저장하도록 구성된 로드 어드레스 예측 테이블을 포함한다. 로드 어드레스 예측 엔진은 로드 명령을 수신하도록 구성된다. 로드 어드레스 예측 엔진은, 로드 명령에 대한 식별자 및 로드 경로 이력 표시자에 기반하여 테이블 인덱스 및 예측기 태그를 생성하도록 추가로 구성된다. 로드 어드레스 예측 엔진은 또한, 복수의 로드 어드레스 예측 테이블 엔트리들 중 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 예측기 태그가 존재하는지 여부를 결정하도록 구성된다. 로드 어드레스 예측 엔진은 부가적으로, 복수의 로드 어드레스 예측 테이블 엔트리들 중 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 예측기 태그가 존재한다고 결정하는 것에 대한 응답으로, 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드로부터의 메모리 어드레스를 로드 명령에 대한 예측된 메모리 어드레스로서 제공하도록 구성된다.

[0011] 다른 양상에서, 프로세서의 로드 어드레스 예측 엔진이 제공된다. 로드 어드레스 예측 엔진은 로드 명령을 수신하기 위한 수단을 포함한다. 로드 어드레스 예측 엔진은, 로드 명령에 대한 식별자 및 로드 경로 이력 표시자에 기반하여 테이블 인덱스 및 예측기 태그를 생성하기 위한 수단을 더 포함한다. 로드 어드레스 예측 엔진은 또한, 로드 어드레스 예측 엔진의 로드 어드레스 예측 테이블의 복수의 로드 어드레스 예측 테이블 엔트리들 중 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 예측기 태그가 존재하는지 여부를 결정하기 위한 수단을 포함한다. 로드 어드레스 예측 엔진은 부가적으로, 로드 어드레스 예측 엔진의 로드 어드레스 예측 테이블의 복수의 로드 어드레스 예측 테이블 엔트리들 중 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 예측기 태그가 존재한다고 결정하는 것에 대한 응답으로, 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드로부터의 메모리 어드레스를 로드 명령에 대한 예측된 메모리 어드레스로서 제공하기 위한 수단을 포함한다.

[0012] 다른 양상에서, 로드 어드레스 예측들을 제공하기 위한 방법이 제공된다. 방법은 프로세서의 로드 어드레스 예측 엔진에 의해 로드 명령을 수신하는 단계를 포함한다. 방법은, 로드 명령에 대한 식별자 및 로드 경로 이력 표시자에 기반하여 테이블 인덱스 및 예측기 태그를 생성하는 단계를 더 포함한다. 방법은 또한, 로드 어드레스 예측 엔진의 로드 어드레스 예측 테이블의 복수의 로드 어드레스 예측 테이블 엔트리들 중 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 예측기 태그가 존재하는지 여부를 결정하는 단계를 포함한다. 방법은 부가적으로, 복수의 로드 어드레스 예측 테이블 엔트리들 중 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 예측기 태그가 존재한다고 결정하는 것에 대한 응답으로, 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드로부터의 메모리 어드레스를 로드 명령에 대한 예측된 메모리 어드레스로서 제공하는 단계를 포함한다.

[0013] 다른 양상에서, 컴퓨터-실행가능 명령들이 저장된 비-일시적인 컴퓨터-판독가능 매체가 제공된다. 프로세서에 의해 실행될 경우, 컴퓨터-실행가능 명령들은 프로세서로 하여금 로드 명령을 수신하게 한다. 컴퓨터-실행가능 명령들은 추가로, 프로세서로 하여금, 로드 명령에 대한 식별자 및 로드 경로 이력 표시자에 기반하여 테이블 인덱스 및 예측기 태그를 생성하게 한다. 컴퓨터-실행가능 명령들은 또한, 프로세서로 하여금, 로드 어드레스 예측 테이블의 복수의 로드 어드레스 예측 테이블 엔트리들 중 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 예측기 태그가 존재하는지 여부를 결정하게 한다. 컴퓨터-실행가능 명령들은 부가적으로, 프로세서로 하여금, 복수의 로드 어드레스 예측 테이블 엔트리들 중 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 예측기 태그가 존재한다고 결정하는 것에 대한 응답으로, 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드로부터의 메모리 어드레스를 로드 명령에 대한 예측된 메모리 어드레스로서 제공하게 한다.

[0014] 도 1은 로드 어드레스 예측들을 제공하기 위한 로드 어드레스 예측 엔진을 포함하는 예시적인 프로세서의 블록 다이어그램이다.

[0015] 도 2는 도 1의 로드 어드레스 예측 엔진의 예시적인 로드 어드레스 예측 테이블의 콘텐츠들을 예시한 블록 다이어그램이다.

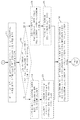

[0016] 도 3a 내지 도 3c는, 인입 로드 명령들을 검출하고, 데이터 값 예측, 데이터 값 프리페칭, 및/또는 메모리 명확성을 가능하게 하기 위한 로드 어드레스 예측들을 제공하기 위한, 도 1의 로드 어드레스 예측 엔진에 대한 예시적인 통신 흐름들을 예시한 다이어그램들이다.

[0017] 도 4a 내지 도 4c는 도 1의 로드 어드레스 예측 엔진에 의해, 인입 로드 명령들을 검출하고 로드 어드레스 예측들을 제공하며, 로드 어드레스 예측 테이블을 트레이닝(train)시키기 위한 예시적인 프로세스를 예시하는 흐름도들이다.

[0018] 도 5는 도 1의 로드 어드레스 예측 엔진을 포함할 수 있는 예시적인 프로세서-기반 시스템의 블록 다이어그램이다.

[0015] 도 2는 도 1의 로드 어드레스 예측 엔진의 예시적인 로드 어드레스 예측 테이블의 콘텐츠들을 예시한 블록 다이어그램이다.

[0016] 도 3a 내지 도 3c는, 인입 로드 명령들을 검출하고, 데이터 값 예측, 데이터 값 프리페칭, 및/또는 메모리 명확성을 가능하게 하기 위한 로드 어드레스 예측들을 제공하기 위한, 도 1의 로드 어드레스 예측 엔진에 대한 예시적인 통신 흐름들을 예시한 다이어그램들이다.

[0017] 도 4a 내지 도 4c는 도 1의 로드 어드레스 예측 엔진에 의해, 인입 로드 명령들을 검출하고 로드 어드레스 예측들을 제공하며, 로드 어드레스 예측 테이블을 트레이닝(train)시키기 위한 예시적인 프로세스를 예시하는 흐름도들이다.

[0018] 도 5는 도 1의 로드 어드레스 예측 엔진을 포함할 수 있는 예시적인 프로세서-기반 시스템의 블록 다이어그램이다.

[0019] 이제 도면의 도들을 참조하여, 본 개시내용의 수 개의 예시적인 양상들이 설명된다. 단어 "예시적인"은 "예, 예시, 또는 예증으로서 기능하는 것"을 의미하도록 본 명세서에서 사용된다. "예시적인" 것으로서 본 명세서에 설명된 임의의 양상은 다른 양상들에 비해 반드시 바람직하거나 유리한 것으로서 해석되는 것은 아니다.

[0020] 발명을 실시하기 위한 구체적인 내용에 개시된 양상들은, 프로세서-기반 시스템들 내의 로드 경로 이력에 기반한 어드레스 예측 테이블들을 사용하여 로드 어드레스 예측들을 제공하는 것을 포함한다. 프로세서의 실행 파이프라인의 전단 명령 파이프라인에서 검출된 주어진 로드 명령에 의해 참조될 수 있는 메모리 어드레스를 예측하기 위해 로드 어드레스 예측 엔진이 제공된다. 테이블 인덱스 및 예측기 태그는, 로드 명령에 대한 식별자(이를테면, 프로그램 카운터) 및 로드 명령에 대한 로드 경로 이력 둘 모두에 기반하여 로드 어드레스 예측 엔진에 의해 생성된다. 그 후, 로드 어드레스 예측 엔진은, 로드 어드레스 예측 테이블 내의 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리가 예측기 태그를 포함하는지 여부를 결정한다. 포함한다면, 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드는 로드 명령에 대한 예측된 메모리 어드레스로서 제공된다. 아래에서 더 상세히 논의되는 바와 같이, 로드 명령에 대한 예측된 메모리 어드레스는 데이터 값 예측, 데이터 값 프리페칭, 및 메모리 명확성과 같은 프로세서 최적화들의 효율을 향상시키기 위해 이용될 수 있다. 몇몇 양상들은, 로드 어드레스 예측 테이블의 로드 어드레스 예측 테이블 엔트리들 내의 신뢰도 값 필드를 사용하여 추가적인 성능 최적화들을 제공할 수 있다. 몇몇 양상들에서, 로드 어드레스 예측 테이블의 로드 어드레스 예측 테이블 엔트리들에서의 선택적인 캐시 방식 필드의 사용을 통해 전력 최적화들이 또한 실현될 수 있다.

[0021] 이와 관련하여, 도 1은 본 명세서에 개시된 바와 같이, 로드 어드레스 예측들을 제공하는 로드 어드레스 예측 엔진(102)을 포함하는 예시적인 프로세서(100)의 블록 다이어그램이다. 프로세서(100)는, 시스템 메모리(106)가 액세스될 수 있게 하는 메모리 인터페이스(104)를 포함한다. 몇몇 양상들에서, 시스템 메모리(106)는 비-제한적인 예로서 더블-레이트 동적 랜덤 액세스 메모리(DRAM)(DDR)를 포함할 수 있다. 프로세서(100)는 명령 캐시(108), 및 시스템 데이터 캐시(110)를 더 포함한다. 몇몇 양상들에서, 시스템 데이터 캐시(110)는 레벨 1(L1) 데이터 캐시를 포함할 수 있다. 프로세서(100)는 다른 엘리먼트들 중에서, 알려진 디지털 로직 엘리먼트들, 반도체 회로들, 프로세싱 코어들, 및/또는 메모리 구조들 중 임의의 하나, 또는 이들의 조합을 포함할 수 있다. 본 명세서에 설명된 양상들은 엘리먼트들의 임의의 특정 어레인지먼트로 제한되지 않으며, 개시된 기법들은 반도체 다이들 또는 패키지들 상의 다양한 구조들 및 레이아웃들로 용이하게 확장될 수 있다.

[0022] 프로세서(100)는, 전단 명령 파이프라인(114) 및 후단 명령 파이프라인(116)으로 세분될 수 있는 실행 파이프라인(112)을 더 포함한다. 본 명세서에서 사용되는 바와 같이, "전단 명령 파이프라인(114)"은 실행 파이프라인(112)의 "시작부"에 전통적으로 로케이팅되고 페칭, 디코딩, 및/또는 명령 큐잉 기능을 제공하는 파이프라인 스테이지들을 지칭할 수 있다. 이와 관련하여, 도 1의 전단 명령 파이프라인(114)은 하나 또는 그 초과의 페치/디코드 파이프라인 스테이지들(118) 및 하나 또는 그 초과의 명령 큐 스테이지들(120)을 포함한다. 비-제한적인 예들로서, 하나 또는 그 초과의 페치/디코드 파이프라인 스테이지들(118)은 F1, F2, 및/또는 F3 페치/디코드 스테이지들(미도시)을 포함할 수 있다. "후단 명령 파이프라인(116)"은 본 명세서에서, 실행을 위해 명령들을 발행하고, 명령들의 실제 실행을 수행하며, 그리고/또는 명령 실행에 의해 요구되거나 또는 생성되는 데이터를 로딩 및/또는 저장하기 위한 실행 파이프라인(112)의 후속 파이프라인 스테이지들을 지칭한다. 도 1의 예에서, 후단 명령 파이프라인(116)은 개명(rename) 스테이지(122), 레지스터 액세스 스테이지(124), 예비 스테이지(126), 하나 또는 그 초과의 디스패치(dispatch) 스테이지들(128), 및 하나 또는 그 초과의 실행 스테이지들(130)을 포함한다. 도 1에 도시된 전단 명령 파이프라인(114)의 스테이지들(118, 120) 및 후단 명령 파이프라인(116)의 스테이지들(122, 124, 126, 128, 130)이 예시의 목적들을 위해서만 제공되며, 프로세서(100)의 다른 양상들이 본 명세서에 예시된 것보다 더 적은 또는 부가적인 파이프라인 스테이지들을 포함할 수 있다는 것이 이해될 것이다.

[0023] 프로세서(100)는 부가적으로, 복수의 레지스터들(134(0) 내지 134(X))에 대한 물리적 저장소를 제공하는 레지스터 파일(132)을 포함한다. 몇몇 양상들에서, 레지스터들(134(0) 내지 134(X))은 하나 또는 그 초과의 범용 레지스터(GPR)들, 프로그램 카운터(미도시), 및/또는 링크 레지스터(미도시)를 포함할 수 있다. 프로세서(100)에 의한 컴퓨터 프로그램들의 실행 동안, 레지스터들(134(0) 내지 134(X))은 레지스터 맵 테이블(138)을 사용하여 하나 또는 그 초과의 아키텍처 레지스터들(136)에 맵핑될 수 있다.

[0024] 예시적인 동작에서, 실행 파이프라인(112)의 전단 명령 파이프라인(114)은 명령 캐시(108)로부터 프로그램 명령들(미도시)을 페칭한다. 프로그램 명령들은, 전단 명령 파이프라인(114)의 하나 또는 그 초과의 페치/디코드 파이프라인 스테이지들(118)에 의해 추가로 디코딩되며, 후단 명령 파이프라인(116)으로의 발행을 기다리는 하나 또는 그 초과의 명령 큐 스테이지들(120)로 전달될 수 있다. 프로그램 명령들이 후단 명령 파이프라인(116)으로 발행된 이후, 후단 명령 파이프라인(116)의 스테이지들(예컨대, 실행 스테이지(들)(130))은 이어서, 발행된 프로그램 명령들을 실행하고, 실행된 프로그램 명령들을 폐기한다.

[0025] 위에서 언급된 바와 같이, 프로세서(100)의 하나의 중요한 기능은, 프로그램 명령들, 특히 로드 명령들 사이의 데이터 종속성들의 충족을 보장함으로써 위험을 방지하는 것이다. 로드 명령들에 대한 데이터 액세스 시간들의 변동들이 그러한 로드 명령들의 실행 레이턴시에 부정적인 영향을 줄 수 있기 때문에, 종래의 프로세서들은 로드 명령들의 실행을 가속화시키기 위해 데이터 프리페칭, 데이터 값 예측, 및 메모리 명확성과 같은 최적화들을 제공했다. 그러나, 이들 최적화들을 추가로 개선시킬 수 있는 부가적인 메커니즘들을 제공하는 것이 바람직할 수 있다.

[0026] 이와 관련하여, 프로세서(100)는 로드 명령들에 대한 로드 어드레스 예측들을 제공하기 위한 로드 어드레스 예측 엔진(102)을 포함한다. 로드 어드레스 예측 엔진(102)이 명확화를 위해 전단 명령 파이프라인(114) 및 후단 명령 파이프라인(116)과 별개인 엘리먼트로서 예시되지만, 로드 어드레스 예측 엔진(102)이 전단 명령 파이프라인(114)의 스테이지들(118, 120) 중 하나 또는 그 초과 및/또는 후단 명령 파이프라인(116)의 스테이지들(122, 124, 126, 128, 130) 중 하나 또는 그 초과에 통합될 수 있다는 것이 이해될 것이다. 로드 어드레스 예측 엔진(102)은, 검출된 로드 명령들의 타겟일 수 있는 예측된 메모리 어드레스들을 저장하기 위한 하나 또는 그 초과의 로드 어드레스 예측 테이블 엔트리들(미도시)을 포함하는 로드 어드레스 예측 테이블(140)을 포함한다. 화살표들(142 및 144)에 의해 표시된 바와 같이, 로드 어드레스 예측 엔진(102)은 실행 파이프라인(112)의 전단 명령 파이프라인(114) 및 후단 명령 파이프라인(116) 각각에 통신가능하게 커플링된다. 유사하게, 로드 어드레스 예측 엔진(102)은 양방향 화살표(146)에 의해 표시된 바와 같이, 시스템 데이터 캐시(110)에 통신가능하게 커플링된다.

[0027] 예시적인 동작에서, 로드 어드레스 예측 엔진(102)은 전단 명령 파이프라인(114)으로부터 인입 로드 명령(미도시)을 수신한다. 로드 어드레스 예측 엔진(102)은 로드 명령에 대한 식별자(예컨대, 프로그램 카운터)에 기반하여 테이블 인덱스(미도시) 및 예측기 태그(미도시)를 생성한다. 로드 명령에 대한 테이블 인덱스 및 예측기 태그는, 현재의 로드 명령으로 유도되었던 로드 명령들의 이전의 시퀀스를 표현하는 로드 경로 이력에 또한 기반한다. 로드 명령에 대한 테이블 인덱스 및 예측기 태그에 로드 경로 이력을 통합시키는 것은 로드 명령에 대한 부가적인 이력 콘텍스트를 제공하며, 이는, 주어진 로드 명령에 대해 생성된 더 고유한 값들을 초래할 수 있다. 비-제한적인 예로서, 몇몇 양상들에서, 로드 경로 이력은, 로드 명령에 선행하는 최근의 명령들(예컨대, 하나 또는 그 초과의 가장 최근의 분기(branch) 명령들)의 프로그램 카운터들의 복수의 비트들과 함께, 로드 명령 그 자체의 프로그램 카운터의 복수의 하위 비트들의 해시(hash)를 생성함으로써 테이블 인덱스 및 예측기 태그에 통합될 수 있다. 그 후, 테이블 인덱스 및 예측기 태그는 결과적인 해시 값으로부터 도출될 수 있다.

[0028] 테이블 인덱스는 로드 어드레스 예측 테이블(140) 내의 로드 액세스 예측 테이블 엔트리에 액세스하기 위하여 로드 어드레스 예측 엔진(102)에 의해 사용된다. 그 후, 로드 어드레스 예측 엔진(102)에 의해 생성된 예측기 태그는 테이블 인덱스에 대응하는 로드 액세스 예측 테이블 엔트리의 예측기 태그 값의 콘텐츠와 비교된다. 예측기 태그가 로드 어드레스 예측 테이블 엔트리의 예측기 태그 값과 매칭하면, 메모리 어드레스 값(미도시)은 로드 어드레스 예측 테이블 엔트리로부터 판독되고, 로드 명령에 대한 예측된 메모리 어드레스로서 로드 어드레스 예측 엔진(102)에 의해 제공된다. 그 후, 예측된 메모리 어드레스는, 비-제한적인 예들로서 데이터 값 예측, 데이터 프리페칭, 및/또는 메모리 명확성과 같은 로드 명령 최적화들을 용이하게 하기 위해 사용될 수 있다. 로드 명령 최적화들을 용이하게 할 시에 로드 어드레스 예측 엔진(102)의 예시적인 양상들의 동작들은 도 3a 내지 도 3c에 대해 아래에서 더 상세히 논의된다.

[0029] 몇몇 양상들에서, 도 1의 로드 어드레스 예측 테이블(140)에 대응할 수 있는 예시적인 로드 어드레스 예측 테이블(200)을 예시하기 위해, 도 2가 제공된다. 도 1의 엘리먼트들은 도 2를 설명할 시에 명확화를 위해 참조된다. 도 2에서 보여지는 바와 같이, 로드 어드레스 예측 엔진(102)은 다수의 로드 어드레스 예측 테이블 엔트리들(202(0) 내지 202(Y))을 포함하는 로드 어드레스 예측 테이블(200)을 제공한다. 로드 어드레스 예측 테이블 엔트리들(202(0) 내지 202(Y)) 각각은 도 1의 전단 명령 파이프라인(114)에서 로드 어드레스 예측 엔진(102)에 의해 검출된 로드 명령(미도시)과 연관될 수 있다. 몇몇 양상들에 따르면, 로드 어드레스 예측 테이블 엔트리들(202(0) 내지 202(Y))에 대한 임의의 에일리어싱 문제들을 제거 또는 감소시키기 위해, 로드 어드레스 예측 테이블(200)은 직접-맵핑 태깅 테이블(direct-mapped tagged table)을 포함할 수 있다.

[0030] 로드 어드레스 예측 테이블 엔트리들(202(0) 내지 202(Y)) 각각은, 로드 어드레스 예측 엔진(102)에 의해 대응하는 로드 명령에 대하여 생성된 예측기 태그(미도시)를 저장하는 예측기 태그 필드(204)를 포함한다. 위에서 언급된 바와 같이, 각각의 예측기 태그 필드(204)의 콘텐츠들은, 로드 명령에 대한 로드 경로 이력과 조합된 로드 명령에 대한 식별자(이를테면, PC)에 기반하여 로드 어드레스 예측 엔진(102)에 의해 생성될 수 있다. 몇몇 양상들에서, 예측기 태그는 대응하는 로드 명령에 대한 추가적인 이력 콘텍스트를 제공하기 위해 분기 방향 이력(미도시) 및/또는 분기 경로 이력(미도시)을 추가로 통합할 수 있다.

[0031] 각각의 로드 어드레스 예측 테이블 엔트리들(202(0) 내지 202(Y))은 또한 메모리 어드레스 필드(206)를 포함한다. 메모리 어드레스 필드(206)는 로드 어드레스 예측 테이블(200)의 트레이닝 동안 채워지며(populate), 로드 어드레스 예측 테이블 엔트리들(202(0) 내지 202(Y))에 대응하는 로드 명령에 의해 이전에 참조되었던 메모리 어드레스를 표현한다. 로드 어드레스 예측 테이블(200)에서의 히트 시에, 메모리 어드레스 필드(206)의 콘텐츠들은 데이터 값 예측, 데이터 값 프리페칭, 및/또는 메모리 명확성 최적화 절차들을 위해 로드 명령에 대한 예측된 메모리 어드레스로서 로드 어드레스 예측 엔진(102)에 의해 제공될 수 있다.

[0032] 추가적인 성능 최적화들을 제공하기 위해, 몇몇 양상들에서, 로드 어드레스 예측 테이블(200)의 로드 어드레스 예측 테이블 엔트리들(202(0) 내지 202(Y)) 각각은 신뢰도 값 필드(208)를 또한 제공할 수 있다. 로드 어드레스 예측 엔진(102)은 최소의 신뢰도 임계치를 표시하도록 미리 셋팅된 신뢰도 임계치 값 필드(210)를 추가로 제공할 수 있다. 로드 어드레스 예측 테이블 엔트리들(202(0) 내지 202(Y)) 각각에 대한 신뢰도 값 필드(208)는, 로드 어드레스 예측 테이블 엔트리(202(0) 내지 202(Y))가 로드 어드레스 예측에 충분히 신뢰가능한 것으로 고려될 수 있는지를 결정하기 위해 신뢰도 임계치 값 필드(210)와 비교될 수 있다. 이러한 방식으로, 신뢰도 값 필드(208)는 신뢰도 임계치 값 필드(210)와 함께, 로드 명령에 대한 예측된 메모리 어드레스에서 신뢰도 레벨을 표시하기 위한 포화 카운터로서 사용될 수 있다. 비-제한적인 예로서, 로드 어드레스 예측 테이블 엔트리들(202(0) 내지 202(Y)) 중 하나, 이를테면 로드 어드레스 예측 테이블 엔트리(202(0))의 초기화 시에, 신뢰도 값 필드(208)는 제로(0)로 셋팅될 수 있다. 후속하는 히트들 시에, 신뢰도 값 필드(208)가 증분될 수 있지만, 메모리 어드레스 필드(206)에 의해 표시된 예측된 메모리 어드레스는, 신뢰도 값 필드(208)가 신뢰도 임계치 값 필드(210)를 초과할 때까지 제공되지 않을 수 있다. 반대로, 예측된 메모리 어드레스가 로드 명령에 대해 제공되지만, 후속하여, 잘못 예측된 것으로 결정되면, 신뢰도 값 필드(208)는 감분되거나 또는 제로(0)로 리셋될 수 있다.

[0033] 로드 어드레스 예측 테이블(200)의 몇몇 양상들은 로드 어드레스 예측 테이블 엔트리들(202(0) 내지 202(Y)) 각각에 선택적인 캐시 방식 필드(212)를 포함시킴으로써 부가적인 전력 최적화들을 제공할 수 있다. 캐시 방식 필드(212)는, 메모리 어드레스 필드(206)에 대응하는 데이터가 로케이팅되는 시스템 데이터 캐시(110) 내의 방식을 표시할 수 있다. 메모리 어드레스 필드(206)로부터의 예측된 메모리 어드레스가 데이터 값 예측을 위해 사용되는 이벤트에서, 캐시 방식 필드(212)는, 시스템 데이터 캐시(110) 내에서 판독될 다수의 세트들을 요구하기보다는, 시스템 데이터 캐시(110) 내의 특정 방식으로부터, 예측된 메모리 어드레스에 대한 데이터를 더 효율적으로 리트리브하기 위해 제공될 수 있다.

[0034] 로드 어드레스 예측 테이블(200)의 로드 어드레스 예측 테이블 엔트리들(202(0) 내지 202(Y))이 도 2에 예시된 필드들(204, 206, 208, 및 212)에 부가하여 다른 필드들을 포함할 수 있다는 것을 몇몇 양상들이 제공할 수 있다는 것이 이해될 것이다. 몇몇 양상들에서, 로드 어드레스 예측 테이블(200)이 당업계에 알려진 연관성(associativity) 및 교체 정책들에 따라 구성되는 캐시로서 구현될 수 있다는 것이 추가로 이해될 것이다. 도 2의 예에서, 로드 어드레스 예측 테이블(200)은 단일 데이터 구조로서 예시된다. 그러나, 몇몇 양상들에서, 로드 어드레스 예측 테이블(200)은 또한 1개 초과의 데이터 구조 또는 캐시를 포함할 수 있다.

[0035] 인입 로드 명령들을 검출하고 로드 어드레스 예측들을 제공하기 위한 도 1의 로드 어드레스 예측 엔진(102)에 대한 예시적인 통신 흐름들을 예시하기 위해, 도 3a 내지 도 3c가 제공된다. 도 3a는 로드 명령을 검출하고, 로드 명령에 대한 테이블 인덱스 및 예측기 태그를 생성하기 위한 예시적인 통신 흐름들을 예시한다. 도 3b는 도 1의 로드 어드레스 예측 테이블(140)의 룩업을 수행하고 로드 어드레스 예측 테이블(140)에서의 히트에 기반하여 데이터 값 예측을 제공하기 위한 예시적인 통신 흐름들을 예시한다. 도 3c는 시스템 데이터 캐시(110)에서의 미스에 기반하여 데이터 값 프리페치를 수행하고, 그리고/또는 메모리 명확성을 위해, 예측된 메모리 어드레스를 제공하는 예시적인 통신 흐름들을 예시한다. 예시의 목적들을 위해, 도 4c에 대해 아래에서 더 상세히 설명되는 바와 같이, 도 3a 내지 도 3c의 로드 어드레스 예측 테이블(140)이 이미 트레이닝을 경험했다고 가정되는 것이 이해될 것이다. 명확화를 위해, 도 1 및 도 2의 엘리먼트들이 도 3a 내지 도 3c를 설명할 시에 참조된다.

[0036] 도 3a에서, 로드 어드레스 예측 엔진(102)은 화살표(302)에 의해 표시된 바와 같이, 전단 명령 파이프라인(114)으로부터 로드 명령(300)을 수신한다. 로드 명령(300)은, 비-제한적인 예로서 프로그램 카운터를 포함할 수 있는 식별자(304)를 포함한다. 로드 명령(300)은 또한, 명령(300)이 액세스하기로 의도하는 어드레스로서 계산될 메모리 어드레스인 "실제 메모리 어드레스(306)"로 지칭되는 참조를 포함한다. 실제 메모리 어드레스(306)가 실행 파이프라인(112)에서 훨씬 더 늦게까지 명확하게 결정될 수 없기 때문에, 로드 어드레스 예측 엔진(102)은 시스템 성능 및 전력 소비를 최적화하려는 시도 시에, 예측된 메모리 어드레스(미도시)를 생성하기 위해 사용된다.

[0037] 로드 명령(300)을 수신한 이후, 로드 어드레스 예측 엔진(102)은 테이블 인덱스(308) 및 예측기 태그(310)를 생성한다. 로드 어드레스 예측 엔진(102)은 화살표들(314, 316) 및 화살표들(318, 320)에 의해 표시된 바와 같이, 테이블 인덱스(308) 및 예측기 태그(310)를 로드 명령(300)의 로드 경로 이력(312) 및 식별자(304)에 기반하게 한다. 몇몇 양상들에서, 부가적인 이력 콘텍스트는, (화살표들(324 및 326)에 의해 표시된 바와 같은) 분기 방향 이력(322) 및/또는 (화살표들(330 및 332)에 의해 표시된 바와 같은) 분기 경로 이력(328)의 사용을 통해 테이블 인덱스(308) 및 예측기 태그(310)에 통합될 수 있다. 일단 테이블 인덱스(308) 및 예측기 태그(310)가 생성되었다면, 동작들은 도 3b로 계속된다.

[0038] 도 3b에서, 로드 어드레스 예측 엔진(102)은 화살표(334)에 의해 표시된 바와 같이, 로드 어드레스 예측 테이블(140)로의 인덱스로서 테이블 인덱스(308)를 사용한다. 이러한 예에서, 테이블 인덱스(308)는 로드 어드레스 예측 테이블 엔트리(202(0))에 대응한다. 그 후, 로드 어드레스 예측 엔진(102)은 화살표(336)에 의해 표시된 바와 같이, 로드 어드레스 예측 테이블 엔트리(202(0))의 예측기 태그 필드(204)의 콘텐츠들과 예측기 태그(310)를 비교한다. 예측기 태그(310)가 예측기 태그 필드(204)의 콘텐츠들과 매칭하지 않으면(즉, 로드 어드레스 예측 테이블(140) 상의 미스), 로드 어드레스 예측 테이블(140)은 로드 명령(300)에 대한 예측된 메모리 어드레스를 포함하지 않으며, 로드 명령(300)의 프로세싱은 종래대로 진행한다. 도 4c에 대해 아래에서 설명되는 바와 같이, 로드 명령(300)의 실행 이후, 로드 어드레스 예측 테이블(140)은 로드 명령(300)을 실행한 결과들에 기반하여 업데이트될 수 있다.

[0039] 예측기 태그(310)가 예측기 태그 필드(204)의 콘텐츠들과 매칭하지 않으면, 로드 어드레스 예측 엔진(102)은, 로드 명령(300)에 대한 예측된 메모리 어드레스(338)를 제공하기 위해 로드 어드레스 예측 테이블 엔트리(202(0))의 메모리 어드레스 필드(206)를 사용한다. 위에서 언급된 바와 같이, 로드 어드레스 예측 테이블(140)이 신뢰도 임계치 값 필드(210)와 함께 신뢰도 값 필드(208)를 이용하는 양상들에서, 신뢰도 값 필드(208)가 신뢰도 임계치 값 필드(210)를 초과하는 경우에만, 로드 어드레스 예측 엔진(102)은 예측된 메모리 어드레스(338)를 제공할 수 있다.

[0040] 몇몇 양상들에서, 예측된 메모리 어드레스(338)는 화살표(340)에 의해 표시된 바와 같이, 예측된 메모리 어드레스(338)에 대한 데이터가 시스템 데이터 캐시(110)에 존재하는지 여부를 결정하기 위해 사용될 수 있다. 예측된 메모리 어드레스(338)에 대한 시스템 데이터 캐시(110) 상에서 히트가 발생하면, 예측된 메모리 어드레스(338)에 대응하는 리트리브된 데이터(342)가 시스템 데이터 캐시(110)로부터 판독된다. 리트리브된 데이터(342)는 화살표(344)에 의해 표시된 바와 같이, 데이터 값 예측으로서 전단 명령 파이프라인(114)에 제공된다.

[0041] 이제 도 3c를 참조하면, 예측된 메모리 어드레스(338)에 대한 시스템 데이터 캐시(110)에서 미스가 발생하면, 로드 어드레스 예측 엔진(102)은 예측된 메모리 어드레스(338)에 대한 데이터 값 프리페치를 용이하게 할 수 있다. 이를 행하기 위해, 예측된 메모리 어드레스(338)에 대응하는 프리페치 데이터(346)가 화살표(348)에 의해 표시된 바와 같이 시스템 메모리(106)로부터 판독될 수 있다. 그 후, 프리페치 데이터(346)는 화살표들(350 및 352)에 의해 표시된 바와 같이, 예측된 메모리 어드레스(338)와 함께 시스템 데이터 캐시(110)에 저장된다. 이러한 방식으로, 프리페치 데이터(346)는, 시스템 데이터 캐시(110)의 예측된 메모리 어드레스(338) 상의 미래의 히트의 이벤트 시에 시스템 데이터 캐시(110)에서 이용가능할 수 있다.

[0042] 몇몇 양상들에서, 예측된 메모리 어드레스(338)는 또한, 메모리 명확성을 개선시키기 위해 기존의 메커니즘들과 함께 사용되도록 후단 명령 파이프라인(116)에 제공될 수 있다. 메모리 명확성에서, 로드 명령(300)과 같은 로드 명령의 계산된 어드레스는 더 오래된 저장 명령들(미도시)의 계산된 어드레스들에 대해 체크된다. 로드 명령(300)의 어드레스가 이전의 저장 명령의 어드레스와 매칭하면, 로드 명령(300)은, 시스템 데이터 캐시(110)를 프로빙(probe)하는 것 대신, 사용에 대해 이용가능하게 될 저장 명령의 데이터를 대기해야 한다. 로드 어드레스 예측 테이블(140)이 로드 명령(300)의 어드레스들을 사용하여 트레이닝될 때, 그것은, 로드 또는 저장 어드레스가 계산되기 전에 로드 또는 저장 어드레스를 예측하는 것을 돕기 위해 사용될 수 있다. 이것은 차례로, 로드 명령들의 더 효율적인 실행을 가능하게 할 수 있다.

[0043] 도 4a 내지 도 4c는 인입 로드 명령들을 검출하고 로드 어드레스 예측들을 제공하며, 도 1의 로드 어드레스 예측 엔진(102)에 의해 로드 어드레스 예측 테이블(140)을 트레이닝시키기 위한 예시적인 프로세스를 예시하는 흐름도들이다. 명확화를 위해, 도 1, 도 2 , 및 도 3a 내지 도 3c 의 엘리먼트들이 도 4a 내지 도 4c를 설명할 시에 참조된다. 동작들은 도 4a에서, 프로세서(100)의 로드 어드레스 예측 엔진(102)이 (예컨대, 프로세서(100)의 실행 파이프라인(112)의 전단 명령 파이프라인(114)으로부터) 로드 명령(300)을 수신하는 것으로 시작한다(블록(400)). 이와 관련하여, 로드 어드레스 예측 엔진(102)은 "로드 명령을 수신하기 위한 수단"으로 본 명세서에서 지칭될 수 있다. 로드 어드레스 예측 엔진(102)은 로드 명령(300)에 대한 식별자(304) 및 로드 경로 이력(312)에 기반하여 테이블 인덱스(308) 및 예측기 태그(310)를 생성한다(블록(402)). 따라서, 로드 어드레스 예측 엔진(102)은, "로드 명령에 대한 식별자 및 로드 경로 이력 표시자에 기반하여 테이블 인덱스 및 예측기 태그를 생성하기 위한 수단"으로 본 명세서에서 지칭될 수 있다. 몇몇 양상들에서, 테이블 인덱스(308) 및 예측기 태그(310)를 생성하기 위한 블록(402)의 동작들은, 로드 명령(300)의 분기 방향 이력(322) 및/또는 분기 경로 이력(328)에 추가로 기반할 수 있다(블록(404)).

[0044] 그 후, 로드 어드레스 예측 엔진(102)은, 로드 어드레스 예측 엔진(102)의 로드 어드레스 예측 테이블(140)의 복수의 로드 어드레스 예측 테이블 엔트리들(202(0) 내지 202(Y)) 중 테이블 인덱스(308)에 대응하는 로드 어드레스 예측 테이블 엔트리(202(0))의 예측기 태그 필드(204)에 예측기 태그(310)가 존재하는지 여부를 결정한다(블록(406)). 따라서, 로드 어드레스 예측 엔진(102)은, "로드 어드레스 예측 엔진의 로드 어드레스 예측 테이블의 복수의 로드 어드레스 예측 테이블 엔트리들 중 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 예측기 태그가 존재하는지 여부를 결정하기 위한 수단"으로 본 명세서에서 지칭될 수 있다. 테이블 인덱스(308)에 대응하는 로드 어드레스 예측 테이블 엔트리(202(0))의 예측기 태그 필드(204)에 예측기 태그(310)가 존재하지 않으면, 로드 명령(300)의 프로세싱은 계속된다(블록(408)). 그 후, 프로세싱은 도 4c의 블록(410)에서 재개된다.

[0045] 그러나, 테이블 인덱스(308)에 대응하는 로드 어드레스 예측 테이블 엔트리(202(0))의 예측기 태그 필드(204)에 예측기 태그(310)가 존재한다고 로드 어드레스 예측 엔진(102)이 판단 블록(406)에서 결정하면, 몇몇 양상들에서, 로드 어드레스 예측 엔진(102)은, 로드 어드레스 예측 테이블 엔트리(202(0))의 신뢰도 값 필드(208)가 로드 어드레스 예측 엔진(102)의 신뢰도 임계치 값 필드(210)를 초과하는지 여부를 추가로 결정할 수 있다(블록(412)). 초과한다면(또는 로드 어드레스 예측 엔진(102)의 양상이 신뢰도 값 필드(208) 및 신뢰도 임계치 값 필드(210)를 이용하지 않는다면), 프로세싱은 도 4b의 블록(414)에서 재개된다. 신뢰도 값 필드(208)가 신뢰도 임계치 값 필드(210)를 초과하지 않는다고 로드 어드레스 예측 엔진(102)이 블록(412)에서 결정하면, 로드 명령(300)의 프로세싱은 계속된다(블록(408)). 그 후, 프로세싱은 도 4c의 블록(410)에서 재개된다.

[0046] 이제 도 4b를 참조하면, 로드 어드레스 예측 엔진(102)은 로드 어드레스 예측 테이블 엔트리(202(0))의 메모리 어드레스 필드(206)로부터의 예측된 메모리 어드레스(338)를 로드 명령(300)에 대한 예측된 메모리 어드레스(338)로서 제공한다(블록(414)). 이와 관련하여, 로드 어드레스 예측 엔진(102)은, "로드 어드레스 예측 엔진의 로드 어드레스 예측 테이블의 복수의 로드 어드레스 예측 테이블 엔트리들 중 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 예측기 태그가 존재한다고 결정하는 것에 대한 응답으로, 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드로부터의 메모리 어드레스를 로드 명령에 대한 예측된 메모리 어드레스로서 제공하기 위한 수단"으로 본 명세서에서 지칭될 수 있다. 몇몇 양상들은, 로드 명령(300)에 대한 예측된 메모리 어드레스(338)가 프로세서(100)의 시스템 데이터 캐시(110)에 존재하는지 여부를 로드 어드레스 예측 엔진(102)이 다음으로 결정하는 것을 제공할 수 있다(블록(416)). 로드 어드레스 예측 테이블 엔트리(202(0))가 선택적인 캐시 방식 필드(212)를 포함하는 양상들에서, 판단 블록(416)에서 행해진 결정은 테이블 인덱스(308)에 대응하는 로드 어드레스 예측 테이블 엔트리(202(0))의 캐시 방식 필드(212)에 부분적으로 기반할 수 있다. 예측된 메모리 어드레스(338)가 시스템 데이터 캐시(110)에 존재한다면, 로드 어드레스 예측 엔진(102)은 시스템 데이터 캐시(110)로부터, 예측된 메모리 어드레스(338)에 대한 데이터(342)를 리트리브한다(블록(418)). 그 후, 리트리브된 데이터(342)는 데이터 값 예측으로서 프로세서(100)의 실행 파이프라인(112)의 후단 명령 파이프라인(116)에 제공된다(블록(420)). 그 후, 프로세싱은 도 4b의 블록(422)에서 재개될 수 있다.

[0047] 로드 명령(300)에 대한 예측된 메모리 어드레스(338)가 프로세서(100)의 시스템 데이터 캐시(110)에 존재하지 않는다고 로드 어드레스 예측 엔진(102)이 도 4b의 판단 블록(416)에서 결정하면, 로드 어드레스 예측 엔진(102)은 프로세서(100)의 시스템 메모리(106)로부터, 예측된 메모리 어드레스(338)에 대응하는 데이터(346)를 프리페칭할 수 있다(블록(424)). 그 후, 프리페칭된 데이터(346)는 프로세서(100)의 시스템 데이터 캐시(110)에 저장된다(블록(426)). 그 후, 프로세싱은 도 4b의 블록(422)에서 재개된다.

[0048] 도 4b를 계속 참조하면, 몇몇 양상들에서, 로드 어드레스 예측 엔진(102)은 또한, 메모리 명확성을 위해, 로드 명령(300)에 대한 예측된 메모리 어드레스(338)로서 로드 어드레스 예측 테이블 엔트리(202(0))의 메모리 어드레스 필드(206)의 메모리 어드레스(338)를 프로세서(100)의 실행 파이프라인(112)의 후단 명령 파이프라인(116)에 제공할 수 있다(블록(422)). 그 후, 프로세싱은 도 4c의 블록(410)에서 계속된다.

[0049] 이제 도 4c를 참조하면, 로드 어드레스 예측 엔진(102)은, 로드 명령(300)의 실행 이후 로드 어드레스 예측 테이블(140)을 트레이닝시키기 위한 동작들을 수행한다. 로드 어드레스 예측 엔진(102)은 먼저, 로드 명령(300)의 실행에 후속하여, 복수의 로드 어드레스 예측 테이블 엔트리들(202(0) 내지 202(Y)) 중 테이블 인덱스(308)에 대응하는 로드 어드레스 예측 테이블 엔트리(202(0))의 예측기 태그 필드(204)에 예측기 태그(310)가 존재하는지 여부를 결정한다(블록(410)). 존재한다면, 로드 어드레스 예측 테이블 엔트리(202(0))는 로드 명령(300)에 대해 존재하며, 로드 명령(300)의 실행의 결과들에 기반하여 업데이트되어야 한다.

[0050] 그에 따라서, 로드 어드레스 예측 엔진(102)은 다음으로, 로드 명령(300)의 실제 메모리 어드레스(306)(즉, 계산된 어드레스)가 로드 명령(300)에 대한 예측된 메모리 어드레스(338)와 매칭하는지 여부를 결정한다(블록(428)). 몇몇 양상들에서, 로드 어드레스 예측 엔진(102)은 또한, 실제 메모리 어드레스(306)의 방식을 캐시 방식 필드(212)와 비교할 수 있다. 실제 메모리 어드레스(306)가 예측된 메모리 어드레스(338)와 매칭하면(그리고 선택적으로는, 캐시 방식 필드(212)가 정확하면), 로드 어드레스 예측 엔진(102)은 테이블 인덱스(308)에 대응하는 로드 어드레스 예측 테이블 엔트리(202(0))의 신뢰도 값 필드(208)를 증분시킬 수 있다(블록(430)). 그러나, 실제 메모리 어드레스(306)가 예측된 메모리 어드레스(338)와 매칭하지 않으면, 로드 어드레스 예측 엔진(102)은 테이블 인덱스(308)에 대응하는 로드 어드레스 예측 테이블 엔트리(202(0))의 신뢰도 값 필드(208)를 리셋한다(블록(432)). 실제 메모리 어드레스(306)가 예측된 메모리 어드레스(338)와 매칭하지만 캐시 방식 필드(212)가 부정확한 일반적이지 않은 이벤트에서, 로드 어드레스 예측 엔진(102)이 캐시 방식 필드(212)를 업데이트함을 유의한다.

[0051] 복수의 로드 어드레스 예측 테이블 엔트리들(202(0) 내지 202(Y)) 중 테이블 인덱스(308)에 대응하는 로드 어드레스 예측 테이블 엔트리(202(0))의 예측기 태그 필드(204)에 예측기 태그(310)가 존재하지 않는다고 로드 어드레스 예측 엔진(102)이 판단 블록(410)에서 결정하면, 로드 어드레스 예측 테이블 엔트리(202(0))는 로드 명령(300)에 대해 존재하는 것으로 보여지지 않는다. 로드 어드레스 예측 엔진(102)은 다음으로, 테이블 인덱스(308)에 대응하는 로드 어드레스 예측 테이블 엔트리(202(0))의 신뢰도 값 필드(208)가 비-제로인지 여부를 결정한다(블록(434)). 비-제로라면, 예측기 태그(310)와의 미스매치가 일시적인 조건일 수 있으므로, 로드 어드레스 예측 엔진(102)은 테이블 인덱스(308)에 대응하는 로드 어드레스 예측 테이블 엔트리(202(0))의 신뢰도 값 필드(208)를 감분시킨다(블록(436)). 테이블 인덱스(308)에 대응하는 로드 어드레스 예측 테이블 엔트리(202(0))의 신뢰도 값 필드(208)가 제로(0)라고 로드 어드레스 예측 엔진(102)이 판단 블록(434)에서 결정하면, 로드 어드레스 예측 엔진(102)은 로드 명령(300)에 대한 예측기 태그(310) 및 실제 메모리 어드레스(306)를 사용하여 테이블 인덱스(308)에 대응하는 로드 어드레스 예측 테이블 엔트리(202(0))를 초기화시킨다(블록(438)).

[0052] 본 명세서에 개시된 양상들에 따라 프로세서-기반 시스템들 내의 로드 경로 이력에 기반한 어드레스 예측 테이블들을 사용하여 로드 어드레스 예측들을 제공하는 것은 임의의 프로세서-기반 디바이스에서 제공되거나 또는 그 디바이스로 통합될 수 있다. 예들은, 셋탑 박스, 엔터테인먼트 유닛, 네비게이션 디바이스, 통신 디바이스, 고정 위치 데이터 유닛, 모바일 위치 데이터 유닛, 모바일 폰, 셀룰러 폰 스마트 폰, 태블릿, 패블릿, 서버, 컴퓨터, 휴대용 컴퓨터, 데스크톱 컴퓨터, 개인 휴대 정보 단말(PDA), 모니터, 컴퓨터 모니터, 텔레비전, 튜너, 라디오, 위성 라디오, 뮤직 플레이어, 디지털 뮤직 플레이어, 휴대용 뮤직 플레이어, 디지털 비디오 플레이어, 비디오 플레이어, 디지털 비디오 디스크(DVD) 플레이어, 휴대용 디지털 비디오 플레이어, 및 자동차(automobile)를 포함하지만 이에 제한되지는 않는다.

[0053] 이와 관련하여, 도 5는 도 1의 로드 어드레스 예측 엔진(LAPE)(102)을 이용할 수 있는 프로세서-기반 시스템(500)의 일 예를 예시한다. 이러한 예에서, 프로세서-기반 시스템(500)은 도 1의 프로세서(100)에 대응할 수 있으며, 하나 또는 그 초과의 프로세서들(504)을 각각 포함하는 하나 또는 그 초과의 CPU들(502)을 포함한다. CPU(들)(502)는 임시로 저장된 데이터에 대한 신속한 액세스를 위해 프로세서(들)(504)에 커플링된 캐시 메모리(506)를 가질 수 있다. CPU(들)(502)는 시스템 버스(508)에 커플링되며, 프로세서-기반 시스템(500)에 포함된 디바이스들을 상호커플링시킬 수 있다. 잘 알려진 바와 같이, CPU(들)(502)는, 시스템 버스(508)를 통해 어드레스, 제어, 및 데이터 정보를 교환함으로써 이들 다른 디바이스들과 통신한다. 예컨대, CPU(들)(502)는 슬레이브 디바이스의 일 예로서의 메모리 제어기(510)에 버스 트랜잭션 요청들을 통신할 수 있다. 도 5에 예시되지 않았지만, 다수의 시스템 버스들(508)이 제공될 수 있다.

[0054] 다른 디바이스들이 시스템 버스(508)에 연결될 수 있다. 도 5에 예시된 바와 같이, 이들 디바이스들은 예들로서, 메모리 시스템(512), 하나 또는 그 초과의 입력 디바이스들(514), 하나 또는 그 초과의 출력 디바이스들(516), 하나 또는 그 초과의 네트워크 인터페이스 디바이스들(518), 및 하나 또는 그 초과의 디스플레이 제어기들(520)을 포함할 수 있다. 입력 디바이스(들)(514)는 입력 키들, 스위치들, 음성 프로세서들 등을 포함하지만 이에 제한되지는 않는 임의의 타입의 입력 디바이스를 포함할 수 있다. 출력 디바이스(들)(516)는 오디오, 비디오, 다른 시각적인 표시자들 등을 포함하지만 이에 제한되지는 않는 임의의 타입의 출력 디바이스를 포함할 수 있다. 네트워크 인터페이스 디바이스(들)(518)는 네트워크(522)로의 그리고 네트워크(522)로부터의 데이터의 교환을 가능하게 하도록 구성된 임의의 디바이스들일 수 있다. 네트워크(522)는, 유선 또는 무선 네트워크, 사설 또는 공용 네트워크, 로컬 영역 네트워크(LAN), 와이드 로컬 영역 네트워크, 무선 로컬 영역 네트워크, 블루투스(BT), 및 인터넷을 포함하지만 이에 제한되지는 않는 임의의 타입의 네트워크일 수 있다. 네트워크 인터페이스 디바이스(들)(518)는 원하는 임의의 타입의 통신 프로토콜을 지원하도록 구성될 수 있다. 메모리 시스템(512)은 하나 또는 그 초과의 메모리 유닛들(524(0) 내지 524(N))을 포함할 수 있다.

[0055] CPU(들)(502)는 또한, 하나 또는 그 초과의 디스플레이들(526)로 전송되는 정보를 제어하기 위해 시스템 버스(508)를 통하여 디스플레이 제어기(들)(520)에 액세스하도록 구성될 수 있다. 디스플레이 제어기(들)(520)는 하나 또는 그 초과의 비디오 프로세서들(528)을 통해 디스플레이될 정보를 디스플레이(들)(526)에 전송하며, 그 프로세서들은 디스플레이될 정보를 디스플레이(들)(526)에 적합한 포맷으로 프로세싱한다. 디스플레이(들)(526)는, 음극선관(CRT), 액정 디스플레이(LCD), 발광 다이오드(LED) 디스플레이, 플라즈마 디스플레이 등을 포함하지만 이에 제한되지는 않는 임의의 타입의 디스플레이를 포함할 수 있다.

[0056] 본 명세서에서 설명된 디바이스들은, 예들로서 임의의 회로, 하드웨어 컴포넌트, 집적 회로(IC), 또는 IC 칩에서 이용될 수 있다. 본 명세서에서 개시된 메모리는 임의의 타입 및 사이즈의 메모리일 수 있으며, 원하는 임의의 타입의 정보를 저장하도록 구성될 수 있다. 이러한 상호교환가능성을 명확히 예시하기 위해, 다양한 예시적인 컴포넌트들, 블록들, 모듈들, 회로들, 및 단계들은 그들의 기능 관점들에서 일반적으로 위에서 설명되었다. 그러한 기능이 어떻게 구현되는지는, 특정한 애플리케이션, 설계 선택들, 및/또는 전체 시스템에 부과된 설계 제약들에 의존한다. 당업자들은 설명된 기능을 각각의 특정 애플리케이션에 대해 다양한 방식들로 구현할 수 있지만, 그러한 구현 결정들이 본 개시내용의 범위를 벗어나게 하는 것으로서 해석되지는 않아야 한다.

[0057] 본 명세서에 개시된 양상들과 관련하여 설명된 다양한 예시적인 로직 블록들, 모듈들, 및 회로들은 프로세서, 디지털 신호 프로세서(DSP), 주문형 집적 회로(ASIC), 필드 프로그래밍가능 게이트 어레이(FPGA) 또는 다른 프로그래밍가능 로직 디바이스, 이산 게이트 또는 트랜지스터 로직, 이산 하드웨어 컴포넌트들, 또는 본 명세서에 설명된 기능들을 수행하도록 설계된 이들의 임의의 결합으로 구현 또는 수행될 수 있다. 프로세서는 마이크로프로세서일 수 있지만, 대안적으로, 프로세서는 임의의 종래의 프로세서, 제어기, 마이크로제어기, 또는 상태 머신일 수 있다. 또한, 프로세서는 컴퓨팅 디바이스들의 조합, 예컨대 DSP와 마이크로프로세서의 조합, 복수의 마이크로프로세서들, DSP 코어와 결합된 하나 또는 그 초과의 마이크로프로세서들, 또는 임의의 다른 그러한 구성으로서 구현될 수 있다.

[0058] 또한, 본 명세서의 예시적인 양상들 중 임의의 양상에서 설명된 동작 단계들은 예들 및 논의를 제공하기 위해 설명된다는 것을 유의한다. 설명된 동작들은 예시된 시퀀스들 이외의 다수의 상이한 시퀀스들에서 수행될 수 있다. 또한, 단일 동작 단계에서 설명된 동작들은 실제로는 다수의 상이한 단계들에서 수행될 수 있다. 부가적으로, 예시적인 양상들에서 논의된 하나 또는 그 초과의 동작 단계들이 결합될 수 있다. 흐름도들에 예시된 동작 단계들은, 당업자에게는 용이하게 명백할 바와 같은 다수의 상이한 변형들을 겪을 수 있다는 것이 이해될 것이다. 당업자들은 또한, 정보 및 신호들이 다양한 상이한 기법들 및 기술들 중 임의의 기법 및 기술을 사용하여 표현될 수 있음을 이해할 것이다. 예컨대, 위의 설명 전반에 걸쳐 참조될 수 있는 데이터, 명령들, 커맨드들, 정보, 신호들, 비트들, 심볼들, 및 칩들은 전압들, 전류들, 전자기파들, 자기장들 또는 자기 입자들, 광학 필드들 또는 광학 입자들, 또는 이들의 임의의 조합에 의해 표현될 수 있다.

[0059] 개시내용의 이전 설명은 당업자가 개시내용을 사용하거나 또는 실시할 수 있도록 제공된다. 개시내용에 대한 다양한 변형들은 당업자들에게 용이하게 명백할 것이며, 본 명세서에서 정의된 일반적인 원리들은 개시내용의 사상 또는 범위를 벗어나지 않으면서 다른 변형들에 적용될 수 있다. 따라서, 개시내용은 본 명세서에 설명된 예들 및 설계들로 제한되도록 의도되는 것이 아니라, 본 명세서에 개시된 원리들 및 신규한 특성들과 일치하는 가장 넓은 범위에 부합할 것이다.

Claims (24)

- 프로세서의 로드 어드레스 예측 엔진으로서,

예측기 태그 필드 및 메모리 어드레스 필드를 각각 포함하는 복수의 로드 어드레스 예측 테이블 엔트리들을 저장하도록 구성된 로드 어드레스 예측 테이블을 포함하며,

상기 로드 어드레스 예측 엔진은,

로드 명령을 수신하고;

상기 로드 명령에 대한 식별자 및 로드 경로 이력 표시자에 기반하여 테이블 인덱스 및 예측기 태그를 생성하고;

상기 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 상기 예측기 태그가 존재하는지 여부를 결정하며; 그리고

상기 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 상기 예측기 태그가 존재한다고 결정하는 것에 대한 응답으로, 상기 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드로부터의 메모리 어드레스를 상기 로드 명령에 대한 예측된 메모리 어드레스로서 제공하도록

구성되는, 로드 어드레스 예측 엔진. - 제1항에 있어서,

분기 방향 이력 또는 분기 경로 이력, 또는 이들의 조합들에 기반하여 상기 테이블 인덱스 및 상기 예측기 태그를 생성하도록 추가로 구성되는, 로드 어드레스 예측 엔진. - 제1항에 있어서,

상기 로드 명령에 대한 상기 예측된 메모리 어드레스가 상기 프로세서의 시스템 데이터 캐시에 존재하는지 여부를 결정하고;

상기 로드 명령에 대한 상기 예측된 메모리 어드레스가 상기 프로세서의 시스템 데이터 캐시에 존재한다고 결정하는 것에 대한 응답으로:

상기 시스템 데이터 캐시로부터 상기 예측된 메모리 어드레스에 대한 데이터를 리트리브하고; 그리고

상기 프로세서의 실행 파이프라인의 후단 명령 파이프라인에 리트리브된 데이터를 데이터 값 예측으로서 제공하며; 그리고

상기 로드 명령에 대한 상기 예측된 메모리 어드레스가 상기 프로세서의 시스템 데이터 캐시에 존재하지 않는다고 결정하는 것에 대한 응답으로:

상기 프로세서의 시스템 메모리로부터 상기 예측된 메모리 어드레스에 대응하는 데이터를 프리페칭(prefetch)하고; 그리고

상기 프로세서의 시스템 데이터 캐시에 프리페칭된 데이터를 저장하도록

추가로 구성되는, 로드 어드레스 예측 엔진. - 제3항에 있어서,

상기 복수의 로드 어드레스 예측 테이블 엔트리들의 각각의 로드 어드레스 예측 테이블 엔트리는 신뢰도 값 필드를 더 포함하고; 그리고

상기 로드 어드레스 예측 엔진은, 상기 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드가 상기 로드 어드레스 예측 엔진의 신뢰도 임계치 값 필드를 초과하는 것에 대한 추가적인 응답으로, 상기 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드의 메모리 어드레스를 상기 로드 명령에 대한 예측된 메모리 어드레스로서 제공하도록 구성되는, 로드 어드레스 예측 엔진. - 제4항에 있어서,

상기 로드 명령의 실행에 후속하여,

상기 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 상기 예측기 태그가 존재한다고 결정하는 것에 대한 응답으로:

상기 로드 명령의 실제 메모리 어드레스가 상기 로드 명령에 대한 예측된 메모리 어드레스와 매칭하는지 여부를 결정하고;

상기 로드 명령의 실제 메모리 어드레스가 상기 로드 명령에 대한 예측된 메모리 어드레스와 매칭한다고 결정하는 것에 대한 응답으로, 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드를 증분시키며; 그리고

상기 로드 명령의 실제 메모리 어드레스가 상기 로드 명령에 대한 예측된 메모리 어드레스와 매칭하지 않는다고 결정하는 것에 대한 응답으로, 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드를 리셋하고; 그리고

상기 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 상기 예측기 태그가 존재하지 않는다고 결정하는 것에 대한 응답으로:

상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드가 비-제로인지 여부를 결정하고;

상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드가 비-제로라고 결정하는 것에 대한 응답으로, 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드를 감분시키며; 그리고

상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드가 제로(0)라고 결정하는 것에 대한 응답으로, 상기 로드 명령에 대한 상기 예측기 태그 및 상기 실제 메모리 어드레스를 이용하여 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리를 초기화시키도록

추가로 구성되는, 로드 어드레스 예측 엔진. - 제3항에 있어서,

상기 복수의 로드 어드레스 예측 테이블 엔트리들의 각각의 로드 어드레스 예측 테이블 엔트리는 캐시 방식(cache way) 필드를 더 포함하고; 그리고

상기 로드 어드레스 예측 엔진은, 상기 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 캐시 방식 필드에 기반하여, 상기 로드 명령에 대한 예측된 메모리 어드레스가 상기 프로세서의 시스템 데이터 캐시에 존재하는지 여부를 결정하도록 구성되는, 로드 어드레스 예측 엔진. - 제1항에 있어서,

메모리 명확성(disambiguation)을 위해, 상기 로드 명령에 대한 예측된 메모리 어드레스로서 상기 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드의 메모리 어드레스를 상기 프로세서의 후단 명령 파이프라인에 제공하도록 구성되는, 로드 어드레스 예측 엔진. - 제1항에 있어서,

집적 회로(IC)로 통합되는, 로드 어드레스 예측 엔진. - 제1항에 있어서,

셋탑 박스; 엔터테인먼트 유닛; 네비게이션 디바이스; 통신 디바이스; 고정 위치 데이터 유닛; 모바일 위치 데이터 유닛; 모바일 폰; 셀룰러 폰; 스마트 폰; 태블릿; 패블릿; 컴퓨터; 휴대용 컴퓨터; 데스크톱 컴퓨터; 개인 휴대 정보 단말(PDA); 모니터; 컴퓨터 모니터; 텔레비전; 튜너; 라디오; 위성 라디오; 뮤직 플레이어; 디지털 뮤직 플레이어; 휴대용 뮤직 플레이어; 디지털 비디오 플레이어; 비디오 플레이어; 디지털 비디오 디스크(DVD) 플레이어; 휴대용 디지털 비디오 플레이어; 및 자동차(automobile)로 이루어진 그룹으로부터 선택되는 디바이스로 통합되는, 로드 어드레스 예측 엔진. - 프로세서의 로드 어드레스 예측 엔진로서,

상기 로드 어드레스 예측 엔진은,

로드 명령을 수신하기 위한 수단;

상기 로드 명령에 대한 식별자 및 로드 경로 이력 표시자에 기반하여 테이블 인덱스 및 예측기 태그를 생성하기 위한 수단;

상기 로드 어드레스 예측 엔진의 로드 어드레스 예측 테이블의 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 상기 예측기 태그가 존재하는지 여부를 결정하기 위한 수단; 및

상기 로드 어드레스 예측 엔진의 로드 어드레스 예측 테이블의 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 상기 예측기 태그가 존재한다고 결정하는 것에 대한 응답으로, 상기 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드로부터의 메모리 어드레스를 상기 로드 명령에 대한 예측된 메모리 어드레스로서 제공하기 위한 수단을 포함하는, 로드 어드레스 예측 엔진. - 로드 어드레스 예측들을 제공하기 위한 방법으로서,

프로세서의 로드 어드레스 예측 엔진에 의해, 로드 명령을 수신하는 단계;

상기 로드 명령에 대한 식별자 및 로드 경로 이력 표시자에 기반하여 테이블 인덱스 및 예측기 태그를 생성하는 단계;

상기 로드 어드레스 예측 엔진의 로드 어드레스 예측 테이블의 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 상기 예측기 태그가 존재하는지 여부를 결정하는 단계; 및

상기 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 상기 예측기 태그가 존재한다고 결정하는 것에 대한 응답으로, 상기 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드로부터의 메모리 어드레스를 상기 로드 명령에 대한 예측된 메모리 어드레스로서 제공하는 단계를 포함하는, 로드 어드레스 예측들을 제공하기 위한 방법. - 제11항에 있어서,

상기 테이블 인덱스 및 예측기 태그를 생성하는 단계는, 분기 방향 이력 또는 분기 경로 이력, 또는 이들의 조합들에 추가로 기반하는, 로드 어드레스 예측들을 제공하기 위한 방법. - 제11항에 있어서,

상기 로드 명령에 대한 상기 예측된 메모리 어드레스가 상기 프로세서의 시스템 데이터 캐시에 존재하는지 여부를 결정하는 단계;

상기 로드 명령에 대한 상기 예측된 메모리 어드레스가 상기 프로세서의 시스템 데이터 캐시에 존재한다고 결정하는 것에 대한 응답으로:

상기 시스템 데이터 캐시로부터 상기 예측된 메모리 어드레스에 대한 데이터를 리트리브하는 단계; 및

상기 프로세서의 실행 파이프라인의 후단 명령 파이프라인에 리트리브된 데이터를 데이터 값 예측으로서 제공하는 단계; 및

상기 로드 명령에 대한 상기 예측된 메모리 어드레스가 상기 프로세서의 시스템 데이터 캐시에 존재하지 않는다고 결정하는 것에 대한 응답으로:

상기 프로세서의 시스템 메모리로부터 상기 예측된 메모리 어드레스에 대응하는 데이터를 프리페칭하는 단계; 및

상기 프로세서의 시스템 데이터 캐시에 프리페칭된 데이터를 저장하는 단계를 더 포함하는, 로드 어드레스 예측들을 제공하기 위한 방법. - 제13항에 있어서,

상기 복수의 로드 어드레스 예측 테이블 엔트리들의 각각의 로드 어드레스 예측 테이블 엔트리는 신뢰도 값 필드를 더 포함하고; 그리고

상기 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드의 메모리 어드레스를 상기 로드 명령에 대한 예측된 메모리 어드레스로서 제공하는 단계는, 상기 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드가 상기 로드 어드레스 예측 엔진의 신뢰도 임계치 값 필드를 초과하는 것에 추가로 응답하는, 로드 어드레스 예측들을 제공하기 위한 방법. - 제14항에 있어서,

상기 로드 명령의 실행에 후속하여,

상기 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 상기 예측기 태그가 존재한다고 결정하는 것에 대한 응답으로:

상기 로드 명령의 실제 메모리 어드레스가 상기 로드 명령에 대한 예측된 메모리 어드레스와 매칭하는지 여부를 결정하는 단계;

상기 로드 명령의 실제 메모리 어드레스가 상기 로드 명령에 대한 예측된 메모리 어드레스와 매칭한다고 결정하는 것에 대한 응답으로, 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드를 증분시키는 단계; 및

상기 로드 명령의 실제 메모리 어드레스가 상기 로드 명령에 대한 예측된 메모리 어드레스와 매칭하지 않는다고 결정하는 것에 대한 응답으로, 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드를 리셋하는 단계; 및

상기 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 상기 예측기 태그가 존재하지 않는다고 결정하는 것에 대한 응답으로:

상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드가 비-제로인지 여부를 결정하는 단계;

상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드가 비-제로라고 결정하는 것에 대한 응답으로, 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드를 감분시키는 단계; 및

상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드가 제로(0)라고 결정하는 것에 대한 응답으로, 상기 로드 명령에 대한 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리를 초기화시키는 단계를 더 포함하는, 로드 어드레스 예측들을 제공하기 위한 방법. - 제13항에 있어서,

상기 복수의 로드 어드레스 예측 테이블 엔트리들의 각각의 로드 어드레스 예측 테이블 엔트리는 캐시 방식 필드를 더 포함하고; 그리고

상기 로드 명령에 대한 예측된 메모리 어드레스가 상기 프로세서의 시스템 데이터 캐시에 존재하는지 여부를 결정하는 단계는, 상기 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 캐시 방식 필드에 기반하는, 로드 어드레스 예측들을 제공하기 위한 방법. - 제11항에 있어서,

메모리 명확성을 위해, 상기 로드 명령에 대한 예측된 메모리 어드레스로서 상기 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드의 메모리 어드레스를 상기 프로세서의 후단 명령 파이프라인에 제공하는 단계를 포함하는, 로드 어드레스 예측들을 제공하기 위한 방법. - 컴퓨터 실행가능 명령들이 저장된 비-일시적인 컴퓨터-판독가능 저장 매체로서,

상기 컴퓨터 실행가능 명령들은, 프로세서에 의해 실행될 경우, 상기 프로세서로 하여금,

로드 명령을 수신하게 하고;

상기 로드 명령에 대한 식별자 및 로드 경로 이력 표시자에 기반하여 테이블 인덱스 및 예측기 태그를 생성하게 하고;

로드 어드레스 예측 테이블의 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 상기 예측기 태그가 존재하는지 여부를 결정하게 하며; 그리고

상기 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 상기 예측기 태그가 존재한다고 결정하는 것에 대한 응답으로, 상기 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드로부터의 메모리 어드레스를 상기 로드 명령에 대한 예측된 메모리 어드레스로서 제공하게 하는, 비-일시적인 컴퓨터-판독가능 저장 매체. - 제18항에 있어서,

상기 프로세서에 의해 실행될 경우, 상기 프로세서로 하여금 추가로, 분기 방향 이력 또는 분기 경로 이력, 또는 이들의 조합들에 기반하여 상기 테이블 인덱스 및 상기 예측기 태그를 생성하게 하는 컴퓨터 실행가능 명령들이 저장되는, 비-일시적인 컴퓨터-판독가능 저장 매체. - 제18항에 있어서,

상기 프로세서에 의해 실행될 경우, 상기 프로세서로 하여금 추가로,

상기 로드 명령에 대한 상기 예측된 메모리 어드레스가 상기 프로세서의 시스템 데이터 캐시에 존재하는지 여부를 결정하게 하고;

상기 로드 명령에 대한 상기 예측된 메모리 어드레스가 상기 프로세서의 시스템 데이터 캐시에 존재한다고 결정하는 것에 대한 응답으로:

상기 시스템 데이터 캐시로부터 상기 예측된 메모리 어드레스에 대한 데이터를 리트리브하게 하고; 그리고

상기 프로세서의 실행 파이프라인의 후단 명령 파이프라인에 리트리브된 데이터를 데이터 값 예측으로서 제공하게 하며; 그리고

상기 로드 명령에 대한 상기 예측된 메모리 어드레스가 상기 프로세서의 시스템 데이터 캐시에 존재하지 않는다고 결정하는 것에 대한 응답으로:

상기 프로세서의 시스템 메모리로부터 상기 예측된 메모리 어드레스에 대응하는 데이터를 프리페칭하게 하고; 그리고

상기 프로세서의 시스템 데이터 캐시에 프리페칭된 데이터를 저장하게 하는

컴퓨터 실행가능 명령들이 저장되는, 비-일시적인 컴퓨터-판독가능 저장 매체. - 제20항에 있어서,

상기 프로세서에 의해 실행될 경우, 상기 프로세서로 하여금 추가로, 상기 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드가 상기 로드 어드레스 예측 엔진의 신뢰도 임계치 값 필드를 초과하는 것에 대한 응답으로, 상기 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드의 메모리 어드레스를 상기 로드 명령에 대한 예측된 메모리 어드레스로서 제공하게 하는 컴퓨터 실행가능 명령들이 저장되는, 비-일시적인 컴퓨터-판독가능 저장 매체. - 제21항에 있어서,

상기 프로세서에 의해 실행될 경우, 상기 프로세서로 하여금 추가로, 상기 로드 명령의 실행에 후속하여,

상기 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 상기 예측기 태그가 존재한다고 결정하는 것에 대한 응답으로:

상기 로드 명령의 실제 메모리 어드레스가 상기 로드 명령에 대한 예측된 메모리 어드레스와 매칭하는지 여부를 결정하게 하고;

상기 로드 명령의 실제 메모리 어드레스가 상기 로드 명령에 대한 예측된 메모리 어드레스와 매칭한다고 결정하는 것에 대한 응답으로, 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드를 증분시키게 하며; 그리고

상기 로드 명령의 실제 메모리 어드레스가 상기 로드 명령에 대한 예측된 메모리 어드레스와 매칭하지 않는다고 결정하는 것에 대한 응답으로, 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드를 리셋하게 하고; 그리고

상기 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 예측기 태그 필드에 상기 예측기 태그가 존재하지 않는다고 결정하는 것에 대한 응답으로:

상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드가 비-제로인지 여부를 결정하게 하고;

상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드가 비-제로라고 결정하는 것에 대한 응답으로, 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드를 감분시키게 하고; 그리고

상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 신뢰도 값 필드가 제로(0)라고 결정하는 것에 대한 응답으로, 상기 로드 명령에 대한 상기 예측기 태그 및 상기 실제 메모리 어드레스를 이용하여 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리를 초기화시키게 하는

컴퓨터 실행가능 명령들이 저장되는, 비-일시적인 컴퓨터-판독가능 저장 매체. - 제20항에 있어서,

상기 프로세서에 의해 실행될 경우, 상기 프로세서로 하여금 추가로, 상기 복수의 로드 어드레스 예측 테이블 엔트리들 중 상기 테이블 인덱스에 대응하는 로드 어드레스 예측 테이블 엔트리의 캐시 방식 필드에 기반하여, 상기 로드 명령에 대한 예측된 메모리 어드레스가 상기 프로세서의 시스템 데이터 캐시에 존재하는지 여부를 결정하게 하는 컴퓨터 실행가능 명령들이 저장되는, 비-일시적인 컴퓨터-판독가능 저장 매체. - 제18항에 있어서,

상기 프로세서에 의해 실행될 경우, 상기 프로세서로 하여금 추가로, 메모리 명확성을 위해, 상기 로드 명령에 대한 예측된 메모리 어드레스로서 상기 로드 어드레스 예측 테이블 엔트리의 메모리 어드레스 필드의 메모리 어드레스를 상기 프로세서의 후단 명령 파이프라인에 제공하게 하는 컴퓨터 실행가능 명령들이 저장되는, 비-일시적인 컴퓨터-판독가능 저장 매체.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US15/087,069 | 2016-03-31 | ||

| US15/087,069 US11709679B2 (en) | 2016-03-31 | 2016-03-31 | Providing load address predictions using address prediction tables based on load path history in processor-based systems |

| PCT/US2017/020357 WO2017172232A1 (en) | 2016-03-31 | 2017-03-02 | Providing load address predictions using address prediction tables based on load path history in processor-based systems |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20180127379A true KR20180127379A (ko) | 2018-11-28 |

Family

ID=58358898

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020187028217A KR20180127379A (ko) | 2016-03-31 | 2017-03-02 | 프로세서-기반 시스템들 내의 로드 경로 이력에 기반한 어드레스 예측 테이블들을 사용하는 로드 어드레스 예측들의 제공 |

Country Status (9)

| Country | Link |

|---|---|

| US (1) | US11709679B2 (ko) |

| EP (1) | EP3436930B1 (ko) |

| JP (1) | JP6744423B2 (ko) |

| KR (1) | KR20180127379A (ko) |

| CN (1) | CN108780398B (ko) |

| BR (1) | BR112018069818A2 (ko) |

| CA (1) | CA3016029A1 (ko) |

| TW (1) | TW201737068A (ko) |

| WO (1) | WO2017172232A1 (ko) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10936713B2 (en) | 2015-12-17 | 2021-03-02 | The Charles Stark Draper Laboratory, Inc. | Techniques for metadata processing |

| US10235176B2 (en) * | 2015-12-17 | 2019-03-19 | The Charles Stark Draper Laboratory, Inc. | Techniques for metadata processing |

| US11281586B2 (en) * | 2017-05-09 | 2022-03-22 | Andes Technology Corporation | Processor and way prediction method thereof |

| US10645133B2 (en) * | 2017-07-12 | 2020-05-05 | Loon Llc | Method and system for delivering content over transient access networks |

| US10503648B2 (en) * | 2017-12-12 | 2019-12-10 | Advanced Micro Devices, Inc. | Cache to cache data transfer acceleration techniques |

| SG11202007272QA (en) | 2018-02-02 | 2020-08-28 | Charles Stark Draper Laboratory Inc | Systems and methods for policy execution processing |

| WO2019152792A1 (en) | 2018-02-02 | 2019-08-08 | Dover Microsystems, Inc. | Systems and methods for policy linking and/or loading for secure initialization |

| EP3788488A1 (en) | 2018-04-30 | 2021-03-10 | Dover Microsystems, Inc. | Systems and methods for checking safety properties |

| US10838731B2 (en) * | 2018-09-19 | 2020-11-17 | Qualcomm Incorporated | Branch prediction based on load-path history |

| TW202022678A (zh) | 2018-11-06 | 2020-06-16 | 美商多佛微系統公司 | 用於停滯主處理器的系統和方法 |

| WO2020132012A1 (en) | 2018-12-18 | 2020-06-25 | Dover Microsystems, Inc. | Systems and methods for data lifecycle protection |

| US10929142B2 (en) * | 2019-03-20 | 2021-02-23 | International Business Machines Corporation | Making precise operand-store-compare predictions to avoid false dependencies |

| US11243774B2 (en) | 2019-03-20 | 2022-02-08 | International Business Machines Corporation | Dynamic selection of OSC hazard avoidance mechanism |

| US11829763B2 (en) | 2019-08-13 | 2023-11-28 | Apple Inc. | Early load execution via constant address and stride prediction |

| US10896041B1 (en) * | 2019-09-25 | 2021-01-19 | Microsoft Technology Licensing, Llc | Enabling early execution of move-immediate instructions having variable immediate value sizes in processor-based devices |

| US11204771B2 (en) * | 2019-10-24 | 2021-12-21 | Arm Limited | Methods and apparatus for handling processor load instructions |

| US11194575B2 (en) * | 2019-11-07 | 2021-12-07 | International Business Machines Corporation | Instruction address based data prediction and prefetching |

| GB2592661B (en) * | 2020-03-05 | 2022-05-11 | Advanced Risc Mach Ltd | An apparatus and method for performing branch prediction |

| TWI768547B (zh) * | 2020-11-18 | 2022-06-21 | 瑞昱半導體股份有限公司 | 管線式電腦系統與指令處理方法 |

| US11630670B2 (en) | 2021-07-21 | 2023-04-18 | Apple Inc. | Multi-table signature prefetch |

| US20230176973A1 (en) * | 2021-12-08 | 2023-06-08 | Arm Limited | Replacement control for candidate producer-consumer relationships trained for prefetch generation |

Family Cites Families (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5287467A (en) | 1991-04-18 | 1994-02-15 | International Business Machines Corporation | Pipeline for removing and concurrently executing two or more branch instructions in synchronization with other instructions executing in the execution unit |

| US6108775A (en) | 1996-12-30 | 2000-08-22 | Texas Instruments Incorporated | Dynamically loadable pattern history tables in a multi-task microprocessor |

| JPH10260834A (ja) | 1997-03-18 | 1998-09-29 | Fujitsu Ltd | ロードアドレス予測装置および並列処理装置およびそのロードアドレス予測方法 |

| US5941981A (en) | 1997-11-03 | 1999-08-24 | Advanced Micro Devices, Inc. | System for using a data history table to select among multiple data prefetch algorithms |

| US6230260B1 (en) | 1998-09-01 | 2001-05-08 | International Business Machines Corporation | Circuit arrangement and method of speculative instruction execution utilizing instruction history caching |

| US6438673B1 (en) | 1999-12-30 | 2002-08-20 | Intel Corporation | Correlated address prediction |

| DE10121792C2 (de) * | 2000-05-26 | 2003-09-25 | Ibm | Universelle Ladeadresse/Wertevorhersageschema |

| US6868491B1 (en) | 2000-06-22 | 2005-03-15 | International Business Machines Corporation | Processor and method of executing load instructions out-of-order having reduced hazard penalty |

| US7062638B2 (en) | 2000-12-29 | 2006-06-13 | Intel Corporation | Prediction of issued silent store operations for allowing subsequently issued loads to bypass unexecuted silent stores and confirming the bypass upon execution of the stores |

| US6907520B2 (en) | 2001-01-11 | 2005-06-14 | Sun Microsystems, Inc. | Threshold-based load address prediction and new thread identification in a multithreaded microprocessor |

| JP3594081B2 (ja) | 2001-01-23 | 2004-11-24 | 日本電気株式会社 | 情報処理装置 |

| JP4030314B2 (ja) | 2002-01-29 | 2008-01-09 | 富士通株式会社 | 演算処理装置 |

| US6976147B1 (en) | 2003-01-21 | 2005-12-13 | Advanced Micro Devices, Inc. | Stride-based prefetch mechanism using a prediction confidence value |

| US7430650B1 (en) | 2004-06-17 | 2008-09-30 | Richard Ross | Generating a set of pre-fetch address candidates based on popular sets of address and data offset counters |

| US7917731B2 (en) | 2006-08-02 | 2011-03-29 | Qualcomm Incorporated | Method and apparatus for prefetching non-sequential instruction addresses |

| US7856548B1 (en) * | 2006-12-26 | 2010-12-21 | Oracle America, Inc. | Prediction of data values read from memory by a microprocessor using a dynamic confidence threshold |

| US7640420B2 (en) | 2007-04-02 | 2009-12-29 | Intel Corporation | Pre-fetch apparatus |

| US8392651B2 (en) * | 2008-08-20 | 2013-03-05 | Mips Technologies, Inc. | Data cache way prediction |

| US8533438B2 (en) | 2009-08-12 | 2013-09-10 | Via Technologies, Inc. | Store-to-load forwarding based on load/store address computation source information comparisons |

| US9189432B2 (en) * | 2010-11-15 | 2015-11-17 | Arm Limited | Apparatus and method for predicting target storage unit |

| US9146739B2 (en) | 2012-06-14 | 2015-09-29 | International Business Machines Corporation | Branch prediction preloading |

| US20140173294A1 (en) | 2012-12-14 | 2014-06-19 | Broadcom Corporation | Techniques for emulating an eeprom device |

| US9367468B2 (en) | 2013-01-15 | 2016-06-14 | Qualcomm Incorporated | Data cache way prediction |

| GB2506462B (en) | 2013-03-13 | 2014-08-13 | Imagination Tech Ltd | Indirect branch prediction |

| US9244827B2 (en) | 2013-09-25 | 2016-01-26 | Intel Corporation | Store address prediction for memory disambiguation in a processing device |

| US9606805B1 (en) | 2015-10-19 | 2017-03-28 | International Business Machines Corporation | Accuracy of operand store compare prediction using confidence counter |

| US10437595B1 (en) | 2016-03-15 | 2019-10-08 | Apple Inc. | Load/store dependency predictor optimization for replayed loads |

| US10353819B2 (en) * | 2016-06-24 | 2019-07-16 | Qualcomm Incorporated | Next line prefetchers employing initial high prefetch prediction confidence states for throttling next line prefetches in a processor-based system |

-

2016

- 2016-03-31 US US15/087,069 patent/US11709679B2/en active Active

-

2017

- 2017-03-02 JP JP2018550596A patent/JP6744423B2/ja not_active Expired - Fee Related

- 2017-03-02 KR KR1020187028217A patent/KR20180127379A/ko active IP Right Grant

- 2017-03-02 EP EP17711898.1A patent/EP3436930B1/en active Active

- 2017-03-02 BR BR112018069818A patent/BR112018069818A2/pt not_active IP Right Cessation

- 2017-03-02 WO PCT/US2017/020357 patent/WO2017172232A1/en active Application Filing

- 2017-03-02 CA CA3016029A patent/CA3016029A1/en not_active Abandoned

- 2017-03-02 TW TW106106784A patent/TW201737068A/zh unknown

- 2017-03-02 CN CN201780016881.8A patent/CN108780398B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP6744423B2 (ja) | 2020-08-19 |

| CN108780398B (zh) | 2022-06-07 |

| WO2017172232A1 (en) | 2017-10-05 |

| CA3016029A1 (en) | 2017-10-05 |

| EP3436930A1 (en) | 2019-02-06 |

| BR112018069818A2 (pt) | 2019-01-29 |

| TW201737068A (zh) | 2017-10-16 |

| US20170286119A1 (en) | 2017-10-05 |

| CN108780398A (zh) | 2018-11-09 |

| US11709679B2 (en) | 2023-07-25 |

| EP3436930B1 (en) | 2020-05-20 |

| JP2019514110A (ja) | 2019-05-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP3436930B1 (en) | Providing load address predictions using address prediction tables based on load path history in processor-based systems | |

| US10353819B2 (en) | Next line prefetchers employing initial high prefetch prediction confidence states for throttling next line prefetches in a processor-based system | |

| US9830152B2 (en) | Selective storing of previously decoded instructions of frequently-called instruction sequences in an instruction sequence buffer to be executed by a processor | |

| KR101705211B1 (ko) | 분기 예측 테이블 스왑 명령(들)에 응답하여 분기 방향 히스토리(들)를 스왑하는 것, 및 관련 시스템들 및 방법들 | |

| EP3433728B1 (en) | Providing references to previously decoded instructions of recently-provided instructions to be executed by a processor | |

| EP3221784B1 (en) | Providing loop-invariant value prediction using a predicted values table, and related apparatuses, methods, and computer-readable media | |

| JP2015535634A (ja) | 実行パイプラインバブルを低減するためにサブルーチンリターンのための分岐ターゲット命令キャッシュ(btic)エントリを確立すること、ならびに関連するシステム、方法、およびコンピュータ可読媒体 | |

| US20160170770A1 (en) | Providing early instruction execution in an out-of-order (ooo) processor, and related apparatuses, methods, and computer-readable media | |

| US20160077836A1 (en) | Predicting literal load values using a literal load prediction table, and related circuits, methods, and computer-readable media | |

| US9858077B2 (en) | Issuing instructions to execution pipelines based on register-associated preferences, and related instruction processing circuits, processor systems, methods, and computer-readable media | |

| EP3335111B1 (en) | Predicting memory instruction punts in a computer processor using a punt avoidance table (pat) | |

| WO2022031816A1 (en) | Mitigation of return stack buffer side channel attacks in a processor | |

| US20160291981A1 (en) | Removing invalid literal load values, and related circuits, methods, and computer-readable media | |

| US20190294443A1 (en) | Providing early pipeline optimization of conditional instructions in processor-based systems |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A302 | Request for accelerated examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right |