KR20180004677A - 브릿지리스 인터리브 역률보정회로 및 그 구동방법 - Google Patents

브릿지리스 인터리브 역률보정회로 및 그 구동방법 Download PDFInfo

- Publication number

- KR20180004677A KR20180004677A KR1020170085018A KR20170085018A KR20180004677A KR 20180004677 A KR20180004677 A KR 20180004677A KR 1020170085018 A KR1020170085018 A KR 1020170085018A KR 20170085018 A KR20170085018 A KR 20170085018A KR 20180004677 A KR20180004677 A KR 20180004677A

- Authority

- KR

- South Korea

- Prior art keywords

- switch

- boost

- inductor

- operation mode

- power factor

- Prior art date

Links

- 238000012937 correction Methods 0.000 title claims abstract description 85

- 238000000034 method Methods 0.000 title claims abstract description 36

- 238000005259 measurement Methods 0.000 abstract description 3

- 238000010586 diagram Methods 0.000 description 19

- 230000008569 process Effects 0.000 description 8

- 230000008859 change Effects 0.000 description 6

- 230000007423 decrease Effects 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 4

- 241001125929 Trisopterus luscus Species 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 239000003990 capacitor Substances 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 238000007796 conventional method Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000000691 measurement method Methods 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 238000005070 sampling Methods 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- ULBXWWGWDPVHAO-UHFFFAOYSA-N Chlorbufam Chemical compound C#CC(C)OC(=O)NC1=CC=CC(Cl)=C1 ULBXWWGWDPVHAO-UHFFFAOYSA-N 0.000 description 1

- 230000001276 controlling effect Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000010363 phase shift Effects 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/42—Circuits or arrangements for compensating for or adjusting power factor in converters or inverters

- H02M1/4208—Arrangements for improving power factor of AC input

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02B—CLIMATE CHANGE MITIGATION TECHNOLOGIES RELATED TO BUILDINGS, e.g. HOUSING, HOUSE APPLIANCES OR RELATED END-USER APPLICATIONS

- Y02B70/00—Technologies for an efficient end-user side electric power management and consumption

- Y02B70/10—Technologies improving the efficiency by using switched-mode power supplies [SMPS], i.e. efficient power electronics conversion e.g. power factor correction or reduction of losses in power supplies or efficient standby modes

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Dc-Dc Converters (AREA)

Abstract

Description

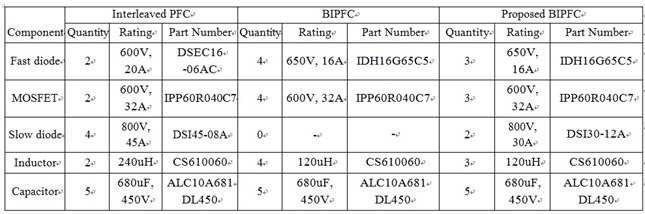

도 2는 본 발명의 일 실시예에 따른 브릿지리스 인터리브 역률보정회로가 개략적으로 구현된 회로도이다.

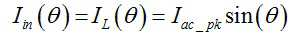

도 3 내지 도 5는 도 2의 브릿지리스 인터리브 역률보정회로의 동작 특성 및 구동 원리가 도시된 도면이다.

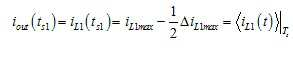

도 6 내지 도 7은 도 2의 전류 센서(500)의 구체적인 동작 방법이 도시된 도면이다.

도 9 내지 도 16은 도 2의 브릿지리스 인터리브 역률보정회로의 실험 결과를 나타낸 도면이다.

200: 배터리

300: 부스트 레그

400: 스위치 회로

500: 단일 전류 센서

Claims (12)

- 입력 전원과 연결되며 인덕터를 포함하는 적어도 하나의 단일 부스트 레그와, 상기 입력 전원과 연결되며 인덕터 및 저속 다이오드를 포함하는 복수의 병합 부스트 레그를 포함하는 복수의 부스트 레그;

하나의 상기 단일 부스트 레그와 연결되는 단일 스위치 회로와, 적어도 두 개의 상기 병합 부스트 레그와 연결되는 병합 스위치 회로를 포함하는 복수의 스위치 회로; 및

상기 스위치 회로와 연결되고, 미리 정해진 동작 구간 및 미리 정해진 전류 측정 시점에 따라 출력 전류를 측정하는 단일 전류 센서를 포함하는, 브릿지리스 인터리브 역률보정회로.

- 제1항에 있어서,

상기 복수의 부스트 레그는 제1 부스트 레그 내지 제4 부스트 레그를 포함하고,

상기 제1 부스트 레그 및 상기 제4 부스트 레그는 상기 단일 부스트 레그이고, 제2 부스트 레그 및 제3 부스트 레그는 상기 병합 부스트 레그인, 브릿지리스 인터리브 역률보정회로.

- 제2항에 있어서,

상기 복수의 스위치 회로는 제1 스위치 회로 내지 제3 스위치 회로를 포함하고,

상기 제1 스위치 회로는 상기 제1 부스트 레그와 연결되고, 제2 스위치 회로는 상기 제2 부스트 레그 및 상기 제3 부스트 레그와 병렬로 연결되며, 상기 제3 스위치 회로는 상기 제4 부스트 레그와 연결되는, 브릿지리스 인터리브 역률보정회로.

- 제1항에 있어서,

상기 스위치 회로는 고속 다이오드 및 스위치를 포함하고,

상기 저속 다이오드는 상기 고속 다이오드와 직렬로 연결되어 상기 입력 전원의 순환 전류를 차단하는, 브릿지리스 인터리브 역률보정회로.

- 제1항에 있어서,

상기 브릿지리스 인터리브 역률보정회로는, 스위칭 주파수가 라인 주파수보다 높은 상태인 경우, 라인 전압의 1/2주기마다 상기 입력 전원으로부터 공급되는 입력 전압의 극성을 변화시키는 부스트 컨버터로 동작되는, 브릿지리스 인터리브 역률보정회로.

- 제5항에 있어서,

상기 브릿지리스 인터리브 역률보정회로는,

상기 라인 전압의 1/2주기동안 변화되는 듀티 사이클 값이 미리 정해진 기준값보다 작은 경우, 상기 복수의 스위치 회로가 제1 동작 모드 내지 제3 동작 모드 중 어느 하나의 동작 모드로 작동되도록 제어하고,

상기 듀티 사이클 값이 상기 기준값보다 큰 경우, 상기 복수의 스위치 회로가 제4 동작 모드 내지 제6 동작 모드 중 어느 하나의 동작 모드로 작동되도록 제어하는, 브릿지리스 인터리브 역률보정회로.

- 제6항에 있어서,

상기 복수의 스위치 회로는,

상기 듀티 사이클 값이 미리 정해진 값보다 작은 경우,

상기 라인 전압의 1/2주기를 구성하는 제1 구간은 제1 동작 모드로 제어되고, 상기 제1 구간 이후의 제2 구간은 제2 동작 모드로 제어되고, 상기 제2 구간 이후의 제3 구간은 제3 동작 모드로 제어되며, 상기 제3 구간 이후의 제4 구간은 상기 제2 동작 모드로 제어되고,

상기 듀티 사이클 값이 미리 정해진 값보다 큰 경우,

상기 라인 전압의 1/2주기를 구성하는 제1 구간은 제4 동작 모드로 제어되고, 상기 제1 구간 이후의 제2 구간은 제5 동작 모드로 제어되고, 상기 제2 구간 이후의 제3 구간은 상기 제4 동작 모드로 제어되며, 상기 제3 구간 이후의 제4 구간은 제6 동작 모드로 제어되는, 브릿지리스 인터리브 역률보정회로.

- 제7항에 있어서,

상기 단일 전류 센서는,

상기 듀티 사이클 값이 미리 정해진 값보다 작은 경우, 상기 제1 구간에서 출력 전류를 측정하여 상기 제1 인덕터의 인덕터 전류를 측정하고, 상기 제3 구간에서 출력 전류를 측정하여 상기 제2 인덕터의 인덕터 전류를 측정하며,

상기 듀티 사이클 값이 미리 정해진 값보다 큰 경우, 상기 제4 구간에서 출력 전류를 측정하여 상기 제1 인덕터의 인덕터 전류를 측정하고, 상기 제2 구간에서 출력 전류를 측정하여 상기 제2 인덕터의 인덕터 전류를 측정하는, 브릿지리스 인터리브 역률보정회로.

- 제7항에 있어서,

상기 복수의 스위치 회로가 제1 스위치 회로 내지 제3 스위치 회로로 마련되는 경우, 상기 브릿지리스 인터리브 역률보정회로는,

상기 제1 동작 모드 및 상기 제6 동작 모드에서 상기 제1 스위치 회로의 제1 스위치와 상기 제3 스위치 회로의 제3 스위치는 턴오프 시키고, 제2 스위치 회로의 제2 스위치는 턴온시키고,

상기 제2 동작 모드에서 상기 상기 제1 스위치 내지 상기 제3 스위치를 턴오프시키고,

상기 제3 동작 모드에서 상기 제1 스위치 및 상기 제3 스위치는 턴온시키고, 상기 제2 스위치는 턴오프시키고,

상기 제4 동작 모드에서 상기 제1 스위치 내지 상기 제3 스위치를 턴온시키며,

상기 제5 동작 모드에서 상기 제1 스위치 및 상기 제3 스위치는 턴온시키고, 상기 제2 스위치는 턴오프시키는, 브릿지리스 인터리브 역률보정회로.

- 인덕터가 구비된 복수의 부스트 레그와, 적어도 하나의 상기 부스트 레그와 연결되는 복수의 스위칭 회로와, 상기 인덕터로부터 전달된 출력 전류를 감지하는 단일 전류 센서를 포함하는 브릿지리스 인터리브 역률보정회로의 동작 방법에 있어서,

상기 복수의 스위칭 회로는,

라인 전압의 소정 주기동안 변화되는 듀티 사이클 값을 미리 정해진 기준값과 비교한 결과에 따라 각각의 스위치 회로의 동작 모드가 제어되고,

상기 단일 전류 센서는,

상기 각각의 스위치 회로의 온오프 조합에 따라 상기 출력 전류를 측정할지 여부가 결정되는, 브릿지리스 인터리브 역률보정회로의 구동 방법. - 제10항에 있어서,

상기 부스트 레그는,

입력 전원과 연결되며 인덕터를 포함하는 적어도 하나의 단일 부스트 레그와, 상기 입력 전원과 연결되며 인덕터 및 저속 다이오드를 포함하는 복수의 병합 부스트 레그를 포함하며,

상기 스위치 회로는,

하나의 상기 단일 부스트 레그와 연결되는 단일 스위치 회로와, 적어도 두 개의 상기 병합 부스트 레그와 연결되는 병합 스위치 회로를 포함하는, 브릿지리스 인터리브 역률보정회로의 구동 방법.

- 제10항에 있어서,

상기 스위치 회로는,

상기 라인 전압의 1/2주기동안 변화되는 듀티 사이클 값이 미리 정해진 기준값보다 작은 경우, 제1 동작 모드 내지 제3 동작 모드 중 어느 하나의 동작 모드로 동작되고,

상기 듀티 사이클 값이 상기 기준값보다 큰 경우, 제4 동작 모드 내지 제6 동작 모드 중 어느 하나의 동작 모드로 동작되는, 브릿지리스 인터리브 역률보정회로의 구동 방법.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020160084209 | 2016-07-04 | ||

| KR20160084209 | 2016-07-04 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020190003060A Division KR102068923B1 (ko) | 2019-01-10 | 2019-01-10 | 브릿지리스 인터리브 역률보정회로 및 그 구동방법 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20180004677A true KR20180004677A (ko) | 2018-01-12 |

Family

ID=61001151

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020170085018A KR20180004677A (ko) | 2016-07-04 | 2017-07-04 | 브릿지리스 인터리브 역률보정회로 및 그 구동방법 |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR20180004677A (ko) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2020159640A1 (en) * | 2019-01-28 | 2020-08-06 | Murata Manufacturing Co., Ltd. | Bootstrap pre-charge circuit in totem-pole power factor correction converter |

| CN111917279A (zh) * | 2020-09-23 | 2020-11-10 | 苏州瑞驱电动科技有限公司 | 一种适用于多路交错并联Boost变换器的参数设计 |

| CN113647003A (zh) * | 2019-03-29 | 2021-11-12 | 株式会社村田制作所 | 交错式功率因数校正电路的自调谐调节器和自调谐调节方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20080002444A1 (en) * | 2006-06-30 | 2008-01-03 | Sampat Shekhawat | High-efficiency power converter system |

| US8385032B1 (en) * | 2011-08-23 | 2013-02-26 | Futurewei Technologies, Inc. | High efficiency bridgeless PFC converter and method |

| KR101303341B1 (ko) * | 2012-05-07 | 2013-09-03 | 주식회사 동아일렉콤 | 브리지리스 역률보상 회로 |

-

2017

- 2017-07-04 KR KR1020170085018A patent/KR20180004677A/ko active Application Filing

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20080002444A1 (en) * | 2006-06-30 | 2008-01-03 | Sampat Shekhawat | High-efficiency power converter system |

| US8385032B1 (en) * | 2011-08-23 | 2013-02-26 | Futurewei Technologies, Inc. | High efficiency bridgeless PFC converter and method |

| KR101303341B1 (ko) * | 2012-05-07 | 2013-09-03 | 주식회사 동아일렉콤 | 브리지리스 역률보상 회로 |

Non-Patent Citations (4)

| Title |

|---|

| Hee-Jun Kim, The 2014 International Power Electronics Conference * |

| Khairul Safuan Bin Muhammad, IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 62, NO. 5, MAY 2015 * |

| Woojin Choi, 전력전자학술대회논문집, 2016.7, 363-364 (2 pages) * |

| 최우진, 전력전자학술대회논문집, 2017.7, 24-25 (2 pages) * |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2020159640A1 (en) * | 2019-01-28 | 2020-08-06 | Murata Manufacturing Co., Ltd. | Bootstrap pre-charge circuit in totem-pole power factor correction converter |

| US11949328B2 (en) | 2019-01-28 | 2024-04-02 | Murata Manufacturing Co., Ltd. | Bootstrap pre-charge circuit in totem-pole power factor correction converter |

| CN113647003A (zh) * | 2019-03-29 | 2021-11-12 | 株式会社村田制作所 | 交错式功率因数校正电路的自调谐调节器和自调谐调节方法 |

| CN111917279A (zh) * | 2020-09-23 | 2020-11-10 | 苏州瑞驱电动科技有限公司 | 一种适用于多路交错并联Boost变换器的参数设计 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP2248249B1 (en) | Electronic driver circuit and method | |

| US9294001B2 (en) | Power converter with dead-time control function | |

| US8026704B2 (en) | System and method for controlling a converter | |

| US20110109283A1 (en) | System and method for controlling a converter | |

| WO2010131496A1 (ja) | Pfcコンバータ | |

| US20130301309A1 (en) | Control circuits and control methods for flyback converters and ac-dc power converters thereof | |

| TW201924200A (zh) | 切換邊界模式交錯電力轉換器之數位控制 | |

| KR20120020080A (ko) | 브리지리스 역률 보상을 위한 방법 및 장치 | |

| CN102810984A (zh) | 一种开关电源电路 | |

| US20120014149A1 (en) | Power conversion apparatus and method | |

| US8773875B2 (en) | Power conversion apparatus | |

| US20170025969A1 (en) | Synchronous rectifier phase control to improve load efficiency | |

| Zhang et al. | A digital adaptive discontinuous current source driver for high-frequency interleaved boost PFC converters | |

| CN109067178B (zh) | 一种同相升降压变换器模式平滑切换的控制系统及方法 | |

| US8824180B2 (en) | Power conversion apparatus | |

| US20200220452A1 (en) | Enhanced power factor correction | |

| TW201924198A (zh) | 具有降低交越失真之切換邊界模式交錯電力轉換器之數位控制 | |

| CN106059294B (zh) | 一种开关电源及变换方法 | |

| US20150171746A1 (en) | Buck type dc-to-dc converter and method of operating the same | |

| Jang et al. | A novel active-current-sharing method for interleaved resonant converters | |

| CN110572041B (zh) | 一种双有源全桥变流器的双边pwm加移相控制方法 | |

| KR20180004677A (ko) | 브릿지리스 인터리브 역률보정회로 및 그 구동방법 | |

| KR102068923B1 (ko) | 브릿지리스 인터리브 역률보정회로 및 그 구동방법 | |

| EP2567453B1 (en) | A controller and a method for a dc converter, and also a dc converter | |

| Channappanavar et al. | Current sensorless Power Factor correction circuit using FPGA |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application |

Patent event code: PA01091R01D Comment text: Patent Application Patent event date: 20170704 |

|

| PA0201 | Request for examination | ||

| PG1501 | Laying open of application | ||

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

Comment text: Notification of reason for refusal Patent event date: 20180725 Patent event code: PE09021S01D |

|

| E601 | Decision to refuse application | ||

| PE0601 | Decision on rejection of patent |

Patent event date: 20181025 Comment text: Decision to Refuse Application Patent event code: PE06012S01D Patent event date: 20180725 Comment text: Notification of reason for refusal Patent event code: PE06011S01I |

|

| E601 | Decision to refuse application | ||

| E801 | Decision on dismissal of amendment | ||

| PE0601 | Decision on rejection of patent |

Patent event date: 20181212 Comment text: Decision to Refuse Application Patent event code: PE06012S01D Patent event date: 20180725 Comment text: Notification of reason for refusal Patent event code: PE06011S01I |

|

| PE0801 | Dismissal of amendment |

Patent event code: PE08012E01D Comment text: Decision on Dismissal of Amendment Patent event date: 20181212 Patent event code: PE08011R01I Comment text: Amendment to Specification, etc. Patent event date: 20181123 Patent event code: PE08011R01I Comment text: Amendment to Specification, etc. Patent event date: 20180820 |

|

| A107 | Divisional application of patent | ||

| PA0107 | Divisional application |

Comment text: Divisional Application of Patent Patent event date: 20190110 Patent event code: PA01071R01D |