KR20090068511A - 3차원 구조의 직렬 l-c 공진기 및 이를 이용한광대역통과여파기 - Google Patents

3차원 구조의 직렬 l-c 공진기 및 이를 이용한광대역통과여파기 Download PDFInfo

- Publication number

- KR20090068511A KR20090068511A KR1020070136164A KR20070136164A KR20090068511A KR 20090068511 A KR20090068511 A KR 20090068511A KR 1020070136164 A KR1020070136164 A KR 1020070136164A KR 20070136164 A KR20070136164 A KR 20070136164A KR 20090068511 A KR20090068511 A KR 20090068511A

- Authority

- KR

- South Korea

- Prior art keywords

- pattern portion

- conductive layer

- substrate

- resonator

- series

- Prior art date

Links

- 239000003990 capacitor Substances 0.000 claims abstract description 28

- 230000000903 blocking effect Effects 0.000 claims abstract description 6

- 239000000758 substrate Substances 0.000 claims description 74

- 230000005540 biological transmission Effects 0.000 claims description 26

- 230000008878 coupling Effects 0.000 claims description 7

- 238000010168 coupling process Methods 0.000 claims description 7

- 238000005859 coupling reaction Methods 0.000 claims description 7

- 238000006243 chemical reaction Methods 0.000 abstract description 6

- 238000013461 design Methods 0.000 abstract description 4

- 238000000034 method Methods 0.000 abstract description 3

- 238000010586 diagram Methods 0.000 description 18

- 238000004088 simulation Methods 0.000 description 14

- 238000003780 insertion Methods 0.000 description 7

- 230000037431 insertion Effects 0.000 description 7

- 238000005516 engineering process Methods 0.000 description 3

- 238000004891 communication Methods 0.000 description 2

- 238000010295 mobile communication Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 230000005672 electromagnetic field Effects 0.000 description 1

- 238000011160 research Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03B—GENERATION OF OSCILLATIONS, DIRECTLY OR BY FREQUENCY-CHANGING, BY CIRCUITS EMPLOYING ACTIVE ELEMENTS WHICH OPERATE IN A NON-SWITCHING MANNER; GENERATION OF NOISE BY SUCH CIRCUITS

- H03B5/00—Generation of oscillations using amplifier with regenerative feedback from output to input

- H03B5/18—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising distributed inductance and capacitance

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H7/00—Multiple-port networks comprising only passive electrical elements as network components

- H03H7/01—Frequency selective two-port networks

- H03H7/0115—Frequency selective two-port networks comprising only inductors and capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01P—WAVEGUIDES; RESONATORS, LINES, OR OTHER DEVICES OF THE WAVEGUIDE TYPE

- H01P1/00—Auxiliary devices

- H01P1/20—Frequency-selective devices, e.g. filters

- H01P1/201—Filters for transverse electromagnetic waves

- H01P1/203—Strip line filters

- H01P1/20327—Electromagnetic interstage coupling

- H01P1/20354—Non-comb or non-interdigital filters

- H01P1/20381—Special shape resonators

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01P—WAVEGUIDES; RESONATORS, LINES, OR OTHER DEVICES OF THE WAVEGUIDE TYPE

- H01P1/00—Auxiliary devices

- H01P1/20—Frequency-selective devices, e.g. filters

- H01P1/201—Filters for transverse electromagnetic waves

- H01P1/203—Strip line filters

- H01P1/2039—Galvanic coupling between Input/Output

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H7/00—Multiple-port networks comprising only passive electrical elements as network components

- H03H7/01—Frequency selective two-port networks

- H03H7/075—Ladder networks, e.g. electric wave filters

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H7/00—Multiple-port networks comprising only passive electrical elements as network components

- H03H7/01—Frequency selective two-port networks

- H03H7/17—Structural details of sub-circuits of frequency selective networks

- H03H7/1741—Comprising typical LC combinations, irrespective of presence and location of additional resistors

- H03H7/175—Series LC in series path

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H7/00—Multiple-port networks comprising only passive electrical elements as network components

- H03H7/01—Frequency selective two-port networks

- H03H7/17—Structural details of sub-circuits of frequency selective networks

- H03H7/1741—Comprising typical LC combinations, irrespective of presence and location of additional resistors

- H03H7/1775—Parallel LC in shunt or branch path

Landscapes

- Physics & Mathematics (AREA)

- Electromagnetism (AREA)

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Control Of Motors That Do Not Use Commutators (AREA)

- Filters And Equalizers (AREA)

Abstract

Description

Claims (7)

- 소정의 유전율을 가진 유전성 기판;상기 기판의 일면의 일부분 상에 소정의 패턴으로 형성된 직렬 L-C 공진기용 제1 도전층의 패턴부;상기 기판의 타면의 일부분 상에 형성된 접지용 제2 도전층의 패턴부를 포함하며,상기 제1 도전층의 패턴부는, 인덕터를 나타내는 전기적 길이와, 커패시터를 나타내는 패턴으로 구성된 3차원 구조를 갖고,상기 제1 도전층의 패턴부는, 대향하는 제1변 중 일측 제1변의 일부분이 사각형상으로 제거된 사각형 홈부를 가지는 사각형 제1 패턴부; 상기 홈부 내에 배치되며, 상기 홈부의 대응하는 3변으로부터 동일한 간격을 두고 각각 이격하는 3변을 가지는 사각형 제2 패턴부; 상기 제1 패턴부와 일체로 연결되며, 상기 제1 패턴부의 타측 제1변의 일부분으로부터 상기 기판의 인접 변을 향하여 소정의 폭과 길이를 가진 직선의 형태로 연장하는 제3 패턴부; 및 상기 제2 패턴부와 일체로 연결되며, 상기 제2 패턴부의 나머지 1변의 일부분으로부터 상기 기판의 인접 변을 향하여 소정의 폭과 길이를 가진 직선의 형태로 연장하는 제4 패턴부를 포함하고,상기 제2 패턴부는 상기 기판의 관통공 내의 도전층에 의해 상기 제2 도전층의 패턴부와 전기적으로 연결된 것을 특징으로 하는 3차원 구조의 직렬 L-C 공진기.

- 소정의 유전율을 가진 유전성 기판;상기 기판의 상면의 일부분 상에 형성된, 복수개 직렬 연결된 제1항의 직렬 L-C 공진기용 제1 도전층의 패턴부;상기 기판의 상면의 일부분 상에 형성되어 상기 복수개의 직렬 L-C 공진기의 각각에 전기적으로 연결되며, 인덕터를 나타내는 단락 스터브와 커패시터를 나타내는 개방 스터브를 가진 복수개의 병렬 L-C 공진기용 제1 도전층의 패턴부; 및상기 기판의 타면의 일부분 상에 형성된 접지용 제2 도전층의 패턴부를 포함하는 것을 특징으로 하는 3차원 구조의 직렬 L-C 공진기를 이용한 광대역통과 여파기.

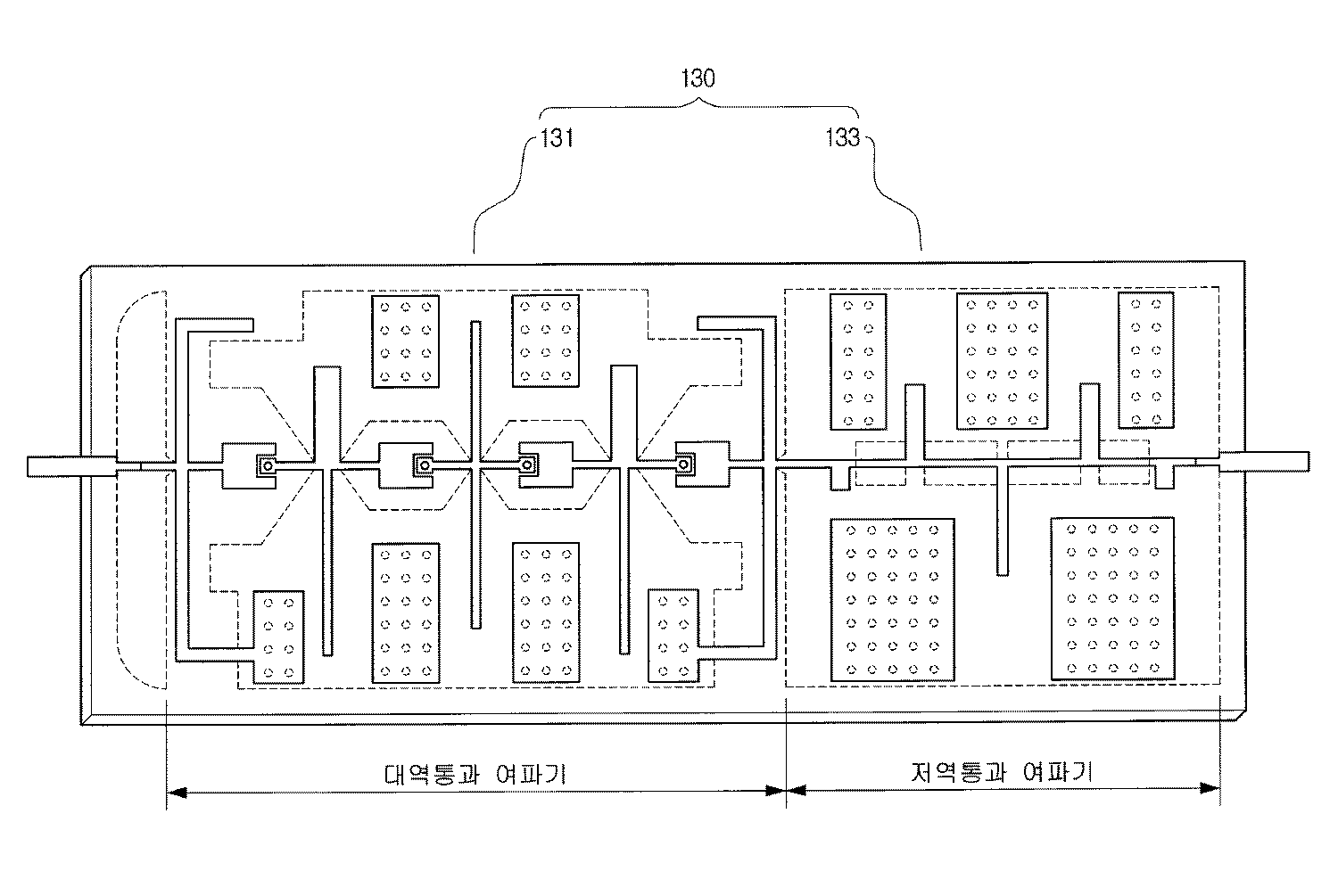

- 소정의 유전율을 가진 유전성 기판;상기 기판의 상면의 일부분 상에 형성된, 복수개 직렬 연결된 제1항의 직렬 L-C 공진기용 제1 도전층의 패턴부와, 상기 기판의 상면의 일부분 상에 형성되어 상기 복수개의 직렬 L-C 공진기의 각각에 전기적으로 연결되며, 인덕터를 나타내는 단락 스터브와 커패시터를 나타내는 개방 스터브를 가진 복수개의 병렬 L-C 공진기용 제1 도전층의 패턴부를 포함하는 대역통과 여파기용 제1 도전층의 패턴부;상기 대역통과 여파기의 대역저지특성을 향상시키기 위해, 상기 대역통과 여 파기용 제1 도전층의 패턴부의 후단에 전기적으로 연결되도록 상기 기판의 상면의 일부분 상에 형성되며, 인덕터를 나타내는 전송선로와 커패시터를 나타내는 개방 스터브를 가진 저역통과 여파기용 제1 도전층의 패턴부; 및상기 기판의 타면의 일부분 상에 형성된 접지용 제2 도전층의 패턴부를 포함하는 것을 특징으로 하는 3차원 구조의 직렬 L-C 공진기를 이용한 광대역통과 여파기.

- 제2항 또는 제3항에 있어서, 상기 병렬 L-C 공진기의 일부분의 단락 스터브와 개방 스터브는, 해당하는 접지용 제2 도전층의 패턴부와 동일 수직선 상에 위치하는 마이크로 스트립 구조를 가지고, 상기 병렬 L-C 공진기의 다른 일부분의 단락 스터브와 개방 스터브는, 해당하는 접지용 제2 도전층의 패턴부와 동일 수직선 상에 위치하지 않는 서스펜디드 스트립 구조를 갖는 것을 특징으로 하는 3차원 구조의 직렬 L-C 공진기를 이용한 광대역통과 여파기.

- 제3항에 있어서, 상기 저역통과 여파기용 제1 도전층의 패턴부의 전송선로는, 해당하는 접지용 제2 도전층의 패턴와 동일 수직선 상에 위치하지 않는 서스펜디드 스트립 구조를 가지고, 상기 저역통과 여파기용 제1 도전층의 패턴부의 개방 스터브는, 해당하는 접지용 제2 도전층의 패턴부와 동일 수직선 상에 위치하는 마 이크로 스트립 구조를 가지는 것을 특징으로 하는 3차원 구조의 직렬 L-C 공진기를 이용한 광대역통과 여파기.

- 제2항 또는 제3항에 있어서, 상기 대역통과 여파기의 접지용 제1 도전층의 패턴부는, 전송선로 사이에 발생되는 커플링 값을 최소화하기 위하여, 상기 대역통과 여파기의 해당 스터브 사이의 기판의 상면 상에 배치된 것을 특징으로 하는 3차원 구조의 직렬 L-C 공진기를 이용한 광대역통과 여파기.

- 제3항에 있어서, 상기 저역통과 여파기의 접지용 제1 도전층의 패턴부는, 전송선로 사이의 발생되는 커플링 값을 최소화하기 위하여, 상기 저역통과 여파기의 해당 스터브 사이의 기판의 상면 상에 배치된 것을 특징으로 하는 3차원 구조의 직렬 L-C 공진기를 이용한 광대역통과 여파기.

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020070136164A KR100957446B1 (ko) | 2007-12-24 | 2007-12-24 | 3차원 구조의 직렬 l-c 공진기 및 이를 이용한광대역통과여파기 |

| US12/810,290 US8531253B2 (en) | 2007-12-24 | 2008-12-16 | Serial L-C resonator with three-dimensional structure and ultra-wide bandpass filter using the same |

| PCT/KR2008/007446 WO2009082117A1 (en) | 2007-12-24 | 2008-12-16 | Serial l-c resonator with three-dimensional structure and ultra-wide bandpass filter using the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020070136164A KR100957446B1 (ko) | 2007-12-24 | 2007-12-24 | 3차원 구조의 직렬 l-c 공진기 및 이를 이용한광대역통과여파기 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20090068511A true KR20090068511A (ko) | 2009-06-29 |

| KR100957446B1 KR100957446B1 (ko) | 2010-05-11 |

Family

ID=40801366

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020070136164A KR100957446B1 (ko) | 2007-12-24 | 2007-12-24 | 3차원 구조의 직렬 l-c 공진기 및 이를 이용한광대역통과여파기 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8531253B2 (ko) |

| KR (1) | KR100957446B1 (ko) |

| WO (1) | WO2009082117A1 (ko) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2924800A1 (en) | 2014-03-28 | 2015-09-30 | Innertron, Inc. | Resonator and filter having the same |

| WO2021261923A1 (ko) * | 2020-06-23 | 2021-12-30 | 삼성전자 주식회사 | 무선 통신 시스템에서 안테나 필터 및 이를 포함하는 전자 장치 |

| US11381214B2 (en) | 2019-09-10 | 2022-07-05 | Korea University Research And Business Foundation | Frequency filter circuit |

| CN116259939A (zh) * | 2023-01-30 | 2023-06-13 | 电子科技大学长三角研究院(湖州) | 一种基于氧化铝陶瓷工艺的悬置带线高通滤波器 |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20140055215A1 (en) * | 2012-08-23 | 2014-02-27 | Harris Corporation | Distributed element filters for ultra-broadband communications |

| US9165723B2 (en) | 2012-08-23 | 2015-10-20 | Harris Corporation | Switches for use in microelectromechanical and other systems, and processes for making same |

| US9053873B2 (en) | 2012-09-20 | 2015-06-09 | Harris Corporation | Switches for use in microelectromechanical and other systems, and processes for making same |

| US9053874B2 (en) | 2012-09-20 | 2015-06-09 | Harris Corporation | MEMS switches and other miniaturized devices having encapsulating enclosures, and processes for fabricating same |

| US8907849B2 (en) | 2012-10-12 | 2014-12-09 | Harris Corporation | Wafer-level RF transmission and radiation devices |

| US9203133B2 (en) | 2012-10-18 | 2015-12-01 | Harris Corporation | Directional couplers with variable frequency response |

| CN105229645B (zh) * | 2013-05-14 | 2018-05-15 | 株式会社村田制作所 | 电感器的仿真方法及电感器的非线性等效电路模型 |

| DE102015006739A1 (de) | 2015-05-22 | 2016-11-24 | Kathrein-Austria Ges.M.B.H. | Hochfrequenzleitersystem mit leitungsgebundener HF-Durchführung |

| CN105024124B (zh) * | 2015-08-13 | 2018-03-06 | 电子科技大学 | 一种新型多枝节多模谐振器及基于其的微带超宽带带通滤波器 |

| JP6723076B2 (ja) | 2016-05-31 | 2020-07-15 | キヤノン株式会社 | フィルタ |

| US10378947B2 (en) | 2016-07-07 | 2019-08-13 | Rosemount Tank Radar Ab | Radar level gauge system with feeding comprising an electrical filter |

| US10480985B2 (en) | 2017-09-29 | 2019-11-19 | Rosemount Tank Radar Ab | Explosion proof radar level gauge |

| CN112421219B (zh) * | 2020-10-26 | 2022-11-29 | 京信通信技术(广州)有限公司 | 散射抑制结构、电磁边界、低频辐射单元及天线 |

| US12009849B2 (en) * | 2021-08-25 | 2024-06-11 | Apple Inc. | Distributed-element filter for mmWave frequencies |

| CN114824701B (zh) * | 2022-04-20 | 2024-01-19 | 中国电子科技集团公司第三十六研究所 | 一种双频滤波器 |

| CN115377632A (zh) * | 2022-07-13 | 2022-11-22 | 广州司南技术有限公司 | 包括具有多边形横截面的管状导电外壳的频率选择装置 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07283679A (ja) * | 1994-04-04 | 1995-10-27 | Advantest Corp | マイクロ波帯用フィルタ |

| JP2002026603A (ja) | 2000-07-07 | 2002-01-25 | Mitsubishi Electric Corp | バンドパスフィルタ |

| KR20020085976A (ko) * | 2001-05-10 | 2002-11-18 | 주식회사 스마텍 | 결합형 라인 공진기를 갖는 적층형 유전체 필터 |

| KR100608316B1 (ko) * | 2004-12-28 | 2006-08-08 | 전자부품연구원 | 대역통과필터 |

| TW200701544A (en) * | 2005-04-28 | 2007-01-01 | Kyocera Corp | Bandpass filter and wireless communications equipment using same |

| JP4523478B2 (ja) | 2005-04-28 | 2010-08-11 | 京セラ株式会社 | 帯域通過フィルタ及び高周波モジュール、並びにこれを用いた無線通信機器 |

| JP2007243462A (ja) | 2006-03-07 | 2007-09-20 | Matsushita Electric Works Ltd | バンドパスフィルタ及び共振器 |

| KR20070034316A (ko) * | 2005-09-23 | 2007-03-28 | 삼성전자주식회사 | 이중 격자 구조를 이용한 대역 저지 필터 |

-

2007

- 2007-12-24 KR KR1020070136164A patent/KR100957446B1/ko active IP Right Grant

-

2008

- 2008-12-16 US US12/810,290 patent/US8531253B2/en active Active

- 2008-12-16 WO PCT/KR2008/007446 patent/WO2009082117A1/en active Application Filing

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2924800A1 (en) | 2014-03-28 | 2015-09-30 | Innertron, Inc. | Resonator and filter having the same |

| KR20150113448A (ko) | 2014-03-28 | 2015-10-08 | 주식회사 이너트론 | 공진기 및 이를 포함하는 필터 |

| US9641148B2 (en) | 2014-03-28 | 2017-05-02 | Innertron, Inc. | Resonator and filter having the same |

| US11381214B2 (en) | 2019-09-10 | 2022-07-05 | Korea University Research And Business Foundation | Frequency filter circuit |

| WO2021261923A1 (ko) * | 2020-06-23 | 2021-12-30 | 삼성전자 주식회사 | 무선 통신 시스템에서 안테나 필터 및 이를 포함하는 전자 장치 |

| CN116259939A (zh) * | 2023-01-30 | 2023-06-13 | 电子科技大学长三角研究院(湖州) | 一种基于氧化铝陶瓷工艺的悬置带线高通滤波器 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20100277259A1 (en) | 2010-11-04 |

| KR100957446B1 (ko) | 2010-05-11 |

| US8531253B2 (en) | 2013-09-10 |

| WO2009082117A1 (en) | 2009-07-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100957446B1 (ko) | 3차원 구조의 직렬 l-c 공진기 및 이를 이용한광대역통과여파기 | |

| Li et al. | Synthesis design of ultra-wideband bandpass filters with composite series and shunt stubs | |

| US8970327B2 (en) | Filter based on a combined via structure | |

| TW201006030A (en) | Band-pass filter circuit and multi-layer structure and method thereof | |

| KR100999512B1 (ko) | 전자기 밴드갭 구조물 | |

| US9583807B2 (en) | Hybrid resonators in multilayer substrates and filters based on these resonators | |

| JPWO2018100923A1 (ja) | Lc共振器およびlcフィルタ | |

| Han et al. | Development of packaged ultra-wideband bandpass filters | |

| CN204244192U (zh) | Lc滤波器电路及高频模块 | |

| Faraghi et al. | Small microstrip low-pass filter by using novel defected ground structure for UWB applications | |

| del Castillo Velazquez-Ahumada et al. | Design of compact low-pass elliptic filters using double-sided MIC technology | |

| US7782157B2 (en) | Resonant circuit, filter circuit, and multilayered substrate | |

| KR101216433B1 (ko) | 메타매질을 이용한 고역 통과 필터 | |

| JP5578440B2 (ja) | 差動伝送線路 | |

| Boutejdar et al. | A novel band-stop filter using octagonal-shaped patterned ground structures along with interdigital and compensated capacitors | |

| Dai et al. | A miniaturized and low insertion loss LTCC filter with two finite transmission zeros for bluetooth application | |

| Hammed et al. | Miniaturized high-order UWB bandpass filter using third-order E-shape microstrip structure | |

| KR20170116436A (ko) | 앰프 모듈 | |

| CN219246895U (zh) | 一种悬置线高通滤波器 | |

| JP2013005121A (ja) | 高周波フィルタ | |

| Liu et al. | Miniaturized quarter-wavelength resonator for common-mode filter based on pattern ground structure | |

| Balalem et al. | Bandpass filters on a modified multilayer coplanar line | |

| Park et al. | New design technique for wide band pass filters using direct frequency conversion design method | |

| Kumar et al. | Control of band stop responses of very compact size microstrip filter of improved Q factor & sharp transition by using hexagonal transmetal DGS | |

| KR101607498B1 (ko) | 스퍼라인 슬롯을 이용한 듀얼모드 대역저지 필터 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application |

Patent event code: PA01091R01D Comment text: Patent Application Patent event date: 20071224 |

|

| PA0201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

Comment text: Notification of reason for refusal Patent event date: 20081216 Patent event code: PE09021S01D |

|

| PG1501 | Laying open of application | ||

| E90F | Notification of reason for final refusal | ||

| PE0902 | Notice of grounds for rejection |

Comment text: Final Notice of Reason for Refusal Patent event date: 20090630 Patent event code: PE09021S02D |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

Patent event code: PE07011S01D Comment text: Decision to Grant Registration Patent event date: 20100428 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

Comment text: Registration of Establishment Patent event date: 20100503 Patent event code: PR07011E01D |

|

| PR1002 | Payment of registration fee |

Payment date: 20100503 End annual number: 3 Start annual number: 1 |

|

| PG1601 | Publication of registration | ||

| FPAY | Annual fee payment |

Payment date: 20130430 Year of fee payment: 4 |

|

| PR1001 | Payment of annual fee |

Payment date: 20130430 Start annual number: 4 End annual number: 4 |

|

| FPAY | Annual fee payment |

Payment date: 20140502 Year of fee payment: 5 |

|

| PR1001 | Payment of annual fee |

Payment date: 20140502 Start annual number: 5 End annual number: 5 |

|

| FPAY | Annual fee payment |

Payment date: 20150506 Year of fee payment: 6 |

|

| PR1001 | Payment of annual fee |

Payment date: 20150506 Start annual number: 6 End annual number: 6 |

|

| FPAY | Annual fee payment |

Payment date: 20160502 Year of fee payment: 7 |

|

| PR1001 | Payment of annual fee |

Payment date: 20160502 Start annual number: 7 End annual number: 7 |

|

| FPAY | Annual fee payment |

Payment date: 20170508 Year of fee payment: 8 |

|

| PR1001 | Payment of annual fee |

Payment date: 20170508 Start annual number: 8 End annual number: 8 |

|

| FPAY | Annual fee payment |

Payment date: 20180503 Year of fee payment: 9 |

|

| PR1001 | Payment of annual fee |

Payment date: 20180503 Start annual number: 9 End annual number: 9 |

|

| FPAY | Annual fee payment |

Payment date: 20180504 Year of fee payment: 10 |

|

| PR1001 | Payment of annual fee |

Payment date: 20180504 Start annual number: 10 End annual number: 10 |

|

| PR1001 | Payment of annual fee |

Payment date: 20200504 Start annual number: 11 End annual number: 11 |

|

| PR1001 | Payment of annual fee |

Payment date: 20240430 Start annual number: 15 End annual number: 15 |