KR20080025053A - 멀티-프로세서 시스템을 위한 메모리 배열 - Google Patents

멀티-프로세서 시스템을 위한 메모리 배열 Download PDFInfo

- Publication number

- KR20080025053A KR20080025053A KR1020077028352A KR20077028352A KR20080025053A KR 20080025053 A KR20080025053 A KR 20080025053A KR 1020077028352 A KR1020077028352 A KR 1020077028352A KR 20077028352 A KR20077028352 A KR 20077028352A KR 20080025053 A KR20080025053 A KR 20080025053A

- Authority

- KR

- South Korea

- Prior art keywords

- memory

- queues

- queue

- bank

- functional unit

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1605—Handling requests for interconnection or transfer for access to memory bus based on arbitration

- G06F13/1652—Handling requests for interconnection or transfer for access to memory bus based on arbitration in a multiprocessor architecture

- G06F13/1657—Access to multiple memories

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/76—Architectures of general purpose stored program computers

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Abstract

멀티-프로세서 시스템 또는 어레이에 적합한 하드웨어 메모리 아키텍처 또는 배열이 제안된다. 본 발명은 기능 유닛(연산 유닛) 및 하나 이상의 메모리 간에 부가되고, 상기 기능 유닛은 하나 이상의 메모리 큐에 쓰기 또는 읽기를 위하여 액세스한다.

멀티-프로세서 시스템(MULTI-PROCESSOR SYSTEM), 메모리 배열(A MEMORY ARRANGEMENT)

Description

본 발명은 멀티-프로세서 시스템에서 이용하기에 적합한 메모리 배열에 관한 것이다.

병렬성이 높은 아키텍처들(highly parallel architectures)은 연산(computation)을 병렬화(paralleizing)하여 높은 성능을 달성한다. 높은 병렬성(parallelism)은 높은 데이터 스루풋(throughput)에 의해 지원되어야 한다. 어떤 연산은 메모리로부터 데이터를 읽거나 메모리에 결과들을 쓰는 것이 필요하기 때문이다. 높은 데이터 스루풋을 달성하기 위하여, 상기 아키텍처들의 메모리 조직(organization)은 동시에 멀티플(multiple) 데이터 액세스를 유지해야 한다. 그렇지 않으면, 상기 아키텍처의 성능이 매우 저하된다.

높은 메모리 대역폭(bandwidth)을 제공하는 하나의 방법은 진정한(true) 멀티포트 메모리(도1)를 설계하는 것이다. 상기 멀티-포트 메모리는 N(N=포트의 수) 데이터를 매 사이클마다 어떤 제한(constraint)도 없이 읽거나 쓸 수 있다. 하지만 N이 2보다 큰 경우, 메모리 시스템의 비용이 매우 높아진다. 면적(area), 시간 지연(delay), 및 전력(power)이 포트 수의 증가와 함께 비선형적으로(non- linearly) 증가할 것이다. 실제로(in practice), 단지 듀얼 포트 에스램(dual-port SRAM)까지가(up to) 널리 이용된다. 어플리케이션들을 보면, 전력 및 비용이 핵심 설계 기준(key design metrics) 이고, 진정한 멀티-포트 메모리는 실용적인(viable) 옵션이 아니다.

멀티플 데이터 액세스를 제공하는 대안(alternative way)은 의사 멀티-포트 시스템(pseudo multi-port system)(도2)을 형성하는 몇 개의 싱글 포트 메모리 뱅크를 모으는(assemble) 것이다. 이러한 접근 방법은 진정한 멀티-포트 접근보다 훨씬 저렴하고 신속하다. 이상적으로는, 동일한 사이클에 있는 모든 데이터 액세스들이 다른 뱅크로 간다면, 진정한 멀티-포트처럼 작동하는 것이고, 동시에 멀티플 메모리 액세스들을 제공할 수 있다. 그러나, 실제로는 몇 개의 메모리 액세스들이 동일한 사이클에 있는 같은 뱅크로 가기가 쉽고, 반면에, 메모리 뱅크는 하나의(single) 사이클에 단지 하나의 메모리 요청을 서비스할 수 있다. 상기 시스템은 모든 메모리 요청들이 서비스될 때까지 대기하도록 정지된다. 이것은 메모리 충돌(conflict)이라고 불리며, 성능을 심각하게 감소시킬 수 있다.

상기 멀티-뱅크 메모리 조직과 관련된 문제점은 어떻게 어드레스 공간이 멀티플 뱅크들 간에서 분할되는가 하는 것이다. 상기 어드레스 공간은 뱅크들 간에 몇 개의 큰 조각들로 분할될 수도 있고, 뱅크들간에 인터리브(interleaved) 될 수도 있다. 상기 첫 번째 방법은 많은 독립적인 데이터 구조들이 있을 때 우수하다. 그러므로 데이터 구조 각각은 충돌 없이 동시에 접근될 수 있도록 다른 뱅크에 할당될 수 있다. 상기 두 번째 방법은 제한된 데이터 구조들만이 있을 때 성능이 높 다. 이 때, 제한된 데이터 구조 내에는 높은 대역폭이 요구된다. 이것은 많은 멀티미디어 및 전기통신 어플리케이션들의 경우이다. 그러므로 상기 인터리브된 멀티-뱅크 메모리가 더 자주 이용된다. 예를 들면, TI's 64x 시리즈는 두 개의 포트의 데이터 액세스를 제공하는 8 메모리 뱅크로 구성된 1 단계 데이터 캐시를 특징으로 한다(TI Inc.."TMS320C64x 기술적 개관", www.ti.com,2005). 상기 데이터 포트들 및 상기 데이터 뱅크들은 8x2 풀 크로스바(full crossbar)를 통해 연결된다. 데이터 레이아웃(data layout)을 주의 깊게 배열함으로써, 그리고 8개 뱅크들 중 2개의 데이터를 액세스(accessing)함으로써, 메모리 충돌은 낮은 수준으로 제어될 수 있다.

본 발명에서 고려되는 시스템들에서, 메모리 충돌을 감소시키는 일(task)은 매우 어렵다. 더 높은 수준의 병렬성(parallelism)을 유지하기 위하여, 전형적인 디지털 시그널 프로세서(digital signal processor;DSP)보다 훨씬 많은 포트를 제공하기 때문이다. 예를 들면, 8x8 어레이(array)에서는 8개 이상의 메모리 포트들을 제공할 필요가 있다. 만약, TI's 64x DSP로 동일한 뱅크 대 포트 비율(bank-to-port ratio)를 유지하려고 하면, 뱅크들의 수는 32개가 될 것이다. 상기 필요한 32x8 크로스바(crossbar)는 TI's 64x DSP의 8x2 의 크로스바보다 16배 비용이 많이 들 수 있고, 전력을 소비할 수 있다. 그러므로 본 발명에서 고려되는 시스템을 위해, 하드웨어 및/또는 소프트웨어 기술들을 이용하여, 더 적은 뱅크 수에 기초하여 상기 메모리 충돌을 감소시키는 더 효율적인 해결책을 찾는 것이 더 나은 방법이다.

본 발명의 일측은, 미국 가출원 번호 60/614379에 개시된 것처럼, 멀티-프로세서 시스템들 및 어레이들에 적합한 하드웨어 메모리 아키텍처 또는 배열을 제안한다. 상기 하드웨어 메모리 아키텍처 또는 배열은 하나 이상의 메모리 큐를 포함한다.

본 발명은 기능 유닛(연산 유닛) 및 하나 이상의 메모리 간에 부가되고, 상기 기능 유닛은 쓰기 또는 읽기를 위하여 하나 이상의 메모리 큐에 액세스한다.

가장 기본적인 실시예에 있어서, 상기 발명은 둘 이상의 기능 유닛, 하나 이상의 메모리 장치, 기능 유닛 각각을 위한 하나 이상의 메모리 큐를 포함하고, 메모리 큐 각각은 기능 유닛과 관련되고, 상기 하나 이상의 메모리 장치는 둘 이상의 메모리 큐들과 연결된다.

상기 멀티-프로세서 시스템은 복수의 메모리 장치들을 포함할 수 있고, 기능 유닛 각각을 위한 메모리 큐들의 수는 하나 이상 메모리 장치들의 수까지이다. 상기 멀티-프로세서 시스템은 어느 메모리 큐 출력이 어느 메모리 장치로 메모리 액세스를 하는지를 선택하는 스위칭 수단을 더 포함할 수 있다.

대안적으로 또는 상기에 더하여, 본 발명의 실시예에 따른 상기 멀티-프로세서 시스템은 메모리 장치 각각을 위한 많은 메모리 큐들을 포함할 수 있고, 메모리 큐들의 수는 하나 이상 기능 유닛들의 수까지이다. 이 경우, 상기 멀티-프로세서 시스템은 어느 메모리 큐 출력이 어느 기능 유닛으로 데이터를 전달하는지를 선택하는 스위칭 수단을 더 포함할 수 있다. 만약 전자의 실시예들이 결합되면, 상기 메모리 장치들을 향하여 액세스하는 또는 상기 메모리 장치들로부터 액세스하는 상기 메모리 큐들이 선택적으로 공유될 수 있다.

상기 스위칭 수단들은 하나 이상의 멀티플렉서를 포함한다. 상기 스위칭 수단들은 메모리 장치 당 하나의 멀티플렉서를 포함한다.

더 바람직한 실시예에서는, 멀티프로세서 시스템에 가능하면 어레이에 배열된 멀티플 기능 유닛들(연산 유닛들) 및 가능하면 뱅크 구조에 배열된 멀티플 메모리들이 제공되고, 적어도 상기 기능 유닛들의 일부를 위해, 메모리 수만큼의 메모리 큐들이 제공되고 기능 유닛 각각의 메모리 큐 각각은 상기 메모리들 중 하나에 전용적으로 할당된다.

또 다른 실시예에서, 적어도 상기 기능 유닛의 일부를 위해 부가적인 재정렬 레지스터 파일이 부가된다. 상기 재정렬 레지스터 파일들은 상기 하나 이상의 메모리 장치에서 출력되는 데이터의 정확한 순서를 저장하기 위해 제공된다.

또 다른 실시예에서, 예를 들어 소위 스크래치패드 메모리(scratchpad memory)라고 불리는 부가적인 메모리가 상기 멀티-프로세서 시스템에 부가된다.

본 발명의 실시예에서, 메모리 장치의 수는 기능 유닛의 수의 4배보다 적다.

본 발명의 실시예에서, 메모리 장치는 싱글 포트 또는 듀얼 포트다.상기 하나 이상의 메모리 장치는 캐시 메모리다. 상기 멀티-프로세서 시스템은 주 메모리에 기초하는 싱크로너스 다이나믹 램(SDRAM)을 더 포함한다.

본 발명의 실시예에서, 기능 유닛들의 수는 8개 이상이다.

본 발명의 실시예에서, 기능 유닛 당 메모리 큐들의 수는 메모리 장치들의 수와 동일하다. 이 경우, 메모리 장치 각각은 상기 기능 유닛들 각각의 메모리 큐와 관련된다.

본 발명의 실시예에 있어서, 메모리 장치들의 수는 2의 거듭제곱이 아니다.

본 발명의 실시예에서, 상기 멀티-프로세서 시스템은 상기 기능 유닛과 관련된 상기 메모리 큐들이 바이패스하도록, 기능 유닛 및 메모리 장치 간에 바이패스 수단을 더 포함한다.

본 발명의 실시예에서, 멀티-프로세서 시스템은 메모리 액세스들을 저 저장 비용 표현으로 저장하는 부가적인 스코어보드(scoreboard)라고도 불리는 스토리지 유닛(storage unit)을 더 포함하고, 서비스할 메모리 액세스를 선택하고, 상기 메모리 장치로 제어 신호를 제공하고, 상기 선택된 메모리 액세스를 서비스하는 제어 수단을 더 포함한다.

본 발명의 실시예에 따른 멀티-프로세서 시스템은 부가적인 메모리들 및 상기 하나 이상의 메모리 장치 및 상기 부가적 메모리들 간에 데이터를 전달하는 디엠에이 컨트롤러(DMA controller)를 더 포함한다.

또 다른 일측에 따르면, 멀티프로세서 아키텍처를 위하여 상기 메모리 대폭역 문제를 해결하는 소프트웨어 기술들 및 방법들은 보여진 아키텍처에 기초한 제안된 메모리 큐를 포함하고, 특히 데이터 레이아웃(data layout)의 이용을 포함한다.

본 발명은 디지털 시스템의 메모리 배열에서 최적화된 데이터 조직을 결정하는 방법을 제공한다. 상기 메모리 배열은 둘 이상의 메모리 장치들을 포함하고, 상기 디지털 시스템은 둘 이상의 기능 유닛들 및 기능 유닛 각각을 위한 하나 이상의 메모리 큐를 포함한다. 메모리 큐 각각은 기능 유닛과 관련되고, 상기 메모리 장치들의 각각은 둘 이상의 메모리 큐들과 연결되고, 상기 디지털 시스템은 어플리케이션의 실행(execution)을 위하여 구성된다.

상기 방법은 데이터 액세스 인스트럭션들(instructions)을 포함하는 상기 어플리케이션의 표현을 로딩하는(loading) 단계; 및 상기 액세스된 데이터를 상기 메모리 장치들로 분배하는 단계, 즉 상기 메모리 배열 및 상기 기능 유닛 간에 최적 동시 데이터 액세싱(accessing)을 획득하는 단계를 포함한다.

상기 데이터가 분할되는 실시예에서, 상기 분배는 최적 동시 데이터 액세싱 비용 함수를 평가함으로써 수행되며, 이는 상기 데이터 분할들을 상기 메모리 장치들로 다양하게 할당(assignments)하기 위한 것이다. 상기 최적 동시 데이터 액세싱 비용은 메모리 충돌의 수에 의해 결정된다.

본 발명은 또한 메모리 배열로 향하는 어느 메모리 액세스가 서비스되어야 하는지를 결정하는 방법을 제공한다. 상기 메모리 배열은 둘 이상의 메모리 장치들, 둘 이상의 기능 유닛들 및 기능 유닛들 각각을 위한 하나 이상의 메모리 큐를 포함하는 디지털 시스템이고, 메모리 큐 각각은 기능 유닛과 관련되고, 각각의 상기 메모리 장치들은 둘 이상의 메모리 큐들과 연결되고, 상기 메모리 액세스는 상기 메모리 큐들에 일시 저장된다. 상기 방법은 스토리지 유닛(storage unit) 또는 스코어보드(scoreboard)에 메모리 액세스 각각을 저 저장 비용 표현으로 저장하는 단계; 메모리 배열로 향하는 어느 메모리 액세스가 서비스되어야 하는지를 결정하기 위한 작동(operation)을 상기 스토리지 유닛에 대하여 수행하는 단계를 포함한다. 상기 스토리지 유닛은 선입 선출 조직(first input first output organization; FIFO organization)으로 둘러싸인다. 상기 저 저장 비용 표현은 1 비트 표현이다.

수행되는 상기 작동은 상기 스토리지 유닛 내에서의 참조 위치에 대하여 상대적으로, 메모리 액세스의 상기 저 저장 비용 표현 중 하나 이상의 위치를 결정하는 것을 포함하고, 상기 상대적 위치(relative position)로부터 상기 스토리지 유닛에 얼마나 길게 상기 저 저장 비용 표현이 있는지 결정하는 단계; 상기 스토리지 유닛에서 가장 긴 상기 표현들 중 하나 또는 그 이상을 선택하는 단계; 및 상기 참조 위치를 변경하는 단계를 포함한다. 하나보다 많은 표현이 선택된 경우, 상기 방법은 랜덤한 방법으로(in a random manner) 하나의 표현의 선택을 더 수행하는 단계를 포함한다.

본 발명은 또한 시스템에서 실행될 어플리케이션을 컴파일링(compiling) 하기에 적합한 정보를 결정하는 방법을 제공한다. 상기 시스템은 둘 이상의 기능 유닛들 및 둘 이상의 메모리 장치들을 구비한 하나의 메모리 배열을 포함하는 디지털 시스템이다. 상기 메모리 배열에서, 하나 이상의 메모리 큐가 기능 유닛 각각을 위해 제공되고, 메모리 큐 각각은 기능 유닛과 관련되고, 상기 메모리 장치들 각각은 둘 이상의 메모리 큐들과 연결된다. 상기 방법은 데이터 액세스 인스트럭션들을 포함하는 소스 코드 표현(source code representation)을 로딩하는 단계를 포함하고; 어느 메모리 장치들의 데이터 액세스들이 상기 어플리케이션을 실행할 때 수행될지를 특징짓는(characterizing) 단계를 포함한다. 실행될 어플리케이션을 컴파일링하기에 적합한 정보를 결정하는 단계는 다른 메모리 장치들로의 데이터 액세스들이 동일한 사이클에서 컴파일러(compiler)에 의해 자유롭게 스케쥴되도록 지시하는(indicating) 단계를 포함한다.

실시예에서, 싱글-인스트럭션-멀티플-데이터(single-instruction-multiple-data; SIMD) 기술은 상기 데이터 레이아웃 접근 기법과 결합하여 이용된다(또는 대안으로 또는 2의 제곱수가 아닌 뱅크들과 결합하여).

실시예에서, 컴파일러는 상기 스크래치패드 메모리가 제공되는 것을 이용하는 것을 지지한다.

실험 결과는 대부분의 메모리 충돌이 상기 제안된 하드웨어 기술들 만으로 하나 또는 그 이상을 이용하여, 또는 상기 제안된 소프트웨어(컴파일러) 기술들의 하나 또는 그 이상과 결합하여 이용함으로써, 합리적 비용으로 제거되거나 감소될 수 있다는 것을 보여준다.

도 1은 멀티플 기능 유닛들(Functional Unit, FU)(몇 개의 유닛들은 레지스터 파일(Register File, RF)에 연결된다)을 구비하는 멀티-프로세서 시스템을 도시한다. 상기 멀티-프로세서 시스템은 어레이에 배열되고, 멀티-포트 메모리 조직을 구비하고, 크로스바 및 상기 어레이의 다른 부분들을 위하여 로드/스토어 기능 유닛들(load/store functional units)로서 기능하는 몇 개의 기능 유닛들과 연결된다.

도 2는 멀티-뱅크 싱글-포트(multi-bank single-port) 메모리 시스템들을 구비한 도 1과 유사한 멀티-프로세서 시스템을 도시한다.

도 3은 역 이산 코사인 변환(Inverse Discrete Cosine Transformation; IDCT) 수평 루프(loop)의 뱅크 액세스 패턴을 도시한다.

도 4는 IDCT 수직 루프의 뱅크 액세스 패턴을 도시한다.

도 5 a)는 쓰루-메모리 크로스-이터레이션 디펜던시(through-memory cross-iteration dependency)를 구비한 루프를, b)는 쓰루-메모리 크로스-이터레이션 디펜던시를 구비하지 않은 루프를 도시한다.

도 6은 앰펙-2(MPEG-2)에서 움직임 보상(motion compensation)를 도시한다.

도 7은 기능 유닛에서 메모리 장치로 향하는 데이터 전달을 위한 하나 이상의 메모리 큐를 포함하는 본 발명의 메모리 아키텍처를 도시한다.

도 8은 본 발명의 메모리 큐 아키텍처의 데이터 흐름(flow)을 표시한다.

도 9는 로드/스토어 기능 유닛 및 관련된 큐들의 세 개의 구조들을 도시한다: a)는 모든 뱅크들에 의해 공유되는 하나의 큐; b)는 모든 뱅크들에 의해 각각 공유되는 멀티플 큐들; c)는 뱅크 각각을 위한 전용 큐이다.

도 10은 도 9a의 상기 구조의 가능한 효과들을 도시한다.

도 11은 도 9b의 상기 구조의 가능한 효과들을 도시한다.

도 12는 큐-투-뱅크 멀티플렉서(queue-to-bank multiplexer)를 도시하고, 상기 멀티 큐들을(각각은 기능 유닛에 연결된다(도시되지 않음))을 뱅크로 연결하는데 이용된다.

도 13은 재정렬 레지스터 파일들이 이용되는 본 발명의 다른 실시예를 도시한다.

도 14는 상기 재정렬 레지스터 파일을 위한 어드레싱 기법 (addressing scheme)을 표시한다.

도 15는 두 개의 정지 상황들을 도시한다: a)는 큐 오버플로우 정지(queue overflow stall)이고; b)는 요청이 시간 내에 서비스되지 못하는 것이다.

도 16은 IDCT 수평 루프의 뱅크 액세스 패턴을 도시한다.

도 17은 IDCT 수직 루프의 뱅크 액세스 패턴을 도시한다.

도 18은 본 발명의 다른 실시예에 따른 메모리 대역폭을 증가시키기 위해 부가된 스크래치패드 메모리 하부시스템 (scratchpad memory subsystem)을 도시한다.

도 19는 본 발명의 실시예에 따른 상기 메모리 큐의 관련 부분의 블록 다이어그램(block diagram)이고, 4개의 기능 유닛들과 연결된 스코어보드를 구비한다. 도 20은 본 발명의 실시예에 따른 블록 다이어그램이고, 멀티-프로세서 시스템은 메모리 장치에서 기능 유닛을 향하여 데이터를 전달하는 하나 이상의 메모리 큐를 포함한다.

도 21은 본 발명의 실시예에 따른 블록 다이어그램이고, 멀티-프로세서 시스템은 기능 유닛에서 메모리 장치를 향하는 데이터를 전달하는 메모리 큐들 및 메모리 장치에서 기능 유닛으로 향하는 데이터를 전달하는 메모리 큐들을 포함한다.

인터리브된

(

interleaved

) 멀티-뱅크 메모리 조직의 기초

엔(N) 뱅크들로 구성된 메모리 조직을 가정한다. 뱅크 각각은 엠-바이트 와이드(M-bite wide) 이다. 메모리 액세스의 뱅크 수는 다음 수식들과 같이 계산될 수 있다.

뱅크 수=(어드레스 / M) % N

뱅크 내 어드레스 = (어드레스 / M) / N

일반적으로, M 및 N은 2의 제곱이고, 예를 들면, M 은 4이고 N은 8이다. 그러므로 상기 뱅크 수 및 뱅크 내 상기 어드레스의 계산은 어렵지 않다(trivial). 어레이 쇼트 데이터[8][8] (array short Data[8][8])는 M은 4이고 N은 8인 멀티-뱅크 메모리 시스템으로 맵핑되고(is mapped to), 각 원소의 뱅크 수는 표1에서 보여지고, 제1 원소는 뱅크 0에서 시작하는 것으로 가정한다.

표 1 8x8 쇼트 어레이의 뱅크 수(1

bank

number

of

an

8x8short

array

)

전형적인 루프들에서 메모리 액세스 특성들

고려 중인 상기 아키텍처에서, 상기 주 연산 모델은 소프트웨어 파이프라이닝(software pipelining)이다. 중요성 및 규칙성 때문에 루프들만이 상기 어레이 모드에서 맵핑된다. 루프는 새로운 이터레이션(iteration)이 소정의 간격으로 초기화될 수 있도록 하는 방법으로 스케쥴된다. 다른 이터레이션들의 실행은 높은 병렬성을 달성하도록 중복된다. 참고로, [Bingfeng Mei, Serge Vernalde, Diederik Verkest, Hugo De Man, Rudy Lauwereins "모듈로 스케쥴링을 이용하는 조잡한 재구성할 수 있는 아키텍처에서 루프-레벨 이용"("Exploiting Loop-Level Parallelism on Coarse-Grained Reconfigurable Architectures Using Modulo Scheduling"), IEE Proceedings Computer & Digital Techniques, Vol. 150, No. 5, Sep. 2003]를 보면 충분히 실시예하고 있다.

상기 전형적인 루프들의 상기 메모리 액세스 특성들을 이해하는 것은 상기 메모리 대역폭 문제를 해결하는 핵심이다. 전형적인 멀티미디어 및 전자통신 어플리케이션들에서, 몇 가지 흥미로운 사실들을 관찰할 수 있다.

첫째로, 특정한 사이클들 및 이터레이션들에서 제한된 메모리 뱅크들로 버스트 요청들(burst requests)이 있다. 하지만, 메모리 뱅크 각각의 평균 메모리 요청은 사이클들 및 이터레이션들에 대해 동일한 수준이다. 예를 들면, IDCT 기능에는 수평 루프 및 수직 루프가 있다. 상기 입력 및 출력 데이터 둘 다 표1에 보여지듯이 8x8 어레이에 저장된다. 상기 수평 루프 동안, 이터레이션 각각은 로우 데이터(row of data)를 읽고 8-포인트 IDCT를 행하고, 상기 동일한 방법으로 다시 쓰 기한다. 상기 수직 루프는 칼럼(column)을 읽고 쓰는 것을 제외하고 유사하게 행동한다. 그러므로, 다음의 뱅크 액세스 패턴을 획득할 수 있다(도 3 및 4에 도시된 것처럼). 이터레이션 각각에서, 뱅크 각각으로의 상기 버스트 요청은 어렵다. 특히, 수직의 경우에 뱅크 8개 중 2개의 이터레이션 각각은 8 개의 요청들을 수신하고, 반면에 다른 뱅크들은 어떤 요청도 수신하지 않는다. 하나의 이터레이션에 초점을 맞추면, 이터레이션 각각은 상기 메모리 충돌 때문에 8개 이상의 사이클들이 필요하다. 하지만, 모든 상기 이터레이션들을 위한 평균 메모리 요청들을 보면, 뱅크 각각은 실제로 이터레이션 당 동일한 2개의 요청들을 수신한다. 이론적으로, 인터리브된 8뱅크 조직은 메모리 관점으로 2개의 사이클들/이터레이션을 유지할 수 있는 것을 의미한다. 상기 메모리 뱅크 충돌을 해결하기 위해 다른 이터레이션들에서 메모리 액세스들을 결합하는 것도 가능하다. 이터레이션들이 중복되는 상기 시스템의 상기 연산 모델과 완벽하게 조화된다.

둘 째, 상기 메모리를 통한 상기 크로스-이터레이션 디펜던스는 상기 전형적인 멀티미디어 및 전자통신 어플리케이션들에서는 드문 것이다. 즉, 상기 메모리 액세스 작동들은 파이프라이닝된 루프의 상기 크리티컬 패스(critical path)에서는 일반적이지 않다. 예를 들면, 도 5a) 및 5b)은 메모리 작동들을 통해서 크로스-이터레이션 디펜던시를 구비한 루프 및 구비하지 않은 루프를 도시한다. 제1 루프에서, 상기 메모리 작동들의 상기 레이턴시는 크리티컬하다. 다음의 이터레이션은 전의 이터레이션이 끝난 후에 시작할 수 있기 때문이다. 상기 메모리 작동이 세 개의 사이클을 차지한다(take)고 가정하면, 이터레이션 각각은 7개 이상의 사이클 을 차지한다(로딩 a[i]를 위한 세 개의 사이클, 애드(add)를 위한 하나의 사이클, 스토어링 a[i+1]를 위한 세 개의 사이클). 만약, 두 개의 사이클만큼 메모리 작동들의 레이텐시를 증가시켜야 하는 기술을 사용한다면, 이터레이션 각각은 7+4=11 개의 사이클들이 필요하다. 상기 수행 불이익(penalty)는 이터레이션 당 4 개의 사이클이다. 제2 루프는 쓰루-메모리 크로스-이터레이션 디펜던시를 구비하지 않는다. 상기 메모리 작동들의 상기 레이턴시는 포괄적인(overall) 수행에 휠씬 작은 영향(impact)을 미친다. 메모리 작동을 2 사이클 증가시키는 동일한 기술이 이용된다면, 상기 포괄적인 오버헤드(overhead)는 100 개의 이터레이션들에 대해 단지 4 개의 사이클들 또는 이터레이션 당 0.04 개 사이클이 있는 것이다. 다행이, 본 목표 어플리케이션에서, 대부분의 커널들(kernels)은 상기 유형에 속하거나, 상기 유형으로 변환될 수 있다. 그러므로, 여기서 보여준 상기 메모리 큐 기술이 이용될 수 있다.

셋 째, 상기 정확한 뱅크 정보는 때때로 설계된 시간에 알려지지 않는다. 이는 메모리 충돌을 피하기 위해 메모리 작동들을 스케쥴할 수 있는 컴파일러-온리 접근(compiler-only approach)을 중재하는 것을 어렵게 한다. 이상적으로, 메모리 액세스 각각의 정확한 뱅크 수가 설계된 시간에 알려 진다면, 작동시간 동안 충돌이 생기지 않는 방법으로 상기 메모리 작동을 스케쥴할 수 있다. 하지만, 많은 커널들을 위한 상기 경우는 아니다. 도 6은 앰펙-2 디코더(MPEG-2 decoder)의 움직임 보상에서 코드(code) 도시한다. 모든 상기 메모리 작동들은 *(...)에 의해 표시된다. 상기 참조 블록 어드레스(상기 코드에 포인터 에스(s))는 움직임 벡 터(motion vevtor)로부터 계산되고 어느 뱅크로부터도 시작할 수 있다. 그러므로, 어떤 메모리 액세스들 간 상기 뱅크 관계, 예들 들면, *addr8_d 및 *addr8_s는 설계된 시간에 알려지지 않는다. 어떤 상황에서도 상기 뱅크 충돌들을 회피할 수 있는 방법으로 상기 메모리 작동들이 스케쥴되는 것은 불가능 하다. 게다가, 에프에프티(FFT) 같은 어떤 커널들에서는, 상기 설계된 시간에 모든 상기 뱅크 정보를 알 수 있어도, 메모리 액세스들 간 상기 뱅크 충돌 관계는 이터레이션들에 걸쳐서 변한다. 이것 역시 컴파일러-온니 접근을 중재하는 것을 어렵게 한다. 고려되는 아키텍처에 이용되는 모듈로 스케쥴링(modulo scheduling) 기술 때문이다. 상기 방법으로, 단지 하나의 이터레이션이 이터리에션들에 걸쳐서 스케쥴되고 반복된다. 하나의 이터레이션에서 메모리 충돌을 방치할 수 있는 방법으로 두 개의 메모리 작동들이 스케쥴된다면, 이터레이션들에 걸친 뱅크 관계의 변화 때문에 상기 메모리 충돌들이 다른 이터레이션들에서 발생하지 않을 것이라는 것을 보장할 수 없다.

상기 관찰들은 더 상술될 상기 제안된 접근의 근거(foundation)를 제공한다. 전형적인 루프들의 상기 메모리 특성들을 이용하여, 메모리 충돌들을 감소할 수 있는 가능한 결합으로 하드웨어 및/또는 소프트웨어 해결책들 제안한다.

메모리 큐 아키텍처

상기 관찰에 기초하여, 전형적인 루프들의 메모리 액세스 특성들의 장점을 이용하여, 메모리 충돌들 감소시키는 아키텍처, 메모리 큐를 제안한다. 메모리 큐의 기본적인 아이디어는 메모리 뱅크 각각이 사이클들 및 이터레이션들에 걸쳐서 상기 버스트 요청을 원활하게(smooth out)하는 버퍼(buffer)를 제공하는 것이다. 바람직하게는, 다른 소프트웨어 변환 기술들과 결합한다. 메모리 충돌들을 크게(greatly) 감소시킬 수 있기 때문이다. 상기 접근의 오버헤드는 하드웨어 비용 및 상기 메모리 작동들의 레이턴시를 증가시키는 것이다. 하지만, 상기에서 지적한 것처럼(as pointed out in the last section), 상기 증가된 메모리 작동 레이턴시는 단지 대부분의 커널들에서, 상기 포괄적인 수행에 작은 불이익을 부가한다. 감소된 메모리 충돌과 비교하면, 상기 오버헤드는 작다.

메모리 큐를 포함하는 본 발명 실시예의 개념의 일반적인 구조는 도 7에 상술되고, 로드/스토어 기능 유닛들, 큐들, 직렬-병렬 중재기(parallel-to-serial arbitrator) 같은 선택적 스위칭 수단들(optional switching means), 메모리 뱅크들 및 선택적 재정렬 레지스터들 같은 몇 개의 구성요소들을 포함한다.

도 8은 메모리 요청의 상기 데이터 흐름을 상술한다. 포괄적인 흐름은 소정의 총 레이턴시, 예를 들면, 5개의 사이클들을 구비한다. 상기 로드/스토어 기능 유닛은 상기 데이터가 5 개의 사이클들에 도달하는 것을 예상한다는 것을 의미한다. 이는 파이프라이닝된 방법에서 상기 메모리 작동들을 실행하고 몇 개의 사이클을 요구하는 다른 프로세서들과 동일하다. 메모리 요청은 처음으로 로드/스토어 기능 유닛에 의해 초기화 된다. 상기 요청은 상기 타겟 어드레스 및 데이터(만약 쓰기라면)를 포함한다. 그런 다음 상기 큐에서 버퍼링되고, 스위칭 수단들 또는 직렬-병렬 논리(parallel-to-serial logic)에 의해 선택되고, 상기 타겟 메모리 뱅크에 도달한다. 쓰기 요청이라면, 여기서 끝이고, 읽기 요청이라면, 상기 메모 리 뱅크에서 출력된 상기 데이터는 정확한 순서를 저장하는 상기 재정렬 레지스터들에서 버퍼링되고, 소정의 레이턴시의 끝까지 대기한다. 상기 흐름동안 태그는 상기 요청과 관련된다. 상기 태그는 상기 소정의 레이턴시에서 초기화 되고 각 사이클에서 1만큼 감소한다. 기본적으로, 상기 태그는 요청의 "긴급성" 및 요청이 제시간에 서비스되지 못한 경우, 상기 멀티프로세서 아키텍처가 정지될 필요가 있는지를 반영하는 정보를 제공한다. 구성요소 각각의 세부사항은 하기에서 논의된다.

로드/스토어 기능 유닛들 및 메모리 뱅크들의 상기 큐들은 메모리 요청들을 버퍼링하고 원활하게 하는 핵심 역할(key role)을 한다. 큐 각각은 하나의 작은 선입선출(Fist-In-First-Out;FIPO)이다. 큐의 크기는 하나의 레지스터만큼 작을 수 있다. 상기 작은 큐들을 함께 그룹핑(grouping)하는 방법은 많다. 도 9는 로드/스토어 기능 유닛 및 연결된 큐들의 세 개의 구조들 a)모든 뱅크들에 의해 공유되는 하나의 큐;b)모든 뱅크들에 의해 공유되는 멀티플 큐들;c)뱅크 각각을 위한 전용 큐를 묘사한다(depict).

로드/스토어 기능 유닛 각각(도 9a)을 위해 단지 하나의 큐만 있는 경우, 명백한 장점은 다른 구조들과 비교 할때, 훨씬 더 낮은 하드웨어 비용이다. 반면에, 상기 단순한 구조는 소위 헤드-오브-라인(head-of-ine; HOL)이라고 불리는 블록킹(도 10)을 생성하기 쉽다. 하나의 사이클에서, 상기 로드/스토어 기능 유닛이 뱅크 A로 요청을 내린다고(issue) 가정한다. 하지만, 상기 뱅크A는 다른 요청들을 서비스하는데 사용되고 있다(is occupied). 다음 사이클에서, 상기 동일한 로드/스 포어 기능 유닛은 또 다른 메모리 요청을 뱅크B로 내린다. 상기 전의 요청이 상기 큐에 아직 남아 있기 때문에, 뱅크B로의 상기 메모리 요청은 상기 뱅크B가 한가하더라도 필요치 않게 블록킹된다. 블록킹이 반드시 정지를 야기시키는 것은 아니다. 하지만, 상기 블록킹된 요청이 시간 내에 서비스되지 않으면, 결국은 정지를 야기시킨다. 그럼에도 불구하고, 어플리케이션의 종류에 따라서, 상기 해결책이 선택될 수 있다.

하나의 대안은 도 9b에서 도시된 것처럼, 로드/스토어 기능 유닛 각각을 위한 멀티플 큐들을 제공하는 것이다. 메모리 요청은 상기 타겟 뱅크 수와 관계없이 상기 큐들 중 하나에 의해 더 자유롭게 버퍼링될 수 있다. 상기 구조는 도 9c에서와 같이 뱅크 각각을 위한 전용 큐들과 비교할 때, 상기 큐 자원들을 더 효율적으로 이용할 수 있다. 반면에, 불필요한 정지들을 감소시킬 수 있다. 왜냐하면, 요청은 전의 요청이 블록킹된다 해도, 대안적인 큐에서 버퍼링될 수 있기 때문이다. 그럼에도 불구하고, 상기 접근은 여전히 몇 개의 단점들을 구비한다. 첫 째, 제어 논리 회로(control-logic)가 꽤 복잡해 진다. 상기 메모리 요청을 큐로 전달하기 위해서는 어느 큐가 비어 있는지 또는 최소로 사용되고 있는지 확인해야 한다. 상기 중재(arbitration)는 중요하며, 지연을 증가시키고 여분의 사이클을 필요로 할 것이다. 둘 째, 상기 큐의 출력 측면에 하드웨어 비용을 부가한다. 큐 각각은 임의의 메모리 뱅크에 대한 요청들을 저장할 수 있으므로, 상기 요청들 중에서 어느 하나를 선택하는 것은 더 넓은 또는 별도의(extra level) 스위칭 수단, 예를 들어 멀티플렉서 등을 필요로 한다. 이것은 실리콘 면적, 시간 지연 및 전력 소비를 증 가시킨다. 마지막으로, 아직도 헤드-오브-라인 블록킹(도 11)을 완전히 해결할 수 없다. 그럼에도 불구하고, 어플리케이션의 종류에 따라서, 상기 해결책은 선택될 수 있다.

상기 잠재적 문제들을 회피하기 위해, 본 발명의 실시예에서, 큐 조직이 중재되었고, 상기 큐 조직은 네트워크 스위칭에서의[Adisak Mekkittkul, Nick McKeown, "입력된 큐잉 스위치에서 100% 처리량 달성을 위한 스타베이션-프리 알고리즘"("Starvation-free Algorithm For Achieving 100% Throughput in a Input-Queued Switch"), International conference on computer communications and networks (ICCCN), Washington, DC, Oct., 1996]. 가상 출력 큐잉(virtual output queuing; VOQ)의 개념과 유사하다(analogous). 로드/스토어 기능 유닛 각각은 뱅크 각각을 위한 분리된 큐를 유지한다. 상기 장점들은 다양한 측면에서 나타난다. 첫 째, 다른 두 개의 구조들이 구비한 것과 같은 헤드-오브-라인 블록킹이 없다. 메모리 요청은 단지 전 요청이 동일한 뱅크에서 아직 서비스되지 않은 때, 블록킹된다. 이런 상황에서, 상기 블록킹은 피할 수 없다. 둘 째, 상기 컨트롤 논리는 멀티플 큐들을 구비한 상기 구조와 비교할 때 더 단순하다. 요청 각각은 어느 큐를 고를지(pick) 결정하지 않고 대응 큐에서 직접 버퍼링될 수 있다. 셋 째, 상기 큐의 상기 출력 면 역시 더 단순하다. 뱅크 각각은 다른 뱅크들로부터의 큐들을 멀티플렉스하는 멀티플렉서가 필요하다. 상기 멀티플렉서 및 상기 중재 회로(arbitration circuit)는 상기 멀티-큐 구조보다 단순하다. 상기 접근의 단점은 더 많은 레지스터들이 필요하다는 것이다. 레지스터의 총 수는 엠(M)x 엔(N)x에 스(S)로 계산 될 수 있고, M은 로드/스토어 기능 유닛들의 총 수이고, N은 뱅크들의 총 수이고 S는 상기 큐 사이즈 이다.

상기 메모리 큐는 메모리 뱅크가 뱅크 충돌들을 야기시킬 수 있는 몇 개의 로드/스토어 유닛들에 의해 생성되는 요청들을 서비스하는 방법을 제어한다. 요청들을 서비스하는 것은 시스템 디자이너에 의해 구성될 수 있는 특정한 레이턴시를 가정한다. 메모리 요청들은 상기 메모리 뱅크가 상기 메모리 요청들을 서비스하도록 준비될 때까지 큐잉된다. 대기중인 요청이 구성된 레이턴시 내에 서비스되지 못해 오랫동안 큐에서 대기할 때, 상기 메모리 큐는 상기 기능 유닛들을 정지한다. 상기 메모리 큐가 대기 중인 요청이 레이턴시를 충족할 가능성을 예상하면, 상기 기능 유닛들은 재활성화된다.

뱅크 각각 및 뱅크를 위해 버퍼링하는 모든 상기 큐들 간에 멀티플렉서가 있다. 사이클 각각에서, 메모리 뱅크는 하나의 요청만 서비스할 수 있기 때문에 상기 큐들에서 멀티플 요청들이 대기 중이라면, 어떤 중재 알고리즘(arbitration algorithm)이 필요하다. 효과적인 기준(criterion)은 요청 각각의 "긴급성"이다. 상기에 언급한 것처럼, 태그는 각각의 요청과 관련된다. 상기 태그는 최초로 미리 정해진 레이턴시에 세트되고 각각의 사이클 후에 1 씩 감소된다. 이것은 상기 로드/스토어 기능 유닛이 상기 태그와 같이, 동일한 사이클 수에 도달하는 데이터를 예상한다는 의미이다. 명백히, 태그가 작을수록, 요청은 더 긴급하다. 예를 들면, 도 12에서는 세 개의 큐들이 다른 태그들을 구비한 요청들을 포함한다. 로드/스토어 기능 유닛2로부터의 요청이 가장 긴급한 것이기 때문에 선택된다. 다른 중 재 알고리즘도 가능하다.

본 발명은 또한 상기 중재 목적을 달성하는 알고리즘을 제안한다. 상기 아이디어는 스코어보드라고도 불리는 스토리지 유닛에 상기 메모리 요청들을 저 저장 비용으로 일시 저장하는 것이다. 이러한 관계에 있어서는, 요청 각각을 위해 1 비트를 저장하는 것으로 충분하다. 상기 스코어보드에서 요청의 위치는 상기 요청이 수신된 시간을 결정한다. 카운터(counter)는 얼마나 오래 현재의 요청이 상기 큐에 머물렀는지 결정하는 것에 이용된다. 상기 카운터는 대기 시간 카운터(waiting time counter;WT)로 참조될 것이다. 상기 두 개의 타이밍 정보는 상기 메모리 큐가 먼저 설명된 것처럼 기능하기에 충분하다.

도 19는 4 개의 로드/스토어 기능 유닛들과 연결된 스코어보드를 구비하는 상기 메모리 큐의 관련 부분들의 블록 다이어그램을 도시한다. 상기 스코어보드의 로우(row)는 특정 로드/스토어 기능 유닛과 관련된 요청들의 시간(timeline)을 나타낸다. 스코어보드의 상기 작동은 두 개의 분리된 프로세스들: 상기 스코어보드 내로 쓰는 프로세스 및 상기 스코어보드로부터 읽어내는 프로세서로 볼 수 있다. 쓰기 프로세서 동안, 시계 사이클(clock cycle) 각각에서, 로드/스토어 기능 유닛들로부터의 모든 요청들은 새로운 칼럼을 부가하는 상기 스코어보드에서 캡쳐되고, 상기 칼럼에 대응하는 로우 각각은 특정한 로드/스토어 기능 유닛을 참조한다. 특정한 사이클에서 상기 메모리 뱅크들로 쓰기 요청들이 만들어 지지 않는다면, 상기 새로운 칼럼은 공백이 될 것이다. 덧붙여, 상기 스코어보드가 비었을 때, 상기 쓰기 프로세서는 상기 메모리 뱅크가 상기 요청들을 즉시 서비스할 수 있 도록 상기 메모리 큐를 바이패스하도록 결정할 수 있다. 상기 쓰기 프로세스는 하나 이상의 기능 유닛들이 정지 할 때 정지한다(halt).

읽기 프로세서 동안, 시계 사이클 각각에서, 상기 스코어보드의 현재 칼럼은 어떤 대기 중인 요청들을 위해 스캔된다. 동일한 칼럼에 있는 요청들은 임의의(arbitrary) 순서로 서비스될 수 있다. 칼럼에 대기 중인 요청들이 없을 때는, 상기 메모리 큐는 다음 칼럼을 향해 이동하고 요청들을 서비스한다. 상기 다음 칼럼이 비어 있다면, 상기 메모리 큐는 다음 칼럼을 향해 이동한다. 요청이 서비스되었을 경우, 상기 메모리 큐는 상기 스코어보드에서 제거된다. 칼럼에 있는 모든 요청들이 서비스되었을 때, 상기 전체의 칼럼은 상기 스코어보드에서 제거된다. 상기 읽기 프로세서는 기능 유닛이 정지될 때 정지하지 않는다.

대기 시간(WT) 카운터가 제공되고, 상기 대기 시간 카운터는 기본적으로 요청들이 상기 큐에서 머무는(resided) 시간의 양을 계산한다. 상기 정의된 레이턴시 내에 요청들이 서비스되지 못할 경우에 상기 기능 유닛들을 정지하는데 이용된다. 상기 WT 카운터는 상기 메모리 뱅크들로부터 수신된 상기 데이터를 재정렬하도록, 상기 필요한 정보를 전달한다. 상기 WT 카운터를 조작(manipulating)하는 것은 상기 코어(정지된/활동 중인)의 상태 및 상기 스코어보드에 있는 대기 중인 요청들의 레이아웃에 달려 있다.

스코어보드의 실행은 상기 태그를 구비한 전 실행과 비교하면, 더 적은 실리콘 영역을 차지한다. 모든 상기 태그들이 하나의 WT 카운터에 의해 대체되기 때문이다. 상기 태그들의 비교는 대기 중인 요청들을 위한 상기 스코어보드를 찾는 것 으로 대체되고, 타이밍을 향상한다. 이것은 로드/스토어 기능 유닛들의 수가 많을 때 특히 더 유리하다.

쓰기 트랜잭션(transaction), 즉, 메모리 뱅크 및 메모리 장치로의 쓰기를 위하여, 상기 메모리 요청이 상기 타겟 메모리 뱅크에 도달하면 상기 데이터 흐름이 끝난다. 상기 읽기 요청, 즉 메모리 뱅크로부터의 읽기를 위하여, 상기 메모리 뱅크로부터 출력되는 상기 데이터는 상기 원래의 로드/스토어 기능 유닛에 디스패치된다(dispatched). 여기서 문제 하나가 발생할 수 있다. 두 개의 읽기 요청들 a 및 b가 동일한 로드/스토어 기능 유닛에 의해 초기화되고 상기 요청들이 각각 뱅크0 및 뱅크1로 간다고 가정한다. a는 b전에 초기화 된다. 그러므로 정확한 순서는 상기 데이터 a 가 b보다 먼저 도달하는 것이다. 하지만, b가 뱅크1이 이용 가능하여 즉시 서비스되는 반면, a가 다른 로드/스토어 기능 유닛들로부터의 요청들을 서비스 중인 뱅크0 때문에 몇 개의 사이클들의 큐에서 블록킹된다면, b의 결과가 사실상 a의 결과보다 먼저 도달할 수 있다. 상기 메모리 큐의 출력 결과들이 순서에 맞지 않음을 것을 의미한다. 게다가, 상기 메모리 레이턴시는 미리 정의되고 컴파일러들은 주어진, 미리 정의된 메모리 레이턴시에 따라서 상기 루프를 스케쥴링하기 때문에, 구체화된 레이턴시가 끝날 때까지 상기 데이터는 어딘가에서 버퍼링되어야 한다.

상기 문제들을 취급할 기법이 이제 제시된다. 몇 개의 재정렬 레지스터 파일들이 정확한 데이터 순서를 획득하기 위하여 상기 메모리 뱅크 및 상기 로드/스토어 기능 유닛들 간에 삽입되고, 미리 정의된 레이턴시가 끝날 때까지 상기 데이 터를 버퍼링한다. 재정렬 레지스터들의 수는 토탈_레이턴시-오버헤드_사이클들(total_latency-overhead_cycles)과 동일하다. 상기 오버헤드 사이클들은 메모리 요청들이 상기 큐들, 직렬병렬 변환(멀티플렉싱), 리얼 메모리 액세스등으로 들어가고(enter) 나가는(leave) 사이클을 포함한다.

상기 재정렬 레지스터 파일은 선입선출이 아니고, 하나의 입력 포트 및 하나의 출력 포트를 구비한다. 두 개의 포트들의 어드레싱 메커니즘은 도 14에서 묘사된다. 모듈로 카운터는 입력 및 출력 어드레스를 생성하는 데 이용된다. 상기 카운터는 매 사이클마다 업데이트된다. 상기 입력 포트 어드레스는 상기 태그 및 상기 카운터 값의 합계이고, 상기 출력 포트 어드레스는 단지 상기 카운터 값이다. 예를 들면, 데이터 a는 사이클 i에 도달하고 데이터b는 태그 1을 구비하는 사이클 i+1에 도달한다. 상기 카운터 값이 사이클 i에서 0이라고 가정하면, a는 레지스터 3에 쓰기되고, b는 레지스터 2에 쓰기된다. 상기 출력 면에서, b는 사이클 i+2에서 읽히고, a는 사이클 i+3에서 읽힌다. 그러므로 상기 잘못된 데이터 순서를 수정하는 것 뿐 아니라, 상기 메모리 큐 아키텍처로부터 두 개의 데이터 모두가 정확한 순간에 출력된다.

상기 발명에 따라서 상기 메모리 요청들을 버퍼링하는 상기 메모리 큐를 구비하여도, 정지들은 여전히 다음의 두 가지 상황들(도 15)에서 발생할 수 있다: 1) 큐는 가득 차있고 새로운 메모리 요청을 버퍼링 할 수 없는 경우; 2) 요청이 상기 소정의 레이턴시 내에 끝나지 못하여 상기 큐에 너무 오래 대기하고 있는 경우이다. 제1 상황의 가능성은 로드/스토어 기능 유닛 각각이 뱅크 각각을 위한 전용 큐를 구비할 경우, 매우 작은 큐를 구비한다 해도 낮다. 큐는 로드/스토어 기능 유닛이 반복적으로 동일한 뱅크를 위한 요청들을 초기화하거나 더 이른 요청들을 정시에 서비스하지 못하지 않는 한(도 15a), 오버플로우(overflow)하지 않는다. 후자의 경우에, 상기 정지는 실행에 따라서 다른 위치들에서 확인될 수 있다. 예를 들어, 상기 메모리 뱅크 및 재정렬 레지스터들이 하나의 사이클을 차지한다고 가정하면, 상기 큐 헤드에 있는 어떤 요청의 상기 태그가 (레이턴시-2)보다 작으면, 정지가 개시된다(trigger). 이것은 상기 요청이 시간 내에 서비스되지 못한다는 것을 의미한다. 그러므로 상기 정지가 개시된다(도 15b).

상기 메모리 큐 아키텍처를 지지하기 위하여, 특별한 편집/컴퍼레이션 기술들은 필요하지 않다. 상기 컴파일러가 멀티-사이클 메모리 오퍼레이션을 지원하는 한 상기 메모리 큐는 제대로 처리될 수 있다.

상기 발명의 대안 실시예가 도 20에서 개시되는데, 4개의 메모리 장치들 M1, M2, M3, M4가 기능 유닛들 FU1. FU2. FU3, FU4에 메모리 큐들 qij, i=1…4,j=1…4를 통해 연결된다(coupled). 도시된 실시예에서, 메모리 장치 각각을 위한 메모리 큐들의 수는 기능 유닛 만큼, 즉 4개이다. 상기 멀티-프로세서 시스템은 어느 메모리 큐 출력이 어느 기능 유닛으로 데이터를 전달하는지를 선택하는 스위칭 수단을 더 포함한다. 도시된 예에서, 상기 스위칭 수단들은 복수개의 멀티플렉서들을 포함한다.

본 발명의 또 다른 실시예가 도21에서 도시되며, 네 개의 기능 유닛들 FU1. FU2. FU3, FU4 및 네 개의 메모리 장치들 M1, M2, M3, M4을 보여준다. 기능 유닛 각각을 위한 네 개의 메모리 큐들 qij, (i=1…4,j+1…4)이 제공되고, 앞에서 도시된, 어느 메모리 큐의 출력이 어느 메모리 장치로 메모리 액세스하는지를 선택하는 4개의 멀티플레서들 MUX1. MUX2, MUX3, MUX4를 도시하는 실시예에서의 스위칭 수단들이 제공된다. 또한 메모리 장치 각각을 위한 네 개의 메모리 큐들 qij'(i=1…4,j+1…4)이 제공되고, 앞에서 도시된, 어느 메모리 큐의 출력이 어느 메모리 장치로 메모리 액세스하는지를 선택하는 4개의 멀티플레서들 MUX1'. MUX2', MUX3', MUX4'를 도시하는 실시예에서의 스위칭 수단들이 제공된다.

상기 도면들에서 도시되지 않은 또 다른 실시예에서, 상기 메모리 큐들 qij 및 메모리 큐들 qij' 는 공유될 수 있다.

메모리 큐의 복잡성 측정

여기서는, 메모리 큐들을 실행하는 상기 하드웨어 비용들을 대략적으로 측정하는 시도를 한다. 가정(Assumptions)은 다음과 같다: 로드/스토어 기능 유닛들의 수는 8개 이고, 뱅크들의 수는 8개 이고, 큐 사이즈는 2이고, 메모리 레이턴시는 5이고 데이터 폭은 32이다. 상기 큐 레지스터는 8(로드/스토어 기능 유닛들) x 8(뱅크들) x 2 (큐 사이즈) x 64(데이터+어드레스)=8192개의 플립-플롭스(flip-flops)를 포함한다는 것을 의미한다. 큐-투-뱅크 멀티플렉서들(queue-to-bank multiplexers)의 수는 8(뱅크) x 64(데이터+어드레스), 8-to-1 멀티플렉서들=512 8-to-1 멀티플렉서들이다. 상기 재정렬 레지스터 파일은 8(뱅크) x 3(레지스터 파일 사이즈) x 32(데이터)=768개의 플립-플롭스 및 8(뱅크) x 32(데이터)=256 3-to- 1 멀티플렉서 및 1-to-3 디멀티플럭서 이다.

다른 더 낮은 하드웨어 비용들 및 컨트롤 논리들은 계산되지 않는다. 비록 상기 메모리 큐는 상당한 하드웨어 자원들에 이용되지만, 활동성 수준 때문에 많은 전력을 소비하지는 않는다. 예를 들면, 8(로드/스토어 기능 유닛들) x 8(뱅크)= 64개의 작은 큐들이다. 하지만, 대부분의 8(로드/스토어 기능 유닛들의 수) 큐들에서, 큐들은 어느 순간에라도 쓰여질 수 있다.

실험 결과

상기 실험들은 메모리 큐 시뮬레이터에 기초한다. 다른 레이턴시, 다른 메모리 뱅크 수, 다른 큐 사이즈 등의 메모리들을 시뮬레이트할 수 있다.

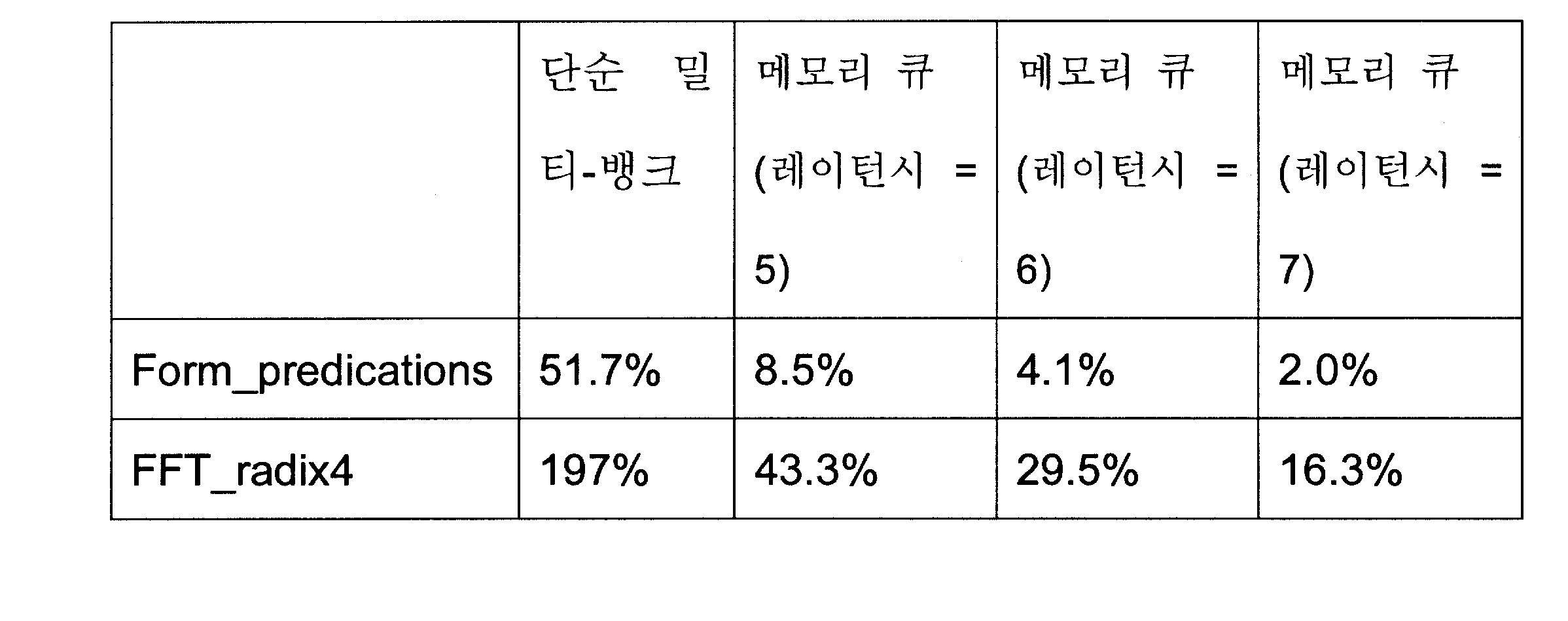

표2는 몇 개의 기능들의 상기 실험 결과들을 열거한다. 처음의 4개는 최적화된 MPEG-2 디코더부터이다. IDCT 애드 블록 (IDCT_add_block) 은 IDCT, 포화(saturation), 및 부가적인 블록들의 기능들을 포함한다. 그것은 3개의 커널들로 구성된다. 폼_프리디케이션즈 (form_predications)는 움직임 보상의 다른 경우들을 위한 8개의 커널들을 포함한다. 디퀀타이즈_인트라(dequantize_intra) 및 디퀀타이즈_넌_인트라(dequantize_non_intra)는 인트라 블록 및 비 인트라 블록들을 위한 두 개의 역양자화(dequantixation) 기능들이다. 각각은 하나의 루프로 구성된다. 에프에프티_레딕스4(FFT_radix4)는 컴플렉스 레딕스-4 패스트 푸리에 변환(fast fourier transformation;FFT) 기능이고 두 개의 루프들로 구성된다. 상기 실험은 7096-포인트 FFT에서 수행된다.

상기 두 번째 칼럼은 단순 멀티-뱅크 조직이 이용된 경우 메모리 충돌의 퍼 센티지이다. 상기의 메모리 조직에서, 상기 포괄적인 멀티프로세서 아키텍처는 모든 상기 메모리 요청들이 사이클 각각을 충족시킬 때까지 정지되어야 한다. 칼럼 3 내지 5는 메모리 충돌 및 몇 개의 다른 메모리 레이턴시들의 오버헤드의 퍼센티지를 상술한다. 상기 메모리 충돌 퍼센티지는 다음의 수식과 같이 정의 된다.

충돌_사이클들/(총_사이클들_충돌_사이클들)

(conflict _ cycles/(total _ cycles - conflict _ cycles))

상기 오버헤드 퍼센티지는 다음의 수식과 같이 정의되고, 상기 여분의 사이클들은 상기 메모리 큐들 이용하는 것 및 이용하지 않는 것 간의 사이클 차이를 나타내고(denote), 보통의 메모리 작동의 레이턴시는 3개의 사이클이라고 추정된다.

엑스트라_사이클들/(총_사이클들-충돌_사이클들)

(extra _ cycles/(total _ cycles - conflict _ cycles))

상기 메모리 큐는 상기 단순 멀티-뱅크 조직과 비교할 때, 상기 메모리 충돌들을 크게 감소시킬 수 있다. 5개 사이클들의 레이턴시를 구비한다 해도, 상기 메모리 충돌은 50 내지 75% 까지 감소한다. 상기 큐 사이즈의 증가는 상기 메모리 충돌들을 더 감소시킬 수 있다. 하지만, 증가하는 성능 오버헤드 및 하드웨어에 대해서는 비용 또한 증가한다. 몇 개의 커널들에서, 상기 오버헤드는 매우 중요하다. 주된 이유는 상기 루프들에 있는 이터레이션들의 수가 다소 제한된다는 것이다. 그러므로, 상기 증가된 메모리 레이턴시는 잘 숨겨질 수 없다.

표2 커널을 위한 메모리 충돌(뱅크=8)

메모리 충돌을 감소시키기 위한 데이터 레이아웃 변경

비록 상기 메모리 큐가 다른 사이클들 및 이터레이션들에 걸쳐서 뱅크 요청들을 원할하게 할 수 있고 메모리 충돌들을 현저히 감소 시킬수 있다 해도, 다른 뱅크들을 위한 상기 메모리 요청들이 첫 번째 장소에서 공평하게 분배되는 것이 여전히 더 바람직하다. 만약, 특정한 뱅크로의 상기 버스트 메모리 요청이 너무 많으면, 상기 요청들을 버퍼링하는 더 긴 큐들이 필요하다. 이것은 오버헤드의 수행을 증가시킬 뿐 아니라, 더 넓은 실리콘 영역 및 더 많은 전력 소비를 필요로 한다.

많은 커널들을 위하여, 상기 메모리 요청들의 뱅크 분배는 데이터 레이아웃 을 최적화하여 변경할 수 있다. 이용되는 주된 방법은 이터레이션 각각에 걸쳐 상기 뱅크 액세스 패턴을 이동하는 것이다. 예를 들면, IDCT 기능에서, 8x8 어레이를 대신하여 8x9 어레이를 할당할 수 있지만, 원소들(elements)의 여분의 칼럼은 연산에서 이용될 수 없다. 상기 여분의 칼럼은 표3에서 보이듯이 상기 어레이의 상기 뱅크 분배로 훌륭하게 변경할 수 있다.

표3 8x9 쇼트 어레이를 위한 뱅크 수

도 16 및 17은 수평 루프 및 수직 루프에서 모든 상기 이터레이션들의 뱅크 분배를 보여준다. 특히, 상기 수직 루프에서 뱅크 각각으로의 요청들이 마주보는 도4로 훌륭하게 원활화된다. 대부분의 뱅크들은 각각의 이터레이션에서 단지 2개의 요청들을 획득한다. 그러므로, 작은 메모리 큐 하나로도 쉽게 처리될 수 있다.

표4는 상기 데이터 레이아웃 최적화가 몇 개의 벤치마크들(benchmarks)에 이용된 후 실험 결과들을 열거한다. IDCT _애그_블록(IDCT_add_block) 및 폼_프리디 케이션즈(form-predications)를 위해, 상기 기술들은 반드시 동일하다. 2디(2D) 어레이들은 여분의 칼럼과 함께 할당된다. 그러므로, 이터레이션 각각에서 이용된 뱅크 수는 다른 뱅크들에 걸쳐있는 버스트 요청을 좀 더 공평하게 분배하기 위하여 이동된다. 두 개의 역양자화 기능들에 적용된 상기 최적화는 단순하다. 16비트 유형의 어떤 변수들은 다른 뱅크들에 분배되기 위하여 32비트 유형으로 대체된다. 상기 IDCT_add_block을 위하여, 거의 모든 상기 메모리 충돌들 단지 상기 간단 변환에 의해 제거된다. 다른 벤치마크들을 위하여, 상기 충돌들은 하드웨어-온니 기술과 비교할 때, 또한 현저히 감소한다. 그러므로, 상기 제안된 아키텍처와 결합하는 데이터 레이아웃 최적화를 위한 시스템적 접근의 상기 이용은 우수한 결과를 나타낸다.

데이터 레이아웃 최적화는 수동으로 수행될 수 있지만, 디자이너의 경험 및 상기 데이터를 변환하는 상기 어플리케이션에 대한 이해가 요구된다. 대안으로, 좀더 시스템적인 접근이 툴(tool)에서 실행된다. 또 다른 접근은 상기 단계를 자동화하지(automate) 않지만, 상기 디자이너가 상기 뱅크 정보에 관한 통찰력(insight)을 획득하고 어떻게 데이터 레이아웃을 변경할 것인가에 관한 약간의 제안들을 하도록 툴들을 제공하는 것이다.

표4 데이터 레이아웃 후 메모리 충돌(뱅크=8)

메모리 대역폭 요구 및 메모리 충돌을 감소하기 위한

에스아이엠디(SIMD)의

이용

메모리 뱅크 각각은 전형적으로 대부분의 경우를 수용하는 32비트 와이드(wide)이다. 하지만 많은 커널들은 8비트 또는 16비트 데이터 유형들에서 작동하고, 많은 상기 데이터 액세스들이 연속적인(consecutive) 어드레스들에서 발생한다. 이것은 귀중한 메모리 대역폭의 비효율적인 이용을 초래할 뿐만 아니라, 불필요한 메모리 뱅크 충돌들을 야기한다. 예를 들면, 루프에서 두 개의 메모리 읽기 A[2*i] 및 A[2*i+1]과 관련하여, 상기 두 개의 액세스들은 동일한 뱅크로 갈 수 있다. 이것은 상기 메모리읽기들을 실행하는 두 개의 메모리 장치들을 필요로 할 뿐만 아니라, 만약, 그것들이 동일한 사이클에서 스케쥴된다면, 단순 멀티-뱅크 시스템에서 정지 사이클을 야기시킨다. 비록 상기의 상황이 상기 메모리 큐에 의해 처리될 수 있지만, 만약 너무 많은 경우가 루프에서 발생한다면 여전히 정지를 초래 할 수 있다. 예를 들면, 폼-프리디케이션즈에서 상기 커널들은 많은 연속적인 8비트 액세스들을 포함한다. 입력 블록으로의 4 개의 액세스들, 참조 블록으로의 4 개의 액세스들 및 출력 블록으로의 4개의 액세스들 모두는 동일한 뱅크로 간다(도6). 그러므로, 긴 메모리 큐를 구비한다 해도, 하나의 이터레이션에 있는 너무 많은 동일한 뱅크 액세스들 때문에 메모리 충돌들을 아직 완전히 제거할 수는 없다. 상기의 상황은 먼저 상술된 상기 데이터 레이아웃 변환에 의해 완화될 수 없다(alleviated).

상기 문제를 해결하기 위하여, 싱글-인스트럭션-멀티플-데이터(single-instruction-multiple-data;SIMD) 기술을 이용한다. 상기 기술은 다른 프로세서들(Interx86, TIDSP, 등)에서 널리 이용된다. 일반적으로, SIMD는 하나의 지시가 병렬로 몇 개의 짧은 데이터 항목들에서 작동하는 기술이다. 본 발명에서는 상기 데이터 액세스 부분에만 SIMD를 이용한다. 상기 기본적 아이디어는 몇 개의 작은 연속적인 데이터 항목들을 하나의 큰 데이터 항목으로 결합하는 것이다. 이것은 하나의 지시에 의해 읽히고 쓰이게된다. 하나의 큰 데이터 아이템이 읽힌 후, 일반적인 쉬프트/앤드(shift/and) 작동들 또는 전용 엠비에이치/엠비엘(mvh/mvl) 작동들에 의해 본래의 작은 데이터 항목들로 분리된다. 유사하게. 상기 더 작은 데이터 항목들은 하나의 큰 데이터 항목으로서 상기 메모리에 쓰기되기 전에 먼저 병합된다. 상기 방법은 메모리 대역폭을 더 효율적으로 이용할 뿐 아니라, 메모리 충돌의 가능성을 감소시킨다.

표 5는 단순 멀티-뱅크 해결책들과 비교하여, 메모리 큐들의 상기 메모리 충돌들을 열거한다. 단지 Form_predications 및 FFT_radix4가 상기 SIMD 변환들에 적용된다. Form_predications에서, 4비트 액세스들은 상기 출력 블록 및 입력 블록을 위하여 하나의 32비트 액세스로 결합된다. 하지만, 상기 참조 블록으로의 상기 액세스들은 결합될 수 없다. 상기 32비트 경계로 정렬(align) 될 수도 정렬되지 않을 수도 있기 때문이다. FFT_radix4에서, 두 개의 16비트 데이터(복소수의 두 부분)는 하나의 32비트 액세스로 결합된다. 두 개의 역양자화(dequantization) 루프들은 메모리 액세스들을 결합할 어떤 기회도 가지지 못한다. 상기 IDCT_add_block은 이미 매우 낮은 메모리 충돌을 구비하므로, 상기 SIMD 변환은 이용되지 않는다.

표5

SIMD

후의 메모리 충돌

상기 SIMD 변환 후, 메모리 충돌들은 변형을 구비하지 않는 상기 버전들과 비교할 때, 현저히 감소한다.

2의 제곱수가 아닌 양의 뱅크(

None

power

-

of

-2

amount

of

banks

)

2의 제곱수가 아닌 양 뱅크들은 특정한 커널들을 위한 더 우수한 경과를 발생시킬 수 있다. 실지로, 그것의 영향은 전에 상술된 것처럼, 상기 데이터 레이아웃 최적화와 매우 유사하다. 상기 밀티미디어 및 전자통신 어플리케이션들의 많은 알고리즘들이 2의 제곱, 예를 들어, 8x8 IDCT, 1024포인트 FFT등의 집합 들(multiples)인 액세스 패턴들 뿐 아니라 데이터 세트들도 구비하기 때문이다. 2의 제곱수가 아닌 양의 메모리 뱅크들을 이용함으로써, 다른 뱅크들로의 상기 메모리 요청들은 좀더 공평하게 분배된다. 그러므로, 더 짧은 메모리 큐를 구비하여도 더 적은 메모리 충돌들을 예상할 수 있다. 다음의 실험들은 데이터 레이아웃 및 FFT_radix4를 제외한 SIMD 변환을 구비하지 않는 벤치마크들에 의해 행해졌다.

표 6 2의 제곱수가 아닌 뱅크들을 위한 메모리 충돌

상기 결과들은 혼재된다. 어떤 2의 제곱수가 아닌 값들은 상기 8뱅크 해결책보다 더 우수하다. 예를 들면, 모든 상기 2의 제곱수가 아닌 값들은 8 뱅크들 보다 훨씬 더 우수하다. 하지만, 어떤 2의 제곱수가 아닌 값들은 상기 8비트 해결책, 예를 들어, IDCT_add_block에서 상기 6뱅크 및 9뱅크 보다 훨씬 더 나쁘다. 다른 커널들 및 다른 어플리케이션들을 위한 보편적인 뱅크들의 수를 찾는 것은 어렵다. 이것은 재구성될 수 있는 아키텍처를 위한 아키텍처 선택 - 다른 어플리케이션들을 실행하기 위해 의도된 - 을 어렵게 한다.

둘 째, 뱅크들의 수가 2의 제곱이면, 상기 뱅크 수 및 하나의 뱅크 내의 어드레스 계산은 사소하다. 뱅크들의 수가 2의 제곱이 아니면, 모듈로 연산 및 분배 연산을 하는 여분의 회로들이 필요하다. 더 나아가, 모듈로 연산은 여전히 하나 이상의 여분의 사이클을 차지하고, 이것은 상기 메모리 큐 상부의 성능 오버헤드를 증가시킬 것이다.

완전한

어플리케이션을

위한 실험 결과

완전한 어플리케이션을 위한 메모리 충돌들의 상기 영향을 이해하기 위하여, MPEG-2 디코더를 시뮬레이트한다. 표 7은 결과들을 열거한다. 비엘아이더블유(VLIW) 코드를 위하여, 상기 단순 멀티-뱅크 조직이 이용된다고 가정한다. 상기 감소한 메모리 충돌이 초래된 수행 불이익을 보상할 수 없도록 상기 더 긴 레이턴시가 스칼라 코드(scalar code)에 있는 훨씬 더 높은 오버헤드를 부가하기(impose) 때문이다. 덧붙여, 상기 어레이 부분만큼 많은 사이클 당 메모리 액세스들이 있지 않다. 그러므로, 단순 멀티-뱅크 조직은 통계적으로(statistically) 메모리 충돌들을 회피함으로써 잘 작동한다.

표7

MPEG

-2 디코더를 위한 포괄적인 메모리 충돌

상기 결과로부터, 포괄적인 충돌은 단순 멀티-뱅크 조직을 이용할 때, 그렇게 현저한 것은 아니라는 것을 알 수 있다. 상기 맵핑된 MPEG-2 디코더에서 상기 시간의 반 이하의 시간이 상기 어레이 모드에서 소비되기 때문이다. 그러므로, 상기 어레이 모드에서 상기 고 메모리 충돌은 포괄적인 수행에서 심각한 것으로 보이지 않는다. 하지만, 상기 어플리케이션이 FFT_radix4 같이 더 커널 지배적(kernel-dominated)이라면, 메모리 충돌들은 전반적인 수행에서 훨씬 더 큰 impact를 구비할 것이다.

메모리 대역폭을 증가시키는

스크래치패드

메모리 부가

많은 경우, 스크래치패드 메모리 부가는 상기 메모리 대역폭을 증가시키는 저렴한 방법이다. 예를 들어, IDCT에서, 하나의 작은 버퍼는 상기 메모리 대역폭이 두 배가 되도록 하기 위하여 수평 루프 및 수직 루프간에 일시적인 데이터를 저장할 수 있다. 유사하게, 움직임 보상 및 H.264/AVC 디코더의 디블록킹 필터(deblocking filter)에서, 역시 작은 버퍼들은 일시적인 데이터를 저장하는 것에 이용될 수 있다.

스위칭 수단들 및 일반적 상황들을 지지하는 메모리 큐들을 특징으로 하는 주 메모리 계층(hierarchy)과 달리, 상기 스크래치패드 메모리는 상기 스위칭 수단들 및 메모리 큐를 구비하지 않고 훨씬 단순할 수 있다. 그러나, 또한 데이터 어레이 내에 고 대역폭을 제공하도록 멀티 뱅크되고(multi-banked) 인터리브되어야 한다. 스크래치패드 메모리 하부시스템은 타겟 어플리케이션에서 요구되는 고 메모리 광역폭을 제공할 뿐만 아니라, 전력을 낮춘다. 더 작은 스크래치패드 메모리는 일반적으로 상기 주 메모리 체계와 비교할 때, 액세스 당 더 낮은 에너지를 소비하기 때문이다.

아키텍처적으로, 상기의 스크래치패드 메모리들을 부가하는 것은 어렵지 않다. 핵심 문제는 컴파일러 서포트를 구비하는 것이다. 상기 첫 번째 실시예에서, 컴파일러는 디자이너가 수동으로 다른 메모리 하부시스템들에 대해 상기 맵핑을 이용하도록 하는 인터패이스들을 제공한다. 두 번째 실시예에서, 상기 컴파일러는 자동적으로 상기 스크래치패드 메모리들의 이용을 이용할 수 있다.

부가적인

실시예

비록, 상기 메모리 큐는 뱅크 충돌들을 많이 감소시킬 수 있지만, 향상될 여지가 아직 많다. 만약, 상기 컴파일러가 설계된 시간에서 알려진 정도의 장점을 이용할 수 있다면, 동일한 메모리 큐 사이즈를 구비하는 메모리 충돌들을 감소시키거나, 또는 동일한 양의 메모리 충돌들을 달성하는 메모리 큐 사이즈를 감소시킬 수 있다. 예를 들면, 두 개의 32비트 메모리 액세스들 A[i] 및 A[i+8]은 하나의 8 뱅크 메모리 시스템에서 항상 같은 뱅크로 간다. 반대로, A[i] 및 A[i+1]은 항상 다른 뱅크들에서 발생한다. 그러므로, 그것들은 동일한 사이클에서 스케쥴될 수 있다. 만약, 상기 컴파일러가 상기 정보를 충분히 이용할 수 있다면, 많은 불필요한 버퍼링들 및 잠재적 정지들을 피할 수 있고, 상기 큐 자원들은 좀더 효율적으로 이용될 수 있다. 그러므로, 상기 컴파일러는 상기 정보를 획득하고 나타내고 이것을 상기 컴파일러로 전달하는 상기 소스 코드를 분석하는 프리컴파일러의 도움을 받아야 하고, 상기 스케쥴러(scheduler) 속에 상기 제한들을 구체화하도록(incorporate) 중재되어야 한다.

위에서 지적한 것처럼, 스크래치패드 메모리 부가는 메모리 대역폭을 증가시키고, 전력 소비를 감소시키는 저렴한 방법이다. 하지만, 상기 컴파일러는 상기 스크래치패드 메모리 접근을 지지해야 한다. 만약, 크로스바가 상기 스크래치패드 메모리 시스템에서 이용되지 않는다면, 정확한 데이터 분석 및 변형 기술들이 FU 각각이 단지 첨부의 메모리 뱅크로 접근하는 것을 보장하는데 필수적이다. 실지로, 상기 메모리 액세스를 특정한 스크래치패드 메모리 시스템으로 수동으로 특정하는 고유(intrinsic) 기능들을 이용하는 것이 가능하다. 고유 기능은 SIMD 액세스 를 지지하는 현재의 컴파일러 및 다른 특별화된 지시들에서 이미 실행된다.

여기서는 단지 1단계의 메모리 조직을 논의한 것이고, 상기 1단계 메모리는 하드웨어 기반의 캐시 또는 소프트웨어로 제어되는 캐시일 수 있다. 상기 메모리 체계에서 더 단계를 구비할 가능성이 있다. 일반적으로, SDRAM 기반의 주 메모리가 있어야 한다. 1단계 메모리 및 다른 단계들 간의 상기 데이터 전송은 전형적으로 DMA 컨트롤러를 통해 수행된다.

Claims (23)

- 둘 이상의 기능 유닛;하나 이상의 메모리 장치; 및기능 유닛 각각을 위하여 요청 및 상기 요청과 관련된 태그를 버퍼링하도록 중재된 하나 이상의 메모리 큐를 포함하고,상기 메모리 큐 각각은 하나의 기능 유닛과 관련되고,상기 하나 이상의 메모리 장치는 상기 둘 이상의 메모리 큐들과 연결되고,상기 하나 이상의 메모리 큐는, 버퍼링된 요청이 미리 결정된 레이턴시 내에 서비스될 수 없도록 상기 메모리 큐 내에서 대기 중일 때, 기능 유닛을 정지시키도록 중재되고, 상기 정지는 상기 태그에 기초하여 수행되는 것을 특징으로 하는 멀티-프로세서 시스템.

- 제1항에 있어서,상기 하나 이상의 메모리 큐는 상기 메모리 큐가 대기 중인 요청이 레이턴시를 충족할 가능성을 예상하면, 정지한 기능 유닛을 재활성화 하도록 더 중재된 것을 특징으로 하는 멀티-프로세서 시스템.

- 제1항 또는 제2항 중 어느 한 항에 있어서,복수의 메모리 장치를 포함하고,각 기능 유닛을 위한 메모리 큐의 수는 하나 이상 메모리 장치의 수까지이고,상기 멀티-프로세서 시스템은 어느 메모리 큐 출력이 어느 메모리 장치로 메모리 액세스를 하는지를 선택하는 스위칭 수단을 더 포함하는 것을 특징으로 하는 멀티-프로세서 시스템.

- 제1항 내지 제3항 중 어느 한 항에 있어서,각 메모리 장치를 위한 메모리 큐의 수는 하나 이상 기능 유닛의 수까지이고,상기 멀티-프로세서 시스템은 어느 메모리 큐 출력이 어느 기능 유닛으로 데이터를 전달하는지를 선택하는 스위칭 수단을 더 포함하는 것을 특징으로 하는 멀티-프로세서 시스템.

- 제3항 또는 제4항 중 어느 한 항에 있어서,상기 스위칭 수단은 하나 이상의 멀티플렉서를 포함하는 것을 특징으로 하는 멀티-프로세서 시스템.

- 제5항에 있어서,상기 스위칭 수단은 메모리 장치 당 하나의 멀티플렉서를 포함하는 것을 특 징으로 하는 멀티-프로세서 시스템.

- 상기 제1항 내지 제6항 중 어느 한 항에 있어서,상기 메모리 장치의 수는 기능 유닛의 수의 4배보다 적은 것을 특징으로 하는 멀티-프로세서 시스템.

- 상기 제1항 내지 제7항 중 어느 한 항에 있어서,메모리 장치는 싱글 포트 또는 듀얼 포트인 것을 특징으로 하는 멀티-프로세서 시스템.

- 상기 제1항 내지 제8항 중 어느 한 항에 있어서,상기 기능 유닛의 수는 8개 이상인 것을 특징으로 하는 멀티-프로세서 시스템.

- 상기 제1항 내지 제9항 중 어느 한 항에 있어서,상기 기능 유닛 당 상기 메모리 큐의 수는 상기 메모리 장치의 수와 동일한 것을 특징으로 하는 멀티-프로세서 시스템.

- 제10항에 있어서,메모리 장치 각각은 상기 기능 유닛 각각의 메모리 큐와 관련되는 것을 특징 으로 하는 멀티-프로세서 시스템.

- 상기 제1항 내지 제11항의 어느 한 항에 있어서,상기 메모리 장치의 수는 2의 거듭제곱이 아닌 것을 특징으로 하는 멀티-프로세서 시스템.

- 상기 제1항 내지 제12항 중 어느 한 항에 있어서,상기 기능 유닛과 관련된 상기 메모리 큐를 바이패스하도록, 기능 유닛 및 메모리 장치 간에 바이패스 수단을 더 포함하는 것을 특징으로 하는 멀티-프로세서 시스템.

- 상기 제1항 내지 제13항 중 어느 한 항에 있어서,상기 하나 이상의 메모리 장치에서 출력되는 데이터의 정확한 순서를 저장하는 재정렬 레지스터 파일을 더 포함하는 것을 특징으로 하는 멀티-프로세서 시스템.

- 상기 제1항 내지 제14항 중 어느 한 항에 있어서,메모리 액세스를 저 저장 비용 표현으로 저장하는 부가적인 스토리지 유닛; 및서비스할 메모리 액세스를 선택하고, 상기 메모리 장치로 제어 신호를 제공 하고, 상기 선택된 메모리 액세스를 서비스하는 제어 수단을 더 포함하는 것을 특징으로 하는 멀티-프로세서 시스템.

- 상기 제1항 내지 제15항 중 어느 한 항에 있어서,상기 하나 이상의 메모리 장치는 캐시 메모리인 것을 특징으로 하는 멀티-프로세서 시스템.

- 제17항에 있어서,주 메모리에 기초하는 싱크로너스 다이나믹 램을 더 포함하는 것을 특징으로 하는 멀티-프로세서 시스템.

- 상기 제1항 내지 제17항 중 어느 한 항에 있어서,부가적인 메모리들; 및상기 하나 이상의 메모리 장치 및 상기 부가적 메모리 간에 데이터를 전달하는 디엠에이 컨트롤러를 더 포함하는 것을 특징으로 하는 멀티-프로세서 시스템.

- 둘 이상의 메모리 장치를 포함하고, 둘 이상의 기능 유닛들 및 기능 유닛들 각각을 위한 하나 이상의 메모리 큐를 포함하는 디지털 시스템이고,메모리 큐 각각은 하나의 기능 유닛과 관련되고, 메모리 장치 각각은 둘 이상의 메모리 큐와 연결되고, 메모리 액세스는 상기 메모리 큐에 임시 저장되는, 메 모리 배열로 향하는 어느 메모리 액세스가 서비스되어야 하는지를 결정하는 방법에 있어서,상기 메모리 큐에 저장되고, 미리 정의된 레이턴시로 초기화된 태그 값을 가지는 태그를 상기 메모리 액세스 각각과 관련시키는 단계;상기 태그 값에 기초하여, 메모리 배열을 향하는 어느 메모리 액세스가 서비스되어야 하는지 결정하는 단계; 및상기 결정된 메모리 액세스를 서비스하고 상기 태그 값을 감소시키는 단계를 포함하는 것을 특징으로 하는 방법.

- 둘 이상의 메모리 장치를 포함하고, 둘 이상의 기능 유닛들 및 기능 유닛들 각각을 위한 하나 이상의 메모리 큐를 포함하는 디지털 시스템이고,메모리 큐 각각은 하나의 기능 유닛과 관련되고, 메모리 장치 각각은 둘 이상의 메모리 큐와 연결되고, 메모리 액세스는 상기 메모리 큐에 임시 저장되는, 메모리 배열로 향하는 어느 메모리 액세스가 서비스되어야 하는지를 결정하는 방법에 있어서,스토리지 유닛에 메모리 액세스 각각을 저 저장 비용 표현으로 저장하는 단계;메모리 배열로 향하는 어느 메모리 액세스가 서비스되어야 하는지를 결정하기 위하여, 상기 스토리지 유닛 내에서의 참조 위치에 대하여 상대적으로, 메모리 액세스의 상기 저 저장 비용 표현 중 하나 이상의 위치를 결정하는 것을 포함하는 작동을 상기 스토리지 유닛에 대하여 수행하는 단계;상기 상대적 위치로부터 상기 스토리지 유닛에 얼마나 길게 상기 저 저장 비용 표현이 있는지 결정하는 단계;상기 스토리지 유닛에서 가장 긴 상기 표현들 중 하나 또는 그 이상을 선택하는 단계; 및상기 참조 위치를 변경하는 단계를 포함하는 것을 특징으로 하는 방법.

- 제20항에 있어서,상기 스토리지 유닛은 선입 선출 기관으로 둘러싸인 것을 특징으로 하는 방법.

- 제20항 또는 제21항 중 어느 한 항에 있어서,상기 저 저장 비용 표현은 1 비트(bit)인 것을 특징으로 하는 방법.

- 제20항 내지 제22항 중 어느 한 항에 있어서,하나보다 많은 표현이 선택된 경우, 랜덤한 방법으로 하나의 표현의 선택을 더 수행하는 것을 특징으로 하는 방법.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US69550605P | 2005-06-30 | 2005-06-30 | |

| US60/695,506 | 2005-06-30 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20080025053A true KR20080025053A (ko) | 2008-03-19 |

| KR100990902B1 KR100990902B1 (ko) | 2010-11-01 |

Family

ID=37106271

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020077028352A KR100990902B1 (ko) | 2005-06-30 | 2006-06-30 | 멀티-프로세서 시스템을 위한 메모리 배열 |

Country Status (5)

| Country | Link |

|---|---|

| EP (2) | EP1896983B1 (ko) |

| JP (1) | JP5117383B2 (ko) |

| KR (1) | KR100990902B1 (ko) |

| AT (1) | ATE520086T1 (ko) |

| WO (1) | WO2007003370A2 (ko) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8813073B2 (en) | 2010-12-17 | 2014-08-19 | Samsung Electronics Co., Ltd. | Compiling apparatus and method of a multicore device |

| US9086959B2 (en) | 2009-10-13 | 2015-07-21 | Samsung Electronics Co., Ltd. | Apparatus to access multi-bank memory |

| KR20200013447A (ko) * | 2018-07-30 | 2020-02-07 | 숭실대학교산학협력단 | 블록체인 지갑 시스템의 캐시 부 채널 공격 방지 장치 및 방법, 상기 방법을 수행하기 위한 기록 매체 |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI543185B (zh) | 2005-09-30 | 2016-07-21 | 考文森智財管理公司 | 具有輸出控制之記憶體及其系統 |

| US20070076502A1 (en) | 2005-09-30 | 2007-04-05 | Pyeon Hong B | Daisy chain cascading devices |

| US7652922B2 (en) | 2005-09-30 | 2010-01-26 | Mosaid Technologies Incorporated | Multiple independent serial link memory |

| US7747833B2 (en) | 2005-09-30 | 2010-06-29 | Mosaid Technologies Incorporated | Independent link and bank selection |

| US11948629B2 (en) | 2005-09-30 | 2024-04-02 | Mosaid Technologies Incorporated | Non-volatile memory device with concurrent bank operations |

| KR101388134B1 (ko) * | 2007-10-01 | 2014-04-23 | 삼성전자주식회사 | 뱅크 충돌 방지 장치 및 방법 |

| EP2110757A1 (en) | 2008-04-14 | 2009-10-21 | Imec | Device and method for parallelizing multicarrier demodulation |

| CN101547209B (zh) * | 2009-05-15 | 2012-01-04 | 杭州华三通信技术有限公司 | 一种信息表项的更新方法和设备 |

| KR101862799B1 (ko) | 2011-12-12 | 2018-05-31 | 삼성전자주식회사 | 메모리 컨트롤러 및 메모리 컨트롤 방법 |

| WO2013100783A1 (en) | 2011-12-29 | 2013-07-04 | Intel Corporation | Method and system for control signalling in a data path module |

| US9274964B2 (en) * | 2012-02-02 | 2016-03-01 | Qualcomm Incorporated | Multi-bank cache memory |

| JP6115564B2 (ja) * | 2012-03-13 | 2017-04-19 | 日本電気株式会社 | データ処理システム、半導体集積回路およびその制御方法 |

| US9507541B2 (en) * | 2012-12-25 | 2016-11-29 | Nec Corporation | Computation device, computation method, and medium |

| KR20140131781A (ko) * | 2013-05-06 | 2014-11-14 | 삼성전자주식회사 | 메모리 제어 장치 및 방법 |

| US10331583B2 (en) | 2013-09-26 | 2019-06-25 | Intel Corporation | Executing distributed memory operations using processing elements connected by distributed channels |

| JP6331944B2 (ja) * | 2014-10-07 | 2018-05-30 | 富士通株式会社 | 情報処理装置、メモリ制御装置及び情報処理装置の制御方法 |

| US11086816B2 (en) | 2017-09-28 | 2021-08-10 | Intel Corporation | Processors, methods, and systems for debugging a configurable spatial accelerator |

| US11307873B2 (en) | 2018-04-03 | 2022-04-19 | Intel Corporation | Apparatus, methods, and systems for unstructured data flow in a configurable spatial accelerator with predicate propagation and merging |

| US10686714B2 (en) | 2018-04-27 | 2020-06-16 | Avago Technologies International Sales Pte. Limited | Traffic management for high-bandwidth switching |

| US10567307B2 (en) | 2018-04-27 | 2020-02-18 | Avago Technologies International Sales Pte. Limited | Traffic management for high-bandwidth switching |

| US11200186B2 (en) | 2018-06-30 | 2021-12-14 | Intel Corporation | Apparatuses, methods, and systems for operations in a configurable spatial accelerator |

| US10891240B2 (en) | 2018-06-30 | 2021-01-12 | Intel Corporation | Apparatus, methods, and systems for low latency communication in a configurable spatial accelerator |

| US10853073B2 (en) | 2018-06-30 | 2020-12-01 | Intel Corporation | Apparatuses, methods, and systems for conditional operations in a configurable spatial accelerator |

| US10915471B2 (en) | 2019-03-30 | 2021-02-09 | Intel Corporation | Apparatuses, methods, and systems for memory interface circuit allocation in a configurable spatial accelerator |

| US11037050B2 (en) * | 2019-06-29 | 2021-06-15 | Intel Corporation | Apparatuses, methods, and systems for memory interface circuit arbitration in a configurable spatial accelerator |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01169565A (ja) * | 1987-12-24 | 1989-07-04 | Fujitsu Ltd | マルチプロセッサ制御方式 |

| US5214769A (en) * | 1987-12-24 | 1993-05-25 | Fujitsu Limited | Multiprocessor control system |

| JPH03257534A (ja) * | 1990-03-07 | 1991-11-18 | Nec Corp | メモリ割り当て方式 |

| US5293607A (en) * | 1991-04-03 | 1994-03-08 | Hewlett-Packard Company | Flexible N-way memory interleaving |

| JPH06314264A (ja) * | 1993-05-06 | 1994-11-08 | Nec Corp | セルフ・ルーティング・クロスバー・スイッチ |

| US6564304B1 (en) * | 2000-09-01 | 2003-05-13 | Ati Technologies Inc. | Memory processing system and method for accessing memory including reordering memory requests to reduce mode switching |

| DE60118617T2 (de) * | 2000-11-03 | 2007-07-05 | Broadcom Corp., Irvine | Vorrichtung und verfahren zum pipeline-mehrfachspeicherzugriff |

| US6963962B2 (en) * | 2002-04-11 | 2005-11-08 | Analog Devices, Inc. | Memory system for supporting multiple parallel accesses at very high frequencies |

| EP1512078B1 (en) * | 2002-05-24 | 2012-04-11 | Silicon Hive B.V. | Programmed access latency in mock multiport memory |

-

2006

- 2006-06-30 JP JP2008518741A patent/JP5117383B2/ja active Active

- 2006-06-30 AT AT06762309T patent/ATE520086T1/de not_active IP Right Cessation

- 2006-06-30 EP EP06762309A patent/EP1896983B1/en active Active

- 2006-06-30 WO PCT/EP2006/006375 patent/WO2007003370A2/en not_active Application Discontinuation

- 2006-06-30 EP EP10184465A patent/EP2317446A1/en not_active Withdrawn

- 2006-06-30 KR KR1020077028352A patent/KR100990902B1/ko active IP Right Grant

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9086959B2 (en) | 2009-10-13 | 2015-07-21 | Samsung Electronics Co., Ltd. | Apparatus to access multi-bank memory |

| US8813073B2 (en) | 2010-12-17 | 2014-08-19 | Samsung Electronics Co., Ltd. | Compiling apparatus and method of a multicore device |

| KR20200013447A (ko) * | 2018-07-30 | 2020-02-07 | 숭실대학교산학협력단 | 블록체인 지갑 시스템의 캐시 부 채널 공격 방지 장치 및 방법, 상기 방법을 수행하기 위한 기록 매체 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP1896983A2 (en) | 2008-03-12 |

| WO2007003370A2 (en) | 2007-01-11 |

| JP5117383B2 (ja) | 2013-01-16 |

| JP2008545187A (ja) | 2008-12-11 |

| WO2007003370A3 (en) | 2007-04-05 |

| KR100990902B1 (ko) | 2010-11-01 |

| EP2317446A1 (en) | 2011-05-04 |

| EP1896983B1 (en) | 2011-08-10 |

| ATE520086T1 (de) | 2011-08-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100990902B1 (ko) | 멀티-프로세서 시스템을 위한 메모리 배열 | |

| US8560795B2 (en) | Memory arrangement for multi-processor systems including a memory queue | |

| US5323489A (en) | Method and apparatus employing lookahead to reduce memory bank contention for decoupled operand references | |

| Rixner et al. | Memory access scheduling | |

| US5822772A (en) | Memory controller and method of memory access sequence recordering that eliminates page miss and row miss penalties | |

| US8554820B2 (en) | Optimized corner turns for local storage and bandwidth reduction | |

| EP0637799A2 (en) | Shared cache for multiprocessor system | |

| US20070143582A1 (en) | System and method for grouping execution threads | |

| Buntinas et al. | Data transfers between processes in an SMP system: Performance study and application to MPI | |

| JP4699468B2 (ja) | プロセッサ内の命令のソース・オペランドを供給するための方法及び装置 | |

| US20020103990A1 (en) | Programmed load precession machine | |

| WO2002033570A2 (en) | Digital signal processing apparatus | |

| US20100325631A1 (en) | Method and apparatus for increasing load bandwidth | |

| CN107562549B (zh) | 基于片上总线和共享内存的异构众核asip架构 | |

| KR20010080208A (ko) | 처리 시스템 스케쥴링 | |

| Moeng et al. | ContextPreRF: Enhancing the performance and energy of GPUs with nonuniform register access | |

| Ausavarungnirun | Techniques for shared resource management in systems with throughput processors | |

| US7370158B2 (en) | SIMD process with multi-port memory unit comprising single-port memories | |

| JP2004503872A (ja) | 共同利用コンピュータシステム | |

| De La Luz et al. | Improving off-chip memory energy behavior in a multi-processor, multi-bank environment | |

| US20040111567A1 (en) | SIMD processor with multi-port memory unit | |

| Yuan et al. | High performance matrix multiplication on many cores | |

| Yu et al. | Study on fine-grained synchronization in many-core architecture | |

| US20060026308A1 (en) | DMAC issue mechanism via streaming ID method | |

| Tanskanen et al. | Parallel memory architecture for TTA processor |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20131007 Year of fee payment: 4 |

|

| FPAY | Annual fee payment |

Payment date: 20181015 Year of fee payment: 9 |

|

| FPAY | Annual fee payment |

Payment date: 20191001 Year of fee payment: 10 |