KR20060043201A - 정보 처리 시스템 및 정보 처리 방법과, 컴퓨터 프로그램 - Google Patents

정보 처리 시스템 및 정보 처리 방법과, 컴퓨터 프로그램 Download PDFInfo

- Publication number

- KR20060043201A KR20060043201A KR1020050016163A KR20050016163A KR20060043201A KR 20060043201 A KR20060043201 A KR 20060043201A KR 1020050016163 A KR1020050016163 A KR 1020050016163A KR 20050016163 A KR20050016163 A KR 20050016163A KR 20060043201 A KR20060043201 A KR 20060043201A

- Authority

- KR

- South Korea

- Prior art keywords

- information processing

- processing apparatus

- address

- storage space

- public area

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/16—Combinations of two or more digital computers each having at least an arithmetic unit, a program unit and a register, e.g. for a simultaneous processing of several programs

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/46—Multiprogramming arrangements

- G06F9/50—Allocation of resources, e.g. of the central processing unit [CPU]

- G06F9/5005—Allocation of resources, e.g. of the central processing unit [CPU] to service a request

- G06F9/5011—Allocation of resources, e.g. of the central processing unit [CPU] to service a request the resources being hardware resources other than CPUs, Servers and Terminals

- G06F9/5016—Allocation of resources, e.g. of the central processing unit [CPU] to service a request the resources being hardware resources other than CPUs, Servers and Terminals the resource being the memory

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/10—Address translation

- G06F12/1027—Address translation using associative or pseudo-associative address translation means, e.g. translation look-aside buffer [TLB]

- G06F12/1036—Address translation using associative or pseudo-associative address translation means, e.g. translation look-aside buffer [TLB] for multiple virtual address spaces, e.g. segmentation

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/10—Address translation

- G06F12/109—Address translation for multiple virtual address spaces, e.g. segmentation

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/14—Protection against unauthorised use of memory or access to memory

- G06F12/1458—Protection against unauthorised use of memory or access to memory by checking the subject access rights

- G06F12/1466—Key-lock mechanism

- G06F12/1475—Key-lock mechanism in a virtual system, e.g. with translation means

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Software Systems (AREA)

- Computer Hardware Design (AREA)

- Storage Device Security (AREA)

- Information Transfer Between Computers (AREA)

- Memory System (AREA)

- Information Retrieval, Db Structures And Fs Structures Therefor (AREA)

Abstract

네트워크 경유로 제휴 동작하는 정보 처리 장치 사이에서 기억 공간의 공유를 행한다. 각 정보 처리 장치는 하나 이상의 물리 기억 장치를 구비하고, 각 물리 기억 장치의 물리 기억 공간, 즉 물리 세그먼트 어드레스를, 논리적인 기억 공간, 즉 가상 어드레스 공간에 맵핑하여, 논리 기억 공간 상에서 처리의 실행이 행하여진다. 본 실시예에서는, 정보 처리 장치가 다른 정보 처리 장치로부터 공개 영역의 사용이 허가되었을 때에는, 이 공개 영역의 물리 세그먼트 어드레스를, 자 장치의 가상 어드레스 공간의 가상 세그먼트 어드레스에 맵핑하여 사용한다.

네트워크, 자 장치, 마스터, 슬레이브, 공개 영역, 메인 프로세서, 서브 프로세서, STB, 액세스 요구

Description

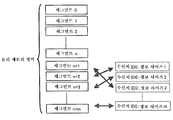

도 1은 본 발명의 일 실시예에 따른 네트워크 시스템의 구성을 도시한 도면.

도 2는 서브 프로세서(23)로부터 메인 메모리(24)에의 액세스 수순을 설명하기 위한 도면.

도 3은 소프트웨어 셀의 구성예를 도시한 도면.

도 4는 DMA 커맨드가 스테이터스 회신 커맨드인 경우의 소프트웨어 셀의 데이터 영역을 도시한 도면.

도 5는 복수의 정보 처리 장치가 가상적인 1대의 정보 처리 장치로서 동작하는 모습을 도시한 도면.

도 6은 정보 처리 컨트롤러의 소프트웨어 구성의 일례를 도시한 도면.

도 7은 4대의 정보 처리 장치가 가상적인 1대의 정보 처리 장치로서 동작하는 모습을 도시한 도면.

도 8은 도 7에 도시한 시스템에서의 분산 처리의 예를 도시한 도면.

도 9는 각 정보 처리 장치 및 시스템의 구체예를 도시한 도면.

도 10은 도 9 중의 하드디스크 레코더의 하드웨어 구성을 도시한 도면.

도 11은 도 9 중의 하드디스크 레코더의 소프트웨어 구성을 도시한 도면.

도 12는 도 9 중의 PDA의 하드웨어 구성을 도시한 도면.

도 13은 도 9 중의 PDA의 소프트웨어 구성을 도시한 도면.

도 14는 도 9 중의 포터블 CD 플레이어의 하드웨어 구성을 도시한 도면.

도 15는 도 9 중의 포터블 CD 플레이어의 소프트웨어 구성을 도시한 도면.

도 16은 본 발명의 일 실시예에 따른 네트워크 시스템의 구성을 모식적으로 도시한 도면.

도 17은 정보 처리 장치가 공개 영역을 형성하기 위한 처리를 설명하기 위한 도면.

도 18은 정보 처리 장치가 공개 영역을 형성하기 위한 처리를 설명하기 위한 도면.

도 19는, 공개 데이터 및 비공개 데이터를 포함하는 다양한 데이터를 관리하는 서버 장치에서, 공개 데이터를 공개 영역에서 유지하는 모습을 도시한 도면.

도 20은 네트워크 접속되어 제휴 동작하는 2대의 셋톱 박스(STB)의 한쪽 STB(a)가 서버, 다른 쪽 STB(b)가 클라이언트로 되어, STB(b)에 STB(a)의 정보를 맵핑한 모습을 도시한 도면.

도 21은 1대의 셋톱 박스 STB(a)가 2대의 셋톱 박스 STB(b) 및 STB(c)에 공개 영역의 사용을 허가하고 있는 모습을 도시한 도면.

도 22는 1대의 셋톱 박스 STB(b)가 2대의 셋톱 박스 STB(a) 및 STB(c)로부터 사용이 허가된 공개 영역을 사용하고 있는 모습을 도시한 도면.

도 23은 공개 영역을 요구하는 정보 처리 장치와 공개 영역을 제공하는 정보 처리 장치 사이에서 행해지는 요구 및 허가 응답에 관한 핸드 쉐이크 수순을 도시한 흐름도.

도 24는 정보 처리 장치 STB(a)의 물리 메모리 공간 상의 공개 영역을 STB(b)측의 가상 메모리 공간에 할당하기 위한 동작 시퀀스를 도시한 도면.

도 25는 맵핑 테이블의 구성을 모식적으로 도시한 도면.

도 26은 정보 처리 장치 STB(b)가 정보 처리 장치 STB(a)의 공개 영역에 액세스하기 위한 동작 시퀀스를 도시한 도면.

도 27은 정보 처리 장치 STB(b)에서의 메모리 액세스의 수순을 설명하기 위한 도면.

<도면의 주요 부분에 대한 부호의 설명>

1, 2, 3, 4, 5, 6 : 정보 처리 장치

7 : 가상적인 1대의 정보 처리 장치

11, 12, 13, 14, 15, 16 : 정보 처리 컨트롤러

21-1∼21-4 : 메인 프로세서

22-1∼22-4 : 메인 프로세서 내 LS(로컬 스토리지)

23-1∼23-12 : 서브 프로세서

24-1∼24-12 : 서브 프로세서 내 LS(로컬 스토리지)

25-1∼25-4 : DMAC

26-1∼26-4 : 메인 메모리

27-1∼27-4 : DC

28-1∼28-6 : 외부 기록부

[문헌 1] 일본특허공개 2002-342165호 공보

[문헌 2] 일본특허공개 2002-351850호 공보

[문헌 3] 일본특허공개 2002-358289호 공보

[문헌 4] 일본특허공개 2002-366533호 공보

[문헌 5] 일본특허공개 2002-366534호 공보

[문헌 6] 일본특허공개 평8-95928호 공보

본 발명은 네트워크 접속된 2 이상의 기기 간에서의 동작을 제휴시키는 정보 처리 시스템 및 정보 처리 방법과, 컴퓨터 프로그램에 관한 것으로, 특히, 네트워크로 접속된 2 이상의 기기 간에서의 동작을 제휴시키는 정보 처리 시스템 및 정보 처리 방법과, 컴퓨터 프로그램에 관한 것이다.

더욱 상세하게는, 본 발명은 네트워크 접속된 복수의 기기가 협조 동작에 의해 분산 처리를 행함으로써, 가상적으로 1대의 기기로서 동작하는 정보 처리 시스템 및 정보 처리 방법과, 컴퓨터 프로그램에 관한 것으로, 특히, 네트워크 경유로 제휴 동작하는 정보 처리 장치 사이에서 기억 공간의 공유를 행하는 정보 처리 시스템 및 정보 처리 방법과, 컴퓨터 프로그램에 관한 것이다.

복수의 컴퓨터끼리 네트워크로 상호 접속함으로써, 정보 자원의 공유, 하드웨어 자원의 공유, 복수의 사용자 사이에서의 콜레보레이션이 실현되는 것이 알려져 있다. 컴퓨터 간의 접속 미디어로서, LAN(Local Area Network), WAN(Wide Area Network), 인터넷 등 다양하다.

특히 최근에는 일반 가정 내에도 컴퓨터나 네트워크 등의 기술이 깊게 침투되어 오고 있다. 가정 내의 퍼스널 컴퓨터나 PDA(Personal Digital Assistants) 등의 정보 기기, 나아가서는 텔레비전 수상기나 비디오 재생 장치 등 AV 기기나, 각종 정보 가전, CE(Consumer Electronics) 기기 등이 홈 네트워크 경유로 상호 접속되어 있다. 또한, 이러한 홈 네트워크는 대부분의 경우, 라우터 경유로 인터넷을 비롯한 외부의 광역 네트워크에 상호 접속되어 있다.

이와 같이 홈 네트워크 상에 복수의 AV 기기가 접속된다고 하는 이용 형태가 상정되지만, 지금까지는 AV 기기 사이에서 충분한 제휴가 이루어져 있지 않다고 하는 문제가 있다.

이러한 문제에 대하여, 최근에는, 네트워크 상의 기기끼리 제휴시키기 위해서, 기기의 협조 동작에 의해 높은 연산 성능을 실현한다고 하는 그리드 컴퓨팅 기술에 관한 연구 개발이 진행되고 있다(예를 들면, 특허 문헌 1 내지 5를 참조할 것).

이 그리드 컴퓨팅 기술에 따르면, 네트워크 상의 복수의 정보 처리 장치가 강조 동작하여 분산 처리를 행하고, 사용자로부터는 가상적으로 1대의 정보 처리 장치로서 동작할 수 있다.

예를 들면, 녹화 예약 기능을 갖는 복수 대의 정보 처리 장치가 네트워크 상에 접속되어 있는 경우, 녹화 예약의 제휴 동작을 실현할 수 있다. 즉, 복수 대의 정보 처리 장치가 홈 네트워크 경유로 녹화 예약의 동작을 제휴시키고 있는 경우, 홈 네트워크 상에서는 가상적으로 1대의 녹화 기기로서 동작한다. 따라서, 사용자는 어느 하나의 기기의 사용자 인터페이스를 이용하여, 홈 네트워크에 접속되어 있는 임의의 기기를 이용하여 녹화 예약을 행할 수 있다.

또한, 이러한 녹화 예약 기능의 제휴에 의해, 예약 시간이 중복된 프로그램(소위 대항 프로그램)을 동시 녹화하는 것이 가능하다. 마찬가지로, 기록한 콘텐츠의 재생 동작을 복수의 기기 간에서 제휴시켜, 동시·동기적인 콘텐츠 재생을 실현할 수 있다. 이 콘텐츠 재생 기능의 제휴에 의해, 별개의 기기에서 기록된 콘텐츠의 재생을 동시, 동기적으로 진행시킴으로써, 콘텐츠 재생에서 채널 전환의 개념을 도입할 수 있다.

이러한 가상적인 1대의 기기에 따르면, 1대의 기기의 하드웨어 자원이나 처리 능력만으로는 사용자로부터의 요구에 응답할 수 없는 경우에도, 네트워크 상에서 제휴·협조 동작하는 다른 기기에서의 잉여 처리 능력을 활용함으로써, 사용자의 요구에 응답할 수 있고, 또한 통상의 1대의 기기에서는 현실적이지 않은 서비스를 실현할 수 있다.

한편, 이러한 가상적인 1대의 정보 처리 시스템에서는, 시스템을 구성하는 정보 처리 장치마다 하드웨어 구성이나 처리 능력, 나아가서는 현재의 처리 부하가 구구하여, 잉여의 처리 능력이 불균일하다고 하는 문제가 있다.

이러한 경우, 네트워크 경유로 제휴하고 있는 정보 처리 장치에서는 잉여의 처리 능력이 없고, 또한 메모리 자원이 결핍되어 있는 한편, 다른 정보 처리 장치에서는 잉여의 처리 능력이 있고, 오퍼레이팅 시스템에서 미사용의 메모리 영역이 충분히 남아 있다고 하는 낭비적 상황이 생길 수 있다.

예를 들면, LAN 회선에 접속된 복수의 컴퓨터 간에서의 메모리의 융통 사용을 가능하게 하고, 메모리 자원의 유효 활용과 스와핑 처리의 고속화를 실현하는 메모리 공유 방식에 대하여 제안이 이루어져 있다(예를 들면, 특허 문헌 6을 참조할 것).

이 경우, 메모리 요구 컴퓨터로부터의 메모리 할당 요구에 응답하여 메모리 할당을 행하는 공유 메모리를 구비한 메모리 관리 컴퓨터를 LAN 상에 미리 설치하는 것이다. 바꿔 말하면, 메모리 요구 컴퓨터와 메모리 관리 컴퓨터는, 메모리 할당 요구에 관한 수속 이외에는 각각 독립하여 동작하는 것이고, 네트워크 상의 각 정보 처리 장치가 제휴하여 가상적으로 1대의 정보 처리 장치로서 동작하는 그리드 컴퓨팅과는 상위하다.

또한, 이 경우, 메모리 요구 컴퓨터측에서는, 다른 컴퓨터로부터 할당된 공유 메모리를 자신의 메모리 공간에 할당하는 것이 아니며, 이 때문에 공유 메모리에의 액세스는 어디까지나 LAN 경유에서의 네트워크 동작임에 틀림없다. 즉, 메모리 요구 컴퓨터측에서는, 공유 메모리에의 액세스를 자신의 메인 메모리에의 액세스와 투과적으로 행할 수 없다.

[특허 문헌 1] 일본특허공개 2002-342165호 공보

[특허 문헌 2] 일본특허공개 2002-351850호 공보

[특허 문헌 3] 일본특허공개 2002-358289호 공보

[특허 문헌 4] 일본특허공개 2002-366533호 공보

[특허 문헌 5] 일본특허공개 2002-366534호 공보

[특허 문헌 6] 일본특허공개 평8-95928호 공보

본 발명의 목적은, 네트워크 접속된 복수의 기기가 협조 동작에 의해 분산 처리를 행함으로써, 가상적으로 1대의 기기로서 동작 할 수 있는, 우수한 정보 처리 시스템 및 정보 처리 방법과, 컴퓨터 프로그램을 제공하는 데에 있다.

본 발명의 또 다른 목적은, 네트워크 경유로 제휴 동작하는 정보 처리 장치 사이에서 기억 공간의 공유를 행할 수 있는, 우수한 정보 처리 시스템 및 정보 처리 방법과, 컴퓨터 프로그램을 제공하는 데에 있다.

본 발명은 상기 과제를 참작하여 이루어진 것으로, 그 제1 측면은, 네트워크 접속되는 복수의 정보 처리 장치의 제휴 동작에 의해 가상적으로 1대의 가상 정보 처리 장치로서 동작하는 정보 처리 시스템으로서,

각 정보 처리 장치는 물리 기억 장치를 구비하고,

적어도 하나의 정보 처리 장치는, 자 장치의 물리 기억 장치의 물리 기억 공간 상에 다른 정보 처리 장치의 사용을 허가하는 공개 영역을 형성하고, 다른 정보 처리 장치로부터의 공개 영역의 사용 요구에 응답하여 사용을 허가하는 것을 특징 으로 하는 정보 처리 시스템이다.

단, 여기서 말하는 「시스템」이란, 복수의 장치(또는, 특정한 기능을 실현하는 기능 모듈)가 논리적으로 집합한 것을 말하며, 각 장치나 기능 모듈이 단일 케이싱 내에 있는지의 여부는 특별히 묻지 않는다.

본 발명에 따른 정보 처리 시스템은, 구체적으로 설명하면, 네트워크 접속되는 복수의 정보 처리 장치의 제휴 동작에 의해 가상적으로 1대의 가상 정보 처리 장치로서 동작한다. 그리고, 가상 정보 처리 장치를 구성하는 적어도 하나의 정보 처리 장치는, 자 장치의 물리 기억 장치의 물리 기억 공간 상에 다른 정보 처리 장치의 사용을 허가하는 공개 영역을 형성한다. 여기서 말하는 물리 기억 장치에는, 메인 메모리나 그 밖의 로컬 메모리, 하드디스크 등의 외부 기억 장치, 나아가서는 자 장치에 로컬 접속되는 각 기기에의 입출력을 할당한 I/O 공간이 포함되고, 제휴 동작을 행하는 정보 처리 장치 사이에서, 이들 정보 자원을 공유하는 것이 가능하게 된다.

이러한 정보 자원의 공유는, 공개 영역을 요구하는 정보 처리 장치와, 공개 영역을 제공하는 정보 처리 장치 사이에서의, 요구 및 허가 응답에 관한 소정의 핸드 쉐이크 수순에 따라서 실현된다. 이 핸드 쉐이크 수순에는 정보 처리 장치 사이의 상호 인증 등의 처리를 포함하여도 된다.

여기서, 공개 영역을 형성한 정보 처리 장치는, 자신의 공개 영역을 분할하고, 다른 복수의 정보 처리 장치에 대하여 동시에 사용 허가를 주도록 하여도 된다. 혹은, 정보 처리 장치는, 다른 2 이상의 정보 처리 장치가 형성한 공개 영역 의 사용을 요구하고, 사용이 허가된 2 이상의 정보 처리 장치의 공개 영역을 동시에 사용하도록 하여도 된다.

각 정보 처리 장치는 하나 이상의 물리 기억 장치를 구비하고, 각 물리 기억 장치의 물리 기억 공간을 논리 기억 공간에 맵핑하고, 통상은 논리 기억 공간 상에서 처리의 실행이 행하여진다. 따라서, 정보 처리 장치가 다른 정보 처리 장치로부터 공개 영역의 사용이 허가되었을 때에는, 이 공개 영역의 물리 기억 공간을 자 장치의 논리 기억 공간에 맵핑하여 사용할 수 있다.

공개 영역을 다른 정보 처리 장치에 제공하는 제1 정보 처리 장치의 제1 기억 공간 변환 수단은, 물리 기억 공간 상의 공개 영역의 물리 어드레스에 공개 영역 어드레스를 할당한다. 또한, 제1 정보 처리 장치가 제공하는 공개 영역을 사용하는 제2 정보 처리 장치의 제2 기억 공간 변환 수단은, 공개 영역의 공개 영역 어드레스에 논리 기억 공간 상의 논리 어드레스를 할당하도록 한다.

따라서, 상기 제2 정보 처리 장치에서 논리 기억 공간에 맵핑된 상기 제1 정보 처리 장치의 공개 영역에의 액세스 요구가 행해졌을 때에는, 상기 제2 기억 공간 변환 수단은, 액세스 요구된 논리 어드레스를 공개 영역 어드레스로 변환하고, 상기 제1 기억 공간 변환 수단은 공개 영역 어드레스를 상기 제1 정보 처리 장치에서의 물리 어드레스로 변환하여 물리 기억 공간에 액세스할 수 있다. 그리고, 상기 제1 기억 공간 변환 수단은, 공개 영역에 할당되어 있는 물리 어드레스로부터 취득한 데이터를 공개 영역 어드레스 상의 데이터로서 상기 제2 기억 공간 변환 수단에 되돌려 보내고, 상기 제2 기억 공간 변환 수단은, 공개 영역 어드레스 상의 데이터를 논리 어드레스 상의 데이터로서 액세스 요구원에 되돌려 보낼 수 있다.

또한, 본 발명의 제2 측면은, 네트워크 접속되는 다른 하나 이상의 정보 처리 장치와의 제휴에 의해 가상적으로 1대의 가상 정보 처리 장치의 일부로서 동작하기 위한 처리를 컴퓨터 시스템 상에서 실행하도록 컴퓨터 판독 가능 형식으로 기술된 컴퓨터 프로그램으로서,

물리 기억 공간 상에 다른 정보 처리 장치의 사용을 허가하는 공개 영역이 형성되어 있고,

다른 정보 처리 장치에 대하여 공개 영역의 사용을 허가하는 단계와,

다른 장치에 사용을 허가하는 공개 영역의 물리 어드레스에 공개 영역 어드레스를 할당하는 단계와,

다른 정보 처리 장치로부터 공개 영역에의 액세스 요구가 행해졌을 때, 그 액세스 요구된 공개 영역 어드레스를 물리 어드레스로 변환하는 단계와,

상기 물리 기억 공간의 상기 물리 어드레스로부터 추출된 데이터를 공개 영역 어드레스 상의 데이터로서 되돌려 보내는 단계

를 포함하는 것을 특징으로 하는 컴퓨터 프로그램이다.

또한, 본 발명의 제3 측면은, 네트워크 접속되는 다른 하나 이상의 정보 처리 장치와의 제휴에 의해 가상적으로 1대의 가상 정보 처리 장치의 일부로서 동작하기 위한 처리를 컴퓨터 시스템 상에서 실행하도록 컴퓨터 판독 가능 형식으로 기술된 컴퓨터 프로그램으로서,

다른 정보 처리 장치가 물리 기억 공간 상에 공개 영역을 형성하고 있고,

다른 정보 처리 장치에 대하여 공개 영역의 사용을 요구하는 단계와,

사용 요구가 허가된 것에 응답하여, 사용이 허가된 공개 영역 어드레스에 논리 어드레스를 할당하는 단계와,

액세스 요구된 논리 어드레스가 다른 정보 처리 장치로부터 사용이 허가되어 있는 공개 영역일 때, 그 액세스 요구된 논리 어드레스를 공개 영역 어드레스로 변환하여 상기 다른 정보 처리 장치에 액세스 요구하는 단계와,

상기 다른 정보 처리 장치로부터 되돌아 온 공개 영역 어드레스 상의 데이터를 논리 어드레스로 변환하여 액세스 요구원에 되돌려 보내는 단계

를 포함하는 것을 특징으로 하는 컴퓨터 프로그램이다.

본 발명의 제2 및 제3의 각 측면에 따른 컴퓨터 프로그램은, 컴퓨터 시스템 상에서 소정의 처리를 실현하도록 컴퓨터 판독 가능 형식으로 기술된 컴퓨터 프로그램을 정의한 것이다. 바꾸어 말하면, 본 발명의 제2 및 제3의 각 측면에 따른 컴퓨터 프로그램을 컴퓨터 시스템에 인스톨함으로써, 컴퓨터 시스템 상에서는 협동적 작용이 발휘되어, 본 발명의 제1 측면에 따른 정보 처리 시스템과 마찬가지의 작용 효과를 얻을 수 있다.

<실시예>

본 발명의 또 다른 목적, 특징이나 이점은, 후술하는 본 발명의 실시예나 첨부하는 도면에 기초하는 보다 상세한 설명에 의해서 분명하게 될 것이다.

이하, 도면을 참조하면서 본 발명의 실시예에 대하여 상세히 설명한다.

A. 시스템 구성

본 발명은 2 이상의 정보 처리 장치 사이에서의 동작을 홈 네트워크 경유로 적합하게 제휴시킴으로써, 별개의 장소로 설정되어 있는 각 기기에서의 녹화 예약 조작을 간이하고 또한 효율적으로 하는 것이다. 네트워크 상의 기기끼리 제휴시키기 위해서, 기기의 협조 동작에 의해 높은 연산 성능을 실현하기 위한 그리드 컴퓨팅 기술을 활용한다.

도 1에는, 그리드 컴퓨팅을 적용하여 구성되는, 네트워크 시스템의 구성을 모식적으로 도시하고 있다.

네트워크는, 인터넷이나 그 밖의 광역 네트워크, 및 광역 네트워크와는 게이트웨이 등을 통하여 접속되는 LAN(Local Area Network)이나 홈 네트워크 등의 사적인 네트워크로 구성된다. 홈 네트워크는, 물리적으로는 10 BaseT나 100 BaseTX, Giga eather 등의 표준 네트워크 인터페이스로 구성할 수 있다. 또한, 홈 네트워크 상에서 다른 기기를 발견하는 구조로서 Upnp(Universal Plug and Play)를 이용할 수 있다. Upnp에 따르면, 네트워크 접속된 기기 간에서, XML(eXtended Markup Language) 형식으로 기술된 정의 파일을 교환하여, 어드레싱 처리, 디스커버리 처리, 서비스 요구 처리를 거쳐서 상호 인증을 행한다. 혹은 동일 세그먼트 내에서의 규정의 기기 정보를 기술한 패킷의 브로드캐스팅함으로써도 실현 가능하다.

네트워크 상에는, 복수의 정보 처리 장치가 접속되어 있다. 정보 처리 장치의 예로서, DVD 레코더나 HD 레코더와 같은, 기록 미디어를 탑재하여 녹화 예약 기능을 구비한 AV 기기, 혹은 컴팩트 디스크 등의 기록 기능을 갖지 않은 재생 전용의 AV 기기, 그 밖의 정보 처리 장치를 들 수 있다. 또한, 정보 처리 장치의 다른 예는, PDA나 퍼스널 컴퓨터 등의 계산기 처리 시스템을 들 수 있다. 도 1에 도시하는 예에서는 네트워크(9)를 통하여 복수의 정보 처리 장치(1, 2, 3, 4)가 접속되어 있다.

A-1. 정보 처리 장치 및 정보 처리 컨트롤러

정보 처리 장치(1, 2, 3, 4)는 예를 들면 각종 AV(Audio and Visual) 기기나 포터블 기기이다(후술).

도시한 대로, 정보 처리 장치(1)는 컴퓨터 기능부로서 정보 처리 컨트롤러(11)를 구비한다. 정보 처리 컨트롤러(11)는, 메인 프로세서(21-1), 서브 프로세서(23-1, 23-2, 23-3), DMAC(다이렉트 메모리 액세스 컨트롤러)(25-1), 및 DC(디스크 컨트롤러)(27-1)를 구비하고 있다. 정보 처리 컨트롤러(11)는 원 칩 IC(집적 회로)로서 구성하는 것이 바람직하다.

메인 프로세서(21-1)는 서브 프로세서(23-1, 23-2, 23-3)에 의한 프로그램 실행(데이터 처리)의 스케줄 관리와, 정보 처리 컨트롤러(11)(정보 처리 장치(1))의 전반적인 관리를 행한다. 단, 메인 프로세서(21-1) 내에서 관리를 행하기 위한 프로그램 이외의 프로그램이 동작하도록 구성할 수도 있다. 이 경우, 메인 프로세서(21-1)는 서브 프로세서로서도 기능하게 된다. 메인 프로세서(21-1)는 LS(로컬 스토리지)(22-1)를 구비하고 있다.

1대의 정보 처리 장치에 구비되는 서브 프로세서는 하나이어도 되지만, 바람직하게는 복수로 한다. 도시한 예에서는 복수인 경우이다. 각 서브 프로세서(23-1, 23-2, 23-3)는 메인 프로세서(21-1)의 제어 하에, 병렬적 또한 독립적으로 프로 그램을 실행하고, 데이터를 처리한다. 또한, 경우에 따라서 메인 프로세서(21-1) 내의 프로그램이 서브 프로세서(23-1, 23-2, 23-3) 내의 프로그램과 제휴하여 동작할 수도 있다. 각 서브 프로세서(23-1, 23-2, 23-3)도, 각각 LS(로컬 스토리지)(24-1, 24-2, 24-3)를 구비하고 있다.

DMAC(직접 메모리 액세스 컨트롤러)(25-1)는, 정보 처리 컨트롤러(11)에 접속된 DRAM(다이내믹 RAM) 등으로 이루어지는 메인 메모리(26-1)에 저장되어 있는 프로그램 및 데이터에 프로세서의 개재없이 액세스하는 것이다. 또한, DC(디스크 컨트롤러)(27-1)는 정보 처리 컨트롤러(11)에 접속된 외부 기록부(28-1, 28-2)에의 액세스 동작을 제어한다.

외부 기록부(28-1, 28-2)는 고정 디스크(하드디스크) 및 리무버블 디스크 중 어느 형태이어도 된다. 또한, 리무버블 디스크로서, MO(자기 디스크), CD±RW, DVD±RW 등의 광 디스크, 메모리 디스크, SRAM(스태틱 RAM), ROM 등, 각종 기록 미디어를 이용할 수 있다. DC(27-1)는 디스크 컨트롤러라고 칭하지만, 요컨대 외부 기록부 컨트롤러이다. 도 1에 도시한 바와 같이, 외부 기록부(28)를 복수 접속할 수 있도록, 정보 처리 컨트롤러(11)를 구성할 수 있다.

메인 프로세서(21-1), 각 서브 프로세서(23-1, 23-2, 23-3), DMAC(25-1), 및 DC(27-1)는, 버스(29-1)에 의해서 상호 접속되어 있다.

정보 처리 컨트롤러(11)에는, 해당 정보 처리 컨트롤러(11)를 탑재하는 정보 처리 장치(1)를 네트워크 전체를 통해서 일의에 식별할 수 있는 식별자가, 정보 처리 장치 ID로서 할당되어 있다. 또한, 메인 프로세서(21-1) 및 각 서브 프로세서 (23-1, 23-2, 23-3)에 대하여도 마찬가지로, 각각을 특정할 수 있는 식별자가, 메인 프로세서 ID 및 서브 프로세서 ID로서 할당된다.

다른 정보 처리 장치(2, 3, 4)도 마찬가지로 구성되기 때문에, 여기서는 설명을 생략한다. 여기서, 부모 번호가 동일한 유닛은 브랜치 번호가 서로 다르더라도, 특별히 단서가 없는 한 동일한 기능을 하는 것으로 한다. 또한, 이하의 설명에서 브랜치 번호가 생략되어 있는 경우에는 브랜치 번호의 차이에 따른 차이를 일으키지 않는 것으로 한다.

A-2. 각 서브 프로세서로부터 메인 메모리에의 액세스

상술한 바와 같이, 하나의 정보 처리 컨트롤러 내의 각 서브 프로세서(23)는, 독립적으로 프로그램을 실행하고 데이터를 처리하지만, 서로 다른 서브 프로세서가 메인 메모리(26) 내의 동일 영역에 대하여 동시에 판독 또는 기입을 행한 경우에는 데이터의 부정합을 일으킬 수 있다. 따라서, 서브 프로세서(23)로부터 메인 메모리(26)에의 액세스는 이하와 같은 수순에 의해서 행한다.

도 2의 (A)에는 메인 메모리(26) 내의 로케이션을 도시하고 있다. 도 2에 도시한 바와 같이, 메인 메모리(26)는 복수의 어드레스를 지정할 수 있는 메모리 로케이션에 의해서 구성되고, 각 메모리 로케이션에 대하여 데이터의 상태를 나타내는 정보를 저장하기 위한 추가 세그먼트가 할당된다. 추가 세그먼트는 F/E 비트, 서브 프로세서 ID 및 LS 어드레스(로컬 스토리지 어드레스)를 포함하는 것으로 된다. 또한, 각 메모리 로케이션에는 후술하는 액세스 키도 할당된다. F/E 비트는 이하와 같이 정의된다.

F/E 비트=0은, 서브 프로세서(23)에 의해서 판독되고 있는 처리 중의 데이터, 또는 빈 상태이기 때문에 최신 데이터가 아닌 무효 데이터이고, 판독 불가임을 나타낸다. 또한, F/E 비트=0은 해당 메모리 로케이션에 데이터 기입 가능함을 나타내고, 기입 후에 1로 설정된다.

F/E 비트=1은 해당 메모리 로케이션의 데이터가 서브 프로세서(23)에 의해서 판독되어 있지 않고, 미 처리의 최신 데이터임을 나타낸다. 해당 메모리 로케이션의 데이터는 판독 가능하고, 서브 프로세서(23)에 의해서 판독된 후에 0으로 설정된다. 또한, F/E 비트=1은 해당 메모리 로케이션이 데이터 기입 불가임을 나타낸다.

또한, 상기 F/E 비트=0(판독 불가/기입 가능)의 상태에서, 해당 메모리 로케이션에 대하여 판독 예약을 설정하는 것은 가능하다. F/E 비트=0의 메모리 로케이션에 대하여 판독 예약을 행하는 경우에는, 서브 프로세서(23)는 판독 예약을 행하는 메모리 로케이션의 추가 세그먼트에, 판독 예약 정보로서 해당 서브 프로세서(23)의 서브 프로세서 ID 및 LS 어드레스를 기입한다.

그 후, 데이터 기입측의 서브 프로세서(23)에 의해, 판독 예약된 메모리 로케이션에 데이터가 기입되고, F/E 비트=1(판독 가능/기입 불가)로 설정되었을 때, 미리 판독 예약 정보로서 추가 세그먼트에 기입된 서브 프로세서 ID 및 LS 어드레스에 판독된다.

복수의 서브 프로세서에 의해서 데이터를 다단계로 처리할 필요가 있는 경우, 이와 같이 각 메모리 로케이션의 데이터의 판독/기입을 제어함으로써, 전 단계 의 처리를 행하는 서브 프로세서(23)가 처리 완료된 데이터를 메인 메모리(26) 상의 소정 어드레스에 기입한 후에 바로, 후 단계의 처리를 행하는 별도의 서브 프로세서(23)가 전 처리 후의 데이터를 판독하는 것이 가능하게 된다.

또한, 도 2의 (B)에는 각 서브 프로세서(23) 내의 LS(24)에서의 메모리 로케이션을 도시하고 있다. 도 2에 도시한 바와 같이, 각 서브 프로세서(23) 내의 LS(24)도, 복수의 어드레스를 지정할 수 있는 메모리 로케이션에 의해서 구성된다. 각 메모리 로케이션에 대해서는 마찬가지로 추가 세그먼트가 할당된다. 추가 세그먼트는 비지 비트를 포함하는 것으로 된다.

서브 프로세서(23)가 메인 메모리(26) 내의 데이터를 자신의 LS(24)의 메모리 로케이션에 판독할 때에는, 대응하는 비지 비트를 1로 설정하여 예약한다. 비지 비트가 1인 메모리 로케이션에는, 다른 데이터는 저장할 수 없다. LS(24)의 메모리 로케이션에 판독 후, 비지 비트는 0으로 되어, 임의의 목적으로 사용할 수 있게 된다.

도 2의 (A)에 도시한 바와 같이, 또한, 각 정보 처리 컨트롤러와 접속된 메인 메모리(26)에는, 메인 메모리(26) 내의 영역을 획정하는 복수의 샌드박스가 포함된다. 메인 메모리(26)는 복수의 메모리 로케이션으로 구성되지만, 샌드박스는 이들 메모리 로케이션의 집합이다. 각 샌드박스는 서브 프로세서(23)마다 할당되고, 해당하는 서브 프로세서를 배타적으로 사용할 수 있다. 즉, 각각의 서브 프로세서(23)는 자신에게 할당된 샌드박스를 사용할 수 있지만, 이 영역을 넘어 데이터의 액세스를 행할 수는 없다.

또한, 메인 메모리(26)의 배타적인 제어를 실현하기 위해서, 도 2의 (C)에 도시한 바와 같은 키 관리 테이블이 이용된다. 키 관리 테이블은 정보 처리 컨트롤러 내의 SRAM과 같은 비교적 고속의 메모리에 저장되고, DMAC(25)와 관련지워진다. 키 관리 테이블 내의 각 엔트리에는 서브 프로세서 ID, 서브 프로세서 키 및 키 마스크가 포함된다.

서브 프로세서(23)가 메인 메모리(26)를 사용할 때의 프로세스는 이하와 같다. 우선, 서브 프로세서(23)는 DMAC(25)에, 판독 또는 기입의 커맨드를 출력한다. 이 커맨드에는, 자신의 서브 프로세서 ID와, 사용 요구처인 메인 메모리(26)의 어드레스가 포함된다.

DMAC(25)는 이 커맨드를 실행하기 전에 키 관리 테이블을 참조하여, 사용 요구원의 서브 프로세서의 서브 프로세서 키를 조사한다. 다음으로, DMAC(25)는, 조사한 사용 요구원의 서브 프로세서 키와, 사용 요구처인 메인 메모리(26) 내의 도 2의 (A)에 도시한 메모리 로케이션에 할당된 액세스 키를 비교하여, 2개의 키가 일치한 경우에만, 상기의 커맨드를 실행한다.

도 2의 (C)에 도시한 키 관리 테이블 상의 키 마스크는, 그 임의의 비트가 1로 됨으로써, 그 키 마스크에 관련지워진 서브 프로세서 키의 대응하는 비트가 0 또는 1로 될 수 있다.

예를 들면, 서브 프로세서 키가 1010이라고 하자. 통상, 이 서브 프로세서 키에 의해서 1010의 액세스 키를 갖는 샌드박스에의 액세스만이 가능하게 된다. 그러나, 이 서브 프로세서 키와 관련지워진 키 마스크가 0001로 설정되어 있는 경 우에는, 키 마스크의 비트가 1로 설정된 자릿수에 대해서만, 서브 프로세서 키와 액세스 키의 일치 판정이 마스크되고, 이 서브 프로세서 키 1010에 의해서 액세스 키가 1010 및 1011 중 어느 하나인 액세스 키를 갖는 샌드박스에의 액세스가 가능하게 된다.

이상과 같이 하여, 메인 메모리(26)의 샌드박스의 배타성이 실현된다. 즉, 하나의 정보 처리 컨트롤러 내에 배치된 복수의 서브 프로세서에 의해서 데이터를 다단계로 처리할 필요가 있는 경우, 전 단계의 처리를 행하는 서브 프로세서와, 후 단계의 처리를 행하는 서브 프로세서만이, 메인 메모리(26)의 소정 어드레스에 액세스할 수 있게 되어, 데이터를 보호할 수 있다.

이러한 메모리의 배타 제어는 예를 들면 이하와 같이 사용할 수 있다. 우선, 정보 처리 장치의 기동 직후에서는, 키 마스크의 값은 전부 제로이다. 메인 프로세서 내의 프로그램이 실행되고, 서브 프로세서 내의 프로그램과 제휴 동작하는 것으로 한다. 제1 서브 프로세서에 의해 출력된 처리 결과 데이터를 일단 메인 메모리에 저장하고, 제2 서브 프로세서에 입력하고자 할 때에는, 해당하는 메인 메모리 영역은 당연히 어떤 쪽의 서브 프로세서로부터도 액세스 가능할 필요가 있다. 이러한 경우에, 메인 프로세서 내의 프로그램은, 키 마스크의 값을 적절하게 변경하여, 복수의 서브 프로세서로부터 액세스할 수 있는 메인 메모리 영역을 형성함으로써, 서브 프로세서에 의한 다단계적인 처리를 가능하게 한다.

보다 구체적으로는, 다른 정보 처리 장치에서의 데이터→제1 서브 프로세서에 의한 처리→제1 메인 메모리 영역→제2 서브 프로세서에 의한 처리→제2 메인 메모리 영역이라고 하는 수순으로 다단계 처리가 행하여질 때에는, 이하와 같은 설정 그대로는, 제2 서브 프로세서는 제1 메인 메모리 영역에 액세스할 수 없다.

제1 서브 프로세서의 서브 프로세서 키 : 0100

제1 메인 메모리 영역의 액세스 키 : 0100

제2 서브 프로세서의 서브 프로세서 키 : 0101

제2 메인 메모리 영역의 액세스 키 : 0101

따라서, 제2 서브 프로세서의 키 마스크를 0001로 함으로써, 제2 서브 프로세서에 의한 제1 메인 메모리 영역에의 액세스를 가능하게 할 수 있다.

A-3. 소프트웨어 셀의 생성 및 구성

도 1의 네트워크 시스템에서는, 정보 처리 장치(1, 2, 3, 4) 사이에서의 분산 처리를 위해서, 정보 처리 장치(1, 2, 3, 4) 사이에서 소프트웨어 셀이 전송된다. 즉, 어떤 정보 처리 장치 내의 정보 처리 컨트롤러에 포함되는 메인 프로세서(21)는, 커맨드, 프로그램 및 데이터를 포함하는 소프트웨어 셀을 생성하고, 네트워크(9)를 통하여 다른 정보 처리 장치로 송신함으로써, 처리를 분산할 수 있다.

도 3에는 소프트웨어 셀의 구성의 일례를 도시하고 있다. 도시하는 소프트웨어 셀은, 송신원 ID, 송신처 ID, 응답처 ID, 셀 인터페이스, DMA 커맨드, 프로그램, 및 데이터로 구성된다.

송신원 ID에는, 소프트웨어 셀의 송신원인 정보 처리 장치의 네트워크 어드레스 및 해당 정보 처리 장치 내의 정보 처리 컨트롤러의 정보 처리 장치 ID, 또한, 해당 정보 처리 장치 내의 정보 처리 컨트롤러가 구비하는 메인 프로세서(21) 및 각 서브 프로세서(23)의 식별자(메인 프로세서 ID 및 서브 프로세서 ID)가 포함된다.

송신처 ID 및 응답처 ID에는, 소프트웨어 셀의 송신처인 정보 처리 장치, 및 소프트웨어 셀의 실행 결과의 응답처인 정보 처리 장치에 대한 동일한 정보가 각각 포함된다.

셀 인터페이스는 소프트웨어 셀의 이용에 필요한 정보로서, 글로벌 ID, 필요한 서브 프로세서의 정보, 샌드박스 사이즈, 및 전회의 소프트웨어 셀 ID로 구성된다.

글로벌 ID는 네트워크 전체를 통해서 해당 소프트웨어 셀을 일의적으로 식별할 수 있는 것으로서, 송신원 ID와, 소프트웨어 셀의 작성 또는 송신의 일시(날짜 및 시각)에 기초하여 작성된다.

필요한 서브 프로세서의 정보는 해당 소프트웨어 셀의 실행에 필요한 서브 프로세서의 수가 설정된다. 샌드박스 사이즈는, 해당 소프트웨어 셀의 실행에 필요한 메인 메모리(26) 내 및 서브 프로세서(23)의 LS(24) 내의 메모리량이 설정된다.

전회의 소프트웨어 셀 ID는, 스트리밍 데이터 등의 시퀀셜한 실행을 요구하는 일 그룹의 소프트웨어 셀 내의, 전회의 소프트웨어 셀의 식별자이다.

소프트웨어 셀의 실행 섹션은 DMA 커맨드, 프로그램 및 데이터로 구성된다. DMA 커맨드에는 프로그램의 기동에 필요한 일련의 DMA 커맨드가 포함되고, 프로그램에는 서브 프로세서(23)에 의해서 실행되는 서브 프로세서 프로그램이 포함된다. 여기서의 데이터는, 이 서브 프로세서 프로그램을 포함하는 프로그램에 의해서 처리되는 데이터이다.

또한, DMA 커맨드에는 로드 커맨드, 킥 커맨드, 기능 프로그램 실행 커맨드, 스테이터스 요구 커맨드, 및 스테이터스 회신 커맨드가 포함된다.

로드 커맨드는 메인 메모리(26) 내의 정보를 서브 프로세서(23) 내의 LS(24)에 로드하는 커맨드이고, 로드 커맨드 자체 외에, 메인 메모리 어드레스, 서브 프로세서 ID 및 LS 어드레스를 포함한다. 메인 메모리 어드레스는 정보의 로드원인 메인 메모리(26) 내의 소정 영역의 어드레스를 나타낸다. 서브 프로세서 ID 및 LS 어드레스는, 정보의 로드처인 서브 프로세서(23)의 식별자 및 LS(24)의 어드레스를 나타낸다.

킥 커맨드는 프로그램의 실행을 개시하는 커맨드로서, 킥 커맨드 자체 외에, 서브 프로세서 ID 및 프로그램 카운터를 포함한다. 서브 프로세서 ID는 킥 대상의 서브 프로세서(23)를 식별하고, 프로그램 카운터는 프로그램 실행용 프로그램 카운터를 위한 어드레스를 제공한다.

기능 프로그램 실행 커맨드는, 어떤 정보 처리 장치가 다른 정보 처리 장치에 대하여, 기능 프로그램의 실행을 요구하는 커맨드이다(후술). 기능 프로그램 실행 커맨드를 수신한 정보 처리 장치 내의 정보 처리 컨트롤러는, 기능 프로그램 ID(후술)에 의해서, 기동할 기능 프로그램을 식별한다.

스테이터스 요구 커맨드는, 송신처 ID로 나타내는 정보 처리 장치의 현재의 동작 상태(상황)에 관한 장치 정보를, 응답처 ID로 나타내는 정보 처리 장치 앞으 로 송신 요구하는 커맨드이다. 기능 프로그램에 대해서는 후술하지만, 도 6에 도시하는 정보 처리 컨트롤러의 메인 메모리(26)가 기억하는 소프트웨어의 구성도에서 기능 프로그램으로 카테고라이즈되는 프로그램이다. 기능 프로그램은 메인 메모리(26)에 로드되고, 메인 프로세서(21)에 의해 실행된다.

스테이터스 회신 커맨드는, 상기의 스테이터스 요구 커맨드를 수신한 정보 처리 장치가, 자신의 장치 정보를 해당 스테이터스 요구 커맨드에 포함되는 응답처 ID로 나타내는 정보 처리 장치에 응답하는 커맨드이다. 스테이터스 회신 커맨드는 실행 섹션의 데이터 영역에 장치 정보를 저장한다.

도 4에는 DMA 커맨드가 스테이터스 회신 커맨드인 경우에서의 소프트웨어 셀의 데이터 영역의 구조를 도시하고 있다.

정보 처리 장치 ID는 정보 처리 컨트롤러를 구비하는 정보 처리 장치를 식별하기 위한 식별자로서, 스테이터스 회신 커맨드를 송신하는 정보 처리 장치의 ID를 나타낸다. 정보 처리 장치 ID는, 전원 투입 시에, 그 정보 처리 장치 내의 정보 처리 컨트롤러에 포함되는 메인 프로세서(21)에 의해서, 전원 투입 시의 일시, 정보 처리 장치의 네트워크 어드레스 및 정보 처리 장치 내의 정보 처리 컨트롤러에 포함되는 서브 프로세서(23)의 수 등에 기초하여 생성된다.

정보 처리 장치 종별 ID에는 해당 정보 처리 장치의 특징을 나타내는 값이 포함된다. 여기서 말하는 정보 처리 장치의 특징이란, 예를 들면, 하드디스크 레코더(후술), PDA(Personal Digital Assistants), 포터블 CD(Compact Disc) 플레이어 등이다. 또한, 정보 처리 장치 종별 ID는, 영상 음성 기록, 영상 음성 재생 등 , 정보 처리 장치가 갖는 기능을 나타내는 것이어도 된다. 정보 처리 장치의 특징이나 기능을 나타내는 값은 미리 정해져 있는 것으로 하여, 정보 처리 장치 종별 ID를 불러냄으로써 해당 정보 처리 장치의 특징이나 기능을 파악하는 것이 가능하다.

MS(마스터/슬레이브) 스테이터스는, 후술하는 바와 같이 정보 처리 장치가 마스터 장치 및 슬레이브 장치 중 어느 것에서 동작하고 있는지를 나타내는 것으로, 이것이 0으로 설정되어 있는 경우에는 마스터 장치로서 동작하고 있는 것을 나타내고, 1로 설정되어 있는 경우에는 슬레이브 장치로서 동작하고 있는 것을 나타낸다.

메인 프로세서 동작 주파수는 정보 처리 컨트롤러 내의 메인 프로세서(21)의 동작 주파수를 나타낸다. 메인 프로세서 사용율은 메인 프로세서(21)에서 현재 동작하고 있는 모든 프로그램에 대한, 메인 프로세서(21)에서의 사용율을 나타낸다. 메인 프로세서 사용율은, 대상 메인 프로세서의 전 처리 능력에 대한 사용 중 처리 능력의 비율을 나타낸 값으로, 예를 들면 프로세서 처리 능력 평가를 위한 단위인 MIPS[Million Instructions Per Second]를 단위로 하여 산출되거나, 또는 단위 시간당 프로세서 사용 시간에 기초하여 산출된다. 후술하는 서브 프로세서 사용율에 대해서도 마찬가지이다.

서브 프로세서 수는 해당 정보 처리 컨트롤러가 구비하는 서브 프로세서(23)의 수를 나타낸다. 서브 프로세서 ID는 해당 정보 처리 컨트롤러 내의 각 서브 프로세서(23)를 식별하기 위한 식별자이다.

서브 프로세서 스테이터스는 각 서브 프로세서(23)의 상태를 나타내는 것으로, unused, reserved, busy 등의 상태가 있다. unused는 해당 서브 프로세서가 현재 사용되고 있지 않고, 사용 예약도 되어 있지 않음을 나타낸다. reserved는 현재는 사용되고 있지 않지만, 예약되어 있는 상태를 나타낸다. busy는 현재 사용 중임을 나타낸다.

서브 프로세서 사용율은, 해당 서브 프로세서에서 현재 실행하고 있거나, 또는 해당 서브 프로세서에 실행이 예약되어 있는 프로그램에 대한, 해당 서브 프로세서에서의 사용율을 나타낸다. 즉, 서브 프로세서 사용율은, 서브 프로세서 스테이터스가 busy인 경우에는 현재의 사용율을 나타내고, 서브 프로세서 스테이터스가 reserved인 경우에는 후에 사용될 예정의 추정 사용율을 나타낸다.

서브 프로세서 ID, 서브 프로세서 스테이터스 및 서브 프로세서 사용율은 하나의 서브 프로세서(23)에 대하여 1조 설정되고, 하나의 정보 처리 컨트롤러 내의 서브 프로세서(23)에 대응하는 조 수가 설정된다.

메인 메모리 총 용량 및 메인 메모리 사용량은 각각, 해당 정보 처리 컨트롤러에 접속되어 있는 메인 메모리(26)의 총 용량 및 현재 사용 중인 용량을 나타낸다.

외부 기록 부수는 해당 정보 처리 컨트롤러에 접속되어 있는 외부 기록부(28)의 수를 나타낸다. 외부 기록부 ID는 해당 정보 처리 컨트롤러에 접속되어 있는 외부 기록부(28)를 일의적으로 식별하는 정보이다. 외부 기록부 종별 ID는 해당 외부 기록부의 종류(예를 들면, 하드디스크, CD±RW, DVD±RW, 메모리 디스크, SRAM, ROM 등)를 나타낸다.

외부 기록부 총 용량 및 외부 기록부 사용량은 각각, 외부 기록부 ID에 의해서 식별되는 외부 기록부(28)의 총 용량 및 현재 사용 중인 용량을 나타낸다.

외부 기록부 ID, 외부 기록부 종별 ID, 외부 기록부 총 용량 및 외부 기록부 사용량은 하나의 외부 기록부(28)에 대하여 1조 설정되는 것으로, 해당 정보 처리 컨트롤러에 접속되어 있는 외부 기록부(28)의 수의 조 수만큼 설정된다. 즉, 하나의 정보 처리 컨트롤러에 복수의 외부 기록부가 접속되어 있는 경우, 각각의 외부 기록부에는 다른 외부 기록부 ID가 할당되고, 외부 기록부 종별 ID, 외부 기록부 총 용량 및 외부 기록부 사용량도 따로따로 관리된다.

A-4. 소프트웨어 셀의 실행

어떤 정보 처리 장치 내의 정보 처리 컨트롤러에 포함되는 메인 프로세서(21)는, 상술한 바와 같은 구성의 소프트웨어 셀을 생성하고, 네트워크(9)를 통하여, 다른 정보 처리 장치 및 해당 장치 내의 정보 처리 컨트롤러에 송신한다. 송신원의 정보 처리 장치, 송신처의 정보 처리 장치, 응답처의 정보 처리 장치, 및 각 장치 내의 정보 처리 컨트롤러는 각각, 상기의 송신원 ID, 송신처 ID 및 응답처 ID에 의해서 식별된다.

소프트웨어 셀을 수신한 정보 처리 장치 내의 정보 처리 컨트롤러에 포함되는 메인 프로세서(21)는, 그 소프트웨어 셀을 메인 메모리(26)에 저장한다. 또한, 송신처의 메인 프로세서(21)는 소프트웨어 셀을 판독하고, 그것에 포함되는 DMA 커맨드를 처리한다.

구체적으로, 송신처의 메인 프로세서(21)는 우선, 로드 커맨드를 실행한다. 이에 의해서, 로드 커맨드에 의해 지시된 메인 메모리 어드레스로부터, 로드 커맨드에 포함되는 서브 프로세서 ID 및 LS 어드레스에 의해 특정되는 서브 프로세서 내의 LS(24)의 소정 영역에, 정보가 로드된다. 여기서 로드되는 정보는, 수신한 소프트웨어 셀에 포함되는 서브 프로세서 프로그램 또는 데이터, 혹은 그 밖의 지시된 데이터이다.

다음으로, 메인 프로세서(21)는 킥 커맨드를, 이것에 포함되는 서브 프로세서 ID에 의해 지시된 서브 프로세서에, 마찬가지로 킥 커맨드에 포함되는 프로그램 카운터와 함께 출력한다.

지시된 서브 프로세서는 그 킥 커맨드 및 프로그램 카운터에 따라서, 서브 프로세서 프로그램을 실행한다. 그리고, 실행 결과를 메인 메모리(26)에 저장한 후, 실행을 완료하였음을 메인 프로세서(21)에 통지한다.

또한, 송신처의 정보 처리 장치 내의 정보 처리 컨트롤러에서 소프트웨어 셀을 실행하는 프로세서는 서브 프로세서(23)에 한정되는 것이 아니고, 메인 프로세서(21)가 소프트웨어 셀에 포함되는 기능 프로그램 등의 메인 메모리용 프로그램을 실행하도록 지정하는 것도 가능하다.

이 경우에는, 송신원의 정보 처리 장치는, 송신처의 정보 처리 장치 앞으로, 서브 프로세서 프로그램 대신에, 메인 메모리용 프로그램 및 그 메인 메모리용 프로그램에 의해서 처리되는 데이터를 포함하여, DMA 커맨드가 로드 커맨드인 소프트웨어 셀을 송신하고, 메인 메모리(26)에 메인 메모리용 프로그램 및 이에 의하여 처리되는 데이터를 기억시킨다.

다음으로, 송신원의 정보 처리 장치는, 송신처의 정보 처리 장치 앞으로, 송신처의 정보 처리 장치 내의 정보 처리 컨트롤러에 대한 메인 프로세서 ID, 메인 메모리 어드레스, 메인 메모리용 프로그램을 식별하기 위한 후술하는 기능 프로그램 ID 등의 식별자, 및 프로그램 카운터를 포함하여, DMA 커맨드가 킥 커맨드 또는 기능 프로그램 실행 커맨드인 소프트웨어 셀을 송신하고, 메인 프로세서(21)에 해당 메인 메모리용 프로그램을 실행시킨다.

이상과 같이, 본 실시예에 따른 네트워크 시스템에서는, 송신원의 정보 처리 장치는, 서브 프로세서 프로그램 또는 메인 메모리용 프로그램을 소프트웨어 셀에 의해서 송신처의 정보 처리 장치로 송신함과 함께, 해당 서브 프로세서 프로그램을 송신처의 정보 처리 장치 내의 정보 처리 컨트롤러에 포함되는 서브 프로세서(23)에 로드시켜, 해당 서브 프로세서 프로그램 또는 해당 메인 메모리용 프로그램을 송신처의 정보 처리 장치에 실행시킬 수 있다.

송신처의 정보 처리 장치 내의 정보 처리 컨트롤러에서는, 수신한 소프트웨어 셀에 포함되는 프로그램이 서브 프로세서 프로그램인 경우에는, 해당 서브 프로세서 프로그램을 지정된 서브 프로세서에 로드시킨다. 그리고, 소프트웨어 셀에 포함되는 서브 프로세서 프로그램 또는 메인 메모리용 프로그램을 실행시킨다.

따라서, 사용자가 송신처의 정보 처리 장치를 조작하지 않더라도, 해당 서브 프로세서 프로그램 또는 해당 메인 메모리용 프로그램을 송신처의 정보 처리 장치 내의 정보 처리 컨트롤러에게 자동적으로 실행시킬 수 있다.

이와 같이 하여 정보 처리 장치는, 자 장치 내의 정보 처리 컨트롤러가 서브 프로세서 프로그램 또는 기능 프로그램 등의 메인 메모리용 프로그램을 갖고 있지 않은 경우에는, 네트워크에 접속된 다른 정보 처리 장치로부터 이들을 취득할 수 있다. 또한, 각 서브 프로세서 사이에서는 DMA 방식에 의해 데이터 전송을 행하고, 또한 상술한 샌드박스를 사용함으로써, 하나의 정보 처리 컨트롤러 내에서 데이터를 다단계로 처리할 필요가 있는 경우에도, 고속으로 또한 고시큐러티로 처리를 실행할 수 있다.

A-5. 네트워크 시스템으로서의 분산 처리

도 5에는 복수의 정보 처리 장치가 가상적인 1대의 정보 처리 장치로서 동작하고 있는 모습을 도시하고 있다. 소프트웨어 셀의 사용에 의한 분산 처리의 결과, 도 5의 상단에 도시한 바와 같이, 네트워크(9)에 접속되어 있는 복수의 정보 처리 장치(1, 2, 3, 4)는, 도 5의 하단에 도시한 바와 같이, 가상적인 1대의 정보 처리 장치(7)로서 동작한다. 단, 이러한 가상적인 동작을 실현하기 위해서는, 이하와 같은 구성에 의해서, 이하와 같은 처리가 실행될 필요가 있다.

A-6. 시스템의 소프트웨어 구성과 프로그램의 로드

도 6에는 개개의 정보 처리 컨트롤러의 메인 메모리(26)가 기억하는 소프트웨어의 구성을 도시하고 있다. 이들 소프트웨어(프로그램)는 정보 처리 장치에 전원이 투입되기 전에, 해당 정보 처리 컨트롤러에 접속되는 외부 기록부(28)에 기록되어 있는 것이다. 각 프로그램은 기능 또는 특징에 의해, 제어 프로그램, 기능 프로그램 및 디바이스 드라이버로 분류된다.

제어 프로그램은, 각 정보 처리 컨트롤러가 동일한 것을 구비하고, 각 정보 처리 컨트롤러의 메인 프로세서(21)가 실행하는 것으로, 후술하는 MS(마스터/슬레이브) 매니저 및 능력 교환 프로그램을 포함한다.

기능 프로그램은 메인 프로세서(21)가 실행하는 것으로, 기록용, 재생용, 소재 검색용 등, 정보 처리 컨트롤러마다 정보 처리 장치에 응답한 것이 구비된다.

디바이스 드라이버는, 정보 처리 컨트롤러(정보 처리 장치)의 입출력(송수신)용으로, 방송 수신, 모니터 출력, 비트 스트림 입출력, 네트워크 입출력 등, 정보 처리 컨트롤러마다 정보 처리 장치에 응답한 것이 구비된다.

케이블의 연결 등에 의해서 정보 처리 장치가 물리적으로 네트워크(9)에 접속된 상태에서, 정보 처리 장치에 주 전원이 투입되어, 정보 처리 장치가 전기적·기능적으로도 네트워크(9)에 접속되면, 그 정보 처리 장치의 정보 처리 컨트롤러의 메인 프로세서(21)는, 제어 프로그램에 속하는 각 프로그램 및 디바이스 드라이버에 속하는 각 프로그램을, 메인 메모리(26)에 로드한다.

프로그램의 로드 수순으로서는, 메인 프로세서(21)는 우선, DC(27)에 판독 명령을 실행시킴으로써, 외부 기록부(28)로부터 프로그램을 판독하고, 다음으로, DMAC(25)에 기입 명령을 실행시킴으로써, 그 프로그램을 메인 메모리(26)에 기입한다.

기능 프로그램에 속하는 각 프로그램에 대해서는, 필요할 때에 필요한 프로그램만을 로드하도록 구성하여도 되고, 또는 다른 카테고리에 속하는 프로그램과 마찬가지로, 주 전원 투입 직후에 각 프로그램을 로드하도록 구성하여도 된다.

기능 프로그램에 속하는 각 프로그램은, 네트워크에 접속된 모든 정보 처리 장치의 외부 기록부(28)에 기록되어 있을 필요는 없으며, 어느 하나의 정보 처리 장치의 외부 기록부(28)에 기록되어 있으면, 상술한 방법에 의해서 다른 정보 처리 장치로부터 로드할 수 있으므로, 결과적으로 도 5의 하단에 도시한 바와 같이, 가상적인 1대의 정보 처리 장치(7)로서 기능 프로그램을 실행할 수 있다.

여기서 상술한 바와 같이 메인 프로세서(21)에 의해서 처리되는 기능 프로그램은, 서브 프로세서(23)에 의해서 처리되는 서브 프로세서 프로그램과 제휴 동작하는 경우가 있다. 그래서, 메인 프로세서(21)가 외부 기록부(28)로부터 기능 프로그램을 판독하고, 메인 메모리(26)에 기입할 때에 대상으로 되는 기능 프로그램과 제휴 동작하는 서브 프로세서 프로그램이 존재하는 경우에는, 해당 서브 프로세서 프로그램도 더불어 동일한 메인 메모리(26)에 기입하는 것으로 한다. 이 경우, 제휴 동작하는 서브 프로세서 프로그램은 1개인 경우도 있고, 복수개인 경우도 있을 수 있다. 복수개인 경우에는, 모든 제휴 동작하는 서브 프로세서 프로그램을 메인 메모리(26)에 기입하게 된다. 메인 메모리(26)에 기입된 서브 프로세서 프로그램은 그 후, 서브 프로세서(23) 내의 LS(24)에 기입되고, 메인 프로세서(21)에 의해서 처리되는 기능 프로그램과 제휴 동작한다.

그리고, 서브 프로세서 프로그램에도 서브 프로세서 프로그램 ID가 할당되고, 이에 의해 서브 프로세서 프로그램을 일의적으로 식별 가능하다. 할당되는 서브 프로세서 프로그램 ID는, 제휴 동작하는 상대로 되는 기능 프로그램의 기능 프로그램 ID와 관련성이 있는 식별자, 예를 들면 기능 프로그램 ID를 부모 번호로 한 다음에, 최후미에 브랜치 번호를 부가시킨 것 등인 경우도 있을 수 있고, 제휴 동작하는 상대로 되는 기능 프로그램의 기능 프로그램 ID와는 관련성이 없는 식별자이어도 된다. 어떻든 간에 기능 프로그램과 서브 프로세서 프로그램이 제휴 동작하는 경우에는, 양자 모두 상대의 식별자인 프로그램 ID를 자신의 프로그램 내에 상호 기억해 놓을 필요가 있다. 기능 프로그램이 복수개의 서브 프로세서 프로그램과 제휴 동작하는 경우에도, 해당 기능 프로그램은 복수개인 모든 서브 프로세서 프로그램의 서브 프로세서 프로그램 ID를 기억해 놓게 된다.

도 3의 소프트웨어 셀에 도시한 바와 같이, 기능 프로그램에는, 프로그램마다 프로그램을 일의적으로 식별할 수 있는 식별자가, 기능 프로그램 ID로서 할당된다. 기능 프로그램 ID는 기능 프로그램의 작성의 단계에서, 작성 일시나 정보 처리 장치 ID 등으로부터 결정된다.

메인 프로세서(21)는 자신이 동작하는 정보 처리 장치의 장치 정보(동작 상태에 관한 정보)를 저장하기 위한 영역을 메인 메모리(26)에 확보하고, 해당 정보를 자 장치의 장치 정보 테이블로서 기록한다. 여기서의 장치 정보는 도 4에 도시한 정보 처리 장치 ID 이하의 각 정보이다.

A-7. 시스템에서의 마스터/슬레이브의 결정

상술한 네트워크 시스템에서는, 어떤 정보 처리 장치에의 주 전원 투입 시, 그 정보 처리 장치의 정보 처리 컨트롤러의 메인 프로세서(21)는, 마스터/슬레이브 매니저(이하, MS 매니저)를 메인 메모리(26)에 로드하여, 실행한다.

MS 매니저는 자신이 동작하는 정보 처리 장치가 네트워크(9)에 접속되어 있 는 것을 검지하면, 동일한 네트워크(9)에 접속되어 있는 다른 정보 처리 장치의 존재를 확인한다. 여기서의 「접속」 또는 「존재」는 상술한 바와 같이, 정보 처리 장치가 물리적으로 네트워크(9)에 접속되어 있을 뿐만 아니라, 전기적·기능적으로도 네트워크(9)에 접속되어 있음을 나타낸다.

또한, 자신이 동작하는 정보 처리 장치를 자 장치, 다른 정보 처리 장치를 타 장치라고 칭한다. 해당 장치도, 해당 정보 처리 장치를 나타내는 것으로 한다.

MS 매니저가 동일한 네트워크(9)에 접속되어 있는 다른 정보 처리 장치의 존재를 확인하는 방법에 대하여 이하에 설명한다.

MS 매니저는, DMA 커맨드가 스테이터스 요구 커맨드이고, 송신원 ID 및 응답처 ID가 해당 정보 처리 장치에서, 송신처 ID를 특정하지 않은 소프트웨어 셀을 생성하여, 해당 정보 처리 장치가 접속된 네트워크 상에 송신하고, 네트워크 접속 확인용의 타이머를 설정한다. 타이머의 타임아웃 시간은, 예를 들면 10분이다.

해당 네트워크 시스템 상에 다른 정보 처리 장치가 접속되어 있는 경우, 그 외 장치는, 상기 스테이터스 요구 커맨드의 소프트웨어 셀을 수신하고, 상기 응답처 ID에 의해 특정되는 스테이터스 요구 커맨드를 발행한 정보 처리 장치에 대하여, DMA 커맨드가 스테이터스 회신 커맨드이고, 또한 데이터로서 자신(그 외 장치)의 장치 정보를 포함하는 소프트웨어 셀을 송신한다. 이 스테이터스 회신 커맨드의 소프트웨어 셀에는, 적어도 해당 타 장치를 특정하는 정보(정보 처리 장치 ID, 메인 프로세서에 관한 정보, 서브 프로세서에 관한 정보 등) 및 해당 타 장치의 MS 스테이터스가 포함된다.

스테이터스 요구 커맨드를 발행한 정보 처리 장치의 MS 매니저는, 상기 네트워크 접속 확인용의 타이머가 타임아웃할 때까지, 해당 네트워크 상의 타 장치로부터 송신되는 스테이터스 회신 커맨드의 소프트웨어 셀의 수신을 감시한다. 그 결과, MS 스테이터스=0(마스터 장치)을 나타내는 스테이터스 회신 커맨드가 수신된 경우에는, 자 장치의 장치 정보 테이블에서의 MS 스테이터스를 1로 설정한다. 이에 의해서, 해당 장치는 슬레이브 장치로 된다.

한편, 상기 네트워크 접속 확인용의 타이머가 타임아웃할 때까지의 동안에 스테이터스 회신 커맨드가 전혀 수신되지 않은 경우, 또는 MS 스테이터스=0(마스터 장치)을 나타내는 스테이터스 회신 커맨드가 수신되지 않은 경우에는, 자 장치의 장치 정보 테이블에서의 MS 스테이터스를 0으로 설정한다. 이에 의해서, 해당 장치는 마스터 장치로 된다.

즉, 어느 장치도 네트워크(9)에 접속되어 있지 않은 상태, 또는 네트워크(9)상에 마스터 장치가 존재하지 않은 상태에서, 새로운 정보 처리 장치가 네트워크(9)에 접속되면, 해당 장치는 자동적으로 마스터 장치로서 설정된다. 한편, 네트워크(9) 상에 이미 마스터 장치가 존재하는 상태에서, 새로운 정보 처리 장치가 네트워크(9)에 접속되면, 해당 장치는 자동적으로 슬레이브 장치로서 설정된다.

마스터 장치 및 슬레이브 장치 중 어느 것에 대하여도, MS 매니저는, 정기적으로 스테이터스 요구 커맨드를 네트워크(9) 상의 타 장치로 송신하여 스테이터스 정보를 조회함으로써, 타 장치의 상황을 감시한다. 그 결과, 네트워크(9)에 접속되어 있는 정보 처리 장치의 주 전원이 차단되거나, 또는 네트워크(9)로부터 정보 처리 장치가 분리됨으로써, 사전에 판정용으로 설정된 소정 기간 내에 특정한 타 장치로부터 스테이터스 회신 커맨드가 회신되지 않았던 경우나, 네트워크(9)에 새로운 정보 처리 장치가 접속되었던 경우 등, 네트워크(9)의 접속 상태에 변화가 있었던 경우에는, 그 정보를 후술하는 능력 교환 프로그램에 통지한다.

A-8. 마스터 장치 및 슬레이브 장치에서의 장치 정보의 취득

메인 프로세서(21)는, MS 매니저로부터, 네트워크(9)에 접속된 다른 정보 처리 장치의 조회 및 자 장치의 MS 스테이터스의 설정 완료의 통지를 받으면, 능력 교환 프로그램을 실행한다.

능력 교환 프로그램은, 자 장치가 마스터 장치인 경우에는, 네트워크(9)에 접속되어 있는 다른 모든 정보 처리 장치에 대한 장치 정보, 즉 각 슬레이브 장치의 장치 정보를 취득한다.

타 장치의 장치 정보의 취득은, 상술한 바와 같이, DMA 커맨드가 스테이터스 요구 커맨드인 소프트웨어 셀을 생성하여 타 장치로 송신하고, 그 후, DMA 커맨드가 스테이터스 회신 커맨드이고, 또한 데이터로서 타 장치의 장치 정보를 포함하는 소프트웨어 셀을 타 장치로부터 수신함으로써 가능하다.

능력 교환 프로그램은, 마스터 장치인 자 장치의 장치 정보 테이블과 마찬가지로, 네트워크(9)에 접속되어 있는 다른 모든 장치(각 슬레이브 장치)에 대한 장치 정보를 저장하기 위한 영역을 자 장치의 메인 메모리(26)에 확보하고, 이들 정보를 타 장치(슬레이브 장치)의 장치 정보 테이블로서 기록한다. 즉, 마스터 장치의 메인 메모리(26)에는, 자 장치를 포함하는 네트워크(9)에 접속되어 있는 모든 정보 처리 장치의 장치 정보가, 장치 정보 테이블로서 기록된다.

한편, 능력 교환 프로그램은, 자 장치가 슬레이브 장치인 경우에는, 네트워크(9)에 접속되어 있는 다른 모든 장치에 대한 장치 정보, 즉 마스터 장치 및 자 장치 이외의 각 슬레이브 장치의 장치 정보를 취득하고, 이들 장치 정보에 포함되는 정보 처리 장치 ID 및 MS 스테이터스를, 자 장치의 메인 메모리(26)에 기록한다. 즉, 슬레이브 장치의 메인 메모리(26)에는, 자 장치의 장치 정보가, 장치 정보 테이블로서 기록됨과 함께, 자 장치 이외의 네트워크(9)에 접속되어 있는 마스터 장치 및 각 슬레이브 장치에 대한 정보 처리 장치 ID 및 MS 스테이터스가, 다른 장치 정보 테이블로서 기록된다.

또한, 마스터 장치 및 슬레이브 장치 중 어느 것에 대하여도, 능력 교환 프로그램은, 상기와 같이 MS 매니저로부터, 새롭게 네트워크(9)에 정보 처리 장치가 접속된 것이 통지되었을 때에는, 그 정보 처리 장치의 장치 정보를 취득하고, 상술한 바와 같이 메인 메모리(26)에 기록한다.

또한, MS 매니저 및 능력 교환 프로그램은, 메인 프로세서(21)에서 실행되는 것에 한하지 않고, 어느 하나의 서브 프로세서(23)에서 실행되어도 된다. 또한, MS 매니저 및 능력 교환 프로그램은, 정보 처리 장치의 주 전원이 투입되고 있는 동안은 상시 동작하는 상주 프로그램인 것이 바람직하다.

A-9. 정보 처리 장치가 네트워크로부터 절단된 경우

마스터 장치 및 슬레이브 장치 중 어느 것에 대하여도, 능력 교환 프로그램은, 상기와 같이 MS 매니저로부터, 네트워크(9)에 접속되어 있는 정보 처리 장치의 주 전원이 차단되거나, 또는 네트워크(9)로부터 정보 처리 장치가 분리된 것이 통지되었을 때에는, 그 정보 처리 장치의 장치 정보 테이블을 자 장치의 메인 메모리(26)로부터 삭제한다.

또한, 이와 같이 네트워크(9)로부터 절단된 정보 처리 장치가 마스터 장치인 경우에는, 이하와 같은 방법에 의해서 새롭게 마스터 장치가 결정된다.

예를 들면, 네트워크(9)로부터 절단되어 있지 않은 정보 처리 장치는 각각, 자 장치 및 타 장치의 정보 처리 장치 ID를 수치로 치환하고, 자 장치의 정보 처리 장치 ID를 타 장치의 정보 처리 장치 ID와 비교하여, 자 장치의 정보 처리 장치 ID가 네트워크(9)로부터 절단되어 있지 않은 정보 처리 장치 중에서 최소인 경우, 그 슬레이브 장치는 마스터 장치로 이행하여, MS 스테이터스를 0으로 설정하고, 마스터 장치로서, 상술한 바와 같이, 네트워크(9)에 접속되어 있는 다른 모든 정보 처리 장치(각 슬레이브 장치)로부터 장치 정보를 취득하여, 메인 메모리(26)에 기록한다.

A-10. 장치 정보에 기초한 분산 처리

도 5의 하단에 도시한 바와 같이 네트워크(9)에 접속되어 있는 복수의 정보 처리 장치(1, 2, 3, 4)를 가상적인 1대의 정보 처리 장치(7)로서 동작시키기 위해서는, 마스터 장치가 사용자의 조작 및 슬레이브 장치의 동작 상태를 파악할 필요가 있다.

도 7에는 4대의 정보 처리 장치가 가상적인 1대의 정보 처리 장치(7)로서 동작하는 모습을 도시하고 있다. 도시하는 예에서는, 정보 처리 장치(1)가 마스터 장치, 정보 처리 장치(2, 3, 4)가 슬레이브 장치 A, B, C로서 각각 동작하고 있는 것으로 한다.

사용자가 네트워크(9)에 접속되어 있는 정보 처리 장치를 조작한 경우, 조작 대상이 마스터 장치(1)이면, 그 조작 정보는 마스터 장치(1)에서 직접 파악된다. 또한, 조작 대상이 슬레이브 장치이면, 그 조작 정보는 조작된 슬레이브 장치로부터 마스터 장치(1)에 송신된다. 즉, 사용자의 조작 대상이 마스터 장치(1)와 슬레이브 장치 중 어느 것인지에 상관없이, 그 조작 정보는 항상 마스터 장치(1)에서 파악된다. 조작 정보의 송신은 예를 들면, DMA 커맨드가 조작 정보 송신 커맨드인 소프트웨어 셀에 의해서 행해진다.

그리고, 마스터 장치(1) 내의 정보 처리 컨트롤러(11)에 포함되는 메인 프로세서(21-1)는, 그 조작 정보에 따라서, 실행할 기능 프로그램을 선택한다. 이 때, 필요하다면, 마스터 장치(1) 내의 정보 처리 컨트롤러(11)에 포함되는 메인 프로세서(21-1)는, 상기의 방법에 의해서 자 장치의 외부 기록부(28-1, 28-2)로부터 메인 메모리(26-1)에 기능 프로그램을 로드하지만, 다른 정보 처리 장치(슬레이브 장치)가 마스터 장치(1)에 기능 프로그램을 송신하여도 된다.

기능 프로그램에는 그 실행 단위마다 필요로 되는, 정보 처리 장치 종별 ID, 메인 프로세서 또는 서브 프로세서의 처리 능력, 메인 메모리 사용량, 외부 기록부에 관한 조건 등의, 장치에 관한 요구 스펙(도 4를 참조할 것)이 규정되어 있다.

마스터 장치(1) 내의 정보 처리 컨트롤러(11)에 포함되는 메인 프로세서(21-1)는, 각 기능 프로그램에 대하여 필요로 되는 상기 요구 스펙을 판독한다. 또한, 사전에 능력 교환 프로그램에 의해서 메인 메모리(26-1)에 기록된 장치 정보 테이블을 참조하여, 각 정보 처리 장치의 장치 정보를 판독한다. 여기서의 장치 정보는, 도 4에 도시한 정보 처리 장치 ID 이하의 각 정보를 나타내고, 메인 프로세서, 서브 프로세서, 메인 메모리 및 외부 기록부에 관한 정보이다.

마스터 장치(1) 내의 정보 처리 컨트롤러(11)에 포함되는 메인 프로세서(21-1)는, 네트워크(9) 상에 접속된 각 정보 처리 장치의 상기 장치 정보와, 기능 프로그램 실행에 필요로 되는 상기 요구 스펙을 순차적으로 비교한다.

예를 들면, 기능 프로그램이 녹화 기능을 필요로 하는 경우에는, 정보 처리 장치 종별 ID에 기초하여, 녹화 기능을 갖는 정보 처리 장치만을 특정하여 추출한다. 또한, 기능 프로그램을 실행하기 위해 필요한 메인 프로세서 또는 서브 프로세서의 처리 능력, 메인 메모리 사용량, 외부 기록부에 관한 조건을 확보할 수 있는 슬레이브 장치를, 실행 요구 후보 장치로서 특정한다. 여기서, 복수의 실행 요구 후보 장치가 특정된 경우에는, 해당 후보 장치로부터 하나의 실행 요구 후보 장치를 특정하여 선택한다.

실행 요구할 슬레이브 장치가 특정되면, 마스터 장치(1) 내의 정보 처리 컨트롤러(11)에 포함되는 메인 프로세서(21-1)는, 그 특정된 슬레이브 장치에 대하여, 자 장치 내의 정보 처리 컨트롤러(11)에 포함되는 메인 메모리(26-1)에 기록되어 있는 해당 슬레이브 장치의 장치 정보 테이블을 갱신한다.

또한, 마스터 장치(1) 내의 정보 처리 컨트롤러(11)에 포함되는 메인 프로세서(21-1)는, DMA 커맨드가 기능 프로그램 실행 커맨드인 소프트웨어 셀을 생성하 고, 해당 소프트웨어 셀의 셀 인터페이스에, 해당 기능 프로그램에 관한 필요한 서브 프로세서의 정보 및 샌드박스 사이즈(도 3을 참조할 것)를 설정하고, 상기 실행 요구되는 슬레이브 장치에 대하여 송신한다.

기능 프로그램의 실행을 요구받은 슬레이브 장치는, 그 기능 프로그램을 실행함과 함께, 자 장치의 장치 정보 테이블을 갱신한다. 이 때, 필요하다면, 슬레이브 장치 내의 정보 처리 컨트롤러에 포함되는 메인 프로세서(21)는, 상기의 방법에 의해서 자 장치의 외부 기록부(28)로부터 메인 메모리(26)에 기능 프로그램 및 해당 기능 프로그램과 제휴 동작하는 서브 프로세서 프로그램을 로드한다.

기능 프로그램의 실행을 요구받은 슬레이브 장치의 외부 기록부(28)에, 필요한 기능 프로그램 또는 해당 기능 프로그램과 제휴 동작하는 서브 프로세서 프로그램이 기록되어 있지 않은 경우에는, 다른 정보 처리 장치가 해당 기능 프로그램 또는 서브 프로세서 프로그램을, 그 기능 프로그램 실행 요구처 슬레이브 장치에 송신하도록, 시스템을 구성하면 된다.

서브 프로세서 프로그램에 대해서는, 상술한 로드 커맨드 및 킥 커맨드를 이용하여 다른 정보 처리 장치에 실행시킬 수도 있다.

기능 프로그램의 실행 종료 후, 기능 프로그램을 실행한 슬레이브 장치 내의 정보 처리 컨트롤러에 포함되는 메인 프로세서(21)는, 종료 통지를 마스터 장치(1) 내의 정보 처리 컨트롤러(11)에 포함되는 메인 프로세서(21-1)에 송신함과 함께, 자 장치의 장치 정보 테이블을 갱신한다. 마스터 장치(1) 내의 정보 처리 컨트롤러(11)에 포함되는 메인 프로세서(21-1)는, 그 종료 통지를 수신하고, 기능 프로그 램을 실행한 슬레이브 장치의 장치 정보 테이블을 갱신한다.

마스터 장치(1) 내의 정보 처리 컨트롤러(11)에 포함되는 메인 프로세서(21-1)는, 자 장치 및 타 장치의 장치 정보 테이블의 참조 결과로부터, 해당 기능 프로그램을 실행할 수 있는 정보 처리 장치로서, 자신을 선택하는 경우도 있을 수 있다. 그 경우에는 마스터 장치(1)가 해당 기능 프로그램을 실행한다.

도 7에 도시한 예에서, 사용자가 슬레이브 장치 A(정보 처리 장치(2))를 조작하고, 해당 조작에 따른 기능 프로그램을 다른 슬레이브 장치 B(정보 처리 장치(3))가 실행하는 경우의 분산 처리에 대하여, 도 8을 참조하면서 설명한다.

도 8에 도시하는 예에서는, 사용자가 슬레이브 장치 A를 조작함으로써, 슬레이브 장치 A를 포함하는 네트워크 시스템 전체의 분산 처리가 개시되고, 우선, 슬레이브 장치 A는 그 조작 정보를 마스터 장치(1)에 송신한다(단계 81).

마스터 장치(1)는, 그 조작 정보를 수신하고(단계 72), 또한 자 장치의 메인 메모리(26-1)에 기록되어 있는 자 장치 및 타 장치의 장치 정보 테이블로부터 각 정보 처리 장치의 동작 상태를 조사하여, 수신한 조작 정보에 따른 기능 프로그램을 실행할 수 있는 정보 처리 장치를 선택한다(단계 73). 도시하는 예에서는, 슬레이브 장치 B가 선택되는 경우를 나타내고 있다.

다음으로, 마스터 장치(1)는 그 선택한 슬레이브 장치 B에 대하여 기능 프로그램의 실행을 요구한다(단계 74).

슬레이브 장치 B는 그 실행 요구를 수신하고(단계 95), 또한 실행 요구된 기능 프로그램을 실행한다(단계 96).

이상과 같이, 사용자는, 1대의 정보 처리 장치만을 조작함으로써, 다른 정보 처리 장치를 조작하지 않고, 복수의 정보 처리 장치(1, 2, 3, 4)를 가상적인 1대의 정보 처리 장치(7)로서 동작시킬 수 있다.

A-11. 각 정보 처리 장치 및 시스템의 구체예

네트워크(9)를 통하여 상호 접속되는 정보 처리 장치(1, 2, 3, 4)는, 상기 한 바와 같은 정보 처리 컨트롤러(11, 12, 13, 14)에 의해서 정보 처리를 행하는 것이면, 기본적으로는 어떠한 구성이어도 된다. 도 9에는 정보 처리 장치의 일 구성예를 도시하고 있다.

정보 처리 컨트롤러(11)를 구비하는 정보 처리 장치(1)의 일례는, 하드디스크 레코더이다. 도 10 및 도 11에는 도면 중의 하드디스크 레코더의 하드웨어 구성 및 소프트웨어 구성을 각각 도시하고 있다. 하드디스크 레코더의 하드웨어 구성으로서는, 도 1에 도시한 외부 기록부(28-1)로서 하드디스크를 내장하고, 도 1에 도시한 외부 기록부(28-2)로서 DVD±R/RW, CD±R/RW, Bluray-Disc(등록 상표) 등의 광 디스크를 장착할 수 있도록 구성됨과 함께, 정보 처리 컨트롤러(11)의 버스(29-1)에 접속된 버스(31-1)에, 방송 수신부(32-1), 영상 입력부(33-1), 음성 입력부(34-1), 영상 출력부(35-1), 음성 출력부(36-1), 조작 패널부(37-1), 리모콘 수광부(38-1) 및 네트워크 접속부(39-1)가 접속되어 있다.

방송 수신부(32-1), 영상 입력부(33-1) 및 음성 입력부(34-1)는, 방송 신호를 수신하거나, 또는 정보 처리 장치(1)의 외부로부터 영상 신호 및 음성 신호를 입력하고, 각각 소정 포맷의 디지털 데이터로 변환하여, 정보 처리 컨트롤러(11)에 서의 처리를 위해 버스(31-1)에 송출한다. 영상 출력부(35-1) 및 음성 출력부(36-1)는, 정보 처리 컨트롤러(11)로부터 버스(31-1)에 송출된 영상 데이터 및 음성 데이터를 처리하여, 디지털 데이터 그대로, 또는 아날로그 신호로 변환하여, 정보 처리 장치(1)의 외부에 송출하는 것이고, 리모콘 수광부(38-1)는 리모콘 송신기(43-1)로부터의 리모콘(원격 조작) 적외선 신호를 수신한다.

도 9 및 도 10에 도시한 바와 같이, 정보 처리 장치(하드디스크 레코더)(1)의 영상 출력부(35-1) 및 음성 출력부(36-1)에는 모니터 표시 장치(41) 및 스피커 장치(42)가 접속된다.

도 9에 예시한 정보 처리 컨트롤러(12)를 구비하는 정보 처리 장치(2)도 하드디스크 레코더이며, 도 10에서 괄호 내에 참조 번호를 붙여 도시한 바와 같이, 정보 처리 장치(1)와 마찬가지로 구성된다. 단, 도 9에 도시한 바와 같이, 정보 처리 장치(하드디스크 레코더)(2)에는, 모니터 표시 장치 및 스피커 장치는 접속되지 않는다.

정보 처리 장치(하드디스크 레코더)(1 및 2), 즉 정보 처리 컨트롤러(11 및 12)의 소프트웨어 구성으로서는, 도 11에 도시한 바와 같이, 제어 프로그램으로서, MS 매니저 및 능력 교환 프로그램을 구비하고, 기능 프로그램으로서, 영상 음성 기록, 영상 음성 재생, 소재 검색 및 프로그램 녹화 예약을 위한 프로그램을 구비하고, 디바이스 드라이버로서, 방송 수신, 영상 출력, 음성 출력, 외부 기록부 입출력 및 네트워크 입출력을 위한 프로그램을 구비한다.

또한, 정보 처리 컨트롤러(13)를 구비하는 정보 처리 장치(3)의 다른 예는, PDA(Personal Digital Assistants)이다. 도 12에는 PDA로서 구성되는 정보 처리 장치(3)의 하드웨어 구성을 도시하고 있다. 도 12에 도시하는 예에서는, 도 1에 도시한 외부 기록부(28-5)로서, 메모리 카드 디스크를 장착할 수 있도록 구성되고, 정보 처리 컨트롤러(13)의 버스(29-3)에 접속된 버스(51)에, 액정 표시부(52), 음성 출력부(53), 카메라부(54), 음성 입력부(55), 키보드부(56) 및 네트워크 접속부(57)가 접속되어 있다.

또한, 도 1에서는 내부를 생략한 정보 처리 컨트롤러(13)는, 메인 프로세서(21-3), 서브 프로세서(23-7, 23-8, 23-9), DMAC(다이렉트 메모리 액세스 컨트롤러)(25-3), DC(디스크 컨트롤러)(27-3) 및 버스(29-3)를 구비하고, 그 메인 프로세서(21-3)는 LS(로컬 스토리지)(22-3)를 갖고, 각 서브 프로세서(23-7, 23-8, 23-9)는 LS(로컬 스토리지)(24-7, 24-8, 24-9)를 구비하고 있다.

또한, 도 13에는, 정보 처리 장치(PDA)(3), 즉 정보 처리 컨트롤러(13)의 소프트웨어 구성을 도시하고 있다. 도 13에 도시한 바와 같이, 제어 프로그램으로서, MS 매니저 및 능력 교환 프로그램을 구비하고, 기능 프로그램으로서, 영상 음성 기록, 영상 음성 재생, 전화번호부, 워드 프로세서 및 표 계산을 위한 프로그램, 및 Web 브라우저를 구비하고, 디바이스 드라이버로서, 영상 출력, 음성 출력, 카메라 영상 입력, 마이크 음성 입력 및 네트워크 입출력을 위한 프로그램을 구비하고 있다.

또한, 정보 처리 컨트롤러(14)를 구비하는 정보 처리 장치(4)는, 포터블 CD 플레이어이다. 도 14에는 포터블 CD 플레이어의 하드웨어 구성을 도시하고 있다. 도시하는 예에서는, 포터블 CD 플레이어는 도 1에 도시한 외부 기록부(28-6)로서, CD(Compact Disc)를 장착할 수 있도록 구성되고, 정보 처리 컨트롤러(14)의 버스(29-4)에 접속된 버스(61)에, 액정 표시부(62), 음성 출력부(63), 조작 버튼부(64) 및 네트워크 접속부(65)가 접속되어 있다.

또한, 도 1에서는 내부를 생략한 정보 처리 컨트롤러(14)는, 메인 프로세서(21-4), 서브 프로세서(23-10, 23-11, 23-12), DMAC(25-4), DC(27-4) 및 버스(29-4)를 구비하고, 그 메인 프로세서(21-4)는 LS(22-4)를 갖고, 각 서브 프로세서(23-10, 23-11, 23-12)는 LS(24-10, 24-11, 24-12)를 갖는다.

도 15에는 정보 처리 장치(포터블 CD 플레이어)(4), 즉 정보 처리 컨트롤러(14)의 소프트웨어 구성을 도시하고 있다. 도시하는 바와 같이, 제어 프로그램으로서, MS 매니저 및 능력 교환 프로그램을 구비하고, 기능 프로그램으로서, 음악 재생을 위한 프로그램을 구비하고, 디바이스 드라이버로서, 음성 출력, CD 제어 및 네트워크 입출력을 위한 프로그램을 구비한다.

도 9에 예시한 네트워크 시스템에서는, 정보 처리 장치(1, 3 및 4)가 네트워크(9) 상에 접속되어 있고, 정보 처리 장치(1)가 마스터 장치(MS 스테이터스=0)로서, 정보 처리 장치(3 및 4)가 슬레이브 장치(MS 스테이터스=1)로서, 설정되어 있는 것으로 한다.

이 상태에서, 새롭게 정보 처리 장치(2)가 네트워크(9)에 접속되면, 상술한 방법에 의해서, 정보 처리 장치(2) 내의 정보 처리 컨트롤러(12)에 포함되는 메인 프로세서(21-2)에서 실행되고 있는 MS 매니저는, 다른 정보 처리 장치(1, 3 및 4) 에 MS 스테이터스를 조회하여, 정보 처리 장치(1)가 이미 마스터 장치로서 존재하는 것을 인식하고, 자 장치(정보 처리 장치(2))를 슬레이브 장치(MS 스테이터스=1)로 설정한다. 또한, 마스터 장치로 설정되어 있는 정보 처리 장치(1)는, 새롭게 추가된 정보 처리 장치(2)를 포함하는 각 장치의 장치 정보를 수집하여, 메인 메모리(26-1) 내의 장치 정보 테이블을 갱신한다.

이러한 상태에서, 사용자에 의해서 슬레이브 장치인 정보 처리 장치(PDA)(3)에서 2 시간의 방송 프로그램을 녹화 예약하기 위한 조작이 행하여진 경우에 대해서, 이하에 설명한다.

이 경우, 슬레이브 장치인 정보 처리 장치(PDA)(3)는, 사용자로부터 녹화 개시 시각, 녹화 종료 시각, 녹화 대상 방송 채널, 녹화 품질 등의 정보를 포함하는 녹화 예약 정보의 입력을 접수하고, 해당 녹화 예약 정보 및 DMA 커맨드로서의 녹화 예약 커맨드를 포함하는 소프트웨어 셀을 생성하여, 마스터 장치인 정보 처리 장치(1)에 송신한다.

DMA 커맨드가 녹화 예약 커맨드인 소프트웨어 셀을 수신한 정보 처리 장치(1) 내의 정보 처리 컨트롤러(11)에 포함되는 메인 프로세서(21-1)는, 녹화 예약 커맨드를 판독함과 함께, 메인 메모리(26-1) 내의 장치 정보 테이블을 참조하여, 해당 녹화 예약 커맨드를 실행 가능한 정보 처리 장치를 특정한다.

우선, 메인 프로세서(21-1)는, 장치 정보 테이블에 포함되는 각 정보 처리 장치(1, 2, 3, 4)의 정보 처리 장치 종별 ID를 판독하여, 녹화 예약 커맨드에 대응하는 기능 프로그램을 실행 가능한 정보 처리 장치를 추출한다. 여기서는, 녹화 기능을 나타내는 정보 처리 장치 종별 ID를 갖는 정보 처리 장치(1, 2)가 후보 장치로서 특정되고, 정보 처리 장치(3, 4)는 후보 장치로부터 제외된다.

다음으로, 마스터 장치인 정보 처리 장치(1) 내의 정보 처리 컨트롤러(11)에 포함되는 메인 프로세서(21-1)는, 장치 정보 테이블을 참조하여, 정보 처리 장치(1, 2)의 메인 프로세서 또는 서브 프로세서의 처리 능력, 메인 메모리에 관한 정보 등의 장치에 관한 정보를 판독하고, 정보 처리 장치(1, 2)가 녹화 예약 커맨드에 대응하는 기능 프로그램의 실행에 필요한 요구 스펙을 만족하는지의 여부를 판단한다. 여기서는, 정보 처리 장치(1, 2) 모두, 녹화 예약 커맨드에 대응하는 기능 프로그램의 실행에 필요한 요구 스펙을 만족하는 것으로 한다.

또한, 메인 프로세서(21-1)는 장치 정보 테이블을 참조하여, 정보 처리 장치(1, 2)의 외부 기록부에 관한 정보를 판독하고, 외부 기록부의 빈 용량이 해당 녹화 예약 커맨드의 실행에 필요한 용량을 만족하는지의 여부를 판단한다. 정보 처리 장치(1, 2)는 하드디스크 레코더이기 때문에, 각각 하드디스크(28-1, 28-3)의, 총 용량과 사용량의 차분이, 각각의 빈 용량에 상당한다.

이 경우, 정보 처리 장치(1)의 하드디스크(28-1)의 빈 용량이, 녹화 시간으로 환산하여 10분이고, 정보 처리 장치(2)의 하드디스크(28-3)의 빈 용량이, 녹화 시간으로 환산하여 20 시간이라고 하자.

이 때, 마스터 장치인 정보 처리 장치(1) 내의 정보 처리 컨트롤러(11)에 포함되는 메인 프로세서(21-1)는, 해당 녹화 예약 커맨드의 실행에 필요한 2 시간 분의 빈 용량을 확보할 수 있는 정보 처리 장치를, 실행 요구처 슬레이브 장치로서 특정한다.

그 결과, 정보 처리 장치(2)만이 실행 요구처 슬레이브 장치로서 선택되고, 마스터 장치인 정보 처리 장치(1) 내의 정보 처리 컨트롤러(11)에 포함되는 메인 프로세서(21-1)는, 사용자에 의해 조작된 정보 처리 장치(3)로부터 송신된 녹화 예약 정보를 포함하는 해당 녹화 예약 커맨드를 정보 처리 장치(2)에 송신하여, 상기 2 시간의 방송 프로그램의 녹화 예약의 실행을 요구한다.

그리고, 정보 처리 장치(2) 내의 정보 처리 컨트롤러(12)에 포함되는 메인 프로세서(21-2)는, 해당 녹화 예약 커맨드를 해석하여, 녹화에 필요한 기능 프로그램을 외부 기록부인 하드디스크(28-3)로부터 메인 메모리(26-2)에 로드하고, 녹화 예약 정보에 따라서 녹화를 실행한다. 그 결과, 녹화 예약된 2 시간의 방송 프로그램의 영상 음성 데이터가 정보 처리 장치(2)의 하드디스크(28-3)에 기록된다.

이와 같이, 도 9의 예의 네트워크 시스템에서도, 사용자는 1대의 정보 처리 장치만을 조작함으로써, 다른 정보 처리 장치를 조작하지 않고서, 복수의 정보 처리 장치(1, 2, 3, 4)를 가상적인 1대의 정보 처리 장치(7)로서 동작시킬 수 있다.

B. 가상적인 1대의 정보 처리 장치에서의 확장 기능의 실현

상술한 바와 같이, 본 발명에 따르면, 네트워크 접속된 복수의 정보 처리 장치가 상호 제휴함으로써 1대의 가상적인 정보 처리 장치를 실현할 수 있다.

본 발명의 다른 실시예로서, 가상 정보 처리 장치를 구성하는 적어도 하나의 정보 처리 장치는, 자 장치의 물리 기억 장치의 물리 기억 공간 상에 다른 정보 처리 장치의 사용을 허가하는 공개 영역을 형성하도록 하였다. 여기서 말하는 물리 기억 장치에는, 메인 메모리나 그 밖의 로컬 메모리, 하드디스크 등의 외부 기억 장치, 나아가서는 자 장치에 로컬 접속되는 각 기기에의 입출력을 할당한 I/O 공간이 포함되고, 제휴 동작을 행하는 정보 처리 장치 사이에서 이들 정보 자원을 공유하는 것이 가능하게 된다.

이러한 정보 자원의 공유는, 공개 영역을 요구하는 정보 처리 장치와 공개 영역을 제공하는 정보 처리 장치 사이에서의, 요구 및 허가 응답에 관한 소정의 핸드 쉐이크 수순에 따라서 실현된다. 이 핸드 쉐이크 수순에는 정보 처리 장치 간의 상호 인증 등의 처리를 포함하여도 된다.

각 정보 처리 장치는 하나 이상의 물리 기억 장치를 구비하고 있고(상술), 통상은 각 물리 기억 장치의 물리 기억 공간, 즉 물리 세그먼트 어드레스를, 논리적인 기억 공간, 즉 가상 어드레스 공간에 맵핑하고, 이 가상 어드레스 공간 상에서 처리의 실행이 행하여진다. 본 실시예에서는, 정보 처리 장치가 다른 정보 처리 장치로부터 공개 영역의 사용이 허가되었을 때에는, 다른 정보 처리 장치의 물리 어드레스 공간에 존재하는 공개 영역을 자 장치의 가상 어드레스 공간에 맵핑하여 사용한다. 즉, 정보 처리 장치는, 다른 정보 처리 장치로부터 얻은 공개 영역의 물리 세그먼트 어드레스를, 자 장치의 가상 어드레스 공간의 가상 세그먼트 어드레스에 맵핑하여 사용한다.

이 세그먼트 변환의 구조는 이하와 같다. 공개 영역을 다른 정보 처리 장치에 제공하는 정보 처리 장치측에서는, 물리 기억 공간 상에서 공개 영역에 할당된 물리 세그먼트 어드레스에 대하여 공개 영역 어드레스를 할당한다. 이 공개 영역 어드레스는, 네트워크 상, 즉 가상 정보 처리 장치 상에서는, 정보 처리 장치를 일의에 식별하는 정보 처리 장치 ID 등으로 이루어지는 수신처 ID와 해당 장치 상에서의 공개 영역 어드레스의 조합으로서 어드레스 표현이 이루어진다. 또한, 다른 정보 처리 장치가 제공하는 공개 영역을 사용하는 정보 처리 장치측에서는, 수신처 ID와 해당 장치 상에서의 공개 영역 어드레스의 조합으로 이루어지는 어드레스 표현을 가상 세그먼트 어드레스로 변환한다.

공개 영역을 제공하는 정보 처리 장치와, 공개 영역을 사용하는 정보 처리 장치의 양쪽의 세그먼트 변환부가 네트워크 경유로 제휴 동작함으로써, 공개 영역을 사용하는 정보 처리 장치측에서는, 가상 세그먼트 어드레스만을 사용함으로써, 자 장치 내의 로컬 메모리와 다른 정보 처리 장치의 공개 영역 중 어디에도 투과적으로 액세스할 수 있다. 즉, 네트워크를 통하여 원격으로 배치되어 있는 공개 영역이 투과적으로 되어, 자 장치 내의 로컬 메모리와 구별하지 않고 액세스하는 것이 가능하게 된다.

예를 들면, 어떤 정보 처리 장치에서, 가상 어드레스 공간에 맵핑되어 있는 다른 정보 처리 장치의 공개 영역에의 액세스 요구가 행해졌을 때에는, 우선, 액세스 요구된 가상 세그먼트 어드레스를 수신처 ID 및 공개 영역 어드레스로 이루어지는 어드레스 표현으로 변환하고, 수신처 ID에 의해 지정되는 정보 처리 장치에 대하여, 액세스 요구를 행한다.

그리고, 액세스 요구를 수리한 정보 처리 장치측에서는, 공개 영역 어드레스를 자 장치 내의 물리 세그먼트 어드레스로 변환하고, 해당하는 물리 세그먼트로부 터 데이터를 취득할 수 있다. 그 후, 물리 세그먼트를 공개 영역 어드레스로 변환하고, 수신처 ID 및 공개 영역 어드레스에서 취득된 데이터로서, 요구원의 정보 처리 장치에 되돌려 보낸다. 요구원의 정보 처리 장치에서는, 수신처 ID 및 공개 영역 어드레스를 가상 세그먼트 어드레스로 변환하고, 요구원의 어플리케이션 등에 대해서는 가상 세그먼트로부터 취득된 데이터로서 되돌려 보낸다.

또한, 공개 영역을 형성한 정보 처리 장치는, 자신의 공개 영역을 분할하여, 다른 복수의 정보 처리 장치에 대하여 동시에 사용 허가를 주도록 하여도 된다. 또한, 정보 처리 장치는 다른 2 이상의 정보 처리 장치가 형성한 공개 영역의 사용을 요구하고, 사용이 허가된 2 이상의 정보 처리 장치의 공개 영역을 동시에 사용하도록 하여도 된다.

도 16에는 본 발명의 일 실시예에 따른 네트워크 시스템의 구성을 모식적으로 도시하고 있다.

도시하는 네트워크 시스템은, 홈 네트워크 등의 로컬 네트워크(30)에 의해 상호 접속된 셋톱 박스(STB)나 AV 기기 등 복수의 정보 처리 장치(10, 11, …)가 상호 제휴함으로써 1대의 가상적인 정보 처리 장치(20)를 구축하고 있다. 이러한 경우, 2대 이상의 정보 처리 장치(10, 11)에서 분산하여 유지되는 정보를 공개 영역에 둠으로써, 사용자로부터 보면 가상적으로 1대의 기기가 유지하는 정보로서 취급할 수 있다.

다음으로, 정보 처리 장치가 공개 영역을 형성하기 위한 처리에 대하여, 도 17 및 도 18을 참조하면서 설명한다.

정보 처리 장치는, 메인 메모리 내에서 예를 들면 오퍼레이팅 시스템에서 사용되고 있지 않은 미사용 영역을 공개 영역에 할당한다. 그리고, 메인 메모리 상에서 공개 영역에 할당된 물리 세그먼트 어드레스에 대하여 공개 영역 어드레스를 할당한다. 이 공개 영역 어드레스는, 네트워크 상, 즉 가상 정보 처리 장치 상에서는, 정보 처리 장치를 일의에 식별하는 정보 처리 장치 ID 등으로 이루어지는 수신처 ID와 정보 사이즈 번호의 조합으로서 어드레스 표현이 이루어진다.

한편, 메인 메모리 내에 미사용 영역이 없는 정보 처리 장치는, 다른 정보 처리 장치에 대하여 공개 영역의 사용을 요구한다. 이 사용 요구가 허가되어, 공개 영역을 획득할 수 있었을 때에는, 수신처 ID와 정보 사이즈 번호의 조합으로 이루어지는 공개 영역 어드레스를 가상 세그먼트 어드레스로 변환하고, 공개 영역을 가상 어드레스 공간에 배치한다. 그 결과, 정보 처리 장치 상에서는, 네트워크를 통하여 원격으로 배치되어 있는 공개 영역이 투과적으로 되어, 자 장치 내의 물리 메모리와 구별하지 않고 액세스하는 것이 가능하게 된다.

예를 들면, 공개 데이터 및 비공개 데이터를 포함하는 다양한 데이터를 관리하는 서버 등의 장치는, 공개 데이터를 공개 영역에서 유지함으로써, 가상적으로 1대로서 동작하는 다른 정보 처리 장치와 정보의 공유를 용이하게 실현할 수 있다(도 19를 참조할 것). 즉, 서버는 슬레이브에 정보나 영역을 공개하고, 클라이언트는 서버가 공개한 정보나 영역을 판독하여 실행할 수 있다. 또한, 클라이언트가 대리 서버로 되고, 다른 클라이언트에 공개하는 것도 가능하다.

도 20에는 네트워크 접속되어 제휴 동작하는 2대의 셋톱 박스(STB)의 한쪽 STB(a)가 서버, 다른 쪽 STB(b)가 클라이언트로 되어, STB(b)에 STB(a)의 정보를 맵핑한 모습을 도시하고 있다.

공개 영역을 형성한 정보 처리 장치는, 자신의 공개 영역을 분할하여, 다른 복수의 정보 처리 장치에 대하여 동시에 사용 허가를 주도록 하여도 된다. 도 21에는 1대의 셋톱 박스 STB(a)가 2대의 셋톱 박스 STB(b) 및 STB(c)에 공개 영역의 사용을 허가하고 있는 모습을 도시하고 있다.

또한, 정보 처리 장치는 다른 2 이상의 정보 처리 장치가 형성한 공개 영역의 사용을 요구하고, 사용이 허가된 2 이상의 정보 처리 장치의 공개 영역을 동시에 사용하도록 하여도 된다. 도 22에는, 1대의 셋톱 박스 STB(b)가 2대의 셋톱 박스 STB(a) 및 STB(c)로부터 사용이 허가된 공개 영역을 사용하고 있는 모습을 도시하고 있다.

1대의 가상 정보 처리 장치로서 제휴 동작하는 정보 처리 장치끼리에서, 상술한 바와 같은 정보 자원의 공유를 행할 때에는, 공개 영역을 요구하는 정보 처리 장치와 공개 영역을 제공하는 정보 처리 장치 사이에서의, 요구 및 허가 응답에 관한 소정의 핸드 쉐이크 수순에 따라서 실현된다. 이 핸드 쉐이크 수순에 대하여, 도 23을 참조하면서 설명한다.

공개 영역을 제공하는 측의 정보 처리 장치 STB(a)측에서는, 메모리 공간 상에서 공개하는 영역과, 공개처로 되는 정보 처리 장치 ID를 미리 설정해 놓는다(단계 S11, S12).

또한, 공개 영역을 사용하는 측의 정보 처리 장치 STB(b)측에서는 미사용 영 역을 조사한다(단계 S21).

그리고, 정보 처리 장치 STB(b)는 정보 처리 장치 STB(a)에 대하여 영역 공개 요구를 발행한다(단계 S22). 이 영역 공개 요구에는 사용하고자 하는 메모리 사이즈를 기재한다.

이에 대하여, 정보 처리 장치 STB(a)측에서는, 이 요구에 응답하여, 정보 처리 장치 STB(b)의 정보 처리 장치 ID에 기초하여, 설정해 놓은 공개처인지의 여부를 인증 처리한다(단계 S13).

여기서, 정보 처리 장치 STB(b)가 대상으로 하는 공개처이면 영역 공개 허가 응답을 되돌려 보낸다(단계 S14). 이 경우, 정보 처리 장치 STB(a)는, 자 장치의 물리 메모리 공간에 형성한 공개 영역의 물리 세그먼트 어드레스와 수신처 ID와 공개 영역 사이즈로 이루어지는 공개 영역 어드레스 간의 맵핑 테이블의 작성을 행한다.

또한, 정보 처리 장치 STB(b)가 대상으로 하는 공개처가 아닌 경우에는 영역 공개 불허가 응답을, 정보 처리 장치 STB(a)는 정보 처리 장치 STB(b)에 되돌려 보낸다(단계 S15).

정보 처리 장치 STB(b)측에서는, 정보 처리 장치 STB(a)로부터의 요구 응답이 허가 및 불허가 중 어느 것인지를 체크한다(단계 S23). 응답이 허가이면, 수신처 ID와 공개 영역 사이즈로 이루어지는 공개 영역 어드레스와 자 장치의 가상 메모리 공간에서 공개 영역에 할당한 가상 세그먼트 간의 맵핑 테이블의 작성을 행한다(단계 S24). 또한, 요구 응답이 불허가이거나, 또는 응답에 에러가 발생한 경우 에는, 맵핑에 실패하였다고 하여, 본 처리 루틴을 이상 종료시킨다(단계 S25).

수신처 ID와 공개 영역 사이즈와 가상 세그먼트 간의 맵핑 테이블은, 공개 영역의 제공원인 정보 처리 장치를 나타내는 수신처 ID와 데이터 길이를, 가상 어드레스 공간 상의 어드레스 번호, 즉 가상 세그먼트 어드레스로 변환함으로써 작성된다.

도 24에는 도 23에 도시한 핸드 쉐이크 수순에 따라서 정보 처리 장치 STB(a)와 STB(b) 사이에서 공개 영역의 사용이 허가된 경우에, 정보 처리 장치 STB(a)의 물리 메모리 공간 상의 공개 영역을 STB(b)측의 가상 메모리 공간에 할당하기 위한 동작 시퀀스를 도시하고 있다.

정보 처리 장치 STB(b)는, 정보 처리 장치 STB(a)에 대하여, 사용하고자 하는 메모리 사이즈를 지정하여, 영역 공개 요구를 발행하고, 정보 처리 장치 STB(a)는 허가 응답을 행한다.

정보 처리 장치 STB(a)측에서는, 자 장치의 물리 메모리 공간에 형성한 공개 영역의 물리 세그먼트 어드레스와 수신처 ID와 공개 영역 사이즈로 이루어지는 공개 영역 어드레스 간의 맵핑 테이블의 작성을 행한다.

또한, 정보 처리 장치 STB(b)측에서는, 수신처 ID와 공개 영역 사이즈로 이루어지는 공개 영역 어드레스와 자 장치의 가상 메모리 공간에서 공개 영역에 할당한 가상 세그먼트 간의 맵핑 테이블의 작성을 행한다.

도 25에는 맵핑 테이블의 구성을 모식적으로 도시하고 있다. 도시하는 바와 같이, 정보 처리 장치 STB(a)측의 맵핑 테이블은, 자 장치의 물리 메모리 공간에 형성한 공개 영역의 물리 세그먼트 어드레스와 수신처 ID와 공개 영역 사이즈로 이루어지는 공개 영역 어드레스 간의 대응 관계를 기술하고 있다. 또한, 정보 처리 장치 STB(b)측의 맵핑 테이블은, 수신처 ID와 공개 영역 사이즈로 이루어지는 공개 영역 어드레스와 자 장치의 가상 메모리 공간에서 공개 영역에 할당한 가상 세그먼트 간의 대응 관계를 기술하고 있다.

이러한 맵핑 테이블을 참조함으로써, 공개 영역을 사용하는 정보 처리 장치 STA(b)측으로부터는, 공개 영역을 제공하는 정보 처리 장치 STB(a)의 정보를, 마치 자 장치의 메인 메모리나 외부 기억 장치 상의 정보인 것처럼 취급할 수 있다. 또한, 정보 처리 장치 STB(a)측에서는, 공개 영역 어드레스를 지정한 액세스 요구에 대하여, 해당하는 물리 세그먼트 어드레스로부터 데이터를 취득하여, 요구원에 되돌려 보낼 수 있다.

도 26에는 정보 처리 장치 STB(b)가 정보 처리 장치 STB(a)의 공개 영역에 액세스하기 위한 동작 시퀀스를 도시하고 있다.

정보 처리 장치 STB(b)에서, 가상 어드레스 공간에 맵핑되어 있는 정보 처리 장치 STB(a)의 공개 영역에의 액세스 요구가 행해졌을 때에는, 우선, 액세스 요구된 가상 세그먼트 어드레스를 수신처 ID 및 세그먼트 번호로 이루어지는 공개 영역 어드레스 표현으로 변환하고, 수신처 ID에서 지정되는 정보 처리 장치 STB(a)에 대하여, 액세스 요구를 행한다.

정보 처리 장치 STB(a)측에서는, 공개 영역 어드레스의 수신처 ID에 기초하여, 자 장치 내의 공개 영역에의 액세스 요구임을 인식하고, 공개 영역 어드레스의 세그먼트 번호를 물리 세그먼트 어드레스로 변환한다. 그리고, 해당하는 물리 세그먼트로부터 데이터를 취득한다. 계속해서, 물리 세그먼트 어드레스를 수신처 ID 및 세그먼트 번호로 이루어지는 공개 영역 어드레스로 다시 변환하고, 수신처 ID 및 공개 영역 어드레스에서 취득된 데이터로서, 요구원의 정보 처리 장치 STB(b)에 되돌려 보낸다.

정보 처리 장치 STB(b)측에서는, 수신처 ID 및 공개 영역 어드레스를 가상 세그먼트 어드레스로 변환하고, 요구원의 어플리케이션 등에 대해서는 가상 세그먼트로부터 취득된 데이터로서 되돌려 보낸다.

도 27에는 정보 처리 장치 STB(b)에서의 메모리 액세스의 수순에 대하여 도해하고 있다. 도 27을 참조하면서, 세그먼트 변환 메카니즘에 기초하여 공개 영역에 메모리 액세스하기 위해서 구조에 대하여 설명한다.

정보 처리 장치 STB(b)에서, 예를 들면 메인 프로세서에서 동작 중인 프로그램, 혹은 서브 프로세서에서 동작 중인 프로그램으로부터 데이터에의 액세스 요구가 발생하였다고 하자. 여기서 말하는 데이터는, 프로그램 코드 및 프로그램 코드가 사용하는 데이터의 양쪽을 포함하는 것으로 한다.

데이터 요구는 통상, 가상 세그먼트 어드레스를 지정하여 행해진다. 가상 세그먼트 어드레스를 세그먼트 변환하고, 그 물리 세그먼트 어드레스가 메인 메모리 상의 세그먼트를 나타내는 경우에는, DMAC(직접 메모리 액세스 컨트롤러)를 이용하여 메모리 액세스하고, 해당하는 물리 메모리 세그먼트로부터 데이터를 취득한다.

또한, 데이터 요구된 가상 세그먼트 어드레스가 하드디스크 등의 외부 기억 장치 상의 세그먼트(섹터)를 나타내는 경우에는, DC(디스크 컨트롤러)를 이용하여 디스크 액세스하여, 해당하는 섹터로부터 데이터를 취득한다.

또한, 데이터 요구된 가상 세그먼트 어드레스가 서브 프로세서의 로컬 메모리 상의 물리 세그먼트 어드레스를 나타내는 경우에는, 해당하는 서브 프로세서를 통하여 로컬 메모리에 액세스하여, 해당하는 물리 메모리 세그먼트로부터 데이터를 취득한다.

이에 대하여, 데이터 요구된 가상 세그먼트 어드레스가 공개 영역 어드레스를 나타내는 경우에는, 수신처 ID/세그먼트 변환부에 의해, 액세스 요구된 가상 세그먼트 어드레스를 수신처 ID 및 세그먼트 번호로 이루어지는 공개 영역 어드레스 표현으로 변환한다. 그리고, 수신처 ID에서 지정되는 정보 처리 장치 STB(a)에 대하여, 액세스 요구를 행한다.

한편, 정보 처리 장치 STB(a)측에서는, 공개 영역 어드레스의 수신처 ID에 기초하여 자 장치 내의 공개 영역에의 액세스 요구임을 인식하고, 수신처 ID/세그먼트 변환부에 의해, 액세스 요구된 공개 영역 어드레스의 세그먼트 번호를 물리 세그먼트 어드레스로 변환한다.

그 물리 세그먼트 어드레스가 메인 메모리 상의 세그먼트를 나타내는 경우에는, DMAC(직접 메모리 액세스 컨트롤러)를 이용하여 메모리 액세스하여, 해당하는 물리 메모리 세그먼트로부터 데이터를 취득한다.

또한, 데이터 요구된 가상 세그먼트 어드레스가 하드디스크 등의 외부 기억 장치 상의 세그먼트(섹터)를 나타내는 경우에는, DC(디스크 컨트롤러)를 이용하여 디스크 액세스하여, 해당하는 섹터로부터 데이터를 취득한다.

계속해서, 수신처 ID/세그먼트 변환부에 의해, 물리 세그먼트 어드레스를 수신처 ID 및 세그먼트 번호로 이루어지는 공개 영역 어드레스로 다시 변환하고, 수신처 ID 및 공개 영역 어드레스에서 취득된 데이터로서, 요구원의 정보 처리 장치 STB(b)에 되돌려 보낸다.

정보 처리 장치 STB(b)측에서는, 수신처 ID/세그먼트 변환부에 의해, 수신처 ID 및 공개 영역 어드레스를 가상 세그먼트 어드레스로 변환하고, 요구원의 프로그램에 대해서는 가상 세그먼트로부터 취득된 데이터로서 되돌려 보낸다.

이와 같이, 네트워크 경유로 제휴하여 1대의 가상 정보 처리 장치로서 동작하는 각 정보 처리 장치 STB(a) 및 STB(b) 사이에서는, 각각의 수신처 ID/세그먼트 변환부가 네트워크 상에서 협조 동작함으로서, 정보 처리 장치 STB(b)가 사용하는 정보 처리 장치 STB(a)의 공개 영역이 투과적으로 되어, 자 장치 내의 물리 메모리와 구별하지 않고 액세스하는 것이 가능하게 된다.

이상, 특정 실시예를 참조하면서, 본 발명에 대하여 상세히 설명하여 왔다. 그러나, 본 발명의 요지를 일탈하지 않는 범위에서 당업자가 해당 실시예의 수정이나 대용을 할 수 있음은 자명하다. 즉, 예시라고 하는 형태로 본 발명을 개시하여 온 것이며, 본 명세서의 기재 내용을 한정적으로 해석하여서는 안 된다. 본 발명의 요지를 판단하기 위해서는 이후에 기재하는 특허청구범위의 란을 참작하여야 한다.

본 발명에 따르면, 네트워크 접속된 복수의 기기가 협조 동작에 의해 분산 처리를 행함으로써, 가상적으로 1대의 기기로서 동작할 수 있는, 우수한 정보 처리 시스템 및 정보 처리 방법과, 컴퓨터 프로그램을 제공할 수 있다.

본 발명의 다른 목적은, 네트워크 경유로 제휴 동작하는 정보 처리 장치 사이에서 기억 공간의 공유를 행할 수 있는, 우수한 정보 처리 시스템 및 정보 처리 방법과, 컴퓨터 프로그램을 제공하는 데에 있다.

예를 들면, 홈 네트워크 상에서 복수의 AV 기기가 제휴하여 구성되는 정보 처리 시스템에서는, AV 기기 사이에서 정보의 공유를 도모할 수 있다. 즉, 하나의 AV 기기에서의 유지 정보를 공유하여, 자원의 보전을 행하거나, 다른 AV 기기의 정보를 변경하거나, 많은 AV 기기의 정보를 다른 서버로부터 변경하거나 할 수 있다. 또한, 다른 AV 기기에 정보를 개시하거나, 많은 AV 기기에 동일한 정보를 개시하거나 할 수 있다.

Claims (24)

- 네트워크 접속되는 복수의 정보 처리 장치의 제휴 동작에 의해 가상적으로 1대의 가상 정보 처리 장치로서 동작하는 정보 처리 시스템으로서,각 정보 처리 장치는 물리 기억 장치를 구비하고,적어도 하나의 정보 처리 장치는, 자 장치의 물리 기억 장치의 물리 기억 공간 상에 다른 정보 처리 장치의 사용을 허가하는 공개 영역을 형성하고, 다른 정보 처리 장치로부터의 공개 영역의 사용 요구에 응답하여 사용을 허가하는 것을 특징으로 하는 정보 처리 시스템.

- 제1항에 있어서,공개 영역을 형성한 정보 처리 장치는, 다른 2 이상의 정보 처리 장치에 대하여 공개 영역의 사용을 허가할 수 있는 것을 특징으로 하는 정보 처리 시스템.

- 제1항에 있어서,정보 처리 장치는, 다른 2 이상의 정보 처리 장치가 형성한 공개 영역의 사용을 요구하고, 사용이 허가된 2 이상의 정보 처리 장치의 공개 영역을 동시에 사용할 수 있는 것을 특징으로 하는 정보 처리 시스템.

- 제1항에 있어서,각 정보 처리 장치는, 하나 이상의 물리 기억 장치와, 각 물리 기억 장치의 물리 기억 공간을 논리 기억 공간에 맵핑하는 기억 공간 변환 수단을 구비하여, 논리 기억 공간에 기초하여 처리를 실행하고,정보 처리 장치의 기억 공간 변환 수단은, 다른 정보 처리 장치로부터 사용이 허가된 공개 영역의 물리 기억 공간을 자 장치의 논리 기억 공간에 맵핑하는 것을 특징으로 하는 정보 처리 시스템.

- 제4항에 있어서,공개 영역을 다른 정보 처리 장치에 제공하는 제1 정보 처리 장치의 제1 기억 공간 변환 수단은, 물리 기억 공간 상의 공개 영역의 물리 어드레스에 공개 영역 어드레스를 할당하고,제1 정보 처리 장치가 제공하는 공개 영역을 사용하는 제2 정보 처리 장치의 제2 기억 공간 변환 수단은, 그 공개 영역의 공개 영역 어드레스에 논리 기억 공간 상의 논리 어드레스를 할당하는 것을 특징으로 하는 정보 처리 시스템.

- 제5항에 있어서,상기 제2 정보 처리 장치에서 논리 기억 공간에 맵핑된 상기 제1 정보 처리 장치의 공개 영역에의 액세스 요구가 행해졌을 때,상기 제2 기억 공간 변환 수단은 액세스 요구된 논리 어드레스를 공개 영역 어드레스로 변환하고,상기 제1 기억 공간 변환 수단은 공개 영역 어드레스를 상기 제1 정보 처리 장치에서의 물리 어드레스로 변환하여 물리 기억 공간에 액세스하는 것을 특징으로 하는 정보 처리 시스템.

- 제6항에 있어서,상기 제1 기억 공간 변환 수단은, 공개 영역에 할당되어 있는 물리 어드레스로부터 취득한 데이터를 공개 어드레스 상의 데이터로서 상기 제2 기억 공간 변환 수단에 되돌려 보내고,상기 제2 기억 공간 변환 수단은, 공개 어드레스 상의 데이터를 논리 어드레스 상의 데이터로서 액세스 요구원에 되돌려 보내는 것을 특징으로 하는 정보 처리 시스템.

- 제1항에 있어서,각 정보 처리 장치는, 물리 기억 장치 상의 오퍼레이팅 시스템에서 미사용 공간에 공개 영역을 형성하는 것을 특징으로 하는 정보 처리 시스템.

- 제1항에 있어서,각 정보 처리 장치는, 프로세서가 사용하는 메인 메모리 또는 프로세서에 로컬 접속되는 그 밖의 로컬 메모리의 메모리 공간 상에 공개 영역을 형성하는 것을 특징으로 하는 정보 처리 시스템.

- 제1항에 있어서,각 정보 처리 장치는, 자 장치에 로컬 접속되는 외부 기억 장치의 기억 공간 상에 공개 영역을 형성하는 것을 특징으로 하는 정보 처리 시스템.

- 제1항에 있어서,각 정보 처리 장치는, 자 장치에 로컬 접속되는 각 기기에의 입출력을 할당한 입출력 기억 공간 상에 공개 영역을 형성하는 것을 특징으로 하는 정보 처리 시스템.

- 네트워크 접속되는 다른 하나 이상의 정보 처리 장치와의 제휴에 의해 가상적으로 1대의 가상 정보 처리 장치의 일부로서 동작하는 정보 처리 장치로서,물리 기억 공간과,상기 물리 공간 상에 형성된, 다른 정보 처리 장치의 사용을 허가하는 공개 영역과,다른 정보 처리 장치로부터의 공개 영역의 사용 요구에 응답하여 상기 공개 영역의 사용을 허가하는 공개 영역 사용 제어 수단을 포함하는 것을 특징으로 하는 정보 처리 장치.

- 제12항에 있어서,다른 정보 처리 장치의 공개 영역의 사용을 요구하는 공개 영역 사용 요구 수단을 더 포함하는 것을 특징으로 하는 정보 처리 장치.

- 제13항에 있어서,상기 물리 기억 공간은 하나 이상의 물리 기억 장치에 의해 구성되고,각 물리 기억 장치의 물리 기억 공간을 논리 기억 공간에 맵핑하는 기억 공간 변환 수단을 더 구비하여, 논리 기억 공간에 기초하여 처리를 실행하고,상기 기억 공간 변환 수단은, 다른 장치에 사용을 허가하는 공개 영역의 물리 어드레스에 공개 영역 어드레스를 할당하고, 다른 장치로부터 사용이 허가된 공개 영역 어드레스에 논리 어드레스를 할당하는 것을 특징으로 하는 정보 처리 장치.

- 제14항에 있어서,다른 정보 처리 장치로부터 공개 영역에의 액세스 요구가 행해졌을 때,상기 기억 공간 변환 수단은, 그 액세스 요구된 공개 영역 어드레스를 물리 어드레스로 변환하고, 상기 물리 기억 공간의 상기 물리 어드레스로부터 추출된 데이터를 공개 영역 어드레스 상의 데이터로서 되돌려 보내는 것을 특징으로 하는 정보 처리 장치.

- 제14항에 있어서,액세스 요구된 논리 어드레스가 다른 정보 처리 장치로부터 사용이 허가되어 있는 공개 영역일 때,상기 기억 공간 변환 수단은, 그 액세스 요구된 논리 어드레스를 공개 영역 어드레스로 변환하여 상기 다른 정보 처리 장치에 액세스 요구하고, 상기 다른 정보 처리 장치로부터 되돌아 온 공개 영역 어드레스 상의 데이터를 논리 어드레스로 변환하여 액세스 요구원에 되돌려 보내는 것을 특징으로 하는 정보 처리 장치.

- 제12항에 있어서,상기 공개 영역은, 물리 기억 장치 상의 오퍼레이팅 시스템에서 미사용 공간에 형성되는 것을 특징으로 하는 정보 처리 장치.

- 제12항에 있어서,상기 공개 영역은, 프로세서가 사용하는 메인 메모리 또는 프로세서에 로컬 접속되는 그 밖의 로컬 메모리의 메모리 공간 상에 형성되는 것을 특징으로 하는 정보 처리 장치.

- 제12항에 있어서,상기 공개 영역은, 자 장치에 로컬 접속되는 외부 기억 장치의 기억 공간 상에 형성되는 것을 특징으로 하는 정보 처리 장치.

- 제12항에 있어서,상기 공개 영역은, 자 장치에 로컬 접속되는 각 기기에의 입출력을 할당한 입출력 기억 공간 상에 형성되는 것을 특징으로 하는 정보 처리 장치.

- 네트워크 접속되는 다른 하나 이상의 정보 처리 장치와의 제휴에 의해 가상적으로 1대의 가상 정보 처리 장치의 일부로서 동작하기 위한 정보 처리 방법으로서,물리 기억 공간 상에 다른 정보 처리 장치의 사용을 허가하는 공개 영역이 형성되어 있고,다른 정보 처리 장치에 대하여 공개 영역의 사용을 허가하는 단계와,다른 장치에 사용을 허가하는 공개 영역의 물리 어드레스에 공개 영역 어드레스를 할당하는 단계와,다른 정보 처리 장치로부터 공개 영역에의 액세스 요구가 행해졌을 때, 그 액세스 요구된 공개 영역 어드레스를 물리 어드레스로 변환하는 단계와,상기 물리 기억 공간의 상기 물리 어드레스로부터 추출된 데이터를 공개 영역 어드레스 상의 데이터로서 되돌려 보내는 단계를 포함하는 것을 특징으로 하는 정보 처리 방법.

- 네트워크 접속되는 다른 하나 이상의 정보 처리 장치와의 제휴에 의해 가상 적으로 1대의 가상 정보 처리 장치의 일부로서 동작하기 위한 정보 처리 방법으로서,다른 정보 처리 장치가 물리 기억 공간 상에 공개 영역을 형성하고 있고,다른 정보 처리 장치에 대하여 공개 영역의 사용을 요구하는 단계와,사용 요구가 허가된 것에 응답하여, 사용이 허가된 공개 영역 어드레스에 논리 어드레스를 할당하는 단계와,액세스 요구된 논리 어드레스가 다른 정보 처리 장치로부터 사용이 허가되어 있는 공개 영역일 때, 그 액세스 요구된 논리 어드레스를 공개 영역 어드레스로 변환하여 상기 다른 정보 처리 장치에 액세스 요구하는 단계와,상기 다른 정보 처리 장치로부터 되돌아 온 공개 영역 어드레스 상의 데이터를 논리 어드레스로 변환하여 액세스 요구원에 되돌려 보내는 단계를 포함하는 것을 특징으로 하는 정보 처리 방법.

- 네트워크 접속되는 다른 하나 이상의 정보 처리 장치와의 제휴에 의해 가상적으로 1대의 가상 정보 처리 장치의 일부로서 동작하기 위한 처리를 컴퓨터 시스템 상에서 실행하도록 컴퓨터 판독 가능 형식으로 기술된 컴퓨터 프로그램으로서,물리 기억 공간 상에 다른 정보 처리 장치의 사용을 허가하는 공개 영역이 형성되어 있고,다른 정보 처리 장치에 대하여 공개 영역의 사용을 허가하는 단계와,다른 장치에 사용을 허가하는 공개 영역의 물리 어드레스에 공개 영역 어드 레스를 할당하는 단계와,다른 정보 처리 장치로부터 공개 영역에의 액세스 요구가 행해졌을 때, 그 액세스 요구된 공개 영역 어드레스를 물리 어드레스로 변환하는 단계와,상기 물리 기억 공간의 상기 물리 어드레스로부터 추출된 데이터를 공개 영역 어드레스 상의 데이터로서 되돌려 보내는 단계를 포함하는 것을 특징으로 하는 컴퓨터 프로그램.

- 네트워크 접속되는 다른 하나 이상의 정보 처리 장치와의 제휴에 의해 가상적으로 1대의 가상 정보 처리 장치의 일부로서 동작하기 위한 처리를 컴퓨터 시스템 상에서 실행하도록 컴퓨터 판독 가능 형식으로 기술된 컴퓨터 프로그램으로서,다른 정보 처리 장치가 물리 기억 공간 상에 공개 영역을 형성하고 있고,다른 정보 처리 장치에 대하여 공개 영역의 사용을 요구하는 단계와,사용 요구가 허가된 것에 응답하여, 사용이 허가된 공개 영역 어드레스에 논리 어드레스를 할당하는 단계와,액세스 요구된 논리 어드레스가 다른 정보 처리 장치로부터 사용이 허가되어 있는 공개 영역일 때, 그 액세스 요구된 논리 어드레스를 공개 영역 어드레스로 변환하여 상기 다른 정보 처리 장치에 액세스 요구하는 단계와,상기 다른 정보 처리 장치로부터 되돌아 온 공개 영역 어드레스 상의 데이터를 논리 어드레스로 변환하여 액세스 요구원에 되돌려 보내는 단계를 포함하는 것을 특징으로 하는 컴퓨터 프로그램.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JPJP-P-2004-00050651 | 2004-02-26 | ||

| JP2004050651A JP2005242598A (ja) | 2004-02-26 | 2004-02-26 | 情報処理システム及び情報処理方法、並びにコンピュータ・プログラム |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20060043201A true KR20060043201A (ko) | 2006-05-15 |

Family

ID=34879596

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020050016163A KR20060043201A (ko) | 2004-02-26 | 2005-02-25 | 정보 처리 시스템 및 정보 처리 방법과, 컴퓨터 프로그램 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20050193085A1 (ko) |

| JP (1) | JP2005242598A (ko) |

| KR (1) | KR20060043201A (ko) |

| CN (1) | CN1312592C (ko) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101024549B1 (ko) * | 2009-10-07 | 2011-03-31 | 삼성중공업 주식회사 | 로봇 제어기의 조인트 맵핑 시스템 |

| KR20140143798A (ko) * | 2012-03-19 | 2014-12-17 | 닛본 덴끼 가부시끼가이샤 | 통신 시스템, 제어 장치, 통신 장치 및 정보 중계 방법 |

| US11263148B2 (en) | 2020-02-13 | 2022-03-01 | SK Hynix Inc. | Mapping host logical address to target address that is selected from combination of first memory's physical addresses and second memory's virtual addresses |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100662120B1 (ko) * | 2003-10-20 | 2006-12-27 | 엘지전자 주식회사 | 홈 네트워킹에 의한 가전기기의 메모리 공용방법 |

| US8261341B2 (en) * | 2005-01-27 | 2012-09-04 | Nokia Corporation | UPnP VPN gateway configuration service |

| JP2007148520A (ja) * | 2005-11-24 | 2007-06-14 | Hitachi Ltd | 情報通知方法及び計算機システム |

| JP4402051B2 (ja) | 2006-01-16 | 2010-01-20 | 株式会社ソニー・コンピュータエンタテインメント | データ処理システムおよびデータ処理方法 |

| WO2007129482A1 (ja) * | 2006-04-06 | 2007-11-15 | Sony Corporation | ブリッジ、プロセッサユニット、情報処理装置およびアクセス制御方法 |

| JP4982740B2 (ja) * | 2006-06-21 | 2012-07-25 | 国立大学法人京都大学 | 計算機、組織構築装置、及び計算機の制御方法 |

| JP4978109B2 (ja) * | 2006-08-10 | 2012-07-18 | 富士通株式会社 | ネットワークシステム及び情報処理方法 |

| US20080077650A1 (en) * | 2006-08-29 | 2008-03-27 | Jared Matthew A | Method and apparatus for transferring data between a home networked device and a storage system |

| US7822935B2 (en) * | 2007-05-03 | 2010-10-26 | Sandisk Il Ltd. | Methods for data-smuggling |

| WO2009032710A2 (en) * | 2007-08-29 | 2009-03-12 | Nirvanix, Inc. | Filing system and method for data files stored in a distributed communications network |

| JP5116497B2 (ja) * | 2008-01-31 | 2013-01-09 | 株式会社日立製作所 | 情報処理システム、i/oスイッチ及びi/oパスの交替処理方法 |

| JP2009205189A (ja) * | 2008-02-26 | 2009-09-10 | Buffalo Inc | フォルダ管理方法 |

| US8914829B2 (en) * | 2009-09-14 | 2014-12-16 | At&T Intellectual Property I, Lp | System and method of proactively recording to a digital video recorder for data analysis |

| US8938761B2 (en) * | 2009-09-14 | 2015-01-20 | At&T Intellectual Property I, Lp | System and method of analyzing internet protocol television content credits information |

| JP2011193410A (ja) * | 2010-03-17 | 2011-09-29 | Toshiba Corp | 放送受信装置 |

| CN101957729B (zh) * | 2010-09-27 | 2014-07-02 | 中兴通讯股份有限公司 | 逻辑块变换方法及基于该方法兼容用户读写的方法和装置 |

| KR101748318B1 (ko) * | 2010-11-22 | 2017-06-27 | 삼성전자 주식회사 | 휴대 단말기의 어플리케이션 실행 방법 및 장치 |

| CN102708063B (zh) * | 2012-04-25 | 2016-02-24 | 北京天地云箱科技有限公司 | 磁盘空间管理方法及装置 |

| CN103678428B (zh) * | 2012-09-26 | 2018-08-31 | 联想(北京)有限公司 | 一种文件系统的创建方法及装置 |

| CN103853670A (zh) * | 2012-11-28 | 2014-06-11 | 联想(北京)有限公司 | 一种信息处理方法及电子设备 |

| CN107220503A (zh) * | 2017-05-31 | 2017-09-29 | 上海联影医疗科技有限公司 | 信息处理方法与信息处理系统 |

| WO2020192925A1 (en) * | 2019-03-28 | 2020-10-01 | Huawei Technologies Co., Ltd. | Apparatus for core specific memory mapping |

| CN114466012B (zh) * | 2022-02-07 | 2022-11-25 | 北京百度网讯科技有限公司 | 内容初始化方法、装置、电子设备和存储介质 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5619671A (en) * | 1993-04-19 | 1997-04-08 | International Business Machines Corporation | Method and apparatus for providing token controlled access to protected pages of memory |

| JPH0895928A (ja) * | 1994-09-21 | 1996-04-12 | Kyushu Nippon Denki Software Kk | メモリ共有方式 |

| US5724551A (en) * | 1996-05-23 | 1998-03-03 | International Business Machines Corporation | Method for managing I/O buffers in shared storage by structuring buffer table having entries include storage keys for controlling accesses to the buffers |

| CA2335561A1 (en) * | 2000-05-31 | 2001-11-30 | Frank J. Degilio | Heterogeneous client server method, system and program product for a partitioned processing environment |

| US6526491B2 (en) * | 2001-03-22 | 2003-02-25 | Sony Corporation Entertainment Inc. | Memory protection system and method for computer architecture for broadband networks |

| US7093104B2 (en) * | 2001-03-22 | 2006-08-15 | Sony Computer Entertainment Inc. | Processing modules for computer architecture for broadband networks |

| US6809734B2 (en) * | 2001-03-22 | 2004-10-26 | Sony Computer Entertainment Inc. | Resource dedication system and method for a computer architecture for broadband networks |

| US6826662B2 (en) * | 2001-03-22 | 2004-11-30 | Sony Computer Entertainment Inc. | System and method for data synchronization for a computer architecture for broadband networks |

| US7233998B2 (en) * | 2001-03-22 | 2007-06-19 | Sony Computer Entertainment Inc. | Computer architecture and software cells for broadband networks |

| CN1405679A (zh) * | 2001-04-26 | 2003-03-26 | 德克萨斯仪器股份有限公司 | 多处理器对象控制 |

-

2004

- 2004-02-26 JP JP2004050651A patent/JP2005242598A/ja not_active Abandoned

-

2005

- 2005-02-08 US US11/054,212 patent/US20050193085A1/en not_active Abandoned

- 2005-02-25 KR KR1020050016163A patent/KR20060043201A/ko not_active Application Discontinuation

- 2005-02-28 CN CNB2005100525161A patent/CN1312592C/zh not_active Expired - Fee Related

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101024549B1 (ko) * | 2009-10-07 | 2011-03-31 | 삼성중공업 주식회사 | 로봇 제어기의 조인트 맵핑 시스템 |

| KR20140143798A (ko) * | 2012-03-19 | 2014-12-17 | 닛본 덴끼 가부시끼가이샤 | 통신 시스템, 제어 장치, 통신 장치 및 정보 중계 방법 |

| US9596129B2 (en) | 2012-03-19 | 2017-03-14 | Nec Corporation | Communication system, control apparatus, communication apparatus, information-relaying method, and program |

| US11263148B2 (en) | 2020-02-13 | 2022-03-01 | SK Hynix Inc. | Mapping host logical address to target address that is selected from combination of first memory's physical addresses and second memory's virtual addresses |

Also Published As

| Publication number | Publication date |

|---|---|

| CN1312592C (zh) | 2007-04-25 |

| US20050193085A1 (en) | 2005-09-01 |

| JP2005242598A (ja) | 2005-09-08 |

| CN1661570A (zh) | 2005-08-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20060043201A (ko) | 정보 처리 시스템 및 정보 처리 방법과, 컴퓨터 프로그램 | |

| EP1569114B1 (en) | Network system, distributed processing method and information processing apparatus | |

| WO2005076131A1 (ja) | 情報処理装置、情報処理方法、情報処理システムおよび情報処理用プログラム | |

| KR101096406B1 (ko) | 정보 처리 시스템 및 정보 처리 방법, 및 컴퓨터 프로그램이 기록된 컴퓨터 판독가능한 기록 매체 | |

| JP4599923B2 (ja) | 情報処理システム及び情報処理方法、並びにコンピュータプログラム | |

| KR20070035037A (ko) | 정보 처리 시스템 및 정보 처리 방법과 컴퓨터 프로그램 | |

| KR20060042399A (ko) | 콘텐츠 처리 시스템 및 콘텐츠 처리 방법과, 컴퓨터 프로그램 | |

| KR101119870B1 (ko) | 정보 처리 시스템 및 정보 처리 방법 | |

| KR101089857B1 (ko) | 콘텐츠 재생 장치, 콘텐츠 기록 장치, 네트워크 시스템, 및콘텐츠 기록·재생 방법 | |

| CN100410918C (zh) | 信息处理装置、系统和方法 | |

| JP2005339174A (ja) | 情報処理システム及び情報処理方法、並びにコンピュータプログラム | |

| JP2005252402A (ja) | コンテンツ記録システム及びコンテンツ記録方法、並びにコンピュータ・プログラム | |

| JP2005339401A (ja) | 情報処理装置及びその制御方法、情報処理コントローラ、情報処理ユニット及びその制御方法、並びにコンピュータプログラム | |

| JP4349189B2 (ja) | ネットワークシステム、番組録画予約方法および情報処理装置 | |

| JP2005267150A (ja) | 情報処理システム及び情報処理方法、並びにコンピュータ・プログラム | |

| JP4329647B2 (ja) | 情報処理システム及び情報処理方法、並びにコンピュータプログラム | |

| JP2005252403A (ja) | コンテンツ記録システム及びコンテンツ記録方法、並びにコンピュータ・プログラム | |

| JP2005251163A (ja) | 情報処理装置、情報処理方法、情報処理システムおよび情報処理用プログラム | |

| KR20060071069A (ko) | 정보 처리 장치, 정보 처리 방법, 정보 처리 시스템 및정보 처리용 컴퓨터 프로그램 | |

| JP2005293418A (ja) | 情報処理装置、ネットワークシステム、処理能力呈示方法および処理能力呈示用プログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid |