KR101622311B1 - 적응가능한 수의 오픈 로우들을 갖는 메모리 디바이스 - Google Patents

적응가능한 수의 오픈 로우들을 갖는 메모리 디바이스 Download PDFInfo

- Publication number

- KR101622311B1 KR101622311B1 KR1020157021212A KR20157021212A KR101622311B1 KR 101622311 B1 KR101622311 B1 KR 101622311B1 KR 1020157021212 A KR1020157021212 A KR 1020157021212A KR 20157021212 A KR20157021212 A KR 20157021212A KR 101622311 B1 KR101622311 B1 KR 101622311B1

- Authority

- KR

- South Korea

- Prior art keywords

- row

- rows

- command

- memory

- address

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/18—Address timing or clocking circuits; Address control signal generation or management, e.g. for row address strobe [RAS] or column address strobe [CAS] signals

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0215—Addressing or allocation; Relocation with look ahead addressing means

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/10—Address translation

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

- G06F13/1689—Synchronisation and timing concerns

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/0604—Improving or facilitating administration, e.g. storage management

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0638—Organizing or formatting or addressing of data

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0653—Monitoring storage devices or systems

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0668—Interfaces specially adapted for storage systems adopting a particular infrastructure

- G06F3/0671—In-line storage system

- G06F3/0673—Single storage device

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/408—Address circuits

- G11C11/4082—Address Buffers; level conversion circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4093—Input/output [I/O] data interface arrangements, e.g. data buffers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1015—Read-write modes for single port memories, i.e. having either a random port or a serial port

- G11C7/1039—Read-write modes for single port memories, i.e. having either a random port or a serial port using pipelining techniques, i.e. using latches between functional memory parts, e.g. row/column decoders, I/O buffers, sense amplifiers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/06—Address interface arrangements, e.g. address buffers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/10—Decoders

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0862—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches with prefetch

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/10—Providing a specific technical effect

- G06F2212/1016—Performance improvement

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/60—Details of cache memory

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Human Computer Interaction (AREA)

- Computer Hardware Design (AREA)

- Dram (AREA)

Abstract

메모리 디바이스는 메모리 어레이, 적어도 하나의 로우 어드레스 버퍼, 로우 데이터 버퍼들의 세트, 로우 디코더, 감지 증폭기들의 어레이, 및 디멀티플렉서를 포함한다. 메모리 어레이는 로우들 및 컬럼들로 조직된 데이터 엘리먼트들을 포함한다. 로우들 각각은 로우 어드레스에 의해 어드레스가능하다. 로우들 각각에서의 데이터 엘리먼트들 각각은 컬럼 어드레스에 의해 어드레스가능하다. 적어도 하나의 로우 어드레스 버퍼는 연속적인 선택된 로우 어드레스들의 세트 중 선택된 로우 어드레스를 홀딩한다. 로우 데이터 버퍼들의 세트는 연속적인 선택된 로우 어드레스들의 세트에 대응하는 선택된 로우들의 각각의 콘텐츠들을 홀딩한다. 로우 디코더는 선택된 로우 어드레스를 디코딩하여 선택된 로우에 액세스한다. 감지 증폭기들의 어레이는 선택된 로우를 판독하고 선택된 로우의 콘텐츠를 디멀티플렉서를 통해 로우 데이터 버퍼들 중 하나로 전송하고, 선택된 로우의 콘텐츠를 선택된 로우로 역방향(back)으로 기록한다.

Description

[0001]본 개시된 실시형태들은 메모리 디바이스들의 분야에 관한 것이고, 보다 구체적으로, 적응가능한 수의 오픈 로우들을 가질 수 있는 메모리 디바이스에 관한 것이다.

[0002]SDRAM(Synchronous dynamic random access memory) 디바이스들은 시스템 클록 신호와 같은 외부 클록 신호와 동기식으로 동작하는 다양한 타입들의 DRAM(dynamic random access memory)이다. SDRAM의 입력 및 출력 데이터는 시스템 클록 신호의 활성 에지와 동기화된다. DDR(Double data rate) SDRAM들은 종래의 SDRAM의 동작 속도의 2배를 제공하는 더 고속의 메모리 디바이스들이다. DDR SDRAM들은, 데이터가 시스템 클록 신호의 상승 에지와 하강 에지 둘 모두에서 전달되게 한다. DDR SDRAM들은 통상적으로 멀티코어 시스템에 사용된다.

[0003]SDRAM 또는 DDR SDRAM은 메모리 어레이들의 세트(뱅크들로도 지칭함)를 포함한다. 각각의 메모리 어레이는 로우들 및 컬럼들로 조직되는 데이터 엘리먼트들을 포함한다. 로우 내 데이터 엘리먼트들 각각은 컬럼 어드레스에 의해 어드레스가능하고, 통상적으로 데이터 워드이다. 로우는 또한 페이지로도 지칭된다. 현재, SDRAM 또는 DDR SDRAM에서는, 단지 하나의 로우만이 한번에 오픈될 수 있다. 일단 오프 로우의 콘텐츠가 로우 데이터 버퍼에서 래칭되면, 오픈 로우 내 상이한 컬럼 어드레스들에 대한 후속하는 메모리 요청들이 로우 데이터 버퍼로부터 신속하게 서비스될 수 있다. 이러한 메모리 액세스를 로우 히트(row hit)라 지칭한다. 상이한 로우가 요청되고 상이한 로우가 오픈될 필요가 있다면, 메모리 액세스를 로우 미스(row miss)라 칭한다. 로우 히트들의 경우, 로우 데이터 버퍼만이 사용되고, 메모리 어레이로의 액세스가 필요하지 않게 된다.

[0004]SDRAM들 또는 DDR SDRAM이 통상적으로 멀티코어 시스템에서 사용된다. 멀티코어 시스템은 복수의 프로세서들을 포함한다. 프로세서들은 통상적으로 다양한 메모리 액세스 패턴들로 메모리 액세스를 요청한다. 리퀘스터들의 다양한 메모리 액세스 패턴들로 인해, SDRAM 또는 DDR SDRAM에서의 고정된 로우 사이즈는 SDRAM 또는 DDR SDRAM의 차선의(sub-optimal) 전력 또는 차선의 성능의 원인이 될 수 있다.

[0005]대형의 로우 사이즈를 이용하는 것은 전반적으로 로우 히트들의 수를 증가시킬 수 있지만, 로우의 오픈 시에 전력 소모를 증가시킬 것이다. 소형의 로우 사이즈를 이용하는 것은 로우의 오픈 시에 전력 소모를 감소시킬 수 있지만, 높은 액세스 구역성(locality)으로 인해 리퀘스터들에 대해 더 적은 로우 히트들이 존재하게 될 것이기 때문에 성능이 저하될 수 있다.

[0006]본 발명의 예시적인 실시형태들은 적응가능한 수의 오픈 로우들을 갖는 메모리 디바이스, 이러한 디바이스의 로우들을 오픈하는 방법, 이러한 메모리 디바이스에 액세스하기 위한 메모리 제어기, 및 이러한 메모리 디바이스를 포함하는 시스템에 관한 것이다.

[0007]본 발명의 일 실시형태는 메모리 디바이스이다. 메모리 디바이스는 메모리 어레이, 적어도 하나의 로우 어드레스 버퍼, 로우 데이터 버퍼들의 세트, 로우 디코더, 감지 증폭기들의 어레이, 및 디멀티플렉서를 포함한다. 메모리 어레이는 로우들 및 컬럼들로 조직된 데이터 엘리먼트들을 포함한다. 로우들 각각은 로우 어드레스에 의해 어드레스가능하다. 로우들 내 데이터 엘리먼트들 각각은 컬럼 어드레스에 의해 어드레스가능하다. 적어도 하나의 로우 어드레스 버퍼는 연속적인 선택된 로우 어드레스들의 세트 중 선택된 로우 어드레스를 홀딩하기 위한 것이다. 로우 데이터 버퍼들의 세트는 연속적인 선택된 로우 어드레스들의 세트에 대응하여 선택된 로우들의 각각의 콘텐츠들을 홀딩하기 위한 것이다. 적어도 하나의 로우 어드레스 버퍼에 그리고 메모리 어레이에 결합된 로우 디코더는 선택된 로우 어드레스를 수신하기 위한 것이고 선택된 로우 어드레스를 디코딩하여 메모리 어레이의 선택된 로우에 액세스하기 위한 것이다. 메모리 어레이에 결합되고 로우 데이터 버퍼들의 세트에 결합된 감지 증폭기들의 어레이는 선택된 로우를 판독하고 선택된 로우의 콘텐츠를 로우 데이터 버퍼들 중 하나로 전송하기 위한 것이고 선택된 로우의 콘텐츠를 선택된 로우로 역방향(back)으로 기록하기 위한 것이다. 감지 증폭기들의 어레이와 로우 데이터 버퍼들의 세트에 결합된 디멀티플렉서는 선택된 로우의 콘텐츠를 감지 증폭기들의 어레이로부터 로우 데이터 버퍼들 중 하나로 제공하기 위한 것이다.

[0008]본 발명의 일 실시형태는 메모리 디바이스 내 로우들을 오픈하는 방법이다. 메모리 디바이스는 로우들 및 컬럼들로 조직된 데이터 엘리먼트들을 포함하는 메모리 어레이를 포함하고, 로우들 각각은 로우 어드레스에 의해 어드레스가능하고, 로우들 내 데이터 엘리먼트들 각각은 컬럼 어드레스에 의해 어드레스가능하다. 방법은, (a)로우를 오픈하라는 제 1 커맨드를 수신하는 동작 ―커맨드는 선택된 로우 어드레스를 포함하고 로우 모드 인디케이터는 선택된 로우 어드레스로부터 시작하여 오픈할 로우들의 수를 지정함―; (b)선택된 로우 어드레스를 적어도 하나의 로우 어드레스 버퍼로 로딩하는 동작; (c)로우 디코더를 이용하여 메모리 어레이 내의 선택된 로우에 액세스하기 위해 선택된 로우 어드레스를 디코딩하는 동작; (d)선택된 로우를 판독하고 선택된 로우의 콘텐츠를 감지 증폭기들의 어레이를 이용하여 로우 데이터 버퍼들의 세트의 대응하는 로우 데이터 버퍼로 전송하는 동작; 그리고, 오픈할 로우들의 지정된 수가 2 이상인 경우, (e)상기 선택된 로우 어드레스에 기초하여 연속적인 선택된 로우 어드레스를 계산하는 동작; 및 (f)상기 선택된 로우 어드레스가 연속적인 선택된 로우 어드레스로 대체됨에 따라, 동작들(b), (c), 및 (d)를 반복하는 동작을 포함한다.

[0009]본 발명의 일 실시형태는 메모리 디바이스에 액세스하기 위한 메모리 제어기이다. 메모리 디바이스는 로우들 및 컬럼들로 조직된 데이터 엘리먼트들을 포함하는 메모리 어레이를 포함한다. 로우들 각각은 로우 어드레스에 의해 어드레스가능하다. 로우들 내 데이터 엘리먼트들 각각은 컬럼 어드레스에 의해 어드레스가능하다. 메모리 디바이스는 적응가능한 수의 오픈 로우들을 가질 수 있다. 메모리 제어기는 아비터(arbiter), 메모리 맵퍼, 및 커맨드 생성기를 포함한다. 아비터는, 리퀘스터로부터 메모리 액세스 요청을 수신하고 스케줄링하기 위한 것이다. 메모리 액세스 요청은 로지컬 어드레스를 포함한다. 아비터는 메모리 액세스 요청을 위해 적응가능한 수의 오픈 로우들을 결정하도록 구성된다. 메모리 맵퍼는 로지컬 어드레스를 로우 어드레스와 컬럼 어드레스를 포함하는 물리적 어드레스로 트랜슬레이팅하기 위한 것으로, 아비터에 결합된다. 커맨드 생성기는 메모리 액세스 요청에 대응하는 커맨드들의 시퀀스를 생성하기 위한 그리고 커맨드들의 시퀀스를 메모리 디바이스로 전송하기 위한 것으로, 메모리 맵퍼 및 아비터에 결합된다. 커맨드들의 시퀀스 중 하나의 커맨드는 적응가능한 수의 오픈 로우들을 지정하는 로우 모드 인디케이터를 포함한다.

[0010]본 발명의 일 실시형태는, 적응가능한 수의 오픈 로우들을 가질 수 있는 메모리 디바이스, 메모리 제어기, 및 프로세서를 포함하는 시스템이다. 메모리 디바이스는 로우들 및 컬럼들로 조직된 데이터 엘리먼트들을 포함하는 메모리 어레이를 포함하며, 로우들 각각은 로우 어드레스에 의해 어드레스가능하고, 로우들 내 데이터 엘리먼트들 각각은 컬럼 어드레스에 의해 어드레스가능하다. 메모리 디바이스는 적응가능한 수의 로우들의 콘텐츠들을 홀딩하기 위한 로우 데이터 버퍼들의 세트를 포함한다. 메모리 제어기는 리퀘스터로부터 메모리 액세스 요청들을 수신하도록 구성되고 메모리 디바이스에 액세스하기 위해 메모리 디바이스에 결합된다. 프로세서는 메모리 제어기에 결합된다. 프로세서는 로우 결정 모듈을 실행할 수 있다. 적응가능한 수의 오픈 로우들은 리퀘스터의 메모리 액세스 패턴의 모니터링으로부터 메모리 제어기에 의해 또는 로우 결정 모듈의 실행으로부터 프로세서에 의해 결정된다.

[0011]첨부한 도면들은, 본 발명의 실시예들의 설명을 보조하기 위해 제시되며, 실시예들의 제한이 아니라 오로지 실시예들의 예시를 위해서만 제공된다.

[0012]도 1은 본 발명의 일 실시형태가 실시될 수 있는 시스템을 예시하는 다이어그램이다.

[0013]도 2는 본 발명의 일 실시형태에 따라 구성된 메모리 디바이스의 실시형태를 도시한다.

[0014]도 3은 본 발명의 일 실시형태에 따라 구성된 메모리 디바이스에서 로우들을 오픈하는 프로세스를 도시하는 흐름도이다.

[0015]도 4는 본 발명의 일 실시형태에 따라 구성된 메모리 디바이스의 로우로부터의 판독을 요청하는 커맨드에 응답하는 프로세스롤 도시하는 흐름도이다.

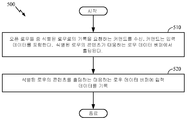

[0016]도 5는 본 발명의 일 실시형태에 따라 구성된 메모리 디바이스의 로우로 기록을 요청하는 커맨드에 응답하는 프로세스를 도시하는 흐름도이다.

[0017]도 6은 본 발명의 일 실시형태에 따라 구성된 메모리 디바이스의 프리차지를 요청하는 커맨드에 응답하는 프로세스를 도시하는 흐름도이다.

[0018]도 7은 도 1에 도시된 메모리 제어기(120)의 실시형태를 도시하는 다이어그램이다.

[0019]도 8은 종래 기술의 SDRAM의 단순화된 상태도를 도시한다.

[0020]도 9는 종래 기술의 통상적인 SDRAM의 동일한 메모리 어레이에서의 2개의 상이한 로우들의 2개의 활성화들의 타이밍도를 도시하는 다이어그램이다.

[0021]도 10은 본 발명의 실시형태에 따라 구성된 SDRAM의 동일한 메모리 어레이에서의 2개의 상이한 로우들의 2개의 활성화들의 타이밍도를 도시하는 다이어그램이다.

[0022]도 11은 본 발명의 실시형태에 따라 구성된 SDRAM의 단순화된 상태도를 도시하는 다이어그램이다.

[0012]도 1은 본 발명의 일 실시형태가 실시될 수 있는 시스템을 예시하는 다이어그램이다.

[0013]도 2는 본 발명의 일 실시형태에 따라 구성된 메모리 디바이스의 실시형태를 도시한다.

[0014]도 3은 본 발명의 일 실시형태에 따라 구성된 메모리 디바이스에서 로우들을 오픈하는 프로세스를 도시하는 흐름도이다.

[0015]도 4는 본 발명의 일 실시형태에 따라 구성된 메모리 디바이스의 로우로부터의 판독을 요청하는 커맨드에 응답하는 프로세스롤 도시하는 흐름도이다.

[0016]도 5는 본 발명의 일 실시형태에 따라 구성된 메모리 디바이스의 로우로 기록을 요청하는 커맨드에 응답하는 프로세스를 도시하는 흐름도이다.

[0017]도 6은 본 발명의 일 실시형태에 따라 구성된 메모리 디바이스의 프리차지를 요청하는 커맨드에 응답하는 프로세스를 도시하는 흐름도이다.

[0018]도 7은 도 1에 도시된 메모리 제어기(120)의 실시형태를 도시하는 다이어그램이다.

[0019]도 8은 종래 기술의 SDRAM의 단순화된 상태도를 도시한다.

[0020]도 9는 종래 기술의 통상적인 SDRAM의 동일한 메모리 어레이에서의 2개의 상이한 로우들의 2개의 활성화들의 타이밍도를 도시하는 다이어그램이다.

[0021]도 10은 본 발명의 실시형태에 따라 구성된 SDRAM의 동일한 메모리 어레이에서의 2개의 상이한 로우들의 2개의 활성화들의 타이밍도를 도시하는 다이어그램이다.

[0022]도 11은 본 발명의 실시형태에 따라 구성된 SDRAM의 단순화된 상태도를 도시하는 다이어그램이다.

[0023]본 발명의 양상들은 하기의 설명에 개시되고 관련 도면들은 본 발명의 특정 실시형태들에 관한 것이다. 대안적인 실시형태들이 본 발명의 범위를 벗어나지 않고 창안될 수 있다. 추가적으로, 본 발명의 잘 알려진 엘리먼트들은, 본 발명의 관련 상세들을 불명료하게 하지 않게 하기 위해서 상세하게 설명되지 않거나 또는 생략될 것이다.

[0024]본 실시형태들의 하나의 개시된 특징은, 흐름도, 흐름 다이어그램, 구조도, 또는 블록 다이어그램으로서 통상적으로 도시되는 프로세스로서 설명될 수 있다. 흐름도는 순차적인 프로세스로서 동작들을 설명할 수 있지만, 동작들 중 많은 것이 병렬로 또는 동시에 수행될 수 있다. 이외에도, 동작들의 순서는 재배열될 수 있다. 프로세스의 동작들이 완료될 경우 프로세스가 종료된다. 프로세스는 방법, 프로그램, 프로시저 등에 대응할 수 있다. 하나의 실시형태가 물리적인 구조를 도시하는 개략도로 설명될 수 있다. 개략도는 기본 개념을 예시하는 것이며 정확한 비율들로 그 구조를 스케일링하거나 도시하지 않을 수 있다는 것을 이해한다.

[0025]본원에 사용된 것으로서, 용어 "에 결합된"은 "와 전기적으로 통신하는"을 의미한다. 이것이 반드시 "와 직접 연결된"을 의미하는 것은 아니다. 함께 결합되는 엘리먼트들은 직접적으로 서로 연결될 수 있거나 또는 하나 또는 그보다 많은 중간 엘리먼트들을 통해 서로 전기 통신을 할 수 있다.

[0026]본 발명의 실시형태들은 적응가능한 수의 오픈 로우들을 갖는 메모리 디바이스, 이러한 디바이스에서 로우들을 오픈하는 방법, 이러한 메모리 디바이스에 액세스하기 위한 메모리 제어기, 및 이러한 메모리 디바이스를 포함하는 시스템에 관한 것이다.

[0027]도 1은 본 발명의 일 실시형태가 실시될 수 있는 시스템(100)을 도시하는 다이어그램이다. 시스템(100)은 중앙 처리 시스템(110), 메모리 제어기(120), 메모리 디바이스(130), 및 복수의 리퀘스터들(140i)(i=1,2,..,n)을 포함한다.

[0028]중앙 처리 시스템(110)은 프로세서(112)를 포함한다. 프로세서(112)는 연관된 캐시 메모리 및 메모리 관리 유닛과 연관되는 프로세서 코어의 형태로 존재할 수 있다. 프로세서(112)는, 하이퍼 스레딩(hyper threading), 보안, 네트워크, 디지털 미디어 기술들을 사용하는 프로세서들, 단일-코어 프로세서들, 멀티-코어 프로세서들, 임베디드(embedded) 프로세서들, 모바일 프로세서들, 마이크로-제어기들, 디지털 신호 프로세서들, 슈퍼스칼라(superscalar) 컴퓨터들, 벡터 프로세서들, SIMD(single instruction multiple data) 컴퓨터들, CISC(complex instruction set computers), RISC(reduced instruction set computers), RISC(reduced instruction set computers), VLIW(very long instruction word) 또는 하이브리드 아키텍처와 같은 임의의 타입의 아키텍처의 중앙 처리 유닛을 나타낸다.

[0029]프로세서(112)는 로우 결정 모듈(116)을 포함할 수 있다. 로우 결정 모듈(116)은 사용 케이스들에 기초하여 메모리 디바이스(130)에서 오픈될 로우들의 적응가능한 수를 계산할 수 있다. 로우 결정 모듈(116)은 하드웨어 모듈 또는 소프트웨어 모듈로서 구현될 수 있다. 일 구현에서, 로우 결정 모듈(116)은, 메모리 제어기(120)를 모니터링하고 메모리 디바이스(130)에서 오프될 로우들의 적응가능한 수를 계산하기 위해 프로세서(112) 상에서 실행되는 소프트웨어 스레드로서 구현된다. 일 구현에서, 프로세서(112)는 오픈될 로우들의 적응가능한 수를 획득하기 위해 로우 결정 모듈(116)을 실행한 다음, 오픈된 로우들의 적응가능한 수를 메모리 제어기(120)로 제공한다.

[0030]중앙 처리 시스템(110)은 버스(150)를 통해, 메모리 제어기(120)와 그리고 리퀘스터들(140i)(i=1, 2, .., n)과 통신할 수 있다.

[0031]리퀘스터들(140i)(i=1, 2, .., n)은, 버스(150)를 통해 메모리 액세스 요청들을 메모리 제어기(120)로 전송할 수 있는 상이한 프로세서들 또는 다른 디바이스들일 수 있다.

[0032]메모리 제어기(120)는 버스(150)를 통해 중앙 처리 시스템(110)과 리퀘스터들(140i)(i=1, 2, .., n)로부터 메모리 액세스 요청들을 수신하고 메모리 버스(125)를 통해 메모리 디바이스(130)에 액세스하도록 구성된다.

[0033]메모리 제어기(120)는 상이한 리퀘스터들(즉, 중앙 처리 시스템(110)과 리퀘스터들(140i)(i=1, 2, .., n)) 사이를 중재하고, 상이한 리퀘스터들을 우선순위화하고, 스케줄링된 방식으로 한 번에 하나씩 리퀘스터들 각각에 대한 서비스를 승인(grant)한다. 메모리 제어기(120)는 각각의 메모리 액세스 요청을 커맨드들의 시퀀스로 트랜슬레이팅하고 커맨드들의 시퀀스를 메모리 디바이스(130)로 전송한다. 커맨드들의 시퀀스 중 하나의 커맨드는 메모리 디바이스(130)에서 로우들의 수를 오픈하라는 요청을 포함한다. 오픈될 로우들의 수는 적응가능하다. 오픈될 수 있는 로우들의 최대 수는 메모리 디바이스(130)의 메모리 어레이 내의 로우 데이터 버퍼들의 수와 동일하다.

[0034]일 실시형태에서, 메모리 제어기(120)는, 서비스되는 리퀘스터의 메모리 액세스 패턴을 모니터링함으로써 오픈될 로우들의 적응가능한 수를 결정한다. 서비스되는 리퀘스터는 중앙 처리 시스템(110) 또는 리퀘스터들(140i)(i=1, 2, .., n) 중 하나일 수 있다. 서비스되는 리퀘스터의 메모리 액세스 패턴으로부터 메모리 액세스 구역성이 결정될 수 있다. 메모리 액세스 구역성은, 특정 메모리 위치가 특정 시각에 요청되는 경우, 근처 메모리 위치들이 바로 뒤에 요청될 가능성이 높다는 개념을 지칭한다.

[0035]오픈될 로우들의 적응가능한 수는, 서비스되는 리퀘스터의 메모리 액세스 패턴을 모니터링하는 메모리 제어기(120)에 의해 또는 로우 결정 모듈을 실행하는 프로세서(112)에 의해 결정된다.

[0036]메모리 디바이스(130)는 메모리 어레이들의 세트(뱅크들로도 지칭됨)를 포함한다. 각각의 메모리 어레이는 로우들 및 컬럼들로 조직되는 데이터 엘리먼트들을 포함한다. 로우들 각각은 로우 어드레스에 의해 어드레스가능하다. 로우 내 데이터 엘리먼트들 각각은 컬럼 어드레스에 의해 어드레스가능하다. 메모리 디바이스(130)는 메모리 어레이 내의 적응가능한 수의 오픈 로우들을 가질 수 있다. 메모리 디바이스(130)는 적응가능한 수의 오픈 로우들의 콘텐츠들을 홀딩하기 위한 로우 데이터 버퍼들의 세트를 포함한다.

[0037]메모리 디바이스(130)는 SDRAM(synchronous dynamic random access memory), DDR SDRAM(double data rate synchronous dynamic random access memory) 또는 임의의 다른 타입의 DRAM(dynamic random access memory)일 수 있다.

[0038]적응가능한 수의 오픈 로우들을 갖는 메모리 디바이스(130)의 특징은 적응가능한 페이지 사이즈를 갖는 특징으로 여겨질 수 있으며, 오픈 페이지는, 종래 기술에서와 같이 하나의 오픈 로우만을 포함하는 것이 아닌 적응가능한 수의 오픈 로우들을 포함할 수 있다.

[0039]도 2는 본 발명의 일 실시형태에 따라 구성된 메모리 디바이스의 실시형태(200)를 도시한다. 시스템(200)은 메모리 어레이들의 세트를 포함하며, 각각의 메모리 어레이는 대응하는 주변 회로들을 갖는다. 명료성을 위해서, 도 2는 하나의 메모리 어레이(260)만을 지닌 시스템(200)을 예시한다. 시스템(200)은 제어 회로(210), 로우 어드레스 버퍼들의 세트(230), 멀티플렉서(240), 로우 디코더(250), 메모리 어레이(260), 감지 증폭기들의 어레이(270), 디멀티플렉서(275), 로우 데이터 버퍼들의 세트(280), 및 컬럼 디코더(290)를 포함한다.

[0040]제어 회로(210)는 제어 로직(212) 및 어드레싱 회로(220)를 포함한다.

[0041]제어 로직(212)은 제어 신호들(202)을 입력들로 수신하도록 구성된다. 제어 신호들(202)는 커맨드를 포함한다. 제어 로직(212)은 커맨드를 디코딩하고 시스템(200)의 나머지 회로소자를 구동하도록 구성된다. 일 구현에서, 제어 신호들(202)은 시스템 클록(CK) 신호, 클록 인에이블(CKE) 신호, 로우 어드레스 스트로브(RAS) 신호, 컬럼 어드레스 스트로브(CAS) 신호, 기록 인에이블(WE) 신호, 및 칩 셀렉트(CS) 신호를 포함한다. CK 및 CKE 신호들은 외부 시스템 클록과 메모리 디바이스(200)의 동작을 동기화하는 데에 사용된다. RAS, CAS, WE, 및 CS의 별개의 조합들은 제어 로직(212)에 의해 수신된 별개의 커맨드들을 정의한다. 커맨드가 메모리 어레이(260) 내의 지정된 로우를 오픈하기 위한 활성화 커맨드인 경우, 제어 신호들(202)은 또한 로우 모드 인디케이터를 제어 로직(212)의 메모리 모드 레지스터(214)로 로딩하는 로드 모드 레지스터 커맨드를 포함할 수 있다. 로우 모드 인디케이터는 오픈될 로우들의 수를 지정하기 위해 사용된다.

[0042]어드레싱 회로(220)가 제어 로직(212)에 결합된다. 어드레싱 회로(220)는 제어 로직(212)으로부터 디코딩된 제어 신호들을 수신한다. 어드레싱 회로(220)는 어드레스 신호들(204)을 입력들로서 수신한다. 어드레스 신호들(204)은 커맨드의 어드레스 부분을 제공한다. 어드레싱 회로(220)는 활성화 커맨드를 지닌 어드레스 신호들(204)로부터 로우 어드레스를 수신한다. 어드레싱 회로(220)는 수신된 로우 어드레스를 로우 어드레스 버퍼들의 세트(230) 내 제 1 버퍼(RAB0)로 제공한다. 메모리 모드 레지스터(214) 내 로우 모드 인디케이터가, 오픈될 로우들의 수가 M이라는 것을 나타내는 경우(예를 들어, M은 4와 같음), 어드레싱 회로(220)는 수신된 로우 어드레스로부터 M-1개의 연속하는 로우 어드레스들을 계산하고 M-1개의 연속 로우 어드레스들을 각각, 로우 데이터 버퍼들의 세트(230)의 나머지 로우 어드레스 버퍼들(RAB1, RAB2, RAB3)로 제공한다. 어드레싱 회로(220)는 단순 증분을 이용함으로써 수신된 로우 어드레스로부터 M-1개의 연속하는 로우 어드레스들을 계산한다. 본 실시형태에서, 로우 어드레스 버퍼들의 세트(230) 내 로우 어드레스 버퍼들의 수가 로우 데이터 버퍼들의 세트(280) 내 로우 데이터 버퍼들의 수와 동일하다는 것을 주목한다. 로우 데이터 버퍼들의 세트(280) 내에 N개의 로우 데이터 버퍼들이 존재하는 경우, M이 N과 동일하거나 N보다 작다면, 로우 모드 인디케이터는 오픈될 M개의 로우들을 지정할 수 있다. 어드레싱 회로(220)는 판독 또는 기록 커맨드를 지닌 어드레스 신호들(204)로부터 컬럼 어드레스를 수신한다. 어드레싱 회로(220)는 수신된 컬럼 어드레스를 컬럼 디코더(290)로 제공한다.

[0043]일 실시형태에서, 연속적인 로우 어드레스들을 한번에 하나씩 홀딩하도록 구성되는 하나의 레지스터를 이용함으로써 로우 어드레스 버퍼들(230)의 세트가 구현된다. 어드레싱 회로(220)는 수신된 로우 어드레스로부터 연속적인 로우 어드레스들을 동적으로 계산한다. 로우 데이터 버퍼들의 세트(280)는, 로우들이 메모리 어레이(260)로부터 한 번에 하나씩 판독됨에 따라, 연속적인 로우 어드레스들에 각각 대응하는 로우들의 콘텐츠들을 홀딩하도록 구성된다. 본 실시형태에서, 로우 데이터 버퍼들의 세트(280) 내에 N개의 로우 데이터 버퍼들이 존재하는 경우, M이 N과 동일하거나 N보다 작다면, 로우 모드 인디케이터는 오픈될 M개의 로우들을 지정할 수 있다. 로우 어드레스 버퍼들(230)를 구현하기 위해 하나의 레지스터가 사용되는 본 실시형태에서는, 멀티플렉서(240)가 필요없다.

[0044]도 2의 구현에서, 로우 어드레스 버퍼들(230)의 세트가 2 이상의 로우 어드레스 버퍼를 포함하는 경우, 멀티플렉서(240)는 로우 어드레스 버퍼들의 세트(230)에 결합되고 로우 디코더(250)에 결합되어 로우 어드레스 버퍼들(230) 중 선택된 버퍼에서 홀딩되는 로우 어드레스를 선택하고 선택된 로우 어드레스를 로우 디코더(250)로 제공한다.

[0045]로우 디코더(250)는 메모리 어레이(260)에 결합된다. 로우 디코더(250)는 선택된 로우 어드레스를 멀티플렉서(240)로부터 (또는 로우 데이터 버퍼들(230)을 구현하기 위해 하나의 레지스터가 사용되는 실시형태에서 하나의 레지스터로부터) 수신하고 선택된 로우 어드레스에 대응하는 선택된 로우에 액세스한다.

[0046]메모리 어레이(260)는 조직된 데이터 엘리먼트들을 로우들과 컬럼들에 포함시킨다. 로우들 각각은 로우 어드레스에 의해 어드레스가능하다. 로우 내 데이터 엘리먼트들 각각은 컬럼 어드레스에 의해 어드레스가능하다.

[0047]감지 증폭기들(270)의 어레이가 메모리 어레이(260)에 결합되고 디멀티플렉서(275)를 통해 로우 데이터 버퍼들의 세트(280)에 결합된다. 감지 증폭기들(270)의 어레이는 선택된 로우를 판독하고 선택된 로우의 콘텐츠를 로우 데이터 버퍼들(280) 중 하나로 전송한다. 프리차지 커맨드가 제어 회로(210)에 의해 수신되는 경우, 감지 증폭기들(270)의 어레이는 또한, 선택된 로우의 콘텐츠를 메모리 어레이(260) 내의 선택된 로우로 역방향으로 기록하기 위해 사용된다. 제어 회로(210)에 의해 프리차지 커맨드가 수신되는 경우, 로우 데이터 버퍼들(280) 내의 콘텐츠가, 감지 증폭기들(270)의 어레이를 이용하여, 메모리 어레이(260) 내의 오픈 로우들에 하나씩 역방향으로 기록된다.

[0048]상술된 바와 같이 프리차지 커맨드가 수신되는 경우, 로우 데이터 버퍼들(280) 내의 콘텐츠들을 이용하여 오픈 로우들 모두를 하나씩 역방향으로 기록하는 대신, 일 실시형태에서, 감지 증폭기들(270)의 어레이는, 선택된 로우의 콘텐츠를 로우 데이터 버퍼들(280) 중 하나로 전송하는 것이 완료될 때 선택된 로우의 콘텐츠를 선택된 로우로 역방향으로 기록하도록 구성된다.

[0049]디멀티플렉서(275)는 감지 증폭기들(270)의 어레이와 로우 데이터 버퍼들의 세트(280)에 결합된다. 디멀티플렉서(275)는 선택된 로우의 콘텐츠를 감지 증폭기들의 어레이로부터 로우 데이터 버퍼들(280) 중 하나에 제공한다. 선택된 로우의 콘텐츠를 수신하는 로우 데이터 버퍼들(280) 중 하나가, 선택된 로우 어드레스를 홀딩하는 로우 어드레스 버퍼들(230) 중 하나에 대응한다.

[0050]로우 데이터 버퍼들의 세트(280)는 로우 어드레스 버퍼들의 세트(230)에 해당한다. 로우 데이터 버퍼들의 세트(280) 내 각각의 로우 데이터 버퍼는 로우 어드레스 버퍼들의 세트(230) 내의 대응하는 로우 어드레스 버퍼에서 홀딩되는 선택된 로우 어드레스에 대응하는 선택된 로우의 콘텐츠를 홀딩하기 위해 사용된다. 로우 데이터 버퍼들의 세트(280)는 로우 어드레스 버퍼들(230)에서 홀딩되는 연속적인 선택된 로우 어드레스들의 세트에 대응하는 선택된 로우들의 각각의 콘텐츠들을 홀딩하기 위해 사용된다. 로우 데이터 버퍼들의 세트(280)가 시스템(200)에 대한 입력/출력 버퍼들로서 사용된다. 일 실시형태에서, 로우 데이터 버퍼들의 세트(280)는 도 2에 도시된 바와 같이 4개의 로우 데이터 버퍼들을 포함한다. 다른 실시형태에서, 로우 데이터 버퍼들의 세트(280)는 2개의 로우 데이터 버퍼들을 포함한다. 로우 데이터 버퍼들(280)은 플립-플롭들 또는 펄스 래치들, 또는 다른 저장 구조물들을 이용하여 구현될 수 있다.

[0051]판독 커맨드 또는 기록 커맨드에 따라, 어드레싱 회로(220)는 어드레스 신호들(204)로부터 컬럼 어드레스를 수신한다. 판독 커맨드는 수신 컬럼 어드레스에서 오픈 로우들 중 지정된 로우로부터의 판독을 요청한다. 기록 커맨드는 수신 컬럼 어드레스에서 오픈 로우들 중 지정된 로우로의 기록을 요청한다. 오픈 로우들 중 지정된 로우는 로우 데이터 버퍼들(280)의 로우 데이터 버퍼에 대응한다. 어드레싱 회로(220)는 수신된 컬럼 어드레스를 컬럼 디코더(290)로 제공한다. 컬럼 디코더(290)는, 오픈 로우들 중 지정된 로우에 대응하는 컨텐츠를 홀딩하는 로우 데이터 버퍼에 액세스하고 컬럼 어드레스에 대응하는 콘텐츠 내의 위치에 액세스한다. 이후, 그 위치에서 로우 데이터 버퍼의 콘텐츠에 대한 판독 또는 기록이 이루어진다. 판독 요청은, 데이터를 로우 데이터 버퍼로부터 입/출력 포트(295)로 전송함으로써 서비스된다. 기록 요청의 경우, 입/출력 포트(295)로부터 인입하는 데이터가 로우 데이터 버퍼들(280) 중 하나에 기록된다.

[0052]프리차지 커맨드가, 활성화 커맨드에 후속하여 제어 회로(210)에 의해 수신되는 경우, 대응하는 로우 데이터 버퍼들의 콘텐츠들 및 감지 증폭기들의 어레이를 이용하여 메모리 어레이 내의 오픈 로우들로 한 번에 하나씩 역방향으로 기록함으로써 그리고 메모리 어레이 내의 오픈 로우들을 클로징함으로써 프리차지 커맨드가 서비스된다. 오픈 로우들의 어드레스들이 로우 어드레스 버퍼들의 세트(230)로부터 획득된다. 로우 어드레스 버퍼들의 세트를 구현하기 위해서 하나의 레지스터만이 사용되는 실시형태에서, 오픈 로우들의 어드레스들이 쉽게 리컴퓨팅될 수 있다.

[0053]도 3은, 본 발명의 일 실시형태들에 따라 구성된 메모리 디바이스에서 로우들을 오픈하는 프로세스(300)를 도시하는 흐름도이다. 메모리 디바이스는 로우들과 컬럼들로 조직된 데이터 엘리먼트들을 포함하는 메모리 어레이를 포함하며, 로우들 각각은 로우 어드레스에 의해 어드레스가능하고, 로우의 데이터 엘리먼트들 각각은 컬럼 어드레스에 의해 어드레스가능하다.

[0054]시작 시, 프로세스(300)는 로우를 오픈하라는 제 1 커맨드를 수신한다(블록 302). 커맨드는 선택된 로우 어드레스와 로우 모드 인디케이터를 포함한다. 로우 모드 인디케이터는, 선택된 로우 어드레스로부터 시작하여 오픈할 로우들의 수를 지정한다. 프로세스(300)는 선택된 로우 어드레스를 적어도 하나의 로우 어드레스 버퍼로 로딩한다(블록 304). 이후, 프로세스(300)는, 로우 디코더를 이용하여, 메모리 어레이 내의 선택된 로우에 액세스하기 위해서 선택된 로우 어드레스를 디코딩한다(블록 306). 프로세스(300)는 선택된 로우를 판독하고, 감지 증폭기들의 어레이를 이용하여 선택된 로우의 콘텐츠를 로우 데이터 버퍼들의 세트의 대응하는 로우 데이터 버퍼로 전송한다(블록 308). 오픈할 로우들의 지정된 수가 1 이하인 경우, 프로세스(300)가 종료된다. 오픈할 로우들의 지정된 수가 2 이상인 경우, 프로세스(300)는 선택된 로우 어드레스에 기초하여 연속적인 선택된 로우 어드레스를 계산하고(블록 310), 선택된 로우 어드레스가 연속적인 선택된 로우 어드레스로 대체됨에 따라 블록(304, 306 및 308)의 동작들을 반복한다(블록 312). 오픈할 로우들의 지정된 수가 N과 같은 경우(N은 3 이상의 수임), 프로세스(300)는, 메모리 어레이로부터 판독된 지정된 N개의 로우들의 콘텐츠들이 로우 데이터 버퍼들의 세트의 대응하는 로우 데이터 버퍼들에서 홀딩될 때까지 블록(310) 및 블록(312)의 동작들을 반복한다(블록 314). 이후, 프로세스(300)가 종료된다.

[0055]도 4는 본 발명의 일 실시형태에 따라 구성된 메모리 디바이스의 로우로부터 판독을 요청하는 커맨드에 응답하는 프로세스(400)를 도시하는 흐름도이다. 판독 커맨드는 활성화 커맨드에 후속한다.

시작 시, 프로세스(400)는 오픈된 지정된 수의 로우들 중 식별된 로우로부터의 판독을 요청하는 커맨드를 수신한다(블록 410). 식별된 로우의 콘텐츠는 로우 데이터 버퍼들의 세트의 대응하는 로우 데이터 버퍼에서 홀딩된다. 프로세스(400)는 커맨드에 응답하여 대응하는 로우 데이터 버퍼로부터 판독한다(블록 420). 이후, 프로세스(400)가 종료된다.

[0056]도 5는 본 발명의 일 실시형태에 따라 구성된 메모리 디바이스의 로우로의 기록을 요청하는 커맨드에 응답하는 프로세스(500)를 도시하는 흐름도이다. 기록 커맨드는 활성화 커맨드에 후속한다.

[0057]시작 시, 프로세스(500)는 오픈 로우들의 식별된 로우로의 기록을 요청하는 커맨드를 수신한다(블록 510). 커맨드는 입력 데이터를 포함한다. 식별된 로우의 콘텐츠가 대응하는 로우 데이터 버퍼에서 홀딩된다. 프로세스(500)는 식별된 로우의 콘텐츠를 홀딩하는 대응하는 로우 데이터 버퍼에 입력 데이터를 기록한다(블록 520). 이후, 프로세스(500)가 종료된다.

[0058]도 6은 본 발명의 일 실시형태에 따라 구성된 메모리 디바이스에서의 프리차지를 요청하는 커맨드에 응답하는 프로세스(600)를 도시하는 흐름도이다. 프리차지 커맨드가 활성화 커맨드에 후속한다.

[0059]시작 시, 프로세스(600)는 프리차지를 요청하는 커맨드를 수신한다(블록 610). 프로세스(600)는 대응하는 로우 데이터 버퍼들의 콘텐츠들과 감지 증폭기들의 어레이를 이용하여 한 번에 하나씩 메모리 어레이 내 오픈 로우들에 역방향으로 기록한다(블록 620). 오픈 로우들의 로우 어드레스들이 로우 어드레스 버퍼들의 세트에서 홀딩된다. 이후, 프로세스(600)는 메모리 어레이의 오픈 로우들을 클로즈한다(블록 630). 이후, 프로세스(600)가 종료된다.

[0060]도 7은 도 1에 도시된 메모리 제어기(120)의 실시형태(700)를 예시하는 다이어그램이다. 시스템(700)은 아비터(710), 메모리 맵퍼(720), 및 커맨드 생성기(730)를 포함한다.

[0061]아비터(710)는 복수의 리퀘스터들로부터 메모리 액세스 요청들을 수신하도록 구성된다. 아비터(710)는 한 번에 하나의 리퀘스터를 서비스하도록 리퀘스터들 사이를 중재하도록 구성된다. 아비터(710)는 질서 정연하게 서비스에 대한 메모리 액세스 요청들을 스케줄링한다. 리퀘스터로부터의 메모리 액세스 요청은 데이터 엘리먼트의 로지컬 어드레스를 포함한다. 아비터(710)는 또한, 메모리 액세스 요청이 서비스되기 위해 메모리 어레이에서 오픈될 로우들의 수를 결정하도록 구성된다.

[0062]본 발명의 일 실시형태에서, 아비터(710)는 중앙 처리 시스템(110)에 포함된 프로세서(112)로부터 수신된 명령에 따라 메모리 어레이에서 오픈될 로우들의 수를 결정한다. 프로세서(112)로부터의 명령은 메모리 어레이에서 오픈될 로우들의 수를 지정한다. 중앙 처리 시스템(110)의 프로세서(112)는 프로세서(112)에 포함된 로우 결정 모듈(116)을 실행할 수 있다. 실행된 로우 결정 모듈(116)은 시스템(700)을 모니터링함으로써 획득된 사용 케이스들에 기초하여 메모리 어레이(260)에서 오픈될 로우들의 수를 결정한다.

[0063]본 발명의 다른 실시형태에서, 아비터(710)는 서비스되는 리퀘스터의 메모리 액세스 패턴을 모니터링함으로써 메모리 어레이에서 오픈될 로우들의 수를 결정한다. 아비터(710)는 메모리 액세스 구역성을 측정하기 위해 리퀘스터의 메모리 사용 패턴을 모니터링한다. 일 실시형태에서, 아비터(710)는, 로우 미스 대 로우 히트의 비를 모니터링함으로써 리퀘스터의 메모리 액세스 패턴을 모니터링하고, 로우 미스 대 로우 히트의 비가 임계치를 초과하는 경우 오픈될 로우들의 수가 2 이상의 로우인지를 결정하도록 구성된다. 다른 실시형태들에서, 리퀘스터의 메모리 액세스 패턴을 모니터링하고 오픈될 로우들의 수를 결정하는 동작들이 메모리 제어기(120)에 포함된 다른 모듈에 의해 수행될 수 있다.

[0064]오픈 로우의 콘텐츠가 로우 데이터 버퍼에서 (또는 다수의 오픈 로우들의 경우, 오픈 로우들의 콘텐츠가 로우 데이터 버퍼들에서) 래칭되면, 오픈 로우(또는 오픈 로우들) 내 상이한 컬럼 어드레스들에 대한 후속하는 메모리 요청들이 로우 데이터 버퍼(또는 로우 데이터 버퍼들)로부터 신속하게 서비스될 수 있다. 이러한 메모리 액세스를 로우 히트라 칭한다. 상이한 로우가 요청되고 로우 데이터 버퍼(또는 로우 데이터 버퍼들)의 콘텐츠(또는 콘텐츠들)가 변경될 필요가 있다면, 메모리 액세스를 로우 미스라 칭한다. 로우 히트들의 경우, 로우 데이터 버퍼들(280)만이 사용되고 메모리 어레이(260)로의 액세스는 필요하지 않다.

[0065]메모리 맵퍼(720)는 아비터(710)에 결합된다. 메모리 맵퍼(720)는, 데이터 엘리먼트의 로지컬 어드레스를 로우 어드레스와 컬럼 어드레스를 포함하는 물리 어드레스로 트랜슬레이트하도록 구성된다.

[0066]커맨드 생성기(730)는 메모리 맵퍼(720) 및 아비터(710)에 결합된다. 커맨드 생성기(730)는 메모리 액세스 요청에 대응하는 커맨드들의 시퀀스를 생성하고 커맨드들의 시퀀스를 메모리 디바이스(130)로 전송하도록 구성된다. 커맨드들의 시퀀스 중 하나의 커맨드는 오픈될 로우들의 수를 지정하는 로우 모드 인디케이터를 포함한다. 예를 들어, 로드 모드 레지스터 커맨드는, 로우 모드 인디케이터를 메모리 디바이스(130)의 메모리 모드 레지스터로 로딩하기 위해 메모리 디바이스(130)로 전송된다.

[0067]종래 기술의 통상적인 SDARM에서, 메모리 어레이 단위로 하나의 로우만이 오픈될 수 있다. 로우는, 메모리 제어기의 소위 "오픈 페이지" 정책 하에서 오픈 상태를 유지한다. 새로운 로우가 동일한 메모리 어레이에서 오픈될 것이 요청되는 경우, SDRAM은 현재 오픈된 로우를 클로즈하고, 새로운 로우를 활성화시키는데, 긴 레이턴시 패널티를 초래한다. 통상적인 SDRAM의 동작들에서 수반되는 다양한 커맨드들 및 시간 지연들이 아래에 설명된다.

[0068]도 8은 종래 기술의 SDRAM의 단순화된 상태도를 도시한다. SDRAM은 다양한 상태들을 갖는 단순한 상태 머신으로 설명될 수 있다. 명료함을 위해서, 도 8은 단지 다음 상태들: 유휴, 활성, 판독, 자동-프리차지와 함께 판독(Reading with Auto-precharge), 기록, 자동-프리차지와 함께 기록(Writing with Auto-precharge), 및 프리자치를 도시한다. 다른 상태들은 생략한다. 명료함을 위해서, 상태도는 단지 하나의 메모리 어레이에 대하여 설명될 것이다. 일 상태에서 다른 상태로의 천이는 커맨드에 의해 트리거되고, 상태 머신이 다른 커맨드에 응답할 준비가 되기 전에 최소 지연 시간을 요구한다. 상태도에서, 상태 천이가 화살표로 도시되고, 상태 천이를 위한 커맨드 시퀀스의 트리거링은 화살표 가까이에 나타내어진다. 상태도에서, 가는 폭을 가진 화살표는 커맨드 시퀀스에 의해 트리거링된 상태 천이를 나타내는 반면, 두꺼운 폭을 갖는 화살표는 자동 시퀀스에 의해 트리거링된 상태 천이를 나타낸다.

[0069]초기화 시퀀스가 수행된 후 또는 리프레시 동작 이후, SDRAM이 유휴 상태에 있다. 유휴 상태에서, 메모리 어레이가 프리차지된다.

[0070]SDRAM이 판독 또는 기록 커맨드에 응답하도록 준비되기 전에, 메모리 어레이 내의 로우가 반드시 먼저 오픈, 즉 활성화된다. 메모리 어레이 내의 로우를 활성화시키기 위해서, 메모리 제어기는 액세스될 메모리 어레이와 로우를 지정하는 활성화(ACT) 커맨드를 전송한다. 활성화 커맨드에 응답하여, 상태 머신은 유휴 상태로부터 활성 상태로 이동한다. 로우를 활성화시키기 위해서 요구되는 시간은 로우-컬럼 지연으로 지칭되고, 또한 로우 컬럼 지연 또는 로우 커맨드 투 컬럼 커맨드 지연으로도 지칭되고, 심볼 tRCD로 표기된다. 이 가변 tRCD는, SDRAM의 제어 회로의 커맨드 인터페이스에서 활성화 커맨드를 래칭하고, 제어 회로를 프로그래밍하고, 메모리 어레이 내의 지정된 로우로부터 감지 증폭기들의 어레이로 데이터 콘텐츠를 판독하고 로우의 콘텐츠 내의 지정된 컬럼 어드레스로 액세스하기 위한 준비로 데이터 콘텐츠를 로우 데이터 버퍼로 래칭하는데 필요한 최소 시간을 나타낸다.

[0071]지정된 로우가 활성화된 후, 감지 증폭기들의 어레이 및 로우 데이터 버퍼는 지정된 로우의 콘텐츠를 포함한다. 지정된 로우로부터 감지 증폭기들의 어레이로의 이러한 판독은 지정된 로우에 대해 파괴적이다(destructive). 이때, 액세스될 시작 컬럼 어드레스를 지정하는 판독(RD) 또는 기록(WD) 커맨드가 이슈될 수 있다. 판독(RD) 커맨드에 응답하여, 상태 머신이 활성 상태로부터 판독 상태로 천이한다. 기록(WR) 커맨드에 응답하여, 상태 머신이 활성 상태로부터 기록 상태로 천이한다. 오픈 로우로부터, 지정된 컬럼 어드레스에서 데이터를 판독하는 시기를 컬럼 어드레스 스트로브(CAS) 레이턴시로 지칭하고, 심볼 tCAS로 표기된다. 변수 tCAS는, SDRAM의 제어 회로의 커맨드 인터페이스에서 커맨드를 래칭하고, 제어 회로를 프로그래밍하고, 요청된 데이터를 로우 데이터 버퍼로부터 게이팅하고 데이터를 메모리 버스에 위치시키는데 필요한 최소 시간을 나타낸다.

[0072]종래 기술의 SDRAM에서, 메모리 어레이 단위로 하나의 로우만이 한번에 오픈될 수 있다. 동일한 메모리 어레이 내의 다른 로우로의 액세스는, 오픈 로우가 먼저 클로즈될 것을 요구한다. 로우가 오픈인 상태로 남아있는 한, 메모리 제어기는 다른 판독(RD) 커맨드들을 동일한 오픈 로우로 이슈할 수 있고, 상태 머신이 판독 상태를 유지한다. 유사하게, 로우가 오픈인 상태로 남아있는 한, 메모리 제어기는 다른 기록(WR) 커맨드들을 동일한 오픈 로우로 이슈할 수 있고, 상태 머신은 기록 상태를 유지한다. 새로운 판독 또는 기록 커맨드 없이 특정 시간 인터벌이 경과되는 경우, 상태 머신은 자동으로 활성 상태로 복귀한다. 오픈 로우가 더 이상 필요하지 않을 경우 또는 메모리 어레이 내의 다른 로우가 오픈될 필요가 없는 경우, 메모리 제어기는 프리차지(PR) 커맨드를 이슈하여 오픈 로우를 클로즈한다. 프리차지(PR) 커맨드에 응답하여, 상태 머신이 활성 상태로부터 프리차징 상태로 천이하고 이후 유휴 상태로 천이한다. 다른 로우를 오픈하기 위해서, 상술된 바와 같이, 메모리 제어기는 다른 활성화(ACT) 커맨드를 이슈하고, 상태 머신이 유휴 상태로부터 활성 상태로 이동한다.

[0073]자동-프리차지와 함께 판독(RDA) 커맨드 또는 자동-프리차지와 함께 기록(WRA) 커맨드는 메모리 제어기에 의해 전송될 수 있다. 이는, SDRAM의 제어 회로로 하여금 특정 조건들을 만족하자마자 오픈 로우를 자동으로 클로즈하게 할 것이며, 이러한 특정 조건들은:(1)활성화 커맨드가 이슈되었기 때문에, 최소의 뱅크 활성화 시간(RAS 활성화 시간으로도 지칭됨, tRAS로 표기됨)이 경과하였음, (2)가장 최근의 판독 커맨드가 이슈되었기 때문에 최소의 판독-투-프리차지(Read to Precharge Delay) 지연(tRTP로 표기됨)이 경과하였음이다. 자동-프리차지와 함께 판독(RDA) 커맨드에 응답하여, 상태 머신은, 프리차지와 함께 판독 상태로 먼저 이동한 후 프리차징 상태로, 이후 유휴 상태로 이동한다. 자동-프리차지와 함께 기록(WRA) 커맨드에 응답하여, 상태 머신이 자동프리차지와 함께 기록 상태로 먼저 이동한 후 프리차징 상태로, 이후 유휴 상태로 이동한다.

[0074]프리차징은, 감지 증폭기들 내의 어레이의 저장된 차지를 데이터 엘리먼트들의 오픈 로우로 역방향으로 전송하기 위해서 SDRAM의 감지 증폭기들의 데이터 라인들 및 어레이를 준비한다. 프리차징은 데이터 엘리먼트들의 다음 로우를 오픈하기 위해 SDRAM 코어를 준비시킨다. 오픈 로우를 프리차지하는 시간이 로우 액세스 스트로브 프리차지 지연으로 지칭되고, 또한 뱅크 프리차지 지연으로 지칭되고, 심볼 tRP로 표기된다. 동일한 메모리 어레이로의 연속 활성화 커맨드들 간의 최소 시간 간격이 메모리 디바이스의 로우 사이클 시간으로 지칭되고 심볼 tRC로 표기된다. 로우 사이클 시간(tRC)은 뱅크 활성화 시간(tRAS) 및 뱅크 프리차지 지연(tRP)의 합계와 동일하다. SDRAM의 2개의 상이한 메모리 어레이들로의 2개의 활성화 명령들 사이의 최소 시간 간격이 판독-투-판독 지연으로 지칭되고, 심볼 tRRD로 표기된다. 상술된 시간 인터벌들 모두(지연들로도 지칭함)가 클록 사이클들로 표현된다. 요청된 시간 지연들을 만족시키기 위해서, 동작시키지 않음(No Operation)(Nop로 표기됨)을 요청하는 커맨드들이 다른 커맨드들 사이에서 메모리 제어기에 의해 전송된다.

[0075]도 9는 종래 기술의 통상적인 SDRAM의 동일한 메모리 어레이 내의 2개의 상이한 로우들의 2개의 활성화들의 타이밍도를 도시하는 다이어그램이다.

[0076]도 9를 참조하면, 제 1 라인은, 시간 축이 왼쪽에서 오른쪽으로 진행하는, 메모리 제어기로부터 수신된 클록 신호 CK와 그의 컴플리멘타리 클록 신호 CK#을 도시한다. 도 9의 제 2 라인은, 도 9의 제 3 라인 상에 나타내어진 커맨드들과 연관된 어드레스 신호들을 도시한다. 어드레스 신호들 및 커맨드들이 메모리 제어기로부터 수신된다. 도 9에 도시되는, 로우-컬럼 지연(tRCD로 표기됨), 판독-투-판독 지연(tRRD로 표기됨), 뱅크 활성화 시간(tRAS로 표기됨), 뱅크 프리차지 지연(tRP로 표기됨), 및 로우 사이클 시간(tRC로 표기됨)은 도 8의 설명에서 설명된 바와 같다.

[0077]도 9를 참조하면, 제 2 활성화 커맨드 다음에 오는 제 2 판독 커맨드는 도 9에 도시되지 않는다. 제 1 판독 커맨드와 유사하게, 동일한 로우-컬럼 지연(tRCD) 후에 이슈된 제 2 판독 커맨드는 제 2 활성화 커맨드로부터 경과되엇다. 이와 같이, 제 1 판독 동작의 완료부터 제 2 판독 커맨드의 시작까지 카운팅하면, 발생된 레이턴시는 뱅크 프리차지 지연(tRP)과 로우-컬럼 지연(tRCD)의 합과 같다.

[0078]도 10은 본 발명의 실시형태에 따라 구성된 SDRAM의 동일한 메모리 어레이 내의 2개의 상이한 로우들의 2개의 활성화들의 타이밍도를 도시하는 다이어그램이다. 활성화 커맨드가 메모리 제어기(120)로부터 수신된 후, 2개 이상의 로우가 지정된 로우 어드레스로부터 시작하여 오픈 상태일 수 있고, 오픈 로우들이 더이상 필요하지 않을 때까지 또는 현재 오픈 상태에 있지 않은 로우를 활성화시키기 위한 커맨드가 수신될 때까지 오픈 상태로 머물러 있게 된다. 오픈될 로우들의 수는 적응가능하고 메모리 제어기(120)에 의해 결정된다. 오픈 로우들 중에 존재하는 새로운 로우에 액세싱할 경우, 현재 오픈 상태에 있는 로우를 클로즈할 필요가 없고(즉, 메모리 어레이를 프리차지할 필요가 없음) 새로운 로우를 활성화시킬 필요가 없다. 도 10은 이러한 상황을 도시한다. 도 10은, 이미 오픈 상태에 있는 로우들 중에 존재하는 새로운 로우에 대한 판독 커맨드가 중간 프리차지 커맨드와 새로운 활성화 커맨드를 필요로 하지 않고 사전 판독 동작의 완료 시 이슈될 수 있다는 것을 도시한다. 이와 같이, 제 1 판독에 후속하여, 제 2 판독이 이미 오픈 상태에 있는 로우들 중에 존재하는 상이한 로우에 대해 이루어지는 상황에서, 도 9에 도시되어 그 타이밍도가 도시되어 있는 종래 기술의 SDRAM과는 달리, 종래 기술의 SDRAM의 제 2 판독과 연관되는 뱅크 프리차지 지연(tRP) 및 로우-컬럼 지연(tRCD)으로 인한 레이턴시는 존재하지 않는다.

[0079]도 11은 본 발명의 실시형태에 따라 구성된 SDRAM의 단순화된 상태도를 도시하는 다이어그램이다. 본 발명의 실시형태에 따라 구성된 SDRAM은 다양한 상태들을 갖는 단순 상태 머신으로서 기술될 수 있다. 명료성을 위해서, 도 11은 단지 다음 상태들: 유휴, 활성, 판독, 멀티-로우 판독, 멀티-로우 기록, 자동-프리차지와 함께 판독, 기록, 자동-프리차지와 함께 기록, 및 프리차징만을 나타낸다. 다른 상태들은 생략된다. 명료성을 위해서, 상태도가 하나의 메모리 어레이에 대해서만 설명될 것이다. 일 상태로부터 다른 상태로의 천이는 커맨드에 의해 트리거링되고, 상태 머신이 다른 커맨드에 응답할 준비가 되기 전에 최소 지연 시간을 요구한다. 도 11의 상태도에서, 상태 천이가 화살표로 도시되고, 상태 천이를 위한 트리거링 커맨드는 화살표 부근에 나타내어진다. 상태도에서, 가는 폭을 가진 화살표는 커맨드 시퀀스에 의해 트리거링된 상태 천이를 나타내는 반면, 두꺼운 폭을 갖는 화살표는 자동 시퀀스에 의해 트리거링된 상태 천이를 나타낸다. 도 11의 상태도는, 멀티-로우 판독 상태 및 멀티-로우 기록 상태의 추가로 인해 도 8의 상태도와 상이하다.

[0080]초기화 시퀀스가 수행된 후 또는 리프레시 동작 이후, SDRAM은 유휴 상태에 있게 된다. 유휴 상태에서, 메모리 어레이가 프리차지된다.

[0081]SDRAM의 로우를 오픈하기 위해서, 메모리 제어기는 메모리 어레이와 액세싱될 로우의 어드레스를 지정하는 활성화(ACT) 커맨드를 전송한다. 활성화 커맨드는 또한, 오픈될 연속하는 로우들의 수를 지정하기 위한 로우 모드 인디케이터를 포함한다. 활성화 커맨드에 응답하여, 상태 머신은 유휴 상태로부터 활성 상태로 이동한다.

[0082]로우 모드 인디케이터가, 하나의 로우만이 오픈될 것을 지정하는 경우, 지정된 로우 어드레스에 따른 로우만이 활성화될 것이다. 지정된 로우가 활성화된 후, 감지 증폭기들의 어레이 및 로우 데이터 버퍼는 지정된 로우의 콘텐츠를 포함한다. 지정된 로우로부터 감지 증폭기들의 어레이로의 이러한 판독은 지정된 로우에 대해 파괴적이다. 이때에, 액세스될 시작 컬럼 어드레스를 지정하는 판독(RD) 또는 기록(WR) 커맨드가 이슈될 수 있다. 판독(RD) 커맨드에 응답하여, 상태 머신은 활성 상태로부터 판독 상태로 천이한다. 기록(WR) 커맨드에 응답하여, 상태 머신은 활성 상태로부터 기록 상태로 천이한다. 지정된 로우가 오픈인 상태로 있는 한, 메모리 제어기는 다른 판독(RD) 커맨드들을 동일한 오픈 로우로 이슈할 수 있고, 상태 머신이 판독 상태를 유지한다. 유사하게, 지정된 로우가 오픈 상태로 남아있는 한, 메모리 제어기는 다른 기록(WR) 커맨드들을 동일한 오픈 로우로 이슈할 수 있고, 상태 머신이 기록 상태를 유지한다. 새로운 판독 또는 기록 커맨드 없이 특정 시간 간격이 경과되는 경우, 상태 머신은 활성 상태로 자동으로 복귀한다.

[00083]로우 모드 인디케이터가 오픈할 N개의 로우들을 지정하는 경우(여기서, N은 2 이상이고 SDRAM의 로우 데이터 버퍼들의 총 수보다 작거나 같다), 지정된 로우 및 N-1개의 연속적인 로우들이 한 번에 하나씩 활성화된다. N개의 로우 각각이 활성화됨에 따라, 활성화되는 로우의 콘텐츠는 메모리 어레이 내의 로우로부터 감지 증폭기들의 어레이로 판독된 후 N개의 대응하는 로우 데이터 버퍼들 중 하나로 판독된다. 판독(RD) 커맨드에 응답하여, 상태 머신은 활성 상태로부터 멀티-로우 판독 상태로 천이한다. 기록(WR) 커맨드에 응답하여 상태 머신은 활성 상태로부터 멀티-로우 기록 상태로 천이한다.

[0084]N개의 로우들이 오픈인 상태로 남아있는 한, 메모리 제어기는 N개의 오픈 로우들의 임의의 로우에 다른 판독(RD) 커맨드들을 이슈할 수 있고, 상태 머신은 멀티-로우 판독 상태를 유지한다. 유사하게, N개의 로우들이 오픈 상태로 남아있는 한, 메모리 제어기는 N개의 오픈 로우들 중 임의의 로우에 다른 기록(WD) 커맨드들을 이슈할 수 있고, 상태 머신은 멀티-로우 판독 상태를 유지한다. 새로운 판독 또는 기록 커맨드 없이 특정 시간 간격이 경과하는 경우, 상태 머신은 활성 상태로 자동으로 복귀한다. N개의 오픈 로우들이 더이상 필요하지 않은 경우 또는 메모리 어레이의 오픈되지 않은 로우가 오픈될 필요가 있는 경우, 메모리 제어기는 N개의 오픈 로우들을 클로즈하는 프리차지(PR) 커맨드를 이슈한다. 프리차지(PR) 커맨드에 응답하여, 상태 머신이 활성 상태로부터 프리차징 상태로 천이한 후 유휴 상태로 천이한다. 다른 로우를 오픈하기 위해서, 상술된 바와 같이, 메모리 제어기는 다른 활성화(ACT) 커맨드를 이슈하고, 상태 머신이 유휴 상태로부터 활성 상태로 이동한다.

[0085]자동-프리차지와 함께 판독(RDA) 커맨드 또는 자동-프리차지와 함께 기록(WRA) 커맨드는 메모리 제어기에 의해 전송될 수 있다. 이는, SDRAM의 제어 회로로 하여금 특정 조건들을 만족하자마자 오픈 로우를 자동으로 한번에 하나씩 클로즈하게 할 것이며, 이러한 특정 조건들은:(1)활성화 커맨드가 이슈되었기 때문에, 최소의 뱅크 활성화 시간(RAS 활성화 시간으로도 지칭됨, tRAS로 표기됨)이 경과하였음, (2)가장 최근의 판독 커맨드가 이슈되었기 때문에 최소의 판독-투-프리차지 지연(Read to Precharge Delay)(tRTP로 표기됨)이 경과하였다는 것이다. 자동-프리차지와 함께 판독(RDA) 커맨드에 응답하여, 상태 머신이 프리차지와 함께 판독 상태로 먼저 이동한 후 프리차징 상태로 이후 유휴 상태로 이동한다. 자동-프리차지와 함께 기록(WRA) 커맨드에 응답하여, 상태 머신이 자동-프리차지와 함께 기록 상태로 먼저 이동한 후 프리차징 상태로 이후 유휴 상태로 이동한다.

[0086]단어 "예시적인"은 "예, 예시 또는 예증으로서 기능하는 것"을 의미하도록 본 명세서에서 사용된다. "예시적인" 것으로서 본 명세서에서 설명된 임의의 실시형태는 다른 실시예들에 비해 반드시 바람직하거나 유리한 것으로서 해석될 필요는 없다. 유사하게, 용어 "본 발명의 실시형태들"은, 본 발명의 모든 실시형태들이 설명된 특성, 이점 또는 동작 모드를 포함하는 것을 요구하지는 않는다.

[0087]본원에 사용된 용어는 특정 실시형태들만을 설명하기 위한 것이며, 본 발명의 실시형태들을 제한하려고 의도하지 않는다. 본원에 사용된 것으로서, 단수 형태("a", "an" 및 "the")는, 문맥상 달리 명확하게 표시하지 않으면, 복수 형태들을 또한 포함하도록 의도된다. 본 명세서에서 사용되는 경우, 용어들 "구비하는", "구비", "포함하는", 및/또는 "포함"이 언급된 특성들, 정수들, 단계들, 동작들, 엘리먼트들, 및/또는 컴포넌트들의 존재를 특정하지만, 하나 또는 그보다 많은 다른 특성들, 정수들, 단계들, 동작들, 엘리먼트들, 컴포넌트들, 및/또는 그들의 그룹들의 존재 또는 부가를 배제하지는 않음을 추가적으로 이해할 것이다.

[0088]추가적으로, 특정한 실시형태들은, 예를 들어, 컴퓨팅 디바이스의 엘리먼트들에 의해 수행될 동작들의 시퀀스들의 관점들에서 설명된다. 본 명세서에 설명된 다양한 동작들이, 특정한 회로들(예를 들어, 주문형 집적 회로(ASIC)들)에 의해, 하나 또는 그보다 많은 프로세서들에 의해 실행되는 프로그램 명령들에 의해, 또는 그 둘의 결합에 의해 수행될 수 있음을 인식할 것이다. 따라서, 본 발명의 다양한 양상들은 다수의 상이한 형태들로 구현될 수도 있으며, 이들 모두는 청구된 청구항들의 범위 내에 있는 것으로 고려된다. 부가적으로, 본 명세서에 설명된 실시예들의 각각에 대해, 임의의 그러한 실시예들의 대응하는 형태는, 예를 들어, 설명된 동작을 수행"하도록 구성된 로직"으로서 본 명세서에서 설명될 수 있다.

[0089]추가적으로 실시형태 전부 또는 일부가 특정 특징들, 기능들에 따른 애플리케이션들에 따라 다양한 수단에 의해 구현될 수 있다. 이러한 수단은 하드웨어, 소프트웨어, 펌웨어, 또는 이들의 임의의 조합을 포함할 수 있다.

[0090]당업자들은, 정보 및 신호들이 다양한 상이한 기술들 및 기법들 중 임의의 기술 및 기법을 사용하여 표현될 수도 있음을 인식할 것이다. 예를 들어, 상기 설명 전반에 걸쳐 언급될 수도 있는 데이터, 명령들, 커맨드들, 정보, 신호들, 비트들, 심볼들, 및 칩들은 전압들, 전류들, 전자기파들, 자기장들 또는 자기 입자들, 광학 필드들, 입자들 또는 이들의 임의의 결합에 의해 표현될 수 있다.

[0091]추가적으로, 당업자들은, 여기에 기재된 실시형태들과 관련하여 설명된 다양한 예시적인 로지컬 블록들, 모듈들, 회로들, 및 알고리즘 단계들이 전자 하드웨어, 컴퓨터 소프트웨어, 또는 이 둘의 결합들로서 구현될 수도 있음을 인식할 것이다. 하드웨어와 소프트웨어의 이러한 상호교환가능성을 명확히 예시하기 위해, 다양한 예시적인 컴포넌트들, 블록들, 모듈들, 회로들, 및 단계들이 그들의 기능의 관점들에서 일반적으로 설명된다. 당업자가 인식할 바와 같이, 그러한 기능이 하드웨어로서 구현될지 또는 소프트웨어로서 구현될지는, 특정한 애플리케이션 및 전체 시스템에 부과된 설계 제약들에 의존한다. 당업자들은 설명된 기능을 각각의 특정한 애플리케이션에 대해 다양한 방식들로 구현할 수도 있지만, 그러한 구현 결정들이 본 발명의 범위를 벗어나게 하는 것으로서 해석되지는 않아야 한다.

[0092]그에 따라, 본 발명은 예시된 실시예들로 제한되지 않고 본원에 설명된 기능을 수행하기 위한 임의의 수단이 본 발명의 실시형태들에 포함된다.

[0093]전술한 본 발명이 본 발명의 예시적인 실시예들을 도시하지만, 첨부된 청구항들에 의해 정의된 바와 같은 본 발명의 범위를 벗어나지 않으면서 다양한 변화들 및 변경들이 행해질 수 있음을 주목해야 한다. 본 명세서에 설명된 본 발명의 실시예들에 따른 방법 청구항들의 기능들, 단계들 및/또는 동작들은 임의의 특정한 순서로 수행될 필요는 없다. 또한, 본 발명의 엘리먼트들이 단수로 설명 또는 청구될 수도 있지만, 단수로의 제한이 명시적으로 언급되지 않으면, 복수가 고려된다.

Claims (20)

- 메모리 디바이스로서,

로우들 및 컬럼들로 조직된 데이터 엘리먼트들을 포함하는 메모리 어레이 ―상기 로우들 각각은 로우 어드레스에 의해 어드레스가능하고, 각각의 상기 로우들 내 데이터 엘리먼트들 각각은 컬럼 어드레스에 의해 어드레스가능함―;

연속적인 선택된 로우 어드레스들의 세트 중 선택된 로우 어드레스를 홀딩하기 위한 적어도 하나의 로우 어드레스 버퍼;

상기 연속적인 선택된 로우 어드레스들의 세트에 대응하는, 선택된 로우들의 각각의 콘텐츠들을 홀딩하기 위한 로우 데이터 버퍼들의 세트;

상기 선택된 로우 어드레스를 수신하기 위한 그리고 상기 선택된 로우 어드레스를 디코딩하여 상기 메모리 어레이의 선택된 로우에 액세스하기 위한, 상기 적어도 하나의 로우 어드레스 버퍼에 그리고 상기 메모리 어레이에 결합된 로우 디코더;

상기 선택된 로우를 판독하고 상기 선택된 로우의 콘텐츠를 상기 로우 데이터 버퍼들 중 하나로 전송하기 위한 그리고 상기 선택된 로우의 콘텐츠를 상기 선택된 로우로 역방향(back)으로 기록하기 위한, 상기 메모리 어레이에 결합되고 상기 로우 데이터 버퍼들의 세트에 결합된 감지 증폭기들의 어레이;

상기 선택된 로우의 상기 콘텐츠를 상기 감지 증폭기들의 어레이로부터 상기 로우 데이터 버퍼들 중 하나로 제공하기 위한, 상기 감지 증폭기들의 어레이와 상기 로우 데이터 버퍼들의 세트에 결합된 디멀티플렉서; 및

제 1 커맨드를 수신하고 디코딩하기 위한 제어 회로를 포함하고,

상기 제 1 커맨드는 지정된 로우 어드레스 및 로우 모드 인디케이터를 포함하고, 상기 로우 모드 인디케이터는 오픈될 로우들의 수를 지정하고, 상기 제어 회로는 상기 로우 모드 인디케이터를 홀딩하기 위한 메모리 모드 레지스터를 포함하는,

메모리 디바이스. - 제 1 항에 있어서,

상기 적어도 하나의 로우 어드레스 버퍼는 상기 연속적인 선택된 로우 어드레스들을 한번에 하나씩 홀딩하도록 구성된 하나의 레지스터이고, 상기 연속적인 선택된 로우 어드레스들은 상기 연속적인 선택된 로우 어드레스들 중 첫번째로부터 동적으로 계산되고, 상기 로우 데이터 버퍼들의 세트는 상기 연속적인 선택된 로우 어드레스들에 각각 대응하는 로우들의 콘텐츠를 홀딩하도록 구성되는, 메모리 디바이스. - 제 1 항에 있어서,

상기 적어도 하나의 로우 어드레스 버퍼는 상기 연속적인 선택된 로우 어드레스들의 세트를 각각 홀딩하도록 구성된 로우 어드레스 버퍼들의 세트이고, 상기 로우 어드레스 버퍼들의 세트는 상기 로우 데이터 버퍼들의 세트에 대응하고,

상기 메모리 디바이스는,

상기 로우 어드레스 버퍼들 중 선택된 버퍼에서 홀딩되는 로우 어드레스를 선택하기 위한 그리고 상기 선택된 로우 어드레스를 상기 로우 디코더로 제공하기 위한, 상기 로우 어드레스 버퍼들의 세트에 결합되고 상기 로우 디코더에 결합된 멀티플렉서를 더 포함하는,

메모리 디바이스. - 제 1 항에 있어서,

상기 감지 증폭기들의 어레이는, 상기 선택된 로우의 콘텐츠를 상기 로우 데이터 버퍼들 중 하나로 전송하는 것이 완료될 때 상기 선택된 로우의 상기 콘텐츠를 상기 선택된 로우로 역방향으로(back) 기록하도록 구성되는, 메모리 디바이스. - 삭제

- 제 1 항에 있어서,

상기 제어 회로는 상기 지정된 로우 어드레스로부터 시작하여 지정된 수의 로우들을 오픈할 것을 상기 메모리 어레이에 명령하도록 구성되고, 오픈된 지정된 수의 로우들의 콘텐츠는, 홀딩을 위해 대응하는 로우 데이터 버퍼들로 이송되는, 메모리 디바이스. - 제 6 항에 있어서,

상기 제어 회로는 상기 제 1 커맨드에 후속하여 제 2 커맨드를 수신하도록 구성되고, 상기 제 2 커맨드는 상기 오픈된 지정된 수의 로우들 중 식별된 로우로부터의 판독을 요청하고, 그리고 상기 식별된 로우의 상기 판독은 대응하는 로우 데이터 버퍼로부터의 판독에 의해 수행되는, 메모리 디바이스. - 제 6 항에 있어서,

상기 제어 회로는 상기 제 1 커맨드에 후속하여 제 3 커맨드를 수신하도록 구성되고, 상기 제 3 커맨드는 상기 오픈된 지정된 수의 로우들 중 식별된 로우로의 기록을 요청하고, 상기 식별된 로우의 콘텐츠는 대응하는 로우 데이터 버퍼에서 홀딩되고, 그리고 상기 기록은 상기 대응하는 로우 데이터 버퍼에 기록함으로써 수행되는, 메모리 디바이스. - 제 6 항에 있어서,

상기 제어 회로는 상기 제 1 커맨드에 후속하여 제 4 커맨드를 수신하도록 구성되고, 상기 제 4 커맨드는 프리차지를 요청하고, 상기 프리차지는 상기 대응하는 로우 데이터 버퍼들 및 상기 감지 증폭기들의 어레이의 콘텐츠들을 이용하여 상기 메모리 어레이 내의 상기 오픈된 지정된 수의 로우들로 한 번에 하나씩 역방향으로 기록함으로써 그리고 상기 오픈된 지정된 수의 로우들을 클로징함으로써 수행되는, 메모리 디바이스. - 제 1 항에 있어서,

상기 로우 데이터 버퍼들의 세트는 4개의 로우 데이터 버퍼들을 포함하는, 메모리 디바이스. - 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/736,662 | 2013-01-08 | ||

| US13/736,662 US9281036B2 (en) | 2013-01-08 | 2013-01-08 | Memory device having an adaptable number of open rows |

| PCT/US2014/010544 WO2014110050A1 (en) | 2013-01-08 | 2014-01-07 | Memory device having an adaptable number of open rows |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20150104169A KR20150104169A (ko) | 2015-09-14 |

| KR101622311B1 true KR101622311B1 (ko) | 2016-05-18 |

Family

ID=50030495

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020157021212A KR101622311B1 (ko) | 2013-01-08 | 2014-01-07 | 적응가능한 수의 오픈 로우들을 갖는 메모리 디바이스 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US9281036B2 (ko) |

| EP (1) | EP2943956B1 (ko) |

| JP (1) | JP5956089B2 (ko) |

| KR (1) | KR101622311B1 (ko) |

| CN (1) | CN104903962B (ko) |

| WO (1) | WO2014110050A1 (ko) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9281036B2 (en) | 2013-01-08 | 2016-03-08 | Qualcomm Incorporated | Memory device having an adaptable number of open rows |

| KR102106064B1 (ko) * | 2013-07-11 | 2020-05-28 | 에스케이하이닉스 주식회사 | 반도체 장치 및 이의 제어 방법 |

| CN110059020B (zh) | 2015-04-23 | 2024-01-30 | 华为技术有限公司 | 扩展内存的访问方法、设备以及系统 |

| US10082964B2 (en) * | 2016-04-27 | 2018-09-25 | Micron Technology, Inc | Data caching for ferroelectric memory |

| CN108139994B (zh) * | 2016-05-28 | 2020-03-20 | 华为技术有限公司 | 内存访问方法及内存控制器 |

| CN108139992B (zh) * | 2016-08-09 | 2020-06-16 | 华为技术有限公司 | 访问存储设备的方法和存储设备 |

| GB2553338B (en) * | 2016-09-02 | 2019-11-20 | Advanced Risc Mach Ltd | Serial communication control |

| WO2021030750A1 (en) | 2019-08-14 | 2021-02-18 | Supermem, Inc. | Computing memory systems |

| WO2022132475A1 (en) * | 2020-12-17 | 2022-06-23 | Micron Technology, Inc. | Memory activation timing management |

| US11704049B2 (en) * | 2021-02-11 | 2023-07-18 | Micron Technology, Inc. | Optimized command sequences |

| US11568932B2 (en) * | 2021-02-22 | 2023-01-31 | Micron Technology, Inc. | Read cache for reset read disturb mitigation |

| US11775197B2 (en) * | 2021-03-25 | 2023-10-03 | Kyocera Document Solutions Inc. | Single command for reading then clearing dynamic random access memory |

| US11600312B1 (en) * | 2021-08-16 | 2023-03-07 | Micron Technology, Inc. | Activate commands for memory preparation |

| CN117608498A (zh) * | 2024-01-22 | 2024-02-27 | 北京象帝先计算技术有限公司 | 一种dram的访问处理方法、缓存控制模块及dram控制器 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6061759A (en) | 1996-02-09 | 2000-05-09 | Apex Semiconductor, Inc. | Hidden precharge pseudo cache DRAM |

| US6389514B1 (en) | 1999-03-25 | 2002-05-14 | Hewlett-Packard Company | Method and computer system for speculatively closing pages in memory |

| US20080282028A1 (en) | 2007-05-09 | 2008-11-13 | International Business Machines Corporation | Dynamic optimization of dynamic random access memory (dram) controller page policy |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0700050A3 (en) * | 1994-08-17 | 1997-07-23 | Oak Technology Inc | Multi-page storage |

| GB2293668B (en) * | 1994-09-30 | 1999-09-29 | Advanced Risc Mach Ltd | Accessing data memories |

| JP3248500B2 (ja) * | 1998-11-12 | 2002-01-21 | 日本電気株式会社 | 半導体記憶装置およびそのデータ読み出し方法 |

| JP3930195B2 (ja) * | 1999-04-09 | 2007-06-13 | 株式会社ルネサステクノロジ | データ処理システム |

| US6625685B1 (en) | 2000-09-20 | 2003-09-23 | Broadcom Corporation | Memory controller with programmable configuration |

| JP2003108438A (ja) * | 2001-09-28 | 2003-04-11 | Supreme Magic:Kk | データ処理装置 |

| US7007133B2 (en) | 2002-05-29 | 2006-02-28 | Micron Technology, Inc. | Synchronous memory open page register |

| US7082514B2 (en) * | 2003-09-18 | 2006-07-25 | International Business Machines Corporation | Method and memory controller for adaptive row management within a memory subsystem |

| US7433258B2 (en) | 2003-10-10 | 2008-10-07 | Datasecure Llc. | Posted precharge and multiple open-page RAM architecture |

| KR20050035699A (ko) * | 2003-10-14 | 2005-04-19 | 삼성전자주식회사 | 메모리 시스템의 에너지 절감 방법 및 장치 |

| US7162567B2 (en) | 2004-05-14 | 2007-01-09 | Micron Technology, Inc. | Memory hub and method for memory sequencing |

| US7389402B2 (en) | 2005-06-07 | 2008-06-17 | Advanced Micro Devices, Inc. | Microprocessor including a configurable translation lookaside buffer |

| GB2441726B (en) | 2005-06-24 | 2010-08-11 | Metaram Inc | An integrated memory core and memory interface circuit |

| US7917676B2 (en) | 2006-03-10 | 2011-03-29 | Qualcomm, Incorporated | Efficient execution of memory barrier bus commands with order constrained memory accesses |

| US7606988B2 (en) | 2007-01-29 | 2009-10-20 | International Business Machines Corporation | Systems and methods for providing a dynamic memory bank page policy |

| US7958301B2 (en) | 2007-04-10 | 2011-06-07 | Marvell World Trade Ltd. | Memory controller and method for memory pages with dynamically configurable bits per cell |

| US8184487B2 (en) * | 2010-08-30 | 2012-05-22 | Micron Technology, Inc. | Modified read operation for non-volatile memory |

| WO2012116369A2 (en) | 2011-02-25 | 2012-08-30 | Fusion-Io, Inc. | Apparatus, system, and method for managing contents of a cache |

| US9281036B2 (en) * | 2013-01-08 | 2016-03-08 | Qualcomm Incorporated | Memory device having an adaptable number of open rows |

-

2013

- 2013-01-08 US US13/736,662 patent/US9281036B2/en active Active

-

2014

- 2014-01-07 WO PCT/US2014/010544 patent/WO2014110050A1/en active Application Filing

- 2014-01-07 CN CN201480004103.3A patent/CN104903962B/zh active Active

- 2014-01-07 EP EP14702117.4A patent/EP2943956B1/en not_active Not-in-force

- 2014-01-07 JP JP2015551843A patent/JP5956089B2/ja not_active Expired - Fee Related

- 2014-01-07 KR KR1020157021212A patent/KR101622311B1/ko not_active IP Right Cessation

-

2016

- 2016-01-05 US US14/988,079 patent/US9343127B1/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6061759A (en) | 1996-02-09 | 2000-05-09 | Apex Semiconductor, Inc. | Hidden precharge pseudo cache DRAM |

| US6389514B1 (en) | 1999-03-25 | 2002-05-14 | Hewlett-Packard Company | Method and computer system for speculatively closing pages in memory |

| US20080282028A1 (en) | 2007-05-09 | 2008-11-13 | International Business Machines Corporation | Dynamic optimization of dynamic random access memory (dram) controller page policy |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2943956A1 (en) | 2015-11-18 |

| CN104903962A (zh) | 2015-09-09 |

| JP2016506009A (ja) | 2016-02-25 |

| WO2014110050A1 (en) | 2014-07-17 |

| EP2943956B1 (en) | 2018-10-03 |

| US20140195764A1 (en) | 2014-07-10 |

| US9343127B1 (en) | 2016-05-17 |

| JP5956089B2 (ja) | 2016-07-20 |

| CN104903962B (zh) | 2017-08-25 |

| US20160133306A1 (en) | 2016-05-12 |

| KR20150104169A (ko) | 2015-09-14 |

| US9281036B2 (en) | 2016-03-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101622311B1 (ko) | 적응가능한 수의 오픈 로우들을 갖는 메모리 디바이스 | |

| JP6761873B2 (ja) | セルフリフレッシュステートマシンmopアレイ | |

| US9293188B2 (en) | Memory and memory controller for high reliability operation and method | |

| US5889714A (en) | Adaptive precharge management for synchronous DRAM | |

| KR101554294B1 (ko) | 추론적 프리챠지의 검출 | |

| US20210073152A1 (en) | Dynamic page state aware scheduling of read/write burst transactions | |

| CN102207916B (zh) | 一种基于指令预取的多核共享存储器控制设备 | |

| JP4786209B2 (ja) | メモリアクセス装置 | |

| US6963516B2 (en) | Dynamic optimization of latency and bandwidth on DRAM interfaces | |

| KR20190022428A (ko) | 고속 메모리 인터페이스들을 위한 명령 중재 | |

| JP7384806B2 (ja) | 連動メモリデバイスに対するメモリ要求のスケジューリング | |

| CN112088368A (zh) | 动态的每存储体和全存储体刷新 | |

| EP3055863A1 (en) | Data processor with memory controller for high reliability operation and method | |

| US20200401321A1 (en) | Speculative hint-triggered activation of pages in memory | |

| US10572168B2 (en) | DRAM bank activation management | |

| JP2019522257A (ja) | 低電力メモリのスロットリング | |

| US7373453B2 (en) | Method and apparatus of interleaving memory bank in multi-layer bus system | |

| US8914612B2 (en) | Data processing with time-based memory access | |

| JP2023530642A (ja) | Dramコマンドストリーク管理 | |

| CN113946435A (zh) | 内存管理技术及计算机系统 | |

| CN112965816B (zh) | 内存管理技术及计算机系统 | |

| US11526278B2 (en) | Adaptive page close prediction |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| LAPS | Lapse due to unpaid annual fee |