KR101503541B1 - 디지털 신호 처리 시스템 및 방법 - Google Patents

디지털 신호 처리 시스템 및 방법 Download PDFInfo

- Publication number

- KR101503541B1 KR101503541B1 KR1020097013533A KR20097013533A KR101503541B1 KR 101503541 B1 KR101503541 B1 KR 101503541B1 KR 1020097013533 A KR1020097013533 A KR 1020097013533A KR 20097013533 A KR20097013533 A KR 20097013533A KR 101503541 B1 KR101503541 B1 KR 101503541B1

- Authority

- KR

- South Korea

- Prior art keywords

- filter

- signal

- shelf

- low

- shelf filter

- Prior art date

Links

- 238000000034 method Methods 0.000 title claims abstract description 36

- 238000012545 processing Methods 0.000 title claims abstract description 28

- 230000005236 sound signal Effects 0.000 claims abstract description 27

- 230000008569 process Effects 0.000 claims abstract description 14

- 238000003672 processing method Methods 0.000 claims description 38

- 238000001914 filtration Methods 0.000 claims description 7

- 230000006870 function Effects 0.000 description 44

- 230000004044 response Effects 0.000 description 25

- 238000010586 diagram Methods 0.000 description 11

- 238000012546 transfer Methods 0.000 description 10

- 239000011800 void material Substances 0.000 description 10

- 230000000694 effects Effects 0.000 description 8

- 238000003491 array Methods 0.000 description 7

- 230000003068 static effect Effects 0.000 description 7

- 230000009467 reduction Effects 0.000 description 6

- 230000008859 change Effects 0.000 description 5

- 238000005070 sampling Methods 0.000 description 5

- 230000007704 transition Effects 0.000 description 5

- 230000003321 amplification Effects 0.000 description 4

- 230000006399 behavior Effects 0.000 description 4

- 238000007906 compression Methods 0.000 description 4

- 238000013461 design Methods 0.000 description 4

- 238000003199 nucleic acid amplification method Methods 0.000 description 4

- 238000007792 addition Methods 0.000 description 3

- 230000000295 complement effect Effects 0.000 description 3

- 230000006835 compression Effects 0.000 description 3

- 230000010354 integration Effects 0.000 description 3

- 238000001228 spectrum Methods 0.000 description 3

- 230000002547 anomalous effect Effects 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 230000001010 compromised effect Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000000750 progressive effect Effects 0.000 description 1

- 238000012892 rational function Methods 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 238000010561 standard procedure Methods 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G10—MUSICAL INSTRUMENTS; ACOUSTICS

- G10L—SPEECH ANALYSIS TECHNIQUES OR SPEECH SYNTHESIS; SPEECH RECOGNITION; SPEECH OR VOICE PROCESSING TECHNIQUES; SPEECH OR AUDIO CODING OR DECODING

- G10L19/00—Speech or audio signals analysis-synthesis techniques for redundancy reduction, e.g. in vocoders; Coding or decoding of speech or audio signals, using source filter models or psychoacoustic analysis

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04R—LOUDSPEAKERS, MICROPHONES, GRAMOPHONE PICK-UPS OR LIKE ACOUSTIC ELECTROMECHANICAL TRANSDUCERS; DEAF-AID SETS; PUBLIC ADDRESS SYSTEMS

- H04R3/00—Circuits for transducers, loudspeakers or microphones

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03G—CONTROL OF AMPLIFICATION

- H03G5/00—Tone control or bandwidth control in amplifiers

- H03G5/005—Tone control or bandwidth control in amplifiers of digital signals

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03G—CONTROL OF AMPLIFICATION

- H03G5/00—Tone control or bandwidth control in amplifiers

- H03G5/16—Automatic control

- H03G5/165—Equalizers; Volume or gain control in limited frequency bands

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03G—CONTROL OF AMPLIFICATION

- H03G9/00—Combinations of two or more types of control, e.g. gain control and tone control

- H03G9/005—Combinations of two or more types of control, e.g. gain control and tone control of digital or coded signals

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04R—LOUDSPEAKERS, MICROPHONES, GRAMOPHONE PICK-UPS OR LIKE ACOUSTIC ELECTROMECHANICAL TRANSDUCERS; DEAF-AID SETS; PUBLIC ADDRESS SYSTEMS

- H04R2430/00—Signal processing covered by H04R, not provided for in its groups

Landscapes

- Engineering & Computer Science (AREA)

- Signal Processing (AREA)

- Physics & Mathematics (AREA)

- Acoustics & Sound (AREA)

- Computational Linguistics (AREA)

- Health & Medical Sciences (AREA)

- Audiology, Speech & Language Pathology (AREA)

- Human Computer Interaction (AREA)

- Multimedia (AREA)

- Tone Control, Compression And Expansion, Limiting Amplitude (AREA)

- Circuit For Audible Band Transducer (AREA)

- Complex Calculations (AREA)

Abstract

본 발명은 오디오 신호를 디지털 방식으로 처리하는 방법 및 시스템을 제공한다. 특히, 본 발명은 스튜디오 품질급 사운드를 재현할 수 있도록 오디오 신호를 디지털 방식으로 처리하도록 구성된 헤드라이너 스피커 시스템을 제공한다.

Description

본 발명은 오디오 신호를 디지털 방식으로 처리하기 위한 방법 및 시스템을 제공한다. 특히, 일부 실시예에서는 스튜디오-품질급 사운드를 오디오 장치들의 전체 스펙트럼에 걸쳐 재현할 수 있도록 오디오 신호를 디지털 방식으로 처리하는 것에 관련된다.

역사적으로, 스튜디오 녹음 과정에 사용되어온 완전한 범위의 오디오 주파수를 완벽하게 재현할 수 있는 것으로 표현될 수 있는 스튜디오 품질급 사운드는 오디오 녹음 스튜디오에서만 적절하게 달성될 수 있었다. 스튜디오 품질급 사운드는 어퍼-미드 주파수 범위를 효율적으로 조작하고 재현할 수 있을 때만 얻어지는 선명도(clarity)와 밝기(brightness)의 레벨을 특징으로 한다. 스튜디오 품질급 사운드의 기술적 뒷받침은 숙련된 녹음 기술자들에 의해서만 제대로 이루어질 수 있지만, 평균적인 청취자들은 스튜디오 품질급 사운드가 나타내는 차이점을 쉽게 귀로 인식할 수 있다.

녹음 스튜디오 외부에서 스튜디오 품질급 사운드를 재현하기 위해 다양한 시도가 있었지만, 이 시도들은 고성능 스피커 설계, 값비싼 하드웨어 비용, 과도한 증폭 출력 등과 같은 댓가에 직면해왔으며, 소정의 절충된 결과만을 얻을 수 있었다. 따라서, 일관되면서도 고품질의 결과를 저렴한 비용으로 스튜디오 품질급 사운드를 스튜디오 외부에서 재현할 수 있는 프로세스에 대한 요구가 존재한다. 또한, 이러한 프로세스를 구현할 수 있는 오디오 장치와, 이 오디오 장치 내에 임베딩될 수 있는 프로세스를 구현할 수 있는 컴퓨터 칩에 대한 요구가 존재한다. 저렴한 스피커를 통해 스튜디오 품질급 사운드를 내보내고자하는 요구가 또한 존재한다.

더우기, 차량용 오디오 시스템 설계에서는 여러가지 종류의 요인들을 고려하여야 한다. 오디오 시스템 설계자는 차량 내 스피커의 위치와 갯수를 선택한다. 각 스피커의 설계된 주파수 응답 역시 결정되어야 한다. 예를 들어, 기기 패널 상에 위치한 스피커의 요망 주파수 응답과 후방 도어 패널의 하부에 위치한 스피커의 요망 주파수 응답은 서로 다를 수 있다.

오디오 시스템 설계자는 장비 변화가 오디오 시스템에 어떻게 영향을 미칠 것인지를 또한 고려하여야 한다. 예를 들어, 컨버터블 차량의 오디오 시스템은 동일한 모델의 하드탑 차량에 동일한 오디오 시스템을 채택했을 때만큼 우수한 사운드를 보이지 못할 수 있다. 차량용 오디오 시스템 옵션들이 크게 변할 수도 있다. 차량용 한개의 오디오 옵션이 채널 당 40와트의 증폭으로 기본 4-스피커 시스템을 포함할 수 있고, 또다른 오디오 옵션은 채널 당 200 와트 증폭의 12-스피커 시스템을 가질 수 있다. 오디오 시스템 설계자는 차량용 오디오 시스템 설계시 이 모든 사항들을 고려하여야 한다. 이러한 이유로, 오디오 시스템 설계는 시간이 소요되고 비용도 많이 든다. 오디오 시스템 설계자들은 신호 처리 및 등화(equalization)에 관하여 비교적 폭넓은 배경 지식을 가지고 있어야 한다.

이러한 고려사항들에 비추어, 차량에서 스튜디오 품질급 사운드를 얻기 위해, 공장에서 설치한 스피커들을 값비싼 비용을 들여 업그레이드하는 등등, 상당한 비용 지출이 일어나고 있다. 이와 같이, 이러한 값비싼 지출을 할 필요없이 차량에서 스튜디오 품질 사운드를 재현할 수 있는 시스템이 필요하다.

본 발명은 오디오 장치의 전체 스펙트럼에 걸쳐 스튜디오 품질급 사운드를 재현할 수 있도록 오디오 신호를 디지털 방식으로 처리하는 방법을 제공함으로서 상술한 요구를 충족시키고자 한다. 본 발명은 이러한 방식으로 오디오 신호를 디지털 방식으로 처리할 수 있는 컴퓨터 칩을 제공하고자 하며, 이러한 칩을 포함하는 오디오 장치를 제공하고자 한다.

본 발명은 스튜디오 품질급 사운드의 재현에 저렴한 스피커를 사용할 수 있게 함으로서 상술한 요구를 충족시키고자 한다. 더우기, 본 발명은 오디오 신호를 디지털 방식으로 조작함으로서 차량의 기존 스피커 시스템을 이용하여 스튜디오 품질 사운드를 재현하는 데 차량에 사용될 수 있는 모바일 오디오 장치를 제공함으로서 상술한 요구를 충족시키고자 한다. 더우기, 공장에서 설치된 차량 스피커들도 본 발명을 이용하여 스튜디오 품질 사운드를 구현하는 데 사용될 수 있게 한다.

일실시예에서는, 오디오 신호를 입력하는 단계와, 이 오디오 신호의 이득을 첫번째로 조정하는 단계와, 이 신호를 제 1 로우 쉘프 필터로 처리하는 단계와, 이 신호를 제 1 하이 쉘프 필터로 처리하는 단계와, 이 신호를 제 1 컴프레서로 처리하는 단계와, 이 신호를 제 2 로우 쉘프 필터로 처리하는 단계와, 이 신호를 제 2 하이 쉘프 필터로 처리하는 단계와, 이 신호를 그래픽 이퀄라이저로 처리하는 단계와, 이 신호를 제 2 컴프레서로 처리하는 단계와, 이 오디오 신호의 이득을 두번째로 조정하는 단계로 구성되는 방법을 제공한다. 본 실시예에서, 오디오 신호는 스튜디오 품질급 사운드가 생성되도록 조작된다. 더우기, 본 실시예에서는 오디오 소스나 프로그램 재료간에 존재하는 임의의 내재적인 볼륨 차이를 보상한다. 그리고, 일정한 출력 레벨의 풍부하고 충실한 사운드를 생성한다.

본 실시예에서는 이동 중인 자동차의 경우처럼, 잡음이 큰 환경에서 스튜디오 품질급 사운드를 재현할 수 있다. 본 발명의 일부 실시예에서는 임의의 환경에서 스튜디오 품질급 사운드를 재현할 수 있다. 이는 콘서트 홀같이 음향 측면에서 잘 설계된 환경들을 포함한다. 이는 평범한 거실, 차량 내부, 등등과 같이 음향 측면에서 양호하지 못한 환경들을 또한 포함한다. 더우기, 일부 실시예에서는 본 발명과 관련하여 사용되는 스피커 및 전기 부품의 품질에 관계없이 스튜디오 품질급 사운드를 재현할 수 있다. 따라서, 본 발명은 최상위급 및 최하위급 전자 장치 및 스피커 어느 쪽으로도, 그리고 그 사이의 어떤 품질의 장비로도 스튜디오 품질급 사운드를 재현하는 데 사용될 수 있다.

일부 실시예에서는 자동차, 비행기, 배, 클럽, 극장, 놀이 공원, 쇼핑몰, 등등과 같은 고잡음 환경에서 음악, 영화, 비디오 게임 등을 재생하는 데 본 발명이 사용될 수 있다. 더우기, 일부 실시예에서는 600 Hz 와 1,000 Hz 사이에 있는 가청 범위 및 오디오 트랜스듀서 모두에 유효한 범위 바깥에 있는 오디오 신호를 처리함으로서 사운드 재현을 개선시키고자 한다. 이 범위 바깥의 오디오를 처리함으로서 더 풍부하고 폭넓은 음향 재현이 가능하다.

일부 실시예에서는 오디오 신호의 베이스 부분이 압축 이전에 감소될 수 있고 압축 이후에 개선될 수 있어서, 스피커에 제시되는 사운드가, 종래의 압축 과정에서 나타나는 머플링 효과(muffling effect)로부터 자유로우면서 베이스 톤이 풍부한 스펙트럼을 가짐을 보장하게 된다. 더우기, 일부 실시예에서는 오디오 신호의 동적 범위가 압축에 의해 감소되기 때문에, 결과적인 출력이 제한된 볼륨 범위 내에서만 제시되었다. 예를 들어, 본 발명은 80 dB 노이즈 플로어와 110 dB 사운드 임계치를 가진 고잡음 환경에서 스튜디오 품질급 사운드를 편안하게 제시할 수 있다.

일부 실시예에서는 상술한 방법이 상술한 방법 이전에, 상술한 방법 이후에, 또는 상술한 방법과 함께 간헐적으로 수행되는 디지털 신호 처리 방법과 결합될 수 있다.

특정 일실시예에서는 상술한 방법을 수행할 수 있는 컴퓨터 칩을 제공한다. 일실시예에서는 컴퓨터 칩이 디지털 신호 프로세서(DSP)일 수 있다. 또다른 실시예에서는 컴퓨터 칩이 컴퓨터, 컴퓨터 소프트웨어, 전기 회로, 전기적인 칩 등등과 같이 상술한 방법을 수행할 수 있는 임의의 프로세서일 수 있다.

일실시예에서는 이러한 컴퓨터 칩을 포함하는 오디오 장치를 제공한다. 오디오 장치는 라디오, CD 플레이어, 테이프 플레이어, MP3 플레이어, 셀 폰, TV, 컴퓨터, 퍼블릭 어드레스 시스템, 게임기(가령, 플레이스테이션 3, X박스 360, 닌텐도 Wii), 홈시어터 시스템, DVD 플레이어, 비디오 카세트 플레이어, 블루레이 플레이어 등등을 포함할 수 있다.

이러한 실시예에서, 본 발명의 칩은 소스 실렉터를 통과한 후 볼륨 조절부에 도달하기 전에 오디오 신호를 처리할 수 있다. 특히, 일부 실시예에서는 오디오 장치에 위치한 본 발명의 칩이 CD 플레이어, 테이프 플레이어, DVD 플레이어, 등등을 포함하는 한개 이상의 소스로부터 오디오 신호들을 처리한다. 본 발명의 칩의 출력은 다른 신호 처리 모듈이나 스피커를 구동시킬 수 있고, 이 경우에 신호 증폭이 자주 이용된다.

특히, 일실시예에서는 이러한 컴퓨터 칩을 포함하는 모바일 오디오 장치를 제공한다. 이러한 모바일 오디오 장치는 자동차에 배치될 수 있고, 가령, 라디오, CD 플레이어, 테이프 플레이어, MP3 플레이어, DVD 플레이어, 또는 비디오 카세트 플레이어 등등을 포함할 수 있다.

본 실시예에서, 모바일 오디오 장치는 각 차량에 부합되도록 조율될 수 있고, 스피커 배치, 승객 배분 설계, 배경 잡음 등등과 같은 차량 내 고유 음향 성질들을 위해, 그리고, 최적 성능을 얻기 위해 사용될 수 있다. 또한 본 실시예에서는 모바일 오디오 장치가 독립적으로 제어되는 모두 4개의 채널들에 대해 정밀한 튜닝을 제공할 수 있다. 또한 본 실시예에서, 본 발명의 모바일 오디오 장치는 200 와트의 출력을 전달할 수 있다. 또한 본 실시예에서는 모바일 오디오 장치가 스튜디오 품질급 사운드를 생성하기 위해 차량의 기존 스피커 시스템(가령, 공장에서 설비한 스피커 시스템)을 이용할 수 있다. 또한 USB 포트를 구성하여 표준 디지털 포맷의 노래들을 재생할 수도 있다. 또한, 위성 라디오로 이용하기 위한 어댑터를 포함할 수도 있다. 또한, 본 발명의 모바일 오디오 장치가 원격 제어기를 포함할 수 있다. 또한 탈착가능한 페이스플레이트를 포함할 수도 있다.

본 발명이 반드시 오디오 분야에 국한되는 것은 아니다.

도 1은 본 발명의 디지털 신호 처리 방법의 일실시예에 대한 블록도표.

도 2는 본 발명의 디지털 신호 처리 방법의 일실시예에 사용되는 로우-쉘프 필터의 효과 도면.

도 3은 하이 패스 및 로우 패스 필터를 이용하여 로우 쉘프 필터가 어떻게 생성되는 지를 도시한 도면.

도 4는 본 발명의 디지털 신호 처리 방법의 일실시예에 사용되는 하이 쉘프 필터의 효과 도면.

도 5는 본 발명의 디지털 신호 처리 방법의 일실시예에 사용되는 벨 필터의 주파수 응답 도면.

도 6은 본 발명의 디지털 신호 처리의 일실시예에 사용되는 그래픽 이퀄라이저의 일실시예의 블록도표.

도 7은 Mitra-Regalia 실현을 이용하여 필터가 구성되는 방식을 도시하는 블록도표.

도 8은 본 발명의 디지털 신호 처리 방법의 일실시예에 사용될 수 있는 크기-보완형 로우 쉘프 필터의 효과 도면.

도 9는 본 발명의 디지털 신호 처리 방법의 일실시예에 사용될 수 있는 크기-보완형 로우 쉘프 필터의 구현예에 대한 블록도표.

도 10은 본 발명의 디지털 신호 처리 방법의 일실시예에 사용될 수 있는 컴프레서의 정적 전이 특성(출력 및 입력 레벨 간의 관계) 도면.

도 11은 본 발명의 디지털 신호 처리 방법의 일실시예에 사용되는 2차 전이 함수의 디렉트 폼 타입 1 구현예의 블록도표.

도 12는 본 발명의 디지털 신호 처리 방법의 일실시예에 사용되는 2차 전이 함수의 디렉트 폼 타입 1 구현예의 블록도표.

1.0 개관

먼저, 선형 시간-불변 시스템에 대한 일부 배경지식이 도움이 될 것이다. 입력 x[k]와 출력 y[k]를 가진 N차의 선형 시간 불변(LTI) 디스크리트-타임 필터는 아래의 차이 방정식에 의해 표현된다.

이때, 필터가 요망 특성을 가지도록 계수 {b0, b1, . . . , bN, a1, a2, . . . , aN}가 결정된다. 요망되는 항은 시간-도메인 거동 또는 주파수 도메인 거동을 표시할 수 있다.

상기 차이 방정식은 임펄스 함수 δ[k]에 의해 표시될 수 있다.

신호 δ[k] 가 상술한 차이 함수에 의해 표현되는 시스템에 공급될 때, 그 결과는 임펄스 응답 h[k] 로 알려져 있다. 임펄스 함수 h[k] 단독으로 임의의 입력 신호에 대한 LTI 디스크리트-시간 시스템의 거동을 완벽하게 특성화시킬 수 있다는 것은 시스템 이론으로부터 잘 알려진 결과다. 즉, h[k] 를 알고 있을 경우, 입력 신호 x[k]에 대한 출력 y[k] 를 컨벌루션으로 알려진 연산에 의해 얻을 수 있다. 공식적으로, h[k] 와 x[k]를 알고 있을 경우, 응답 y[k] 는 다음과 같이 연산된다.

z-변환에 대한 배경지식 역시 도움이 될 것이다. 시간 도메인 및 주파수 도메인 간의 관계는 z-변환이라는 형태로 나타난다. 임펄스 응답 h[k]에 의해 표현되는 시스템의 z-변환은 함수 H(z)로 규정될 수 있으며, 그 세부사항은 아래와 같다.

이때, z는 복소 변수로서, 실수부와 허수부를 가진다. 복소 변수가 복소평면의 단위원으로 제한될 경우, 그 결과는 아래와 같이 라디알 형태로 표현될 수 있는 복소 변수다.

디스크리트-시간 퓨리에 변환에 대한 배경지식 역시 도움이 된다. z 를 라디알 형태로 표현할 경우, z-변환을 단위 원으로 제한하는 것은 디스크리트-시간 퓨 리에 변환(DTFT)으로 알려져 있고, 아래와 같이 나타난다.

특히 관심이 되는 사항은, 주어진 주파수의 사인곡선에 의해 여기될 때 시스템이 어떻게 동작하는가 하는 점이다. LTI 시스템의 이론으로부터 가장 주목할만한 결과 중 하나는 사인곡선들이 이러한 시스템들의 아이겐함수라는 것이다. 이는, 사인곡선 sin(θOk) 에 대한 LTI 시스템의 스테디-스테이트 응답이 동일 주파수 θ0의 사인곡선이며, 입력으로부터 진폭과 위상이 다를 뿐이다. 실제로, 입력 x[k] = sin(θ0k) 일 때, LTI 시스템의 스테디 스테이트 출력 yss[k]는 다음과 같다.

이때,

마지막으로, 주파수 응답에 대한 배경지식이 필요할 것이다. 상술한 수식들은 사인곡선에 의해 구동될 때 LTI 시스템의 스테디 스테이트 응답이 동일 주파수의 사인곡선이며, 이 주파수에서의 DTFT의 크기만큼 스케일링되며, 그리고, 이 주파수에서의 DTFT의 위상만큼 시간 오프셋을 가진다. 본 발명의 목적을 위해, 주관심사항은 스테디 스테이트 응답의 진폭이고, LTI 시스템이 사인곡선에 의해 구동될 때 입력에 대한 출력의 상대적 크기를 DTFT가 우리에게 제공한다는 점이다. 입력 신호가 사인곡선들의 선형 조합으로 표현될 수 있다(퓨리에 디컴포지션 이론)는 것은 잘 알려진 사항이기 때문에, DTFT는 임의의 입력 신호에 대해 응답을 제공할 수 있다. 정성적으로 판단할 때, DTFT는 시스템이 한 범위 내의 입력 주파수들에 대해 어떻게 응답하는 지를 보여주며, 주어진 주파수의 신호 중 얼마나가 시스템의 출력에 나타날 것인지를 의미있게 측정한 값들을 제시하는 DTFT의 크기 플롯을 함께 나타낼 것이다. 이러한 이유로, DTFT는 시스템의 주파수 응답으로 잘 알려져 있다.

2.0 디지털 신호 처리

도 1은 본 발명의 일실시예에 따른 방법(100)의 디지털 신호 처리 순서를 도시한다. 도 1과 관련하여, 방법(100)은 입력 이득 조정(101), 제 1 로우 쉘프 필터(102), 제 1 하이 쉘프 필터(103), 제 1 컴프레서(104), 제 2 로우 쉘프 필터(105), 제 2 하이 쉘프 필터(106), 그래픽 이퀄라이저(107), 제 2 컴프레서(108), 출력 이득 조정(109)의 단계들을 포함한다.

일실시예에 따르면, 디지털 신호 처리 방법(100)은 입력 오디오 신호(110)를 입력으로 취하여, 단계(101-109)들을 실행하고, 출력 오디오 신호(111)를 출력으로 제공한다. 일실시예에 따르면, 디지털 신호 처리 방법(100)은 디지털 신호 프로세서(DSP)같은 컴퓨터 칩 상에서 실행가능하다. 일실시예에서는 이러한 칩이 라디오, MP3 플레이어, 게임기, 셀폰, TV, 컴퓨터, 또는 퍼블릭 어드레스 시스템같은 더 큰 오디오 장치의 일부분일 수 있다. 일실시예에서는 오디오 신호가 오디오 장치로부터 출력되기 전에 디지털 신호 처리 방법(100)이 오디오 신호들에 대해 수행될 수 있다. 일실시예에서는 오디오 신호가 소스 실렉터를 통과한 후 볼륨 제어부를 통과 하기 전에 디지털 신호 처리 방법(100)이 오디오 신호에 대해 수행될 수 있다.

일실시예에 따르면, 단계(101-109)들이 순서에 따라 진행될 수 있으며, 이와는 다른 순서로 진행될 수도 있다. 일실시예에서는 단계(101-109)들만이 배타적으로 수행될 수 있고, 또다른 실시예에서는 다른 단계들이 부가될 수도 있다. 일실시예에서는 각각의 단계(101-109)가 모두 실행될 수 있지만, 또다른 실시예에서는 일부 단계가 빠질 수도 있다.

일실시예에 따르면, 디지털 신호 처리 방법(100)의 차후 내부 포인트에서 디지털 오버플로를 방지할 수 있는 레벨로 입력 오디오 신호(110)를 조정하기 위해 입력 이득 조정(101)이 요망 크기의 이득을 제공한다.

일실시예에 따르면, 각각의 로우 쉘프 필터(102, 105)는 코너 주파수라 불리는 소정의 주파수보다 위의 모든 주파수에 대해 0dB의 명목 이득을 가지는 필터다. 코너 주파수보다 낮은 주파수에 대해, 로우 쉘프 필터가 부스트 모드인지 또는 컷 모드인지에 따라 로우 쉘프 필터는 +/- G dB의 이득을 가진다. 이는 도 2에 도시된다.

도 2는 본 발명의 일실시예에 의해 구현되는 로우 쉘프 필터의 효과를 도시한다. 도 2와 관련하여, 로우 쉘프 필터의 목적은 코너 주파수보다 큰 주파수들 모두를 변경없이 남겨두고, 코너 주파수보다 작은 모든 주파수들을 고정된 크기 G dB만큼 부스트시키거나 잘라내는(cut) 것이다. 0dB 포인트는 요망하는 1000 Hz보다 약간 높다는 점에 주목하여야 한다. 코너 주파수에서 -3dB에 놓인 응답을 가지도록 컷 모드로 로우 쉘프 필터를 명시하는 것이 표준이며, 최대 부스트로부터 3dB 아래 인 G - 3dB에 코너 주파수의 응답이 놓이도록 부스트 모드의 로우 쉘프 필터가 명시된다. 게다가, 쉘프 필터를 생성하기 위한 모든 텍스트북 공식들이 이러한 응답들을 이끈다. 이는 소정 크기의 비대칭성을 야기하는데, 이 경우, 부스트 또는 컷 G의 거의 모든 값들에 대해, 컷 또는 부스트된 로우 쉘프 필터들이 서로의 미러 이미지가 아니다. 이는 본 발명에 의해 취급될 필요가 있는 사항에 해당하며, 필터의 구현예에 대한 혁신적 접근법을 필요로한다.

이러한 비대칭성을 무시하고, 러우 쉘프 필터를 생성하기 위한 표준 방법은 하이 패스 필터와 로우 패스 필터의 가중 합으로 나타난다. 예를 들어, -G dB의 이득과 1000 Hz의 코너 주파수를 가진 컷 모드의 로우 쉘프 필터의 경우를 고려해보자. 도 3은 1000 컷오프 주파수를 가진 하이 패스 필터와, 1000 Hz의 컷오프 주파수를 가진 로우 패스 필터(-G dB로 스케일링됨)를 도시한다. 직렬로 인가되는 이 두 필터의 총 효과는 도 2의 로우 쉘프 필터와 유사하다. 실제로, 부스트나 컷이 없는 모드로부터 G dB의 부스트나 컷을 가진 모드로 전이시의 가파름(즉, 기울기)에는 일부 제한이 있다. 도 3은 이러한 제한사항을 도시하며, 이때, 1000 Hz에 코너 주파수가 나타나고, 1000 Hz 미만의 특정 주파수일때까지는 요망하는 G dB의 부스트나 컷이 이루어지지 않는다. 본 발명의 쉘프 필터들 모두는 1차 쉘프 필터임을 주목하여야 한다. 즉, 이 필터들이 1차 회전 전이 함수에 의해 표현될 수 있다.

일실시예에서는 각각의 하이 쉘프 필터(103, 106)이 로우 쉘프 필터의 미러 이미지에 지나지 않는다. 즉, 코너 주파수 아래의 모든 주파수들은 수정없이 남겨지며, 코너 주파수 위의 주파수들은 G dB만큼 부스트 또는 컷된다. 가파름과 비대칭성에 관한 동일한 보류 경고가 하이 쉘프 필터에 적용된다. 도 4는 본 발명의 일실시예에 의해 구현되는 하이 쉘프 필터의 효과를 도시한다. 도 4와 관련하여, 1000 Hz 하이 쉘프 필터가 도시된다.

도 5는 본 발명의 일실시예에 따른 방법(100)에 의해 구현되는 벨 필터의 일례의 주파수 응답을 도시한다. 도 5에 도시되는 바와 같이, 각각의 2차 필터들이 고정 중심 주파수에서 벨 형태의 부스트 또는 컷을 나타낸다. 이때, F1(z)의 중심 주파수는 30Hz, F11(z)의 중심 주파수는 16,000 Hz이며, 나머지 필터들은 서로 약 1 옥타브 간격으로 그 중심을 가진다. 도 5와 관련하여, 벨-형 필터의 중심 주파수는 1000 Hz다. 이 필터는 중심 주파수(1000 Hz) 위와 아래의 주파수에 대해 0dB의 명목 이득을 가지며, 1000Hz에서 -GdB의 이득을, 그리고 1000 Hz 부근의 영역에서 벨-형 응답을 가진다.

필터의 형태는 단일 파라미터의 특징을 가진다. 즉, 품질 팩터 Q로 표현된다. 품질 팩터는 3-dB 대역폭 B에 대한 필터의 중심 주파수의 비로 규정된다. 3-dB 대역폭은 도면에서, 필터 응답이 -3dB 포인트를 거칠 때 두 주파수 간의 Hz 차이로 나타난다.

도 6은 본 발명의 일실시예에 따른 일례의 그래픽 이퀄라이저 블록(600)을 도시한다. 도 6과 관련하여, 그래픽 이퀄라이저(600)는 11개의 2차 필터, F1(z), F2(z),..., F11(z)의 직렬 뱅크로 구성된다. 일실시예에 따르면, 그래픽 이퀄라이 저(107)(도 1 참조)가 그래픽 이퀄라이저(600)로 구현된다.

11개의 2차 필터들 각각은 아래와 같은 공식으로 연산될 수 있다.

이러한 수식을 이용할 때 한가지 문제점이 나타난다. 위 다섯개의 계수 {b0, b1, b2, a1, a2} 각각이 품질 팩터 Q와 이득 G에 직접 좌우된다는 것이다. 이는, 필터들이 튜닝가능하도록 하기 위해, 즉, 변수 Q와 G를 가지도록 하기 위해, 모두 다섯개의 계수들이 실시간으로 재연산되어야 함을 의미한다. 이는 이러한 연산이 그래픽 이퀄라이저(107)를 실행하는 데 가용한 메모리를 손쉽게 소모시킬 수 있고, 그리고 수용불가능한 과량의 지연이나 폴트 문제를 생성할 수 있기 때문에 문제가 된다. 이러한 문제점은 Mitra-Gegalia Realization을 이용하여 방지할 수 있다.

디지털 신호 처리 이론으로부터 생기는 가장 중요한 결과는 디지털 신호 처리 방법(100)에 사용되는 필터들을 구현하는 데 사용된다. 이 결과는 다양한 필터들이 올패스 필터와 입력으로부터의 피드포워드 브랜치의 가중 합으로 분해될 수 있다는 점을 제시한다. 이 결과의 중요성은 명백해질 것이다. 우선은, 2차 전이 함수 H(z)가 품질 팩터 Q와 샘플링 주파수 Fs 및 fc의 중심 주파수를 가진 벨 틸터를 표현하기 위해 아래와 같이 구현되고 있다고 가정해보자.

보조적인 값 k1, k2는 아래와 같이 규정된다.

그리고 전이 함수 A(z)는 아래와 같이 정의된다.

A(z)는 올패스 필터인 것으로 확인될 수 있다. 이는 A(z)의 진폭이 모든 주파수에 대해 일정하다는 것을 의미하며, 단지 위상만이 주파수의 함수로 변한다는 것을 의미한다. A(z)는 각각의 벨-형 필터에 대한 빌딩 블록으로 사용될 수 있다. 다음의 매우 중요한 결과가 나타날 수 있다.

이는 Mitra-Regalia Realization의 핵심에 해당한다. 튜닝가능한 이득을 가진 벨 필터가 매우 명시적인 방식으로 이득 G를 포함시킨 것을 보여주도록 구현될 수 있다. 이는 도 7에 도시되는 데, 도 7에서는 본 발명의 일실시예에 따른 Mitra-Regalia Realization을 이용하여 구성되는 일례의 필터를 도시한다.

이와 같이 직관적이지 않은 방식으로 필터를 분해하는 데는 매우 좋은 이유가 있다. 상기한 방정식과 관련하여, a와 b 계수들 각각이 G 변화시마다(즉, 그래픽 이퀄라이저 "슬라이더" 중 하나가 이동할 때마다) 재연산될 필요가 있음을 기억해보자. a와 b 계수에 대해 수행될 필요가 있는 연산들이 도시되지는 않지만, 이들 은 매우 복잡하고 시간 소요가 크며, 이들을 실시간으로 재연산하는 것은 실용적이지 않다. 그러나 전형적인 그래픽 이퀄라이저에서는 이득 G와 품질 팩터 Q가 일정하게 유지되고 G만이 변하도록 허용된다. 이것이 방금 언급한 방정식을 매력적으로 만드는 것이다. A(z)가 어떤 방식으로든 이득 G에 좌우되지 않다는 것을 위 방정식에서 확인할 수 있고, Q와 중심 주파수 fc가 일정하게 유지될 경우 k1과 k2가 G에관계없이 일정하게 유지됨을 방정식으로부터 확인할 수 있다. 따라서, 이 변수들은 한번에 연산될 수 있는 것이다. 이득 변수 연산은 실시간으로 한 쌍의 단순한 양들을 변화시킴으로서 이루어진다.

와

이들은 매우 간단한 연산에 해당하며, 한 쌍의 CPU 사이클만을 필요로한다. 이는 올 패스 전이 함수 A(z)를 구현하는 방식에 관한 질문만을 남기며, 이러한 질문은 사소한 사항에 불과하다. 따라서 전체 그래픽 이퀄라이저 뱅크는 11개의 직렬 벨 필터로 구성되며, 각각의 벨 필터는 각자의 Mitra-Regalia Realization을 통해 구현된다.

상술한 바와 같이, 필터가 커팅시에 비해 부스팅되고 있을 때 종래의 쉘프 필터의 응답에는 비대칭성이 존재한다. 이는 커팅시보다 부스팅시 3-dB 포인트에 대해 서로 다른 규정을 가진 설계 기술에 기인한다. 디지털 신호 처리 방법(100)은 필터 H1(z)와 H3(z)가 서로 미러 이미지임에 의존하며, 이는 H2(z)와 H4(z)에 대해서도 마찬가지로 적용된다. 이는 부스팅 쉘프 필터에 대해 특별한 필터 구조의 이용을 야기하였으며, H1, H3, 그리고, H2, H4에 대해 완벽한 크기 소거를 이끄는 필터 구조의 이용을 야기하였다(도 8 참조). 이러한 타입의 주파수 응답은 크기 보완형(magnitude complementary)이라고 알려져 있다.

이 구조는 본 발명에 대해 독자적이다. 일반적으로, 보완형 크기 응답을 가진 필터를 임의의 필터 H(z)에 대해 도출하는 것은 간단한 수학적 계산에 해당한다. 필터 H-1(z)는 확실히 빌(bill)에 부합하지만, z의 안정한 또는 구현가능한 함수는 아닐 수 있다. 이 경우에 해법은 수학적 관심사이며 실제로 이용가능하지 않다. 이는 종래의 쉘프 필터를 이용하는 경우에 해당한다. 상술한 방정식들은 올패스 필터로부터 벨 필터를 어떻게 제작하는 지를 보여준다. 이 방정식은 1차 올패스 필터 A(z)로 시작하는 쉘프 필터를 구성함에 있어 마찬가지로 적용된다.

그리고 α는 다음과 같이 선택된다.

이때, fc는 요망 코너 주파수이고, Fs는 샘플링 주파수다. 상술한 방정식을 적용하여 항을 정리하면 이는 아래와 같이 표현될 수 있다.

이는 로우 쉘프 릴터에 대한 방정식이다. 참고로, 항 (1-G)를 (G-1)로 변화시킴으로서 하이 쉘프 필터를 얻을 수 있다. H(z)의 역수를 취함으로서, 아래의 결과를 얻을 수 있다.

이 방정식은 지연없는 루프를 가지기 때문에 문제가 된다. 이는, 종래의 상태-변화 방법들을 통해 구현될 수 없다는 것을 의미한다. 다행스럽게도, 지연없는 루프로 합리적 함수들을 어떻게 구현하는 지를 보여주는 시스템 이론으로부터 얻은 최근의 결과들이 있다. Fontana와 karjalainen은 각각의 단계가 시간에 따라 두개의 서브 단계로 나뉘어질 수 있음을 보여주었다.

도 9는 발명의 일실시예에 따른 크기-보완형 로우 쉘프 필터의 예를 도시한다. 도 9에서는 제 1 서브 단계 중("서브샘플 1"로 표시됨), 필터 A(z)에 제로 입력을 공급하고 그 출력 l0[k]를 연산한다. 이와 동일한 서브샘플 중, l0[k]의 값을 이용하여 출력 y[k]를 연산하고, 이는 방금 상술한 방정식으로부터 아래와 같이 실행될 수 있다.

이 두 연산은 스위치들이 "서브샘플 1" 위치에 있는 경우에 해당한다는 것을 도 9로부터 알 수 있다. 그후, 스위치들이 "서브샘플 2" 위치로 던져지고, 남겨진 유일한 사항은 필터 A(z)의 내부 상태를 업데이트하는 것이다. 이러한 신규한 필터 구조는 완벽한 크기 보완성으로 나타난다. 이는 아래의 방식으로 본 발명에서 이용될 수 있다. 즉, 디지털 신호 처리 방법(100)의 쉘프 필터들이 컷 모드에 있을 때, 아래의 방정식이 사용될 수 있다.

그러나, 디지털 신호 처리 방법(100)의 쉘프 필터들이 부스트 모드에 있는 경우, 다음의 방정식이 컷 모드에 사용되는 G와 동일한 값으로 이용될 수 있다.

이는 쉘프 필터가 도 8에서처럼 서로 완벽한 미러 이미지임을 나타낸다. 이는 디지털 신호 처리 방법(100)에 꼭 필요한 사항이다. 참고로, 수식 16은 (1-G)/2 항의 부호를 변화시킴으로서 하이 쉘프 필터를 만들도록 변경될 수 있다.

각각의 컴프레서(104, 108)는 신호의 피크 레벨과 평균 레벨 간의 비를 감소시킴으로서 신호의 동적 범위를 변경시키도록 설계된 동적 범위 컴프레서에 해당한 다. 컴프레서는 네가지 양을 특징으로 한다. 즉, 어택 시간 Tatt, 릴리스 시간 Trel, 임계값 KT, 그리고 비 r을 특징으로 한다. 간단하게 말해서, 신호의 엔빌롭은 신호 레벨의 개략적 윤곽을 제시하는 알고리즘에 의해 트래킹된다. Tatt와 같은 시간 주기동안 이 레벨이 임계치 KT를 넘어서면, 컴프레서는 KT보다 큰 모든 dB에 대해 비 r dB만큼 신호의 레벨을 감소시킨다. 신호의 엔빌롭이 릴리스 시간 Trel과 같은 주기동안 KT 아래로 떨어지면, 컴프레서는 레벨 감소를 중지한다. 도 10은 본 발명의 일실시예에 따라 구현되는 컴프레서의 정적 전이 특성(출력 및 입력 레벨간의 관계)를 도시한다.

정적 전이 특성을 세밀하게 검사하는 것이 도움이 된다. 임의의 순간 k에서의 신호 레벨 L[k]이 연산되고 있다고 가정해보자. 한개의 단일 정적 레벨 L을 고려해보자. L이 컴프레서의 트리거 임계값 KT보다 작을 경우, 컴프레서는 아무 작업도 하지 않고 신호를 불변으로 만들 것이다. 그러나, L이 KT보다 클 경우, 컴프레서는 레벨 L이 KT보다 큰 모든 dB에 대해 r dB만큼 입력 신호를 감소시킨다.

L이 KT보다 큰 사례를 고려해보는 것이 바람직하다. 이는 20 log10(L) > 20 log10(KT) 인 경우를 의미한다. 이러한 사례에서, 초과 이득, 즉, 레벨이 임계값을 넘기는 dB의 크기는 gexcess = 20 log10(L) - 20 log10(KT) 다. 컴프레서가 초과 이득의 매 dB에 대해 rdB만큼 입력을 감소시킴에 따라, 이득 감소 gR은 다음과 같이 표현될 수 있다.

이로부터, 20 log10(y) = gR * 20 log10(x)로 주어지는 컴프레서의 출력 y으로, 요망하는 입력 대 출력 관계가 충족된다.

이 방정식을 로그 도메인이 아닌 선형 도메인으로 변환시키면 아래의 수식을 얻을 수 있다.

이는 아래와 같이 정리될 수 있다.

컴프레서 알고리즘의 가장 중요한 부분은 신호 레벨의 의미있는 추정치를 결정하는 것이다. 이는 매우 직관적인 방식으로 이루어진다. 신호의 절대값의 진행형 "적분"(running "integration")이 유지되고, 이때, 그 레벨이 적분되는 속도는 요망하는 어택 시간에 의해 결정된다. 신호의 순간적 레벨이 현재의 적분 레벨 이하로 떨어질 때, 적분 레벨은 릴리스 시간에 의해 결정되는 속도로 떨어지게 된다.

어택 시간 Tatt 와 릴리스 시간 Trel이 주어졌을 때, 레벨 L[k]를 추적하는 데 사용되는 수식은 아래와 같다.

이때, 아래의 관계가 인정된다.

그리고,

상술한 바와 같은 레벨 연산의 매 포인트마다, 연산되는 L[k]는 임계값 KT에 비교되고, L[k]가 KT 보다 클 경우, 입력 신호 x{k}가 이 레벨이 임계값을 넘어서는 크기에 비례하는 양만큼 스케일링된다. 그 비례 상수는 컴프레서 비 r과 같다. 상당한 수학적 조작 이후, 컴프레서의 입력과 출력 간에 아래의 관계가 성립된다.

수식 18에서 연산된 레벨 L[k]로, Gexcess는 다음과 같이 연산된다.

이는 초과 이득의 양을 나타낸다. 초과 이득이 1보다 작을 경우, 입력 신호는 변화없이 출력으로 전달된다. 초과 이득이 1을 넘을 경우 이득 감소 GR이 다음과 같이 연산된다.

이어서 입력 신호가 RG에 의해 스케일링되어 출력에 전달된다.

이 과정을 통해, 입력 신호 레벨의 매 1dB 증가에 대해 1/r dB 만큼 증가되는 레벨을 가진 출력 신호가 생성된다.

실제로, 위 방정식들에 대해 역수 KT -1을 연산하는 것은 시간이 많이 걸린다. 왜냐하면, 실시간 나눗셈에 있어서 컴퓨터 칩들이 매우 불량하기 때문이다. KT가 미리 알려져 있고 사용자가 이를 변화시킬 때만 KT가 변하기 때문에, 미리 연산된 KT -1 값들의 표가 메모리에 저장되어 필요에 따라 사용될 수 있다. 마찬가지로, GR을 연산하는 위 방정식에서의 지수 연산은 실시간 수행이 매우 어렵다. 그래서, 미리 연산된 값들이 근사치로 사용될 수 있다. Gexess가 단위값보다 클 경우에만 GR이 고려대상이기 때문에, GR=1 부터 GR = 100 까지 정수 값들에 대해 미리 연산된 GR의 100개의 값과 같은 리스트가 모든 가능한 비 r 값에 대해 생성될 수 있다. GR이 정수가 아닌 경우에, GR을 연산하는 위 방정식의 양이 아래와 같은 방식으로 근사될 수 있다. Gexcess가 Gexcess의 가장 가까운 정수값을 넘는 만큼의 크기를 interp라고 하자. 다시 말해서,

또한 GR ,0과 GR ,1이 미리 연산된 값을 의미한다고 하자.

선형 보간이 사용되어 GR의 근사치를 다음과 같이 구할 수 있다.

GR의 실제값과 위 방정식에서 GR의 근사치 간의 오차는 본 발명의 목적을 위해 무시되는 것으로 나타날 수 있다. 더우기, GR의 근사치의 연산은 단지 2~3개의 산술 연산 사이클을 필요로하는 것에 불과하고 그 이상의 연산은 기연산된 표로부터 읽어들이게 된다. 일실시예에 따르면, Gexcess의 100개의 정수 점들에 대해 그리고 비 r의 6가지 값에 대한 표가 메모리에 저장될 수 있다. 이러한 실시예에서, 전체 메모리 이용은 단지 메모리의 600개 워드에 불과하며, 이는 GR의 실제값을 연산하는 데 필요한 수백개의 연산 사이클에 비해 바람직하다고 할 것이다. 이는 본 발명의 핵심적 장점에 해당한다.

디지털 신호 처리 방법(100)의 각각의 디지털 필터는 다양한 잠재적 구조 중 임의의 한가지를 이용하여 구현될 수 있다. 이때, 각각의 구조는 복잡도, 시간당 처리량, 계수 감도, 안정성, 고정점 거동, 그리고 그외 다른 수치적 고려사항 등의 범주에서 절충을 택하게 된다. 구체적 일실시예에서, 타입 1의 디렉트 폼 구조(DF1)로 알려진 간단한 구조가 사용될 수 있다. DF1 구조는 바람직한 다수의 성질을 가지며, 이 중 어느 것도 관심대상인 필터의 전이 함수와 차이 방정식에 명확한 상관관계를 가지지 않는다. 디지털 신호 처리 방법(100)의 모든 디지털 필터들 은 1차 또는 2차 필터에 해당한다.

2차 필터를 먼저 세부적으로 점검할 것이다. 상술한 바와 같이, 2차 필터로 구현되는 전이 함수는 다음과 같이 주어진다.

이는 아래의 차이 함수에 대응한다.

도 11은 본 발명의 일실시예에 따른 2차 필터의 DF1 구조를 도시한다. 도 11에 도시되는 바와 같이, 이 필터 구조의 멀티플라이어 계수는 상기 차이 방정식 및 전이 함수의 계수들에 대응한다. 심벌 z-1과 함께 표시된 블록들은 지연 레지스터이며, 그 출력들은 매 연산 단계마다 요구된다. 이 레지스터들의 출력은 상태 변수로 불리며, 디지털 신호 처리 방법(100)의 일부 실시예에서는 이들에 대해 메모리가 할당된다. 디지털 필터의 출력은 다음과 같이 연산된다.

먼저, 모든 상태 변수들이 0으로 설정된다. 다시 말해서,

시간 k=0에서, 다음의 연산이 수행된다(도 11 참조).

그후, 이 레지스터들이 업데이트되어 x[k-1]에 의해 표시되는 레지스터가 x[0]을 홀딩하고, x[k-2]에 의해 표시되는 레지스터가 x[-1]을 홀딩하며, y[k-1]에 의해 표시되는 레지스터가 y[0]을 홀딩하고, y[k-2]에 의해 표시되는 레지스터가 y[-1]을 홀딩한다.

시간 k=1에서, 다음의 연산이 수행된다.

그후 레지스터 업데이트가 다시 완료되어 x[k-1]에 의해 표시되는 레지스터가 x[1]을 홀딩하고, x[k-2]에 의해 표시되는 레지스터가 x[0]을 홀딩하며, y[k-1]에 의해 표시되는 레지스터가 y[1]을 홀딩하고, y[k-2]에 의해 표시되는 레지스터가 y[0]을 홀딩한다.

이 프로세스는 모든 순간 k에 대해 반복된다. 새로운 입력 x[k]가 들어오고, 새로운 출력 y[k]가 연산되며, 상태 변수들이 업데이트된다.

일반적으로, 디지털 필터링 연산은 데이터 스트림 x[0], x[1], x[2],... 등등의 데이터 스트림에 대해 수행되는 한 세트의 곱셈 및 덧셈으로 간주될 수 있다. 이때, 계수 b0, b1, b2, a1, a2와, 상태 변수 x[k-1], x[k-2], y[k-1], y[k-2]를 이용하게 된다.

특정 상황에서 이를 명시하는 것이 바람직할 것이다. 그래픽 이퀄라이저(107)의 기본 빌딩 블록을 구성하는 벨 필터의 검사가 도움이 된다. 상술한 바와 같이, 벨 필터는 샘플링 주파수 Fs, 중심 주파수 fc에서의 이득 G, 그리고 품질 팩터 Q를 이용하여 아래와 같이 구현될 수 있다.

이때, A(z)는 아래와 같이 규정되는 올패스 필터다.

이때, k1과 k2는 아래의 수식들을 통해 fc와 Q로부터 연산된다.

k1과 k2 값은 기연산되어 있어, 메모리에 표 형태로 저장되어 있다. 특정 값의 Q와 fc에 대한 필터를 구현하기 위해, k1 및 k2에 대응하는 값들이 이 표에서 조사된다. 이 알고리즘에 11개의 fc값과 16개의 ㅃ 값이 존재하기 때문에, 그리고 필터는 단일 샘플링 주파수 fs에서 동작하고 k2만이 fc와 Q 모두에 의존하기 때문에, k1 및 k2 계수 세트에 대한 전체 저장 요건들이 매우 작다(기껏해야 11x 16 x 2 워드에 불과하다).

A(z)에 대한 상술한 방정식으로부터, 그 계수들이 대칭임을 알 수 있다. 즉, 방정식은 아래와 같이 표현될 수 있다.

이때, 아래의 관계가 인정된다.

위 방정식에서 주어진 바와 같은 A(z)는 다음과 같은 차이 방정식을 제시한다.

이는 다음의 수식을 도출할 수 있다.

특정 일실시예에서, 상태 변수들은 x[k-2]에 대응하는 xv[0], x[k-1]에 대응하는 xv[1], y[k-2]에 대응하는 yv[0], y[k-1]에 대응하는 yv[1]의 형태로 어레이 xv와 yv에 저장될 수 있다. 다음의 코드-스니펫(code-snippet)은 단일 단계의 올패스 필터를 구현한다.

void allpass(float *xv, float *yv, float *input, float *output)

{

*output = geq_b0 * (*input - yv[0]) + geq_b1 * (xv[1] - yv[1]) + xv[0]

xv[0] = xv[1]; \\ update

xv[1] = *input; \\ update

yv[0] = yv[1]; \\update

yv[1] = *output; \\update

}

이제 이 루프는 위 방정식들에 따라 올패스 필터 둘레로 채택되어야 한다. 이는 아래와 같이 간단하게 구현될 수 있다.

void bell(float *xv, float *yv, float gain, float *input, float *output)

{

allpass(xv, yv, input, output);

*output = 0.5 * (1.0-gain) * (*output) + 0.5 * (1.0+gain) * (*input);

}

좀더 구체적으로, 앞서의 두 코드 스니펫들은 아래와 같은 단일 루틴으로 결합될 수 있다.

void bell(float *xv, float *yv, float gain, float *input, float *output)

{

float ap_output = geq_b0 * (*input - yv[0])

+ geq_b1 * (xv[1] - yv[1]) + xv[0]

xv[0] = xv[1]; \\ update

xv[1] = *input; \\ update

yv[0] = yv[1]; \\update

yv[1] = *output; \\update

*output = 0.5 * (1.0-gain) * ap_output + 0.5 * (1.0+gain) * (*input);

}

이제 일차 필터가 세부적으로 점검될 것이다. 이 필터들은 아래와 같은 전이 함수로 표시될 수 있다.

이는 아래의 차이 함수에 대응한다.

도 12는 본 발명의 일실시예에 따른 1차 필터의 DF1 구조를 도시한다. 도 12와 관련하여, 이 필터 구조의 멀티플라이어 계수들은 전이 함수와 차이 방정식의 계수들에 명확하게 대응한다. 디지털 필터의 출력은 아래와 같이 계산된다.

먼저, 상태 변수들 각각이 0으로 설정된다. 다시 말해서,

시간 k=0에서 다음의 연산이 수행된다(도 11 참조).

그후, 레지스터들이 업데이트되어 x[k-1]에 의해 표시된 레지스터가 x[0]을 홀딩하고, y[k-1]에 의해 표시된 레지스터는 y[0]을 홀딩한다.

시간 k=1에서, 다음의 연산이 수행된다.

그후, 레지스터 업데이트가 다시 연산되어 x[k-1]에 의해 표시된 레지스터가 x[1]을 홀딩하고, y[k-1]에 의해 표시된 레지스터는 y[1]을 홀딩한다.

이 프로세스는 그후 모든 순간 k에 대해 반복된다. 새로운 입력 x[k]가 들어오고, 새 출력 y[k]가 연산되며, 상태 변수들이 업데이트된다.

일반적으로, 디지털 필터링 연산은 데이터 스트림 x[0], x[1], x[2],... 등등의 데이터 스트림에 대해 수행되는 한 세트의 곱셈 및 덧셈으로 간주될 수 있다. 이때, 계수 b0, b1, a1과, 상태 변수 x[k-1], y[k-1] 을 이용하게 된다.

상술한 방정식들로 돌아가서, 1차 쉘프 필터가 아래의 방정식을 1차 올패스 필터 A(z)에 적용함으로서 생성될 수 있다.

일차 올패스 필터 A(z)는 아래와 같다.

이때, 아래와 같이 α가 선택된다.

이때, fc는 요망 코너 주파수이고, Fs는 샘플링 주파수다. 위 올패스 필터 A(z)는 아래의 차이 함수에 대응한다.

올패스 계수 α가 allpass_coeff로 표시되고, 방정식 항들을 재배열하면 위 방정식은 아래와 같이 표시된다.

디지털 신호 처리 방법(100)의 한가지 특정 소프트웨어 구현이 이제부터 세부적으로 제시될 것이다.

상술한 바와 같은 입력 신호 조정(101)과 출력 이득 조정(10)이 다음과 같이 구현되는 "스케일" 함수를 이용하여 실현될 수 있다.

void scale(gain, float *input, float *output)

{

for (i = 0; i < NSAMPLES; i++)

{

*output++ = inputGain * (*input++);

}

}

제 1 로우 쉘프 필터(102)와 제 2 로우 쉘프 필터(105)가 다음과 같이 구현되는 "low_shelf" 함수를 이용하여 실현될 수 있다.

void low_shelf(float *xv, float *yv, float *wpt, float *input, float *output)

{

float l;

int i;

for (i = 0; i < NSAMPLES; i++)

{

if (wpt[2] < 0.0) \\ cut mode, use conventional realization

{ \\ allpass_coef = alpha

yv[0] = ap_coef * (*input) + (ap_coef * ap_coef - 1.0) * xv[0];

xv[0] = ap_coef * xv[0] + *input;

*output++ = 0.5 * ((1.0 + wpt[0]) * (*input++) + (1.0 - wpt[0]) * yv[0]);

}

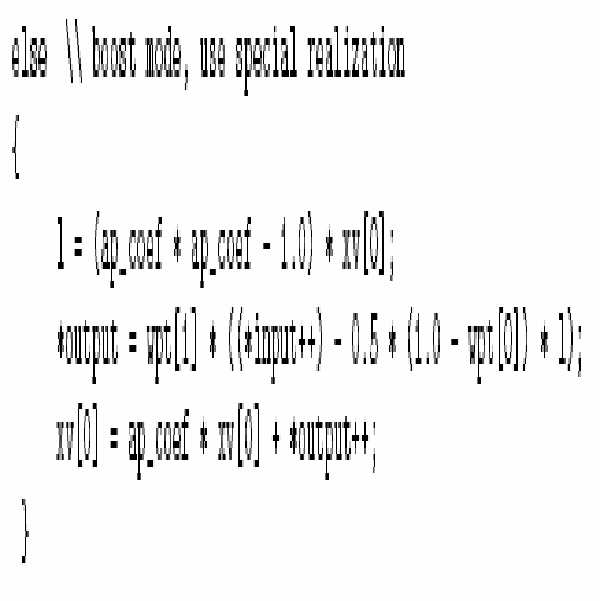

else \\ boost mode, use special realization

{

l = (ap_coef * ap_coef - 1.0) * xv[0];

*output = wpt[1] * ((*input++) - 0.5 * (1.0 - wpt[0]) * l);

xv[0] = ap_coef * xv[0] + *output++;

}

}

}

이 함수가 좀더 복잡해짐에 따라, 이에 대한 세부적 설명이 적절할 것이다. 먼저, 이 함수의 규정사항을 제시한다.

void low_shelf(float *xv, float *yv, float *wpt, float *input, float *output)

"low shelf" 함수는 다섯가지 부동소수점 어레이에 대한 포인터들을 파라미터로 취한다. 어레이 xv와 yv는 이 필터에 대한 "x" 및 "y" 상태 변수들을 가진다. 쉘프 필터들이 모두 1차 필터들이기 때문에, 상태 변수 어레이들이 1의 길 이(length 1)에 불과하다. 디지털 신호 처리 방법(100)에 사용되는 각각의 쉘프 필터에 대해 개별적인 "x"와 "y"의 상태 변수들이 존재한다. 사용되는 다음 어레이는 특정 쉘프 필터에 속한 필터 계수들 "wpt"의 어레이다. wpt는 3의 길이를 가지며, 이때, 원소 wpt[0], wpt[1], wpt[2] 는 다음을 표현한다.

α는 올패스 계수이고, G는 쉘프 필터 이득이다. α의 값은 모든 쉘프 필터에 대해 동일하다. 왜냐하면, 코너 주파수에 의해서만 결정되기 때문이다. 디지털 신호 처리 방법(100)의 모두 네개의 쉘프 필터들이 1kHz의 코너 주파수를 가진다는 점에 주목하여야 한다. G의 값은 각각의 쉘프 필터마다 서로 다르다.

어레이 "input"은 각각의 쉘프 필터에 대한 입력으로 공급되는 입력 샘플들의 블록이고, 필터 연산의 결과는 "output" 어레이에 저장된다.

다음의 두 코드 라인들은 한개의 루프 카운터 변수 i와 보조 양 l에 대해 공간을 할당한다. 보조 양 l은 도 9로부터 나타나는 양 l0[k]에 해당한다.

다음의 라인 코드,

는 총 NSAMPLES 회를 따르는 코드를 실행하며, 이때, NSAMPLES는 디지털 신호 처리 방법(100)에 사용되는 데이터 블록의 길이에 해당한다.

이어서 신뢰도 테스트가 이어진다.

앞서 언급한 방정식들을 돌아보면, wpt[2]<0은 컷 모드의 쉘프 필터에 대응하고, wpt[2]>=0은 부스트 모드의 쉘프 필터에 대응한다. 쉘프 필터가 컷 모드에 있을 경우, 다음의 코드가 수행된다.

xv[0]의 값은 단순히 상태 변수 x[k]에 해당하고, yv[0]은 yv[k]에 해당한다. 위 코드는 아래 방정식들의 구현에 지나지 않는다.

쉘프 필터가 컷 모드에 있을 경우 다음의 코드가 수행된다.

이는 아래의 방정식들을 구현한다.

제 1 하위 쉘프 필터(103)와 제 2 하이 쉘프 필터(106)는 다음과 같이 구현되는 "high-shelf" 함수를 이용함으로서 실현될 수 있다.

void high_shelf(float *xv, float *yv, float *wpt, float *input, float *output)

{

float l;

int i;

for (i = 0; i < NSAMPLES; i++)

{

if (wpt[2] < 0.0) \\ cut mode, use conventional realization,

{ \\ allpass_coef = alpha

yv[0] = allpass_coef * (*input) + (allpass_coef * allpass_coef - 1.0) * xv[0];

xv[0] = allpass_coef * xv[0] + *input;

*output++ = 0.5 * ((1.0 + wpt[0]) * (*input++) - (1.0 - wpt[0]) * yv[0]);

}

else \\ boost mode, use special realization

{

l = (allpass_coef * allpass_coef - 1.0) * xv[0];

*output = wpt[1] * ((*input++) + 0.5 * (1.0 - wpt[0]) * l);

xv[0] = allpass_coef * xv[0] + *output++;

}

}

}

하이 쉘프 필터의 구현은 로우 쉘프 필터의 구현과 전혀 다른 것이 없다. 위 두 함수들을 비교해보면, 실질적인 유일한 차이점은 단일 계수의 부호에 있다. 따라서, 프로그램 진행이 동일하다.

그래픽 이퀄라이저(107)는 아래와 같이 구현되는 "bell" 필터 함수에 대한 11개의 콜을 이용하여 구현될 수 있다.

void bell(float *xv, float *yv, float *wpt, float *input, float *output)

{

float geq_gain = wpt[0]; \\ G

float geq_b0 = wpt[1]; \\ k2

float geq_b1 = wpt[2]; \\ k1(1+k2)

float ap_output;

int i;

for (i = 0; i < NSAMPLES; i++)

{

ap_output = geq_b0 * (*input - yv[0]) + geq_b1 * (xv[1] - yv[1]) + xv[0];

xv[0] = xv[1]; \\ update

xv[1] = *input; \\ update

yv[0] = yv[1]; \\update

yv[1] = *output; \\update

*output++ = 0.5 * (1.0-gain) * ap_output + 0.5 * (1.0+gain) * (*input++);

}

}

이 함수 bell()은 어레이 xv("x" 상태 변수), yv("y" 상태 변수), wpt(그래픽 EQ 파라미터 G, k2, k1(1+k2) 포함), 입력 샘플들의 블록 "input", 그리고 출력 샘플의 저장 장소에 대한 포인터들을 아규먼트로 취한다. 위 코드 스니펫의 첫번째 네개의 문장들은 간단한 아규먼트 문장으로서 별도의 설명이 필요치 않다.

for 루프는 NSMAPLES 횟수만큼 실행되며, NSAMPLES는 입력 데이터의 블록의 크기에 해당한다. 다음 문장은 아래의 과정에 해당한다.

위 문장은 상술한 바와 같이 올패스 필터의 출력을 연산한다. 다음의 네개의 문장들은 다음의 과정에 해당한다.

이는 x[k - 1]에 저장된 값을 x[k - 2]로 이동시킨다.

이는 입력 [k]의 값을 to x[k - 1]로 이동시킨다.

이는 y[k - 1]에 저장된 값을 y[k - 2] 로 이동시킨다.

이는 올패스 필터의 출력인 output[k]의 값을 y[k-1]로 이동시킨다.

마지막으로, 벨 필터의 출력은 다음과 같이 연산된다.

제 1 컴프레서(104)와 제 2 컴프레서(108)는 다음과 같이 "compressor" 함수를 이용하여 구현될 수 있다.

void compressor(float *input, float *output, float *wpt, int index)

{

static float level;

float interp, GR, excessGain, L, invT, ftempabs;

invT = wpt[2];

int i, j;

for (i = 0; i < NSAMPLES; i ++)

{

ftempabs = fabs(*input++);

level = (ftempabs >= level)? wpt[0] * (level - ftempabs) +

ftempabs : wpt[1] * (level - ftempabs) + ftempabs;

GR = 1.0;

if (level * invT > 1.0)

{

excessGain = level *invT;

interp = excessGain - trunc(excessGain);

j = (int) trunc(excessGain) - 1;

if (j < 99)

{

GR = table[index][j] + interp * (table[index][j+1] - table[index][j]);

// table[][] is the exponentiation table

}

else

{

GR = table[index][99];

}

}

*output++ = *input++ * GR;

}

}

컴프레서 함수는 입력, 출력, wpt 어레이, 그리고 정수, 인덱스에 대한 아규먼트 포인터들을 입력으로 취한다. 입력 및 출력 어레이들이 입력 및 출력 데이터의 블록용으로 사용된다. 첫번째 코드 라인,

은 함수에 대한 콜들 간에 연산된 신호 레벨을 유지하는 "level"이라 불리는 값에 대한 정적 저장공간을 할당한다. 이는 레벨이 연속적으로 검색되어야할 필요가 있는 것이기 때문이다. 즉, 단일 블록 데이터의 실행 중에서만이 아니라 프로그램의 전체 구간에 대해서 검색되어야 하기 때문이다.

다음 코드 라인,

은 컴프레서 알고리즘의 연산 중 사용되는 몇개의 양들에 대한 임시 저장소를 할당한다. 이 양들은 블록 단위로 필요할 뿐이며, 각각이 함수를 통과한 후 이양들이 폐기될 수 있다.

다음 코드 라인,

은 컴프레서 임계값의 역수를 추출하여, 이 역수는 wpt[2]에 저장되고, wpt 어레이의 세번째 원소에 해당한다. wpt 어레이의 나머지 원소들은 어택 시간, 릴리 스 시간, 컴프레서 비를 포함한다.

다음 코드 라인은 컴프레서 루프가 NSAMPLES 만큼 반복됨을 표시한다. 다음의 두 코드 라인은 상술한 방정식들에 따른 레벨 연산을 구현한다. 이를 살펴보기 위해, 이 라인의 아래와 같은 사항을 살펴보자.

이 라인은 아래의 확장 문장에 해당한다.

이는 위 필요한 방정식을 수행하는 데 필요한 것이다. 이때, wpt[0]은 어택 상수 αatt를 저장하고, wpt[1]은 릴리스 상수 αrel를 저장한다.

그후, 이득 감소 GR이 단위값과 같다고 가정할 수 있다. 그후, 비교 과정이 수행된다.

이는 level > T 인 지를 묻는 것과 동일한 것이다. 즉, 신호 레벨이 임계치보다 높은 지를 묻는 것과 동일한 것이다. 그렇지 않을 경우, 아무것도 수행되지 않는다. 신호 레벨이 임계치보다 높을 경우, 이득 감소가 연산된다. 먼저, 초과 이득이 다음과 같이 연산된다.

이는 위 방정식들을 이용하여 연산된 바와 같다. 다음의 두 문장,

은 위 방정식들에 따라 지수함수적 값들의 표로 인덱스 값을 연산한다.

다음 라인들,

은 앞서 설명한 보간을 구현한다. 2차원 어레이 "table"은 두개의 인덱스로 파라미터화된다. 즉, index와 j로 파라미터화된다. 값 j는 초과 이득의 가장 가까운 정수 값이다. 이 표는 다음과 같은 값을 가진다.

이는 앞서 설명한 방정식들로부터 필요한 값으로 인식될 수 있다. 이때, "floor" 연산은 필요치 않다. 왜냐하면 j가 정수값이기 때문이다. 마지막으로, 입력은 다음과 같이 연산된 이득 감소 GR에 의해 스케일링된다.

이 값은 출력 어레이에서의 다음 위치에 기입되고, 입력 블록의 모든 NSAMPLES 값들이 소모될 때까지 이 프로세스가 입력 어레이 내 다음 값으로 계속된 다.

실제로, 앞서 언급한 각각의 함수가 한 순간의 단일 샘플보다는 입력 및 출력 데이터의 어레이를 취급하고 있음을 주목하여야 한다. 이는 프로그램을 크게 실제로 변화시키는 것이 아니다. 이는 위 루틴들이 참조에 의해 그 입력 및 출력을 통과시킨 경우를 힌트로 하여 파악할 수 있다. 이 알고리즘이 NSAMPLES들의 길이에 해당하는 블록을 취급한다고 가정할 때, 데이터의 어레이들을 벨-필터 함수에 채택하는 데 필요한 수정사항은 코드로의 루핑을 다음과 같이 이용하는 것이다.

void bell(float *xv, float *yv, float gain, float *input, float *output)

{

float ap_output;

int i;

for (i = 0; i < NSAMPLES; i++)

{

ap_output = geq_b0 * (*input - yv[0])

+ geq_b1 * (xv[1] - yv[1]) + xv[0]

xv[0] = xv[1]; \\ update

xv[1] = *input; \\ update

yv[0] = yv[1]; \\update

yv[1] = *output; \\update

*output++ = 0.5 * (1.0-gain) * ap_output + 0.5 * (1.0+gain) * (*input++);

}

}

디지털 신호 처리 방법(100)은 전체적으로 볼 때, 다음과 같이 위 함수들 각각을 호출하는 프로그램으로 구현될 수 있다.

// it is assumed that floatBuffer contains a block of

// NSAMPLES samples of floating-point data.

// The following code shows the instructions that

// are executed during a single pass

scale(inputGain, floatBuffer, floatBuffer);

low_shelf(xv1_ap, yv1_ap, &working_table[0], floatBuffer, floatBuffer);

high_shelf(xv2_ap, yv2_ap, &working_table[3], floatBuffer, floatBuffer);

compressor(floatBuffer, floatBuffer, &working_table[6], ratio1Index);

low_shelf(xv3_ap_left, yv3_ap_left, xv3_ap_right, yv3_ap_right, &working_table[11], floatBuffer, floatBuffer);

high_shelf(xv4_ap_left, yv4_ap_left, xv4_ap_right, yv4_ap_right, &working_table[14], floatBuffer, floatBuffer);

bell(xv1_geq, yv1_geq, &working_table[17], floatBuffer, floatBuffer);

bell(xv2_geq, yv2_geq, &working_table[20], floatBuffer, floatBuffer);

bell(xv3_geq, yv3_geq, &working_table[23], floatBuffer, floatBuffer);

bell(xv4_geq, yv4_geq, &working_table[26], floatBuffer, floatBuffer);

bell(xv5_geq, yv5_geq, &working_table[29], floatBuffer, floatBuffer);

bell(xv6_geq, yv6_geq, &working_table[32], floatBuffer, floatBuffer);

bell(xv7_geq, yv7_geq, &working_table[35], floatBuffer, floatBuffer);

bell(xv8_geq, yv8_geq, &working_table[38], floatBuffer, floatBuffer);

bell(xv9_geq, yv9_geq, &working_table[41], floatBuffer, floatBuffer);

bell(xv10_geq, yv10_geq, &working_table[44], floatBuffer, floatBuffer);

bell(xv11_geq, yv11_geq, &working_table[47], floatBuffer, floatBuffer);

compressor(floatBuffer, floatBuffer, &working_table[50], ratio1Index);

scale(outputGain, floatBuffer, floatBuffer);

위에 제시된 바와 같이, scale 함수, low_shelf 함수, high_shelf 함수, bell 함수, 그리고 compressor 함수에 대한 복수개의 콜이 존재한다. 더우기, xv1, yv1, xv2, yv2, 등등과 같은 어레이에 대한 참조들이 존재한다. 이 어레이들은 다양한 루틴들에 대한 콜들 간에 유지될 필요가 있는 상태 변수들이며, 프로세스 내 다양한 필터들의 내부 상태를 저장한다. working_table이라 불리는 어레이에 대한 반복된 참조 역시 존재한다. 이 표는 알고리즘 전반에 사용되는 기연산된 다양한 계수들을 홀딩한다. 디지털 신호 처리 방법(100)의 본 실시예같은 알고리즘들은 두 부분으로 나누어질 수 있다. 즉, 실시간 처리 루프에 사용되는 계수들의 연산과, 실시간 처리 루프 자체로 나누어질 수 있다. 실시간 루프는 단순한 곱셈과 덧셈으로 이루어지며, 이들은 실시간 수행이 간단한 편이다. 계수 연산은 복잡한 초월 함수, 삼각 함수, 그리고 그외 다른, 실시간 수행이 효과적이지 못한 연산들을 필요로한다. 다행스럽게도, 계수들이 런타임 중 정적이며, 실시간 처리 이전에 미리 연산될 수 있다. 이 계수들은 디지털 신호 처리 방법을 이용할 각각의 오디오 장치에 대해 구체적으로 연산될 수 있다. 구체적으로, 디지털 신호 처리 방법(100)이 차량용으로 구성된 모바일 오디오 장치에 사용될 경우, 이 계수들은 각각의 차량에 대해 개별적으로 연산될 수 있고, 오디오 장치들은 스피커 배치, 승객 구획 설계, 배경 잡음 등등과 같은 각 차량의 고유 음향 성질을 위해, 그리고, 최적 성능을 얻기 위해 사용될 수 있다.

예를 들어, 특정 청취 환경이 정상파로부터의 응답같은 이러한 아날로그적인 오디오 응답을 생성할 수 있다. 가령, 이러한 정상파들은 자동차같은 좁은 청취 환경에서 자주 나타난다. 자동차의 길이는 약 400 사이클 길이에 해당한다. 이러한 환경에서 일부 정상파는 이 주파수에서 설정되고 일부는 그 아래로 설정된다. 정상파들은 신경에 거슬리는 음향 신호를 제시할 수 있는 주파수에서 증폭된 신호를 제시한다. 동일 모델의 차처럼, 동일한 특성을 가지면서 동일한 크기 형태를 가진 차량들은 그들의 유사한 크기, 형태, 구조적 배치, 스피커 배치, 스피커 품질, 그리 고 스피커 크기 등등으로 인해 동일한 변칙성을 제시할 수 있다. 추가적인 일실시예에서, 수행되는 조정의 빈도 및 크기는 청취 환경에서의 차후 제안을 위해 변칙적인 응답을 감소시키기 위해 그래픽 이퀄라이저(107)에 사용되도록 미리 설정되어 저장될 수 있다.

이전 섹션에서 제시된 "working tables"(작업표)는 메모리에 저장되어 필요시 불러들일 수 있는 기연산된 값들로 구성된다. 이는 런타임시 상당한 연산양을 절감하게 되고, 디지털 신호 처리 방법(100)이 저렴한 디지털 신호 처리 칩으로도 실현될 수 있게 한다.

본 섹션에서 상세하게 제시한 알고리즘이 블록 형태로 쓰여진다는 점에 주목하여야 한다. 앞서 설명한 프로그램은 디지털 신호 처리 방법(`100)의 단순한 특정 소프트웨어 실시예에 지나지 않으며, 본 발명을 어떤 방식으로든 제한하고자 하는 것이 아니다. 이 소프트웨어 실시예는 라디오, MP3 플레이어, 게임기, 셀 폰, TV, 컴퓨터, 퍼블릭 어드레스 시스템 등등과 같은 오디오 장치에 사용하기 위한 컴퓨터 칩에 프로그래밍될 수 있다. 이 소프트웨어 실시예는 입력으로 오디오 신호를 취하여 수정된 형태로 이 오디오 신호를 출력하는 효과를 가진다.

Claims (25)

- 신호의 이득을 첫번째로 조정하는 단계와,조정된 신호를 제 1 로우 쉘프 필터로 필터링하는 단계와,필터링된 신호를 제 1 컴프레서로 압축하는 단계와,이 신호를 그래픽 이퀄라이저로 처리하는 단계와,처리된 신호를 제 2 컴프레서로 압축하는 단계와,압축된 신호의 이득을 두번째로 조정하는 단계와,이 신호를 출력하는 단계를 포함하며,필터링된 신호를 제 1 컴프레서로 압축하기 전에, 제 1 로우 쉘프 필터로부터 수신한 신호를 제 1 하이 쉘프 필터로 필터링하는 단계와,신호를 그래픽 이퀄라이저로 처리하기 전에, 제 2 로우 쉘프 필터로 신호를 필터링하는 단계와,신호가 제 2 로우 쉘프 필터로 필터링된 후, 신호를 제 2 하이 쉘프 필터로 필터링하는 단계를 추가로 포함하는 것을 특징으로 하는 신호 처리 방법.

- 삭제

- 제 1 항에 있어서, 신호가 오디오 신호인 것을 특징으로 하는 신호 처리 방 법.

- 제 1 항에 있어서, 수신한 신호의 이득을 첫번째로 조정하는 단계는, 제 1 이득 증폭기를 이용하여 수행되고, 신호의 이득을 두번째로 조정하는 단계는 제 2 이득 증폭기를 이용하여 수행되는 것을 특징으로 하는 신호 처리 방법.

- 제 1 항에 있어서, 제 1 로우 쉘프 필터의 컷오프 주파수가 1000 Hz 인 것을 특징으로 하는 신호 처리 방법.

- 제 1 항에 있어서, 제 1 하이 쉘프 필터의 컷오프 주파수가 1000 Hz 인 것을 특징으로 하는 신호 처리 방법.

- 제 1 항에 있어서, 상기 그래픽 이퀄라이저가 직렬연결된 11개의 2차 필터들을 포함하는 것을 특징으로 하는 신호 처리 방법.

- 제 7 항에 있어서, 각각의 2차 필터가 벨 필터인 것을 특징으로 하는 신호 처리 방법.

- 제 8 항에 있어서, 직렬연결된 11개의 2차 필터 중 첫번째 2차 필터의 중심 주파수는 30 Hz 이고, 11개의 2차 필터 중 마지막 2차 필터의 중심 주파수는 16,000 Hz 인 것을 특징으로 하는 신호 처리 방법.

- 제 9 항에 있어서, 두번째부터 열번째까지의 2차 필터들의 중심 주파수는 서로 1 옥타브 간격을 가지는 것을 특징으로 하는 신호 처리 방법.

- 제 1 항에 있어서, 제 2 로우 쉘프 필터는 크기-보완형 로우 쉘프 필터인 것을 특징으로 하는 신호 처리 방법.

- 신호를 증폭시키도록 구성된 제 1 이득 증폭기와,증폭된 신호를 필터링시키도록 구성된 제 1 로우 쉘프 필터와,필터링된 신호를 압축하도록 구성된 제 1 컴프레서와,상기 필터링된 신호를 처리하도록 구성된 그래픽 이퀄라이저와,처리된 신호를 제 2 컴프레서로 압축하도록 구성된 제 2 컴프레서와,상기 제 2 컴프레서에 의해 압축된 신호의 이득을 증폭시키면서 출력 신호를 출력하도록 구성된 제 2 이득 증폭기를 포함하며,필터링된 신호를 제 1 컴프레서로 압축하기 전에, 제 1 로우 쉘프 필터로부터 수신한 신호를 필터링시키도록 구성되는 제 1 하이 쉘프 필터와,신호를 그래픽 이퀄라이저로 처리하기 전에, 수신한 신호를 필터링하도록 구성된 제 2 로우 쉘프 필터와,제 2 로우 쉘프 필터로 필터링한 후, 신호를 필터링하도록 구성된 제 2 하이 쉘프 필터를 추가로 포함하는 것을 특징으로 하는 스피커 시스템.

- 삭제

- 제 12 항에 있어서, 신호가 오디오 신호인 것을 특징으로 하는 스피커 시스템.

- 제 12 항에 있어서, 제 1 로우 쉘프 필터의 컷오프 주파수가 1000 Hz 인 것을 특징으로 하는 스피커 시스템.

- 제 12 항에 있어서, 제 1 하이 쉘프 필터의 컷오프 주파수가 1000 Hz 인 것을 특징으로 하는 스피커 시스템.

- 제 12 항에 있어서, 상기 그래픽 이퀄라이저가 직렬연결된 11개의 2차 필터들을 포함하는 것을 특징으로 하는 스피커 시스템.

- 제 17 항에 있어서, 각각의 2차 필터가 벨 필터인 것을 특징으로 하는 스피커 시스템.

- 제 18 항에 있어서, 직렬연결된 11개의 2차 필터 중 첫번째 2차 필터의 중심 주파수는 30 Hz 이고, 11개의 2차 필터 중 마지막 2차 필터의 중심 주파수는 16,000 Hz 인 것을 특징으로 하는 스피커 시스템.

- 제 19 항에 있어서, 두번째부터 열번째까지의 2차 필터들의 중심 주파수는 서로 1 옥타브 간격을 가지는 것을 특징으로 하는 스피커 시스템.

- 제 12 항에 있어서, 제 2 로우 쉘프 필터는 크기-보완형 로우 쉘프 필터인 것을 특징으로 하는 스피커 시스템.

- 삭제

- 삭제

- 삭제

- 삭제

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US86171106P | 2006-11-30 | 2006-11-30 | |

| US60/861,711 | 2006-11-30 | ||

| PCT/US2007/085919 WO2008067454A2 (en) | 2006-11-30 | 2007-11-29 | System and method for digital signal processing |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20090101209A KR20090101209A (ko) | 2009-09-24 |

| KR101503541B1 true KR101503541B1 (ko) | 2015-03-18 |

Family

ID=39468718

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020097013533A KR101503541B1 (ko) | 2006-11-30 | 2007-11-29 | 디지털 신호 처리 시스템 및 방법 |

Country Status (14)

| Country | Link |

|---|---|

| EP (1) | EP2095513B1 (ko) |

| JP (1) | JP5048782B2 (ko) |

| KR (1) | KR101503541B1 (ko) |

| CN (1) | CN101589429B (ko) |

| AU (1) | AU2007325096B2 (ko) |

| BR (1) | BRPI0719552A2 (ko) |

| CA (1) | CA2670973C (ko) |

| DK (1) | DK2095513T3 (ko) |

| IL (1) | IL198914A (ko) |

| MX (1) | MX2009005699A (ko) |

| NO (1) | NO341534B1 (ko) |

| NZ (1) | NZ577201A (ko) |

| RU (1) | RU2483363C2 (ko) |

| WO (1) | WO2008067454A2 (ko) |

Cited By (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9195433B2 (en) | 2006-02-07 | 2015-11-24 | Bongiovi Acoustics Llc | In-line signal processor |

| US9276542B2 (en) | 2004-08-10 | 2016-03-01 | Bongiovi Acoustics Llc. | System and method for digital signal processing |

| US9281794B1 (en) | 2004-08-10 | 2016-03-08 | Bongiovi Acoustics Llc. | System and method for digital signal processing |

| US9344828B2 (en) | 2012-12-21 | 2016-05-17 | Bongiovi Acoustics Llc. | System and method for digital signal processing |

| US9348904B2 (en) | 2006-02-07 | 2016-05-24 | Bongiovi Acoustics Llc. | System and method for digital signal processing |

| US9398394B2 (en) | 2013-06-12 | 2016-07-19 | Bongiovi Acoustics Llc | System and method for stereo field enhancement in two-channel audio systems |

| US9397629B2 (en) | 2013-10-22 | 2016-07-19 | Bongiovi Acoustics Llc | System and method for digital signal processing |

| US9413321B2 (en) | 2004-08-10 | 2016-08-09 | Bongiovi Acoustics Llc | System and method for digital signal processing |

| US9564146B2 (en) | 2014-08-01 | 2017-02-07 | Bongiovi Acoustics Llc | System and method for digital signal processing in deep diving environment |

| US9621994B1 (en) | 2015-11-16 | 2017-04-11 | Bongiovi Acoustics Llc | Surface acoustic transducer |

| US9615813B2 (en) | 2014-04-16 | 2017-04-11 | Bongiovi Acoustics Llc. | Device for wide-band auscultation |

| US9638672B2 (en) | 2015-03-06 | 2017-05-02 | Bongiovi Acoustics Llc | System and method for acquiring acoustic information from a resonating body |

| US9741355B2 (en) | 2013-06-12 | 2017-08-22 | Bongiovi Acoustics Llc | System and method for narrow bandwidth digital signal processing |

| US9883318B2 (en) | 2013-06-12 | 2018-01-30 | Bongiovi Acoustics Llc | System and method for stereo field enhancement in two-channel audio systems |

| US9906858B2 (en) | 2013-10-22 | 2018-02-27 | Bongiovi Acoustics Llc | System and method for digital signal processing |

| US9906867B2 (en) | 2015-11-16 | 2018-02-27 | Bongiovi Acoustics Llc | Surface acoustic transducer |

| US10069471B2 (en) | 2006-02-07 | 2018-09-04 | Bongiovi Acoustics Llc | System and method for digital signal processing |

| US10158337B2 (en) | 2004-08-10 | 2018-12-18 | Bongiovi Acoustics Llc | System and method for digital signal processing |

| US10639000B2 (en) | 2014-04-16 | 2020-05-05 | Bongiovi Acoustics Llc | Device for wide-band auscultation |

| US10701505B2 (en) | 2006-02-07 | 2020-06-30 | Bongiovi Acoustics Llc. | System, method, and apparatus for generating and digitally processing a head related audio transfer function |

| US10820883B2 (en) | 2014-04-16 | 2020-11-03 | Bongiovi Acoustics Llc | Noise reduction assembly for auscultation of a body |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11431312B2 (en) | 2004-08-10 | 2022-08-30 | Bongiovi Acoustics Llc | System and method for digital signal processing |

| US8565449B2 (en) * | 2006-02-07 | 2013-10-22 | Bongiovi Acoustics Llc. | System and method for digital signal processing |

| US10848118B2 (en) | 2004-08-10 | 2020-11-24 | Bongiovi Acoustics Llc | System and method for digital signal processing |

| US9615189B2 (en) | 2014-08-08 | 2017-04-04 | Bongiovi Acoustics Llc | Artificial ear apparatus and associated methods for generating a head related audio transfer function |

| US11202161B2 (en) | 2006-02-07 | 2021-12-14 | Bongiovi Acoustics Llc | System, method, and apparatus for generating and digitally processing a head related audio transfer function |

| US10848867B2 (en) | 2006-02-07 | 2020-11-24 | Bongiovi Acoustics Llc | System and method for digital signal processing |

| US9741350B2 (en) * | 2013-02-08 | 2017-08-22 | Qualcomm Incorporated | Systems and methods of performing gain control |

| CN103312322B (zh) * | 2013-05-16 | 2016-08-17 | 中国电子科技集团公司第四十一研究所 | 一种本振电路及本振信号产生方法 |

| CN104363002B (zh) * | 2014-08-15 | 2017-07-21 | 广州电蟒信息技术有限公司 | 一种基于数字均衡器通过参数变换对音效进行处理的方法 |

| CA3096877A1 (en) | 2018-04-11 | 2019-10-17 | Bongiovi Acoustics Llc | Audio enhanced hearing protection system |

| CN108776259B (zh) * | 2018-06-26 | 2020-03-24 | 电子科技大学 | 基于数字带宽限制技术的功率分析仪 |

| WO2020028833A1 (en) | 2018-08-02 | 2020-02-06 | Bongiovi Acoustics Llc | System, method, and apparatus for generating and digitally processing a head related audio transfer function |

| CN110545350B (zh) * | 2019-07-17 | 2020-10-30 | 浙江工业大学 | 一种在手机免提状态下增加音频播放音量的方法 |

| DE102019005855B4 (de) * | 2019-08-20 | 2021-03-18 | Christoph Kemper | Verfahren zum Anpassen eines Klangwandlers an einen Referenzklangwandler |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4184047A (en) * | 1977-06-22 | 1980-01-15 | Langford Robert H | Audio signal processing system |

| US4696044A (en) * | 1986-09-29 | 1987-09-22 | Waller Jr James K | Dynamic noise reduction with logarithmic control |

| US5210806A (en) * | 1989-11-07 | 1993-05-11 | Pioneer Electronic Corporation | Digital audio signal processing apparatus |

| JP2005500768A (ja) * | 2001-08-15 | 2005-01-06 | アップル・コンピューター・インコーポレーテッド | スピーカ周波数特性補償ツール |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5530888U (ko) * | 1978-08-21 | 1980-02-28 | ||

| US4356558A (en) * | 1979-12-20 | 1982-10-26 | Martin Marietta Corporation | Optimum second order digital filter |

| US4538297A (en) * | 1983-08-08 | 1985-08-27 | Waller Jr James | Aurally sensitized flat frequency response noise reduction compansion system |

| SU1319288A1 (ru) * | 1985-12-29 | 1987-06-23 | Всесоюзный научно-исследовательский институт радиовещательного приема и акустики им.А.С.Попова | Цифровое устройство регулировани динамического диапазона звукового сигнала |

| JPH1073815A (ja) * | 1996-06-19 | 1998-03-17 | Seiko Instr Inc | 反射型液晶表示装置 |

| US5990955A (en) * | 1997-10-03 | 1999-11-23 | Innovacom Inc. | Dual encoding/compression method and system for picture quality/data density enhancement |

| EP0935342A3 (en) * | 1998-01-15 | 2001-05-16 | Texas Instruments Incorporated | Improvements in or relating to filters |

| US20030216907A1 (en) * | 2002-05-14 | 2003-11-20 | Acoustic Technologies, Inc. | Enhancing the aural perception of speech |

| WO2003104924A2 (en) * | 2002-06-05 | 2003-12-18 | Sonic Focus, Inc. | Acoustical virtual reality engine and advanced techniques for enhancing delivered sound |

| US7676048B2 (en) * | 2004-05-14 | 2010-03-09 | Texas Instruments Incorporated | Graphic equalizers |

| WO2006020427A2 (en) * | 2004-08-10 | 2006-02-23 | Anthony Bongiovi | System for and method of audio signal processing for presentation in a high-noise environment |

| US20070253577A1 (en) * | 2006-05-01 | 2007-11-01 | Himax Technologies Limited | Equalizer bank with interference reduction |

-

2007

- 2007-11-29 RU RU2009120382/08A patent/RU2483363C2/ru active

- 2007-11-29 CN CN200780050323XA patent/CN101589429B/zh active Active

- 2007-11-29 WO PCT/US2007/085919 patent/WO2008067454A2/en active Application Filing

- 2007-11-29 BR BRPI0719552-4A patent/BRPI0719552A2/pt not_active IP Right Cessation

- 2007-11-29 KR KR1020097013533A patent/KR101503541B1/ko active IP Right Grant

- 2007-11-29 EP EP07864902.7A patent/EP2095513B1/en active Active

- 2007-11-29 JP JP2009539481A patent/JP5048782B2/ja not_active Expired - Fee Related

- 2007-11-29 MX MX2009005699A patent/MX2009005699A/es active IP Right Grant

- 2007-11-29 AU AU2007325096A patent/AU2007325096B2/en not_active Ceased

- 2007-11-29 DK DK07864902.7T patent/DK2095513T3/en active

- 2007-11-29 NZ NZ577201A patent/NZ577201A/en not_active IP Right Cessation

- 2007-11-29 CA CA2670973A patent/CA2670973C/en active Active

-

2009

- 2009-05-24 IL IL198914A patent/IL198914A/en active IP Right Grant

- 2009-06-24 NO NO20092403A patent/NO341534B1/no not_active IP Right Cessation

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4184047A (en) * | 1977-06-22 | 1980-01-15 | Langford Robert H | Audio signal processing system |

| US4696044A (en) * | 1986-09-29 | 1987-09-22 | Waller Jr James K | Dynamic noise reduction with logarithmic control |

| US5210806A (en) * | 1989-11-07 | 1993-05-11 | Pioneer Electronic Corporation | Digital audio signal processing apparatus |

| JP2005500768A (ja) * | 2001-08-15 | 2005-01-06 | アップル・コンピューター・インコーポレーテッド | スピーカ周波数特性補償ツール |

Cited By (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9276542B2 (en) | 2004-08-10 | 2016-03-01 | Bongiovi Acoustics Llc. | System and method for digital signal processing |

| US9281794B1 (en) | 2004-08-10 | 2016-03-08 | Bongiovi Acoustics Llc. | System and method for digital signal processing |

| US10158337B2 (en) | 2004-08-10 | 2018-12-18 | Bongiovi Acoustics Llc | System and method for digital signal processing |

| US9413321B2 (en) | 2004-08-10 | 2016-08-09 | Bongiovi Acoustics Llc | System and method for digital signal processing |

| US9195433B2 (en) | 2006-02-07 | 2015-11-24 | Bongiovi Acoustics Llc | In-line signal processor |

| US9348904B2 (en) | 2006-02-07 | 2016-05-24 | Bongiovi Acoustics Llc. | System and method for digital signal processing |

| US9350309B2 (en) | 2006-02-07 | 2016-05-24 | Bongiovi Acoustics Llc. | System and method for digital signal processing |

| US10069471B2 (en) | 2006-02-07 | 2018-09-04 | Bongiovi Acoustics Llc | System and method for digital signal processing |

| US10701505B2 (en) | 2006-02-07 | 2020-06-30 | Bongiovi Acoustics Llc. | System, method, and apparatus for generating and digitally processing a head related audio transfer function |

| US9793872B2 (en) | 2006-02-07 | 2017-10-17 | Bongiovi Acoustics Llc | System and method for digital signal processing |

| US9344828B2 (en) | 2012-12-21 | 2016-05-17 | Bongiovi Acoustics Llc. | System and method for digital signal processing |

| US9883318B2 (en) | 2013-06-12 | 2018-01-30 | Bongiovi Acoustics Llc | System and method for stereo field enhancement in two-channel audio systems |

| US9741355B2 (en) | 2013-06-12 | 2017-08-22 | Bongiovi Acoustics Llc | System and method for narrow bandwidth digital signal processing |

| US9398394B2 (en) | 2013-06-12 | 2016-07-19 | Bongiovi Acoustics Llc | System and method for stereo field enhancement in two-channel audio systems |

| US10313791B2 (en) | 2013-10-22 | 2019-06-04 | Bongiovi Acoustics Llc | System and method for digital signal processing |

| US9906858B2 (en) | 2013-10-22 | 2018-02-27 | Bongiovi Acoustics Llc | System and method for digital signal processing |

| US9397629B2 (en) | 2013-10-22 | 2016-07-19 | Bongiovi Acoustics Llc | System and method for digital signal processing |

| US9615813B2 (en) | 2014-04-16 | 2017-04-11 | Bongiovi Acoustics Llc. | Device for wide-band auscultation |

| US10820883B2 (en) | 2014-04-16 | 2020-11-03 | Bongiovi Acoustics Llc | Noise reduction assembly for auscultation of a body |

| US10639000B2 (en) | 2014-04-16 | 2020-05-05 | Bongiovi Acoustics Llc | Device for wide-band auscultation |

| US9564146B2 (en) | 2014-08-01 | 2017-02-07 | Bongiovi Acoustics Llc | System and method for digital signal processing in deep diving environment |

| US9638672B2 (en) | 2015-03-06 | 2017-05-02 | Bongiovi Acoustics Llc | System and method for acquiring acoustic information from a resonating body |

| US9998832B2 (en) | 2015-11-16 | 2018-06-12 | Bongiovi Acoustics Llc | Surface acoustic transducer |

| US9906867B2 (en) | 2015-11-16 | 2018-02-27 | Bongiovi Acoustics Llc | Surface acoustic transducer |

| US9621994B1 (en) | 2015-11-16 | 2017-04-11 | Bongiovi Acoustics Llc | Surface acoustic transducer |

Also Published As

| Publication number | Publication date |

|---|---|

| NO341534B1 (no) | 2017-12-04 |

| IL198914A (en) | 2014-04-30 |

| WO2008067454A2 (en) | 2008-06-05 |

| NZ577201A (en) | 2012-06-29 |

| RU2009120382A (ru) | 2011-01-10 |

| EP2095513A2 (en) | 2009-09-02 |

| CN101589429A (zh) | 2009-11-25 |

| CN101589429B (zh) | 2013-05-22 |

| NO20092403L (no) | 2009-08-21 |

| RU2483363C2 (ru) | 2013-05-27 |

| MX2009005699A (es) | 2009-11-10 |

| BRPI0719552A2 (pt) | 2014-04-29 |

| IL198914A0 (en) | 2010-02-17 |

| EP2095513B1 (en) | 2016-10-19 |

| CA2670973C (en) | 2016-10-11 |

| AU2007325096B2 (en) | 2012-01-12 |

| EP2095513A4 (en) | 2014-06-25 |

| KR20090101209A (ko) | 2009-09-24 |

| CA2670973A1 (en) | 2008-06-05 |

| DK2095513T3 (en) | 2016-12-12 |

| WO2008067454A3 (en) | 2008-08-07 |

| JP2010512067A (ja) | 2010-04-15 |

| JP5048782B2 (ja) | 2012-10-17 |

| AU2007325096A1 (en) | 2008-06-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101503541B1 (ko) | 디지털 신호 처리 시스템 및 방법 | |

| AU2012202127B2 (en) | System and method for digital signal processing | |

| US8160274B2 (en) | System and method for digital signal processing | |

| CA2785743C (en) | System and method for digital signal processing | |

| US9281794B1 (en) | System and method for digital signal processing | |

| US10291195B2 (en) | System and method for digital signal processing | |

| US8229136B2 (en) | System and method for digital signal processing | |

| US8705765B2 (en) | Ringtone enhancement systems and methods | |

| US10158337B2 (en) | System and method for digital signal processing | |

| US9413321B2 (en) | System and method for digital signal processing | |

| US11431312B2 (en) | System and method for digital signal processing | |

| JPH06177688A (ja) | オーディオ信号処理装置 | |

| US10848118B2 (en) | System and method for digital signal processing |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20180309 Year of fee payment: 4 |

|

| FPAY | Annual fee payment |

Payment date: 20190222 Year of fee payment: 5 |