KR100678354B1 - 빠른 디코드 명령들을 이용하기 위한 방법 및 데이터 처리 시스템 - Google Patents

빠른 디코드 명령들을 이용하기 위한 방법 및 데이터 처리 시스템Info

- Publication number

- KR100678354B1 KR100678354B1 KR1019970035518A KR19970035518A KR100678354B1 KR 100678354 B1 KR100678354 B1 KR 100678354B1 KR 1019970035518 A KR1019970035518 A KR 1019970035518A KR 19970035518 A KR19970035518 A KR 19970035518A KR 100678354 B1 KR100678354 B1 KR 100678354B1

- Authority

- KR

- South Korea

- Prior art keywords

- instruction

- bitfield

- state

- unit

- central processing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

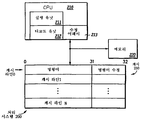

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3802—Instruction prefetching

- G06F9/3812—Instruction prefetching with instruction modification, e.g. store into instruction stream

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0875—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches with dedicated cache, e.g. instruction or stack

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/3017—Runtime instruction translation, e.g. macros

- G06F9/30174—Runtime instruction translation, e.g. macros for non-native instruction set, e.g. Javabyte, legacy code

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30181—Instruction operation extension or modification

- G06F9/30185—Instruction operation extension or modification according to one or more bits in the instruction, e.g. prefix, sub-opcode

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Software Systems (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Quality & Reliability (AREA)

- Advance Control (AREA)

- Memory System Of A Hierarchy Structure (AREA)

- Executing Machine-Instructions (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US08/684,717 US6523095B1 (en) | 1996-07-22 | 1996-07-22 | Method and data processing system for using quick decode instructions |

| US684,717 | 1996-07-22 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR980010777A KR980010777A (ko) | 1998-04-30 |

| KR100678354B1 true KR100678354B1 (ko) | 2007-11-12 |

Family

ID=24749266

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970035518A Expired - Fee Related KR100678354B1 (ko) | 1996-07-22 | 1997-07-22 | 빠른 디코드 명령들을 이용하기 위한 방법 및 데이터 처리 시스템 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6523095B1 (enExample) |

| JP (1) | JP3830236B2 (enExample) |

| KR (1) | KR100678354B1 (enExample) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9098297B2 (en) * | 1997-05-08 | 2015-08-04 | Nvidia Corporation | Hardware accelerator for an object-oriented programming language |

| US20090240928A1 (en) * | 2008-03-18 | 2009-09-24 | Freescale Semiconductor, Inc. | Change in instruction behavior within code block based on program action external thereto |

| US9851990B2 (en) * | 2015-01-30 | 2017-12-26 | American Megatrends, Inc. | Method and system for performing on-demand data write through based on UPS power status |

| US9886387B2 (en) | 2015-01-30 | 2018-02-06 | American Megatrends, Inc. | Method and system for performing on-demand data write through based on virtual machine types |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4910656A (en) * | 1987-09-21 | 1990-03-20 | Motorola, Inc. | Bus master having selective burst initiation |

| DE68924306T2 (de) * | 1988-06-27 | 1996-05-09 | Digital Equipment Corp | Mehrprozessorrechneranordnungen mit gemeinsamem Speicher und privaten Cache-Speichern. |

| US5155824A (en) * | 1989-05-15 | 1992-10-13 | Motorola, Inc. | System for transferring selected data words between main memory and cache with multiple data words and multiple dirty bits for each address |

| JPH0625984B2 (ja) * | 1990-02-20 | 1994-04-06 | インターナシヨナル・ビジネス・マシーンズ・コーポレーシヨン | マルチプロセツサ・システム |

| US5426765A (en) * | 1991-08-30 | 1995-06-20 | Compaq Computer Corporation | Multiprocessor cache abitration |

| GB2260628A (en) * | 1991-10-11 | 1993-04-21 | Intel Corp | Line buffer for cache memory |

| US5428761A (en) * | 1992-03-12 | 1995-06-27 | Digital Equipment Corporation | System for achieving atomic non-sequential multi-word operations in shared memory |

| JP3242161B2 (ja) * | 1992-09-11 | 2001-12-25 | 株式会社日立製作所 | データプロセッサ |

| US5572700A (en) * | 1993-04-30 | 1996-11-05 | Intel Corporation | Cache access controller and method for permitting caching of information in selected cache lines |

| US5555392A (en) * | 1993-10-01 | 1996-09-10 | Intel Corporation | Method and apparatus for a line based non-blocking data cache |

-

1996

- 1996-07-22 US US08/684,717 patent/US6523095B1/en not_active Expired - Fee Related

-

1997

- 1997-07-15 JP JP20545597A patent/JP3830236B2/ja not_active Expired - Fee Related

- 1997-07-22 KR KR1019970035518A patent/KR100678354B1/ko not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP3830236B2 (ja) | 2006-10-04 |

| US6523095B1 (en) | 2003-02-18 |

| KR980010777A (ko) | 1998-04-30 |

| JPH1091434A (ja) | 1998-04-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3771273B2 (ja) | 述語レジスタ・セットをレストアする方法および装置 | |

| US5926646A (en) | Context-dependent memory-mapped registers for transparent expansion of a register file | |

| CN1150455C (zh) | 强静态预测分支指令的优化执行 | |

| US12455745B2 (en) | Processor subroutine cache | |

| US5978904A (en) | Data processor | |

| US6823447B2 (en) | Software hint to improve the branch target prediction accuracy | |

| US5168571A (en) | System for aligning bytes of variable multi-bytes length operand based on alu byte length and a number of unprocessed byte data | |

| US6076156A (en) | Instruction redefinition using model specific registers | |

| US7000094B2 (en) | Storing stack operands in registers | |

| US5187793A (en) | Processor with hierarchal memory and using meta-instructions for software control of loading, unloading and execution of machine instructions stored in the cache | |

| US20020152361A1 (en) | Directed least recently used cache replacement method | |

| US5423048A (en) | Branch target tagging | |

| KR20030034243A (ko) | 변환된 명령어의 재시작 | |

| US20050257037A1 (en) | Controlling execution of a block of program instructions within a computer processing system | |

| JPH09120372A (ja) | プリフェッチ命令を用いるハーバードアーキテクチャキャッシュメモリの調和したソフトウェア制御 | |

| US5958045A (en) | Start of access instruction configured to indicate an access mode for fetching memory operands in a microprocessor | |

| US5193156A (en) | Data processor with pipeline which disables exception processing for non-taken branches | |

| JP2001202253A (ja) | データ処理方法およびデータ処理装置 | |

| US5835972A (en) | Method and apparatus for optimization of data writes | |

| KR19990014132A (ko) | 데이터 프로세서에서 조건부 분기 실행을 제어하기 위한 방법 및 장치 | |

| KR20040045467A (ko) | 자바 하드웨어 가속기에 대한 추론적 실행 | |

| KR100678354B1 (ko) | 빠른 디코드 명령들을 이용하기 위한 방법 및 데이터 처리 시스템 | |

| US8484446B2 (en) | Microprocessor saving data stored in register and register saving method | |

| US6647487B1 (en) | Apparatus and method for shift register rate control of microprocessor instruction prefetches | |

| US6308242B1 (en) | Apparatus for adaptively controlling a prefetch queue based on various flush conditions |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-3-3-R10-R17-oth-X000 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-3-3-R10-R17-oth-X000 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| A201 | Request for examination | ||

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| E801 | Decision on dismissal of amendment | ||

| PE0801 | Dismissal of amendment |

St.27 status event code: A-2-2-P10-P12-nap-PE0801 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| R19-X000 | Request for party data change rejected |

St.27 status event code: A-3-3-R10-R19-oth-X000 |

|

| N231 | Notification of change of applicant | ||

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| J301 | Trial decision |

Free format text: TRIAL DECISION FOR APPEAL AGAINST DECISION TO DECLINE AMENDMENT REQUESTED 20040730 Effective date: 20050929 Free format text: TRIAL NUMBER: 2004102000042; TRIAL DECISION FOR APPEAL AGAINST DECISION TO DECLINE AMENDMENT REQUESTED 20040730 Effective date: 20050929 |

|

| PJ1301 | Trial decision |

St.27 status event code: A-3-3-V10-V15-crt-PJ1301 Decision date: 20050929 Appeal event data comment text: Appeal Kind Category : Appeal against decision to decline amendment, Appeal Ground Text : 1997 35518 Appeal request date: 20040730 Appellate body name: Patent Examination Board Decision authority category: Office appeal board Decision identifier: 2004102000042 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| T11-X000 | Administrative time limit extension requested |

St.27 status event code: U-3-3-T10-T11-oth-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 5 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 6 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| FPAY | Annual fee payment |

Payment date: 20130110 Year of fee payment: 7 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 7 |

|

| FPAY | Annual fee payment |

Payment date: 20140109 Year of fee payment: 8 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 8 |

|

| LAPS | Lapse due to unpaid annual fee | ||

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 20150130 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 20150130 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |