KR100436098B1 - 데이터프로세서,데이터처리시스템,및데이터프로세서를이용한외부장치로의액세스방법 - Google Patents

데이터프로세서,데이터처리시스템,및데이터프로세서를이용한외부장치로의액세스방법 Download PDFInfo

- Publication number

- KR100436098B1 KR100436098B1 KR1019970008475A KR19970008475A KR100436098B1 KR 100436098 B1 KR100436098 B1 KR 100436098B1 KR 1019970008475 A KR1019970008475 A KR 1019970008475A KR 19970008475 A KR19970008475 A KR 19970008475A KR 100436098 B1 KR100436098 B1 KR 100436098B1

- Authority

- KR

- South Korea

- Prior art keywords

- external

- signal

- bus

- address

- master

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

- G06F13/1694—Configuration of memory controller to different memory types

Abstract

외부 마스터 칩 선택 액세스가 제어 레지스터(810)를 사용하는 내부 마스터 액세스의 시간 길이와 동일하거나 다를 수 있도록, 사용자는 데이터 프로세서(3)를 프로그램할 수 있다. 또한, 사용자는, 데이터 프로세서의 내부 칩 선택 및 기록 인에이블 발생 로직(8)을 여전히 사용하지만, 내부 전송 확인 로직을 턴오프 하고, 외부 전송 확인 로직을 추가할 수 있다. 이 특징은 칩 선택 베이스에 따라 사용자가 프로그램할 수 있으며, 외부 칩 선택 및 기록 인에이블 로직을 요청하지 않고 사용자가 다른 외부 마스터 액세스를 보상하도록 하는 유연한 해결책을 제공한다. 따라서, 오버헤드가 유지되며 효율이 증가한다.

Description

본 발명의 분야

본 발명은 일반적으로는 외부 마스터와 외부 메모리간에서 정보를 통신하는 데이터 프로세서에 관한 것이며, 보다 특정적으로는 외부 다이나믹 랜덤 액세스 메모리(DRAM), 외부 칩 선택 가능한 장치, 및 외부 마스터간에서 정보를 통신하는 데이터 프로세서에 관한 것이다.

본 발명의 배경

다이나믹 랜덤 액세스 메모리(DRAM) 회로들은 일반적으로는 무수한 데이터 처리 동작들 동안에 사용하기 위해 비용이 안 드는(inexpensive) 메모리를 제공하기 위해 반도체 데이터 처리 시스템에서 사용된다. 공통의 DRAM 회로들에 액세스하는 복수의 데이터 프로세서들을 사용한 현재의 데이터 처리 시스템들은 적절한 어드레스 다중화를 제공하기 위해 외부 멀티플렉서를 전형적으로 필요로 한다. 어드레스 다중화는 메모리 엑세스 동작 동안에 DRAM 회로에 적절한 어드레스를 제공하기 위해 요구된다. DRAM 회로의 핀 수는 전형적으로 한정되기 때문에, 복수의 데이터 프로세서들 중 하나에 의해 적합한 제어가 제공되는 경우, DRAM 회로의 동일한 사전 선택된 부분의 집적 회로 핀들에 로우 어드레스 또는 컬럼 어드레스를 제공하기 위해 멀티플렉서가 요구된다. 데이터 프로세서는, 로우 어드레스 또는 컬럼 어드레스가 DRAM 회로의 사전 선택된 부분의 집적회로 핀들에 현재 제공되는지 여부를 나타내기 위해 RAS(로우 어드레스 스트로브(Row Address Strobe))신호 또는 CAS(컬럼 어드레스 스트로브(Column Address Strobe))신호를 DRAM 회로에 제공한다. 부가적으로, DRAM 회로에 판독 또는 기록 액세스를 지시하기 위해 DRAMW 신호가 제공된다. 전형적인 DRAM 회로에서는, RAS 신호는 DRAM 회로의 사전 선택된 부분의 집적 회로 핀들이 로우 어드레스 값을 수신하고 있는 것을 나타내며, CAS 버스는 DRAM 회로의 사전 선택된 부분의 집적 회로 핀들이 컬럼 어드레스를 수신하고 있는 것을 나타낸다. RAS, CAS 및 DRAMW 신호들 이외에도, 데이터 프로세서는 또한 일반적으로 멀티플렉서에 대하여 제어를 제공하기 위해 적어도 하나의 집적 회로 핀을 지정해야 한다. 집적 회로 핀들의 수가 한정되는 종래 기술 영역에 있어서, 멀티플렉서의 제어를 제공하기 위해 단일의 핀을 사용하는 것은 데이터 처리 시스템의 설계자들에게는 번거로울 수 있다.

더욱이, 종래 기술의 구성에 있어서 멀티플렉서를 구현하는데 필요한 외부 로직은 종종 외부 마스터를 포함하는 데이터 처리 시스템에 대한 실질적인 양의 오버헤드 비용을 더한다. Advanced Micro Devices에 의해 제조된 AM29200 및 International Business Machines에 의해 제조된 PPC403GA를 사용하는 데이터 처리 시스템들에 있어서, 상술된 바와 같은 외부 멀티플렉싱이 요구된다. 이 시스템들 각각은 도 1에서 도시된 바와 같은 구성을 필요로 한다. 따라서, 현재의 DRAM 제어기들의 구성이 적절히 기능한다 하더라도, 상기 멀티플렉서를 제어하기 위해 상술된 멀티플렉서 또는 여분의 외부 집적 회로 핀의 사용을 요구하지 않는 데이터 처리 시스템의 필요성이 존재한다.

데이터 처리 시스템의 설계자들의 관심을 일으키는 다른 영역은 내부 및 외부 마스터 장치가 함께 데이터 프로세서 내에서 칩 선택 및 기록 인에이블 발생 로직을 사용하는 경우에 생긴다. 외부 마스터가 내부 칩 선택 발생을 이용하여 버스 전송을 개시하는 경우, 때때로, 외부 마스터는 칩 선택된 메모리를 액세스하는데내부 마스터와는 다른 양의 시간을 필요로 한다. 이는 외부 마스터 어드레스 및 버스 속성들이 내부 마스터 어드레스 및 버스 속성들과 동일한 시간 양으로 내부 제어기에 이용 가능하지 않기 때문이다. 만일 이러한 경우가 생기고 외부 마스터가 내부 칩 선택 발생 로직을 사용하는 것을 희망하면, 종래 기술의 해결책은 외부 마스터의 액세스에 정합하기 위해 내부 마스터의 액세스를 변경하는 것을 요구하거나 또는 내부 마스터의 액세스가 외부 마스터의 액세스보다 한 클럭 짧도록 허용하는 것이다.

만일 사용자가 상기의 해결책들 중 어느 하나를 사용할 수 없다면, 사용자는 내부 칩 선택 및 기록 인에이블 발생 로직을 사용할 수 없을 것이다. 이 경우에, 사용자는 외부 마스터 액세스들에 대해 이러한 로직을 외부 시스템에 부가해야 한다. 따라서, 외부 마스터가 외부 메모리를 액세스할 때 외부 마스터 액세스의 타이밍이 내부 마스터 액세스의 타이밍과 동일하거나 또는 한 사이클 느린 것을 요구하지 않고, 사용자가 내부적으로 구현된 칩 선택 및 기록 인에이블 발생 로직을 이용하도록 하는 데이터 프로세서의 필요성이 존재한다.

본 발명의 상세한 기술

본 발명은 데이터 프로세서, 외부 메모리 또는 장치, 및 외부 마스터간에서 정보를 통신하기 위한 장치와 방법을 제공한다. 본 발명의 장치와 방법은 데이터 프로세서가 외부 마스터에 의해 액세스 동안 외부 메모리 또는 장치를 적절하게 제어하도록 해서 외부 인터페이스 회로의 필요성을 절감시키며 데이터 처리 시스템에연관된 오버헤드 비용을 절감시킨다.

본 발명에서, DRAM 회로의 액세스 중에 멀티플렉싱 기능을 수행하기 위한 어떠한 외부 회로도 필요하지 않도록, 데이터 처리 시스템에서 외부 메모리를 제어하기 위한 작동의 회로 및 방법이 제공된다. 또한, 본 발명은 외부 마스터 장치에 의한 DRAM(dynamic random access memory) 액세스를 위한 데이터 프로세서에서 외부 멀티플렉서 및 전용 집적 회로 핀의 필요성을 제거한다. 본 발명은 도 1에 도시된 바와 같이, 종래 기술의 데이터 처리 시스템에 의해 요구된 것과 같은 전용의 집적 회로 핀을 필요로 하지 않고도 DRAM 회로를 액세스하는데 필요한 멀티플렉싱 기능을 실시한다. 본 발명의 데이터 프로세서의 증가된 유연성 및 저감된 집적 회로 핀의 요구는 보다 낮은 시스템 비용을 가지며 반도체 시장에 있어서 최신의 진보를 활용하기 위해 용이하게 업데이트될 수 있는 데이터 처리 시스템을 구현한다.

본 발명의 제 2 양태에 있어서, 사용자는, 외부 마스터의 칩 선택 액세스가 내부 마스터의 액세스와 동일한 수의 사이클로 될 수 있거나, 또는 외부 전송 확인 종료를 사용할 수 있으며, 임의의 수의 사이클로 될 수 있도록 본 발명의 데이터 프로세서를 프로그램할 수 있다. 사용자는 아직도 내부 칩 선택 및 기록 인에이블 발생 로직을 사용하며, 내부 및 외부 마스터 칩 선택 액세스를 위해 독립적으로 그리고 칩 선택에 기초하여 외부 전송 확인 종료의 사용을 프로그램할 수 있다. 본 발명의 이 양태에 의해 제공된 유연성은 사용자가 외부 칩 선택 및 기록 인에이블 발생 로직을 요구하지 않는 다른 외부 마스터 사이클 타이밍을 보상하게 한다. 따라서, 본 발명의 이 실시예에 있어서 오버헤드가 유지되어 효율이 증가한다.

다음의 설명에 있어서, 본 발명을 구현하는 데이터 처리 시스템의 일 실시예의 접속과 동작이 보다 상세히 제공될 것이다.

도 1은 외부 메모리 제어기를 실시하는 데이터 처리 시스템의 종래 기술의 구성을 도시한 블록도.

도 2는 본 발명의 일 실시예에 따른 외부 메모리 제어기를 실시하는 데이터 처리 시스템의 구성을 도시한 블록도.

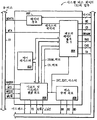

도 3은 본 발명의 일 실시예에 따른 데이터 프로세서를 도시한 블록도.

도 4는 도 3의 데이터 프로세서의 시스템 버스 제어기를 도시한 블록도.

도 5는 도 4의 시스템 버스 제어기에 의해 실행된 기능을 도시한 흐름도.

도 6은 본 발명에 따른 DRAM 회로의 외부 마스터 개시 액세스의 제 1 예를 도시한 타이밍 블록도.

도 7은 본 발명에 따른 DRAM 회로의 외부 마스터 개시 풀 페이지 액세스의 제 2 예를 도시한 타이밍 블록도.

도 8은 본 발명에 따른 DRAM 회로의 외부 마스터 개시 액세스의 제 3 예를 도시한 타이밍 블록도.

도 9는 본 발명에 따른 DARM 회로의 외부 마스터 개시 액세스의 제 4 예를도시한 타이밍 블록도.

도 10은 본 발명에 따른 칩 선택 가능한 회로의 외부 마스터 개시 액세스의 제 1 예를 도시한 타이밍 블록도.

도 11은 본 발명에 따른 칩 선택 가능한 회로의 외부 마스터 개시 액세스의 제 3 예를 도시한 타이밍 블록도.

도 12a는 도 4의 시스템 버스 제어기의 다수의 칩 선택 레지스터들에 포함된 칩 선택 어드레스 레지스터를 도시한 표.

도 12b는 도 4의 시스템 버스 제어기의 다수의 칩 선택 레지스터들에 포함된 칩 선택 마스크 레지스터를 도시한 표.

도 12c는 도 4의 시스템 버스 제어기의 다수의 칩 선택 레지스터들에 포함된 칩 선택 제어 레지스터를 도시한 표.

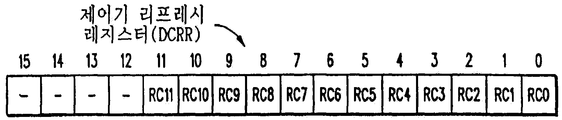

도 13a는 도 4의 시스템 버스 제어기의 다수의 DRAM 제어 레지스터들에 포함된 DRAM 제어기 리프레쉬 레지스터를 도시한 표.

도 13b는 도 4의 시스템 버스 제어기의 다수의 DRAM 제어 레지스터들에 포함된 DRAM 제어장치 타이밍 레지스터를 도시한 표.

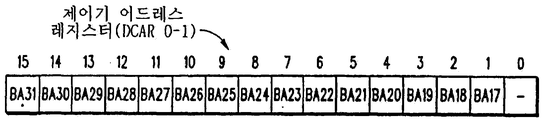

도 13c는 도 4의 시스템 버스 제어기의 다수의 DRAM 제어 레지스터들에 포함된 DRAM 제어기 어드레스 레지스터를 도시한 표.

도 13d는 도 4의 시스템 버스 제어기의 다수의 DRAM 제어 레지스터들에 포함된 DRAM 제어기 마스크 레지스터를 도시한 표.

도 13e는 도 4의 시스템 버스 제어기의 다수의 DRAM 제어 레지스터들에 포함된 DRAM 제어기 제어 레지스터를 도시한 표.

도 14a는 본 발명의 일 실시예에서 구현된 8 비트 데이터 포트 사이즈의 어드레스 멀티플렉싱 구성을 도시한 표.

도 14b는 본 발명의 일 실시예에서 구현된 16 비트 데이터 포트 사이즈의 어드레스 멀티플렉싱 구성을 도시한 표.

도 14c는 본 발명의 일 실시예에서 구현된 32 비트 데이터 포트 사이즈의 어드레스 멀티플렉싱 구성들을 도시한 표.

도 15는 본 발명에 따른 칩 선택 가능한 회로의 외부 마스터 개시 액세스의 제 2 예를 도시한 타이밍 블록도

도 16은 본 발명에 따른 칩 선택 가능한 회로의 외부 마스터 개시 액세스의 제 4 예를 도시한 타이밍 블록도.

* 도면의 주요부분에 대한 부호의 설명 *

2 : CPU 3 : 데이터 프로세서

4 : 메모리 관리 장치/제어 장치 6 : 메모리

8 : 시스템 버스 제어 장치 10 : 디버그 모듈

12, 13 : 슬레이브 모듈 14 : 마스터 모듈

본 발명의 접속에 관하여

본 발명의 접속에 관한 다음의 설명에서, "버스"라는 용어는 하나 또는 그 이상의 여러 타입의 정보, 즉 데이터, 어드레스, 제어, 또는 상태(status)와 같은 것을 전송하는데 사용될 수 있는 다수의 신호 또는 컨덕터를 언급하는데 사용될 것이다. "어서트하다(assert)"와 "부정하다(negate)"라는 용어는 신호, 상태 비트, 또는 유사한 장치를 각각 그 논리적으로 참 또는 논리적으로 거짓 상태로 만드는 것을 언급하는 경우에 사용될 것이다. 만일 논리적으로 참 상태가 논리 레벨 1이라면, 논리적으로 거짓 상태는 논리 레벨 0이 될 것이다. 그리고 만일 논리적으로 참 상태가 논리 레벨 0이라면, 논리적으로 거짓 상태는 논리 레벨 1이 될 것이다.

또한, 숫자에 선행하는 기호 "$"는 그 숫자가 16진수 또는 16을 베이스로 하는 형식으로 표현된다는 것을 나타낸다. 숫자에 선행하는 기호 "%"는 숫자가 2진수 또는 2를 베이스로 하는 형식으로 표현된다는 것을 나타낸다.

본 발명에 관한 다음의 설명에서, 필드 및 비트라는 용어는 상호 교환 가능할 수 있다는 점을 주의하여야 한다.

도 2는 본 발명의 일 실시예에 따른 데이터 처리 시스템(202)을 나타낸다. 데이터 처리 시스템(202)은 데이터 프로세서(3), 외부 버스 마스터(205), 메모리(206) 및 DRAM(207)을 포함한다. 데이터 프로세서(3)는 E-버스(외부 버스;External Bus)를 통해 외부 버스 마스터(205), 메모리(206) 및 DRAM(207)에 연결된다. E-버스는 버스 중재 버스(Bus Arbitration bus), 판독/신호, 전송 개시 (TS) 신호, 전송 확인(TA) 신호 및 데이터 프로세서(3)와 외부 버스 마스터(205) 사이의 사이즈 버스를 연결한다. 어드레스 버스와 데이터 버스는 또한 데이터 프로세서(3)와 외부 버스 마스터(205), 메모리(206) 및 DRAM(207) 각각 사이에 E-버스에 의해 연결된다. 또한, 데이터 프로세서(3)는 E-버스를 통해 로우 어드레스 스트로브(RAS) 신호, 컬럼 어드레스 스트로브(CAS) 신호 및 DRAM 기록(DRAMW) 신호를 제공하기 위해 DRAM(207)에 연결된다. 데이터 프로세서(3)는 E-버스를 통해 칩 선택(CS) 신호, 기록 인에이블(WE) 버스를 제공하기 위해 메모리(206)에 연결된다. 버스 중재 버스는 본 발명의 실시예에서 버스 요구(BR), 버스 승인(BR) 및 버스 구동(BD) 신호의 편집물(compilation)이다. 그러나, 버스 중재 및 그것에 관련된 신호는 데이터 처리 기술에 잘 공지되어 있고 다른 신호를 포함하는 다른 구성은 여기서 구현될 수 있다.

도 3을 참조하면, 도 3은 본 발명의 일 실시예에 따른 데이터 프로세서(3)를 나타낸다. 데이터 프로세서(3)는 시스템 버스 제어기(8), 코어(9), 슬레이브 모듈(12), 슬레이브 모듈(13), 마스터 모듈(14) 및 디버그 모듈(10)을 포함한다. 시스템 버스 제어기(8)는 E-버스를 통해 외부 장치(여기서는 도시되지 않음)에 연결된다. 시스템 버스 제어기(8)는 S-버스를 통해 슬레이브 모듈(12)과 슬레이브 모듈(13)에 연결된다. S-버스는 슬레이브 모듈 버스이다. 시스템 버스 제어기(8)는 M-버스(23)를 통해 코어(9)와 마스터 모듈(14)에 연결된다. M-버스(23)는 마스터모듈 버스이다. 도 3이 본 발명의 일 실시예를 나나낸다는 점을 이해하여야 한다. 따라서, 다수의 슬레이브 모듈 및 다수의 마스터 모듈은 데이터 프로세서(3)의 다른 실시예에서 구현될 수 있다.

코어(9)는 CPU(2), 메모리 관리 유닛(MMU)/제어기(4) 및 메모리(6)를 포함한다. CPU(2), MMU/제어기(4), 메모리(6) 및 디버그 모듈(10)은 각각 K-버스(25)를 통해 서로 연결된다. CPU(2)와 메모리(6) 양자는 또한 MMU/제어기(4)에 직접 접속된다. MMU/제어기(4)는 M-버스(23)를 통해 데이터 프로세서(3)의 나머지 부분에 정보를 제공한다. CPU(2)는 외부 장치로부터 리셋 신호를 수신한다. 디버그 모듈(10)은 데이터 프로세서(3)의 외부의 장치(여기서는 도시되지 않음)와 다수의 디버그 정보를 통신한다.

도 4는 시스템 버스 제어기(8)의 일부를 나타낸다. 시스템 버스 제어기(8)는 데이터 패스 회로(802), 메모리 제어기(804), 버스 중재 회로(806), 디코드 및 어드레스 발생 회로(808), 제어 레지스터(810)를 포함한다.

E-버스는 양방향으로 외부 데이터 버스를 데이터 패스 제어회로(802)에 연결시킨다. M-버스(23)는 또한 양방향으로 마스터 데이터(MData) 버스를 데이터 패스 회로(802)에 연결시킨다. 데이터 패스 회로(802)는 또한 레지스터 데이터 신호를 수신하기 위해 메모리 제어기(804)에 연결된다.

메모리 제어기(804)는 마스터 전송 확인(MTA) 신호를 제공하기 위해 M-버스(23)에 연결된다. 메모리 제어기(804)는 기록 인에이블(WE) 버스, 칩 선택(CS) 신호, DRAM 기록(DRAMW) 신호, 로우 어드레스 스트로브(RAS) 신호, 컬럼어드레스 스트로브(CAS) 버스, 전송 확인(TA) 신호를 제공하기 위해 E-버스에 연결된다.

메모리 제어기(804)는 다수의 제어 정보를 수신하기 위해 제어 레지스터(810)에 또한 연결된다. 메모리 제어기(804)는 DRAM_히트 신호 및 CS_히트 신호를 수신하기 위해 디코드 및 어드레스 생성 회로(808)에 연결된다. 메모리 제어기(804)는마스터(내부가 아닌 외부 마스터) 신호를 수신하기 위해 버스 중재 회로(806)에 연결된다.

버스 중재 회로(806)는 버스 승인(BG) 신호를 수신하기 위해 그리고 버스 요구(BR) 신호 및 버스 구동(BD) 신호를 제공하기 위해 E-버스에 연결된다. 버스 중재 회로는 상기의마스터 신호를 제공하기 위해 디코드 및 어드레스 발생 회로(808)에 연결된다.

디코드 및 어드레스 발생 회로(808)는 양방향으로 어드레스 값, 전송 개시(TS) 신호, 판독/신호, 사이즈 버스와 통신하기 위해 E-버스에 연결된다. 디코드 및 어드레스 발생 회로(808)는 또한 다수의 제어 정보를 수신하기 위해 제어 레지스터(810)에 연결된다. 디코드 및 어드레스 발생 회로(808)는 또한 마스터 어드레스(MADDR) 값, 마스터 전송 개시(MTS) 신호, 마스터 사이즈(MSIZE)버스, 및 마스터 판독/신호를 수신하기 위해 M-버스에 연결된다.

레지스터에 관한 기술

본 발명의 일 실시예를 구현하는 시스템 버스 제어기(8)의 일부는 다수의 제어 레지스터(810)를 포함한다. 본 발명을 구현하는데 사용되는 각각의 레지스터는 이후에 보다 상세히 기술될 것이다. 또한, 본 발명의 작동 중에 제어 레지스터(810)를 사용하는 것은 이후에 보다 상세히 기술될 것이다.

다수의 제어 레지스터(810)는 도 12a 내지 도 12c 및 도 13a 내지 13e에 보다 상세히 나타나 있다. 다수의 제어 레지스터(810)는 칩 선택 어드레스 레지스터(CSARO-7), 칩 선택 마스크 레지스터(CSMRO-CSMR7) 및 칩 선택 제어 레지스터(CSCRO-CSCR7)를 포함한다.

다수의 칩 선택 어드레스 레지스터(CSAR)들 중 대표적인 하나는 도 12a에 나타나 있다. 각각의 칩 선택 어드레스 레지스터는 칩 선택 핀의 베이스 어드레스를 결정한다. 각각의 비트(BA31 내지 BA16)는 각각의 칩 선택에 전용의 메모리의 베이스 어드레스 위치를 정의한다. 이 비트는 칩 선택 메모리가 액세스되어지는지를 결정하기 위해 내부 어드레스 버스의 상위 비트와 비교된다.

다수의 칩 선택 마스크 레지스터(CSMR)들 중 대표적인 하나는 도 12b에 나타나있다. 각각의 CSMR은 각각의 칩 선택에 대한어드레스 마스크를 결정한다. 또한, 각각의 CSMR은 칩 선택 신호에 대해 허용되는 액세스의 타입의 정의를 결정한다.

도 12b에서, BAM31 내지 BAM16이라는 라벨이 붙은 저장 로케이션은 베이스 어드레스 마스크를 나타낸다. 이 필드는 어드레스 마스크 비트의 사용을 통해 각각의 칩 선택에 전용의 메모리의 블록을 정의한다. 베이스 어드레스 마스크 비트는 논리적으로 반전되어, 앞서 언급한 CSAR에 저장된 베이스 어드레스의 상위 비트 및내부 어드레스 버스의 상위 비트로 "AND"로 된다. 2개의 값은 다음으로 칩 선택 어드레스 공간이 액세스되는지를 결정하기 위해 비교된다. 베이스 어드레스 마스크 비트들 중 하나가 논리 1인 경우, 이 비트는 칩 선택 어드레스 디코드 작동으로부터 디스에이블된다. 베이스 어드레스 마스크 비트들 중 하나가 논리 0인 경우, 내부 어드레스 버스로부터 대응하는 어드레스 비트는 적절한 디코드 어드레스를 결정하기 위해 CSAR내의 대응하는 비트와 비교된다. CPU, SC, SD, UC 및 UD라는 라벨이 붙은 CSMR 비트는 특정 어드레스 공간을 마스크하고 칩 선택을 특정 어드레스 공간 또는 공간들에 배치시킨다. 디스에이블된 어드레스 공간에서, 상기 어드레스 공간에 있어서 로케이션으로의 액세스는 통상의 외부 버스 액세스가 되고 칩 선택이 활성화되지 않는다. 어드레스 공간 마스크 비트는 CPU 공간 마스크, 슈퍼바이저 코드 어드레스 공간 마스크(SC), 슈퍼바이저 데이터 어드레스 공간 마스크(SD), 사용자 코드 어드레스 공간 마스크(UC) 및 사용자 데이터 어드레스 공간 마스크(UD)를 포함한다. CSMR에서 어드레스 공간 마스크 비트들 중 하나가 논리 1의 값일 때, 대응하는 어드레스 공간은 칩 선택 활성화 및 동작에서 디스에이블로 된다. 만일 어드레스 공간이 대응하는 어드레스 공간 마스크 비트가 어서트(assert)되는 경우에 액세스되면, 칩 선택 활성화는 발생하지 않을 것이고 비 칩 선택의 외부 사이클이 발생된다. CSMR에서 어드레스 비트들 중 하나가 논리 0의 값이면, 대응하는 어드레스 공간은 칩 선택 동작에 대해 인에이블된다. 칩 선택을 사용하는 액세스는 이 어드레스 공간에서 발생할 수 있다.

도 12c는 칩 선택 제어 레지스터(CSCR)를 나타낸다. 각각의 CSCR은 내부 자동 확인 종료를 제어하고, 외부 마스터 자동 확인 종료를 제어하고, 포트 사이즈를 지시하기 위해 칩 선택 및 기록 인에이블 어서트와 타이밍을 제어하며 칩 선택의 각각의 버스트 능력을 지시하는데 사용된다.

작동 중에, 칩 선택 0(CSO) 신호는 전역 또는 부트(boot) 칩 선택을 외부 집적회로 핀에 제공한다. 전역 칩 선택에 따라, CSO는 시스템 초기화가 일어나기 전에 부트 ROM에 대한 어드레스 디코딩을 허용한다. 또한, CSO 신호의 출력은 본 데이터 프로세서 상에 구현된 어느 다른 칩 선택 집적회로 핀과는 다르다. 시스템 리셋 동작 후에, CSO 집적회로 핀은 모든 어드레스에 대해 어서트(assert)된다. 이와 같은 능력은 부트 ROM이 외부 어드레스 공간내의 임의의 어드레스에 위치하도록 허용한다. CSO 집적회로 핀은 대응하는 CSMR(CSMRO)이 기록되는 상태에 의한 방법으로 작동한다. 그 포인트까지, CSO의 포트 사이즈 및 내부 자동 확인 기능은 리셋 부정에서 샘플링된 다수의 집적회로 핀 상에 제공된 값에 따라 결정된다. 다음의 표 1은 CSO에 대응하는 칩 선택에 대한 포트 사이즈를 선택하는데 사용되는 값을 나타낸다.

[표 1]

표 2는 데이터 프로세서(3)에서 내부 자동 확인 기능을 인에이블하거나 디스에이블하는 값을 나타낸다. CSO에 대해, 시스템 리셋시에, 판독 및 기록 전송 동작모두는 인에이블되고 버스팅은 디스에이블된다.

[표 2]

도 12c에서, 대기 상태(WS[3:0])는 AA(자동 확인) 필드 또는 EMAA(외부 마스터 자동 확인) 필드가 논리값 1과 동등한 경우에 유효하다. 유효한 경우에, WS[3:0] 필드는 전송 확인 발생되기 이전에 삽입될 다수의 대기 상태를 정의한다. 내부 마스터 초기화 사이클에 대해서는, 만일 외부 전송 확인이 지시된 수의 대기 상태가 발생되기 전에 수신되면, 외부 전송 확인은 상기 사이클을 종료시킬 것이다.

EMAA 필드는 대응하는 칩 선택 어드레스 공간과 "히트(hit)"하는 외부 마스터 초기화 사이클 중에 전송 확인의 구동과 어서트(assert)를 제어한다. 만일 EMAA 필드가 논리값이 1이면, 메모리 제어기(804)로부터의 전송 확인은 출력에 세트될 것이고 값 WS[3:0]에 의해 결정된 시간에 어서트(assert)된다. 외부 버스 마스터(205)로부터의 외부 전송 확인(TA) 종료는 디스에이블되어야 한다는 것을 유념하여야 한다. EMAA가 논리값이 0인 경우, 메모리 제어기(804)로부터의 외부 전송 확인 신호는 외부 마스터 초기화 버스 사이클 중에는 구동되지 않고, 외부 버스 마스터(205)로부터 외부 TA 종료가 제공되어야 한다.

AA 필드는 대응하는 칩 선택 어드레스 공간에서 히트하는 내부적으로 초기화된 버스 사이클 중에 내부 TA의 어서트(assert)를 제어한다. 만일 AA 필드가 논리값 1로 세트된다면, 내부 TA는 WS[3:0] 필드에 의해 결정된 시간에 어서트(assert)될 것이다. 메모리 제어기(804)로부터의 전송 확인 신호는 모든 내부적으로 초기화된 사이클 중에 패키지 집적회로 핀이 입력에 세트되게 전송된다. AA 필드가 논리값 0을 저장하는 경우, 내부 전송 확인은, 전송 확인 종료가 외부 버스 마스터(205)로부터 수신될 때까지는, 발생되지 않을 것이다.

PS[1:0](포트 사이즈) 필드는 각각의 칩 선택과 관련된 데이터의 폭을 지정한다. PS 필드는, 데이터가 기록 사이클 중에 어디에서 구동될 것인가 및 데이터가 판독 사이클 중에 어디에서 샘플링될 것인가를 결정한다. 예를 들어, 만일 PS 필드가 2진값 00을 갖는다면, 프로그램된 포트 사이즈는 32 비트이고 데이터는 데이터[31:0]라는 라벨이 붙은 다수의 집적 회로 핀 상에서 샘플링되고 구동될 것이다. 만일 PS 필드가 2진값 01을 갖는다면, 프로그램된 포트 사이즈는 8 비트이고 데이터는 단지 데이터[31:24]라는 라벨이 붙은 다수의 집적 회로 핀 상에서 샘플링되고 구동될 것이다. 만일 PS 필드가 2진값 10을 갖는다면, 프로그램된 포트 사이즈는 16 비트이고 데이터는 단지 데이터[31:16]라는 라벨이 붙은 다수의 집적 회로 핀 상에서 샘플링되고 구동될 것이다.

BRST(버스트 인에이블; Burst Enable) 필드는 각각의 칩 선택과 관련된 메모리의 "버스트 가능성(burstability)"을 표시한다. 만일 BRST 필드가 논리값 1으로 세트되면, 요구된 전송 사이즈보다 작은 포트 사이즈까지의 모든 전송 또는 상기의 요구된 전송 사이즈보다 작은 포트 사이즈로부터의 모든 전송은, "버스트"될 것이다. 예를 들어, 8 및 16 비트 포트로의 롱워드(longword) 전송, 8 비트 포트로의워드 전송 및 8, 16 및 32 비트 포트로의 라인 전송은 모두가 "버스트"될 것이다. BRST 필드가 논리값 0을 갖는다면, 지정된 포트 사이즈보다 큰 모든 전송은 지정된 포트 사이즈보다 크지 않은 개개의 비-버스트 전송으로 분리될 것이다.

ASET(어드레스 셋업 인에이블; Address Setup Enable) 필드는 어드레스 유효성의 지시자(indicator)와 관련된 칩 선택의 어서트(assert)를 제어한다. ASET 필드가 논리값이 0이면, 칩 선택은 어드레스 버스상의 어드레스가 유효한 경우에 어서트(assert)된다. ASET 필드가 논리값이 1이면, 칩 선택은 어드레스 버스상의 어드레스가 유효화된 한 사이클 이후에 어서트(assert)된다.

WRAH(기록 어드레스 홀드 인에이블; Write Address Hold Enable) 필드는 칩 선택 기록 사이클 동안 칩 선택과 기록 인에이블이 인에이블 어드레스 홀드 시간을 제어한다. WRAH 값이 논리값 0이면, 어드레스는 기록 동작의 실행중의 임의의 여분의 사이클 동안에 보존되지 않는다. WRAH 필드가 논리값 1을 갖는다면, 어드레스는 기록 동작의 실행중의 전송 확인이 어서트(assert)로 된 한 사이클 이후동안 보존된다.

RDAH(판독 어드레스 홀드 인에이블; Read Address Hold Enable) 필드는 칩 선택 판독 사이클 동안 칩 선택 신호가 어서트(assert)로 된 후 어드레스 홀드 시간을 제어한다. RDAH 값이 논리 0의 값이라면, 어드레스는 판독 동작의 실행중의 임의의 여분의 사이클 동안에 보존되지 않는다. RDAH 필드가 논리값 1을 가지면, 어드레스는 전송 확인이 판독 동작의 실행 중에 어서트(assert)로 된 한 사이클 이후 동안 보존된다.

WR(기록 인에이블; Write Enable) 필드는 기록 사이클시 칩 선택 및 기록 인에이블 신호의 어서트(assert)를 제어한다. WR 필드가 0의 논리값을 가지면, 칩 선택 신호는 기록 동작의 실행 중에 활성화되지 않는다. WR 필드가 1의 논리값을 가지면, 칩 선택 신호는 기록 동작의 실행 중에 활성화되지 않는다.

RD(판독 인에이블; Read Enable) 필드는 판독 사이클시 칩 선택 신호의 어서트(assert)를 제어한다. RD 필드가 0의 논리값을 가지면, 칩 선택 신호는 판독 동작의 실행 중에 활성화되지 않는다. RD 필드가 1의 논리값을 가지면, 칩 선택 신호는 판독 동작의 실행 중에 활성화되지 않는다.

다수의 제어 레지스터(810)는 DRAM 제어기 리프레쉬 레지스터(DCRR), DRAM 제어기 타이밍 레지스터(DCTR), 다수의 DRAM 제어기 어드레스 레지스터(DCAR0-DCAR1), 다수의 DRAM 제어기 마스크 레지스터(DCMR0-DCMR1) 및 다수의 DRAM 제어기 제어 레지스터(DCCR0-DCCR1)를 포함한다.

DCCR은 도 13a에서 보다 상세히 도시된다. DRAM 제어기 리프레쉬 카운터 레지스터는 리프레쉬 사이클간의 다수의 시스템 클럭을 제어한다. 도 13a에서, 리프레쉬 카운트 필드(RC11-RC0)는 메모리 제어기(804)에 의한 리프레쉬 요구에 관한 주파수를 제어한다. 리프레쉬 카운트 필드에 저장된 값은 리프레쉬 주기를 결정하기 위해 16 시스템 클럭이 곱해진다.

도 13b에 보다 상세히 도시된 DCTR은 DRAM의 다수의 뱅크에 대한 DRAM 액세스를 위한 타이밍을 제어한다. 이 레지스터에서의 필드는 메모리 제어기(804)에 의해 제공된 모든 타입의 DRAM 액세스에 대한 로우 어드레스 스트로브(RAS) 및 컬럼어드레스 스트로브(CAS) 버스를 변경한다. DCTR에서, 외부 마스터 DRAM 액세스중의 구동 어드레스(DAEM) 필드는 외부 마스터에 의한 DRAM의 액세스 중에 모든 어드레스 라인 상에서 메모리 제어기(804)의 출력 드라이버를 제어한다. 어드레스 신호를 출력하도록 구성된 어드레스 버스의 일부는 외부 마스터에 대한 로우 및 컬럼 어드레스 멀티플렉싱을 제공하도록 구동될 수 있다. DAEM 필드는 DRAM으로의 내부적의 초기화된 액세스 중에 어드레스의 구동에 영향을 미치지 않는다. 동작중에, DAEM 필드가 0의 논리값을 가지면, 어드레스 신호는 외부 마스터 DRAM 엑세스 중에 구동되지 않는다. 역으로, DAEM 필드가 1의 논리값을 갖는다면, 어드레스 신호는 외부 마스터 DRAM 액세스 중에 로우 및 컬럼 어드레스 멀티플렉싱을 제공하도록 구동된다.

EDO(확장 데이터 출력; Extended Data Out) 필드는 DRAM 뱅크에 EDO DRAM이 존재하는지를 그리고 페이지 모드 액세스 중에 EDO 시간에 대한 CAS 버스를 어서트(assert)하도록 메모리 제어기(804)를 지시하는지를 지정한다. 상기의 수순은 메모리 제어기(804)가 EDO DRAM에 의한 특정 CAS 타이밍을 이용하는 것을 허용한다.

RCD(RAS 대 CAS 지연) 필드는 RAS 신호의 어서트(assert)와 CAS 버스의 어서트(assert) 중에 다수의 시스템 클럭을 제어한다. 이 필드는 페이지 및 논-페이지(non-page) 모드 액세스에 대해서만 유효하다. 이는 리프레쉬 사이클을 제어하지 않는다. RCD 필드가 0의 논리값을 가지면, RAS 신호는 CAS 버스의 어서트(assert)이전에 하나의 시스템 클럭을 어서트(assert)할 것이다. RCD 필드가1의 논리값을 갖는다면, RAS 신호는 CAS 버스의 어서트(assert) 이전에 2개의 시스템 클럭을 어서트(assert)할 것이다.

RSH1-RSH0(논-페이지 모드 RAS 홀드 시간) 필드는 CAS 버스의 어서트(assert) 이후에 RAS 신호가 어서트(assert)로 된 상태를 유지하고 있는 시스템 클럭의 수를 제어한다. 이 필드는 논-페이지 모드 판독 및 기록 사이클 중에 RAS 신호의 타이밍을 제어한다. 이 필드가 2진값 00을 갖는 경우, RAS 신호는 CAS 버스의 어서트(assert) 이후에 1과 1/2 시스템 클럭을 부정할 것이다. 유사하게, 상기 필드가 2진값 01을 갖는 경우, RAS 신호는 CAS 버스의 어서트(assert) 이후에 2와 1/2 시스템 클럭을 부정할 것이다. 더욱이, 이 필드가 2진값 10을 갖는 경우, RAS 신호는 CAS 버스의 어서트(assert) 이후에 3과 1/2 시스템 클럭을 부정할 것이다.

CRP1-CRP0(논-페이지 모드 CAS-RAS 프리차지 시간) 필드는 버스 마스터가 백-투-백(back-to-back) DRAM 액세스를 요구하는 경우 CAS 버스의 부정 이후에 RAS 신호가 부정으로 된 상태를 유지하는 시스템 클럭의 수를 제어한다. CRP 필드가 2진값 00을 갖는 경우, RAS 신호는 CAS 버스의 부정 이후에 1과 1/2의 시스템 클럭을 어서트(assert)할 것이다. 유사하게, CRP 필드가 2진값 01을 갖는 경우, RAS 신호는 CAS 버스의 부정 이후에 2와 1/2의 시스템 클럭을 어서트(assert)할 것이다. 또한, CRP 필드가 2진값 10을 갖는 경우, RAS 신호는 CAS 버스의 부정 이후에 3과 1/2의 시스템 클럭을 어서트(assert)할 것이다.

CAS(페이지 모드 컬럼 어드레스 스트로브 타이밍) 필드는 EDO 필드와 함께,페이지 모드 DRAM 액세스 중에 CAS가 액티브한 상태로 유지되는 최소한의 시스템 클럭 수를 제어한다. 표 3은 CAS와 EDO 필드 사이의 관계를 나타낸다.

[표 3]

CP(CAS 프리차지 타이밍; CAS Prechsrge Timing) 필드는 EDO 필드와 함께, DRAM 액세스 이후에 CAS 버스가 인액티브 상태로 유지되는 다수의 시스템 클럭을 제어한다. 이 필드는 페이지 모드의 판독 및 기록 사이클 이후에만 CAS 버스 인액티브 타이밍을 제어한다. 표 4는 CP와 EDO 필드사이의 관계를 나타낸다.

[표 4]

CSR(RAS 리프레쉬 전의 CAS에 대한 CAS 셋업 시간; CAS Setup Time for CAS Before RAS Refresh) 필드는 리프레쉬 사이클 중에만 CAS 버스의 어서트(assert)와 RAS 사이클의 어서트(assert) 사이의 시스템 클럭의 수를 제어한다. CSR 필드가 0의 논리값을 갖는 경우, CAS 버스는 RAS 신호의 어서트(assert) 이전에 1 시스템 클럭을 어서트(assert)할 것이다. CSR 필드가 1의 논리값을 갖는 경우, CAS 버스는RAS 신호의 어서트(assert) 이전에 2 시스템 클럭을 어서트(assert)할 것이다.

다수의 DRAM 제어기 어드레스 레지스터(DCAR)중의 대표적인 하나는 도 13c에 나타나 있다. 각각의 DRAM 제어기 어드레스 레지스터는 각각의 DRAM 뱅크에 전용의 메모리의 베이스 어드레스를 저장한다. 이 비트는 DRAM 뱅크가 액세스되는지를 결정하기 위해 내부 어드레스 버스의 상위 비트와 비교된다.

다수의 DRAM 제어기 마스크 레지스터(DCMR)중의 대표적인 하나는 도 13d에 나타나 있다. 각각의 DCMR은 각각의 DRAM 뱅크에 대한 어드레스 마스크를 결정한다. 또한, 각각의 DCMR은 이 신호에 대해 허용되는 액세스의 타입의 정의를 결정한다.

도 13d에서, BAM31 내지 BAM17로 라벨이 붙은 저장 로케이션은 베이스 어드레스 마스크를 나타낸다. 이 필드는 어드레스 마스크 비트를 사용하여 각각의 DRAM 뱅크에 전용의 메모리의 블록을 정의한다. 베이스 어드레스 마스크 비트는 논리적으로 반전되며 앞서 언급된 DCAR에 저장된 베이스 어드레스의 상위 비트와 내부 어드레스 버스의 상위 비트로 "AND" 된다. 이 2개의 값은 다음으로 DRAM 뱅크 어드레스 공간이 액세스되고 있는지를 결정하기 위해서 비교된다. 베이스 어드레스 마스크 비트 중 하나가 논리값 1이면, 이 비트는 DRAM 뱅크 어드레스 디코드 동작에서 디스에이블된다. 베이스 어드레스 마스크 비트중 하나가 논리값 0이면, 내부 어드레스 버스로부터 대응하는 어드레스 비트는 적절한 디코드 어드레스를 결정하기 위해 DCAR내의 대응하는 비트와 비교된다. SC, SD, UC 및 UD로 라벨이 붙은 DCMR 비트는 특정 어드레스 공간을 마스크하고 특정 어드레스 공간 또는 공간들에 DRAM 뱅크를 배치한다. 디스에이블되는 어드레스 공간에서, 상기 어드레스 공간내의 로케이션으로의 액세스는 논-DRAM 외부 버스 액세스가 되어 어떠한 DRAM도 활성화되지 않는다. 어드레스 공간 마스크 비트는 슈퍼바이저 코드 어드레스 공간 마스크(SC), 슈퍼바이저 데이터 어드레스 공간 마스크(SD), 사용자 코드 어드레스 공간 마스크(UC) 및 사용자 데이터 어드레스 공간 마스크(UD)를 포함한다. DCMR내의 어드레스 공간 마스크 비트 중의 하나가 논리값이 1이면, 대응하는 어드레스 공간은 DRAM 활성화 및 동작에서 디스에이블된다. 만일 어드레스 공간이 대응하는 어드레스 공간 마스크 비트가 어서트(assert)되는 경우에 엑세스되면, 어떠한 DRAM 활성화도 발생하지 않을 것이고, 외부 논-DRAM 사이클이 발생된다. DCMR내의 어드레스 마스크 비트 중 하나가 논리값이 0이면, 대응하는 어드레스 공간은 DRAM 동작에 대해 인에이블된다. DRAM을 사용하는 액세스는 이 어드레스 공간에 대해 발생할 수 있다.

도 13e는 DRAM 제어기 제어 레지스터(DCCR)를 나타낸다. 각각의 DCCR은 포트 사이즈, 페이지 사이즈, 페이지 모드 및 데이터 처리 시스템에서 구현된 각각의 DRAM 뱅크의 활성화를 제어하는데 사용된다. DCCR에서, PS[1:0](포트 사이즈) 필드는 DRAM 어드레스 공간과 관련된 데이터 폭을 지정한다. 상기 PS 필드가 2진값 00을 갖는 경우, 프로그램된 포트 사이즈는 32 비트이고 데이터는 데이터[31:0]로 라벨이 붙은 다수의 집적 회로 핀 상에서 샘플링되고 구동될 것이다. 만일 PS 필드가 2진값 01을 갖는 경우, 프로그램된 포트 사이즈는 8 비트이고 데이터는 단지 데이터[31:24]로 라벨이 붙은 다수의 집적 회로 핀 상에서 샘플링되고 구동될 것이다.만일 PS 필드가 2진값 10을 갖는 경우, 프로그램된 포트 사이즈는 16 비트이고 데이터는 단지 데이터[31:16]로 라벨이 붙은 다수의 집적 회로 핀 상에서 샘플링되고 구동될 것이다. 만일 PS 필드가 2진값 11을 갖는 경우, 프로그램된 포트사이즈는 16 비트이고, 데이터는 단지 데이터[31:16]로 라벨이 붙은 다수의 집적회로 핀 상에서 샘플링되고 구동될 것이다.

BPS[1:0] 뱅크 페이지 사이즈 필드는 페이지 모드 DRAM이 사용되는 경우 각각의 DRAM 뱅크에 대한 페이지 사이즈를 정의한다. BPS 필드가 2진값 00을 갖는 경우, 페이지 사이즈는 512 바이트 페이지로 정의된다. BPS 필드가 2진값 01을 갖는 경우, 페이지 사이즈는 1K바이트 페이지로 정의된다. 유사하게, BPS 필드가 2진값 10을 갖는 경우, 페이지 사이즈는 2 K바이트 페이지로 정의된다.

포트 사이즈(PS[1:0])와 뱅크 페이지 사이즈(BPS[1:0])는 DRAM 사이클의 컬럼 어드레스 페이스(column address phase) 중에 어드레스 버스의 멀티플렉싱을 결정하기 위해 함께 사용된다. 포트 사이즈와 뱅크 사이즈의 모든 조합에 대한 어드레스 버스 멀티플렉싱은 도 14a 내지 도 14c에 나타나 있다.

PM[1:0](페이지 모드 선택; Page Mode Select) 필드는 각각의 DRAM 뱅크에 대해 허용된 페이지 모드 액세스의 타입을 선택한다. PM 필드가 2진값 00을 갖는 경우, 어떠한 페이지 모드 액세스도 허용되지 않는다. PM 필드가 2진값 01을 갖는 경우, 페이지 모드 액세스는 버스트 액세스 시에 허용된다. 또한, PM 필드가 2진값 11을 갖는 경우, 동작에 있어서 통상의 페이지 모드가 허용된다.

WR(기록 인에이블; Write Enable) 필드는 기록 사이클에 대한 DRAM 제어 신호의 어서트(assert)를 제어한다. WR 필드가 논리값 0을 갖는 경우, DRAM 제어 신호는 기록 동작 중에 활성화되지 않는다. WR 필드가 논리값 1을 갖는 경우, DRAM 제어 신호는 기록 동작 중에 활성화된다.

RD(판독 인에이블; Read Enable) 필드는 판독 사이클에 대한 DRAM 제어 신호의 어서트(assert)를 제어한다. RD 필드가 논리값 0을 갖는 경우, DRAM 제어 신호는 판독 동작 중에 활성화되지 않는다. RD 필드가 논리값 1을 갖는 경우, DRAM 제어 신호는 판독 동작 중에 활성화된다.

작동에 관한 기술

도 2에서 나타난 바와 같이, 본 발명의 작동 중에, 외부 버스 마스터(205)는 외부 멀티플렉서를 사용하지 않고 또는 선행 기술의 데이터 처리 시스템에 의해 요구된 어느 다른 외부 회로를 사용하지 않고 데이터 프로세서(3)의 내부의 메모리 제어기를 사용하여 DRAM(207)에 액세스할 수 있다. 본 발명은 외부 멀티플렉서, 그리고 심지어 데이터 프로세서(3)내의 내부적으로 DRAM의 로우 및 컬럼 어드레스를 멀티플렉싱하는 독자적인 회로와 기술을 구현함으로서 외부 마스터 초기화 DRAM 액세스 중에 외부 멀티플렉싱 제어를 제공하기 위한 전용의 집적 회로 핀에 대한 필요성을 제거한다.

이러한 외부 액세스 중에, 외부 버스 마스터(205)는 전송 개시(TS) 신호, 사이즈 버스 및 판독/기록(R/) 신호를 본 발명의 데이터 프로세서(3)에 어서트(assert)함으로서 데이터 전송 동작을 개시한다. 외부 버스 마스터(205)는 어드레스 값을 데이터 프로세서(3)에 또한 제공한다. 초기의 타이밍 사이클 중에,TS, R/, 사이즈 및 어드레스 신호를 포함하는 액세스 정보는 본 발명에 관한 데이터 프로세서(3)에서 구현된 메모리 제어기(도 2에서는 도시되지 않음)에 의해 저장된다. TS 신호의 어서트(assert) 이후의 차후의 타이밍 사이클 중에, 외부 버스 마스터(205)는 어드레스 버스를 트리-스테이트(tri-state)로 한다. 동일한 타이밍 사이클 중에, 데이터 프로세서(3)에서 구현된 메모리 제어기는 앞서 언급한 어드레스 값을 외부 어드레스 버스 상에 보강하기를 시작하여 RAS(로우 어드레스 스트로브) 신호를 어서트(assert)한다. 다수의 프로그램 가능한 제어 비트에 의해 결정된 적절한 시점에서, 메모리 제어기는 그후 컬럼 어드레스를 제공하고 CAS 신호를 어서트(assert)한다. 본 발명의 동작에 관한 이 양태는 이어서 첨부 도면과 관련하여 보다 상세히 기술될 것이다.

더욱이, 본 발명은 외부 버스 마스터(205)가 데이터 프로세서(3)의 내부의 메모리 제어기에 의해 발생된 내부 칩 선택 및 기록 인에이블 신호를 사용하는 경우, 칩 선택 및 기록 인에이블 신호의 외부 발생을 제공하기 위한 필요성을 제거한다. 사용자는 외부 마스터 칩 선택 액세스가 내부 마스터 액세스와 동일하게 되도록 데이터 프로세서(3)를 프로그램할 수 있거나, 또는 외부에서 발생된 전송 확인을 사용하기 위해 내부 또는 외부 마스터 액세스를 프로그램할 수 있다. 이와 같이, 사용자는 여전히 내부 칩 선택 및 기록 인에이블 발생 로직을 사용하면서도, 내부 전송 확인 로직을 턴오프하고 외부 전송 확인 로직을 추가할 수가 있다. 내부 전송 확인 로직은 다른 마스터에 의한 사용에 관계없이, 내부 또는 외부 마스터 초기화 사이클을 위해 턴 오프될 수 있다. 이 특징은 칩 선택 베이스에 따라 사용자가 프로그램 가능하다. 본 발명의 양태에 의해 제공된 유연성은 사용자가 외부 칩 선택 및 기록 인에이블 로직이 필요 없이도 외부 마스터 액세스의 다른 타이밍을 보상하도록 허용한다. 따라서, 오버헤드가 보존되어 효율성이 본 발명의 상기 실시예에서 증가된다.

또한, 본 발명에 관한 회로와 방법은 외부 버스 마스터(205)가 외부 제어 회로를 추가하지 않고 내부 마스터(데이터 프로세서(3))와 다른 수의 대기 상태를 사용하여 칩 선택 가능한 장치에 액세스하도록 허용한다. 외부 마스터가 데이터 프로세서(3)의 내부의 칩 선택 회로를 사용하고 내부 마스터와 다른 수의 대기 상태를 사용하여, 메모리에 액세스하도록 하기 위해, 본 발명은 레지스터 비트가 프로그램되도록 허용하여 내부 칩 선택 회로는 외부 액세스 중에 전송 확인 신호를 어서트(assert)하지 않을 것이다. 따라서, 외부 액세스 중에, 데이터 프로세서(3)의 칩 선택 로직은 내부에서 발생된 칩 선택 및 기록 인에이블 신호를 부정하기 전에 외부에서 발생된 전송 확인 신호를 대기할 것이다. 본 발명의 이 양태는 내부 및 외부 마스터 사이의 대기 상태의 수가 다른 경우에 요청되는 외부 회로의 양을 감소시킨다.

비록 본 발명에 의해 구현된 독자적인 회로와 기술은 이후에 보다 상세히 논의될 것이지만, 본 발명의 동작에 관한 일반적인 기술은 이제 제공될 것이다.

도 3은 데이터 프로세서(3)를 보다 상세히 나타낸다. 데이터 프로세서(3)의 동작 중에, 코어(9)는 CPU(2), MMU/제어기(4) 및 메모리(6)를 접속하기 위해 K-버스(25)를 사용한다. 본 발명의 실시예에서, K-버스(25)는 고속이며 단일 사이클의액세스 버스이다. 메모리(6)는 RAM, ROM, 캐쉬 블록, FLASH 메모리, 내부 DRAM 및 그것의 임의의 조합을 포함할 수 있다. 모든 다른 시스템의 모듈과 주변장치는 M-버스(23)를 통해 코어(9)에 연결된다. M-버스(23)는 다수의 버스 마스터중 하나에 의해 개시된 데이터 전송을 실행하는데 사용되는 내부 멀티 마스터 버스이다. 시스템 버스 제어기(8)는 다수의 기능을 제공한다. 시스템 버스 제어기(8)는 내부 M-버스(23)와 외부 E-버스 사이의 인터페이스를 제공한다. 또한, 시스템 버스 제어기(8)는 S-버스 상에서 모든 데이터 전송을 제어하는 초점(focal point)으로 작용한다. S-버스는 타이머와 시리얼 통신 채널과 같은 슬레이브 주변 모듈(12와 13)을 데이터 프로세서(3)에 접속하는데 사용된다.

본 발명에서, 코어(9)는 성능을 최대화하기 위해 고속, 단일 사이클의 K-버스(25)와 상호 접속된다. 이 고속 버스에 직접 연결되지 않은 전송에 대해, M-버스(23)는 코어(9) 및 마스터 모듈(14)과 같은 임의의 내부 버스 마스터로부터의 대역폭을 제공한다. 시스템 버스 제어기(8)는 내부 M-버스(23)와 외부 E-버스 사이의 접속을 제공하며, 또한 슬레이브 모듈(12와 13)과 같은 슬레이브 주변 모듈에 대해서 보다 저렴하고, 보다 낮은 대역폭의 S-버스에 의해 모든 데이터 전송을 위한 제어 기능을 제공한다.

도 2의 소자(205)와 같은, 외부 버스 마스터가 데이터 프로세서(3)의 내부 제어 메카니즘을 통해 외부 메모리를 제어하도록 허용하는 DRAM 제어기는 시스템 버스 제어기(8)내에서 구현된다. 일부의 시스템 버스 제어기(8)는 도 4에서 보다 상세히 나타난다.

데이터 처리 시스템(202)의 칩 선택 가능한 장치의 액세스 동작 중에, 외부 버스 마스터(205)(도 2에 도시됨)는, TS(전송 개시) 신호를 어서트(assert)함으로서, 원하는 데이터에 대응하는 적절한 어드레스 값을 제공함으로서, 데이터값이 판독되가나 또는 기록되는지를 표시하는 R/신호를 제공함으로서, 그리고 사이즈 버스를 제공함으로서 데이터 전송 요구를 시작한다. 본 발명을 구현하는데 사용되는 흐름도와 회로의 보다 상세한 설명을 위해 도 4와 도 5를 언급해보자.

TS 신호, 어드레스 값, R/신호 및 사이즈 버스가 외부 버스 마스터(205)로부터 출력된 경우, 이들은 디코드 및 어드레스 발생 회로(808)(도 4에 도시됨)에 저장된다. 버스 중재 회로(806)(도 4에 도시됨)는 데이터 프로세서(3)가 E-버스를 제어할 수 있는 때를 결정한다. BG 및 BD 신호가 부정되는 경우, 외부 장치는 E-버스를 제어할 수 있으며 버스 중재 회로(806)는마스터 신호를 어서트(assert)한다. BD는 내부 마스터가 E-버스를 구동하고 있지 않다는 것을 나타내기 위해 버스 중재 회로(806)에 의해 부정될 것이다. BR은 내부 마스터가 E-버스의 지배(mastership)를 필요로 하는 경우에 어서트(assert)된다. 따라서, 외부 버스 마스터(205)가 DRAM(207) 또는 메모리(206)로의 액세스가 희망되는 것을 나타내기 위해 적절한 제어 신호를 어서트(assert)하는 경우, 버스 중재 회로(806)는 BG 신호의 값을 조사하고 이것이 부정되었는지를 결정하고, 다음으로 버스 중재 회로(806)는 상기마스터 신호를 어서트(assert)한다. 이전에 언급한 바와 같이, 상기마스터 신호는 메모리 제어기(804)와 디코드 및어드레스 발생 회로(808) 양자에 제공된다.

다음으로, 디코드 및 어드레스 발생 회로(808)는 전송 개시(TS) 신호가 외부 버스 마스터(205)에 의해 어서트(assert)되었는지를 결정한다. 만일 TS 신호가 어서트(assert)되었다면, 디코드 및 어드레스 발생 회로(808)는 어드레스 값, R/신호 그리고 데이터 시스템(202)내의 장치가 액세스될 것인가를 결정하는 사이즈 버스를 디코드한다. 디코드 및 어드레스 발생회로(808)는 그것에 제공된 어드레스가 DRAM(207)내의 메모리 로케이션으로 액세스하는 것을 나타내기 위하여 DRAM_히트(DRAM_hit) 신호를 어서트(assert)한다. 유사하게, 디코드 및 어드레스 발생 회로(808)는 그것에 제공된 어드레스가 메모리(206)와 같은 칩 선택 가능한 외부 장치로 액세스하는 것을 나타내기 위해, CS_히트 신호를 어서트(assert)한다. 메모리(206)만이 본 발명의 실시예에서 나타나 있지만, 다른 칩 선택 가능한 장치도 메모리(206) 이외에 또는 그것을 대신하여 구현될 수 있다는 점을 이해하여야 한다. 다수의 칩 선택 가능한 장치를 포함하는 시스템에 있어서, CS_히트 신호는 임의의 이 장치가 액세스되는 경우에, 어드레스가 디코드 및 어드레스 발생 회로(808)에 제공되는지를 나타내도록 어서트(assert)될 것이다. 또한, 메모리(206)는 SRAM, ROM, EEPROM, EPROM, FLASH, 또는 시리얼 인터페이스 또는 타이머와 같은 임의의 칩 선택 가능한 장치와 같은 임의의 타입의 외부 메모리로서 구현될 수 있다.

외부 마스터에 의한 DRAM 액세스

도 5는 외부 버스 마스터(205)에 의한 DRAM(207)의 액세스에 대해 이후에 기술하는 동안 언급되어야 한다.

만일 DRAM_히트 신호가 DRAM(207)내의 메모리 로케이션이 액세스되었는지를 나타내도록 어서트(assert)되면, 메모리 제어기(804)는 다음으로 제어 레지스터(810)의 DCTR 레지스터(도 13b에서 도시됨)내의 DAEM(Drive Address during External Master DRAM accesses) 비트가 외부 버스 마스터(205)에 의한 DRAM(207)의 액세스 중에 모든 어드레스 라인 상에 메모리 제어기(804)의 출력 드라이버를 인에이블하기 위해 외부 사용자에 의해 프로그램되었는지를 결정한다. 만일 DAEM 필드가 세트되면(본 발명의 실시예에서는 논리값 1로 세트됨), 메모리 제어기(804)는 디코드 및 어드레스 발생 회로(808)가 E-버스의 어드레스 버스의 일부로부터 로우 어드레스를 나타내는 어드레스를 구동하게 한다. 1/2의 타이밍 사이클 이후에, RAS 신호는 메모리 제어기(804)에 의해 어서트(assert)된다. 다음으로, DCTR내의 RCD 필드에 의해 결정된 시간의 한 주기 이후에, 디코드 및 어드레스 발생 회로(808)는 E-버스의 어드레스 부분으로부터 도 14a 내지 도 14c에 기술된 바와 같은 디코드 및 어드레스 발생 회로(808)에 의해 형성된 컬럼 어드레스를 나타내는 새로운 어드레스를 구동시킨다. 1/2의 타이밍 사이클 이후에, CAS 버스는 메모리 제어기(804)에 의해 어서트(assert)된다. 또한, 이것이 DRAM(207)의 기록 액세스이면, DRAMW 신호는 어서트으로 되고 이것이 DRAM(207)의 판독 액세스이면 DRAMW 신호는 부정된다. 또한, 메모리 제어기(804)는 DRAM(207)의 액세스가 완료되는 경우, TA(전송 확인; Transfer Acknowledg) 신호를 외부 버스 마스터에 어서트(assert)한다.

도 6 내지 도 9는 본 발명의 여러 실시예에서 메모리 제어기(804)에 의해 구현된 타이밍을 나타내는 타이밍도를 제공한다.

도 6은 DRAM(207)이 먼저 기록되고 다음으로 판독되며, 제공된 어드레스 값이 구동되어야 하는지를 나타내도록 제어 레지스터(810)의 DCTR 내의 DAEM 필드가 어서트(assert)되는 본 발명의 제 1 실시예를 나타낸다. 도 6에서, Clk(Clock) 신호가 제공된다. 데이터 처리 시스템 내에서, 클럭 신호의 발생, 사용 및 라우팅은 기술상 잘 공지되어 있으므로 보다 상세히 논의하지 않을 것이다. 도 6에서 나타난 바와 같이, 외부 버스 마스터(205)는 제 1 타이밍 사이클 중에 어드레스 값, 전송 개시(TS) 신호, R/신호 및 사이즈 버스를 데이터 프로세서(3)에 제공한다. 이 타이밍 예의 제 1 부분에서, R/신호는 데이터 프로세서(3)가 DRAM(207)에 데이터 값을 기록하고 있는지를 나타내기 위해 부정된다는 점을 주의하라.

외부 버스 마스터(205)가 어드레스 값을 전송한지 한 타이밍 사이클 이후에, 외부 버스 마스터(205)는 TS 신호를 부정하며, 어드레스를 트리-스테이트(tri-state)로 하며 기록되는 데이터를 구동한다.

TS 신호가 부정된지 한 타이밍 사이클 이후에, 일부의 시스템 버스 제어기(8)의 디코드 및 어드레스 발생 회로(808)는, DRAM(207)에서 메모리 로케이션으로의 액세스에 필요한 로우 어드레스처럼, 외부 버스 마스터(205)에 의해 이전에 구동된 어드레스를 출력한다. 디코드 및 어드레스 발생 회로(808)가 DRAM(207)에 어드레스를 제공하는 경우, 메모리 제어기(804)는 또한 기록 동작이 실행되고있다는 것을 나타내기 위해 DRAMW 신호를 어서트(assert)한다. 1/2 타이밍 사이클 이후에, 메모리 제어기(804)는 그것에 제공되고 있는 어드레스가 로우 어드레스라는 것을 DRAM(207)에 나타내기 위해 RAS 신호를 어서트(assert)한다.

어드레스가 한 타이밍 사이클 동안 제공된 후, 디코드 및 어드레스 발생 회로(808)는, DRAM(207)에 로우 어드레스가 제공된 동일한 집적회로 핀을 통하여, 일부가 컬럼 어드레스인 새로운 어드레스 값을 DRAM(207)에 제공한다. 1/2의 타이밍 사이클 이후에, 디코더 및 어드레스 발생 회로(808)가 새로운 어드레스 값을 제공한 후, 메모리 제어기(804)는 그것에 제공된 어드레스가 컬럼 어드레스라는 것을 DRAM(207)에 나타내기 위해 CAS 버스를 어서트(assert)한다.

1/2의 타이밍 사이클 이후에, 메모리 제어기(804)는 버스 액세스의 종료를 나타내기 위해 외부 버스 마스터(205)에 TA 신호를 어서트(assert)한다.

TA 신호가 어서트(assert)된지 한 타이밍 사이클 이후에, 메모리 제어기(805)는 RAS 신호, CAS 버스, TA 신호를 부정한다. 또한, DRAM(207)에 제공된 어드레스 및 데이터 값은 트리-스테이트(tri-state)로 된다.

다음으로, DRAM 판독 동작은 실행되고, 이것의 타이밍은 도 6에 나타난다. 도 6에서 나타난 바와 같이, 외부 버스 마스터(205)는 어드레스 값, 전송 개시(TS)신호, R/신호 및 사이즈 버스를 제 1 타이밍 사이클 동안에 데이터 프로세서(3)에 제공한다. 상기 타이밍 예의 제 1 부분에서, R/신호는 데이터 프로세서(3)가 DRAM(207)으로부터 데이터 값을 판독하고 있는지를 나타내기 위해어서트(assert)된다는 점을 주의해야 한다.

외부 버스 마스터(205)가 어드레스 값을 전송한지 한 타이밍 사이클 이후에, TS 신호는 부정되고 어드레스 버스는 외부 버스 마스터(205)에 의해 트리-스테이트(tri-state)로 된다.

TS 신호가 부정된지 한 타이밍 사이클 이후에, 일부의 시스템 버스 제어기(8)의 디코드 및 어드레스 발생 회로(808)는 DRAM(207)에서 메모리 위치를 액세스하는데 필요한 로우 어드레스처럼 외부 버스 마스터(205)에 의해 사전에 구동되는 어드레스 값을 출력한다. 디코드 및 어드레스 발생회로(808)가 어드레스를 DRAM(207)에 제공하는 경우, 메모리 제어기(804)는 판독 동작이 실행되고 있는지를 나타내기 위해 DRAMW 신호를 부정한다.

디코드 및 어드레스 발생 회로(808)가 어드레스를 제공한지 1/2의 타이밍 사이클 이후에, 메모리 제어기(804)는 이것에 제공되고 있는 어드레스가 로우 어드레스인지를 DRAM(207)에 나타내기 위해 RAS 신호를 어서트(assert)한다.

어드레스가 한 타이밍 사이클동안 제공된 후, 디코드 및 어드레스 발생 회로(808)는 DRAM(207)에 로우 어드레스가 제공된 동일한 집적회로 핀을 통하여, 일부가 컬럼 어드레스인 새로운 어드레스 값을 DRAM(207)에 제공한다.

디코드 및 어드레스 발생 회로(808)가 새로운 어드레스를 제공한지 1/2의 타이밍 사이클 이후에, 메모리 제어기(804)는 그것에 제공되고 있는 어드레스가 컬럼 어드레스인지를 DRAM(207)에 나타내기 위해 CAS 버스를 어서트(assert)한다.

1/2의 타이밍 사이클 이후에, 메모리 제어기(804)는 버스 액세스의 종료를나타내기 위해 TA 신호를 어서트(assert)한다. TA 신호가 먼저 부정되면, E-버스를 통해 DRAM(207)에 제공된 데이터는 유효하고 에러 없이 외부 버스 마스터(205)에 의해 사용될 수 있다.

TA 신호가 한 클럭 사이클 이후에 어서트(assert)되는 경우, RAS 신호, CAS 버스, TA 신호는 부정된다. 또한, 메모리 제어기(804)에 의해 제공된 어드레스와 DRAM(207)에 의해 제공된 데이터는 트리-스테이트(tri-state)로 된다.

도 7은 DRAM(207)이 먼저 기록되고 다음으로 판독되며, 제공된 어드레스 값이 구동되어야 하는지를 나타내도록 제어 레지스터(810)의 DCTR 내의 DAEM 필드가 어서트(assert)되는 본 발명의 제 2 실시예를 나타낸다. 도 7에서, Clk(Clock) 신호가 제공된다. 데이터 처리 시스템 내에서 클럭 신호의 발생, 사용 및 라우팅은 기술상 잘 공지되어 있으므로 보다 상세히 논의하지 않을 것이다. 도 7에서 나타난 바와 같이, 외부 버스 마스터(205)는 제 1 타이밍 사이클 중에, 어드레스 값, 전송 개시(TS) 신호, R/신호 및 사이즈 버스를 데이터 프로세서(3)에 제공한다. 이 타이밍 예의 제 1 부분에서, R/신호는 데이터 프로세서(3)가 DRAM(207)에 데이터 값을 기록하고 있는지를 나타내기 위해 부정된다는 점을 주의하라.

외부 버스 마스터(205)가 어드레스 값을 전송한지 한 타이밍 사이클 이후에, 외부 버스 마스터(205)는 TS 신호를 부정하며, 어드레스를 트리-스테이트(tri-state)로 하며 기록되는 데이터를 구동한다.

TS 신호가 부정된지 한 타이밍 사이클 이후에, 일부의 시스템 버스제어기(8)의 디코드 및 어드레스 발생 회로(808)는, DRAM(207)에서 메모리 로케이션으로의 액세스에 필요한 로우 어드레스처럼, 외부 버스 마스터(205)에 의해 이전에 구동된 어드레스를 출력한다. 디코드 및 어드레스 발생 회로(808)가 DRAM(207)에 어드레스를 제공하는 경우, 메모리 제어기(804)는, 기록 동작이 실행되고 있다는 것을 나타내기 위해 DRAMW 신호를 또한 어서트(assert)한다. 1/2 타이밍 사이클 이후에, 메모리 제어기(804)는 그것에 제공되고 있는 어드레스가 로우 어드레스라는 것을 DRAM(207)에 나타내기 위해 RAS 신호를 어서트(assert)한다.

어드레스가 한 타이밍 사이클 동안 제공된 후, 디코드 및 어드레스 발생 회로(808)는, DRAM(207)에 로우 어드레스가 제공된 동일한 집적회로 핀을 통하여, 일부가 컬럼 어드레스인 새로운 어드레스 값을 DRAM(207)에 제공한다. 1/2의 타이밍 사이클 이후에, 디코더 및 어드레스 발생 회로(808)가 새로운 어드레스 값을 제공한 후, 메모리 제어기(804)는 그것에 제공된 어드레스가 컬럼 어드레스라는 것을 DRAM(207)에 나타내기 위해 CAS 버스를 어서트(assert)한다.

1/2의 타이밍 사이클 이후에, 메모리 제어기(804)는 버스 액세스의 종료를 나타내기 위해 외부 버스 마스터(205)에 TA 신호를 어서트(assert)한다.

TA 신호가 어서트(assert)된지 한 타이밍 사이클 이후에, 메모리 제어기(804)는 CAS 버스 및 TA 신호를 부정한다. 또한, DRAM(207)에 제공된 어드레스 및 데이터 값은 트리-스테이트(tri-state)로 된다. RAS 신호는 페이지 상의 연속적인 어드레스가 액세스되는 동안 어서트(assert)된 상태를 유지한다는 점을 주의하라. RAS 신호는,

현재의 DRAM 뱅크에 대한 어드레스가 동일한 페이지 또는 로우 상에 있지 않을 때까지(1),

다른 DRAM 뱅크로의 액세스가 발생할 때까지(2), 또는

리프레쉬 동작이 발생할 때까지(3) 어서트(assert)된 상태를 유지한다.

다음으로, DRAM의 판독 동작은 실행되고, 그것의 타이밍은 도 7에 나타난다. 도 7에서 나타난 바와 같이, 외부 버스 마스터(205)는 어드레스 값, 전송 개시(TS)신호, R/신호 및 사이즈 버스를 제 1 타이밍 사이클 중에 데이터 프로세서(3)에 제공한다. 이 타이밍 예의 제 1 부분에서, R/신호는 데이터 프로세서(3)가 DRAM(207)으로부터 데이터를 판독하고 있는지를 나타내기 위해 어서트(assert)된다는 점을 주의해야 한다.

외부 버스 마스터(205)가 어드레스 값을 전송한지 한 티이밍 사이클 이후에, TS 신호는 부정되고 어드레스 버스는 외부 버스 제어기(205)에 의해 트리-스테이트(tri-state)로 된다.

TS 신호가 부정된지 한 타이밍 사이클 이후에, 디코드 및 어드레스 발생 회로(808)는 일부가 컬럼 어드레스인 새로운 어드레스 값을, DRAM(207)에 로우 어드레스가 제공된 동일 집적 회로 핀을 통하여, DRAM(207)에 제공한다.

디코드 및 어드레스 발생 회로(808)가 새로운 어드레스를 제공한지 1/2의 타이밍 사이클 이후에, 메모리 제어기(804)는 그것에 제공되고 있는 어드레스가 컬럼 어드레스인지를 DRAM(207)에 나타내기 위해 CAS 버스를 어서트(assert)한다.

1/2의 타이밍 사이클 이후에, 메모리 제어기(804)는 버스 액세스의 종료를 나타내기 위해 TA 신호를 어서트(assert)한다. TA 신호가 먼저 부정되면, E-버스를 통해 DRAM(207)에 제공된 데이터는 유효하고 에러 없이 외부 버스 마스터(205)에 의해 사용될 수 있다. TA 신호가 한 클럭 사이클 이후에 어서트(assert)되는 경우, CAS 버스 및 TA 신호는 부정된다. 또한 메모리 제어기(804)에 의해 제공된 어드레스와 DRAM(207)에 의해 제공된 데이터는 트리-스테이트(tri-state)로 된다.

도 8은 DRAM(207)이 먼저 기록되고 다음으로 판독되며, 제공된 어드레스 값이 구동되어야 하는지를 나타내도록 제어 레지스터(810)의 DCTR 내의 DAEM 필드가 어서트(assert)되는 본 발명의 제 2 실시예를 나타낸다. 도 8에서, Clk(Clock) 신호가 제공된다. 데이터 처리 시스템 내에서 클럭 신호의 발생, 사용 및 라우팅은 기술상 잘 공지되어 있으므로 보다 상세히 논의하지 않을 것이다.

도 8에서 나타난 바와 같이, 외부 버스 마스터(205)는 제 1 타이밍 사이클중에 어드레스 값, 전송 개시(TS) 신호, R/신호 및 사이즈 버스를 데이터 프로세서(3)에 제공한다. 상기 타이밍 예의 제 1 부분에서, R/신호는 데이터 프로세서(3)가 DRAM(207)에 데이터 값을 기록하고 있는지를 나타내기 위해 부정된다는 점을 주의하라.

외부 버스 마스터(205)가 어드레스 값을 전송한지 한 타이밍 사이클 이후에, 외부 버스 마스터(205)는 TS 신호를 부정하며, 어드레스를 트리-스테이트(tri-state)로 하며 기록되는 데이터를 구동한다. TS 신호가 부정되는 경우, 일부의 시스템 버스 제어기(8)의 디코드 및 어드레스 발생 회로(808)는, DRAM(207)에서 메모리 로케이션으로의 액세스에 필요한 로우 어드레스처럼, 외부 버스 마스터(205)에 의해 구동된 어드레스를 보강한다. 디코드 및 어드레스 발생 회로(808)가 DRAM(207)에 어드레스를 제공하는 경우, 메모리 제어기(804)는, 기록 동작이 실행되고 있다는 것을 나타내기 위해 DRAMW 신호를 또한 어서트(assert)한다. 1/2 타이밍 사이클 이후에, 메모리 제어기(804)는 그것에 제공되고 있는 어드레스가 행 어드레스라는 것을 DRAM(207)에 나타내기 위해 RAS 신호를 어서트(assert)한다.

어드레스가 한 타이밍 사이클 동안 제공된 후, 디코드 및 어드레스 발생 회로(808)는, DRAM(207)에 로우 어드레스가 제공된 동일한 집적회로 핀을 통하여, 일부가 컬럼 어드레스인 새로운 어드레스 값을 DRAM(207)에 제공한다. 1/2의 타이밍 사이클 이후에, 디코더 및 어드레스 발생 회로(808)가 새로운 어드레스 값을 제공한 후, 메모리 제어기(804)는 그것에 제공된 어드레스가 컬럼 어드레스라는 것을 DRAM(207)에 나타내기 위해 CAS 버스를 어서트(assert)한다.

1/2의 타이밍 사이클 이후에, 메모리 제어기(804)는 버스 액세스의 종료를 나타내기 위해 외부 버스 마스터(205)에 TA 신호를 어서트(assert)한다.

TA 신호가 어서트(assert)된지 한 타이밍 사이클 이후에, 메모리 제어기(804)는 RAS 신호, CAS 버스 및 TA 신호를 부정한다. 또한, DRAM(207)에 제공된 어드레스 및 데이터 값은 트리-스테이트(tri-state)로 된다.

다음으로, DRAM 판독 동작이 실행되고, 그것의 타이밍은 도 8에 나타난다. 도 8에서 나타난 바와 같이, 외부 버스 마스터(205)는 어드레스 값, 전송 개시(TS)신호, R/신호 및 사이즈 버스를 제 1 타이밍 사이클 중에 데이터 프로세서(3)에 제공한다. 이 타이밍 예의 제 1 부분에서, R/신호는 데이터 프로세서(3)가 DRAM(207)으로부터 데이터를 판독하고 있는지를 나타내기 위해 어서트(assert)된다는 점을 주의해야 한다.

외부 버스 마스터(205)가 어드레스 값을 전송한지 한 타이밍 사이클 이후에, TS 신호와 어드레스 버스는 부정된다. TS 신호가 부정되는 경우, 일부의 시스템 버스 제어기(8)의 디코드 및 어드레스 발생 회로(808)는 DRAM(207)에서 메모리 로케이션으로의 액세스에 필요한 로우 어드레스처럼, 외부 버스 마스터(205)에 의해 구동된 어드레스 값을 보강한다. 디코드 및 어드레스 발생회로(808)가 DRAM(207)에 어드레스를 제공하는 경우, 메모리 제어기(804)는 판독 동작이 실행되고 있는지를 나타내기 위해 DRAMW 신호를 부정한다.

디코드 및 어드레스 발생 회로(808)가 어드레스를 제공한지 1/2의 타이밍 사이클 이후에, 메모리 제어기(804)는 그것에 제공되고 있는 어드레스가 로우 어드레스인지를 DRAM(207)에 나타내기 위해 RAS 신호를 어서트(assert)한다.

어드레스가 한 타이밍 사이클 동안 제공된 후, 디코드 및 어드레스 발생 회로(808)는, DRAM(207)에 로우 어드레스가 제공된 동일한 집적회로 핀을 통하여, 일부가 컬럼 어드레스인 새로운 어드레스 값을 DRAM(207)에 제공한다.

디코드 및 어드레스 발생 회로(808)가 새로운 어드레스를 제공한지 1/2의 타이밍 사이클 이후에, 메모리 제어기(804)는 이것에 제공되고 있는 어드레스가 컬럼어드레스인지를 DRAM(207)에 나타내기 위해 CAS 버스를 어서트(assert)한다.

1/2의 타이밍 사이클 이후에, 메모리 제어기(804)는 버스 액세스의 종료를 나타내기 위해 TA 신호를 어서트(assert)한다. TA 신호가 먼저 부정되면, E-버스를 통해 DRAM(207)에 제공된 데이터는 유효하고 에러 없이 외부 버스 마스터(205)에 의해 사용될 수 있다. TA 신호가 한 클럭 사이클 이후에 어서트(assert)되는 경우, RAS 신호, CAS 버스 및 TA 신호는 부정된다. 또한, 메모리 제어기(804)에 의해 제공된 어드레스와 DRAM(207)에 의해 제공된 데이터는 트리-스테이트(tri-state)로 된다.

도 9는 제어 레지스터(810)내의 DCTR의 DAEM 필드가 어서트(assert)되지 않는 경우를 나타낸다. DAEM 필드가 어서트(assert)되지 않는 경우, 데이터 처리 시스템(202)의 설계자는 선행 기술의 시스템에서 요구되는 것과 같은 멀티플렉서를 구현하도록 요구받을 것이다. 설계자로 하여금 외부 멀티플렉서를 구현할 것인지 아닌지를 선택하도록 함으로서, 본 발명은 매우 큰 유연성을 제공한다.

도 9는 DRAM(207)이 먼저 기록되고 다음으로 판독되며, 어드레스가 디코드 및 어드레스 발생 회로(808)에 의해 구동되어야 하는지를 나타내도록 제어 레지스터(810)의 DCTR 내의 DAEM 필드가 어서트(assert)되는 본 발명의 제 4 실시예를 나타낸다. 도 9에서, Clk(Clock) 신호가 제공된다. 데이터 처리 시스템 내에서 클럭 신호의 발생, 사용 및 라우팅은 기술상 잘 공지되어 있으므로 보다 상세히 논의하지 않을 것이다. 도 9에서 나타난 바와 같이, 외부 버스 마스터(205)는 제 1 타이밍 사이클 중에, 어드레스 값, 전송 개시(TS) 신호, R/신호 및 사이즈 버스를데이터 프로세서(3)에 제공한다. 상기 타이밍 예의 제 1 부분에서, R/신호는 데이터 프로세서(3)가 DRAM(207)에 데이터 값을 기록하고 있는지를 나타내기 위해 부정된다는 점을 주의하라.

외부 버스 마스터(205)가 어드레스 값을 전송한지 한 타이밍 사이클 이후에, 외부 버스 마스터(205)는 TS 신호를 부정하며, 기록되는 데이터를 구동한다. 1/2의 타이밍 사이클 이후에, 메모리 제어기(804)는 이것에 제공되고 있는 어드레스가 로우 어드레스인지를 DRAM(207)에 나타내기 위해 RAS 신호를 어서트(assert)한다.

한 타이밍 사이클 후에, 메모리 제어기(804)는 그것에 제공된 어드레스가 컬럼 어드레스인지를 DRAM(207)에 나타내기 위해 CAS 버스를 어서트(assert)한다.

1/2의 타이밍 사이클 후에, 메모리 제어기(804)는 버스 액세스의 종료를 나타내기 위해 외부 버스 마스터(205)에 TA 신호를 어서트(assert)한다.

TA 신호가 어서트(assert)된지 한 타이밍 사이클 이후에, 메모리 제어기(805)는 RAS 신호, CAS 버스, TA 신호를 부정한다. 또한, DRAM(207)에 제공된 어드레스 및 데이터 값은 트리-스테이트(tri-state)로 된다.

다음으로, DRAM 판독 동작은 실행되고, 그것의 타이밍은 도 9에 나타난다. 도 9에서 나타난 바와 같이, 외부 버스 마스터(205)는 어드레스 값, 전송 개시(TS)신호, R/신호 및 사이즈 버스를 제 1 타이밍 사이클 중에 데이터 프로세서(3)에 제공한다. 이 타이밍 예의 제 1 부분에서, R/신호는 데이터 프로세서(3)가 DRAM(207)으로부터 데이터 값을 판독하고 있는지를 나타내기 위해 어서트(assert)된다는 점을 주의해야 한다.

외부 버스 마스터(205)가 어드레스 값을 전송한지 한 타이밍 사이클 이후에, TS 신호는 부정된다.

1/2의 타이밍 사이클 후에, 메모리 제어기(804)는 그것에 제공된 어드레스가 로우 어드레스인지를 DRAM(207)에 나타내기 위해 RAS 신호를 어서트(assert)한다.

한 타이밍 사이클 후에, 메모리 제어기(804)는 그것에 제공된 어드레스가 컬럼 어드레스인지를 DRAM(207)에 나타내기 위해 CAS 버스를 어서트(assert)한다.

1/2의 타이밍 사이클 후에, 메모리 제어기(804)는 버스 액세스의 종료를 나타내기 위해 TA 신호를 어서트(assert)한다. TA 신호가 먼저 부정되면, E-버스를 통해 DRAM(207)에 제공된 데이터는 유효하고 에러 없이 외부 버스 마스터(205)에 의해 사용될 수 있다. TA 신호가 한 클럭 사이클 이후에 어서트(assert)되는 경우, RAS 신호, CAS 버스, TA 신호는 부정된다. 또한, DRAM(207)에 의해 제공된 데이터는 트리-스테이트(tri-state)로 된다.

도 6 내지 도 9 각각에서, 컬럼 어드레스는 CAS 버스가 어서트(assert)되는 경우에 DRAM(207)에 제공된다. 본 발명의 작동 결과로 생기는 어드레스 값의 예는 도 14a 내지 도 14c에 나타나 있다. 각각의 이 도면은 다른 포트 사이즈가 본 발명에서 개시된 회로 및 방법의 작동 중에 액세스된 DRAM에서 구현되는 경우에 요구되는 멀티플렉싱을 나타낸다.

블록도, 흐름도, 타이밍도를 통하여 외부 버스 마스터에 의한 DRAM 액세스의 실행에 대한 이전의 설명으로부터, 데이터 프로세서, 외부 메모리 및 외부 마스터사이에서 정보를 통신하는 장치 및 방법이 설명되었다. 본 발명의 이 부분을 요약하면, 데이터 처리 시스템내의 외부 메모리를 제어하여 DRAM 회로 액세스 중에 멀티플렉싱 기능을 실행하는데 어떤 외부 회로도 필요 없는 작동에 관한 회로와 방법이 제공된다. 또한, 데이터 프로세서(3)에서 내부적인 멀티플렉싱을 사용하고 CAS 버스를 사용하여, 본 발명은 외부 멀티플렉서, 그리고 외부 마스터 장치에 의한 DRAM 액세스를 위한 데이터 프로세서상의 전용의 집적회로 핀의 필요성을 제거한다. 본 발명은 도 1에서 나타난 바와 같이, 선행 기술의 데이터 처리 시스템이 필요로 하는 것과 같은 전용의 집적 회로 핀의 요청 없이 DRAM 회로로의 액세스에 필요한 멀티플렉싱 기능을 구현한다. 본 발명의 데이터 프로세서에 관한 집적회로 핀의 감소된 필요조건과 증가된 유연성의 증가로 인해 시스템 비용은 저렴해지고, 반도체 시장에서의 최근의 발전을 이용하도록 용이하게 업데이트될 수 있다.

외부 마스터에 의한 칩 선택가능 액세스에 관하여

도 5에서는, 본 발명의 다른 양태는 보다 상세히 기술될 것이다. CS_히트 신호가 메모리(206)와 같은, 칩 선택 가능한 장치내의 로케이션이 액세스되었다는 것을 나타내도록 어서트(assert)되면, 다른 메모리 장치의 외부 버스 마스터(205)에 의해 시작된 액세스 동작 중에 전송 확인의 출력 및 어서트(assert)를 제어하기 위해 메모리 제어기(804)는 제어 레지스터(810)의 CSCR 레지스터(도 12c에는 도시되지 않음)내의 EMAA(External Master Automatic Acknowledge) 필드가 외부 사용자에 의해 프로그램되었는지를 나타내도록 어서트(assert)된다. EMAA 필드가 어서트(assert)되면(본 발명의 실시예에서는 논리값이 1), 메모리 제어기(804)는도 12c의 CSCR 레지스터 내에 프로그램된 대기 상태 값(WS[3:0])에 의해 결정된 시간의 길이 동안 전송 확인(TA; Transfer Acknowledge) 신호를 부정하고, 한 클럭 사이클동안 TA 신호를 어서트(assert)한다. CSCR과 같은, 칩 선택 레지스터는 주어진 어드레스 공간에 대응한다. 칩 선택 레지스터를 사용하고 구현하는 것은 데이터 처리 기술에서 잘 공지되어 더 상세히 기술하지 않을 것이다.

EMAA 필드가 어서트(assert)된 경우, 메모리 제어기(804)는 메모리(206)에 대한 제어를 제공하기 위해, CS(Chip Select) 신호, WE(Write Enable) 버스, TA 신호를 제공한다. 이 신호를 사용하여, 데이터 프로세서(3)는 외부 버스 마스터(205)에 대한 메모리(206)를 효과적으로 제어한다. 역으로, EMAA 필드가 부정되면, 메모리 제어기(804)는 단지 CS 신호 및 WE(Write Enable) 버스만 제공한다. 메모리(206)에 대한 제어를 제공하기 위해 TA(전송 확인) 신호를 제공하기보다는, 메모리 제어기(804)는 외부 버스 마스터(205) 또는 다른 외부 회로(여기서는 도시되지 않음)에 의해 외부에서 제공된 TA 신호를 샘플링한다.

도 10, 도 11, 도 15 및 도 16은 본 발명의 여러 실시예에서 메모리 제어기(804)에 의해 구현된 타이밍을 나타내는 타이밍도를 제어한다.

도 10은 메모리가 먼저 기록된 후 판독되며, 메모리 제어기(804)가 TA(전송 확인) 신호를 제공해야 하는지를 나타내도록 제어 레지스터(810)의 CSCR 내의 EMAA 필드가 어서트(assert)되는 본 발명의 제 1 실시예를 나타낸다. 도 10에서, Clk(Clock) 신호가 제공된다. 데이터 처리 시스템 내에서 클럭 신호의 발생, 사용 및 라우팅은 기술상 잘 공지되어 있으므로 보다 상세히 논의하지 않을 것이다. 도10에서 나타난 바와 같이, 외부 버스 마스터(205)는 제 1 타이밍 사이클 중에 어드레스 값, 전송 개시(TS) 신호, R/신호 및 사이즈 버스를 데이터 프로세서(3)에 제공한다. 이 타이밍 예의 제 1 부분에서, R/신호는 외부 마스터(205)가 메모리(206)에 데이터 값을 기록하고 있는지를 나타내기 위해 부정된다는 점을 주의하라. 다음의 타이밍 사이클 중에, TS 신호는 부정되고 외부 버스 마스터(205)는 메모리(206)에 기록되는 데이터를 구동하기 시작한다. 이 타이밍 사이클 중에, 전송 확인(TA) 신호는 트리-스테이트(tri-state)로 된다.

TS 신호가 부정된지 한 타이밍 사이클 이후에, 일부의 시스템 버스 제어기(8)의 메모리 제어기(804)는 메모리(206) 또는 어느 다른 선택된 장치가 외부 버스 마스터(205)에 의해 액세스되었는지를 나타내기 위해 CS(Chip Select) 신호를 어서트(assert)한다. 또한, 메모리 제어기(804)는 전송 확인(TA) 신호를 동일한 타이밍 사이클 중에 부정한다.

다음의 타이밍 사이클 중에, 메모리 제어기(804)는 외부 마스터(205)에 의해 제공된 데이터로 기록된 어드레스 버스를 통해 전송된 어드레스 로케이션 메모리(206)를 인에이블 상태로 만들기 위해, 기록 인에이블(WE) 버스를 어서트(assert)한다. 또한, 메모리 제어기(804)는 전송 확인(TA) 신호를 이 다음의 타이밍 사이클 중에 어서트(assert)한다.

다음의 타이밍 사이클 중에, TA 신호는 CS 신호와 WE 버스가 부정되고 데이터 값이 트리-스테이트(tri-state)로 되는 동안 다시 부정된다.

다음으로, 데이터 판독 동작은 실행되고, 그것의 타이밍은 도 10에 나타난다. 도 10에서 나타난 바와 같이, 외부 버스 마스터(205)는 다른 어드레스 값, 전송 개시(TS) 신호, R/신호 및 사이즈 버스를 제 1 타이밍 사이클 중에 데이터 프로세서(3)에 제공한다. 이 타이밍 예의 제 1 부분에서, R/신호는 외부 버스 마스터(205)가 메모리(206)로부터 데이터 값을 판독하고 있는지를 나타내기 위해 어서트(assert)된다는 점을 주의해야 한다. 이 타이밍 사이클 중에, 메모리 제어기(804)에 의해 출력된 전송 확인(TA) 신호는 트리-스테이트(tri-state)로 된 채 유지된다.

TS 신호가 부정된지 한 타이밍 사이클 이후에, 일부의 시스템 버스 제어기(8)의 메모리 제어기(804)는 메모리(206) 또는 임의의 다른 선택된 장치가 외부 버스 마스터(205)에 의해 액세스되었는지를 나타내기 위해 칩 선택(CS) 신호를 어서트(assert)한다. 또한, 메모리 제어기((804)는 전송 확인(TA) 신호를 동일한 타이밍 사이클 중에 어서트(assert)한다. 시간내의 상기 시점에서, 메모리(206)는 외부 버스 마스터(205)에 유효한 데이터 값을 제공한다.

다음의 타이밍 사이클 중에, 메모리 제어기(804)는 전송 확인(TA) 신호와 CS 신호를 부정한다. 다음의 타이밍 사이클 중에, 메모리(206)는 외부 버스 마스터(205)에 의해 상기로부터 판독된 데이터 값을 전송하는데 이전에 사용됐던 집적회로 핀을 트리-스테이트(tri-state)로 한다.

다음의 타이밍 사이클 중에, 메모리 제어기(804)로부터 출력된 TA 신호는 다시 트리-스테이트(tri-state)로 된다.

도 15는 메모리(206)가 먼저 기록되고 다음으로 판독되며, 메모리 제어기(804)가 전송 확인(TA) 신호를 제공하지 않아야 하는지를 나타내도록 제어 레지스터(810)의 CSCR 내의 EMAA 필드가 어서트(assert)되는 본 발명의 제 1 실시예를 나타낸다. 이 경우에, 메모리 제어기(804)로부터 출력된 TA 신호는 트리-스테이트(tri-state)로 될 것이고, TA 신호는 외부 버스 마스터(205) 또는 다른 외부 회로(여기서는 도시되지 않음)에 의해 외부에서 제공되어야 한다.

도 15에서, Clk(Clock) 신호가 제공된다. 데이터 처리 시스템 내에서 클럭 신호의 발생, 사용 및 라우팅은 기술상 잘 공지되어 있으므로 보다 상세히 논의하지 않을 것이다. 도 15에서 나타난 바와 같이, 외부 버스 마스터(205)는 제 1 타이밍 사이클 중에 어드레스 값, 전송 개시(TS) 신호, R/신호 및 사이즈 버스를 데이터 프로세서(3)에 제공한다. 이 타이밍 예의 제 1 부분에서, R/신호는 외부 마스터(205)가 메모리(206)에 데이터 값을 기록하고 있는지를 나타내기 위해 부정된다는 점을 주의하라. 다음의 타이밍 사이클 중에, TS 신호는 부정되고 외부 버스 마스터(205)는 메모리(206)에 기록되는 데이터를 구동하기 시작한다. 이 전체 타이밍 시퀀스 중에, 메모리 제어기(804)로부터 출력된 전송 확인(TA) 신호는 트리-스테이트(tri-state)로 된 채 유지된다.

TS 신호가 부정된지 한 타이밍 사이클 이후에, 일부의 시스템 버스 제어기(8)의 메모리 제어기(804)는 메모리(206) 또는 임의의 다른 선택된 장치가외부 버스 마스터(205)에 의해 액세스되었는지를 나타내기 위해 칩 선택(CS) 신호를 어서트(assert)한다. 이 타이밍 사이클 중에, 외부 버스(205) 또는 다른 외부 회로(여기서는 도시되지 않음)로부터 출력된 TA 신호는 부정된 채 유지된다.

다음의 타이밍 사이클 중에, 메모리 제어기(804)는, 외부 마스터(205)에 의해 제공된 데이터로 기록된 어드레스 버스를 통해 전송된 어드레스 로케이션 메모리(206)를 인에이블 상태로 만들기 위해, 기록 인에이블(WE) 버스를 어서트(assert)한다. 또한, 외부 버스 마스터(205) 또는 다른 외부 회로(여기서는 도시되지 않음)는 전송 확인(TA) 신호를 다음의 타이밍 사이클 중에 어서트(assert)한다.

다음의 타이밍 사이클 중에, TA 신호는 CS 신호와 WE 버스가 부정되고 데이터 값이 트리-스테이트(tri-state)로 되는 동안 다시 부정된다. TA 신호는 외부 버스 마스터(205) 또는 다른 외부 회로에 의해 요구된 다수의 대기 상태이후에 어서트(assert)된다. TA 신호를 어서트(assert)하는 외부 버스 마스터(205) 또는 다른 외부 회로는, 제어 레지스터(810)의 CSCR의 WS[3:0] 비트에 의해 나타난 대기 상태의 수에 관계없이, CS 신호와 WE 버스의 어서트(assert)를 임의의 수의 사이클까지 확장시킨다.

다음으로, 메모리 판독 동작은 실행되고, 그것의 타이밍은 도 15에 나타난다. 도 15에서 나타난 바와 같이, 외부 버스 마스터(205)는 어드레스 값, 전송 개시(TS) 신호, R/신호 및 사이즈 버스를 제 1 타이밍 사이클 중에 데이터 프로세서(3)에 제공한다. 이 타이밍 예의 제 1 부분에서, R/신호는 외부 버스 마스터(205)가 메모리(206)로부터 데이터를 판독하고 있는지를 나타내기 위해 어서트(assert)된다는 점을 주의해야 한다. 이 타이밍 사이클 중에, 메모리 제어기(804)에 의해 출력된 전송 확인(TA) 신호는 트리-스테이트(tri-state)로 되어 유지된다.

TS 신호가 부정된지 한 타이밍 사이클 이후에, 일부의 시스템 버스 제어기(8)의 메모리 제어기(804)는 메모리(206) 또는 임의의 다른 선택된 장치가 외부 버스 마스터(205)에 의해 액세스되었는지를 나타내기 위해 칩 선택(CS) 신호를 어서트(assert)한다. 이 타이밍 사이클 중에, 외부 버스 마스터(205) 또는 다른 외부 회로로부터 출력된 TA 신호는 부정된 상태로 유지된다.

다음의 타이밍 사이클 중에, 메모리(206)는 외부 버스 마스터(205)에 유효한 데이터 값을 제공한다. 외부 버스 마스터(205) 또는 다른 외부 회로는 버스 사이클의 종료를 나타내는 TA 신호를 어서트(assert)한다.

다음의 타이밍 사이클 중에, TA 신호는 CS 신호가 부정되고 데이터 값이 트리-스테이트(tri-state)로 되는 동안 다시 부정된다. TA 신호는 외부 버스 마스터(205)에 의해 요청되고 외부 버스 마스터(205) 또는 다른 외부 회로에 의해 결정된 다수의 대기 상태이후에 어서트(assert)된다. TA 신호를 어서트(assert)하는 외부 버스 마스터(205) 또는 다른 외부 회로는, 제어 레지스터(810)의 CSCR의 WS[3:0]비트에 의해 나타난 대기 상태의 수에 관계없이, CS 신호의 어서트(assert)를 임의의 수의 사이클까지 확장시킨다.

도 11은 메모리(206)가 먼저 기록되고 다음으로 판독되며, 메모리 제어기(804)가 전송 확인(TA) 신호를 제공해야 하는지를 나타내도록 제어 레지스터(810)의 CSCR 내의 EMAA 필드가 어서트(assert)되는 본 발명의 제 3 실시예를 나타낸다. 도 11에서, Clk(Clock) 신호가 제공된다. 데이터 처리 시스템 내에서 클럭 신호의 발생, 사용 및 라우팅은 기술상 잘 공지되어 있으므로 보다 상세히 논의하지 않을 것이다. 도 11에서 나타난 바와 같이, 외부 버스 마스터(205)는 제 1 타이밍 사이클 중에 어드레스 값, 전송 개시(TS) 신호, R/신호 및 사이즈 버스를 데이터 프로세서(3)에 제공한다. 이 타이밍 예의 제 1 부분에서, R/신호는 외부 버스 마스터(205)가 메모리(206)에 데이터 값을 기록하고 있는지를 나타내기 위해 부정된다는 점을 주의하라. 다음의 타이밍 사이클 중에, TS 신호는 부정되고 외부 버스 마스터(205)는 메모리(206)에 기록되는 데이터 값의 유효 사이즈 값을 구동하기 시작한다. 이 타이밍 사이클 중에, 전송 확인(TA) 신호는 트리-스테이트(tri-state)로 된다.

TS 신호가 부정된지 한 타이밍 사이클 이후에, 일부의 시스템 버스 제어기(8)의 메모리 제어기(804)는 메모리(206) 또는 임의의 다른 선택된 장치가 외부 버스 마스터(205)에 의해 액세스되었는지를 나타내기 위해 칩 선택(CS) 신호를 어서트(assert)한다. 또한, 메모리 제어기(804)는 전송 확인(TA) 신호를 동일한 타이밍 사이클 중에 부정한다. 동시에, 외부 버스 마스터(205)는 기록되는 데이터를 메모리(206)에 제공한다.

다음의 타이밍 사이클 중에, 메모리 제어기(804)는 외부 버스 마스터(205)에 의해 제공된 데이터로 기록된 어드레스 버스를 통해 전송된 어드레스 로케이션 메모리(206)를 인에이블 상태로 만들기 위해, 기록 인에이블(WE) 버스를 어서트(assert)한다. 또한, 메모리 제어기(804)는 전송 확인(TA) 신호를 이 다음의 타이밍 사이클 중에 어서트(assert)한다.

다음의 타이밍 사이클 중에, TA 신호는 CS 신호와 WE 버스가 부정되고 데이터 값이 트리-스테이트(tri-state)로 되는 동안 다시 부정된다.

다음으로, 데이터 판독 동작은 실행되고, 그것의 타이밍은 도 11에 나타난다. 도 11에 나타난 바와 같이, 외부 버스 마스터(205)는 다른 어드레스 값, 전송 개시(TS) 신호, R/신호 및 다른 사이즈 버스를 제 1 타이밍 사이클 중에 데이터 프로세서(3)에 제공한다. 이 타이밍 예의 제 1 부분에서, R/신호는 데이터 프로세서(3)가 메모리(206)로부터 데이터 값을 판독하고 있는지를 나타내기 위해 어서트(assert)된다는 점을 주의해야 한다. 이 타이밍 사이클 중에, 전송 확인(TA) 신호는 트리-스테이트(tri-state)로 된 채 유지된다.

TS 신호가 부정되는 동일한 타이밍 사이클 중에, 일부의 시스템 버스 제어기(8)의 메모리 제어기(804)는 메모리(206) 또는 임의의 다른 선택된 장치가 외부 버스 마스터(205)에 의해 액세스되었는지를 나타내기 위해 칩 선택(CS) 신호를 어서트(assert)한다. 또한, 메모리 제어기((804)는 전송 확인(TA) 신호를 동일한 타이밍 사이클 중에 어서트(assert)한다. 시점에서, 메모리(206)는 일부의 시스템 버스 제어기(8)의 데이터 패스(802)에 유효한 데이터 값을 제공한다.

다음의 타이밍 사이클 중에, 메모리 제어기(804)는 전송 확인(TA) 신호와 CS 신호를 부정한다. 다음의 타이밍 사이클 중에, 메모리(206)는 외부 버스 마스터(205)에 의해 그것으로부터 판독된 데이터 값을 전송하는데 이전에 사용됐던 집적 회로 핀을 트리-스테이트(tri-state)로 한다.

다음의 타이밍 사이클 중에, TA 신호는 다시 트리-스테이트(tri-state)로 된다.

도 16은 메모리(206)가 먼저 기록되고 다음으로 판독되며, 메모리 제어기(804)가 전송 확인(TA) 신호를 제공하지 않아야 하는지를 나타내도록 제어 레지스터(810)의 CSCR 내의 EMAA 필드가 부정되는 본 발명의 제 4 실시예를 나타낸다. 이 경우에, 메모리 제어기(804)로부터 출력된 TA 신호는 트리-스테이트(tri-state)로 될 것이고, TA 신호는 외부 버스 마스터(205) 또는 다른 외부 회로(여기서는 도시되지 않음)에 의해 외부에서 제공되어야 한다.

도 16에서, Clk(Clock) 신호가 제공된다. 데이터 처리 시스템 내에서 클럭 신호의 발생, 사용 및 라우팅은 기술상 잘 공지되어 있으므로 보다 상세히 논의하지 않을 것이다. 도 16에서 나타난 바와 같이, 외부 버스 마스터(205)는 제 1 타이밍 사이클 중에 어드레스 값, 전송 개시(TS) 신호, R/신호 및 사이즈 버스를 데이터 프로세서(3)에 제공한다. 상기 타이밍 예의 제 1 부분에서, R/신호는 외부 버스 마스터(205)가 메모리(206)에 데이터 값을 기록하고 있는지를 나타내기위해 부정된다는 점을 주의하라. 다음의 타이밍 사이클 중에, TS 신호는 부정되고 외부 버스 마스터(205)는 메모리(206)에 기록되는 데이터를 구동하기 시작한다. 이 전체 타이밍 시퀀스 중에, 메모리 제어기(804)로부터 출력된 전송 확인(TA) 신호는 트리-스테이트(tri-state)로 된 채 유지된다.

TS 신호가 부정된지 한 타이밍 사이클 이후에, 일부의 시스템 버스 제어기(8)의 메모리 제어기(804)는 메모리(206) 또는 임의의 다른 선택된 장치가 외부 버스 마스터(205)에 의해 액세스되었는지를 나타내기 위해 칩 선택(CS) 신호를 어서트(assert)한다. 이 타이밍 사이클 중에, 외부 버스(205) 또는 다른 외부 회로(여기서는 도시되지 않음)로부터 출력된 TA 신호는 부정된 채 유지된다.

다음의 타이밍 사이클 중에, 메모리 제어기(804)는, 외부 버스 마스터(205)에 의해 제공된 데이터로 기록된 어드레스 버스를 통해 전송된 어드레스 로케이션 메모리(206)를 인에이블 상태로 만들기 위해, 기록 인에이블(WE) 버스를 어서트(assert)한다. 또한, 외부 버스 마스터(205) 또는 다른 외부 회로(여기서는 도시되지 않음)는 TA 신호를 이 다음의 타이밍 사이클 중에 어서트(assert)한다.

다음의 타이밍 사이클 중에, TA 신호는 CS 신호와 WE 버스가 부정되고 데이터 값이 트리-스테이트(tri-state)로 되는 동안 다시 부정된다. TA 신호는 외부 버스 마스터(205)에 의해 요청되고 외부 버스 마스터(205) 또는 다른 외부 회로에 의해 결정된 다수의 대기 상태 이후에 어서트(assert)된다. TA 신호를 어서트(assert)하는 외부 버스 마스터(205) 또는 다른 외부 회로는, 제어 레지스터(810)의 CSCR의 WS[3:0] 비트에 의해 나타난 대기 상태의 수에 관계없이,CS 신호와 WE 버스의 어서트(assert)를 임의의 수의 타이밍 사이클까지 확장시킨다.

다음으로, 메모리 판독 동작이 실행되고, 그것의 타이밍은 도 16에 나타난다. 도 16에 나타난 바와 같이, 외부 버스 마스터(205)는 다른 어드레스 값, 전송 개시(TS) 신호, R/신호 및 사이즈 버스를 제 1 타이밍 사이클 중에 데이터 프로세서(3)에 제공한다. 이 타이밍 예의 제 1 부분에서, R/신호는 데이터 프로세서(3)가 메모리(206)로부터 데이터 값을 판독하고 있는지를 나타내기 위해 어서트(assert)된다는 점을 주의해야 한다. 이 타이밍 사이클 중에, 메모리 제어기(804)에 의해 출력된 전송 확인(TA) 신호는 트리-스테이트(tri-state)로 되어 유지된다.

TS 신호가 부정된지 한 타이밍 사이클 이후에, 일부의 시스템 버스 제어기(8)의 메모리 제어기(804)는 메모리(206) 또는 임의의 다른 선택된 장치가 외부 버스 마스터(205)에 의해 액세스되었는지를 나타내기 위해 칩 선택(CS) 신호를 어서트(assert)한다. 이 타이밍 사이클 중에, 외부 버스 마스터(205) 또는 다른 외부 회로로부터 출력된 TA 신호는 부정된 상태로 유지된다.

다음의 타이밍 사이클 중에, 메모리(206)는 외부 버스 마스터(205)에 유효한 데이터 값을 제공한다. 외부 버스 마스터(205) 또는 다른 외부 회로는 버스 사이클의 종료를 나타내는 TA 신호를 어서트(assert)한다.

다음의 타이밍 사이클 중에, TA 신호는 CS 신호가 부정되고 데이터 값이 트리-스테이트(tri-state)로 되는 동안 다시 부정된다. TA 신호는 외부 버스 마스터(205)에 의해 요청되고 외부 버스 마스터(205) 또는 다른 외부 회로에 의해 결정된 다수의 대기 상태 이후에 어서트(assert)된다. TA 신호를 어서트(assert)하는 외부 버스 마스터(205) 또는 다른 외부 회로는, 제어 레지스터(810)의 CSCR의 WS[3:0] 비트에 의해 나타난 대기 상태의 수에 관계없이, CS 신호의 어서트(assert)를 임의의 수의 사이클까지 확장시킨다.

여기서 제공된 블록도, 흐름도, 타이밍도로부터, 외부 버스 마스터(205)가 데이터 프로세서(3)의 메모리 제어기(804)에 의해 발생된 내부 칩 선택을 사용하는 경우, 본 발명은 전송 확인 신호의 외부 발생을 제공하기 위한 필요성을 제거한다는 것을 관찰할 수 있을 것이다. 사용자는 어드레스 및 속성이 저장된 후, 외부 마스터 칩 선택 액세스가 내부 마스터 액세스와 동일할 수 있도록, 데이터 프로세서(3)를 프로그램할 수 있다. 또한 사용자는, 여전히 내부 칩 선택 및 기록 인에이블 발생 로직을 사용하지만, 내부 전송 확인 로직을 턴 오프하고 외부 전송 확인 로직을 추가할 수도 있다. 이 특징은 칩 선택 베이스에 따라서 사용자가 프로그램 가능하다. 본 발명의 이 양태에 의해 제공된 유연성으로 인해, 사용자는 외부 칩 선택 및 기록 인에이블 발생 로직을 요청하지 않고도 외부 마스터 액세스의 다른 타이밍을 보상할 수가 있다. 따라서, 오버헤드가 보존되고 효율성은 본 발명의 상기 실시예에서 증가된다.

또한, 본 발명에 관한 회로 및 방법은 외부 버스 마스터(205)가 외부 메모리 제어 회로를 추가 없이도 내부 마스터(데이터 프로세서(3))와는 다른 수의 대기 상태를 사용함으로서, 칩 선택 가능한 메모리에 액세스할 수 있게 한다. 외부 버스 마스터(205)가 데이터 프로세서(3)의 내부의 칩 선택 회로, 내부 마스터, 그리고 내부 마스터와는 다른 수의 대기 상태를 사용하여, 메모리(206)에 액세스하는 것을 허용하기 위해, 본 발명은 레지스터 비트가 프로그램되게 허용하므로 내부 칩 선택 회로는 외부 액세스 중에 전송 확인 신호를 어서트(assert)하지 않을 것이다. 따라서, 외부 액세스 중에, 데이터 프로세서(3)의 칩 선택 로직은, 내부에서 발생된 칩 선택 신호 및 기록 인에이블 버스를 부정하기 이전에, 외부에서 발생된 전송 확인 신호를 대기할 것이다. 본 발명의 이 양태로 인해, 대기 상태의 수가 내부 및 외부 마스터 사이에서 다른 경우에 요구되는 외부 회로의 양을 감소시킨다.

외부 메모리의 내부 액세스

도 5를 다시 참조하면,마스터 신호가 부정되면, 디코드 및 어드레스 발생 블록(808)은 외부 마스터가 외부 메모리에 액세스하고 있지 않으며, 데이터 프로세서(3)가 MTS(Master Transfer Start) 신호를 사용하여 외부 메모리에 액세스하려고 하는지를 평가한다. MTS 신호가 어서트(assert)되면, 데이터 프로세서(3)는 외부 메모리의 내부 마스터 액세스를 하려할 것이다.

만일 MTS 신호가 어서트(assert)된다면, 디코드 및 어드레스 발생 회로(808)는, 데이터 처리 시스템(202)내의 어느 장치가 액세스 되고있는지를 결정하기 위해, 마스터 어드레스(MADDR) 값, MR/신호 및 M사이즈 버스를 디코드한다. 디코드 및 어드레스 발생 회로(808)는 다음으로 그것에 제공된 어드레스가 DRAM(207)내의 메모리 로케이션에 액세스하는지를 나타내기 위해 DRAM_히트 신호를어서트(assert)한다. 유사하게, 디코드 및 어드레스 발생 회로(808)는 그것에 제공된 어드레스가 메모리(206)와 같은 다른 외부 장치에 액세스하는지를 나타내기 위해 CS_히트 신호를 어서트(assert)한다. 메모리(206)만이 본 발명의 실시예에 나타나 있지만, 다른 칩 선택 가능한 장치가 메모리(206) 이외에도 또는 메모리 대신에 구현될 수 있을 것이라는 점을 이해하여야 한다. 만일, 다른 칩 선택 가능한 장치가 구현된다면, CS_히트 신호는 디코드 및 어드레스 발생 회로(808)에 제공된 어드레스가 상기 장치 중 하나에 액세스한다는 것을 나타낼 것이다. 또한, 메모리(206)는 SRAM, ROM, EEPROM, 시리얼 인터페이스 또는 타이머와 같은 플래쉬 또는 칩 선택 가능한 주변 장치와 같은 임의의 타입의 외부 메모리로 구현될 수도 있다는 점에 주목하여야 한다.

DRAM_히트 신호가 DRAM(207)내의 메모리 로케이션이 액세스되었다는 것을 나타내기 위해 어서트(assert)된다면, 메모리 제어기(804)는 다음으로 디코드 및 어드레스 발생 회로(808)가 TS, R/, 사이즈 및 어드레스 값을 E-버스에 구동하게 한다. 메모리 제어기(804)는 또한 버스 중재 회로(806)가 버스 요구(BR) 신호 및 버스 구동(BD) 신호를 E- 버스를 통해 외부 메모리에 구동하도록 한다. 또한 메모리 제어기(804)는 RAS, CAS 및 DRAMW 신호를 E-버스를 통해 외부 메모리에 제공한다. 데이터 패스(802)는 R/신호가 부정되는 경우 데이터를 구동하며 R/신호가 상기 모드의 작동 중에 어서트(assert)되는 경우에 데이터를 샘플링한다. 메모리 제어기(804)는 이후에 버스 사이클의 종료를 나타내기 위해 TA 신호를 구동시킨다.

만일 DRAM_히트 신호가 DRAM(207)내의 메모리 로케이션이 액세스된다는 것을 나타내기 위해 부정되면, 메모리 제어기(804)는 디코드 및 어드레스 발생 회로(808)가 E-버스를 통해 외부 메모리에 TS, R/, 사이즈 및 어드레스 값을 구동하게 한다. 또한 메모리 제어기(804)는 CS 신호 및 WE 버스를 E-버스를 통해 외부 메모리에 제공한다. 데이터 패스(802)는 R/신호가 부정되는 경우 데이터를 구동하며 R/신호가 이 모드의 작동 중에 어서트(assert)되는 경우 데이터를 샘플링한다. 만일 AA가 어서트(assert)되면, 메모리 제어기(804)는 대기 상태의 수 이후의 또는 외부 TA 신호가 어서트(assert)되는 경우에 TA 신호를 어서트(assert)한다. TA 신호가 외부 장치에 의해 버스 사이클의 종료를 나타내기 위해 어서트(assert)되면, 메모리 제어기(804)는 MTA(Master Transfer Acknowledge) 신호를 어서트(assert)한다. 데이터 패스(802)는 판독 동작이 실행된 경우 M-버스(23)를 통해 다른 부분의 데이터 프로세서(3)의 데이터를 또한 구동한다.

결론

본 발명은 데이터 프로세서, 외부 메모리, 외부 마스터와의 사이에서 정보를 통신하는 독자적이고 유용한 장치 및 방법을 제공한다. 본 발명에 관한 방법과 장치는 데이터 프로세서가 외부 마스터에 의해 액세스 중에 외부 메모리를 적절히 제어하도록 하여, 외부의 인터페이스 회로가 보다 적게 필요해지고 데이터 처리 시스템과 관련된 초과 비용이 감소된다.

여기에서 기술된 본 발명의 구현은 단지 예로서만 제공되었다. 그러나, 여기서 기술된 기능을 실행하는 많은 다른 구현 수단이 존재할 수 있다. 예를 들어, 본 발명은 많은 타입의 외부 장치에 대한 액세스에 적용되고 DRAM에 한정되지 않는다. 또한, 도 12a 내지 도 12c 및 13a 내지 13e에 도시된 제어 레지스터(810)는 증가, 감소 및 심지어 몇몇의 예에서는 삭제될 수 있다는 점을 이해하여야 한다. 또한, DRAM 제어기는 본 발명에 관한 칩 선택 기능과 함께 또는 별개로 구현될 수 있다는 점을 이해하여야 한다. 본 발명이 특정 실시예와 관련하여 기술 및 도시되어 있지만, 본 분야의 기술자에게는 다른 수정과 개선이 이루어질 수 있을 것이다. 따라서, 본 발명은 나타난 특정 형태에 제한되지 않고 첨부된 청구항은 본 발명의 범위를 벗어나지 않는 모든 변형을 포함할 것이다.

Claims (3)

- 데이터 프로세서(3)에 있어서,다수의 내부 어드레스 신호들, 다수의 내부 데이터 신호들 및 다수의 내부 제어 신호들을 내부 버스에 제공하기 위한 CPU(2)와,내부 버스 및 데이터 프로세서(3) 외부에 있는 적어도 하나의 장치(207)간에 다수의 외부 제어 신호들 및 다수의 외부 어드레스 신호들을 전하기 위한 외부 버스 제어기와,데이터 프로세서(3)가 전송 확인(transfer acknowledge) 신호를 발생시켜야 하는 때를 선택적으로 나타내는 외부 확인(external acknowledge) 비트를 저장하기 위한 제어 레지스터(810)와,상기 내부 버스에 연결되어, 외부 확인 비트가 제 1 로직 상태에 있는 경우, 외부 버스 마스터에 의해 개시된 액세스에 응답하여 전송 확인 신호를 어서트(assert)하고, 외부 확인 비트가 제 2 로직 상태에 있는 경우, 외부 버스 마스터에 의해 개시된 액세스에 응답하여 인액티브 상태로 전송 확인 신호를 유지하기 위한 메모리 제어기(804)를 포함하며,상기 메모리 제어기(804)는 외부의 확인 비트를 수신하기 위해 제어 레지스터(801)에 연결되고 전송 확인 신호를 제공하기 위해 외부 버스 제어기에 연결되는, 데이터 프로세서(3).

- 데이터 처리 시스템에 있어서,외부 장치(207)와,외부 버스 마스터(205)로서, 외부 장치(207)로의 제 1 액세스를 개시하기 위해 전송 개시 신호, 외부 어드레스 값 및 다수의 외부 제어 신호들을 어서트(assert)하는 상기 외부 버스 마스터(205)와,데이터 프로세서(3)를 포함하며,상기 데이터 프로세서(3)는,정보를 외부 장치(207) 및 외부 버스 마스터(205)와 통신하기 위한 다수의 집적 회로 핀들과,데이터 프로세서(3)에 의해 실행되는 액세스 타입을 결정하기 위한 버스 중재 회로(806)로서, 외부 버스 마스터(205)가 외부 장치(207)의 액세스를 실행하는 경우를 나타내기 위해 제 1 로직 상태에서 외부 마스터 제어 신호를 제공하는, 상기 버스 중재 회로(806)와,외부 버스 마스터(205)에 의해 외부 장치(207)의 액세스의 종료를 나타내기 위해 데이터 프로세서(3)가 전송 확인 신호를 발생시켜야 하는지를 나타내도록 외부 전송 확인 비트를 저장하고 제공하기 위한 제어 레지스터(810), 및외부 전송 확인 비트가 제 2의 소정의 로직 상태에 있고 외부 마스터 제어 신호가 제 1 로직 상태에 있는 경우, 다수의 집적 회로 핀들 중 제 1 핀에 전송 확인 신호를 제공하기 위한 메모리 제어기(804)로서, 전송 확인 신호를 제공하기 위해 다수의 집적 회로 핀들에 연결되며, 외부 마스터 제어 신호를 수신하기 위해 버스 중재 회로(806)에 연결되며, 외부 전송 확인 비트를 수신하는 제어 레지스터(810)에 연결되는, 상기 메모리 제어기(804)를 포함하는, 데이터 처리 시스템.

- 데이터 프로세서(3)를 사용하여 외부 장치(207)를 액세스하기 위한 방법에 있어서,다수의 집적 회로 핀들의 제 1 부분으로부터의 외부 버스 마스터(205)로부터 버스 승인 신호 및 외부 어드레스 값을 수신하는 단계와,상기 버스 승인 신호가 제 1 로직 상태에 있는 경우를 나타내기 위해, 버스 중재 회로(806)를 사용하여 외부 마스터 제어 신호를 선택적으로 어서트(assert)하는 단계와,상기 외부 마스터 제어 신호가 어서트(assert)되는 경우, 디코드 및 어드레스 발생 회로(808)를 사용하여 외부 어드레스 값을 디코드하는 단계와,제어 레지스터(810)로부터 제어 비트를 액세스하는 단계로서, 상기 제어 비트는 데이터 프로세서(3)가 전송 확인 신호를 발생시켜야 하는 경우를 나타내는, 상기 액세스 단계와,상기 제어 비트가 제 2 로직 상태에 있고 외부 마스터 제어 신호가 어서트(assert)되는 경우, 외부 어드레스 값이 소정의 범위 내에 있음을 결정하는 디코드 및 어드레스 발생 회로에 응답하여 전송 확인 신호를 발생시키는 단계, 및상기 제어 비트가 제 3 로직 상태에 있고 외부 마스터 제어 신호가어서트(assert)되는 경우, 상기 외부 어드레스 값이 소정의 범위 내에 있음을 결정하는 디코드 및 어드레스 발생 회로에 응답하여 전송 확인 신호를 인액티브로 유지하는 단계를 포함하는, 방법.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US623,482 | 1996-03-28 | ||

| US08/623,482 US5740382A (en) | 1996-03-28 | 1996-03-28 | Method and apparatus for accessing a chip-selectable device in a data processing system |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR970066899A KR970066899A (ko) | 1997-10-13 |

| KR100436098B1 true KR100436098B1 (ko) | 2004-08-16 |

Family

ID=24498247

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970008475A KR100436098B1 (ko) | 1996-03-28 | 1997-03-13 | 데이터프로세서,데이터처리시스템,및데이터프로세서를이용한외부장치로의액세스방법 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US5740382A (ko) |

| EP (1) | EP0798644A3 (ko) |

| JP (1) | JP3817327B2 (ko) |

| KR (1) | KR100436098B1 (ko) |

| CN (1) | CN1118028C (ko) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5854944A (en) * | 1996-05-09 | 1998-12-29 | Motorola, Inc. | Method and apparatus for determining wait states on a per cycle basis in a data processing system |

| GB2362482A (en) | 2000-05-15 | 2001-11-21 | Ridgeway Systems & Software Lt | Direct slave addressing to indirect slave addressing |

| US6798711B2 (en) * | 2002-03-19 | 2004-09-28 | Micron Technology, Inc. | Memory with address management |

| JP2005038230A (ja) * | 2003-07-16 | 2005-02-10 | Oki Electric Ind Co Ltd | システムlsi |

| KR100746646B1 (ko) * | 2006-07-11 | 2007-08-06 | 삼성전자주식회사 | 디스플레이 구동 회로 및 이를 갖는 액정 표시 장치 |

| CN115529275B (zh) * | 2022-11-28 | 2023-04-07 | 中国人民解放军国防科技大学 | 一种报文处理系统及方法 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4615017A (en) * | 1983-09-19 | 1986-09-30 | International Business Machines Corporation | Memory controller with synchronous or asynchronous interface |

| US4617624A (en) * | 1984-04-16 | 1986-10-14 | Goodman James B | Multiple configuration memory circuit |

| US4745407A (en) * | 1985-10-30 | 1988-05-17 | Sun Microsystems, Inc. | Memory organization apparatus and method |

| US5151986A (en) * | 1987-08-27 | 1992-09-29 | Motorola, Inc. | Microcomputer with on-board chip selects and programmable bus stretching |

| US5448744A (en) * | 1989-11-06 | 1995-09-05 | Motorola, Inc. | Integrated circuit microprocessor with programmable chip select logic |

| JP2762138B2 (ja) * | 1989-11-06 | 1998-06-04 | 三菱電機株式会社 | メモリコントロールユニット |

| US5522064A (en) * | 1990-10-01 | 1996-05-28 | International Business Machines Corporation | Data processing apparatus for dynamically setting timings in a dynamic memory system |

| US5418924A (en) * | 1992-08-31 | 1995-05-23 | Hewlett-Packard Company | Memory controller with programmable timing |

| US5511182A (en) * | 1994-08-31 | 1996-04-23 | Motorola, Inc. | Programmable pin configuration logic circuit for providing a chip select signal and related method |

-

1996

- 1996-03-28 US US08/623,482 patent/US5740382A/en not_active Expired - Lifetime

-

1997

- 1997-02-21 CN CN97102640A patent/CN1118028C/zh not_active Expired - Fee Related

- 1997-03-13 KR KR1019970008475A patent/KR100436098B1/ko not_active IP Right Cessation

- 1997-03-20 EP EP97104768A patent/EP0798644A3/en not_active Withdrawn

- 1997-03-24 JP JP09012497A patent/JP3817327B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN1118028C (zh) | 2003-08-13 |

| US5740382A (en) | 1998-04-14 |

| KR970066899A (ko) | 1997-10-13 |

| JPH1091568A (ja) | 1998-04-10 |

| EP0798644A3 (en) | 1999-05-06 |

| JP3817327B2 (ja) | 2006-09-06 |

| CN1165346A (zh) | 1997-11-19 |

| EP0798644A2 (en) | 1997-10-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6393576B1 (en) | Apparatus and method for communication between integrated circuit connected to each other by a single line | |

| US5873114A (en) | Integrated processor and memory control unit including refresh queue logic for refreshing DRAM during idle cycles | |

| EP0692764B1 (en) | Memory throttle for PCI master | |

| EP1488323B1 (en) | Memory system with burst length shorter than prefetch length | |

| US6681301B1 (en) | System for controlling multiple memory types | |

| JP4507186B2 (ja) | モードレジスタにおけるバースト長設定の変更を行わずに、異なるバースト長のアクセスをサポートするdram | |

| KR100341948B1 (ko) | 제어된버스트메모리액세스기능을갖는데이타처리기및그방법 | |

| US20070055813A1 (en) | Accessing external memory from an integrated circuit | |

| KR20020077331A (ko) | 집적 회로 | |

| US5555209A (en) | Circuit for latching data signals from DRAM memory | |

| JP6710219B2 (ja) | 統合プロセッサを備えたdram回路 | |

| US6085261A (en) | Method and apparatus for burst protocol in a data processing system | |

| US6892289B2 (en) | Methods and structure for using a memory model for efficient arbitration | |

| EP0757316B1 (en) | External device selection unit for data processor | |

| KR100436098B1 (ko) | 데이터프로세서,데이터처리시스템,및데이터프로세서를이용한외부장치로의액세스방법 | |

| US5448699A (en) | Apparatus with leading edge delay circuit for selectively sending a delayed substitute version of a signal transmitted between an expansion card and a system bus | |

| KR100297895B1 (ko) | 동기식 dram-타입 메모리와 시스템 버스간의 데이터 전송을 제어하는 방법 및 장치 | |

| US5717931A (en) | Method and apparatus for communicating between master and slave electronic devices where the slave device may be hazardous | |

| US5890196A (en) | Method and apparatus for performing page mode accesses | |

| US7747832B2 (en) | Method for controlling a memory access | |

| KR100298955B1 (ko) | 데이타처리시스템 | |

| US5704048A (en) | Integrated microprocessor with internal bus and on-chip peripheral | |

| US5893932A (en) | Address path architecture | |

| KR100441996B1 (ko) | 직접 메모리 액세스 제어기 및 제어 방법 | |

| US5765217A (en) | Method and apparatus to perform bus reflection operation using a data processor |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20130523 Year of fee payment: 10 |

|

| FPAY | Annual fee payment |

Payment date: 20140526 Year of fee payment: 11 |

|

| LAPS | Lapse due to unpaid annual fee |