KR100298552B1 - 명령디코딩장치 - Google Patents

명령디코딩장치 Download PDFInfo

- Publication number

- KR100298552B1 KR100298552B1 KR1019970040738A KR19970040738A KR100298552B1 KR 100298552 B1 KR100298552 B1 KR 100298552B1 KR 1019970040738 A KR1019970040738 A KR 1019970040738A KR 19970040738 A KR19970040738 A KR 19970040738A KR 100298552 B1 KR100298552 B1 KR 100298552B1

- Authority

- KR

- South Korea

- Prior art keywords

- command

- pla

- signal

- flop

- flip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/3005—Arrangements for executing specific machine instructions to perform operations for flow control

- G06F9/30065—Loop control instructions; iterative instructions, e.g. LOOP, REPEAT

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/40—Bus structure

- G06F13/4063—Device-to-bus coupling

- G06F13/4068—Electrical coupling

- G06F13/4072—Drivers or receivers

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/44—Arrangements for executing specific programs

- G06F9/448—Execution paradigms, e.g. implementations of programming paradigms

- G06F9/4496—Unification in logic programming

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/44—Arrangements for executing specific programs

- G06F9/448—Execution paradigms, e.g. implementations of programming paradigms

- G06F9/4498—Finite state machines

Landscapes

- Engineering & Computer Science (AREA)

- Software Systems (AREA)

- Theoretical Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Complex Calculations (AREA)

Abstract

Description

Claims (3)

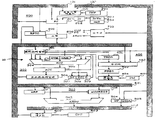

- 명령을 공급하는 버스와; 시스템을 초기화시키는 리셋 신호에 응답하여 클리어되며 반복 제어신호에 응답하여 상기 버스로부터 공급되는 명령을 지연하는 제1 지연기와; 상기 명령을 디코딩하여 제어신호를 발생하는 프로그램 로직 어레이(PLA)와; 상기 프로그램 로직 어레이(PLA)의 제어에 의해 분기를 결정하는 유한 스테이트 머신(FSM)과; 상기 프로그램 로직 어레이(PLA)로부터 출력되는 제어신호와 상기 리셋신호 중 하나를 출력하는 제1 절환기와; 상기 제1 절환기의 출력신호에 응답하여 상기 버스로부터의 명령과 상기 제1 지연기로부터 지연된 명령을 출력하는 제2 절환기와; 상기 제2 절환기로부터 출력되는 명령을 지연하여 상기 프로그램 로직 어레이(PLA)에 공급하는 제2 지연기를 구비한 것을 특징으로 하는 명령 디코딩 장치.

- 제1항에 있이서, 상기 프로그램 로직 어레이(PLA)와 유한 스테이트 머신(FSM)를 등기시키기 위한 플립플롭을 추가로 구비한 것을 특징으로 하는 명령 디코딩 장치.

- 제1항에 있어서, 상기 제2 지연기의 출력신호는 상기 제1 절환기에 피드백되는 것을 특징으로 하는 명령 디코딩 장치.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019970040738A KR100298552B1 (ko) | 1997-08-25 | 1997-08-25 | 명령디코딩장치 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019970040738A KR100298552B1 (ko) | 1997-08-25 | 1997-08-25 | 명령디코딩장치 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR19990017723A KR19990017723A (ko) | 1999-03-15 |

| KR100298552B1 true KR100298552B1 (ko) | 2001-10-26 |

Family

ID=37528509

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970040738A Expired - Fee Related KR100298552B1 (ko) | 1997-08-25 | 1997-08-25 | 명령디코딩장치 |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR100298552B1 (ko) |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR950003977A (ko) * | 1993-07-07 | 1995-02-17 | 세끼모또 타다히로 | 실행된 명령 스트림을 추적하기 위해 사용되는 신호를 발생하기 위한 회로를 포함하는 마이크로프로세서 |

-

1997

- 1997-08-25 KR KR1019970040738A patent/KR100298552B1/ko not_active Expired - Fee Related

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR950003977A (ko) * | 1993-07-07 | 1995-02-17 | 세끼모또 타다히로 | 실행된 명령 스트림을 추적하기 위해 사용되는 신호를 발생하기 위한 회로를 포함하는 마이크로프로세서 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR19990017723A (ko) | 1999-03-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100227276B1 (ko) | 단일 사이클 마이크로 명령을 이용한 명령 스케줄링 방법 및 프로세서 | |

| JP5199931B2 (ja) | Riscアーキテクチャを有する8ビットマイクロコントローラ | |

| US8612726B2 (en) | Multi-cycle programmable processor with FSM implemented controller selectively altering functional units datapaths based on instruction type | |

| KR20040016829A (ko) | 파이프라인식 프로세서에서의 예외 취급 방법, 장치 및시스템 | |

| JPS6058490B2 (ja) | 命令ブランチ機構 | |

| US7543014B2 (en) | Saturated arithmetic in a processing unit | |

| US5410721A (en) | System and method for incrementing a program counter | |

| US5958000A (en) | Two-bit booth multiplier with reduced data path width | |

| US5410660A (en) | System and method for executing branch on bit set/clear instructions using microprogramming flow | |

| US20090228686A1 (en) | Energy efficient processing device | |

| JP4073721B2 (ja) | データ処理装置 | |

| US4896264A (en) | Microprocess with selective cache memory | |

| US5386534A (en) | Data processing system for generating symmetrical range of addresses of instructing-address-value with the use of inverting sign value | |

| KR100298552B1 (ko) | 명령디코딩장치 | |

| EP0086307B1 (en) | Microcomputer system for digital signal processing | |

| KR100292460B1 (ko) | 콘디셔널브랜치명령수행방법및이를이용한명령수행장치 | |

| KR100240108B1 (ko) | 디지탈신호처리기의 조건부 분기 명령 수행방법 | |

| KR19990017121A (ko) | 디지탈신호처리기의 조건부 분기 명령수행 방법 | |

| JPH0749854A (ja) | マイクロコンピュータ素子及びそれを用いた マイクロコンピュータ装置 | |

| US20060218383A1 (en) | Integrated circuit device | |

| Palani | Digital Signal Processor | |

| JP4382076B2 (ja) | データ処理装置 | |

| Bhatele | An Implementation of Picoblaze 8-bit Microcontroller in Verilog | |

| Nyasulu et al. | Architecture and Implementation of a Computational RAM Controller | |

| PROCESSOR | ESP2 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-3-3-R10-R17-oth-X000 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R11-asn-PN2301 St.27 status event code: A-3-3-R10-R13-asn-PN2301 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R11-asn-PN2301 St.27 status event code: A-3-3-R10-R13-asn-PN2301 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R11-asn-PN2301 St.27 status event code: A-3-3-R10-R13-asn-PN2301 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

Fee payment year number: 1 St.27 status event code: A-2-2-U10-U11-oth-PR1002 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R11-asn-PN2301 St.27 status event code: A-5-5-R10-R13-asn-PN2301 |

|

| PR1001 | Payment of annual fee |

Fee payment year number: 4 St.27 status event code: A-4-4-U10-U11-oth-PR1001 |

|

| PR1001 | Payment of annual fee |

Fee payment year number: 5 St.27 status event code: A-4-4-U10-U11-oth-PR1001 |

|

| PR1001 | Payment of annual fee |

Fee payment year number: 6 St.27 status event code: A-4-4-U10-U11-oth-PR1001 |

|

| FPAY | Annual fee payment |

Payment date: 20070418 Year of fee payment: 7 |

|

| PR1001 | Payment of annual fee |

Fee payment year number: 7 St.27 status event code: A-4-4-U10-U11-oth-PR1001 |

|

| LAPS | Lapse due to unpaid annual fee | ||

| PC1903 | Unpaid annual fee |

Not in force date: 20080602 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE St.27 status event code: A-4-4-U10-U13-oth-PC1903 |

|

| PC1903 | Unpaid annual fee |

Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 20080602 St.27 status event code: N-4-6-H10-H13-oth-PC1903 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |