JP7486480B2 - 表示装置および電子機器 - Google Patents

表示装置および電子機器 Download PDFInfo

- Publication number

- JP7486480B2 JP7486480B2 JP2021523124A JP2021523124A JP7486480B2 JP 7486480 B2 JP7486480 B2 JP 7486480B2 JP 2021523124 A JP2021523124 A JP 2021523124A JP 2021523124 A JP2021523124 A JP 2021523124A JP 7486480 B2 JP7486480 B2 JP 7486480B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- layer

- light

- electrode

- capacitor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000003990 capacitor Substances 0.000 claims description 132

- 239000004973 liquid crystal related substance Substances 0.000 claims description 84

- 230000015572 biosynthetic process Effects 0.000 claims description 14

- 229910044991 metal oxide Inorganic materials 0.000 claims description 11

- 150000004706 metal oxides Chemical class 0.000 claims description 11

- 229910052733 gallium Inorganic materials 0.000 claims description 8

- 229910052738 indium Inorganic materials 0.000 claims description 8

- 229910052719 titanium Inorganic materials 0.000 claims description 8

- 229910052782 aluminium Inorganic materials 0.000 claims description 7

- 229910052725 zinc Inorganic materials 0.000 claims description 6

- 229910052684 Cerium Inorganic materials 0.000 claims description 5

- 229910052779 Neodymium Inorganic materials 0.000 claims description 5

- 229910052732 germanium Inorganic materials 0.000 claims description 5

- 229910052746 lanthanum Inorganic materials 0.000 claims description 5

- 229910052727 yttrium Inorganic materials 0.000 claims description 5

- 229910052726 zirconium Inorganic materials 0.000 claims description 5

- 229910052718 tin Inorganic materials 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 409

- 239000004065 semiconductor Substances 0.000 description 131

- 230000006870 function Effects 0.000 description 77

- 238000000034 method Methods 0.000 description 51

- 239000000758 substrate Substances 0.000 description 49

- 238000010586 diagram Methods 0.000 description 40

- 239000010408 film Substances 0.000 description 40

- 239000000463 material Substances 0.000 description 35

- 239000011701 zinc Substances 0.000 description 30

- 229920005989 resin Polymers 0.000 description 23

- 239000011347 resin Substances 0.000 description 23

- 229910052751 metal Inorganic materials 0.000 description 19

- 230000008569 process Effects 0.000 description 18

- 230000001965 increasing effect Effects 0.000 description 16

- 229910052760 oxygen Inorganic materials 0.000 description 16

- 238000000149 argon plasma sintering Methods 0.000 description 15

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 14

- 230000005684 electric field Effects 0.000 description 14

- 239000001301 oxygen Substances 0.000 description 14

- 230000002829 reductive effect Effects 0.000 description 14

- 239000002131 composite material Substances 0.000 description 13

- 125000004429 atom Chemical group 0.000 description 12

- 239000013078 crystal Substances 0.000 description 12

- 239000012535 impurity Substances 0.000 description 12

- 239000002184 metal Substances 0.000 description 12

- 150000001875 compounds Chemical class 0.000 description 10

- 230000001976 improved effect Effects 0.000 description 10

- 239000011241 protective layer Substances 0.000 description 10

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 9

- 238000009792 diffusion process Methods 0.000 description 9

- 239000001257 hydrogen Substances 0.000 description 9

- 229910052739 hydrogen Inorganic materials 0.000 description 9

- 230000003287 optical effect Effects 0.000 description 9

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 8

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 8

- 230000007547 defect Effects 0.000 description 8

- 238000004519 manufacturing process Methods 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 7

- 239000000203 mixture Substances 0.000 description 7

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 6

- 239000000969 carrier Substances 0.000 description 6

- 230000008878 coupling Effects 0.000 description 6

- 238000010168 coupling process Methods 0.000 description 6

- 238000005859 coupling reaction Methods 0.000 description 6

- 239000000565 sealant Substances 0.000 description 6

- 239000000126 substance Substances 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 5

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 5

- 239000003086 colorant Substances 0.000 description 5

- 238000001514 detection method Methods 0.000 description 5

- 238000000295 emission spectrum Methods 0.000 description 5

- 230000005669 field effect Effects 0.000 description 5

- 239000011521 glass Substances 0.000 description 5

- 229910052710 silicon Inorganic materials 0.000 description 5

- 239000010703 silicon Substances 0.000 description 5

- 125000006850 spacer group Chemical group 0.000 description 5

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 4

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 4

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 4

- 239000004983 Polymer Dispersed Liquid Crystal Substances 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 230000008859 change Effects 0.000 description 4

- 239000004020 conductor Substances 0.000 description 4

- 239000010949 copper Substances 0.000 description 4

- 238000010894 electron beam technology Methods 0.000 description 4

- 239000000945 filler Substances 0.000 description 4

- 229910052735 hafnium Inorganic materials 0.000 description 4

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 4

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 4

- 230000007246 mechanism Effects 0.000 description 4

- 239000002105 nanoparticle Substances 0.000 description 4

- 229910052757 nitrogen Inorganic materials 0.000 description 4

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- 238000004544 sputter deposition Methods 0.000 description 4

- 238000002834 transmittance Methods 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- 239000011787 zinc oxide Substances 0.000 description 4

- UWCWUCKPEYNDNV-LBPRGKRZSA-N 2,6-dimethyl-n-[[(2s)-pyrrolidin-2-yl]methyl]aniline Chemical compound CC1=CC=CC(C)=C1NC[C@H]1NCCC1 UWCWUCKPEYNDNV-LBPRGKRZSA-N 0.000 description 3

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 3

- 206010052128 Glare Diseases 0.000 description 3

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 3

- 229910052799 carbon Inorganic materials 0.000 description 3

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical compound [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 3

- 229920001940 conductive polymer Polymers 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 238000000151 deposition Methods 0.000 description 3

- 230000008021 deposition Effects 0.000 description 3

- 229910001882 dioxygen Inorganic materials 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 238000002149 energy-dispersive X-ray emission spectroscopy Methods 0.000 description 3

- 230000001747 exhibiting effect Effects 0.000 description 3

- 239000005262 ferroelectric liquid crystals (FLCs) Substances 0.000 description 3

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 3

- -1 indium and zinc Chemical compound 0.000 description 3

- 229910003437 indium oxide Inorganic materials 0.000 description 3

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 3

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 3

- 150000002739 metals Chemical class 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 3

- 229910052759 nickel Inorganic materials 0.000 description 3

- 238000005192 partition Methods 0.000 description 3

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 3

- 229920000642 polymer Polymers 0.000 description 3

- 230000001681 protective effect Effects 0.000 description 3

- 239000003566 sealing material Substances 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- 239000002356 single layer Substances 0.000 description 3

- 238000005477 sputtering target Methods 0.000 description 3

- 238000003860 storage Methods 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 3

- 239000010409 thin film Substances 0.000 description 3

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 3

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 3

- VUFNLQXQSDUXKB-DOFZRALJSA-N 2-[4-[4-[bis(2-chloroethyl)amino]phenyl]butanoyloxy]ethyl (5z,8z,11z,14z)-icosa-5,8,11,14-tetraenoate Chemical group CCCCC\C=C/C\C=C/C\C=C/C\C=C/CCCC(=O)OCCOC(=O)CCCC1=CC=C(N(CCCl)CCCl)C=C1 VUFNLQXQSDUXKB-DOFZRALJSA-N 0.000 description 2

- PAYRUJLWNCNPSJ-UHFFFAOYSA-N Aniline Chemical compound NC1=CC=CC=C1 PAYRUJLWNCNPSJ-UHFFFAOYSA-N 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 2

- KAESVJOAVNADME-UHFFFAOYSA-N Pyrrole Chemical compound C=1C=CNC=1 KAESVJOAVNADME-UHFFFAOYSA-N 0.000 description 2

- YTPLMLYBLZKORZ-UHFFFAOYSA-N Thiophene Chemical compound C=1C=CSC=1 YTPLMLYBLZKORZ-UHFFFAOYSA-N 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- 238000002441 X-ray diffraction Methods 0.000 description 2

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 2

- 230000009471 action Effects 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical group 0.000 description 2

- 229910052784 alkaline earth metal Chemical group 0.000 description 2

- 150000001342 alkaline earth metals Chemical group 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 238000000231 atomic layer deposition Methods 0.000 description 2

- 229910052790 beryllium Inorganic materials 0.000 description 2

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 230000003098 cholesteric effect Effects 0.000 description 2

- 239000011651 chromium Substances 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 2

- 239000002274 desiccant Substances 0.000 description 2

- 230000005611 electricity Effects 0.000 description 2

- 239000005038 ethylene vinyl acetate Substances 0.000 description 2

- 238000007667 floating Methods 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- 230000004313 glare Effects 0.000 description 2

- 230000005525 hole transport Effects 0.000 description 2

- 238000003384 imaging method Methods 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 229910010272 inorganic material Inorganic materials 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 229910052742 iron Inorganic materials 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 239000011777 magnesium Substances 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 239000000178 monomer Substances 0.000 description 2

- 239000002159 nanocrystal Substances 0.000 description 2

- 239000010955 niobium Substances 0.000 description 2

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 2

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 229920000915 polyvinyl chloride Polymers 0.000 description 2

- 239000004800 polyvinyl chloride Substances 0.000 description 2

- 239000002096 quantum dot Substances 0.000 description 2

- 230000000717 retained effect Effects 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- 229920001187 thermosetting polymer Polymers 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 229910001930 tungsten oxide Inorganic materials 0.000 description 2

- 229910052720 vanadium Inorganic materials 0.000 description 2

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-M Acrylate Chemical compound [O-]C(=O)C=C NIXOWILDQLNWCW-UHFFFAOYSA-M 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 239000004986 Cholesteric liquid crystals (ChLC) Substances 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 239000005264 High molar mass liquid crystal Substances 0.000 description 1

- CERQOIWHTDAKMF-UHFFFAOYSA-M Methacrylate Chemical compound CC(=C)C([O-])=O CERQOIWHTDAKMF-UHFFFAOYSA-M 0.000 description 1

- 239000004988 Nematic liquid crystal Substances 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 239000004990 Smectic liquid crystal Substances 0.000 description 1

- 239000004974 Thermotropic liquid crystal Substances 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 230000000996 additive effect Effects 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 239000011230 binding agent Substances 0.000 description 1

- 230000004397 blinking Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 239000006229 carbon black Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 238000004040 coloring Methods 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 238000007872 degassing Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 125000004386 diacrylate group Chemical group 0.000 description 1

- 229910003460 diamond Inorganic materials 0.000 description 1

- 239000010432 diamond Substances 0.000 description 1

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 239000000975 dye Substances 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 229910001195 gallium oxide Inorganic materials 0.000 description 1

- 230000012447 hatching Effects 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 230000001939 inductive effect Effects 0.000 description 1

- 150000002484 inorganic compounds Chemical class 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000000691 measurement method Methods 0.000 description 1

- 229910021645 metal ion Inorganic materials 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 1

- 230000000116 mitigating effect Effects 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 239000012788 optical film Substances 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 230000036961 partial effect Effects 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 238000001782 photodegradation Methods 0.000 description 1

- 239000000049 pigment Substances 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 239000000523 sample Substances 0.000 description 1

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000006104 solid solution Substances 0.000 description 1

- 230000008093 supporting effect Effects 0.000 description 1

- 238000010897 surface acoustic wave method Methods 0.000 description 1

- 229930192474 thiophene Natural products 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- LEONUFNNVUYDNQ-UHFFFAOYSA-N vanadium atom Chemical compound [V] LEONUFNNVUYDNQ-UHFFFAOYSA-N 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/122—Pixel-defining structures or layers, e.g. banks

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136213—Storage capacitors associated with the pixel electrode

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09F—DISPLAYING; ADVERTISING; SIGNS; LABELS OR NAME-PLATES; SEALS

- G09F9/00—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements

- G09F9/30—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements in which the desired character or characters are formed by combining individual elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05B—ELECTRIC HEATING; ELECTRIC LIGHT SOURCES NOT OTHERWISE PROVIDED FOR; CIRCUIT ARRANGEMENTS FOR ELECTRIC LIGHT SOURCES, IN GENERAL

- H05B33/00—Electroluminescent light sources

- H05B33/12—Light sources with substantially two-dimensional radiating surfaces

- H05B33/14—Light sources with substantially two-dimensional radiating surfaces characterised by the chemical or physical composition or the arrangement of the electroluminescent material, or by the simultaneous addition of the electroluminescent material in or onto the light source

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1213—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1216—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/123—Connection of the pixel electrodes to the thin film transistors [TFT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

- H10K59/1315—Interconnections, e.g. wiring lines or terminals comprising structures specially adapted for lowering the resistance

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1334—Constructional arrangements; Manufacturing methods based on polymer dispersed liquid crystals, e.g. microencapsulated liquid crystals

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/13624—Active matrix addressed cells having more than one switching element per pixel

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Nonlinear Science (AREA)

- General Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Mathematical Physics (AREA)

- Optics & Photonics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computer Hardware Design (AREA)

- Geometry (AREA)

- Ceramic Engineering (AREA)

- Theoretical Computer Science (AREA)

- Thin Film Transistor (AREA)

- Electroluminescent Light Sources (AREA)

Description

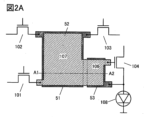

図2A、図2Bは、キャパシタの構成を説明する図である。

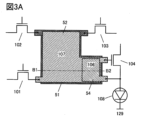

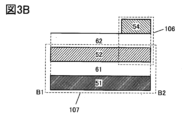

図3A、図3Bは、キャパシタの構成を説明する図である。

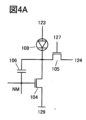

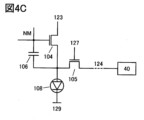

図4A乃至図4Cは、画素回路を説明する図である。

図5は、画素回路を説明する図である。

図6は、画素回路の動作を説明するタイミングチャートである。

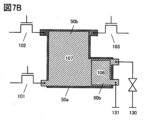

図7Aは、画素回路を説明する図である。図7Bは、キャパシタの構成を説明する図である。

図8A、図8Bは、画素回路を説明する図である。

図9は、画素回路を説明する図である。

図10は、画素回路を説明する図である。

図11は、画素回路を説明する図である。

図12A、図12Bは、画素レイアウトを説明する図である。

図13A、図13Bは、画素レイアウトを説明する図である。

図14A、図14Bは、画素レイアウトを説明する図である。

図15A乃至図15Cは、画素レイアウトを説明する図である。

図16A、図16Bは、画素レイアウトを説明する図である。

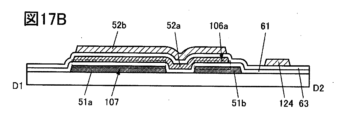

図17A、図17Bは、画素レイアウトを説明する図である。

図18A、図18Bは、画素レイアウトを説明する図である。

図19は、表示装置を説明する図である。

図20A乃至図20Cは、表示装置を説明する図である。

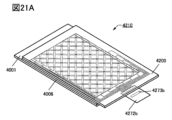

図21A、図21Bは、タッチパネルを説明する図である。

図22A、図22Bは、表示装置を説明する図である。

図23は、表示装置を説明する図である。

図24A、図24Bは、表示装置を説明する図である。

図25A、図25Bは、表示装置を説明する図である。

図26A乃至図26Eは、表示装置を説明する図である。

図27A乃至図27Cは、トランジスタを説明する図である。

図28A乃至図28Cは、トランジスタを説明する図である。

図29A、図29Bは、トランジスタを説明する図である。

図30A乃至図30Fは、電子機器を説明する図である。

本実施の形態では、本発明の一態様である表示装置について、図面を参照して説明する。

本実施の形態では、液晶デバイスを用いた表示装置の構成例と、発光デバイスを用いた表示装置の構成例について説明する。なお、本実施の形態においては、実施の形態1で説明した表示装置の要素、動作および機能の説明は省略する。

本実施の形態では、上記実施の形態に示した各トランジスタに置き換えて用いることのできるトランジスタの一例について、図面を用いて説明する。

図27Aは、ボトムゲート型のトランジスタの一種であるチャネル保護型のトランジスタ810のチャネル長方向の断面図である。図27Aにおいて、トランジスタ810は基板771上に形成されている。また、トランジスタ810は、基板771上に絶縁層772を介して電極746を有する。また、電極746上に絶縁層726を介して半導体層742を有する。電極746はゲート電極として機能できる。絶縁層726はゲート絶縁層として機能できる。

図28Aに例示するトランジスタ842は、トップゲート型のトランジスタの1つである。電極744aおよび電極744bは、絶縁層728および絶縁層729に形成した開口部において半導体層742と電気的に接続する。

本発明の一態様に係る表示装置を用いることができる電子機器として、表示機器、パーソナルコンピュータ、記録媒体を備えた画像記憶装置または画像再生装置、携帯電話、携帯型を含むゲーム機、携帯データ端末、電子書籍端末、ビデオカメラ、デジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、デジタルオーディオプレイヤー等)、複写機、ファクシミリ、プリンタ、プリンタ複合機、現金自動預け入れ払い機(ATM)、自動販売機などが挙げられる。これら電子機器の具体例を図30A乃至図30Fに示す。

Claims (8)

- 第1のキャパシタと、第2のキャパシタと、表示素子と、を画素に有し、

前記第1のキャパシタおよび前記第2のキャパシタは、前記表示素子と電気的に接続され、

前記第1のキャパシタは、第1の導電層、第1の誘電体層、第2の導電層が当該順序で積層された構成を有し、

前記第2のキャパシタは、前記第2の導電層、第2の誘電体層、第3の導電層が当該順序で積層された構成を有し、

前記第1のキャパシタと、前記第2のキャパシタは、互いに重なる領域を有し、

前記画素は、さらに第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、を有し、

前記第1のトランジスタのソースまたはドレインの一方は、前記第2の導電層と電気的に接続され、

前記第2のトランジスタのソースまたはドレインの一方および前記第3のトランジスタのソースまたはドレインの一方は、前記第3の導電層と電気的に接続される、表示装置。 - 請求項1において、

前記第2のキャパシタは、前記第1のキャパシタよりも容量値が大きい、表示装置。 - 請求項1又は2において、

前記画素は、前記表示素子として発光素子を有し、

前記画素は、さらに第4のトランジスタと、第5のトランジスタと、を有し

前記第4のトランジスタのゲートは、前記第2の導電層と電気的に接続され、

前記第4のトランジスタのソースまたはドレインの一方、前記第5のトランジスタのソースまたはドレインの一方、および前記発光素子の一方の電極は、前記第1の導電層と電気的に接続される、表示装置。 - 請求項1乃至3のいずれか一項において、

前記画素は、前記表示素子として液晶素子を有し、

前記液晶素子の一方の電極は、前記第2の導電層と電気的に接続される、表示装置。 - 請求項1乃至4のいずれか一項において、

前記第1のトランジスタ乃至前記第3のトランジスタは、チャネル形成領域に金属酸化物を有する、表示装置。 - 請求項1乃至5のいずれか一項において、

前記第2の導電層は、金属酸化物を有する、表示装置。 - 請求項5又は6において、

前記金属酸化物は、Inと、Znと、M(MはAl、Ti、Ga、Ge、Sn、Y、Zr、La、Ce、NdまたはHf)と、を有する、表示装置。 - 請求項1乃至7のいずれか一項に記載の表示装置と、カメラと、を有し、

前記カメラで撮像した画像を前記表示装置で表示する、電子機器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2024075383A JP2024116116A (ja) | 2019-05-30 | 2024-05-07 | 表示装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019101319 | 2019-05-30 | ||

| JP2019101319 | 2019-05-30 | ||

| PCT/IB2020/054663 WO2020240329A1 (ja) | 2019-05-30 | 2020-05-18 | 表示装置および電子機器 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2024075383A Division JP2024116116A (ja) | 2019-05-30 | 2024-05-07 | 表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JPWO2020240329A1 JPWO2020240329A1 (ja) | 2020-12-03 |

| JPWO2020240329A5 JPWO2020240329A5 (ja) | 2023-05-24 |

| JP7486480B2 true JP7486480B2 (ja) | 2024-05-17 |

Family

ID=73552693

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021523124A Active JP7486480B2 (ja) | 2019-05-30 | 2020-05-18 | 表示装置および電子機器 |

| JP2024075383A Pending JP2024116116A (ja) | 2019-05-30 | 2024-05-07 | 表示装置 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2024075383A Pending JP2024116116A (ja) | 2019-05-30 | 2024-05-07 | 表示装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US11988926B2 (ja) |

| JP (2) | JP7486480B2 (ja) |

| KR (1) | KR20220013390A (ja) |

| CN (1) | CN113841253A (ja) |

| WO (1) | WO2020240329A1 (ja) |

Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20040183978A1 (en) | 2003-03-20 | 2004-09-23 | Hun Jeoung | Array substrate for in-plane switching liquid crystal display device and method of fabricating the same |

| JP2006186320A (ja) | 2004-12-03 | 2006-07-13 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法、並びに表示装置 |

| JP2007123861A (ja) | 2005-09-29 | 2007-05-17 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法 |

| US20120104405A1 (en) | 2010-11-02 | 2012-05-03 | Hee-Dong Choi | Array substrate for organic electroluminescent device and method of fabricating the same |

| US20150008395A1 (en) | 2013-07-08 | 2015-01-08 | Samsung Display Co., Ltd. | Organic light emitting diodes display |

| CN104376813A (zh) | 2013-11-26 | 2015-02-25 | 苹果公司 | 用于显示器像素单元阈值电压补偿电路的电容器结构 |

| US20150187861A1 (en) | 2013-12-30 | 2015-07-02 | Lg Display Co., Ltd. | Organic light emitting diode display device |

| US20160300864A1 (en) | 2015-04-09 | 2016-10-13 | Samsung Display Co., Ltd. | Thin film transistor array substrate and display apparatus including the same |

| WO2016190187A1 (ja) | 2015-05-25 | 2016-12-01 | シャープ株式会社 | 表示装置の駆動回路 |

| CN108010494A (zh) | 2016-10-31 | 2018-05-08 | 乐金显示有限公司 | 栅极驱动器和使用该栅极驱动器的显示装置 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7586121B2 (en) * | 2004-12-07 | 2009-09-08 | Au Optronics Corp. | Electroluminescence device having stacked capacitors |

| EP1998373A3 (en) | 2005-09-29 | 2012-10-31 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method thereof |

| JP5078246B2 (ja) | 2005-09-29 | 2012-11-21 | 株式会社半導体エネルギー研究所 | 半導体装置、及び半導体装置の作製方法 |

| EP2494597A4 (en) | 2009-10-30 | 2015-03-18 | Semiconductor Energy Lab | SEMICONDUCTOR COMPONENT |

| KR101830791B1 (ko) | 2011-09-08 | 2018-02-22 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 |

| KR20170031313A (ko) * | 2015-09-10 | 2017-03-21 | 삼성디스플레이 주식회사 | 디스플레이 장치 |

| US20170102577A1 (en) * | 2015-10-09 | 2017-04-13 | Kent State University | Electro-optical devices utilizing alternative transparent conductive oxide layers |

| US11054710B2 (en) | 2017-08-11 | 2021-07-06 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic device |

| WO2019043483A1 (en) | 2017-08-31 | 2019-03-07 | Semiconductor Energy Laboratory Co., Ltd. | DISPLAY DEVICE AND ELECTRONIC DEVICE |

| US11574573B2 (en) | 2017-09-05 | 2023-02-07 | Semiconductor Energy Laboratory Co., Ltd. | Display system |

| CN113299716B (zh) * | 2021-05-21 | 2023-03-17 | 武汉华星光电半导体显示技术有限公司 | 一种显示面板 |

-

2020

- 2020-05-18 KR KR1020217041714A patent/KR20220013390A/ko unknown

- 2020-05-18 JP JP2021523124A patent/JP7486480B2/ja active Active

- 2020-05-18 CN CN202080037155.6A patent/CN113841253A/zh active Pending

- 2020-05-18 US US17/612,384 patent/US11988926B2/en active Active

- 2020-05-18 WO PCT/IB2020/054663 patent/WO2020240329A1/ja active Application Filing

-

2024

- 2024-03-08 US US18/599,770 patent/US20240248355A1/en active Pending

- 2024-05-07 JP JP2024075383A patent/JP2024116116A/ja active Pending

Patent Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20040183978A1 (en) | 2003-03-20 | 2004-09-23 | Hun Jeoung | Array substrate for in-plane switching liquid crystal display device and method of fabricating the same |

| JP2006186320A (ja) | 2004-12-03 | 2006-07-13 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法、並びに表示装置 |

| JP2007123861A (ja) | 2005-09-29 | 2007-05-17 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法 |

| US20120104405A1 (en) | 2010-11-02 | 2012-05-03 | Hee-Dong Choi | Array substrate for organic electroluminescent device and method of fabricating the same |

| US20150008395A1 (en) | 2013-07-08 | 2015-01-08 | Samsung Display Co., Ltd. | Organic light emitting diodes display |

| CN104376813A (zh) | 2013-11-26 | 2015-02-25 | 苹果公司 | 用于显示器像素单元阈值电压补偿电路的电容器结构 |

| US20150187861A1 (en) | 2013-12-30 | 2015-07-02 | Lg Display Co., Ltd. | Organic light emitting diode display device |

| US20160300864A1 (en) | 2015-04-09 | 2016-10-13 | Samsung Display Co., Ltd. | Thin film transistor array substrate and display apparatus including the same |

| WO2016190187A1 (ja) | 2015-05-25 | 2016-12-01 | シャープ株式会社 | 表示装置の駆動回路 |

| CN108010494A (zh) | 2016-10-31 | 2018-05-08 | 乐金显示有限公司 | 栅极驱动器和使用该栅极驱动器的显示装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2024116116A (ja) | 2024-08-27 |

| US20240248355A1 (en) | 2024-07-25 |

| CN113841253A (zh) | 2021-12-24 |

| US11988926B2 (en) | 2024-05-21 |

| US20220252949A1 (en) | 2022-08-11 |

| JPWO2020240329A1 (ja) | 2020-12-03 |

| WO2020240329A1 (ja) | 2020-12-03 |

| KR20220013390A (ko) | 2022-02-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11626082B2 (en) | Display device and electronic device | |

| US12039952B2 (en) | Display apparatus and electronic device | |

| US11715435B2 (en) | Display apparatus and electronic device | |

| JP2024045230A (ja) | 表示装置 | |

| JP2024094375A (ja) | 表示装置 | |

| JP7487111B2 (ja) | 表示装置および電子機器 | |

| US11822198B2 (en) | Display device and electronic device | |

| US11435637B2 (en) | Display apparatus and electronic device | |

| JP7486480B2 (ja) | 表示装置および電子機器 | |

| JP7412360B2 (ja) | 表示装置および電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230516 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20230516 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20240409 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20240507 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7486480 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |