JP7368552B1 - 情報処理装置、及び制御方法 - Google Patents

情報処理装置、及び制御方法 Download PDFInfo

- Publication number

- JP7368552B1 JP7368552B1 JP2022100814A JP2022100814A JP7368552B1 JP 7368552 B1 JP7368552 B1 JP 7368552B1 JP 2022100814 A JP2022100814 A JP 2022100814A JP 2022100814 A JP2022100814 A JP 2022100814A JP 7368552 B1 JP7368552 B1 JP 7368552B1

- Authority

- JP

- Japan

- Prior art keywords

- processing

- module

- bios

- post time

- information

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/14—Error detection or correction of the data by redundancy in operations

- G06F11/1402—Saving, restoring, recovering or retrying

- G06F11/1415—Saving, restoring, recovering or retrying at system level

- G06F11/142—Reconfiguring to eliminate the error

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/14—Error detection or correction of the data by redundancy in operations

- G06F11/1402—Saving, restoring, recovering or retrying

- G06F11/1415—Saving, restoring, recovering or retrying at system level

- G06F11/1417—Boot up procedures

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/22—Detection or location of defective computer hardware by testing during standby operation or during idle time, e.g. start-up testing

- G06F11/2284—Detection or location of defective computer hardware by testing during standby operation or during idle time, e.g. start-up testing by power-on test, e.g. power-on self test [POST]

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/44—Arrangements for executing specific programs

- G06F9/4401—Bootstrapping

- G06F9/4403—Processor initialisation

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2201/00—Indexing scheme relating to error detection, to error correction, and to monitoring

- G06F2201/865—Monitoring of software

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Software Systems (AREA)

- Quality & Reliability (AREA)

- Computer Security & Cryptography (AREA)

- Computer Hardware Design (AREA)

- Debugging And Monitoring (AREA)

- Test And Diagnosis Of Digital Computers (AREA)

Abstract

【解決手段】情報処理装置は、BIOSの部分機能を示すモジュールを識別するモジュール識別情報と、当該モジュールに対してのPOST処理に要する処理時間を示すPOST時間の基準値とを対応付けて記憶する基準POST時間記憶部と、前記BIOSに基づく処理を実行するBIOS処理部であって、前記BIOSの設定に応じた前記モジュールごとに前記POST処理を実行し、実行した前記モジュールごとの前記POST時間を測定する処理と、前記モジュールに対して測定した前記POST時間と、前記基準POST時間記憶部が記憶する当該モジュールの前記モジュール識別情報に対応する前記基準値とに基づいて、前記POST時間が増大しているか否かを判定し、異常のある前記モジュールである異常モジュールを特定する処理とを実行するBIOS処理部とを備える。

【選択図】図2

Description

なお、本実施形態において、CPU11と、チップセット21とは、メイン制御部10に対応する。また、メイン制御部10は、メモリ(メインメモリ12)に記憶されたプログラムを実行するプロセッサ(メインプロセッサ)の一例である。

メインメモリ12は、CPU11の実行プログラムの読み込み領域として、又は、実行プログラムの処理データを書き込む作業領域として利用される書き込み可能メモリである。メインメモリ12は、例えば、複数個のDRAM(Dynamic Random Access Memory)チップで構成される。この実行プログラムには、BIOS(Basic Input Output System)、OS、周辺機器類をハードウェア操作するための各種ドライバ、各種サービス/ユーティリティ、アプリケーションプログラム等が含まれる。

表示部14は、例えば、液晶ディスプレイであり、ビデオサブシステム13から出力された描画データ(表示データ)に基づく表示画面を表示する。

オーディオシステム24は、音データの記録、再生、出力を行う。

USBコネクタ26は、USBを利用した周辺機器類を接続するためのコネクタである。

電源回路33は、例えば、DC/DCコンバータ、充放電ユニット、電池ユニット、AC/DCアダプタなどを含んでおり、AC/DCアダプタ、又は電池ユニットから供給される直流電圧を、ノートPC1を動作させるために必要な複数の電圧に変換する。また、電源回路33は、エンベデッドコントローラ31からの制御に基づいて、ノートPC1の各部に電力を供給する。

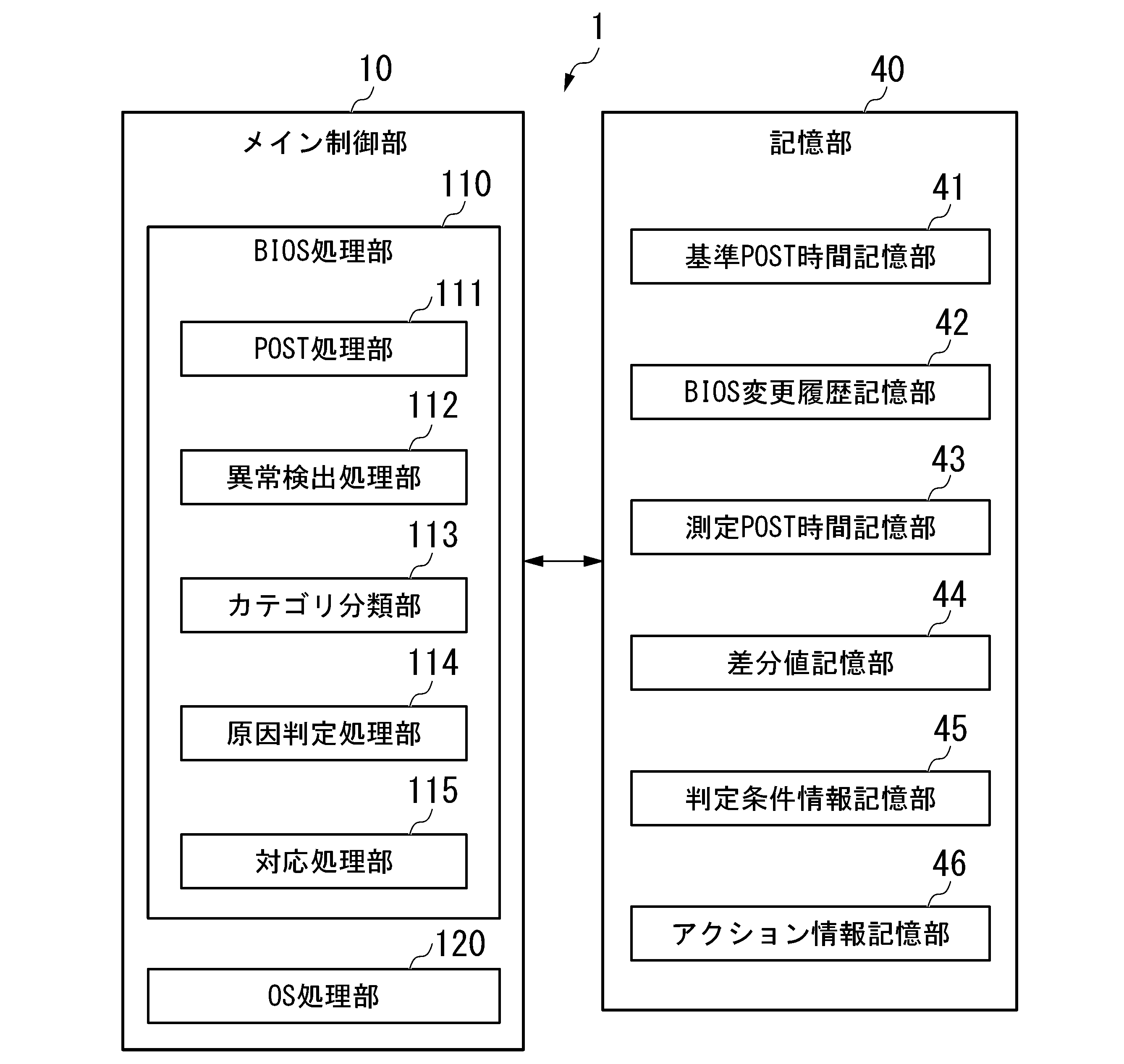

図2は、本実施形態によるノートPC1の機能構成の一例を示す機能ブロック図である。なお、図2では、ノートPC1が備える機能構成のうち、本発明に関連する構成のみを記載している。

記憶部40は、例えば、BIOSメモリ22により実現される記憶部であり、例えば、BIOSに関連する情報を記憶する。なお、BIOSの設定は、記憶部40に記憶されているものとする。

また、記憶部40は、基準POST時間記憶部41と、BIOS変更履歴記憶部42と、測定POST時間記憶部43と、差分値記憶部44と、判定条件情報記憶部45と、アクション情報記憶部46とを備える。

図3に示すように、基準POST時間記憶部41は、モジュール名と、基準値と、属性とを対応付けて記憶する。

ここで、モジュール名は、BIOSの部分機能を示すモジュールの名称を示している。モジュール名は、モジュールを識別するモジュール識別情報の一例である。

また、属性は、POST処理の内容が、ソフトウェア(S/W)に関連するのか、ハードウェア(H/W)に関連するのかを示す属性情報である。

図4に示すように、BIOS変更履歴記憶部42は、イベントと、要素とを対応付けたイベントログを記憶する。

図5に示すように、測定POST時間記憶部43は、モジュール名と、POST時間測定値と、過去測定値とを対応付けて記憶する。

図6に示すように、差分値記憶部44は、モジュール名と、差分値と、差分平均値とを対応付けて記憶する。

図7に示すように、判定条件情報記憶部45は、カテゴリ名と、小分類と、検出されたイベントと、原因とを対応付けて記憶する。

図8に示すように、アクション情報記憶部46は、カテゴリ名と、原因と、対応処理とを対応付けて記憶する。

また、BIOS処理部110は、POST処理部111と、異常検出処理部112と、カテゴリ分類部113と、原因判定処理部114と、対応処理部115とを備える。

また、異常検出処理部112は、POST時間が増大していると判定したモジュールを異常(問題)のある異常モジュールと特定する。

カテゴリ“B”:S/Wに関してPOST時間が徐々に増大しているもの(S/W、漸増)

カテゴリ“C”:H/Wに関してPOST時間が急激に増大しているもの(H/W、漸増)

カテゴリ“D”:H/Wに関してPOST時間が徐々に増大しているもの(H/W、急増)

図9において、グラフの縦軸は、POST時間を示し、横軸は、起動回数を示している。また、グラフ内の“×”は、POST時間の測定値を示している。

この例では、差分値ΔtNと、差分平均値μとの関係は、下記の式(2)に表される。

図10において、グラフの縦軸は、POST時間を示し、横軸は、起動回数を示している。また、グラフ内の“×”は、POST時間の測定値を示している。

この例では、差分値ΔtNと、差分平均値μとの関係は、下記の式(3)に表される。

カテゴリ分類部113は、異常モジュールが、これらの急増と漸像とのいずれか、及びソフトウェアとハードウェアとのいずれに関連するのかに応じて、上述したカテゴリ“A”~カテゴリ“D”の4種類のカテゴリに分類する。

図11は、本実施形態によるノートPC1の動作の一例を示すフローチャートである。ここでは、ノートPC1の起動する際のPOST処理の増加による異常原因の特定処理及び対応処理の動作について説明する。

平均値(差分平均値)と属性とからPOST時間の異常なモジュール(異常モジュール)をカテゴリに分類する。BIOS処理部110のカテゴリ分類部113は、上述した式(2)及び式(3)を用いて、POST時間が、徐々に増加した漸増と急激に増加した急増とのいずれかであるかを判定する。

これにより、本実施形態によるノートPC1は、ロールバック処理による修復(復旧)を、自動的に実行することができ、信頼性を向上させることができる。

これにより、本実施形態によるノートPC1は、リカバリ処理による修復(復旧)を、自動的に実行することができ、信頼性を向上させることができる。

これにより、本実施形態によるノートPC1は、BIOSにより起動する際に、異常箇所を適切に、且つ自動的に特定することができる。

例えば、上記の実施形態において、情報処理装置がノートPC1(1a)である例を説明したが、これに限定されるものではなく、例えば、タブレット端末装置、デスクトップPCなどの他の情報処理装置であってもよい。

また、「コンピュータシステム」は、インターネットやWAN、LAN、専用回線等の通信回線を含むネットワークを介して接続された複数のコンピュータ装置を含んでもよい。また、「コンピュータ読み取り可能な記録媒体」とは、フレキシブルディスク、光磁気ディスク、ROM、CD-ROM等の可搬媒体、コンピュータシステムに内蔵されるハードディスク等の記憶装置のことをいう。このように、プログラムを記憶した記録媒体は、CD-ROM等の非一過性の記録媒体であってもよい。

10 メイン制御部

11 CPU

12 メインメモリ

13 ビデオサブシステム

14、53 表示部

21 チップセット

22 BIOSメモリ

23 HDD

24 オーディオシステム

25 WLANカード

26 USBコネクタ

31 エンベデッドコントローラ(EC)

32 入力部

33 電源回路

40 記憶部

41 基準POST時間記憶部

42 BIOS変更履歴記憶部

43 測定POST時間記憶部

44 差分値記憶部

45 判定条件情報記憶部

46 アクション情報記憶部

110 BIOS処理部

111 POST処理部

112 異常検出処理部

113 カテゴリ分類部

114 原因判定処理部

115 対応処理部

120 OS処理部

Claims (7)

- BIOS(Basic Input Output System)の部分機能を示すモジュールを識別するモジュール識別情報と、当該モジュールに対してのPOST(Power On Self Test)処理に要する処理時間を示すPOST時間の基準値とを対応付けて記憶する基準POST時間記憶部と、

前記BIOSに基づく処理を実行するBIOS処理部であって、

前記BIOSの設定に応じた前記モジュールごとに前記POST処理を実行し、実行した前記モジュールごとの前記POST時間を測定する処理と、

前記モジュールに対して測定した前記POST時間と、前記基準POST時間記憶部が記憶する当該モジュールの前記モジュール識別情報に対応する前記基準値とに基づいて、前記POST時間が増大しているか否かを判定し、異常のある前記モジュールである異常モジュールを特定する処理と

を実行するBIOS処理部と

を備え、

前記BIOS処理部は、

前記モジュールに異常があると特定された場合に、前記POST時間が、徐々に増加した漸増と急激に増加した急増とのいずれかであるかと、当該モジュールがソフトウェアとハードウェアとのいずれに関連するのかとに基づいて、前記異常モジュールをカテゴリに分類し、分類したカテゴリに基づいて、異常の原因を推定する

情報処理装置。 - 前記BIOS処理部は、

今回測定した前記POST時間と、前回の前記POST時間との差分値と、過去の前記差分値の平均値とに基づいて、前記POST時間が前記漸増と前記急増とのいずれかであるかを判定する

請求項1に記載の情報処理装置。 - 前記BIOSの設定変更及び内蔵デバイスの変更を含む前記BIOSの環境変更に関する変更履歴を記憶する変更履歴記憶部を備え、

前記BIOS処理部は、

前記変更履歴記憶部から、前記異常モジュールに関連する前記変更履歴を取得し、前記異常モジュールに関連する前記変更履歴と、前記カテゴリとに基づいて、前記異常の原因を推定する

請求項1に記載の情報処理装置。 - 前記カテゴリと、前記異常の原因と、対応処理を示す対応処理情報とを対応付けて記憶する対応処理記憶部を備え、

前記BIOS処理部は、

前記カテゴリ及び前記異常の原因に対応する前記対応処理情報を、前記対応処理記憶部から取得し、取得した前記対応処理情報に基づく対応処理を実行する

請求項1から請求項3のいずれか一項に記載の情報処理装置。 - 前記対応処理情報には、前記BIOSの環境を変更前に戻すロールバック処理を示すロールバック処理情報が含まれ、

前記BIOS処理部は、

前記カテゴリ及び前記異常の原因に対応する前記対応処理情報が、前記ロールバック処理情報である場合に、前記ロールバック処理情報に基づく前記ロールバック処理を実行する

請求項4に記載の情報処理装置。 - 前記対応処理情報には、前記BIOSの環境を復旧するリカバリ処理を示すリカバリ処理情報が含まれ、

前記BIOS処理部は、

前記カテゴリ及び前記異常の原因に対応する前記対応処理情報が、前記リカバリ処理情報である場合に、前記リカバリ処理情報に基づく前記リカバリ処理を実行する

請求項4に記載の情報処理装置。 - BIOS(Basic Input Output System)の部分機能を示すモジュールを識別するモジュール識別情報と、当該モジュールに対してのPOST(Power On Self Test)処理に要する処理時間を示すPOST時間の基準値とを対応付けて記憶する基準POST時間記憶部と、前記BIOSに基づく処理を実行するBIOS処理部とを備える情報処理装置の制御方法であって、

前記BIOS処理部が、前記BIOSの設定に応じた前記モジュールごとに前記POST処理を実行し、実行した前記モジュールごとの前記POST時間を測定するステップと、

前記BIOS処理部が、前記モジュールに対して測定した前記POST時間と、前記基準POST時間記憶部が記憶する当該モジュールの前記モジュール識別情報に対応する前記基準値とに基づいて、前記POST時間が増大しているか否かを判定し、異常のある前記モジュールである異常モジュールを特定するステップと、

前記BIOS処理部が、前記モジュールに異常があると特定された場合に、前記POST時間が、徐々に増加した漸増と急激に増加した急増とのいずれかであるかと、当該モジュールがソフトウェアとハードウェアとのいずれに関連するのかとに基づいて、前記異常モジュールをカテゴリに分類し、分類したカテゴリに基づいて、異常の原因を推定するステップと

を含む制御方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2022100814A JP7368552B1 (ja) | 2022-06-23 | 2022-06-23 | 情報処理装置、及び制御方法 |

| US18/306,233 US20230418710A1 (en) | 2022-06-23 | 2023-04-24 | Information processing apparatus, and control method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2022100814A JP7368552B1 (ja) | 2022-06-23 | 2022-06-23 | 情報処理装置、及び制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP7368552B1 true JP7368552B1 (ja) | 2023-10-24 |

| JP2024001936A JP2024001936A (ja) | 2024-01-11 |

Family

ID=88418499

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022100814A Active JP7368552B1 (ja) | 2022-06-23 | 2022-06-23 | 情報処理装置、及び制御方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20230418710A1 (ja) |

| JP (1) | JP7368552B1 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US12474934B2 (en) | 2023-07-27 | 2025-11-18 | Dell Products L.P. | System context-controlled third-party firmware display and configuration by parsing pre-boot firmware application based on virtual forms representation (VFR) |

| US12333015B2 (en) | 2023-07-27 | 2025-06-17 | Dell Products L.P. | System context-aware third party firmware safe assurance configuration |

| US20250036420A1 (en) * | 2023-07-27 | 2025-01-30 | Dell Products L.P. | System bios method to offer resiliency using best-known configuration for third party firmware configuration |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008225929A (ja) | 2007-03-13 | 2008-09-25 | Toshiba Corp | 情報処理装置 |

| JP2014021577A (ja) | 2012-07-13 | 2014-02-03 | Nec Computertechno Ltd | 故障予測装置、故障予測システム、故障予測方法、及び、故障予測プログラム |

-

2022

- 2022-06-23 JP JP2022100814A patent/JP7368552B1/ja active Active

-

2023

- 2023-04-24 US US18/306,233 patent/US20230418710A1/en not_active Abandoned

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008225929A (ja) | 2007-03-13 | 2008-09-25 | Toshiba Corp | 情報処理装置 |

| JP2014021577A (ja) | 2012-07-13 | 2014-02-03 | Nec Computertechno Ltd | 故障予測装置、故障予測システム、故障予測方法、及び、故障予測プログラム |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2024001936A (ja) | 2024-01-11 |

| US20230418710A1 (en) | 2023-12-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7368552B1 (ja) | 情報処理装置、及び制御方法 | |

| TWI571736B (zh) | 自動除錯資訊收集之方法及系統 | |

| JP3831377B2 (ja) | コンピュータ・システムにおける電力障害を解析する方法および装置 | |

| US8935509B2 (en) | Method for controlling BMC having customized SDR | |

| US9927853B2 (en) | System and method for predicting and mitigating corrosion in an information handling system | |

| CN104636221B (zh) | 一种计算机系统故障处理方法和装置 | |

| CN102063354A (zh) | 服务器的压力测试方法 | |

| US10997046B2 (en) | Integrity check staging | |

| WO2020010890A1 (zh) | 基于bmc监控服务器cpu资源利用率的方法及系统 | |

| US6985826B2 (en) | System and method for testing a component in a computer system using voltage margining | |

| US20090138740A1 (en) | Method and computer device capable of dealing with power fail | |

| CN110457907B (zh) | 一种固件程序检测方法和装置 | |

| CN113672306B (zh) | 服务器组件自检异常恢复方法、装置、系统及介质 | |

| CN111338698A (zh) | 一种bios准确引导服务器启动的方法及系统 | |

| US20050033952A1 (en) | Dynamic scheduling of diagnostic tests to be performed during a system boot process | |

| CN113608939A (zh) | 性能测试中服务器启动计时方法、装置、终端及存储介质 | |

| CN111176958B (zh) | 信息监测方法、系统和存储介质 | |

| CN116775141A (zh) | 异常检测方法、装置、计算机设备及存储介质 | |

| CN110347558A (zh) | 一种服务器设备故障诊断方法和装置以及设备 | |

| TW201734779A (zh) | 通知開機階段的方法及伺服器系統 | |

| US20210349775A1 (en) | Method of data management and method of data analysis | |

| US11086371B2 (en) | Heat suppression in an information processing device in an initial setting mode | |

| CN115426607B (zh) | 一种音频诊断方法、装置、电子设备及存储介质 | |

| JP2005165415A (ja) | 情報処理装置、システム起動方法、およびシステム起動プログラム | |

| CN116700823A (zh) | 一种操作系统安装方法、装置、设备及存储介质 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20220623 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20221216 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20230829 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230915 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20231003 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20231012 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7368552 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |