JP7282688B2 - Flexible part with layered structure with metal layers - Google Patents

Flexible part with layered structure with metal layers Download PDFInfo

- Publication number

- JP7282688B2 JP7282688B2 JP2019561901A JP2019561901A JP7282688B2 JP 7282688 B2 JP7282688 B2 JP 7282688B2 JP 2019561901 A JP2019561901 A JP 2019561901A JP 2019561901 A JP2019561901 A JP 2019561901A JP 7282688 B2 JP7282688 B2 JP 7282688B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- flexible

- coated substrate

- mox

- layers

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 229910052751 metal Inorganic materials 0.000 title claims description 59

- 239000002184 metal Substances 0.000 title claims description 59

- 239000010410 layer Substances 0.000 claims description 330

- 239000000758 substrate Substances 0.000 claims description 84

- 239000004020 conductor Substances 0.000 claims description 34

- 239000000463 material Substances 0.000 claims description 31

- 238000000034 method Methods 0.000 claims description 30

- 229910015269 MoCu Inorganic materials 0.000 claims description 25

- 229910015153 MoAg Inorganic materials 0.000 claims description 23

- 229910052750 molybdenum Inorganic materials 0.000 claims description 23

- 239000010409 thin film Substances 0.000 claims description 23

- 229910052709 silver Inorganic materials 0.000 claims description 21

- 229910052802 copper Inorganic materials 0.000 claims description 20

- 239000000203 mixture Substances 0.000 claims description 16

- 229910052737 gold Inorganic materials 0.000 claims description 14

- 238000004519 manufacturing process Methods 0.000 claims description 13

- 238000005452 bending Methods 0.000 claims description 12

- 230000008021 deposition Effects 0.000 claims description 10

- 239000011521 glass Substances 0.000 claims description 10

- 239000011159 matrix material Substances 0.000 claims description 10

- 239000000654 additive Substances 0.000 claims description 9

- 230000000996 additive effect Effects 0.000 claims description 8

- 238000005259 measurement Methods 0.000 claims description 8

- 239000006104 solid solution Substances 0.000 claims description 7

- 239000004973 liquid crystal related substance Substances 0.000 claims description 6

- 239000011888 foil Substances 0.000 claims description 3

- 229910052500 inorganic mineral Inorganic materials 0.000 claims description 2

- 239000011707 mineral Substances 0.000 claims description 2

- 229920000642 polymer Polymers 0.000 claims description 2

- 239000002356 single layer Substances 0.000 claims description 2

- 239000010949 copper Substances 0.000 description 43

- 239000004065 semiconductor Substances 0.000 description 31

- 239000011733 molybdenum Substances 0.000 description 19

- 239000010931 gold Substances 0.000 description 18

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 17

- 238000000576 coating method Methods 0.000 description 14

- 239000011248 coating agent Substances 0.000 description 12

- 238000000151 deposition Methods 0.000 description 12

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 12

- 238000004544 sputter deposition Methods 0.000 description 12

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 11

- 239000000843 powder Substances 0.000 description 11

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 10

- 229910052782 aluminium Inorganic materials 0.000 description 9

- 230000001419 dependent effect Effects 0.000 description 9

- 239000012212 insulator Substances 0.000 description 9

- 239000004332 silver Substances 0.000 description 9

- 239000010936 titanium Substances 0.000 description 9

- 239000011651 chromium Substances 0.000 description 8

- JAONJTDQXUSBGG-UHFFFAOYSA-N dialuminum;dizinc;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Al+3].[Al+3].[Zn+2].[Zn+2] JAONJTDQXUSBGG-UHFFFAOYSA-N 0.000 description 8

- 239000010955 niobium Substances 0.000 description 8

- 238000005240 physical vapour deposition Methods 0.000 description 8

- 239000000126 substance Substances 0.000 description 8

- 230000002093 peripheral effect Effects 0.000 description 7

- 229920001721 polyimide Polymers 0.000 description 7

- 239000000523 sample Substances 0.000 description 7

- 238000009864 tensile test Methods 0.000 description 7

- 239000004642 Polyimide Substances 0.000 description 6

- 229910052581 Si3N4 Inorganic materials 0.000 description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 6

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 6

- 229910021417 amorphous silicon Inorganic materials 0.000 description 6

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 6

- 238000005336 cracking Methods 0.000 description 6

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 6

- 239000011241 protective layer Substances 0.000 description 6

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 6

- 229910052814 silicon oxide Inorganic materials 0.000 description 6

- 238000005477 sputtering target Methods 0.000 description 6

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 5

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 239000012535 impurity Substances 0.000 description 5

- 230000000977 initiatory effect Effects 0.000 description 5

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 5

- 239000012925 reference material Substances 0.000 description 5

- 229910052719 titanium Inorganic materials 0.000 description 5

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 4

- 239000000956 alloy Substances 0.000 description 4

- 229910052804 chromium Inorganic materials 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 239000007789 gas Substances 0.000 description 4

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 4

- 229910052758 niobium Inorganic materials 0.000 description 4

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 4

- 230000003287 optical effect Effects 0.000 description 4

- 229910052697 platinum Inorganic materials 0.000 description 4

- 229910052710 silicon Inorganic materials 0.000 description 4

- 239000010703 silicon Substances 0.000 description 4

- 239000010944 silver (metal) Substances 0.000 description 4

- 229910052715 tantalum Inorganic materials 0.000 description 4

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 4

- 229920001621 AMOLED Polymers 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 3

- 239000013078 crystal Substances 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 239000010408 film Substances 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 238000007731 hot pressing Methods 0.000 description 3

- 229910044991 metal oxide Inorganic materials 0.000 description 3

- 150000004706 metal oxides Chemical class 0.000 description 3

- -1 polyethylene terephthalates Polymers 0.000 description 3

- 229920005591 polysilicon Polymers 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 235000012431 wafers Nutrition 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- 229910052779 Neodymium Inorganic materials 0.000 description 2

- 238000002441 X-ray diffraction Methods 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 238000007792 addition Methods 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 239000005388 borosilicate glass Substances 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 238000000635 electron micrograph Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 238000002474 experimental method Methods 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 229910052741 iridium Inorganic materials 0.000 description 2

- 150000002751 molybdenum Chemical class 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- KDLHZDBZIXYQEI-UHFFFAOYSA-N palladium Substances [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 2

- 229920003223 poly(pyromellitimide-1,4-diphenyl ether) Polymers 0.000 description 2

- 238000005245 sintering Methods 0.000 description 2

- 238000012360 testing method Methods 0.000 description 2

- 238000010290 vacuum plasma spraying Methods 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 229910017488 Cu K Inorganic materials 0.000 description 1

- 229910017541 Cu-K Inorganic materials 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- 239000004734 Polyphenylene sulfide Substances 0.000 description 1

- 229910000831 Steel Inorganic materials 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- WYTGDNHDOZPMIW-RCBQFDQVSA-N alstonine Natural products C1=CC2=C3C=CC=CC3=NC2=C2N1C[C@H]1[C@H](C)OC=C(C(=O)OC)[C@H]1C2 WYTGDNHDOZPMIW-RCBQFDQVSA-N 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 239000002800 charge carrier Substances 0.000 description 1

- 229910052729 chemical element Inorganic materials 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000005056 compaction Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 230000032798 delamination Effects 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000009501 film coating Methods 0.000 description 1

- 238000005242 forging Methods 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- LNEPOXFFQSENCJ-UHFFFAOYSA-N haloperidol Chemical compound C1CC(O)(C=2C=CC(Cl)=CC=2)CCN1CCCC(=O)C1=CC=C(F)C=C1 LNEPOXFFQSENCJ-UHFFFAOYSA-N 0.000 description 1

- 238000001513 hot isostatic pressing Methods 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 239000010445 mica Substances 0.000 description 1

- 229910052618 mica group Inorganic materials 0.000 description 1

- 230000037230 mobility Effects 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 229920006280 packaging film Polymers 0.000 description 1

- 239000012785 packaging film Substances 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 229920001568 phenolic resin Polymers 0.000 description 1

- 239000005011 phenolic resin Substances 0.000 description 1

- 229920003207 poly(ethylene-2,6-naphthalate) Polymers 0.000 description 1

- 229920000058 polyacrylate Polymers 0.000 description 1

- 229920006122 polyamide resin Polymers 0.000 description 1

- 229920001230 polyarylate Polymers 0.000 description 1

- 229920000515 polycarbonate Polymers 0.000 description 1

- 239000004417 polycarbonate Substances 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920006393 polyether sulfone Polymers 0.000 description 1

- 229920000139 polyethylene terephthalate Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920001955 polyphenylene ether Polymers 0.000 description 1

- 229920000069 polyphenylene sulfide Polymers 0.000 description 1

- 238000004663 powder metallurgy Methods 0.000 description 1

- 238000001556 precipitation Methods 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 238000001953 recrystallisation Methods 0.000 description 1

- 239000013074 reference sample Substances 0.000 description 1

- 238000005096 rolling process Methods 0.000 description 1

- 238000007493 shaping process Methods 0.000 description 1

- 238000002490 spark plasma sintering Methods 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 239000010959 steel Substances 0.000 description 1

- OFIYHXOOOISSDN-UHFFFAOYSA-N tellanylidenegallium Chemical compound [Te]=[Ga] OFIYHXOOOISSDN-UHFFFAOYSA-N 0.000 description 1

- 238000007751 thermal spraying Methods 0.000 description 1

- 229920006337 unsaturated polyester resin Polymers 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 239000011787 zinc oxide Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K77/00—Constructional details of devices covered by this subclass and not covered by groups H10K10/80, H10K30/80, H10K50/80 or H10K59/80

- H10K77/10—Substrates, e.g. flexible substrates

- H10K77/111—Flexible substrates

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/22—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the process of coating

- C23C14/24—Vacuum evaporation

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B22—CASTING; POWDER METALLURGY

- B22F—WORKING METALLIC POWDER; MANUFACTURE OF ARTICLES FROM METALLIC POWDER; MAKING METALLIC POWDER; APPARATUS OR DEVICES SPECIALLY ADAPTED FOR METALLIC POWDER

- B22F3/00—Manufacture of workpieces or articles from metallic powder characterised by the manner of compacting or sintering; Apparatus specially adapted therefor ; Presses and furnaces

- B22F3/12—Both compacting and sintering

- B22F3/14—Both compacting and sintering simultaneously

- B22F3/15—Hot isostatic pressing

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/06—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the coating material

- C23C14/14—Metallic material, boron or silicon

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/06—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the coating material

- C23C14/14—Metallic material, boron or silicon

- C23C14/20—Metallic material, boron or silicon on organic substrates

- C23C14/205—Metallic material, boron or silicon on organic substrates by cathodic sputtering

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/22—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the process of coating

- C23C14/34—Sputtering

- C23C14/3407—Cathode assembly for sputtering apparatus, e.g. Target

- C23C14/3414—Metallurgical or chemical aspects of target preparation, e.g. casting, powder metallurgy

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C24/00—Coating starting from inorganic powder

- C23C24/02—Coating starting from inorganic powder by application of pressure only

- C23C24/04—Impact or kinetic deposition of particles

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C28/00—Coating for obtaining at least two superposed coatings either by methods not provided for in a single one of groups C23C2/00 - C23C26/00 or by combinations of methods provided for in subclasses C23C and C25C or C25D

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C28/00—Coating for obtaining at least two superposed coatings either by methods not provided for in a single one of groups C23C2/00 - C23C26/00 or by combinations of methods provided for in subclasses C23C and C25C or C25D

- C23C28/30—Coatings combining at least one metallic layer and at least one inorganic non-metallic layer

- C23C28/32—Coatings combining at least one metallic layer and at least one inorganic non-metallic layer including at least one pure metallic layer

- C23C28/322—Coatings combining at least one metallic layer and at least one inorganic non-metallic layer including at least one pure metallic layer only coatings of metal elements only

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C28/00—Coating for obtaining at least two superposed coatings either by methods not provided for in a single one of groups C23C2/00 - C23C26/00 or by combinations of methods provided for in subclasses C23C and C25C or C25D

- C23C28/30—Coatings combining at least one metallic layer and at least one inorganic non-metallic layer

- C23C28/34—Coatings combining at least one metallic layer and at least one inorganic non-metallic layer including at least one inorganic non-metallic material layer, e.g. metal carbide, nitride, boride, silicide layer and their mixtures, enamels, phosphates and sulphates

- C23C28/345—Coatings combining at least one metallic layer and at least one inorganic non-metallic layer including at least one inorganic non-metallic material layer, e.g. metal carbide, nitride, boride, silicide layer and their mixtures, enamels, phosphates and sulphates with at least one oxide layer

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C28/00—Coating for obtaining at least two superposed coatings either by methods not provided for in a single one of groups C23C2/00 - C23C26/00 or by combinations of methods provided for in subclasses C23C and C25C or C25D

- C23C28/30—Coatings combining at least one metallic layer and at least one inorganic non-metallic layer

- C23C28/34—Coatings combining at least one metallic layer and at least one inorganic non-metallic layer including at least one inorganic non-metallic material layer, e.g. metal carbide, nitride, boride, silicide layer and their mixtures, enamels, phosphates and sulphates

- C23C28/345—Coatings combining at least one metallic layer and at least one inorganic non-metallic layer including at least one inorganic non-metallic material layer, e.g. metal carbide, nitride, boride, silicide layer and their mixtures, enamels, phosphates and sulphates with at least one oxide layer

- C23C28/3455—Coatings combining at least one metallic layer and at least one inorganic non-metallic layer including at least one inorganic non-metallic material layer, e.g. metal carbide, nitride, boride, silicide layer and their mixtures, enamels, phosphates and sulphates with at least one oxide layer with a refractory ceramic layer, e.g. refractory metal oxide, ZrO2, rare earth oxides or a thermal barrier system comprising at least one refractory oxide layer

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/133305—Flexible substrates, e.g. plastics, organic film

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1218—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition or structure of the substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

- H01L27/1244—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits for preventing breakage, peeling or short circuiting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41733—Source or drain electrodes for field effect devices for thin film transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42384—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/45—Ohmic electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/45—Ohmic electrodes

- H01L29/456—Ohmic electrodes on silicon

- H01L29/458—Ohmic electrodes on silicon for thin film silicon, e.g. source or drain electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/4908—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET for thin film semiconductor, e.g. gate of TFT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78603—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the insulating substrate or support

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/17—Passive-matrix OLED displays

- H10K59/179—Interconnections, e.g. wiring lines or terminals

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

- H10K59/805—Electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K71/00—Manufacture or treatment specially adapted for the organic devices covered by this subclass

- H10K71/60—Forming conductive regions or layers, e.g. electrodes

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B22—CASTING; POWDER METALLURGY

- B22F—WORKING METALLIC POWDER; MANUFACTURE OF ARTICLES FROM METALLIC POWDER; MAKING METALLIC POWDER; APPARATUS OR DEVICES SPECIALLY ADAPTED FOR METALLIC POWDER

- B22F3/00—Manufacture of workpieces or articles from metallic powder characterised by the manner of compacting or sintering; Apparatus specially adapted therefor ; Presses and furnaces

- B22F3/10—Sintering only

- B22F3/105—Sintering only by using electric current other than for infrared radiant energy, laser radiation or plasma ; by ultrasonic bonding

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B22—CASTING; POWDER METALLURGY

- B22F—WORKING METALLIC POWDER; MANUFACTURE OF ARTICLES FROM METALLIC POWDER; MAKING METALLIC POWDER; APPARATUS OR DEVICES SPECIALLY ADAPTED FOR METALLIC POWDER

- B22F3/00—Manufacture of workpieces or articles from metallic powder characterised by the manner of compacting or sintering; Apparatus specially adapted therefor ; Presses and furnaces

- B22F3/12—Both compacting and sintering

- B22F3/14—Both compacting and sintering simultaneously

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13452—Conductors connecting driver circuitry and terminals of panels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K2102/00—Constructional details relating to the organic devices covered by this subclass

- H10K2102/301—Details of OLEDs

- H10K2102/311—Flexible OLED

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/549—Organic PV cells

Description

本発明は、請求項1の前提部の特徴を有するMo系層の層平面内での電気伝導率維持のための添加物の使用、請求項2の前提部の特徴を有するフレキシブル被覆部品、及び請求項20の前提部の特徴を有するフレキシブル被覆部品の製造方法に関する。

The present invention relates to the use of an additive for maintaining the electrical conductivity in the layer plane of the Mo-based layer having the features of the preamble of

フレキシブル部品の分野における技術的進歩は、薄膜材料分野での進歩と密接に関連している。特に、この進歩は、電子工学、特に、電子(ディスプレイ画面)、例えば、液晶表示装置(液晶ディスプレイ画面:TFT-LCD)、AM-OLED(アクティブマトリックス有機発光ダイオード)又はマイクロLED(発光ダイオード)ディスプレイ画面のアクティブ制御のための構造の一部(アクティブマトリックス)としての、例えば、薄膜トランジスタ(TFT)等の薄膜部品の分野でのさらなる発展を可能にする。アクティブマトリックス構造は、別の用途、例えば、X線放射のためのセンサアレイにおいても使用することができる。これらの用途においては、導電体経路は、行(「ゲートライン」、「ロウ」)及び列(「信号ライン」、「行ライン」、「データライン」)としてマトリックス状に配置されている。導電体路は、電気信号、電流又は電圧をある地点から別の地点へと伝達するための導電経路を提供する。 Technological advances in the field of flexible components are closely related to advances in the field of thin film materials. In particular, this progress is due to electronics, in particular electronics (display screens), such as liquid crystal displays (liquid crystal display screens: TFT-LCD), AM-OLED (active matrix organic light emitting diode) or micro LED (light emitting diode) displays. It allows further development in the field of thin film components, for example thin film transistors (TFTs), as part of the structure (active matrix) for the active control of screens. Active matrix structures can also be used in other applications, such as sensor arrays for X-ray radiation. In these applications, the conductor paths are arranged in a matrix in rows (“gate lines”, “rows”) and columns (“signal lines”, “row lines”, “data lines”). An electrical conductor path provides a conductive path for the transmission of electrical signals, currents or voltages from one point to another.

各アクティブマトリックスの行又は列は、長く細い導体路(例えば、数センチメートル~2メートル弱までの長さ、数マイクロメートル~数十マイクロメートルまでの幅、及び数十ナノメートル~数百ナノメートルまでの全層厚さを有する)からなり、この導体路は、薄膜トランジスタ領域にTFTのゲート電極(「制御電極」)又はソース/ドレイン電極(「流入電極」及び「流出電極」)を形成するそれぞれ1つ以上の拡張部を有する。それらの導体路は、TFTのゲート電極又はソース/ドレイン電極と、外部接触のための接触領域(「導体パッド」)又はディスプレイ画面制御のためのゲートドライバ構造及びデータドライバ構造(行ドライバ及び列ドライバ)が配置されている基板の周辺領域に接続する。 Each active matrix row or column consists of long, thin conductor tracks (e.g., lengths from a few centimeters to just under two meters, widths from a few micrometers to tens of micrometers, and tens of nanometers to hundreds of nanometers). ), which form the gate electrode (“control electrode”) or the source/drain electrode (“inflow electrode” and “outflow electrode”) of the TFT in the thin film transistor area, respectively. It has one or more extensions. These conductor tracks are the gate electrodes or source/drain electrodes of the TFTs and contact areas ("contact pads") for external contact or gate driver structures and data driver structures (row drivers and column drivers) for display screen control. ) are located on the peripheral area of the substrate.

アクティブマトリックス制御によって、それぞれの個々の画素(ピクセル)の輝度は、1つのTFT(例えば、TFT-LCD)又は複数のTFT(例えば、AM-OLEDディスプレイ画面)を全体にわたって個別に調節できる。この場合に、長いゲート導体路及び信号導体路に沿った電圧降下はできるだけ低いことが重要である。なぜなら、長さに依存する不要な輝度差が画素に生ずることとなるからである(人間の目は輝度差に対して非常に敏感に反応する)。 With active matrix control, the brightness of each individual picture element (pixel) can be individually adjusted across a single TFT (eg TFT-LCD) or multiple TFTs (eg AM-OLED display screen). In this case, it is important that the voltage drop along long gate conductor tracks and signal conductor tracks is as low as possible. This is because unnecessary length-dependent luminance differences will occur in pixels (the human eye is very sensitive to luminance differences).

屈曲性、フレキシブル、又は回動可能な基板上に配置されているアクティブマトリックス構造の場合に、特に、長い行導体路及び列導体路は、高い変形応力及び/又は曲げ応力及び/又はねじり応力を受けている。TFT構造内のゲート電極及びソース/ドレイン電極では空間的な広がり(一般的に、数マイクロメートル~数十マイクロメートルまでの辺長を有する矩形面)がはるかに小さいため、この応力は非常に小さくなる。特に、導体路材料が脆性の場合には、この応力により、すぐに何桁も電気抵抗が増加する。その結果、導体路に沿って配置されたTFTには規定の電圧が均一に供給されなくなり、ディスプレイ画面用途の場合には、長さに依存する輝度差が生じることがある。極端な場合には、導体路はその電気伝導性を完全に失い、画素の全面消灯(Totalausfall)が生ずることもある。 In the case of active matrix structures arranged on flexible, flexible or pivotable substrates, in particular long row and column conductor tracks are subject to high deformation and/or bending and/or torsion stresses. I am receiving . This stress is very large because the spatial extent of the gate and source /drain electrodes in the TFT structure is much smaller (generally rectangular areas with side lengths of a few micrometers up to tens of micrometers). becomes smaller. Especially when the conductor track material is brittle, this stress quickly leads to an increase in the electrical resistance by many orders of magnitude. As a result , the TFTs arranged along the conductor path are not uniformly supplied with a defined voltage , and in the case of display screen applications , length-dependent luminance differences may occur. In extreme cases, the conductor track may completely lose its electrical conductivity, resulting in total fall of the pixel.

特に、モバイル用途、例えば、携帯電話、タブレットPC、PDA(携帯情報端末)のためのディスプレイ画面の場合に、ディスプレイ画面基板上には、画像コンテンツの表示のための実際のユニットの他にさらに周辺電気回路が実装されている。それは、例えばゲート電極の制御用回路(ゲートドライバ)、ソース/ドレイン電極の制御回路(データドライバ)、DC-DC変換器、デジタル-アナログ変換器、タイミングコントローラ、又はバッファ回路及びインターフェイス回路である。そのようなディスプレイ画面とその制御ユニットとの組み合わせは、システムオンパネル(SOP)(ディスプレイ画面パネルに搭載されたシステム)又は基板がガラスから成る場合にはシステムオンガラス(SOG)(ガラスに搭載されたシステム)と呼ばれる。別個の筐体を含む外部集積回路(IC)として実装する代わりに、ディスプレイ画面制御のための周辺電気回路を基板上に直接配置することは有利である。基本的な利点は、低い製造コスト、低い電流消費、狭い所要スペース、及び高い信頼性である。システムオンパネルディスプレイ画面は、しばしば低温ポリシリコン(low temperature poly-Silicon)(LTPS)技術によって実現されるが、アモルファスシリコン又は金属酸化物等の別の半導体によっても可能である。基板上に配置された周辺回路の一部は、電気導体路、ゲートライン及び信号ラインを介して個々の画素のTFTと接続され、その長さは、ディスプレイ画面の大きさに応じて数mmから200cmまでである。変形、曲げ又はねじり応力を受けて導体路の抵抗変化は、ディスプレイ画面の個々の画素又は行全体若しくは列全体の消灯を防ぐために、或いはディスプレイ画面の輝度又は色の不要な差(「ムラ」)を防ぐために、できる限り小さくすべきである。 Especially in the case of display screens for mobile applications, e.g. mobile phones, tablet PCs, PDAs (Personal Digital Assistants), on the display screen substrate, besides the actual unit for the display of the image content, there are further peripherals. An electrical circuit is implemented. It is, for example, a circuit for controlling gate electrodes (gate driver), a control circuit for source/drain electrodes (data driver), a DC-DC converter, a digital-analog converter, a timing controller, or a buffer circuit and an interface circuit. The combination of such a display screen and its control unit can be System on Panel (SOP) (system mounted on display screen panel) or System on Glass (SOG) if the substrate is made of glass (mounted on glass). system). It is advantageous to place the peripheral electrical circuitry for display screen control directly on the substrate instead of implementing it as an external integrated circuit (IC) that includes a separate housing. The basic advantages are low manufacturing costs, low current consumption, small space requirements and high reliability. System-on-panel display screens are often realized with low temperature poly-Silicon (LTPS) technology, but other semiconductors such as amorphous silicon or metal oxides are also possible. Some of the peripheral circuits arranged on the substrate are connected to the TFTs of individual pixels via electrical conductor paths, gate lines and signal lines, the length of which varies from a few millimeters to several millimeters depending on the size of the display screen. Up to 200 cm. Changes in the resistance of conductor tracks under deformation, bending or torsional stresses may be used to prevent the extinguishing of individual pixels or entire rows or columns of the display screen, or to unwanted differences in luminance or color ("mura") of the display screen. should be as small as possible to prevent

フレキシブル接触センサ(例えば、抵抗性センサ又は容量性センサ)もマトリックス状に配置されたx電極及びy電極を使用するが、一般的に、アクティブTFT構造を有していない。数cm~数mまでのより大きなセンサの場合には、非常に長く細い、例えば、10cm~100cmの長さ及び5μm~50μmの幅を有する導体路構造が使用される。この用途の場合にも、変形、曲げ又はねじり応力受けた導体路の抵抗変化(増加)はできるだけ小さくすべきである。さもないとセンサの故障(例えば、信号対雑音比の低下による)が起こる可能性があるからである。 Flexible contact sensors (eg, resistive or capacitive sensors) also use matrix-arranged x- and y-electrodes, but generally do not have an active TFT structure. For larger sensors, from a few centimeters to several meters, very long and narrow conductor track structures are used, for example with lengths of 10 cm to 100 cm and widths of 5 μm to 50 μm. For this application, too, the resistance change (increase) of the conductor tracks subjected to deformation, bending or torsion stress should be as small as possible. Otherwise, sensor failure (eg, due to reduced signal-to-noise ratio) may occur.

特許文献1(図7)において、曲げ応力を受けている導体路中の機械的応力を減らすために、非直線的、例えば、正弦曲線形、波形、矩形波形、蛇行形又はのこぎり波形の導体路構造が提案されている。亀裂伝播を防ぐために、分岐して再結合した導体路構造(上記文献中の図8c)が提案されている。しかしながら、これらの全ての構造は単純な直線導体路よりも多くのスペースを必要とし、電流は2つの地点の間で全体的により長い経路を伝わらなければならないので、さらなる電圧降下又は信号対雑音比が低下する可能性がある。 In U.S. Pat. No. 6,300,000 (FIG. 7), non-linear, e.g., sinusoidal, wavy, rectangular, serpentine or saw-tooth conductor tracks are used to reduce mechanical stress in conductor tracks under bending stress. structure is proposed. To prevent crack propagation, a bifurcated and recombined conductor track structure (FIG. 8c in the above document) has been proposed. However, all these structures require more space than a simple straight conductor track, and the current must travel an overall longer path between two points, resulting in additional voltage drop or signal-to-noise ratio. may decline.

さらに、新たな集積化技術の開発の進歩により、電子装置とフレキシブル基板との組み合わせ、及びその結果として、よりフレキシブルの高い電子部品の製造も可能となる。問題のこの種の従来技術は、特許文献2により形成される。従来技術に関するさらなる情報については、この文献を参照されたい。 Furthermore, advances in the development of new integration techniques have made it possible to combine electronic devices with flexible substrates and, as a result, manufacture more flexible electronic components. A prior art of this kind in question is formed by US Pat. For more information on the prior art, please refer to this document.

本発明の目的は、1回又は繰り返しの曲げ応力、引張応力、及び/又はねじり応力を受けるフレキシブル基板上に施された金属層の電気伝導率維持することである。特に、本発明の目的は、フレキシブル基板上の電気導体路(金属層)である。電気導体路に沿った、すなわち層平面内での導体路の電気抵抗は、変形応力、曲げ応力又はねじり応力を受けた場合に、ほんの少し、特に、10%以下しか変化しない。 It is an object of the present invention to maintain the electrical conductivity of metal layers applied on flexible substrates that are subjected to single or repeated bending, tensile and/or torsional stresses. In particular, the object of the invention is an electrical conductor track (metal layer) on a flexible substrate. The electrical resistance of the conductor track along the conductor track, ie in the layer plane, changes only slightly, in particular less than 10%, when subjected to deformation, bending or torsion stress.

上記目的は、請求項1に記載の添加物の使用、請求項2に記載のフレキシブル被覆部品、及び請求項20の特徴を有するフレキシブル被覆部品の製造方法によって解決される。本発明の好適な実施形態は、従属請求項に規定されている。

The object is solved by the use of an additive according to

本発明によって、フレキシブル部品の1回又は繰り返しの曲げ応力及び/又は引張応力及び/又はねじり応力を受けた場合に、Mo系(モリブデン系の)層又は金属層の層平面内での電気伝導率維持を保証する。これは、フレキシブル部品の延性向上によって実現される。 According to the invention, the electrical stability in the layer plane of the Mo-based (molybdenum-based) or metal layers when subjected to single or repeated bending stresses and/or tensile stresses and/or torsional stresses of the flexible part. Ensures conductivity maintenance. This is achieved by increasing the ductility of the flexible part.

請求項2に規定されたように、複数の金属層をフレキシブル基板上に設けることができる。その際、各金属層には、半導体層又は電気絶縁性層が両側に直接隣接しており、かつ金属層自体が請求項2により単層構造、2層構造又は3層構造として形成されるという制限が加えられる。

As defined in

Mo系層又はMoX層は、少なくとも50重量%のMo、特に、少なくとも60重量%のMoを含有する。 The Mo-based layer or MoX layer contains at least 50% by weight Mo, in particular at least 60% by weight Mo.

MoX層は、別のXを含有するMoX部分層を有する複数のMoX部分層から構成できる。 The MoX layer can consist of multiple MoX sublayers with another X-containing MoX sublayer.

電気伝導率維持以外に、延性向上により機械的損傷許容性が増加する。例えば、多層複合材料の層間剥離の危険性を低下させる。 Besides maintaining electrical conductivity, increased ductility increases mechanical damage tolerance. For example, it reduces the risk of delamination of multilayer composites.

当然ながら、Mo系層(MoX層)は、添加物Xを除き純粋なMoである必要はないが、むしろ不純物、特に、PVD(物理的気相成長)法、中でも、スパッタリング法(陰極スパッタリング)のプロセス雰囲気に由来する不純物(例えば、Ar、O、N、C)が存在する場合がある。しかしながら、金属不純物は0.5原子%以下でなければならない。 Of course, the Mo-based layer (MoX layer) does not have to be pure Mo, except for the additive X, but rather impurities, especially the PVD (Physical Vapor Deposition) method, especially the sputtering method (cathode sputtering). Impurities (eg, Ar, O, N, C) may be present from the process atmosphere of . However, metal impurities should be less than 0.5 atomic percent.

上記の元素Cu、Ag、Auのうちでも、Cuが特に好ましい。本明細書では、所望の効果を達成するためには、より低い原子%で十分である。さらに、CuはAg及びAuよりもより費用対効果が良い。 Among the above elements Cu, Ag, and Au, Cu is particularly preferred. A lower atomic % is sufficient here to achieve the desired effect. Furthermore, Cu is more cost effective than Ag and Au.

本発明によれば、層状構造は、一方の側に直接隣接している半導体層又は電気絶縁性層を有する金属層と、他方の側に金属層に直接隣接している半導体層又は電気絶縁性層とを有する。これらの特性は、少なくともフレキシブル被覆部品のある領域において満たされている(しかしながら、フレキシブル部品、特に、フレキシブル電子部品の全ての領域で必ずしも満たされる必要はない)。さらに、可能な隣接層を以下に詳細に説明する。この場合に、「電気絶縁性」とは、電気抵抗が1メガオームより大きいことを意味すると理解すべきである。 According to the invention, the layered structure comprises a metal layer with a semiconducting or electrically insulating layer directly adjacent on one side and a semiconducting or electrically insulating layer directly adjacent to the metal layer on the other side. layer. These properties are met at least in some areas of the flexible covering component (but not necessarily in all areas of the flexible component, especially the flexible electronic component). Further possible adjacent layers are described in detail below. In this case, "electrically insulating" should be understood to mean an electrical resistance greater than 1 megohm.

本明細書では、フレキシビリティ及び「フレキシブル」とは、部品の使用に関連する特性に悪影響を与えることなく曲げ応力を吸収する、及び/又はそのような応力に耐える特性と理解すべきである。すなわち、十分にフレキシブルな部品は、大幅に向上した延性も有する。 As used herein, flexibility and "flexible" should be understood as the property of absorbing and/or withstanding bending stresses without adversely affecting the properties associated with the use of the part. That is, fully flexible parts also have significantly improved ductility.

大幅に向上した延性とは、本発明の意味において、部品及び/又は当然ながら含まれる1つ又は複数の層も、亀裂発生及び亀裂成長に対して高い抵抗性を有し、亀裂がある伸びまで形成されず、又はより大きな伸びで初めて形成されるか、又は亀裂進行の変化を意味すると理解すべきである。 Significantly increased ductility in the sense of the invention means that the component and/or of course also the included layer or layers have a high resistance to crack initiation and crack growth up to the elongation at which cracking occurs. It should be understood to mean no formation, or formation only at greater elongation, or a change in crack progression.

延性及びその結果としてのフレキシビリティを説明するために、本発明の範囲においては臨界伸びを使用する。臨界伸びは、フレキシブル基板上の1つ又は複数の層の電気抵抗Rが、初期状態に対して10%だけ高くなったとき(R/R 0 =1.1)の伸びε k 、として定義される。十分に高さの高いフレキシブルな部品においては、臨界伸びεkは大幅に増大し、1つ又は複数の層の導電性は、大幅に長く維持される。 Critical elongation is used within the scope of the present invention to describe ductility and resulting flexibility. The critical elongation is defined as the elongation ε k at which the electrical resistance R of a layer or layers on a flexible substrate increases by 10% relative to the initial state (R/R 0 =1.1) . be done. In flexible parts of sufficiently high height , the critical elongation ε k increases significantly and the conductivity of one or more layers remains significantly longer.

フレキシブル基板とは、本発明の範囲においては、曲げ応力を加えたときに、基板上に堆積された1又は複数の層(被覆)に伸びεが生ずる基板と理解すべきである。1つ又は複数の層が基板よりもずっと薄い場合に、伸びは、近似的にε=ds/2Rによって記述される(dsは基板の厚さ、Rは曲げ半径である)。1つ又は複数の層が基板と比べて非常に薄い場合には、1つ又は複数の層における伸びは、引張応力又は圧縮応力のみにほぼ等しく設定できる。例えば、フレキシブル基板は、1つ以上のポリマー素材、例えば、ポリイミド、ポリカーボネート、ポリエチレンテレフタレート、ポリエチレンナフタレート、ポリエーテルスルホン、ポリアリレート又は多環式オレフィン系で構成できる。1つ以上のポリマー材料をベースとする大部分のフレキシブル基板は、8GPa以下の弾性率を有する。薄板ガラス(1mm以下の厚さを有するガラス)、1mm以下の厚さを有する金属板、例えば、鋼板、1mm以下の厚さを有するアルミニウム箔、銅板若しくはチタン箔、又は例えば、雲母等の鉱物材料も、本発明によるフレキシブル部品に適したフレキシブル基板である。 A flexible substrate, within the scope of the present invention, is to be understood as a substrate on which the layer or layers (coatings) deposited thereon undergo an elongation ε when subjected to a bending stress. If one or more layers are much thinner than the substrate, the elongation is approximately described by ε=ds/2R, where ds is the thickness of the substrate and R is the bend radius. If the layer or layers are very thin compared to the substrate, the elongation in the layer or layers can be set approximately equal to only tensile or compressive stress. For example, flexible substrates can be composed of one or more polymeric materials such as polyimides, polycarbonates, polyethylene terephthalates, polyethylene naphthalates, polyethersulfones, polyarylates, or polycyclic olefins. Most flexible substrates based on one or more polymeric materials have elastic moduli of 8 GPa or less. Thin glass (glass having a thickness of 1 mm or less), metal sheets having a thickness of 1 mm or less, such as steel sheets, aluminum foils, copper sheets or titanium foils having a thickness of 1 mm or less, or mineral materials such as mica. are also flexible substrates suitable for flexible components according to the present invention.

本発明に適したフレキシブル基板は、同様に、1つ又は複数の層及び/又は1つ又は複数の材料から構成できる。そのような基板は、他の材料から成る1つ以上の層で既に予め完全に又は部分的にのみ被覆できる。 Flexible substrates suitable for the present invention can likewise be composed of one or more layers and/or one or more materials. Such substrates can already be completely or only partially pre-coated with one or more layers of other materials.

この部品は、フレキシブル被覆部品であるのが好ましい。例えば、金属防湿層又は光学層を有する包装薄膜等のフレキシブル被覆部品と比較して、フレキシブル被覆電子部品は、少なくとも1つの電流を伝導する層を有する。これには、例えば、フレキシブル回路、フレキシブルディスプレイ画面、フレキシブルセンサ素子、フレキシブル薄膜コンデンサ、フレキシブル薄膜電池又は単純な導電性薄膜、例えば、フレキシブルプリント回路基板が該当する。本発明により構成できる上記のフレキシブル電子部品の例は、本明細書の最初に説明した。 This part is preferably a flexible cover part. Flexible coated electronic components have at least one current-conducting layer, compared to flexible coated components such as, for example, packaging films with metallic moisture barriers or optical layers. This includes, for example, flexible circuits, flexible display screens, flexible sensor elements, flexible thin-film capacitors, flexible thin-film batteries or simple conductive thin-films, such as flexible printed circuit boards. Examples of such flexible electronic components that can be constructed in accordance with the present invention were described earlier in this specification.

本発明によるフレキシブル被覆部品の金属層は、1μm以下の厚さを有するのが好ましい。金属層は、好ましくは5nmの最小厚さを有し、さらに好ましくは少なくとも10nmの厚さを有する。また、5nm~300nmの厚さ、5nm~100nmの厚さはなおさらに好ましい。上記の層厚さは、金属層が接着構造層又は拡散障壁層として使用される場合に特に有利である。或いは150nm~400nmの厚さ範囲が有利である。150nm~400nmの層厚さは、本発明による被覆されたフレキシブル部品をディスプレイ画面において、例えば、ゲート電極層として使用するために特に良く適している。 The metal layer of the flexible jacket according to the invention preferably has a thickness of 1 μm or less. The metal layer preferably has a minimum thickness of 5 nm, more preferably at least 10 nm. Also, a thickness of 5 nm to 300 nm, even more preferably a thickness of 5 nm to 100 nm. The layer thicknesses mentioned are particularly advantageous when the metal layer is used as an adhesion structure layer or as a diffusion barrier layer. Alternatively, a thickness range of 150 nm to 400 nm is advantageous. A layer thickness of 150 nm to 400 nm is particularly well suited for using the coated flexible parts according to the invention in display screens, for example as gate electrode layers.

請求項2又はその従属請求項の1つに規定された1つ又は複数の金属層は、薄膜トランジスタ(TFT)の一部になることができる。

The metal layer or layers defined in

本発明による部品の例示的実施形態では、少なくとも1つのMoX層において、Xが元素Cuであり、このMoCu層が0.5原子%以下~50原子%以下のCuを含有し、好ましくは1原子%以上~20原子%以下のCuを含有することができる。この場合に、金属層のMoX層全体をMoCuから構成するのが特に好ましい。 In an exemplary embodiment of the component according to the invention, in at least one MoX layer, X is elemental Cu, said MoCu layer containing ≦0.5 atomic % to ≦50 atomic % Cu, preferably 1 atomic % to 20 atomic % or less of Cu. In this case, it is particularly preferred for the entire MoX layer of the metal layer to consist of MoCu.

本発明による部品の例示的実施形態では、少なくとも1つのMoX層において、Xが元素Agであり、このMoAg層が10原子%以上~50原子%以下のAgを含有し、好ましくは20原子%以上~50原子%以下のAgを含有することができる。この場合に、金属層のMoX層全体がMoAgから構成するのが特に好ましい。 In an exemplary embodiment of the component according to the invention, in at least one MoX layer, X is the element Ag, the MoAg layer containing >10 to <50 atomic % Ag, preferably >20 atomic % It can contain Ag up to ˜50 atomic %. In this case, it is particularly preferred that the entire MoX layer of the metal layer consists of MoAg.

本発明による部品の例示的実施形態では、少なくとも1つのMoX層において、Xが元素Auであり、このMoAu金属層が5原子%以上~20原子%以下のAuを含有することができる。この場合に、金属層のMoX層全体がMoAuから構成するのが特に好ましい。 In an exemplary embodiment of the component according to the invention, in at least one MoX layer, X is the element Au, and this MoAu metal layer may contain ≧5 atomic % and ≦20 atomic % Au. In this case, it is particularly preferred that the entire MoX layer of the metal layer consists of MoAu.

本発明による構成部品の例示的実施形態では、各々のMoX層が、200マイクロオームcm以下、好ましくは100マイクロオームcm以下、特に好ましくは50マイクロオームcm以下の層抵抗ρを有することができる。 In exemplary embodiments of the component according to the invention, each MoX layer can have a layer resistance ρ of 200 micro-Ohm cm or less, preferably 100 micro-Ohm cm or less, particularly preferably 50 micro-Ohm cm or less.

本発明による部品の例示的実施形態では、金属層に直接隣接している半導体層又は電気絶縁性層の少なくも一方を複数の層として形成することができる。また、直接隣接している層又は電気絶縁層の両方を複数の層として形成することができる。 In exemplary embodiments of the component according to the invention, at least one of the semiconductor layer or the electrically insulating layer directly adjacent to the metal layer can be formed as a plurality of layers. Also, both the immediately adjacent layers or the electrically insulating layers can be formed as multiple layers.

本発明による構成部品の例示的実施形態では、金属層は全体で50マイクロオームcm以下、好ましくは10マイクロオームcm以下、特に好ましくは3.5マイクロオームcm以下の層抵抗ρを有することができる。 In an exemplary embodiment of the component according to the invention, the metal layers in total can have a layer resistance ρ of 50 micro-Ohm cm or less, preferably of 10 micro-Ohm cm or less, particularly preferably of 3.5 micro-Ohm cm or less. .

本発明による方法では、0.5原子%以上~50原子%以下のXを含有し、XがCu、Ag、Auの群から選択される1つの元素である少なくとも1つのMoX層が堆積される。この場合に、MoX層は、請求項2に規定されているように金属層を形成できるか又はその一部になることができる。

In the method according to the present invention, at least one MoX layer is deposited containing ≧0.5 atomic % and ≦50 atomic % of X, where X is one element selected from the group of Cu, Ag, Au. . In this case, the MoX layer can form or be part of the metal layer as defined in

少なくとも1つのMoX層及び/又は金属層の堆積は、各種種類の蒸着法によって行うことができる。例えば、上記の堆積は、物理蒸着又は化学蒸着によって行うことができる。 Deposition of the at least one MoX layer and/or metal layer can be done by various types of vapor deposition methods. For example, the deposition can be by physical vapor deposition or chemical vapor deposition.

しかしながら、少なくとも1つのMoX層及び/又は金属層の堆積が、PVD法、特に、スパッタリング法によって行うことが有利である。PVD法(物理的気相成長)は、薄膜被覆技術として知られている。この技術は、被覆材料の粒子を気相に変換してから、基板上に堆積させる。PVD法による堆積によって、特に、均一に堆積できる。その特性は、被覆された面全体にわたり等しく等方的である被覆を堆積できる。この方法のさらなる利点は、結果として実現できる低い基板温度である。従って、例えば、ポリマーの被覆が可能となる。さらに、PVD層は基板への非常に良好な接着の点で優れている。 However, it is advantageous if the deposition of at least one MoX layer and/or metal layer is performed by a PVD method, in particular a sputtering method. PVD (Physical Vapor Deposition) is known as thin film coating technology. This technique converts particles of the coating material into the gas phase before depositing them on the substrate. Deposition by the PVD method allows a particularly uniform deposition. Its properties allow it to deposit a coating that is equally isotropic over the entire coated surface. A further advantage of this method is the low substrate temperature that can be achieved as a result. Thus, for example, polymer coatings are possible. Moreover, the PVD layer is distinguished by very good adhesion to the substrate.

MoX層又は金属層がスパッタリング法(陰極スパッタリング法とも言う)によって堆積される場合に特に好ましい。スパッタリング法は、大きな面積の均一な被覆に比較的容易に使用できるため、大量生産に費用対効果が良い。 It is particularly preferred if the MoX layer or metal layer is deposited by a sputtering method (also called cathode sputtering method). Sputtering methods are relatively easy to use for uniform coating of large areas, making them cost effective for mass production.

本発明による方法が、0.5原子%~50原子%以下の間のXを含有するMo系のターゲットを設ける工程をさらに含むことが非常に好ましい。 It is highly preferred that the method according to the invention further comprises the step of providing a Mo-based target containing between 0.5 atomic % and up to 50 atomic % of X.

0.5原子%~50原子%以下の間のXを含有するMo系のターゲットは、少なくとも1つのMoX層及び/又は少なくとも1つの金属層の堆積前に設けられる。従って、MoX層及び/又は金属層は、設けられたターゲットから堆積される。 A Mo-based target containing between 0.5 atomic % and up to 50 atomic % of X is provided prior to the deposition of the at least one MoX layer and/or the at least one metal layer. Thus, MoX layers and/or metal layers are deposited from the targets provided.

この場合に、ターゲットとは、被覆装置の被覆供給源と理解すべきである。1つの好適

な方法においては、使用されるターゲットは、スパッタリング法のためのスパッタリングターゲットである。

In this case, the target should be understood as the coating source of the coating device. In one preferred method, the target used is a sputtering target for sputtering processes.

被覆物の化学組成は、使用するターゲットの化学組成によって決定される。しかしながら、ターゲットに中に含まれる元素のスパッタリング挙動(スパッタリング収率)が僅かに異なることによって、被覆物の組成がターゲット組成からずれることがある。 The chemical composition of the coating is determined by the chemical composition of the target used . However , slight differences in the sputtering behavior (sputtering yield) of the elements contained in the target can cause the composition of the coating to deviate from the target composition .

例えば、MoCuターゲットからCuが優先的にスパッタリングされることによって、堆積された被覆中のCu含有量が僅かに増加することがある。例えば、10原子%以上のCuを含有する被覆を形成するために、対応するターゲットは10原子%以下のCuを含有することができる。 For example, preferential sputtering of Cu from a MoCu target may slightly increase the Cu content in the deposited coating. For example, to form a coating containing 10 atomic % or more Cu, the corresponding target can contain 10 atomic % or less Cu.

単一のターゲットを使用する代わりに、別々のターゲットからの同時堆積、好ましくは同時スパッタリングによっても、金属層を堆積できる。この場合に、被覆物の化学組成は、異なるターゲットの選択によってさらに制御することができる。 Instead of using a single target, the metal layers can also be deposited by co-deposition, preferably co-sputtering , from separate targets. In this case, the chemical composition of the coating can be further controlled by selection of different targets.

金属層の堆積にさらに適したスパッタリングターゲットの製造は、例えば、粉末冶金によって行うことができる。 The manufacture of sputtering targets, which are more suitable for depositing metal layers, can be carried out, for example, by powder metallurgy.

スパッタリングターゲットの製造のための可能な粉末冶金的方法は、ホットプレス(HP)又は放電プラズマ焼結(SPS)等のホットプレス方法に基づいている。両方の場合において、粉末混合物をプレス金型内に充填し、その金型内で加熱し、高い圧縮圧力及び高い温度で焼結/圧縮して高密度部品にする。この場合に、優先配向(肌理)を有しない均一な結晶粒を有する均質な微細構造が生じる。 Possible powder metallurgical methods for the production of sputtering targets are based on hot pressing methods such as hot pressing (HP) or spark plasma sintering (SPS). In both cases, the powder mixture is filled into a press die, heated in the die and sintered/ compacted at high compaction pressure and temperature into a dense part. In this case, a homogeneous microstructure with uniform grains without preferential orientation (texture) results.

スパッタリングターゲット製造のための類似の粉末冶金的方法は、熱間等方圧加圧法(HIP)である。この場合に、圧縮される材料は、変形可能な高密度容器(通常、金属缶)中に充填される。この場合に、この材料は、粉末、粉末混合物又は圧粉体(圧縮粉末の形で)にすることができる。この容器中に存在する材料は、保護ガス(例えば、アルゴン)下で、加圧容器中において高温高圧で焼結される。ガス圧があらゆる方向から作用するため、この方法は等方圧加圧法と呼ばれる。代表的なプロセスパラメーターは、例えば、1100℃及び100MPaで3時間の保持時間である。この場合に、優先配向(肌理)を有しない均一な結晶粒を有する均質な微細構造が生じる。 A similar powder metallurgical method for sputtering target manufacture is hot isostatic pressing (HIP). In this case, the material to be compressed is packed into a deformable high-density container (usually a metal can). In this case, this material can be a powder, a powder mixture or a compact (in the form of compacted powder). The material present in this container is sintered at high temperature and pressure in a pressurized container under protective gas (eg argon). This method is called isostatic pressurization because the gas pressure acts from all directions. Typical process parameters are, for example, 1100° C. and 100 MPa with a hold time of 3 hours. In this case, a homogeneous microstructure with uniform grains without preferential orientation (texture) results.

粉末冶金的方法によるスパッタリングターゲット製造のさらなる選択肢は、焼結とその後の成形である。この場合に、粉末成形体は水素雰囲気下又は真空下で高温焼結される。焼結後に、例えば、圧延又は鍛造等の成形工程を行うことで、99%超の高い相対密度が得られる。この場合に、優先配向(肌理)を有する細長い結晶粒を有する微細構造が生じる。任意の後続の低張力焼きなまし又は再結晶化焼きなましの場合に、均一な結晶粒を有する均質な微細構造が得られるが、なお優先配向(肌理)を有する。 A further option for manufacturing sputtering targets by powder metallurgical methods is sintering followed by shaping. In this case, the powder compact is sintered at high temperature in a hydrogen atmosphere or under vacuum. After sintering, a forming step such as rolling or forging, for example, results in high relative densities of over 99%. In this case, a microstructure with elongated grains with preferential orientation (texture) results. In the case of an optional subsequent low tension anneal or recrystallization anneal, a homogeneous microstructure with uniform grains is obtained , but still with preferred orientation (texture).

粉末冶金的方法によるスパッタリングターゲット製造のさらなる選択肢は、対応する支持構造物、例えば、金属又は管上に、粉末又は粉末混合物を溶射法、例えば、低温ガス溶射又は真空プラズマ溶射(VPS)によって施すことである。 A further option for sputtering target manufacture by powder metallurgical methods is to apply the powder or powder mixture onto a corresponding support structure, such as a metal or tube , by thermal spraying methods, such as cold gas spraying or vacuum plasma spraying (VPS). is.

以下で、本発明を例示的実施形態及び図面に基づきより詳細に説明する。 The invention is explained in more detail below on the basis of exemplary embodiments and drawings.

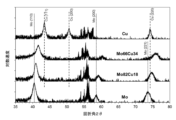

実施例1

一連の複数の実験の範囲内で、Mo系の各種金属層をポリイミド基板上に堆積させた。この場合に、各種化学組成を有する層を形成した。

Example 1

Within a series of experiments, various Mo-based metal layers were deposited on polyimide substrates. In this case, layers with different chemical compositions were formed.

Mo系の金属層の組成を表1に要約した。 The compositions of the Mo-based metal layers are summarized in Table 1.

[表1]スパッタリングされたMoCu層の化学組成

Table 1 Chemical Composition of Sputtered MoCu Layers

モリブデン系合金のための参照材料として、純粋なMoを50nmの厚さを有するモリブデン層の形で使用した。 As a reference material for molybdenum-based alloys, pure Mo was used in the form of a molybdenum layer with a thickness of 50 nm.

全ての層を、ポリイミドから成る50μm厚さの薄膜(PI、例えば、Kapton(登録商標))上に室温で堆積した。この場合に、プロセスパラメーターは、結果に対する異なるプロセス条件の影響を可能な限り排除するために一定に保った。層厚さは、結果に対する形状効果の影響を避けるために50nmで一定に保った。 All layers were deposited at room temperature on 50 μm thick thin films of polyimide (PI, eg Kapton®). In this case the process parameters were kept constant in order to eliminate as much as possible the influence of different process conditions on the results. The layer thickness was kept constant at 50 nm to avoid shape effects on the results.

基板表面は完全に被覆されており、エッチング処理などによる微細構造の形成は行わなかった。 The substrate surface was completely covered , and no fine structure was formed by etching or the like .

ポリイミド基板上の層試料に対して、MTS Tyron 250(登録商標)汎用試験機を用いて一軸引張試験を実施した。試験構成を図1に概略的に示す。この場合に、基板を15%の最大伸びεまで弾性変形させた。引張試験の間に、四点法を使用して層の電気抵抗Rを連続的に記録した。測定開始時の電気抵抗をR0と呼ぶ。この場合に、初期状態における試料長さ(クランプ間の自由長さ)は20mmであり、幅は5mmであった。

Uniaxial tensile tests were performed on layer samples on polyimide substrates using an

測定構成を図1に概略的に示す。この場合に、Lconstは、伸びが生じていない固定クランプ長を示す。ここで、フレキシブル基板上の層の電気抵抗Rが、初期状態に対して10%だけ増加する伸び、つまりR/R0=1.1を、臨界伸びε k と定義した。 The measurement setup is shown schematically in FIG. In this case, Lconst denotes the fixed clamping length without elongation. Here, the elongation at which the electrical resistance R of the layer on the flexible substrate increases by 10% relative to the initial state, ie, R/R 0 =1.1, was defined as the critical elongation ε k .

この引張試験によって求められた臨界伸びεkを表2に示す。 Table 2 shows the critical elongation ε k determined by this tensile test.

[表2]調べたMo層及びMoCu層の臨界伸びεk並びに純Moからなる参照試料との差。さらに、非導電性ホウケイ酸塩ガラス(Corning Eagle XG(登録商標))上の500nm厚さの層の層抵抗を示す。

Table 2 Critical elongation ε k of the investigated Mo and MoCu layers and their difference from the reference sample consisting of pure Mo. Furthermore, the layer resistance of a 500 nm thick layer on non-conductive borosilicate glass (Corning Eagle XG®) is shown.