JP7204353B2 - Transistors and semiconductor devices - Google Patents

Transistors and semiconductor devices Download PDFInfo

- Publication number

- JP7204353B2 JP7204353B2 JP2018114837A JP2018114837A JP7204353B2 JP 7204353 B2 JP7204353 B2 JP 7204353B2 JP 2018114837 A JP2018114837 A JP 2018114837A JP 2018114837 A JP2018114837 A JP 2018114837A JP 7204353 B2 JP7204353 B2 JP 7204353B2

- Authority

- JP

- Japan

- Prior art keywords

- oxide

- insulator

- film

- transistor

- conductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Description

本発明の一態様は、半導体装置、ならびに半導体装置の作製方法に関する。または、本発明の一態様は、半導体ウエハ、モジュール、および電子機器に関する。 One embodiment of the present invention relates to a semiconductor device and a method for manufacturing the semiconductor device. Alternatively, one aspect of the present invention relates to semiconductor wafers, modules, and electronic devices.

なお、本明細書等において半導体装置とは、半導体特性を利用することで機能し得る装置全般を指す。トランジスタなどの半導体素子をはじめ、半導体回路、演算装置、記憶装置は、半導体装置の一態様である。表示装置(液晶表示装置、発光表示装置など)、投影装置、照明装置、電気光学装置、蓄電装置、記憶装置、半導体回路、撮像装置、および電子機器などは、半導体装置を有すると言える場合がある。 Note that a semiconductor device in this specification and the like refers to all devices that can function by utilizing semiconductor characteristics. A semiconductor element such as a transistor, a semiconductor circuit, an arithmetic device, and a memory device are examples of semiconductor devices. Display devices (liquid crystal display devices, light-emitting display devices, etc.), projection devices, lighting devices, electro-optic devices, power storage devices, storage devices, semiconductor circuits, imaging devices, electronic devices, and the like can be said to have semiconductor devices in some cases. .

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物(コンポジション・オブ・マター)に関するものである。 Note that one embodiment of the present invention is not limited to the above technical field. One embodiment of the invention disclosed in this specification and the like relates to a product, a method, or a manufacturing method. Alternatively, one aspect of the invention relates to a process, machine, manufacture, or composition of matter.

トランジスタに適用可能な半導体薄膜として、シリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。酸化物半導体としては、例えば、酸化インジウム、酸化亜鉛などの一元系金属の酸化物のみでなく、多元系金属の酸化物も知られている。多元系金属の酸化物の中でも、特に、In-Ga-Zn酸化物(以下、IGZOとも呼ぶ。)に関する研究が盛んに行われている。 Silicon-based semiconductor materials are widely known as semiconductor thin films applicable to transistors, but oxide semiconductors are attracting attention as other materials. As oxide semiconductors, for example, not only single-component metal oxides such as indium oxide and zinc oxide, but also multi-component metal oxides are known. In--Ga--Zn oxides (hereinafter also referred to as IGZO) have been extensively studied among multicomponent metal oxides.

IGZOに関する研究により、酸化物半導体において、単結晶でも非晶質でもない、CAAC(c-axis aligned crystalline)構造およびnc(nanocrystalline)構造が見出された(非特許文献1乃至非特許文献3参照。)。非特許文献1および非特許文献2では、CAAC構造を有する酸化物半導体を用いてトランジスタを作製する技術も開示されている。さらに、CAAC構造およびnc構造よりも結晶性の低い酸化物半導体でさえも、微小な結晶を有することが、非特許文献4および非特許文献5に示されている。

Research on IGZO has found a CAAC (c-axis aligned crystalline) structure and an nc (nanocrystalline) structure, which are neither single crystal nor amorphous, in oxide semiconductors (see Non-Patent

さらに、IGZOを活性層として用いたトランジスタは極めて低いオフ電流を持ち(非特許文献6参照。)、その特性を利用したLSIおよびディスプレイが報告されている(非特許文献7および非特許文献8参照。)。

Furthermore, a transistor using IGZO as an active layer has an extremely low off-state current (see Non-Patent Document 6), and LSIs and displays utilizing this characteristic have been reported (see Non-Patent

チャネル形成領域に酸化物半導体を有するトランジスタであって、前記トランジスタは、ゲート、ソース、及びドレインを有し、前記酸化物半導体の下方には、第1の絶縁体が形成され、前記ゲートと、前記酸化物半導体との間には、第2の絶縁体が形成され、前記第1の絶縁体、及び前記第2の絶縁体のいずれか一方または双方は、シリコンを含む層と、ガリウムを含む層と、を有する、ことを特徴とするトランジスタ。 A transistor including an oxide semiconductor in a channel formation region, the transistor including a gate, a source, and a drain; a first insulator is formed below the oxide semiconductor; A second insulator is formed between the oxide semiconductor, and one or both of the first insulator and the second insulator include a layer containing silicon and a layer containing gallium. A transistor comprising: a layer;

本発明の一態様は、良好な電気特性を有する半導体装置を提供することを課題の一つとする。または、本発明の一態様は、信頼性が良好な半導体装置を提供することを課題の一つとする。または、本発明の一態様は、微細化または高集積化が可能な半導体装置を提供することを課題の一つとする。または、本発明の一態様は、オン電流が大きい半導体装置を提供することを課題の一つとする。または、本発明の一態様は、高い周波数特性を有する半導体装置を提供することを課題の一つとする。または、本発明の一態様は、生産性の高い半導体装置を提供することを課題の一つとする。 An object of one embodiment of the present invention is to provide a semiconductor device with favorable electrical characteristics. Another object of one embodiment of the present invention is to provide a highly reliable semiconductor device. Another object of one embodiment of the present invention is to provide a semiconductor device that can be miniaturized or highly integrated. Another object of one embodiment of the present invention is to provide a semiconductor device with high on-state current. Another object of one embodiment of the present invention is to provide a semiconductor device with high frequency characteristics. Another object of one embodiment of the present invention is to provide a highly productive semiconductor device.

本発明の一態様は、長期間においてデータの保持が可能な半導体装置を提供することを課題の一つとする。本発明の一態様は、データの書き込み速度が速い半導体装置を提供することを課題の一つとする。本発明の一態様は、設計自由度が高い半導体装置を提供することを課題の一つとする。本発明の一態様は、消費電力を抑えることができる半導体装置を提供することを課題の一つとする。本発明の一態様は、新規な半導体装置を提供することを課題の一つとする。 An object of one embodiment of the present invention is to provide a semiconductor device capable of holding data for a long time. An object of one embodiment of the present invention is to provide a semiconductor device with high data writing speed. An object of one embodiment of the present invention is to provide a semiconductor device with a high degree of freedom in design. An object of one embodiment of the present invention is to provide a semiconductor device that can consume less power. An object of one embodiment of the present invention is to provide a novel semiconductor device.

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。 The description of these problems does not preclude the existence of other problems. Note that one embodiment of the present invention does not necessarily solve all of these problems. Problems other than these are self-evident from the descriptions of the specification, drawings, claims, etc., and it is possible to extract problems other than these from the descriptions of the specification, drawings, claims, etc. is.

本発明の一態様は、チャネル形成領域に酸化物半導体を有するトランジスタであって、トランジスタは、ゲート、ソース、及びドレインを有し、酸化物半導体の下方には、第1の絶縁体が形成され、ゲートと、酸化物半導体との間には、第2の絶縁体が形成され、第1の絶縁体、及び第2の絶縁体のいずれか一方または双方は、シリコンを含む層と、ガリウムを含む層と、を有する。 One embodiment of the present invention is a transistor including an oxide semiconductor in a channel formation region, the transistor includes a gate, a source, and a drain, and a first insulator is formed below the oxide semiconductor. , a second insulator is formed between the gate and the oxide semiconductor, and one or both of the first insulator and the second insulator include a layer containing silicon and gallium. a layer comprising;

本発明の一態様は、チャネル形成領域に酸化物半導体を有するトランジスタであって、トランジスタは、第1のゲート、第2のゲート、ソース、及びドレインを有し、第2のゲートと、酸化物半導体との間には、第1の絶縁体が形成され、第1のゲートと、酸化物半導体との間には、第2の絶縁体が形成され、第1の絶縁体、及び第2の絶縁体のいずれか一方または双方は、シリコンを含む層と、ガリウムを含む層と、を有する。 One embodiment of the present invention is a transistor including an oxide semiconductor in a channel formation region, the transistor including a first gate, a second gate, a source, and a drain; A first insulator is formed between the semiconductor, a second insulator is formed between the first gate and the oxide semiconductor, and the first insulator and the second insulator are formed between the first gate and the oxide semiconductor. Either or both of the insulators have a layer containing silicon and a layer containing gallium.

上記において、請求項1または請求項2のいずれか一項において、酸化物半導体は、インジウム、亜鉛、およびガリウムを含む。

In the above, in any one of

上記において、酸化物半導体、およびガリウムを含む層は、結晶構造を有している。 In the above, the oxide semiconductor and the layer containing gallium have a crystal structure.

上記において、容量素子と、を有する半導体装置であって、容量素子は、トランジスタに含まれるシリコンを含む層と、ガリウムを含む層と、を有する。 In the above semiconductor device including the capacitor, the capacitor includes a layer containing silicon and a layer containing gallium which are included in the transistor.

上記において、容量素子は、トランジスタの上方に形成される。 In the above, the capacitor is formed above the transistor.

上記において、容量素子は、トランジスタの下方に形成される。 In the above, the capacitor is formed below the transistor.

上記トランジスタは、第3の絶縁体と、第4の絶縁体と、を有する半導体装置であって、第3の絶縁体は、アルミニウムと、酸素と、を有し、第4の絶縁体は、シリコンと、窒素と、を有し、トランジスタの上面、下面、及び側面のいずれか一または複数は、第3の絶縁体、及び第4の絶縁体によって覆われている。 The transistor is a semiconductor device including a third insulator and a fourth insulator, the third insulator including aluminum and oxygen, and the fourth insulator comprising: It contains silicon and nitrogen, and one or more of a top surface, a bottom surface, and side surfaces of the transistor are covered with a third insulator and a fourth insulator.

上記において、第3の絶縁体は、第4の絶縁体よりも内側に位置する。 In the above, the third insulator is located inside the fourth insulator.

本発明の一態様により、良好な電気特性を有する半導体装置を提供することができる。または、本発明の一態様により、信頼性が良好な半導体装置を提供することができる。または、本発明の一態様により、微細化または高集積化が可能な半導体装置を提供することができる。または、本発明の一態様により、オン電流が大きい半導体装置を提供することができる。または、本発明の一態様により、高い周波数特性を有する半導体装置を提供することができる。または、本発明の一態様により、生産性の高い半導体装置を提供することができる。 According to one embodiment of the present invention, a semiconductor device with favorable electrical characteristics can be provided. Alternatively, according to one embodiment of the present invention, a highly reliable semiconductor device can be provided. Alternatively, according to one embodiment of the present invention, a semiconductor device that can be miniaturized or highly integrated can be provided. Alternatively, according to one embodiment of the present invention, a semiconductor device with high on-state current can be provided. Alternatively, according to one embodiment of the present invention, a semiconductor device with high frequency characteristics can be provided. Alternatively, according to one embodiment of the present invention, a semiconductor device with high productivity can be provided.

または、長期間においてデータの保持が可能な半導体装置を提供することができる。または、データの書き込み速度が速い半導体装置を提供することができる。または、設計自由度が高い半導体装置を提供することができる。または、消費電力を抑えることができる半導体装置を提供することができる。または、新規な半導体装置を提供することができる。 Alternatively, a semiconductor device capable of holding data for a long time can be provided. Alternatively, a semiconductor device with high data writing speed can be provided. Alternatively, a semiconductor device with a high degree of freedom in design can be provided. Alternatively, a semiconductor device with low power consumption can be provided. Alternatively, a novel semiconductor device can be provided.

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。 Note that the description of these effects does not preclude the existence of other effects. Note that one embodiment of the present invention does not need to have all of these effects. Effects other than these are self-evident from the descriptions of the specification, drawings, claims, etc., and it is possible to extract effects other than these from the descriptions of the specification, drawings, claims, etc. is.

以下、実施の形態について図面を参照しながら説明する。ただし、実施の形態は多くの異なる態様で実施することが可能であり、趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。 Hereinafter, embodiments will be described with reference to the drawings. However, those skilled in the art will readily appreciate that the embodiments can be embodied in many different forms and that various changes in form and detail can be made without departing from the spirit and scope thereof. be. Therefore, the present invention should not be construed as being limited to the description of the following embodiments.

また、図面において、大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお、図面は、理想的な例を模式的に示したものであり、図面に示す形状または値などに限定されない。例えば、実際の製造工程において、エッチングなどの処理により層やレジストマスクなどが意図せずに目減りすることがあるが、理解を容易とするために省略して示すことがある。また、図面において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する場合がある。また、同様の機能を指す場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。 Also, in the drawings, sizes, layer thicknesses, or regions may be exaggerated for clarity. Therefore, it is not necessarily limited to that scale. The drawings schematically show ideal examples, and are not limited to the shapes or values shown in the drawings. For example, in an actual manufacturing process, layers, resist masks, and the like may be unintentionally reduced due to processing such as etching, but are sometimes omitted for ease of understanding. In addition, in the drawings, the same reference numerals may be used in common for the same parts or parts having similar functions, and repeated description thereof may be omitted. Moreover, when referring to similar functions, the hatch patterns may be the same and no particular reference numerals may be attached.

また、特に上面図(「平面図」ともいう。)や斜視図などにおいて、発明の理解を容易とするため、一部の構成要素の記載を省略する場合がある。また、一部の隠れ線などの記載を省略する場合がある。 In particular, in top views (also referred to as “plan views”) and perspective views, description of some components may be omitted in order to facilitate understanding of the invention. Also, description of some hidden lines may be omitted.

また、本明細書等において、第1、第2等として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。また、本明細書等に記載されている序数詞と、本発明の一態様を特定するために用いられる序数詞は一致しない場合がある。 In this specification and the like, the ordinal numbers such as first and second are used for convenience and do not indicate the order of steps or the order of stacking. Therefore, for example, "first" can be appropriately replaced with "second" or "third". Also, the ordinal numbers described in this specification and the like may not match the ordinal numbers used to specify one aspect of the present invention.

また、本明細書等において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。したがって、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。 In this specification and the like, terms such as “above” and “below” are used for convenience in order to describe the positional relationship between configurations with reference to the drawings. In addition, the positional relationship between the configurations changes appropriately according to the direction in which each configuration is drawn. Therefore, it is not limited to the words and phrases described in the specification, and can be appropriately rephrased according to the situation.

例えば、本明細書等において、XとYとが直接的に接続されている場合と、XとYとが接続されている、と明示的に記載されている場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合とが、本明細書等に開示されているものとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも、図または文章に記載されているものとする。 For example, in this specification and the like, when X and Y are directly connected and when it is explicitly stated that X and Y are connected, X and Y are electrically The present specification and the like disclose the case where X and Y are functionally connected and the case where X and Y are functionally connected. Therefore, it is assumed that the connection relationships other than the connection relationships shown in the drawings or the text are not limited to the predetermined connection relationships, for example, the connection relationships shown in the drawings or the text.

ここで、X、Yは、対象物(例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など)であるとする。 Here, X and Y are objects (for example, devices, elements, circuits, wiring, electrodes, terminals, conductive films, layers, etc.).

また、ソースやドレインの機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、ソースやドレインの用語は、入れ替えて用いることができる場合がある。 Also, the functions of the source and the drain may be interchanged when using transistors of different polarities or when the direction of current changes in circuit operation. Therefore, in this specification and the like, the terms "source" and "drain" can be used interchangeably in some cases.

なお、本明細書等において、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネル幅(以下、「実効的なチャネル幅」ともいう。)と、トランジスタの上面図において示されるチャネル幅(以下、「見かけ上のチャネル幅」ともいう。)と、が異なる場合がある。例えば、ゲート電極が半導体の側面を覆う場合、実効的なチャネル幅が、見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつゲート電極が半導体の側面を覆うトランジスタでは、半導体の側面に形成されるチャネル形成領域の割合が大きくなる場合がある。その場合は、見かけ上のチャネル幅よりも、実効的なチャネル幅の方が大きくなる。 Note that in this specification and the like, depending on the structure of a transistor, the channel width in a region where a channel is actually formed (hereinafter also referred to as an "effective channel width") and the channel width shown in a top view of the transistor. (hereinafter also referred to as “apparent channel width”). For example, when the gate electrode covers the side surface of the semiconductor, the effective channel width becomes larger than the apparent channel width, and its influence cannot be ignored. For example, in a fine transistor in which a gate electrode covers the side surface of a semiconductor, the proportion of the channel formation region formed on the side surface of the semiconductor may be large. In that case, the effective channel width is larger than the apparent channel width.

このような場合、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるためには、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。 In such a case, it may be difficult to estimate the effective channel width by actual measurement. For example, in order to estimate the effective channel width from design values, it is necessary to assume that the shape of the semiconductor is known. Therefore, it is difficult to accurately measure the effective channel width if the shape of the semiconductor is not accurately known.

本明細書では、単にチャネル幅と記載した場合には、見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅などは、断面TEM像などを解析することなどによって、値を決定することができる。 In this specification, simply describing the channel width may refer to the apparent channel width. Alternatively, in this specification, simply referring to the channel width may refer to the effective channel width. The values of the channel length, channel width, effective channel width, apparent channel width, etc. can be determined by analyzing a cross-sectional TEM image or the like.

なお、半導体の不純物とは、例えば、半導体を構成する主成分以外をいう。例えば、濃度が0.1原子%未満の元素は不純物と言える。不純物が含まれることにより、例えば、半導体のDOS(Density of States)が高くなることや、結晶性が低下することなどが起こる場合がある。半導体が酸化物半導体である場合、半導体の特性を変化させる不純物としては、例えば、第1族元素、第2族元素、第13族元素、第14族元素、第15族元素、および酸化物半導体の主成分以外の遷移金属などがあり、例えば、水素、リチウム、ナトリウム、シリコン、ホウ素、リン、炭素、窒素などがある。酸化物半導体の場合、水も不純物として機能する場合がある。また、酸化物半導体の場合、例えば不純物の混入によって酸素欠損を形成する場合がある。また、半導体がシリコンである場合、半導体の特性を変化させる不純物としては、例えば、酸素、水素を除く第1族元素、第2族元素、第13族元素、第15族元素などがある。

Note that impurities in a semiconductor refer to, for example, substances other than the main components that constitute the semiconductor. For example, an element whose concentration is less than 0.1 atomic percent can be said to be an impurity. When impurities are contained, for example, the DOS (Density of States) of the semiconductor may increase, the crystallinity may decrease, and the like. When the semiconductor is an oxide semiconductor, impurities that change the characteristics of the semiconductor include, for example,

なお、本明細書等において、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものである。また、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多いものである。 Note that in this specification and the like, silicon oxynitride contains more oxygen than nitrogen as its composition. Silicon nitride oxide contains more nitrogen than oxygen in its composition.

また、本明細書等において、「絶縁体」という用語を、絶縁膜または絶縁層と言い換えることができる。また、「導電体」という用語を、導電膜または導電層と言い換えることができる。また、「半導体」という用語を、半導体膜または半導体層と言い換えることができる。 In this specification and the like, the term “insulator” can be replaced with an insulating film or an insulating layer. Also, the term “conductor” can be replaced with a conductive film or a conductive layer. Also, the term "semiconductor" can be interchanged with a semiconductor film or a semiconductor layer.

また、本明細書等において、「平行」とは、二つの直線が-10度以上10度以下の角度で配置されている状態をいう。したがって、-5度以上5度以下の場合も含まれる。また、「略平行」とは、二つの直線が-30度以上30度以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が80度以上100度以下の角度で配置されている状態をいう。したがって、85度以上95度以下の場合も含まれる。また、「略垂直」とは、二つの直線が60度以上120度以下の角度で配置されている状態をいう。 In this specification and the like, "parallel" means a state in which two straight lines are arranged at an angle of -10 degrees or more and 10 degrees or less. Therefore, the case of -5 degrees or more and 5 degrees or less is also included. Also, "substantially parallel" means a state in which two straight lines are arranged at an angle of -30 degrees or more and 30 degrees or less. "Perpendicular" means that two straight lines are arranged at an angle of 80 degrees or more and 100 degrees or less. Therefore, the case of 85 degrees or more and 95 degrees or less is also included. In addition, "substantially perpendicular" means a state in which two straight lines are arranged at an angle of 60 degrees or more and 120 degrees or less.

なお、本明細書において、バリア膜とは、水、水素などの不純物および酸素の透過を抑制する機能を有する膜のことであり、当該バリア膜に導電性を有する場合は、導電性バリア膜と呼ぶことがある。 Note that in this specification, a barrier film is a film that has a function of suppressing permeation of impurities such as water and hydrogen, and oxygen. I may call

本明細書等において、金属酸化物(metal oxide)とは、広い表現での金属の酸化物である。金属酸化物は、酸化物絶縁体、酸化物導電体(透明酸化物導電体を含む。)、酸化物半導体(Oxide Semiconductorまたは単にOSともいう。)などに分類される。例えば、トランジスタの半導体層に金属酸化物を用いた場合、当該金属酸化物を酸化物半導体と呼称する場合がある。つまり、OS FETあるいはOSトランジスタと記載する場合においては、酸化物または酸化物半導体を有するトランジスタと換言することができる。 In this specification and the like, a metal oxide is a metal oxide in broad terms. Metal oxides are classified into oxide insulators, oxide conductors (including transparent oxide conductors), oxide semiconductors (also referred to as oxide semiconductors or simply OSs), and the like. For example, when a metal oxide is used for a semiconductor layer of a transistor, the metal oxide is sometimes called an oxide semiconductor. In other words, an OS FET or an OS transistor can also be referred to as a transistor including an oxide or an oxide semiconductor.

また、本明細書等において、ノーマリーオフとは、ゲートに電位を印加しない、またはゲートに接地電位を与えたときに、トランジスタに流れるチャネル幅1μmあたりの電流が、室温において1×10-20A以下、85℃において1×10-18A以下、または125℃において1×10-16A以下であることをいう。 In this specification and the like, the term “normally off” means that a current per 1 μm of channel width flowing through a transistor when no potential is applied to the gate or when a ground potential is applied to the gate is 1×10 −20 at room temperature. A or less, 1×10 −18 A or less at 85° C., or 1×10 −16 A or less at 125° C.

(実施の形態1)

本実施の形態では、半導体装置の一形態を、図1乃至図10を用いて説明する。

(Embodiment 1)

In this embodiment, one mode of a semiconductor device will be described with reference to FIGS.

<トランジスタの構造1>

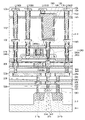

以下では、本発明の一態様に係るトランジスタ200を有する半導体装置の一例について説明する。図1(A)、図1(B)、および図1(C)は、本発明の一態様に係るトランジスタ200、およびトランジスタ200周辺の上面図および断面図である。図1(A)は上面図であり、図1(B)は、図1(A)に示す一点鎖線A1-A2、図1(C)は、一点鎖線A3-A4に対応する断面図である。なお、図1(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。

<

An example of a semiconductor device including the

本発明の一態様の半導体装置は、トランジスタ200と、層間膜として機能する絶縁体212、絶縁体214、絶縁体216、絶縁体280、絶縁体282、絶縁体284、および絶縁体284と、を有する。

A semiconductor device of one embodiment of the present invention includes the

[トランジスタ200]

図1に示すように、トランジスタ200は、基板(図示せず。)の上に配置され、絶縁体216に埋め込まれるように配置された導電体205と、絶縁体216の上および導電体205の上に配置された絶縁体222と、絶縁体222の上に配置された絶縁体224と、絶縁体224の上に配置された酸化物230(酸化物230a、酸化物230b、および酸化物230c)と、酸化物230の上に配置された絶縁体250と、絶縁体250上に配置された絶縁体252と、絶縁体252上に配置された導電体260(導電体260a、および導電体260b)と、酸化物230bの上面の一部と接する導電体240aおよび導電体240bと、絶縁体224の上面の一部、酸化物230aの側面、酸化物230bの側面、導電体240aの側面、導電体240aの上面、導電体240bの側面、および導電体240bの上面に接して配置された絶縁体274と、を有する。

[Transistor 200]

As shown in FIG. 1,

トランジスタ200において、酸化物230は、半導体として機能する金属酸化物(以下、酸化物半導体ともいう)を用いることが好ましい。チャネル形成領域に酸化物半導体を用いたトランジスタは、非導通状態において極めてリーク電流(オフ電流)が小さいため、低消費電力の半導体装置が提供できる。また、酸化物半導体は、スパッタリング法、ALD(Atomic Layer Deposition)法などを用いて成膜できるため、高集積型の半導体装置を構成するトランジスタ200に用いることができる。

In the

例えば、酸化物230に用いることができる酸化物半導体として、In-M-Zn酸化物(元素Mは、アルミニウム、ガリウム、イットリウム、錫、銅、バナジウム、ベリリウム、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、マグネシウムなどから選ばれた一種、または複数種)等がある。特に、元素Mは、アルミニウム、ガリウム、イットリウム、または錫を用いるとよい。また、酸化物230に用いることができる酸化物半導体として、In-M酸化物、In-Zn酸化物、またはM-Zn酸化物を用いてもよい。

For example, as an oxide semiconductor that can be used for the

一方で、酸化物半導体を用いたトランジスタは、酸化物半導体中の水素、窒素、金属元素などの不純物、および酸素欠損によって、その電気特性が変動しやすく、信頼性が悪くなる場合がある。 On the other hand, in a transistor using an oxide semiconductor, electrical characteristics are likely to vary due to oxygen vacancies and impurities such as hydrogen, nitrogen, and a metal element in the oxide semiconductor, and reliability may be degraded.

例えば、酸化物半導体に含まれる水素は、金属原子と結合する酸素と反応して水になるため、酸素欠損を形成する場合がある。該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。従って、酸素欠損が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。このため、酸化物半導体中の酸素欠損はできる限り低減されていることが好ましい。 For example, hydrogen contained in an oxide semiconductor reacts with oxygen that bonds to a metal atom to form water, which may cause oxygen vacancies. When hydrogen enters the oxygen vacancies, electrons, which are carriers, may be generated. Therefore, a transistor including an oxide semiconductor containing oxygen vacancies is likely to have normally-on characteristics. Therefore, oxygen vacancies in the oxide semiconductor are preferably reduced as much as possible.

また、酸化物半導体中の酸素欠損は、例えば、酸化物半導体に近接して設けられる構造体に金属を用いる場合に、該金属に酸化物半導体の酸素原子が吸収されることで、生じる場合がある。また、酸素原子を吸収した金属が、酸化し、高抵抗化する場合がある。また、酸化物半導体に近接して設けられる構造体中の水素が、酸化物半導体中に拡散することで、酸素欠損を生じる場合がある。 Further, oxygen vacancies in the oxide semiconductor may occur, for example, when a metal is used for a structure provided close to the oxide semiconductor, oxygen atoms of the oxide semiconductor are absorbed by the metal. be. Also, the metal that has absorbed the oxygen atoms may be oxidized and have a high resistance. In addition, hydrogen in a structure provided close to an oxide semiconductor may diffuse into the oxide semiconductor to cause oxygen vacancies.

酸化物半導体中の酸素欠損を低減するためには、酸化物半導体の近傍に、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物を配置するとよい。例えば、絶縁体250、および絶縁体280には、化学量論的組成よりも酸素が過剰に存在する領域(以下、過剰酸素領域ともいう)が形成されていることが好ましい。当該過剰酸素が、酸化物半導体へと拡散することで、酸素欠損を補償することができる。

In order to reduce oxygen vacancies in the oxide semiconductor, an oxide containing more oxygen than the stoichiometric composition is preferably placed near the oxide semiconductor. For example, the

例えば、図1に示すトランジスタ200において、ソース電極、およびドレイン電極として機能する導電体240と、酸化物230bが接する。例えば、導電体240に用いた導電性材料が、酸化物230の酸素を吸収する性質を有する場合、または酸化物230に水素、窒素、金属元素などの不純物を供給する性質を有する場合、酸化物230の導電体240と接する領域、または当該領域の近傍において、酸素が欠乏する、または不純物が拡散することにより、部分的に低抵抗化される。従って、酸化物230と導電体240とのコンタクト抵抗を低減することができる。

For example, in the

一方で、図1に示すトランジスタ200において、ゲート電極として機能する導電体260は、ゲート絶縁体として機能する絶縁体250、および絶縁体252を介して、酸化物230と重畳する。例えば、導電体260が、酸化物230の酸素を吸収する性質を有する場合、または酸化物230に水素、窒素、金属元素などの不純物を供給する性質を有する場合、ゲート絶縁体を介して、酸化物230の酸素を奪う、または不純物が拡散する蓋然性が高い。

On the other hand, in the

酸化物230の導電体260と重畳する領域は、チャネルが形成される領域を有するため、低抵抗化することで、トランジスタのノーマリーオン化、リーク電流の増大、またはストレス印加によるしきい値電圧のシフト等、トランジスタの電気特性の不良が生じる場合がある。特に、トランジスタ200が微細化した場合、ソースとドレインとの間が短絡する蓋然性が高くなる。

A region of the

つまり、酸化物半導体を用いたトランジスタは、酸化物半導体中のチャネルが形成される領域に不純物および酸素欠損が存在すると、電気特性が変動しやすく、信頼性が悪くなる場合がある。また、酸化物半導体中のチャネルが形成される領域に酸素欠損が含まれていると、トランジスタはノーマリーオン特性となりやすい。従って、酸化物230のチャネルが形成される領域中の不純物、および酸素欠損はできる限り低減されていることが好ましい。

That is, in a transistor including an oxide semiconductor, when impurities and oxygen vacancies are present in a region where a channel is formed in the oxide semiconductor, electrical characteristics are likely to vary, and reliability may be degraded. In addition, when oxygen vacancies are included in a region where a channel is formed in the oxide semiconductor, the transistor tends to have normally-on characteristics. Therefore, it is preferable that impurities and oxygen vacancies in the region where the channel of

そこで、ゲート絶縁体は、酸素、水素、または不純物に対してバリア性を有する膜を含むことが好ましい。具体的には、図1に示すトランジスタ200は、少なくともゲート絶縁体として機能する絶縁体250、および絶縁体252を有する。ここで、導電体260と接する絶縁体252は、酸素、水素、または不純物に対しバリア性を有する膜を用いるとよい。

Therefore, the gate insulator preferably contains a film having barrier properties against oxygen, hydrogen, or impurities. Specifically, the

なお、本明細書において、不純物の拡散を抑制する機能を有する膜を、不純物が透過しにくい膜、不純物の透過性が低い膜、不純物に対してバリア性を有する膜、不純物に対するバリア膜などと呼ぶ場合がある。同様に、水素または酸素の拡散を抑制する機能を有する膜を、水素または酸素が透過しにくい膜、水素または酸素の透過性が低い膜、水素または酸素に対してバリア性を有する膜、水素または酸素に対するバリア膜などと呼ぶ場合がある。 Note that in this specification, a film having a function of suppressing impurity diffusion is referred to as a film through which impurities are difficult to permeate, a film with low impurity permeability, a film having a barrier property against impurities, a barrier film against impurities, or the like. may be called. Similarly, the film having the function of suppressing the diffusion of hydrogen or oxygen is selected from a film impermeable to hydrogen or oxygen, a film having low permeability to hydrogen or oxygen, a film having barrier properties against hydrogen or oxygen, It is sometimes called a barrier film against oxygen.

特に、酸化物230としてIn-Ga-Zn酸化物を用いる場合、絶縁体252としてガリウム酸化物、酸化物230bよりもガリウムの含有量が多い、またはIn-Ga-Zn酸化物の中で酸化物230bよりも絶縁性が高い材料を用いることが好ましい。絶縁体252を構成する元素と、酸化物230を構成する元素が共通であるため、例えば、絶縁体252を構成する元素が、酸化物230へと拡散したとしても、酸化物230の低抵抗化の要因とならない。

In particular, when an In--Ga--Zn oxide is used as the

具体的には、酸化物230bとして、In:Ga:Zn=4:2:3[原子数比]のIn-Ga-Zn酸化物を用いた場合、絶縁体252は、In:Ga:Zn=1:3:4[原子数比]、またはIn:Ga:Zn=1:3:4[原子数比]近傍のIn-Ga-Zn酸化物を用いることができる。なお、上記In:Ga:Zn=1:3:4[原子数比]近傍のIn-Ga-Zn酸化物としては、例えば、In:Ga:Zn=1:2.97:2.61[原子数比]のIn-Ga-Zn酸化物などが挙げられる。

Specifically, when an In—Ga—Zn oxide having an atomic ratio of In:Ga:Zn=4:2:3 is used as the

特に、酸化ガリウムは、窒化シリコンよりも誘電率が高い高誘電率絶縁材料であり、いわゆるhigh-k材料である。トランジスタの微細化、および高集積化が進むと、ゲート絶縁体の薄膜化により、リーク電流などの問題が生じる場合がある。ゲート絶縁体として機能する絶縁体にhigh-k材料を用いることで、物理膜厚を保持したまま、ゲート絶縁体の等価酸化膜厚(EOT)の薄膜化が可能となる。従って、トランジスタ動作時のゲート電位の低減が可能となる。 In particular, gallium oxide is a high dielectric constant insulating material having a dielectric constant higher than that of silicon nitride, and is a so-called high-k material. As transistors are miniaturized and highly integrated, thinning of gate insulators may cause problems such as leakage current. By using a high-k material for the insulator that functions as the gate insulator, it is possible to reduce the equivalent oxide thickness (EOT) of the gate insulator while maintaining the physical thickness. Therefore, it is possible to reduce the gate potential during transistor operation.

なお、絶縁体252は、酸化物230のチャネルが形成される領域上に形成される。後述するが、チャネル形成領域は、結晶性を有することが好ましい。そこで、絶縁体252の形成では、酸化物230への成膜ダメージが生じにくい成膜方法を用いることが好ましい。例えば、ALD法は、被成膜面へのダメージが生じにくい成膜方法である。よって、絶縁体252をALD法によって成膜することで、被成膜面である酸化物230への成膜ダメージを低減し、酸化物230の結晶性を保持することができる。

Note that the

また、絶縁体252は、絶縁体280などに形成された開口の底部および側面に形成される。また、ゲート絶縁体として機能する絶縁体252の膜厚は、当該開口の底部で均一であることが好ましい。ALD法は、段差や凹凸を有する構造体に対して被覆性に優れた成膜方法である。よって、絶縁体252をALD法によって成膜することで、当該開口の底部で絶縁体252の膜厚を均一にすることができる。

Also, the

なお、酸化物230と絶縁体252との間に、絶縁体250を有していてもよい。酸化物230と近接する絶縁体250は、加熱により脱離する酸素(過剰酸素ともいう。)を含むことが好ましい。または、絶縁体250は、水素濃度が低く、化学量論的組成よりも酸素が過剰に存在する領域(以下、過剰酸素領域ともいう。)を有することが好ましい。絶縁体250が有する過剰酸素は、生産工程における加熱処理、または加熱を伴う処理により、酸化物230へと拡散し、酸化物230の酸素欠損を低減し、トランジスタのノーマリーオン化を抑制することができる。

Note that an

例えば、水素濃度が低く、過剰酸素領域を有する絶縁体として、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコンなどを用いることができる。特に、酸化シリコン、および酸化窒化シリコンは熱に対して安定であるため好ましい。具体的に、水素濃度が低く、過剰酸素領域または過剰酸素を有する絶縁体は、SIMSにより得られる水素濃度が、5×1020atoms/cm3未満、好ましくは1×1020atoms/cm3未満、より好ましくは5×1019atoms/cm3未満とする。また、TDS(Thermal Desorption Spectroscopy)分析にて、酸素分子に換算しての酸素の脱離量が2.0×1014molecules/cm2以上、好ましくは1.0×1015molecules/cm2以上である。なお、当該TDS分析時における膜の表面温度としては100℃以上700℃以下、または100℃以上500℃以下の範囲が好ましい。 For example, silicon oxide, silicon oxynitride, silicon nitride oxide, silicon nitride, or the like can be used as the insulator having a low hydrogen concentration and an excess oxygen region. In particular, silicon oxide and silicon oxynitride are preferable because they are stable against heat. Specifically, an insulator having a low hydrogen concentration and an excess oxygen region or excess oxygen has a hydrogen concentration of less than 5×10 20 atoms/cm 3 , preferably less than 1×10 20 atoms/cm 3 by SIMS. , more preferably less than 5×10 19 atoms/cm 3 . Further, according to TDS (Thermal Desorption Spectroscopy) analysis, the amount of oxygen desorption in terms of oxygen molecules is 2.0×10 14 molecules/cm 2 or more, preferably 1.0×10 15 molecules/cm 2 or more. is. The surface temperature of the film during the TDS analysis is preferably in the range of 100° C. to 700° C. or in the range of 100° C. to 500° C.

ゲート絶縁体として機能する絶縁体を、high-k材料と、熱的に安定している材料との積層構造とすることで、物理膜厚を保ちながら、トランジスタ動作時のゲート電位の低減が可能となる。また、熱的に安定かつ比誘電率の高い積層構造とすることができる。 The gate potential during transistor operation can be reduced while maintaining the physical film thickness by making the insulator that functions as a gate insulator into a laminated structure of a high-k material and a thermally stable material. becomes. Moreover, it is possible to obtain a laminated structure that is thermally stable and has a high dielectric constant.

上記構造と同様に、酸化物230と、ゲート電極として機能する導電体205との間に配置された、ゲート絶縁体として機能する絶縁体は、酸素、水素、または不純物に対してバリア性を有する膜を含むことが好ましい。具体的には、図1に示すトランジスタ200は、少なくともゲート絶縁体として機能する絶縁体222、および絶縁体224を有する。

Similar to the structure above, the insulator functioning as the gate insulator, placed between the

従って、導電体205と接する絶縁体222は、酸素、水素、または不純物に対しバリア性を有する膜を用いるとよい。一方、酸化物230と接する絶縁体224は、加熱により脱離する酸素(過剰酸素ともいう。)を含むことが好ましい。または、絶縁体250は、水素濃度が低く、化学量論的組成よりも酸素が過剰に存在する領域(以下、過剰酸素領域ともいう。)を有することが好ましい。また、熱的に安定している材料を用いるとよい。

Therefore, for the

ゲート絶縁体として機能する絶縁体を、high-k材料と、熱的に安定している材料との積層構造とすることで、物理膜厚を保ちながら、トランジスタ動作時のゲート電位の低減が可能となる。また、熱的に安定かつ比誘電率の高い積層構造とすることができる。 The gate potential during transistor operation can be reduced while maintaining the physical film thickness by making the insulator that functions as a gate insulator into a laminated structure of a high-k material and a thermally stable material. becomes. Moreover, it is possible to obtain a laminated structure that is thermally stable and has a high dielectric constant.

以上より、安定した電気特性を有する半導体装置を提供することができる。また、信頼性が高い半導体装置を提供することができる。また、消費電力が小さい半導体装置を提供することができる。 As described above, a semiconductor device having stable electrical characteristics can be provided. Further, a highly reliable semiconductor device can be provided. Further, a semiconductor device with low power consumption can be provided.

以下では、本発明の一態様に係るトランジスタ200を有する半導体装置の詳細な構成について説明する。

A detailed structure of the semiconductor device including the

まず、チャネル形成領域として機能する領域を有する酸化物230は、酸化物230a、酸化物230b、および酸化物230cを有することが好ましい。具体的には、酸化物230bと絶縁体224との間には、酸化物230aを配置する。また、酸化物230bと絶縁体250との間には、酸化物230cを配置する。

First,

酸化物230b下に酸化物230aを有することで、酸化物230aよりも下方に形成された構造物から、酸化物230bへの不純物の拡散を抑制することができる。また、酸化物230b上に酸化物230cを有することで、酸化物230cよりも上方に形成された構造物から、酸化物230bへの不純物の拡散を抑制することができる。

By providing the

酸化物230は、酸化物半導体として機能する金属酸化物を用いることが好ましい。例えば、チャネルが形成される領域の金属酸化物としては、バンドギャップが2eV以上、好ましくは2.5eV以上のものを用いることが好ましい。このように、バンドギャップの大きい金属酸化物を用いることで、トランジスタのオフ電流を低減することができる。

A metal oxide that functions as an oxide semiconductor is preferably used for the

なお、図では酸化物230a、酸化物230b、および酸化物230cを単層で示したが、本発明はこれに限られるものではない。例えば、酸化物230a、酸化物230b、および酸化物230cを2層以上の積層構造として設ける構成にしてもよい。特に、酸化物230cは、酸化物230bと接する第1の層と、絶縁体250と接する第2の層を有することが好ましい。

Note that the

例えば、酸化物230cの第1の層に、酸化物230bと同じ組成の酸化物を用いる。一方、酸化物230cの第2の層には、第1の層よりも、不純物に対してバリア性が高い組成の酸化物を用いることが好ましい。酸化物230の第1の層に、酸化物230bと同じ組成の酸化物を用いることで、生産工程により、酸化物230bの表面に生じた欠損を補償することができる。また、第2の層に不純物に対してバリア性を有する膜を用いることで、酸化物230bに不純物が拡散することを抑制することができる。

For example, an oxide having the same composition as the

さらに、酸化物230cを上記積層構造とすることで、詳細は後述するが、絶縁体280が有する過剰酸素領域の酸素が、酸化物230cの第1の層を介し、酸化物230のチャネルが形成される領域に生じた酸素欠損を低減することができる。一方で、酸化物230cの第2の層により、絶縁体280が有する過剰酸素領域の酸素が、導電体260へ拡散することを抑制することができる。

Further, when the

なお、トランジスタ200では、チャネル形成領域およびその近傍において、酸化物230が、酸化物230a、酸化物230b、および酸化物230cの3層の積層構造を有する構成について示しているが、本発明はこれに限られるものではない。例えば、酸化物230は、酸化物230bの単層、酸化物230aと酸化物230bの2層構造、酸化物230bと酸化物230cの2層構造、または4層以上の積層構造を設ける構成としてもよい。

Note that in the

次に、導電体260は、第1のゲート(トップゲートともいう。)電極として機能する場合がある。また、導電体205は、第2のゲート(ボトムゲートともいう。)電極として機能する場合がある。

また、導電体205に印加する電位は、導電体260に印加する電位と、連動させず、独立して変化させてもよい。具体的には、導電体205に印加する電位により、トランジスタ200の閾値電圧を制御することができる。特に、導電体205に負の電位を印加することにより、トランジスタ200の閾値電圧を0Vより大きくし、オフ電流を低減することが可能となる。したがって、導電体205に負の電位を印加したほうが、印加しない場合よりも、導電体260に印加する電位が0Vのときのドレイン電流を小さくすることができる。

Further, the potential applied to the

また、例えば、図1(A)、および図1(C)に示すように、導電体205と、導電体260とを重畳して設けることで、導電体260、および導電体205に電位を印加した場合、導電体260から生じる電界と、導電体205から生じる電界と、がつながり、酸化物230に形成されるチャネル形成領域を覆うことができる。

Further, for example, as illustrated in FIGS. 1A and 1C, the

つまり、第1のゲート電極としての機能を有する導電体260の電界と、第2のゲート電極としての機能を有する導電体205の電界によって、チャネル形成領域を電気的に取り囲むことができる。本明細書において、第1のゲート電極、および第2のゲート電極の電界によって、チャネル形成領域を電気的に取り囲むトランジスタの構造を、surrounded channel(S-channel)構造とよぶ。

That is, the electric field of the

なお、図1では、導電体205の第1の導電体および導電体205の第2の導電体を積層する構成について示しているが、本発明はこれに限られるものではない。例えば、導電体205を単層、または3層以上の積層構造として設ける構成にしてもよい。構造体が積層構造を有する場合、形成順に序数を付与し、区別する場合がある。

Note that FIG. 1 shows a structure in which the first conductor of the

一例として、図1では、第2のゲートとして機能する導電体205は、絶縁体214および絶縁体216の開口の内壁に接して第1の導電体が形成され、さらに内側に第2の導電体が形成されている。ここで、第1の導電体および第2の導電体の上面の高さと、絶縁体216の上面の高さは同程度にすることが好ましい。

As an example, in FIG. 1, the

また、導電体205の第1の導電体は、水、酸素、または金属元素などの不純物の拡散を抑制する機能を有する導電性材料を用いることが好ましい。または、酸素の少なくとも一の拡散を抑制する機能を有する導電性材料を用いることが好ましい。

For the first conductor of the

導電体205の第1の導電体が酸素の拡散を抑制する機能を持つことにより、導電体205の第2の導電体が酸化して導電率が低下することを抑制することができる。

Since the first conductor of the

また、導電体205が配線の機能を兼ねる場合、導電体205の第2の導電体は、タングステン、銅、またはアルミニウムを主成分とする、導電性が高い導電性材料を用いることが好ましい。なお、導電体205の第2の導電体を単層で図示したが、積層構造としてもよく、例えば、チタン、窒化チタンと上記導電性材料との積層としてもよい。

In the case where the

また、第1のゲート電極として機能する導電体260は、導電体260a、および導電体260a上の導電体260bを有する。導電体260aは、導電体205の第1の導電体と同様に、水素原子、水素分子、水分子、窒素原子、窒素分子、酸化窒素分子(N2O、NO、NO2など)、銅原子などの不純物の拡散を抑制する機能を有する導電性材料を用いることが好ましい。または、酸素(例えば、酸素原子、酸素分子など)の少なくとも一の拡散を抑制する機能を有する導電性材料を用いることが好ましい。

In addition, the

導電体260aが酸素の拡散を抑制する機能を持つことにより、酸化物230、および絶縁体250から導電体260bへの過剰酸素の拡散が抑制される。従って、絶縁体250が有する過剰酸素による導電体260bの酸化が抑制され、導電率が低下することを防止することができる。また、酸化物230へ供給する過剰酸素量の減少を抑制することができる。

Since the

酸素の拡散を抑制する機能を有する導電性材料としては、例えば、タンタル、窒化タンタル、ルテニウムまたは酸化ルテニウムなどを用いることが好ましい。また、導電体260aとして、酸化物230として用いることができる酸化物半導体を用いることができる。その場合、導電体260bをスパッタリング法で成膜することで、導電体260aの電気抵抗値を低下させて導電体とすることができる。これをOC(Oxide Conductor)電極と呼ぶことができる。

As the conductive material having a function of suppressing diffusion of oxygen, tantalum, tantalum nitride, ruthenium, ruthenium oxide, or the like is preferably used, for example. Further, an oxide semiconductor that can be used as the

導電体260bは、タングステン、銅、またはアルミニウムを主成分とする導電性材料を用いることが好ましい。また、導電体260は、配線として機能するため、導電性が高い導電体を用いることが好ましい。例えば、タングステン、銅、またはアルミニウムを主成分とする導電性材料を用いることができる。また、導電体260bは積層構造としてもよく、例えば、チタン、窒化チタンと上記導電性材料との積層としてもよい。

A conductive material containing tungsten, copper, or aluminum as its main component is preferably used for the

続いて、絶縁体250、および絶縁体252は、第1のゲート絶縁体として機能する。また、絶縁体222、および絶縁体224は、第2のゲート絶縁体としての機能を有する。詳細は前述の記載を参照することができる。

次に、導電体240(導電体240a、および導電体240b)は、一方がソース電極として機能し、他方がドレイン電極として機能する場合がある。

Next, one of the conductors 240 (the

導電体240aと、導電体240bとは、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、銀、タンタル、またはタングステンなどの金属、またはこれを主成分とする合金を用いることができる。特に、窒化タンタルなどの金属窒化物膜は、水素または酸素に対するバリア性があり、また、耐酸化性が高いため、好ましい。

The

また、図では単層構造を示したが、2層以上の積層構造としてもよい。例えば、窒化タンタルとタングステン膜を積層するとよい。また、チタン膜とアルミニウム膜を積層してもよい。また、タングステン膜上にアルミニウム膜を積層する二層構造、銅-マグネシウム-アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜上に銅膜を積層する二層構造、タングステン膜上に銅膜を積層する二層構造としてもよい。 In addition, although a single-layer structure is shown in the drawing, a laminated structure of two or more layers may be used. For example, a tantalum nitride film and a tungsten film are preferably stacked. Alternatively, a titanium film and an aluminum film may be stacked. A two-layer structure in which an aluminum film is stacked over a tungsten film, a two-layer structure in which a copper film is stacked over a copper-magnesium-aluminum alloy film, a two-layer structure in which a copper film is stacked over a titanium film, a two-layer structure in which a copper film is stacked over a titanium film, A two-layer structure in which copper films are stacked may be used.

また、チタン膜または窒化チタン膜と、そのチタン膜または窒化チタン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にチタン膜または窒化チタン膜を形成する三層構造、モリブデン膜または窒化モリブデン膜と、そのモリブデン膜または窒化モリブデン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造等がある。なお、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。 In addition, a three-layer structure in which a titanium film or a titanium nitride film is laminated, an aluminum film or a copper film is laminated on the titanium film or the titanium nitride film, and a titanium film or a titanium nitride film is formed thereon, a molybdenum film or a There is a three-layer structure including a molybdenum nitride film, an aluminum film or a copper film laminated on the molybdenum film or the molybdenum nitride film, and a molybdenum film or a molybdenum nitride film formed thereon. Note that a transparent conductive material containing indium oxide, tin oxide, or zinc oxide may be used.

また、導電体240上に、バリア性を有する絶縁体274を設けてもよい。絶縁体274は、酸素、または水素に対してバリア性を有する物質を用いることが好ましい。当該構成により、詳細は後述するが、絶縁体280が有する過剰酸素領域の酸素が、導電体240と反応し、酸化することを防止することができる。

Further, an

絶縁体274には、例えば、窒化シリコンや金属酸化物を用いることができる。特に、酸化アルミニウム、酸化ハフニウム、酸化ガリウムなどの、酸素や水素に対してバリア性のある絶縁膜を用いることが好ましい。また、CVD法で形成した窒化シリコンを用いてもよい。

Silicon nitride or metal oxide can be used for the

絶縁体274を有することで、導電体240の材料選択の幅を広げることができる。例えば、導電体240に、タングステンや、アルミニウムなどの耐酸化性が低い一方で導電性が高い材料を用いることができる。また、例えば、成膜、または加工がしやすい導電体を用いることができる。

By including the

また、導電体240の酸化を抑制し、絶縁体224、および絶縁体280から、脱離した酸素を効率的に酸化物230へと供給することができる。また、導電体240に導電性が高い導電体を用いることで、消費電力が小さいトランジスタ200を提供することができる。

In addition, oxidation of the

続いて、絶縁体212、絶縁体214、絶縁体216、絶縁体280、絶縁体282、絶縁体283、および絶縁体284は、層間膜として機能する。

Subsequently, the

層間膜としては、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化ハフニウム、酸化タンタル、酸化ジルコニウム、チタン酸ジルコン酸鉛(PZT)、チタン酸ストロンチウム(SrTiO3)または(Ba,Sr)TiO3(BST)などの絶縁体を単層または積層で用いることができる。またはこれらの絶縁体に、例えば、酸化アルミニウム、酸化ビスマス、酸化ゲルマニウム、酸化ニオブ、酸化シリコン、酸化チタン、酸化タングステン、酸化イットリウム、酸化ジルコニウムを添加してもよい。またはこれらの絶縁体を窒化処理してもよい。上記の絶縁体に酸化シリコン、酸化窒化シリコンまたは窒化シリコンを積層して用いてもよい。 The interlayer film may be silicon oxide, silicon oxynitride, silicon nitride oxide, aluminum oxide, hafnium oxide, tantalum oxide, zirconium oxide, lead zirconate titanate (PZT), strontium titanate (SrTiO 3 ) or (Ba, Sr). Insulators such as TiO 3 (BST) can be used in single layers or stacks. Alternatively, aluminum oxide, bismuth oxide, germanium oxide, niobium oxide, silicon oxide, titanium oxide, tungsten oxide, yttrium oxide, or zirconium oxide may be added to these insulators. Alternatively, these insulators may be nitrided. Silicon oxide, silicon oxynitride, or silicon nitride may be stacked over the above insulator.

例えば、絶縁体216は、比誘電率が低い、いわゆるLow-k材料を用いることが好ましい。誘電率が低い材料を層間膜とすることで、配線間に生じる寄生容量を低減することができる。

For example, the

また、絶縁体280、および絶縁体284は、絶縁体216と同様に、比誘電率が低い、いわゆるLow-k材料であること好ましい。誘電率が低い材料を層間膜とすることで、配線間に生じる寄生容量を低減することができる。

Further, the

特に、絶縁体280には、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物を用いることが好ましい。絶縁体280は、トランジスタ200の酸化物230cと接するため、酸化物230cを介して、酸化物230においてチャネルが形成される領域に生じた酸素欠損を低減することができる。つまり、トランジスタ200近傍の層間膜に、過剰酸素領域を有する絶縁体を設けることで、トランジスタ200が有する酸化物230の酸素欠損を低減することで、信頼性を向上させることができる。

In particular, for the

絶縁体282は、酸素、水素、および水に対するバリア性を有することが好ましい。絶縁体282が、酸素に対するバリア性を有することで、過剰酸素領域の酸素は、絶縁体284側へ拡散することなく、効率よく酸化物230へ供給することができる。

The

また、絶縁体212、絶縁体214、絶縁体282、および絶縁体283は、水または水素などの不純物、および酸素の拡散を抑制する機能を有する絶縁性材料を用い、トランジスタ200と、過剰酸素領域を有する絶縁体280とを、封止する(取り囲む)構造を有する。

The

例えば、図10(A)、および図10(B)に示す。図10(A)は、本発明の一態様に係る基板10上に設けられたトランジスタ200、およびトランジスタ200周辺の上面図である。また、図10(B)は、図10(A)に示す一点鎖線A1-A2に対応する断面図である。なお、図10では、図の明瞭化のために一部の要素を省いて図示している。

For example, it is shown in FIG. 10(A) and FIG. 10(B). FIG. 10A is a top view of the

図10(A)、および図10(B)に示す半導体装置は、基板10上に設けられたトランジスタ200、およびトランジスタ200を包む構造を有する絶縁体12、絶縁体12のさらに外側に絶縁体14を有する。

The semiconductor device shown in FIGS. 10A and 10B includes a

トランジスタ200が有する酸化物230は、水素、水、または金属酸化物などの不純物により電気特性が変動する蓋然性が高くなるため、外部から不純物の侵入を遮断することが好ましい。そこで、バリア性を有する絶縁体を用いて、絶縁体12、および絶縁体14で示す積層構造により、トランジスタ200を封止することが好ましい。

The electric characteristics of the

絶縁体12、および絶縁体14として、例えば、酸化アルミニウムまたは酸化ハフニウムなどを用いることができる。また、他にも、例えば、酸化マグネシウム、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジムまたは酸化タンタルなどの金属酸化物、窒化酸化シリコンまたは窒化シリコンなどを用いることができる。

As the

なお、絶縁体12、および絶縁体14は、異なる膜種を用いることが好ましい。異なる膜種を積層することで、外部から侵入する不純物に対し、より多くの種類の不純物の拡散を抑制することができる。具体的には、絶縁体12には、酸化アルミニウムを用い、絶縁体14には、窒化シリコンを用いるとよい。

Note that the

また、絶縁体12、および絶縁体14は、同じ膜種を異なる成膜方法を用いて形成してもよい。例えば、絶縁体12をスパッタリング法で成膜し、絶縁体14をALD法により成膜してもよい。本構造とすることで、絶縁体14よりも厚く成膜した絶縁体12を、緻密な膜である絶縁体14で被膜することで、歩留まりよく封止することが可能となる。

Further, the

また、図10(C)、および図10(D)に示すように、複数のトランジスタ200を一括して包囲してもよい。また、トランジスタ200の密度が異なる領域ごとに、包囲してもよい。

Alternatively, as shown in FIGS. 10C and 10D, a plurality of

具体的には、図10(C)、および図10(D)に示す半導体装置は、基板10上にトランジスタ200の密度が高い領域20と、密度が低い領域30を有する。トランジスタ密度が高い領域20において、絶縁体22、および絶縁体24は、複数のトランジスタ200の四方を取り囲む。また、トランジスタ密度が低い領域30においては、絶縁体32、および絶縁体34が、トランジスタ200の四方を取り囲む。ここで、絶縁体22、および絶縁体24が、取り囲むトランジスタ200の個数は、絶縁体32、および絶縁体34が、取り囲むトランジスタ200の個数よりも、多い。

Specifically, the semiconductor device shown in FIGS. 10C and 10D has a

従って、基板10上のトランジスタ密度が異なる領域ごとに、バリア性を有する絶縁体により封止することで、トランジスタ200への不純物の拡散を抑制することができる。また、トランジスタ200へ拡散する過剰酸素量のばらつきを低減することができる。従って、複数のトランジスタ200間において、電気特性のバラツキを低減することができる。

Therefore, by sealing regions having different transistor densities on the

ここで、図10に示す絶縁体12、絶縁体14、絶縁体22、絶縁体24、絶縁体32、および絶縁体34に対応する絶縁体として、絶縁体212、絶縁体214、絶縁体282、および絶縁体283を用いることができる。

Here, as insulators corresponding to the

例えば、絶縁体12、絶縁体22、および絶縁体32として、絶縁体212、絶縁体283を配置することができる。また、絶縁体14、絶縁体24、および絶縁体34として、絶縁体214、絶縁体282を配置することができる。また、絶縁体214と絶縁体216の積層構造は、絶縁体282と絶縁体283の積層構造帯と、基板上で接する領域を有する。

For example, the

従って、絶縁体212、絶縁体214、絶縁体282、および絶縁体283は、水または水素などの不純物が、基板側からトランジスタ200に混入するのを抑制するバリア膜として機能する。具体的には、絶縁体212、絶縁体214、絶縁体282、および絶縁体283は、水素原子、水素分子、水分子、窒素原子、窒素分子、酸化窒素分子(N2O、NO、NO2など)、銅原子などの不純物の拡散を抑制する機能を有する(上記不純物が透過しにくい。)絶縁性材料を用いることが好ましい。または、酸素(例えば、酸素原子、酸素分子など)の少なくとも一の拡散を抑制する機能を有する(上記酸素が透過しにくい。)絶縁性材料を用いることが好ましい。また、例えば、絶縁体212、絶縁体214、絶縁体282、および絶縁体283として酸化アルミニウムや窒化シリコンなどを用いてもよい。当該構成により、水素、水などの不純物が、基板、基板端、または絶縁体284よりも上方からトランジスタ200側に拡散するのを抑制することができる。

Therefore, the

また、トランジスタ200を覆う絶縁体280は、その下方の凹凸形状を被覆する平坦化膜として機能してもよい。本構造とすることで、絶縁体280よりも上方に配置する膜の被膜性が向上する。従って、絶縁体282が、断膜することなく、トランジスタ200と絶縁体280とを封止することができる。

In addition, the

上記構造を有することで、オン電流が大きい酸化物半導体を有するトランジスタを有する半導体装置を提供することができる。または、オフ電流が小さい酸化物半導体を有するトランジスタを有する半導体装置を提供することができる。または、電気特性の変動を抑制し、安定した電気特性を有すると共に、信頼性を向上させた半導体装置を提供することができる。 With the above structure, a semiconductor device including a transistor including an oxide semiconductor with high on-state current can be provided. Alternatively, a semiconductor device including a transistor including an oxide semiconductor with low off-state current can be provided. Alternatively, it is possible to provide a semiconductor device in which variation in electrical characteristics is suppressed, stable electrical characteristics are obtained, and reliability is improved.

<トランジスタの構造2>

図2には、トランジスタ200を有する半導体装置の一例を示す。図2(A)は半導体装置の上面を示す。なお、図の明瞭化のため、図2(A)において一部の膜は省略されている。また、図2(B)は、図2(A)に示す一点鎖線A1-A2に対応する断面図であり、図2(C)はA3-A4に対応する断面図である。

<

FIG. 2 illustrates an example of a semiconductor device including a

なお、図2に示す半導体装置において、図1に示した半導体装置を構成する構造と同機能を有する構造には、同符号を付記する。 In the semiconductor device shown in FIG. 2, structures having the same functions as those constituting the semiconductor device shown in FIG. 1 are denoted by the same reference numerals.

図2に示すトランジスタ200は、導電体260と絶縁体252との間に、絶縁体254を設けた構造である。また、絶縁体250は、必ずしも設ける必要はない。同様に、導電体205と絶縁体224との間に、絶縁体220を設けた構造である。また、絶縁体250、および絶縁体222は、必ずしも設ける必要はない。

The

絶縁体254は、例えば、水素濃度が低く、熱に強い絶縁体であることが好ましい。絶縁体254として、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコンなどを用いることができる。特に、酸化シリコン、および酸化窒化シリコンは熱に対して安定であるため好ましい。具体的に、水素濃度が低く、過剰酸素領域または過剰酸素を有する絶縁体は、SIMSにより得られる水素濃度が、5×1020atoms/cm3未満、好ましくは1×1020atoms/cm3未満、より好ましくは5×1019atoms/cm3未満とする。

The

ゲート絶縁体として機能する絶縁体を、high-k材料と、熱的に安定している材料との積層構造とすることで、物理膜厚を保ちながら、トランジスタ動作時のゲート電位の低減が可能となる。また、熱的に安定かつ比誘電率の高い積層構造とすることができる。 The gate potential during transistor operation can be reduced while maintaining the physical film thickness by making the insulator that functions as a gate insulator into a laminated structure of a high-k material and a thermally stable material. becomes. Moreover, it is possible to obtain a laminated structure that is thermally stable and has a high dielectric constant.

また、酸化物230としてIn-Ga-Zn酸化物を用い、絶縁体252としてガリウム酸化物など、酸化物230よりもガリウムの含有量が多い絶縁材料を用いる場合、酸化物230と絶縁体252とが接する構造とすることで、酸化物230と絶縁体252との界面における欠陥準位密度を低くすることができる。そのため、界面散乱によるキャリア伝導への影響が小さくなり、トランジスタ200は高いオン電流、および高い周波数特性を得ることができる。

In the case where an In--Ga--Zn oxide is used as the

また、絶縁体274上に、絶縁体275を配置してもよい。絶縁体275は、バリア性を有することが好ましい。絶縁体275を設ける場合、絶縁体274は、異なる膜種を用いるとよい。異なる膜種を積層することで、外部から侵入する不純物に対し、より多くの種類の不純物の拡散を抑制することができる。

Alternatively, an

また、絶縁体275は、絶縁体274と、同じ膜種を異なる成膜方法を用いて形成してもよい。例えば、絶縁体274をスパッタリング法で成膜し、絶縁体275をALD法により成膜してもよい。本構造とすることで、絶縁体275よりも厚く成膜した絶縁体274を、緻密な膜である絶縁体275で被膜することで、歩留まりよく封止することが可能となる。

Alternatively, the

上記構造を有することで、オン電流が大きい酸化物半導体を有するトランジスタを有する半導体装置を提供することができる。または、オフ電流が小さい酸化物半導体を有するトランジスタを有する半導体装置を提供することができる。または、電気特性の変動を抑制し、安定した電気特性を有すると共に、信頼性を向上させた半導体装置を提供することができる。 With the above structure, a semiconductor device including a transistor including an oxide semiconductor with high on-state current can be provided. Alternatively, a semiconductor device including a transistor including an oxide semiconductor with low off-state current can be provided. Alternatively, it is possible to provide a semiconductor device in which variation in electrical characteristics is suppressed, stable electrical characteristics are obtained, and reliability is improved.

<トランジスタの構造3>

図3には、トランジスタ200を有する半導体装置の一例を示す。図3(A)は半導体装置の上面を示す。なお、図の明瞭化のため、図3(A)において一部の膜は省略されている。また、図3(B)は、図3(A)に示す一点鎖線A1-A2に対応する断面図であり、図3(C)はA3-A4に対応する断面図である。

<

FIG. 3 illustrates an example of a semiconductor device including a

なお、図3に示す半導体装置において、図1、または図2に示した半導体装置を構成する構造と同機能を有する構造には、同符号を付記する。 In the semiconductor device shown in FIG. 3, structures having the same functions as those constituting the semiconductor device shown in FIG. 1 or 2 are denoted by the same reference numerals.

図3に示すトランジスタ200は、第1のゲート絶縁体と、第2のゲート絶縁体の積層構造が異なる。特に、第1のゲート電極として機能する導電体260と、第2のゲート電極として機能する導電体205に異なる電位が印加される場合、第1のゲート絶縁体の構造、および第2のゲート絶縁体の構造は、各電位に対し適宜選択すればよい。

The

例えば、図3に示すように、第1のゲート絶縁体は、絶縁体250、絶縁体252、および絶縁体254の積層構造を用いることができる。一方、第2のゲート絶縁体は、絶縁体221、絶縁体223、絶縁体225の積層構造を用いることができる。

For example, as shown in FIG. 3, the first gate insulator can use a laminate structure of

例えば、絶縁体221、および絶縁体225は、酸素、水素、または不純物に対してバリア性を有する膜を用いることが好ましい。

For example, the

特に、酸化物230としてIn-Ga-Zn酸化物を用いる場合、絶縁体221、および絶縁体225としてガリウム酸化物など、酸化物230よりもガリウムの含有量が多い絶縁材料を用いることが好ましい。絶縁体221、および絶縁体225を構成する元素と、酸化物230を構成する元素が共通であるため、例えば、絶縁体221、および絶縁体225を構成する元素が、酸化物230へと拡散したとしても、酸化物230の低抵抗化の要因とならない。

In particular, when In—Ga—Zn oxide is used as the

また、酸化ガリウムは、窒化シリコンよりも誘電率が高い高誘電率絶縁材料であり、いわゆるhigh-k材料である。トランジスタの微細化、および高集積化が進むと、ゲート絶縁体の薄膜化により、リーク電流などの問題が生じる場合がある。ゲート絶縁体として機能する絶縁体にhigh-k材料を用いることで、物理膜厚を保持したまま、ゲート絶縁体の等価酸化膜厚(EOT)の薄膜化が可能となる。従って、トランジスタ動作時のゲート電位の低減が可能となる。 Gallium oxide is a high dielectric constant insulating material having a higher dielectric constant than silicon nitride, and is a so-called high-k material. As transistors are miniaturized and highly integrated, thinning of gate insulators may cause problems such as leakage current. By using a high-k material for the insulator that functions as the gate insulator, it is possible to reduce the equivalent oxide thickness (EOT) of the gate insulator while maintaining the physical thickness. Therefore, it is possible to reduce the gate potential during transistor operation.

一方で、酸化ガリウムなどいわゆるhigh-k材料は、結晶化しやすい傾向がある。また、ゲート絶縁体の結晶性が高いと、リーク電流が生じる蓋然性が高くなる。そこで、絶縁体221と絶縁体225との間に、非晶質である絶縁体223を配置することが好ましい。絶縁体223を有することで、絶縁体221と絶縁体225の結晶率が高い場合でも、リーク電流の発生を抑制することができる。

On the other hand, so-called high-k materials such as gallium oxide tend to crystallize easily. Also, the higher the crystallinity of the gate insulator, the higher the probability of leakage current. Therefore, it is preferable to arrange an

上記構造を有することで、オン電流が大きい酸化物半導体を有するトランジスタを有する半導体装置を提供することができる。または、オフ電流が小さい酸化物半導体を有するトランジスタを有する半導体装置を提供することができる。または、電気特性の変動を抑制し、安定した電気特性を有すると共に、信頼性を向上させた半導体装置を提供することができる。 With the above structure, a semiconductor device including a transistor including an oxide semiconductor with high on-state current can be provided. Alternatively, a semiconductor device including a transistor including an oxide semiconductor with low off-state current can be provided. Alternatively, it is possible to provide a semiconductor device in which variation in electrical characteristics is suppressed, stable electrical characteristics are obtained, and reliability is improved.

<半導体装置の構成材料>

以下では、半導体装置に用いることができる構成材料について説明する。

<Semiconductor Device Constituent Materials>

Constituent materials that can be used for the semiconductor device are described below.

<<基板>>

トランジスタ200を形成する基板としては、例えば、絶縁体基板、半導体基板、または導電体基板を用いればよい。絶縁体基板としては、例えば、ガラス基板、石英基板、サファイア基板、安定化ジルコニア基板(イットリア安定化ジルコニア基板など)、樹脂基板などがある。また、半導体基板としては、例えば、シリコン、ゲルマニウムなどの半導体基板、または炭化シリコン、シリコンゲルマニウム、ヒ化ガリウム、リン化インジウム、酸化亜鉛、酸化ガリウムからなる化合物半導体基板などがある。さらには、前述の半導体基板内部に絶縁体領域を有する半導体基板、例えば、SOI(Silicon On Insulator)基板などがある。導電体基板としては、黒鉛基板、金属基板、合金基板、導電性樹脂基板などがある。または、金属の窒化物を有する基板、金属の酸化物を有する基板などがある。さらには、絶縁体基板に導電体または半導体が設けられた基板、半導体基板に導電体または絶縁体が設けられた基板、導電体基板に半導体または絶縁体が設けられた基板などがある。または、これらの基板に素子が設けられたものを用いてもよい。基板に設けられる素子としては、容量素子、抵抗素子、スイッチ素子、発光素子、記憶素子などがある。

<<Substrate>>

As a substrate for forming the

<<絶縁体>>

絶縁体としては、絶縁性を有する酸化物、窒化物、酸化窒化物、窒化酸化物、金属酸化物、金属酸化窒化物、金属窒化酸化物などがある。

<<insulator>>

As insulators, there are insulating oxides, nitrides, oxynitrides, nitride oxides, metal oxides, metal oxynitrides, metal nitride oxides, and the like.

例えば、トランジスタの微細化、および高集積化が進むと、ゲート絶縁体の薄膜化により、リーク電流などの問題が生じる場合がある。ゲート絶縁体として機能する絶縁体に、high-k材料を用いることで物理膜厚を保ちながら、トランジスタ動作時の低電圧化が可能となる。一方、層間膜として機能する絶縁体には、比誘電率が低い材料を用いることで、配線間に生じる寄生容量を低減することができる。したがって、絶縁体の機能に応じて、材料を選択するとよい。 For example, as transistors are miniaturized and highly integrated, thinning of gate insulators may cause problems such as leakage current. By using a high-k material for the insulator that functions as the gate insulator, it is possible to reduce the voltage during transistor operation while maintaining the physical film thickness. On the other hand, by using a material with a low dielectric constant for the insulator functioning as an interlayer film, parasitic capacitance generated between wirings can be reduced. Therefore, the material should be selected according to the function of the insulator.

また、比誘電率の高い絶縁体としては、酸化ガリウム、酸化ハフニウム、酸化ジルコニウム、アルミニウムおよびハフニウムを有する酸化物、アルミニウムおよびハフニウムを有する酸化窒化物、シリコンおよびハフニウムを有する酸化物、シリコンおよびハフニウムを有する酸化窒化物、またはシリコンおよびハフニウムを有する窒化物などがある。 Insulators with a high relative dielectric constant include gallium oxide, hafnium oxide, zirconium oxide, oxides containing aluminum and hafnium, oxynitrides containing aluminum and hafnium, oxides containing silicon and hafnium, and silicon and hafnium. oxynitrides with silicon, or nitrides with silicon and hafnium.

また、比誘電率が低い絶縁体としては、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、空孔を有する酸化シリコン、または樹脂などがある。 Insulators with a low relative dielectric constant include silicon oxide, silicon oxynitride, silicon nitride oxide, silicon nitride, silicon oxide to which fluorine is added, silicon oxide to which carbon is added, silicon oxide to which carbon and nitrogen are added, and an empty silicon oxide. There are silicon oxide with pores, resin, and the like.

また、酸化物半導体を用いたトランジスタは、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体(絶縁体214、絶縁体222、絶縁体82、および絶縁体283など)で囲うことによって、トランジスタの電気特性を安定にすることができる。水素などの不純物および酸素の透過を抑制する機能を有する絶縁体としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウム、またはタンタルを含む絶縁体を、単層で、または積層で用いればよい。具体的には、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体として、酸化アルミニウム、酸化マグネシウム、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タンタルなどの金属酸化物、窒化アルミニウム、窒化アルミニウムチタン、窒化チタン、窒化酸化シリコン、窒化シリコンなどの金属窒化物を用いることができる。

A transistor including an oxide semiconductor is surrounded by an insulator (such as the

また、ゲート絶縁体として機能する絶縁体は、加熱により脱離する酸素を含む領域を有する絶縁体であることが好ましい。例えば、加熱により脱離する酸素を含む領域を有する酸化シリコンまたは酸化窒化シリコンを酸化物230と接する構造とすることで、酸化物230が有する酸素欠損を補償することができる。

An insulator that functions as a gate insulator preferably has a region containing oxygen that is released by heating. For example, by forming a structure in which silicon oxide or silicon oxynitride having a region containing oxygen released by heating is in contact with the

<<導電体>>

導電体としては、アルミニウム、クロム、銅、銀、金、白金、タンタル、ニッケル、チタン、モリブデン、タングステン、ハフニウム、バナジウム、ニオブ、マンガン、マグネシウム、ジルコニウム、ベリリウム、インジウム、ルテニウム、イリジウム、ストロンチウム、ランタンなどから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いることが好ましい。例えば、窒化タンタル、窒化チタン、タングステン、チタンとアルミニウムを含む窒化物、タンタルとアルミニウムを含む窒化物、酸化ルテニウム、窒化ルテニウム、ストロンチウムとルテニウムを含む酸化物、ランタンとニッケルを含む酸化物などを用いることが好ましい。また、窒化タンタル、窒化チタン、チタンとアルミニウムを含む窒化物、タンタルとアルミニウムを含む窒化物、酸化ルテニウム、窒化ルテニウム、ストロンチウムとルテニウムを含む酸化物、ランタンとニッケルを含む酸化物は、酸化しにくい導電性材料、または、酸素を吸収しても導電性を維持する材料であるため、好ましい。また、リン等の不純物元素を含有させた多結晶シリコンに代表される、電気伝導度が高い半導体、ニッケルシリサイドなどのシリサイドを用いてもよい。

<<Conductor>>

Conductors include aluminum, chromium, copper, silver, gold, platinum, tantalum, nickel, titanium, molybdenum, tungsten, hafnium, vanadium, niobium, manganese, magnesium, zirconium, beryllium, indium, ruthenium, iridium, strontium, and lanthanum. It is preferable to use a metal element selected from among the above, an alloy containing the above-described metal elements as a component, or an alloy or the like in which the above-described metal elements are combined. For example, tantalum nitride, titanium nitride, tungsten, nitride containing titanium and aluminum, nitride containing tantalum and aluminum, ruthenium oxide, ruthenium nitride, oxide containing strontium and ruthenium, oxide containing lanthanum and nickel, and the like are used. is preferred. Also, tantalum nitride, titanium nitride, nitrides containing titanium and aluminum, nitrides containing tantalum and aluminum, ruthenium oxide, ruthenium nitride, oxides containing strontium and ruthenium, and oxides containing lanthanum and nickel are difficult to oxidize. It is preferable because it is a conductive material or a material that maintains conductivity even after absorbing oxygen. Alternatively, a semiconductor with high electrical conductivity, typified by polycrystalline silicon containing an impurity element such as phosphorus, or a silicide such as nickel silicide may be used.

また、上記の材料で形成される導電層を複数積層して用いてもよい。例えば、前述した金属元素を含む材料と、酸素を含む導電性材料と、を組み合わせた積層構造としてもよい。また、前述した金属元素を含む材料と、窒素を含む導電性材料と、を組み合わせた積層構造としてもよい。また、前述した金属元素を含む材料と、酸素を含む導電性材料と、窒素を含む導電性材料と、を組み合わせた積層構造としてもよい。 Alternatively, a plurality of conductive layers formed using any of the above materials may be stacked and used. For example, a laminated structure in which the material containing the metal element described above and the conductive material containing oxygen are combined may be used. Alternatively, a laminated structure may be employed in which the material containing the metal element described above and the conductive material containing nitrogen are combined. Alternatively, a laminated structure may be employed in which the material containing the metal element described above, the conductive material containing oxygen, and the conductive material containing nitrogen are combined.

なお、トランジスタのチャネル形成領域に酸化物を用いる場合において、ゲート電極として機能する導電体には、前述した金属元素を含む材料と、酸素を含む導電性材料と、を組み合わせた積層構造を用いることが好ましい。この場合は、酸素を含む導電性材料をチャネル形成領域側に設けるとよい。酸素を含む導電性材料をチャネル形成領域側に設けることで、当該導電性材料から離脱した酸素がチャネル形成領域に供給されやすくなる。 Note that in the case where an oxide is used for a channel formation region of a transistor, a stacked-layer structure in which the above-described material containing the metal element and a conductive material containing oxygen are combined is used for a conductor functioning as a gate electrode. is preferred. In this case, a conductive material containing oxygen is preferably provided on the channel formation region side. By providing the conductive material containing oxygen on the channel formation region side, oxygen released from the conductive material is easily supplied to the channel formation region.

特に、ゲート電極として機能する導電体として、チャネルが形成される金属酸化物に含まれる金属元素および酸素を含む導電性材料を用いることが好ましい。また、前述した金属元素および窒素を含む導電性材料を用いてもよい。例えば、窒化チタン、窒化タンタルなどの窒素を含む導電性材料を用いてもよい。また、インジウム錫酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、シリコンを添加したインジウム錫酸化物を用いてもよい。また、窒素を含むインジウムガリウム亜鉛酸化物を用いてもよい。このような材料を用いることで、チャネルが形成される金属酸化物に含まれる水素を捕獲することができる場合がある。または、外方の絶縁体などから混入する水素を捕獲することができる場合がある。 In particular, a conductive material containing oxygen and a metal element contained in a metal oxide in which a channel is formed is preferably used as a conductor functioning as a gate electrode. Alternatively, a conductive material containing the metal element and nitrogen described above may be used. For example, a conductive material containing nitrogen such as titanium nitride or tantalum nitride may be used. Further, indium tin oxide, indium oxide containing tungsten oxide, indium zinc oxide containing tungsten oxide, indium oxide containing titanium oxide, indium tin oxide containing titanium oxide, indium zinc oxide, and silicon were added. Indium tin oxide may also be used. Alternatively, indium gallium zinc oxide containing nitrogen may be used. By using such a material, hydrogen contained in the metal oxide in which the channel is formed can be captured in some cases. Alternatively, it may be possible to capture hydrogen mixed from an outer insulator or the like.

<半導体装置の作製方法>

次に、図1に示す、本発明の一態様に係るトランジスタ200を有する半導体装置の作製方法を、図4乃至図9を用いて説明する。

<Method for manufacturing a semiconductor device>

Next, a method for manufacturing a semiconductor device including the

図4乃至図9において、各図の(A)は上面図を示す。また、各図の(B)は、(A)に示すA1-A2の一点鎖線で示す部位に対応する断面図であり、トランジスタ200のチャネル長方向の断面図でもある。また、各図の(C)は、(A)にA3-A4の一点鎖線で示す部位に対応する断面図であり、トランジスタ200のチャネル幅方向の断面図でもある。なお、各図の(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。

4 to 9, (A) in each figure shows a top view. (B) of each figure is a cross-sectional view corresponding to the portion indicated by the dashed-dotted line A1-A2 shown in (A), and is also a cross-sectional view of the

まず、基板(図示しない。)を準備し、当該基板上に絶縁体212、および絶縁体214を成膜する。絶縁体212、および絶縁体214の成膜は、スパッタリング法、化学気相成長(CVD:Chemical Vapor Deposition)法、分子線エピタキシー(MBE:Molecular Beam Epitaxy)法、パルスレーザ堆積(PLD:Pulsed Laser Deposition)法、ALD法などを用いて行うことができる。

First, a substrate (not shown) is prepared, and

なお、CVD法は、プラズマを利用するプラズマCVD(PECVD:Plasma Enhanced CVD)法、熱を利用する熱CVD(TCVD:Thermal CVD)法、光を利用する光CVD(Photo CVD)法などに分類できる。さらに用いる原料ガスによって金属CVD(MCVD:Metal CVD)法、有機金属CVD(MOCVD:Metal Organic CVD)法に分けることができる。 The CVD method can be classified into a plasma enhanced CVD (PECVD) method using plasma, a thermal CVD (TCVD) method using heat, a photo CVD (Photo CVD) method using light, and the like. . Further, the method can be classified into a metal CVD (MCVD: Metal CVD) method and an organic metal CVD (MOCVD: Metal Organic CVD) method depending on the raw material gas used.

プラズマCVD法は、比較的低温で高品質の膜が得られる。また、熱CVD法は、プラズマを用いないため、被処理物へのプラズマダメージを小さくすることが可能な成膜方法である。例えば、半導体装置に含まれる配線、電極、素子(トランジスタ、容量素子など)などは、プラズマから電荷を受け取ることでチャージアップする場合がある。このとき、蓄積した電荷によって、半導体装置に含まれる配線、電極、素子などが破壊される場合がある。一方、プラズマを用いない熱CVD法の場合、こういったプラズマダメージが生じないため、半導体装置の歩留まりを高くすることができる。また、熱CVD法では、成膜中のプラズマダメージが生じないため、欠陥の少ない膜が得られる。 The plasma CVD method can obtain high quality films at relatively low temperatures. Moreover, since the thermal CVD method does not use plasma, it is a film formation method capable of reducing plasma damage to the object to be processed. For example, wiring, electrodes, elements (transistors, capacitive elements, etc.) included in a semiconductor device may be charged up by receiving charges from plasma. At this time, the accumulated charges may destroy wiring, electrodes, elements, and the like included in the semiconductor device. On the other hand, a thermal CVD method that does not use plasma does not cause such plasma damage, so that the yield of semiconductor devices can be increased. Moreover, since the thermal CVD method does not cause plasma damage during film formation, a film with few defects can be obtained.

CVD法は、ターゲットなどから放出される粒子が堆積する成膜方法とは異なり、被処理物の表面における反応により膜が形成される成膜方法である。したがって、被処理物の形状の影響を受けにくく、良好な段差被覆性を有する成膜方法である。 The CVD method is a film forming method in which a film is formed by a reaction on the surface of the object to be processed, unlike a film forming method in which particles emitted from a target or the like are deposited. Therefore, it is a film forming method which is not easily affected by the shape of the object to be processed and which has good step coverage.

CVD法は、原料ガスの流量比によって、得られる膜の組成を制御することができる。例えば、CVD法では、原料ガスの流量比によって、任意の組成の膜を成膜することができる。また、例えば、CVD法では、成膜しながら原料ガスの流量比を変化させることによって、組成が連続的に変化した膜を成膜することができる。原料ガスの流量比を変化させながら成膜する場合、複数の成膜室を用いて成膜する場合と比べて、搬送や圧力調整に掛かる時間を要さない分、成膜に掛かる時間を短くすることができる。したがって、半導体装置の生産性を高めることができる場合がある。 In the CVD method, the composition of the obtained film can be controlled by the flow rate ratio of the raw material gases. For example, in the CVD method, a film of any composition can be formed by changing the flow rate ratio of source gases. Further, for example, in the CVD method, by changing the flow rate ratio of the source gases while forming the film, it is possible to form a film whose composition is continuously changed. When forming a film while changing the flow rate ratio of the raw material gases, the time required for film formation is reduced compared to film formation using multiple film formation chambers, as the time required for transportation and pressure adjustment is not required. can do. Therefore, productivity of semiconductor devices can be improved in some cases.

本実施の形態では、絶縁体212として、スパッタリング法、またはCVD法を用いて、窒化シリコンを成膜する。また、絶縁体214は、スパッタリング法、またはCVD法を用いて、酸化アルミニウムを成膜する。また、例えば、絶縁体212として、スパッタリング法によって酸化アルミニウムを成膜し、絶縁体214として、ALD法によって酸化アルミニウムを成膜する構造としてもよい。または、絶縁体212として、ALD法によって酸化アルミニウムを成膜し、絶縁体214として、スパッタリング法によって酸化アルミニウムを成膜する構造としてもよい。

In this embodiment, the

次に、絶縁体214上に絶縁体216を成膜する。絶縁体216の成膜は、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。本実施の形態では、絶縁体216となる絶縁膜として、CVD法によって酸化シリコンを成膜する。

Next, an

次に、絶縁体216に絶縁体214に達する開口を形成する。開口とは、例えば、溝やスリットなども含まれる。また、開口が形成された領域を指して開口部とする場合がある。開口の形成はウェットエッチングを用いてもよいが、ドライエッチングを用いるほうが微細加工には好ましい。また、絶縁体214は、絶縁体216をエッチングして溝を形成する際のエッチングストッパ膜として機能する絶縁体を選択することが好ましい。例えば、溝を形成する絶縁体216に酸化シリコン膜を用いた場合は、絶縁体214は窒化シリコン膜、酸化アルミニウム膜、酸化ハフニウム膜を用いるとよい。

Next, an opening is formed in

ドライエッチング装置としては、平行平板型電極を有する容量結合型プラズマ(CCP:Capacitively Coupled Plasma)エッチング装置を用いることができる。平行平板型電極を有する容量結合型プラズマエッチング装置は、平行平板型電極の一方の電極に高周波電圧を印加する構成でもよい。または平行平板型電極の一方の電極に複数の異なった高周波電圧を印加する構成でもよい。または平行平板型電極それぞれに同じ周波数の高周波電圧を印加する構成でもよい。または平行平板型電極それぞれに周波数の異なる高周波電圧を印加する構成でもよい。または高密度プラズマ源を有するドライエッチング装置を用いることができる。高密度プラズマ源を有するドライエッチング装置は、例えば、誘導結合型プラズマ(ICP:Inductively Coupled Plasma)エッチング装置などを用いることができる。 As a dry etching device, a capacitively coupled plasma (CCP) etching device having parallel plate electrodes can be used. A capacitively coupled plasma etching apparatus having parallel plate electrodes may be configured to apply a high frequency voltage to one electrode of the parallel plate electrodes. Alternatively, a plurality of different high-frequency voltages may be applied to one of the parallel plate electrodes. Alternatively, a high-frequency voltage having the same frequency may be applied to each of the parallel plate electrodes. Alternatively, high-frequency voltages having different frequencies may be applied to parallel plate electrodes. Alternatively, a dry etching apparatus having a high density plasma source can be used. For example, an inductively coupled plasma (ICP) etching apparatus can be used as a dry etching apparatus having a high-density plasma source.

開口の形成後に、導電体205の第1の導電体となる導電膜を成膜する。該導電膜は、酸素の透過を抑制する機能を有する導電体を含むことが望ましい。たとえば、窒化タンタル、窒化タングステン、窒化チタンなどを用いることができる。または、酸素の透過を抑制する機能を有する導電体と、タンタル、タングステン、チタン、モリブデン、アルミニウム、銅、モリブデンタングステン合金との積層膜とすることができる。導電体205の第1の導電体となる導電膜の成膜は、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。

After the opening is formed, a conductive film to be the first conductor of the

本実施の形態では、導電体205の第1の導電体となる導電膜として、スパッタリング法によって窒化タンタル膜、または、窒化タンタルの上に窒化チタンを積層した膜を成膜する。導電体205の第1の導電体として金属窒化物を用いることにより、後述する導電体205の第2の導電体として銅などの拡散しやすい金属を用いても、当該金属が導電体205の第1の導電体から外に拡散するのを防ぐことができる。

In this embodiment mode, as the conductive film to be the first conductor of the

次に、導電体205の第1の導電体となる導電膜上に、導電体205の第2の導電体となる導電膜を成膜する。該導電膜の成膜は、メッキ法、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。本実施の形態では、導電体205の第2の導電体となる導電膜として、タングステンを成膜する。

Next, a conductive film to be the second conductor of the

次に、CMP(Chemical Mechanical Polishing)処理を行うことで、導電体205の第1の導電体となる導電膜、および導電体205の第2の導電体となる導電膜の一部を除去し、絶縁体216を露出する。その結果、開口部のみに、導電体205の第1の導電体となる導電膜、および導電体205の第2の導電体となる導電膜が残存する。これにより、上面が平坦な、導電体205の第1の導電体および導電体205の第2の導電体を含む導電体205を形成することができる(図4参照。)。なお、当該CMP処理により、絶縁体216の一部が除去される場合がある。

Next, CMP (Chemical Mechanical Polishing) treatment is performed to remove part of the conductive film that serves as the first conductor of the

なお、導電体205を形成した後に、導電体205の第2の導電体の一部を除去し、導電体205および絶縁体216上に導電膜を成膜し、CMP処理を行う工程を行ってもよい。当該CMP処理により、当該導電膜の一部を除去し、絶縁体216を露出する。なお、導電体205の第2の導電体の一部は、ドライエッチング法などを用いて除去するとよい。また、当該導電膜には、導電体205の第1の導電体または導電体205の第2の導電体と同様の材料を用いるとよい。

Note that after the

上記工程により、上面が平坦な、上記導電膜を含む導電体205を形成することができる。絶縁体216と導電体205の上面の平坦性を向上させることにより、酸化物230b、酸化物230cを形成するCAAC-OSの結晶性を向上させることができる。

Through the above steps, the

ここからは、上記と異なる導電体205の形成方法について以下に説明する。

From here, a method of forming the

絶縁体214上に、導電体205となる導電膜を成膜する。該導電膜の成膜は、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。また、該導電膜は、多層膜とすることができる。本実施の形態では、該導電膜としてタングステンを成膜する。

A conductive film to be the

次に、リソグラフィー法を用いて、上記導電膜を加工し、導電体205を形成する。

Next, the conductive film is processed by lithography to form a

なお、リソグラフィー法では、まず、マスクを介してレジストを露光する。次に、露光された領域を、現像液を用いて除去または残存させてレジストマスクを形成する。次に、当該レジストマスクを介してエッチング処理することで導電体、半導体、絶縁体などを所望の形状に加工することができる。例えば、KrFエキシマレーザ光、ArFエキシマレーザ光、EUV(Extreme Ultraviolet)光などを用いて、レジストを露光することでレジストマスクを形成すればよい。また、基板と投影レンズとの間に液体(例えば水)を満たして露光する、液浸技術を用いてもよい。また、前述した光に代えて、電子ビームやイオンビームを用いてもよい。なお、電子ビームやイオンビームを用いる場合には、マスクは不要となる。なお、レジストマスクは、アッシングなどのドライエッチング処理を行う、ウェットエッチング処理を行う、ドライエッチング処理後にウェットエッチング処理を行う、またはウェットエッチング処理後にドライエッチング処理を行うことで、除去することができる。 In the lithography method, first, the resist is exposed through a mask. The exposed regions are then removed or left behind using a developer to form a resist mask. Next, a conductor, a semiconductor, an insulator, or the like can be processed into a desired shape by etching treatment through the resist mask. For example, a resist mask may be formed by exposing a resist using KrF excimer laser light, ArF excimer laser light, EUV (Extreme Ultraviolet) light, or the like. Alternatively, a liquid immersion technique may be used in which a liquid (for example, water) is filled between the substrate and the projection lens for exposure. Also, an electron beam or an ion beam may be used instead of the light described above. A mask is not necessary when using an electron beam or an ion beam. Note that the resist mask can be removed by dry etching treatment such as ashing, wet etching treatment, dry etching treatment followed by wet etching treatment, or wet etching treatment followed by dry etching treatment.

また、レジストマスクの代わりに絶縁体や導電体からなるハードマスクを用いてもよい。ハードマスクを用いる場合、導電体205となる導電膜上にハードマスク材料となる絶縁膜や導電膜を形成し、その上にレジストマスクを形成し、ハードマスク材料をエッチングすることで所望の形状のハードマスクを形成することができる。導電体205となる導電膜のエッチングは、レジストマスクを除去してから行っても良いし、レジストマスクを残したまま行っても良い。後者の場合、エッチング中にレジストマスクが消失することがある。導電体205となる導電膜のエッチング後にハードマスクをエッチングにより除去しても良い。一方、ハードマスクの材料が後工程に影響が無い、あるいは後工程で利用できる場合、必ずしもハードマスクを除去する必要は無い。

A hard mask made of an insulator or a conductor may be used instead of the resist mask. In the case of using a hard mask, an insulating film or a conductive film serving as a hard mask material is formed over the conductive film serving as the

次に、絶縁体214、および導電体205上に絶縁体216となる絶縁膜を成膜する。当該絶縁膜は、導電体205の上面、および側面と接するように形成する。当該絶縁膜の成膜は、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。

Next, an insulating film to be the

ここで、絶縁体216となる絶縁膜の膜厚は、導電体205の膜厚以上とすることが好ましい。例えば、導電体205の膜厚を1とすると、絶縁体216となる絶縁膜の膜厚は、1以上3以下とする。

Here, the thickness of the insulating film to be the

次に、絶縁体216となる絶縁膜にCMP処理を行うことで、絶縁体216となる絶縁膜の一部を除去し、導電体205の表面を露出させる。これにより、上面が平坦な、導電体205と、導電体205の側面と接する絶縁体216と、を形成することができる。以上が、導電体205の異なる形成方法である。

Next, the insulating film to be the

次に、絶縁体216、および導電体205上に絶縁体222を成膜する。絶縁体222は、水素および水に対してバリア性を有する。絶縁体222が、水素および水に対してバリア性を有することで、トランジスタ200の周辺に設けられた構造体に含まれる水素および水が、絶縁体222を通じてトランジスタ200の内側へ拡散することが抑制され、酸化物230中の酸素欠損の生成を抑制することができる。

Next, an

また、絶縁体222として、酸化物230に含まれる元素と共通の金属元素を有する酸化物を含む絶縁体を成膜するとよい。

Further, as the

特に、酸化物230としてIn-Ga-Zn酸化物を用いる場合、絶縁体222としてガリウム酸化物など、酸化物230よりもガリウムの含有量が多い絶縁材料を用いることが好ましい。絶縁体222を構成する元素と、酸化物230を構成する元素が共通であるため、例えば、絶縁体222を構成する元素が、酸化物230へと拡散したとしても、酸化物230の低抵抗化の要因とならない。

In particular, when an In—Ga—Zn oxide is used as the

絶縁体222の成膜は、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。

The

なお、絶縁体222は、後述するALD法によって成膜することが好ましい。

Note that the

例えば、絶縁体222として、ALD法によって、酸化ガリウム膜を成膜する場合、ガリウムのプリカーサとして、トリメチルガリウム、トリエチルガリウム、三塩化ガリウム、トリス(ジメチルアミド)ガリウム、ガリウム(III)アセチルアセトナート、トリス(2、2、6、6-テトラメチル-3、5-ヘプタンジオン酸)ガリウム、ジメチルクロロガリウム、ジエチルクロロガリウムなどを用いることができる。

For example, when a gallium oxide film is formed as the

なお、上記プリカーサには、金属元素の他に、炭素および塩素の一方または両方を含むものがある。炭素を含むプリカーサを用いて形成された酸化膜には炭素が含まれる場合がある。また、塩素を含むプリカーサを用いて形成された酸化膜には塩素が含まれる場合がある。 In addition to the metal element, some precursors contain one or both of carbon and chlorine. An oxide film formed using a carbon-containing precursor may contain carbon. Also, an oxide film formed using a chlorine-containing precursor may contain chlorine.

続いて、加熱処理を行ってもよい。加熱処理は、250℃以上650℃以下、好ましくは300℃以上500℃以下、さらに好ましくは320℃以上450℃以下で行えばよい。なお、加熱処理は、窒素ガスもしくは不活性ガスの雰囲気、または酸化性ガスを10ppm以上、1%以上、もしくは10%以上含む雰囲気で行う。また、加熱処理は減圧状態で行ってもよい。または、加熱処理は、窒素ガスもしくは不活性ガスの雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10ppm以上、1%以上、または10%以上含む雰囲気で加熱処理を行ってもよい。 Subsequently, heat treatment may be performed. The heat treatment may be performed at 250° C. or higher and 650° C. or lower, preferably 300° C. or higher and 500° C. or lower, more preferably 320° C. or higher and 450° C. or lower. Note that the heat treatment is performed in a nitrogen gas atmosphere, an inert gas atmosphere, or an atmosphere containing 10 ppm or more, 1% or more, or 10% or more of an oxidizing gas. Moreover, you may perform heat processing in a pressure-reduced state. Alternatively, heat treatment is performed in an atmosphere of nitrogen gas or an inert gas, and then heat treatment is performed in an atmosphere containing 10 ppm or more, 1% or more, or 10% or more of an oxidizing gas in order to compensate for desorbed oxygen. may

本実施の形態では、加熱処理として、絶縁体222の成膜後に窒素雰囲気にて400℃の温度で1時間の処理を行った後に、連続して酸素雰囲気にて400℃の温度で1時間の処理を行う。当該加熱処理によって、絶縁体222に含まれる水、水素などの不純物を除去することなどができる。また、加熱処理は、絶縁体224の成膜後などのタイミングで行うこともできる。

In this embodiment, heat treatment is performed in a nitrogen atmosphere at 400° C. for 1 hour after the

次に、絶縁体222上に絶縁体224を成膜する。絶縁体224の成膜は、スパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。本実施の形態では、絶縁体224として、CVD法によって酸化シリコンを成膜する。

Next, an

ここで、絶縁体224に過剰酸素領域を形成するために、減圧状態で酸素を含むプラズマ処理を行ってもよい。酸素を含むプラズマ処理は、例えばマイクロ波を用いた高密度プラズマを発生させる電源を有する装置を用いることが好ましい。または、基板側にRF(Radio Frequency)を印加する電源を有してもよい。高密度プラズマを用いることより、高密度の酸素ラジカルを生成することができ、基板側にRFを印加することで、高密度プラズマによって生成された酸素ラジカルを効率よく絶縁体224内に導くことができる。または、この装置を用いて不活性ガスを含むプラズマ処理を行った後に、脱離した酸素を補うために酸素を含むプラズマ処理を行ってもよい。なお、当該プラズマ処理の条件を適宜選択することにより、絶縁体224に含まれる水、水素などの不純物を除去することができる。その場合、加熱処理は行わなくてもよい。

Here, in order to form an excess oxygen region in the

ここで、絶縁体224上に、例えば、スパッタリング法によって、酸化アルミニウムを成膜し、該酸化アルミニウムを絶縁体224に達するまで、CMP処理を行ってもよい。当該CMP処理を行うことで絶縁体224表面の平坦化および平滑化を行うことができる。当該酸化アルミニウムを絶縁体224上に配置してCMP処理を行うことで、CMP処理の終点検出が容易となる。また、CMP処理によって、絶縁体224の一部が研磨されて、絶縁体224の膜厚が薄くなることがあるが、絶縁体224の成膜時に膜厚を調整すればよい。絶縁体224表面の平坦化および平滑化を行うことで、後に成膜する酸化物の被覆率の悪化を防止し、半導体装置の歩留りの低下を防ぐことができる場合がある。また、絶縁体224上に、スパッタリング法によって、酸化アルミニウムを成膜することにより、絶縁体224に酸素を添加することができるので好ましい。

Here, an aluminum oxide film may be formed over the

次に、絶縁体224上に、酸化膜230A、酸化膜230Bを順に成膜する(図4参照。)。なお、酸化膜230Aおよび酸化膜230Bは、大気環境にさらさずに連続して成膜することが好ましい。大気開放せずに成膜することで、酸化膜230A、および酸化膜230B上に大気環境からの不純物または水分が付着することを防ぐことができ、酸化膜230Aと酸化膜230Bとの界面近傍を清浄に保つことができる。

Next, an

酸化膜230A、および酸化膜230Bの成膜はスパッタリング法、CVD法、MBE法、PLD法、ALD法などを用いて行うことができる。なお、酸化膜230A、および酸化膜230BをALD法によって成膜する場合、先の実施の形態で説明した内容を参酌することができる。

The

例えば、酸化膜230A、および酸化膜230Bとして、ALD法によって、In-Ga-Zn酸化膜を成膜する場合、インジウムのプリカーサとして、トリメチルインジウム、トリス(2、2、6、6-テトラメチル-3、5-ヘプタンジオン酸)インジウム、シクロペンタジエニルインジウムなどを用いる。また、ガリウムのプリカーサとして、トリメチルガリウム、トリエチルガリウム、三塩化ガリウム、トリス(ジメチルアミド)ガリウム、ガリウム(III)アセチルアセトナート、トリス(2、2、6、6-テトラメチル-3、5-ヘプタンジオン酸)ガリウム、ジメチルクロロガリウム、ジエチルクロロガリウムなどを用いる。また、亜鉛のプリカーサとして、ジメチル亜鉛、ジエチル亜鉛、ビス(2、2、6、6-テトラメチル-3、5-ヘプタンジオン酸)亜鉛などを用いる。酸化物230aおよび酸化物230bに求める特性に合わせて、In-Ga-Zn酸化膜の成膜に用いるプリカーサの種類、導入量などを適宜組み合わせるとよい。

For example, when In—Ga—Zn oxide films are formed by ALD as the

なお、上記プリカーサには、金属元素の他に、炭素および塩素の一方または両方を含むものがある。炭素を含むプリカーサを用いて形成された酸化膜には炭素が含まれる場合がある。また、塩素を含むプリカーサを用いて形成された酸化膜には塩素が含まれる場合がある。 In addition to the metal element, some precursors contain one or both of carbon and chlorine. An oxide film formed using a carbon-containing precursor may contain carbon. Also, an oxide film formed using a chlorine-containing precursor may contain chlorine.

また、例えば、酸化膜230A、および酸化膜230Bをスパッタリング法によって成膜する場合は、スパッタリングガスとして酸素、または、酸素と希ガスの混合ガスを用いる。スパッタリングガスに含まれる酸素の割合を高めることで、成膜される酸化膜中の過剰酸素を増やすことができる。また、上記の酸化膜をスパッタリング法によって成膜する場合は、上記のIn-M-Zn酸化物ターゲットなどを用いることができる。また、ターゲットには、直流(DC)電源または、高周波(RF)電源などの交流(AC)電源が接続され、ターゲットの電気伝導度に応じて、必要な電力を印加することができる。

Further, for example, when the

特に、酸化膜230Aの成膜時に、スパッタリングガスに含まれる酸素の一部が絶縁体224に供給される場合がある。したがって、当該スパッタリングガスに含まれる酸素の割合は70%以上、好ましくは80%以上、より好ましくは100%とすればよい。

In particular, part of oxygen contained in the sputtering gas may be supplied to the

また、酸化膜230Bをスパッタリング法で形成する場合、スパッタリングガスに含まれる酸素の割合を、30%を超えて100%以下、好ましくは70%以上100%以下として成膜すると、酸素過剰型の酸化物半導体が形成される。酸素過剰型の酸化物半導体をチャネル形成領域に用いたトランジスタは、比較的高い信頼性が得られる。ただし、本発明の一態様はこれに限定されない。酸化膜230Bをスパッタリング法で形成する場合、スパッタリングガスに含まれる酸素の割合を1%以上30%以下、好ましくは5%以上20%以下として成膜すると、酸素欠乏型の酸化物半導体が形成される。酸素欠乏型の酸化物半導体をチャネル形成領域に用いたトランジスタは、比較的高い電界効果移動度が得られる。また、基板を加熱しながら成膜を行うことによって、当該酸化膜の結晶性を向上させることができる。

Further, when the

本実施の形態では、酸化膜230Aとして、スパッタリング法によって、In:Ga:Zn=1:3:4[原子数比]のIn-Ga-Zn酸化物ターゲットを用いて成膜する。また、酸化膜230Bとして、スパッタリング法によって、In:Ga:Zn=4:2:4.1[原子数比]のIn-Ga-Zn酸化物ターゲットを用いて成膜する。なお、各酸化膜は、成膜条件、および原子数比を適宜選択することで、酸化物230に求める特性に合わせて形成するとよい。

In this embodiment, the

ここで、絶縁体222、絶縁体224、酸化膜230A、および酸化膜230Bを、大気に暴露することなく成膜することが好ましい。例えば、マルチチャンバー方式の成膜装置を用いればよい。

Here, the

次に、加熱処理を行ってもよい。当該加熱処理は、上述した加熱処理条件を用いることができる。当該加熱処理によって、酸化膜230A、および酸化膜230B中の水、水素などの不純物を除去することなどができる。本実施の形態では、窒素雰囲気にて400℃の温度で1時間の処理を行った後に、連続して酸素雰囲気にて400℃の温度で1時間の処理を行う。