以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

1.D/A変換回路の構成

図1に本実施形態のD/A変換回路80の構成例を示す。D/A変換回路80は、電圧生成回路30、電圧選択回路40、演算増幅器OPA、OPB(第1、第2の演算増幅器)を含む。なおD/A変換回路80は図1の構成には限定されず、その一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

電圧生成回路30は、複数の電圧V1〜Vj(jは2以上の整数)を生成する。電圧生成回路30は、電源間(VDDA、VSS間)に直列に接続された複数の抵抗を有し、これらの複数の抵抗により電圧分割された電圧をV1〜Vjとして出力する。これらの電圧V1〜Vjは電源間の電圧を例えば等分割した電圧である。但し、電圧V1〜Vjは、液晶パネル等の表示パネルでの画像表示のための階調電圧であってもよく、この場合には、電圧V1〜Vjは表示パネルの階調特性に応じた電圧になる。

電圧選択回路40は、入力データDIに基づいて、電圧V1〜Vjから電圧選択を行い、選択電圧として電圧VK(第Kの電圧)と電圧VL(第Lの電圧。K及びLは互いに異なる1以上の整数)を出力する。具体的には電圧選択回路40は、電圧生成回路30からの電圧V1〜Vjと入力データDIに基づいて、電圧V1〜Vjの中から入力データDIに対応する電圧を、電圧VK、VLとして出力する。例えば電圧選択回路40は、入力データDIをデコードするデコーダーを有しており、電圧選択回路40は、デコーダーからの制御信号に基づいて、電圧V1〜Vjの中から入力データDIに対応する電圧を、電圧VK、VLとして選択して出力する。電圧VK、VLは、例えば電圧V1〜Vjのうちの隣合う電圧(分割電圧)である。例えばVKが電圧V1〜Vjの隣合う電圧の一方の電圧である場合には、VLは他方の電圧である。例えばVKが隣合うV1、V2の一方の電圧である場合に、VLは他方の電圧であり、例えばVK=V1、VL=V2である。VKが隣合うV3、V4の一方の電圧である場合に、VLは他方の電圧であり、例えばVK=V3、VL=V4である。他の電圧V5〜Vjについても同様である。

演算増幅器OPA(第1の演算増幅器)は、電圧選択回路40から電圧VKが入力され、電圧VXを出力する。演算増幅器OPAは例えばボルテージフォロワー接続となっており、電圧VKに対応する電圧をVXとして出力する。演算増幅器OPB(第2の演算増幅器)は、電圧選択回路40から電圧VLが入力され、電圧VYを出力する。演算増幅器OPBは例えばボルテージフォロワー接続となっており、電圧VLに対応する電圧をVYとして出力する。

そして本実施形態では演算増幅器OPA、OPBがチョッパー型の演算増幅器になっている。チョッパー型の演算増幅器(チョッパー・スタビライズド・アンプ)は、チョッピング周波数fpでチョッピング動作を行う演算増幅器である。チョッパー型の演算増幅器では、DCの入力信号がチョッピングの変調によりACの入力信号に変換されて演算増幅器に入力される。そして演算増幅器のACの出力信号がフィルター回路により平滑化されてDCの信号に戻される。

具体的には、第1、第2の入力信号が、変調用のチョッパー回路により変調されて、演算増幅器の増幅段(入力差動段)に入力される。図1の演算増幅器OPAでは、第1の入力信号は電圧VKの信号であり、第2の入力信号はOPAの出力端子からのフィードバック信号である。演算増幅器OPBでは、第1の入力信号は電圧VLの信号であり、第2の入力信号はOPBの出力端子からのフィードバック信号である。そして増幅段の第1、第2の出力信号が、復調用のチョッパー回路により復調されて、出力段(出力差動段)に入力されて、出力段から例えばシングルエンドの信号(VX、VYの信号)が出力される。このように演算増幅器OPA、OPBとしてチョッパー型の演算増幅器を用いることで、オフセット電圧をキャンセルできる。これにより後述の図6で説明するようにD/A変換の非直線性誤差を低減できる。またフリッカーノイズ等の低周波数帯域ノイズを低減できる。

例えば図1において、演算増幅器OPAのオフセット電圧が正極性及び負極性の一方の極性であり、演算増幅器OPBのオフセット電圧が他方の極性である場合に、D/A変換の非直線性誤差が大きくなってしまう。この点、図1では演算増幅器OPA、OPBの両方をチョッパー型の演算増幅器にしている。従って、演算増幅器のオフセット電圧を原因とするD/A変換の非直線性誤差の悪化を抑制できる。

図2に本実施形態のD/A変換回路80の詳細な構成例を示す。図2のD/A変換回路80は、D/A変換器DACA、DACB(第1、第2のD/A変換器)を含む。DACAは、図1で説明したように電圧生成回路30と電圧選択回路40により構成される。DACBは、電圧生成回路46と電圧選択回路48により構成される。

例えばDACAの電圧選択回路40は、入力データDIの上位側ビットに基づいて電圧選択を行う。具体的には電圧選択回路40は、電圧生成回路30からの電圧V1〜Vjと入力データDIの上位qビット(qは1以上の整数)に基づいて、電圧V1〜Vjの中から上位qビットに対応する電圧を、VK、VLとして出力する。

DACBの電圧生成回路46(第2の電圧生成回路)は、演算増幅器OPA、OPBの出力電圧VX、VY(第1、第2の出力電圧)の間を電圧分割した複数の電圧V1〜Vlを生成する。例えば電圧生成回路46は、演算増幅器OPAの出力電圧VXのノードと演算増幅器OPBの出力電圧VYのノードの間に直列に接続された複数の抵抗を有し、これらの複数の抵抗により電圧分割された電圧を、電圧V1〜Vlとして出力する。これらの電圧V1〜VlはVX、VYの間の電圧を例えば等分割した電圧である。

そしてDACBの電圧選択回路48(第2の電圧選択回路)は、入力データDIの下位側ビットに基づいて電圧選択を行う。具体的には電圧選択回路48は、電圧生成回路46からの電圧V1〜Vlと入力データDIの下位pビット(pは1以上の整数)に基づいて、電圧V1〜Vlの中から下位pビットに対応する電圧を、VMとして出力する。

演算増幅器OPC(第3の演算増幅器)は、DACBの電圧選択回路48からの電圧VMが入力され、電圧VDAを出力する。この電圧VDAの信号はフィルター回路120に入力され、フィルター回路120により平滑化された電圧VQの信号が、フィルター回路120から出力される。フィルター回路120としてはローパスフィルターを用いることができる。

例えば演算増幅器OPCはボルテージフォロワーの接続となっており、電圧VMに対応する電圧をVDAとして出力する。この演算増幅器OPCとしては、例えばチョッパー型の演算増幅器を用いることができる。例えばチョッピング周波数fpでチョッピング動作を行うチョッパー型の演算増幅器を用いることができる。但し演算増幅器OPCとして、チョッパー型ではない通常型の演算増幅器を用いてもよい。

なお図1の電圧VX、VYからD/A変換結果の電圧VDAを生成する回路は、図2のような電圧生成回路46、電圧選択回路48等により構成される回路(D/A変換器)には限定されない。例えば抵抗分割ではなく、キャパシターを用いた電荷再分配方式等の種々のD/A変換方式で電圧VDAを生成してもよい。

図3にDACA、DACBの詳細な構成例を示す。図3に示すように、D/A変換回路80は、上位側のD/A変換器DACAと、下位側のD/A変換器DACBと、ボルテージフォロワー接続された演算増幅器OPA、OPB、OPC(オペアンプ)を含む。

上位側のDACAは、VDDAのノードとVSSのノードとの間に直列接続された複数の抵抗RA1〜RANを含む。また上位側のDACAは、これらの抵抗RA1〜RANによる電圧分割ノードに一端が接続される複数のスイッチ素子SA1〜SAN+1と、入力データDIの上位qビットのデータに基づいて、スイッチ素子SA1〜SAN+1をオン又オフにするスイッチ制御信号を生成するデコーダー104(スイッチ制御回路)を含む。

上位側のDACAは、複数の抵抗RA1〜RANのうち上位qビットのデータにより特定される抵抗の両端の分割電圧のうち、一方の分割電圧を演算増幅器OPAの非反転入力端子に出力し、他方の分割電圧を演算増幅器OPBの非反転入力端子に出力する。これにより、当該一方の電圧が、ボルテージフォロワー接続された演算増幅器OPAによりインピーダンス変換されて、電圧VXとして下位側のDACBに供給される。また当該他方の電圧が、ボルテージフォロワー接続された演算増幅器OPBによりインピーダンス変換されて、電圧VYとして下位側のDACBに供給される。

例えば上位qビットのデータにより抵抗RA1が特定された場合には、抵抗RA1の両端の分割電圧のうち、高電位側の分割電圧Vjが、オンになったスイッチ素子SA1を介して、電圧VKとして演算増幅器OPAに供給される。また低電位側の分割電圧Vj−1が、オンになったスイッチ素子SA2を介して、電圧VLとして演算増幅器OPBに供給される。上位qビットのデータにより抵抗RA2が特定された場合には、抵抗RA2の両端の分割電圧のうち、低電位側の分割電圧Vj−2が、オンになったスイッチ素子SA3を介して、電圧VKとして演算増幅器OPAに供給される。また高電位側の分割電圧Vj−1が、オンになったスイッチ素子SA2を介して、電圧VLとして演算増幅器OPBに供給される。そして演算増幅器OPA、OPBは、上位側のDACAから供給された電圧VK、VLをインピーダンス変換した電圧VX、VYを、下位側のDACBに供給する。

下位側のDACBは、電圧VXのノードと電圧VYのノードとの間に直列接続された複数の抵抗RB1〜RBMを含む。また下位側のDACBは、これらの抵抗RB1〜RBMによる電圧分割ノードに一端が接続される複数のスイッチ素子SB1〜SBM+1と、入力データDIの下位pビットのデータに基づいて、スイッチ素子SB1〜SBM+1をオン又オフにするスイッチ制御信号を生成するデコーダー106(スイッチ制御回路)を含む。

そして下位側のDACBは、抵抗RB1〜RBMによる複数の分割電圧のうち、下位pビットのデータにより選択された1つの分割電圧を、選択された電圧VMとして、オンになったスイッチ素子を介して、ボルテージフォロワー接続された演算増幅器OPCの非反転入力端子に出力する。そして演算増幅器OPCは、電圧VMをインピーダンス変換した電圧をVDAとして出力する。

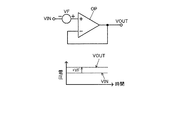

次に、チョッパー型の演算増幅器の詳細について説明する。図4は通常型の演算増幅器OPをボルテージフォロワー接続した例である。このような接続構成では、演算増幅器OPの差動対のトランジスターの僅かな特性差(しきい値電圧のミスマッチ)に起因してオフセット電圧VFが発生する。即ち、演算増幅器OPをボルテージフォロワー接続することで、理想的には仮想接地により出力電圧VOUTは入力電圧VINに等しくなるが、オフセット電圧VFが存在すると、VOUT=VIN+VFになってしまう。このようにVOUT=VIN+VFになると、後述の図6で説明するように、D/A変換の非直線性誤差が大きくなってしまい、例えばデジタル制御温度補償型水晶発振器(DTCXO)等の発振器に適用した場合に、周波数ホッピング等の問題が発生してしまう。

図5はチョッパー型の演算増幅器OPHの構成例である。演算増幅器OPHはボルテージフォロワー接続されている。具体的には演算増幅器OPHの非反転入力端子側のノードN1には入力電圧VINの信号が入力され、反転入力端子側のノードN2には、出力電圧VOUTの信号がフィードバックされて入力される。ノードN1、N2とノードN3、N4の間には、変調用のチョッパー回路ASW1(変調回路、スイッチ回路)が設けられる。変調用のチョッパー回路ASW1は、アナログのスイッチ素子により構成され、ノードN1がノードN3に接続されノードN2がノードN4に接続される第1の状態と、ノードN1がノードN4に接続されノードN2がノードN3に接続される第2の状態とを、チョッピング周波数fpの周期で切り替える。この切り替えはチョッピング周波数fpの変調制御信号に基づき行われる。ノードN3、N4は、演算増幅器OPHの増幅段DFC(増幅回路、入力差動段)の非反転入力端子、反転入力端子に接続される。増幅段DFCでは、図4と同様にオフセット電圧VFが発生する。

演算増幅器OPHの増幅段DFCと出力段QSC(出力回路)の間には、復調用のチョッパー回路ASW2(復調回路、スイッチ回路)が設けられる。具体的には増幅段DFCの非反転出力端子のノードN5、反転出力端子のノードN6と、出力段QSCの非反転入力端子のノードN7、反転入力端子のノードN8の間に、復調用のチョッパー回路ASW2が設けられる。復調用のチョッパー回路ASW2は、アナログのスイッチ素子により構成され、ノードN5がノードN7に接続されノードN6がノードN8に接続される第1の状態と、ノードN5がノードN8に接続されノードN6がノードN7に接続される第2の状態とを、チョッピング周波数fpの周期で切り替える。この切り替えはチョッピング周波数fpの復調制御信号に基づき行われる。そして出力段QSCの出力電圧VOUTの信号が、変調用のチョッパー回路ASW1の反転入力端子側のノードN2にフィードバックされる。また出力段QSCの出力電圧VOUTの信号はローパスフィルターLPFに入力され、ローパスフィルターLPFにより平滑化された電圧LPFOUTの信号が出力される。図5に示すように、ローパスフィルターLPFの平滑化により、LPFOUT=VINとなり、オフセット電圧VFが除去(低減)された電圧LPFOUTが出力されるようになる。このようにオフセット電圧VFを除去するオフセットキャンセルが行われることで、D/A変換の非直線性誤差を低減できるようになる。

図6に、入力データ(入力コード)とD/A変換結果の電圧との関係を示すD/A変換特性の一例を示す。図6のA1は、図1〜図3の演算増幅器OPA、OPBのオフセット電圧がVF=0Vである場合の理想的なD/A変換特性である。A2は、演算増幅器OPA、OPBのオフセット電圧VFが共に電圧VOF(例えばVOF=+5.5mV)である場合のD/A変換特性である。一方、A3は、例えば演算増幅器OPAのオフセット電圧がVF=0Vであり、演算増幅器OPBのオフセット電圧がVF=VOF(例えばVOF=+5.5mV)である場合のD/A変換特性である。A1、A2に示すように演算増幅器OPA、OPBのオフセット電圧VFが同一電圧である場合には、D/A変換特性の非直線性誤差は少ないが、A3に示すように演算増幅器OPA、OPBのオフセット電圧VFが異なる電圧になってしまうと、非直線性誤差が悪化する。例えば非直線性誤差が1LSB以上になるのは望ましくない。そして図1〜図3の演算増幅器OPA、OPBとして、図4のような通常型の演算増幅器OPを用いてしまうと、図6のA3に示すように非直線性誤差が非常に悪化する事態が生じるおそれがある。

この点、本実施形態では、図1〜図3の演算増幅器OPA、OPBとして、図5に示すようなチョッパー型の演算増幅器OPHを用いている。従って、演算増幅器OPA、OPBのオフセット電圧VFを実質的に0Vに近づけることが可能になり、図6のA3に示すような大きな非直線性誤差が発生するのを防止できるようになる。

図7はチョッパーの変調、復調を説明するための周波数特性図である。図7のE1は、D/A変換回路80の入力信号(所望信号)であり、その周波数成分はベースバンド帯域(低周波数帯域)に存在する。この入力信号(VIN)は、チョッパー回路ASW1による変調により、E2に示すように高周波数帯域に周波数変換(変調)される。即ちチョッピング周波数fpの高調波に対応する周波数に周波数変換される。一方、E3はフリッカーノイズ等の低周波数帯域に存在するノイズ(不要信号)である。なお熱ノイズは低周波数帯域から高周波数帯域に均等に存在する。

そしてE2に示すように高周波数帯域に周波数変換された入力信号の周波数成分は、チョッパー回路ASW2による復調により、E4に示すようにベースバンド帯域に戻される。一方、フリッカーノイズ等の低周波数帯域ノイズは、E5に示すように高周波数帯域に周波数変換される。従って、例えばカットオフ周波数fcのローパスフィルターLPFによりローパスフィルター処理を行うことで、入力信号を通過させながら、フリッカーノイズ等の低周波数帯域ノイズを低減できるようになる。

このように本実施形態ではD/A変換回路80の演算増幅器として、チョッパー型の演算増幅器(OPA、OPB、OPC)を用いている。このようにすることで、図6で説明したD/A変換の非直線性誤差を低減できるようになる。更に図7で説明したように、フリッカーノイズ等の低周波数帯域ノイズを低減できるようになり、D/A変換の精度向上等を図れるようになる。

例えば図4の通常型の演算増幅器OPにおいても、差動対のトランジスターの面積を増やせば、オフセット電圧VFを小さくできる。しかしながら、オフセット電圧VFを1/2にするには、トランジスターの面積を例えば4倍程度にする必要があり、回路面積が大幅に増加する。この点、図5のチョッパー型の演算増幅器OPHを用いれば、チョッパー回路ASW1、ASW2等を設けるだけで、オフセット電圧VFを殆ど0Vにすることが可能になり、回路面積の増加を最小限に抑えたオフセットキャンセル(オートゼロ)を実現できるという利点がある。また後述するようにPWM変調で用いられるローパスフィルターをチョッパー用のローパスフィルターとして共用することで、回路面積の増加を更に抑えることが可能になる。

図8、図9に演算増幅器の詳細な構成例を示す。これらはレールトゥーレール方式の演算増幅器であり、図8はレールトゥーレール方式の通常型の演算増幅器の構成例であり、図9はレールトゥーレール方式のチョッパー型の演算増幅器の構成例である。

図9のチョッパー型の演算増幅器では、図8の構成に加えて、複数のスイッチ素子(MOSトランジスター)から構成される変調用、復調用のチョッパー回路ASW1、ASW2が設けられている。即ち、図9のチョッパー型の演算増幅器は、トランジスターTC1〜TC18により構成される増幅段DFCと、トランジスターTC19、TC20により構成される出力段QSCと、チョッパー回路ASW1、ASW2を含む。なおBP、BN、BP2、BN2はバイアス電圧である。

変調用のチョッパー回路ASW1はスイッチ素子S1、S2を含む。スイッチ素子S1は、入力信号NINのノードと、トランジスターTC2、TC4のゲートのノードNA1及びトランジスターTC3、TC5のゲートのノードNA2との間に設けられる。スイッチ素子S2は、入力信号PINのノードと、ノードNA1及びNA2との間に設けられる。入力信号NINとPINは差動信号を構成し、図5の例ではVOUT、VINの信号に相当する。トランジスターTC2とTC3、トランジスターTC4とTC5は、各々、差動対のトランジスターを構成する。そして、これらのスイッチ素子S1、S2により、第1の状態(φ1)では、入力信号NINが、トランジスターTC2、TC4のゲートに入力され、入力信号PINが、トランジスターTC3、TC5のゲートに入力される。第2の状態(φ2)では、入力信号NINが、トランジスターTC3、TC5のゲートに入力され、入力信号PINが、トランジスターTC2、TC4のゲートに入力される。これによりチョッパーの変調が実現される。

復調用のチョッパー回路ASW2はスイッチ素子S3、S4、S5、S6を含む。スイッチ素子S3は、トランジスターTC7、TC8のゲートのノードNA3とノードNA4との間に設けられる。スイッチ素子S4は、トランジスターTC17、TC18のゲートのノードNA6とノードNA7との間に設けられる。スイッチ素子S5は、ノードNA4及びNA5と、出力段QSCのトランジスターTC19のゲートのノードNA9との間に設けられる。スイッチ素子S6は、ノードNA7及びNA8と、出力段QSCのトランジスターTC20のゲートのノードNA10との間に設けられる。

これらのスイッチ素子S3〜S6により、第1の状態(φ1)では、ノードNA3がノードNA4に接続され、ノードNA6がノードNA7に接続されると共に、ノードNA5がノードNA9に接続され、ノードNA8がノードNA10に接続される。第2の状態(φ2)では、ノードNA3がノードNA5に接続され、ノードNA6がノードNA8に接続されると共に、ノードNA4がノードNA9に接続され、ノードNA7がノードNA10に接続される。これによりチョッパーの復調が実現される。

図9の構成によれば、演算増幅器のレールトゥーレール動作を実現しながら、チョッパーの変調、復調も実現できるようになる。レールトゥーレール動作を行うことで、出力の不感帯を無くすことができ、例えば電源電圧が低い場合にも、演算増幅器の出力振幅を最大限にすることが可能になり、D/A変換回路の性能を向上できる。

2.電圧選択回路、電圧生成回路

図10に電圧選択回路40の構成例を示す。電圧選択回路40はデコーダー42を含む。デコーダー42は、入力データDIのデコード処理を行って、制御信号SC1〜SCi(iは2以上の整数)を出力する。入力データDIはD/A変換の対象となるデータである。制御信号SC1〜SCiは、電圧選択回路40のセレクターを構成するトランジスターをオン又はオフにする信号である。デコーダー42が行うデコード処理は公知の処理であるため、詳細な説明は省略する。

また電圧選択回路40は、2段以上の複数のセレクターブロックBLA、BLB、BLC・・・BLFを含む。BLA・・・BLFの各セレクターブロックは1又は複数のセレクターにより構成され、各セレクターは、例えばMOS型のトランジスターにより構成される。そして前段のセレクターブロックが有するセレクターの出力が後段のセレクターブロックが有するセレクターに入力される。具体的には、1段目(前段)のセレクターブロックBLAが有するセレクターの出力が、2段目(後段)のセレクターブロックBLBに入力される。2段目(前段)のセレクターブロックBLBが有するセレクターの出力が、3段目(後段)のセレクターブロックBLCに入力される。最終段のセレクターブロックBLFは、その前段のセレクターブロックが有するセレクターの出力が入力され、電圧選択を行ってD/A変換電圧VDQ(VK、VL)を出力する。

1段目のセレクターブロックBLAには、電圧生成回路30からの電圧V1〜Vjが入力される。そして最終段のセレクターブロックBLFが、D/A変換電圧VDQを出力する。具体的には、電圧選択回路40は、セレクターブロックBLA〜BLFにより、いわゆるトーナメント方式で電圧選択を行って、最終的なD/A変換電圧VDQを出力する。トーナメント方式は、セレクターブロックの各セレクターが制御信号に基づき電圧選択を行うことで、セレクターに入力された複数の電圧の中から1つの電圧が選択され、これによりセレクターに対応するブロックの電圧が順次に勝ち残りで選択されて行く電圧選択方式である。

複数段のセレクターブロックBLA〜BLFの各々は複数のトランジスター(例えばP型トランジスター、N型トランジスター)により構成される。具体的には各セレクターブロックBLA〜BLFは1又は複数のセレクターを有し、当該セレクターが複数のトランジスターにより構成される。

そして本実施形態では、セレクターブロック(少なくとも最終段のセレクターブロック)を構成する複数のトランジスターのうち、電源ノード(VDDA、VSS)から遠い側の第2のトランジスターは、電源ノードから近い側の第1のトランジスターに比べて、低いしきい値電圧に設定されている。具体的には、セレクターブロック(BLA〜BLF)を構成する複数のトランジスターのうち、高電位側電源ノード(VDDA)から遠い側の第2のP型トランジスターは、高電位側電源ノードから近い側の第1のP型トランジスターに比べて、低いしきい値電圧に設定されている。また低電位側電源ノード(VSS)から遠い側の第2のN型トランジスターは、低電位側電源ノードから近い側の第1のN型トランジスターのしきい値電圧に比べて、低いしきい値電圧に設定されている。ここで、電源ノードから遠い側のトランジスターとは、電源ノードから近い側のトランジスターに比べて、トラジスターの入力電圧(入力電圧範囲)が、電源電圧から離れた電圧(電源電圧との差が大きい電圧)となるトランジスターである。電源ノードから近い側の第1のトランジスターの入力電圧をVIN1とし、電源ノードから遠い側の第2のトランジスターを入力電圧VIN2とし、電源電圧をVPWRとした場合に、例えば、|VPWR−VIN2|>|VPWR−VIN1|が成り立つ。

このようにすれば、例えば低消費電力化のために電源電圧を低い電圧にした場合にも、電源ノードから遠い側の第2のトランジスターが低いしきい値電圧に設定されていることで、電圧選択回路40による適正な電圧選択を実現できる。従って、低消費電力化を図りながらも適正な電圧選択を行ってD/A変換電圧VDQを出力できるようになる。

図11は電圧選択回路40の詳細な構成例の説明図である。図11のTA13〜TA20は、図10のセレクターブロックBLAのセレクターを構成するトランジスターであり、TB7〜TB10はセレクターブロックBLBのセレクターを構成するトランジスターである。TF4、TF5はセレクターブロックBLFのセレクターを構成するトランジスターである。1段目のトランジスターTA13〜TA20は、制御信号SC1により排他的にオン又はオフになる。例えば図11では、奇数番目のトランジスターTA13、TA15、TA17、TA19がオンになっており、偶数番目のトランジスターTA14、TA16、TA18、TA20がオフになっている。また2段目のトランジスターTB7〜TB10は、制御信号SC2により排他的にオン又はオフになる。例えば図11では、奇数番目のトランジスターTB7、TB9がオフになっており、偶数番目のトランジスターTB8、TB10がオンになっている。そして最終段のトランジスターTF4、TF5では、TF4がオンになっており、TF5がオフになっている。これにより図11では、電圧V15が選択されて、D/A変換電圧VDQ=V15が出力されている。

この場合に、例えばオフになっているトランジスターTF5においても、オフリーク電流ILが流れる。このオフリーク電流ILは、VDDAからラダー抵抗回路33の抵抗(R23〜R19等)及びオン状態のトランジスターTA19、TB10を介して、オフ状態のトランジスターTF5を流れ、オン状態のトランジスターTF4に流れ込む。そして、このオフリーク電流ILは、オン状態のトランジスターTB8、TA15を介して、電圧V15のノードに流れ込み、ラダー抵抗回路33の抵抗(R14〜R1)を介してVSS側に流れる。

このようにラダー抵抗回路33を用いた場合には、オフリーク電流ILが存在するため、このオフリーク電流ILによる悪影響を低減する必要がある。このために本実施形態では図12に示すように、電圧生成回路30に2つのラダー抵抗回路31、32を設けている。

具体的には電圧生成回路30は、高電位側の電源電圧VDDAと低電位側の電源電圧VSSを抵抗分割するラダー抵抗回路31(第1のラダー抵抗回路)と、電源電圧VDDAと電源電圧VSSを抵抗分割するラダー抵抗回路32(第2のラダー抵抗回路)を含む。ラダー抵抗回路31は、VDDAとVSSの間に直列接続された抵抗RDN、RD0〜RD255、RDPを含む。ラダー抵抗回路32は、VDDAとVSSの間に直列接続された抵抗REN、RE0〜RE255、REPを含む。RD0〜RD255、RE0〜RE255の各抵抗の抵抗値をRとした場合に、抵抗RDN、RENの抵抗値は24Rであり、抵抗RDP、REPの抵抗値は31Rである。

そして電圧選択回路40は、ラダー抵抗回路31の複数の分割電圧から選択された電圧を、電圧VKとして演算増幅器OPAに出力し、ラダー抵抗回路32の複数の分割電圧から選択された電圧を、電圧VLとして演算増幅器OPBに出力する。そして電圧VK、VLを演算増幅器OPA、OPBによりインピーダンス変換した電圧VX、VYが、図2のDACBの電圧生成回路46のラダー抵抗回路47に供給される。電圧選択回路48は、入力データDIの下位pビットに基づいて電圧選択を行い、選択された電圧VMが演算増幅器OPCによりインピーダンス変換されて、電圧VDAとして出力される。

そして図12では、ラダー抵抗回路31の分割電圧V0(広義には第sの分割電圧Vs。sは1以上の整数)が、電圧VKとして演算増幅器OPAに供給されている。この場合には、ラダー抵抗回路32の分割電圧V1(広義には第tの分割電圧Vt。tは1以上の整数)が、電圧VLとして演算増幅器OPBに供給される。

一方、図13では、ラダー抵抗回路31の分割電圧V2(広義には第s+1の分割電圧Vs+1)が、電圧VKとして演算増幅器OPAに供給されている。この場合には、ラダー抵抗回路32の電圧V1(第tの分割電圧Vt)が、電圧VLとして演算増幅器OPBに供給される。即ち図12、図13では、演算増幅器OPBの接続先は、分割電圧V1(Vt)のノードのままで、演算増幅器OPAの接続先が、分割電圧V0(Vs)のノードから分割電圧V1(Vs+1)のノードに切り替わっている。

また図14では、ラダー抵抗回路31の分割電圧V2(第s+1の分割電圧Vs+1)が、電圧VKとして演算増幅器OPAに供給されている。この場合には、ラダー抵抗回路32の分割電圧V3(広義には第t+1の分割電圧Vt+1)が、電圧VLとして演算増幅器OPBに供給される。即ち図13、図14では、演算増幅器OPAの接続先は、分割電圧V2(Vs+1)のノードのままで、演算増幅器OPBの接続先が、分割電圧V1(Vt)のノードから分割電圧V3(Vt+1)のノードに切り替わっている。

このようにすれば、例えば図6のA4、A5に示すD/A変換(入力コード)の切り替わりポイントにおいて、電圧が不連続に変化して、D/A変換特性が悪化してしまう事態を抑制できるようになる。即ち、図6のA4、A5は入力データ(入力コード)に対してD/A変換の電圧が切り替わるポイントである。そして、演算増幅器OPA、OPBの接続先となるラダー抵抗回路が図3のように1つのラダー抵抗回路だけとなる構成において、演算増幅器OPA、OPBの両方の接続先が切り替えポイントにおいて同時に変化してしまうと、電圧が不連続に変化する事態が生じてしまう。例えば図11で説明したように電圧選択回路40のトランジスターにはオフリーク電流ILが流れる。従って、演算増幅器OPA、OPBの接続先が切り替わった際に、このオフリーク電流ILが演算増幅器OPA、OPB側に流れることなどにより、演算増幅器OPA、OPBの入力ノードの電圧が変化してしまう。そして演算増幅器OPA、OPBの接続先となるラダー抵抗回路が1つだけとなる構成において、演算増幅器OPA、OPBの両方の接続先が同時に変化してしまうと、演算増幅器OPA、OPBの入力ノードの電圧の両方が変化してしまい、図6のA4、A5の切り替えポイントにおいて、電圧が不連続に変化する事態が生じてしまう。

この点、図12、図13、図14では、演算増幅器OPAの接続先はラダー抵抗回路31であり、演算増幅器OPBの接続先はラダー抵抗回路32であり、各演算増幅器が異なるラダー抵抗回路に接続される構成になっている。そして例えば図12、図13では、演算増幅器OPBの接続先は、ラダー抵抗回路32の分割電圧V1のノードのままで変化せずに、演算増幅器OPAの接続先だけが、ラダー抵抗回路31の分割電圧V0のノードから分割電圧V2のノードに切り替わっている。このように演算増幅器OPBの接続先は、ラダー抵抗回路32の分割電圧V1のノードのままで変化しないため、図11のようなオフリーク電流ILが発生していても、演算増幅器OPBの入力電圧は変化しない。従って、図6のA4、A5に示すようなD/A変換の切り替えポイントにおいて、電圧が不連続に変化してしまうのを抑制できる。

同様に、図13、図14では、演算増幅器OPAの接続先は、ラダー抵抗回路31の分割電圧V2のノードのままで変化せずに、演算増幅器OPBの接続先だけが、ラダー抵抗回路32の分割電圧V1のノードから分割電圧V3のノードに切り替わっている。このように演算増幅器OPAの接続先は、ラダー抵抗回路31の分割電圧V2のノードのままで変化しないため、図11のようなオフリーク電流ILが発生していても、演算増幅器OPAの入力電圧は変化しない。従って、図6のA4、A5に示すようなD/A変換の切り替えポイントにおいて、電圧が不連続に変化してしまうのを抑制できる。従って、演算増幅器OPA、OPBに対して1つのラダー抵抗回路しか設けない構成において生じるD/A変換特性の悪化を防止できるようになる。

3.回路装置

図15に、本実施形態のD/A変換回路80を有する回路装置500の構成例を示す。例えば図15の回路装置500は、DTCXOやOCXO等のデジタル方式の発振器を実現する回路装置(半導体チップ)である。回路装置500は、A/D変換回路20、処理回路50、発振信号生成回路140を含む。また回路装置500は温度センサー10、バッファー回路160を含むことができる。なお回路装置500は図15の構成には限定されず、その一部の構成要素(例えば温度センサー、バッファー回路、A/D変換回路等)を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

振動子XTALは、例えば水晶振動子等の圧電振動子である。振動子XTALは、恒温槽を備える恒温槽型水晶発振器(OCXO)に内蔵されている振動子、或いは恒温槽を備えない温度補償型水晶発振器(TCXO)に内蔵されている振動子などである。振動子XTALは共振器(電気機械的な共振子又は電気的な共振回路)であってもよい。振動子XTALとしては、圧電振動子、SAW(Surface Acoustic Wave)共振子、シリコン基板を用いて形成されたシリコン製振動子としてのMEMS(Micro Electro Mechanical Systems)振動子等を採用できる。

温度センサー10は、温度検出電圧VTDを出力する。具体的には、環境(回路装置)の温度に応じて変化する温度依存電圧を、温度検出電圧VTDとして出力する。

A/D変換回路20は、温度センサー10からの温度検出電圧VTDのA/D変換を行って、温度検出データDTDを出力する。例えば温度検出電圧VTDのA/D変換結果に対応するデジタルの温度検出データDTD(A/D結果データ)を出力する。A/D変換回路20のA/D変換方式としては、例えば逐次比較方式や逐次比較方式に類似する方式などを採用できる。なおA/D変換方式とし、計数型、並列比較型又は直並列型等を採用してもよい。このA/D変換回路20にも本実施形態のD/A変換回路80を用いることができる。

処理回路50(DSP:デジタル信号処理回路)は種々の信号処理を行う。例えば処理回路50(温度補償部)は、温度検出データDTDに基づいて発振周波数(発振信号の周波数)の温度補償処理を行う。そして発振周波数の周波数制御データDDSを出力する。具体的には処理回路50は、温度に応じて変化する温度検出データDTD(温度依存データ)と、温度補償処理用の係数データ(近似関数の係数のデータ)などに基づいて、温度変化があった場合にも発振周波数を一定にするための温度補償処理を行う。この処理回路50は、ゲートアレイ等のASIC回路により実現してもよいし、プロセッサーとプロセッサー上で動作するプログラムにより実現してもよい。

発振信号生成回路140は発振信号SSCを生成する。例えば発振信号生成回路140は、処理回路50からの周波数制御データDDSと振動子XTALを用いて、周波数制御データDDSにより設定される発振周波数の発振信号SSCを生成する。一例としては、発振信号生成回路140は、周波数制御データDDSにより設定される発振周波数で振動子XTALを発振させて、発振信号SSCを生成する。

なお発振信号生成回路140は、ダイレクト・デジタル・シンセサイザー方式で発振信号SSCを生成する回路であってもよい。例えば振動子XTAL(固定発振周波数の発振源)の発振信号をリファレンス信号として、周波数制御データDDSで設定される発振周波数の発振信号SSCをデジタル的に生成してもよい。

発振信号生成回路140は、D/A変換回路80と発振回路150を含む。D/A変換回路80は、処理回路50からの周波数制御データDDS(処理回路の出力データ)のD/A変換を行う。D/A変換回路80に入力される周波数制御データDDSは、処理回路50による温度補償処理後の周波数制御データ(周波数制御コード)である。

発振回路150は、D/A変換回路80の出力電圧VQと振動子XTALを用いて、発振信号SSCを生成する。例えば発振回路150は、振動子XTALを発振させることで、発振信号SSCを生成する。具体的には発振回路150は、D/A変換回路80の出力電圧VQを周波数制御電圧(発振制御電圧)とした発振周波数で、振動子XTALを発振させる。この場合には、発振回路150は、周波数制御電圧に応じて容量値が変化する可変容量キャパシター(バリキャップ等)を含むことできる。

バッファー回路160は、発振信号生成回路140(発振回路150)で生成された発振信号SSCのバッファリングを行って、バッファリング後の信号SQを出力する。信号SQは、例えばクリップドサイン波信号や矩形波信号などである。

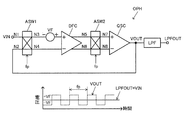

また図15に示すようにD/A変換回路80は、変調回路90とD/A変換器100とフィルター回路120を含む。D/A変換器100は、例えば図2のD/A変換器DACA、DACB、演算増幅器OPA、OPB、OPCにより構成される回路である。

変調回路90は、処理回路50からi=(n+m)ビットの周波数制御データDDSを受ける(i、n、mは1以上の整数)。一例としてはi=20、n=16、m=4である。そして変調回路90は、周波数制御データDDSのmビット(例えば4ビット)のデータに基づいて、周波数制御データDDSのnビット(例えば16ビット)のデータを変調する。具体的には変調回路90は、周波数制御データDDSのPWM変調を行う。なお変調回路90の変調方式はPWM変調(パルス幅変調)には限定されず、例えばPDM変調(パルス密度変調)等のパルス変調であってもよく、パルス変調以外の変調方式であってもよい。例えば周波数制御データDDSのnビットのデータに対して、mビットのディザー処理(ディザリング処理)を行うことでビット拡張(nビットからiビットへのビット拡張)を実現してもよい。

D/A変換器100は、変調回路90により変調されたnビットのデータのD/A変換を行う。例えばn=16ビットのデータのD/A変換を行う。

フィルター回路120は、D/A変換により得られた電圧VDAを平滑化する。例えばローパスフィルター処理を行って電圧VDAを平滑化する。このようなフィルター回路120を設けることで、例えばPWM変調された信号のPWM復調が可能になる。なおフィルター回路120としては、例えば抵抗又はキャパシター等の受動素子を用いたパッシブフィルターを採用できる。但しフィルター回路120としてSCFなどのアクティブフィルターを用いることも可能である。

例えばDTCXO等のデジタル方式の発振器では、その発振周波数の周波数ドリフトが原因で、発振器が組み込まれた通信装置において通信エラー等が発生してしまうという問題がある。例えばデジタル方式の発振器では、温度センサーからの温度検出電圧をA/D変換し、得られた温度検出データに基づいて周波数制御データの温度補償処理を行い、当該周波数制御データに基づいて発振信号を生成する。この場合に、温度変化により周波数制御データの値が大きく変化すると、これが原因で周波数ホッピングの問題が生じることが判明した。このような周波数ホッピングが生じると、GPS関連の通信装置を例にとれば、GPSのロックが外れてしまうなどの問題が発生してしまう。

このような周波数ホッピングを原因とする通信エラーの発生を抑制し、周波数精度の向上を図るためには、D/A変換回路80の分解能をできる限り高くする必要がある。

しかしながら、例えば抵抗ストリング型等のD/A変換器100だけで、例えばi=20ビットというような高分解能のD/A変換を実現するのは困難である。またD/A変換回路80の出力ノイズ(出力電圧のノイズ)が大きいと、当該出力ノイズが原因となって、周波数精度の向上の実現が難しくなる。

そこで図15では、D/A変換回路80に変調回路90を設ける。また処理回路50は、D/A変換器100の分解能であるnビット(例えば16ビット)よりもビット数が多いi=m+nビットの周波数制御データDDSを出力する。処理回路50は、例えば温度補償処理等のデジタル信号処理を実現するために、浮動小数点演算等を行っているため、このようなnビット(例えばn=16ビット)よりもビット数が多いi=m+nビットの周波数制御データDDSを出力することは容易である。

そして変調回路90は、i=m+nのうちのmビットのデータに基づいて、i=m+nのうちのnビットのデータの変調(PWM変調等)を行い、変調後のnビットのデータDMをD/A変換器100に出力する。そしてD/A変換器100がデータDMのD/A変換を行い、得られた電圧VDAの平滑化処理をフィルター回路120が行うことで、i=m+nビット(例えば20ビット)というような高分解能のD/A変換を実現できるようになる。

この構成によれば、D/A変換器100として例えば出力ノイズが少ない抵抗ストリング型等を採用できるため、D/A変換回路80の出力ノイズを低減でき、周波数精度の劣化の抑制が容易になる。例えば変調回路90での変調によりノイズが発生するが、当該ノイズについても、フィルター回路120のカットオフ周波数の設定により十分に減衰することができ、当該ノイズを原因とする周波数精度の劣化を抑制できる。

なおD/A変換回路80の分解能はi=20ビットには限定されず、20ビットよりも高い分解能であってもよいし、低い分解能であってもよい。また変調回路90の変調のビット数もm=4ビットには限定されず、4ビットよりも大きくてもよいし(例えばm=8ビット)、小さくてもよい。

また図15では、D/A変換回路80の前段に、温度補償処理等のデジタル信号処理を行う処理回路50が設けられていることを、有効活用している。即ち、処理回路50は、例えば浮動小数点演算などにより、高精度で、温度補償処理等のデジタル信号処理を実行している。従って、例えば浮動小数点演算の結果の仮数部の下位ビットも有効なデータとして扱って、バイナリーデータに変換すれば、例えばi=m+n=20ビットというような高いビット数での周波数制御データDDSも、容易に出力できる。図15ではこの点に着目し、このような高いビット数であるi=m+nビットの周波数制御データDDSを、D/A変換回路80に供給し、mビットの変調回路90とnビットのD/A変換器100を用いて、i=m+nビットというような高分解能のD/A変換の実現に成功している。

このようにD/A変換回路80の分解能を高分解能にすることで、上述した周波数ホッピングの発生を抑制できる。これにより周波数ホッピングを原因とする通信エラー等の発生を抑制することが可能になる。

また、このような周波数ホッピングの問題以外にも、DTCXOやOCXOなどのデジタル方式の発振器では、発振周波数に対して非常に高い周波数精度が要求される。例えばTDD(Time Division Duplex)方式では、上がりと下りで同じ周波数を用いて時分割でデータが送受信され、各機器に割り当てられたタイムスロットの間にはガードタイムが設定されている。このため、適正な通信を実現するためには、各機器において時刻同期を行う必要があり、正確な絶対時刻の計時が要求される。例えば基準信号(GPS信号やインターネットを介した信号)が消失又は異常となるホールドオーバーが発生した場合には、基準信号が無い状態で発振器側が正確に絶対時刻を計時する必要がある。このため、このような機器(GPS関連機器、基地局等)に用いられる発振器には、非常に高い発振周波数精度が要求される。

この点、図15の回路装置500の構成によれば、D/A変換回路80に、変調回路90やフィルター回路120を設けるだけで、例えばi≧20ビットとなるような非常に高い分解能のD/A変換回路80を実現でき、このように分解能が高くなることで、発振周波数の高精度化を実現できる。そして、このような変調回路90やフィルター回路120を設けることによる回路装置500のチップサイズの増加や消費電力の増加は、それほど大きくない。更に処理回路50では浮動点小数点演算などにより温度補償処理を実行しているため、例えばi≧20ビットとなるような周波数制御データDDSをD/A変換回路80に出力することも容易である。従って、図15の回路装置500の構成は、発振周波数の高精度化と、回路装置500の規模や消費電力の増加の抑制とを、両立して実現できるという利点がある。

なお処理回路50は、第1の温度から第2の温度に温度が変化した場合に、第1の温度(第1の温度検出データ)に対応する第1のデータから、第2の温度(第2の温度検出データ)に対応する第2のデータへと、k×LSB単位で変化(k×LSBずつ変化)する周波数制御データDDSを出力する。ここでk≧1であり、kは1以上の整数である。例えば周波数制御データDDSのビット数(D/A変換回路の解像度)をiとした場合に、k<2iであり、kは2iよりも十分に小さい整数である(例えばk=1〜8)。更に具体的にはk<2mである。例えばk=1の場合には、処理回路50は、1LSB単位(1ビット単位)で第1のデータから第2のデータに変化する周波数制御データDDSを出力する。即ち、第1のデータから第2のデータに向かって、1LSB(1ビット)ずつシフトしながら変化するような周波数制御データDDSを出力する。なお周波数制御データDDSの変化ステップ幅は、1LSBには限定されず、例えば2×LSB、3×LSB、4×LSB・・・というように2×LSB以上の変化ステップ幅であってもよい。

このように、処理回路50から出力される周波数制御データDDSが、k×LSBずつ変化するようになれば、例えば温度が第1の温度から第2の温度に変化した場合に、D/A変換回路80の出力電圧VQに大きな電圧変化が生じ、この電圧変化が原因で周波数ホッピングが発生してしまう事態を抑制できる。これにより当該周波数ホッピングが原因で通信エラー等が生じるのを防止できるようになる。

図16、図17、図18はPWM変調の説明図である。図16に示すように、変調回路90は、処理回路50からのi=(n+m)ビットの周波数制御データDDSを受ける。そして、この周波数制御データDDSの下位のmビットのデータ(ビットb1〜b4)に基づいて、周波数制御データDDSの上位のnビット(ビットb5〜b20)のデータのPWM変調を行う。そして、当該nビットのデータのうち、上位のqビットのデータ(ビットb13〜b20)が、図2、図3の上位側のDACAに入力され、下位のpビットのデータ(ビットb5〜b12)が、下位側のDACBに入力される。

図17はPWM変調の第1の方式の説明図である。DY、DZは、データDMの上位のnビットのデータであり、nビット表現においてDY=DZ+1が成り立つデータである。

PWM変調に用いられる下位のm=4ビットのデータで表されるデューティー比が、例えば8対8である場合には、図17に示すように、8個の16ビットのデータDYと8個の16ビットのデータDZが時分割で、変調回路90からD/A変換器100(DACA、DACB)に出力される。

また下位のm=4ビットのデータで表されるデューティー比が10対6である場合には、10個のデータDYと6個のデータDZが時分割で、変調回路90からD/A変換器100に出力される。同様に、下位のm=4ビットのデータで表されるデューティー比が14対2である場合には、14個のデータDYと2個のデータDZが時分割で出力される。

図18はPWM変調の第2の方式の説明図である。PWM変調に用いられるm=4ビットの各ビットb4、b3、b2、b1が、論理レベル「1」である場合に、図18において各ビットに対応づけられた出力パターン(各ビットの右側に示される出力パターン)が選択される。

例えばビットb4=1で、b3=b2=b1=0である場合には、ビットb4に対応づけられた出力パターンだけが期間P1〜P16において出力される。即ち、n=16ビットのデータがDZ、DY、DZ、DY・・・・の順で時分割に、変調回路90からD/A変換器100に出力される。これにより、データDY、DZの出力回数は共に8回となり、図17においてデューティー比が8対8である場合と同様のPWM変調が実現される。

またビットb4=b2=1で、b3=b1=0である場合には、ビットb4とb2に対応づけられた出力パターンが期間P1〜P16において出力される。これによりデータDY、DZの出力回数は、各々、10回、6回になり、デューティー比が10対6である場合と同様のPWM変調が実現される。同様に、ビットb4=b3=b2=1で、b1=0である場合には、データDY、DZの出力回数は、各々、14回、2回になり、デューティー比が14対2である場合と同様のPWM変調が実現される。

4.フィルター回路の共用

本実施形態では図15のフィルター回路120を、PWMの変調回路90用のローパスフィルターとして用いると共に、チョッパー型の演算増幅器OPA、OPB用のローパスフィルターとして用いており、PWM変調とチョッパー動作でフィルター回路120を共用している。具体的には、PWMの変調回路90の変調周波数をfmとし、チョッパー型の演算増幅器OPA、OPB(及びOPC)のチョッピング周波数をfpとした場合に、fm=fpに設定している。例えばPWMの変調周波数がfm=256KHzである場合に、チョッピング周波数もfp=256KHzに設定する。

そしてフィルター回路120は、変調回路90の変調によるリップル電圧と、チョッパー型の演算増幅器OPA、OPBのチョッピングによるリップル電圧が、所与の電圧レベルVNSよりも小さくなるように減衰する周波数特性のローパスフィルターとなっている。この電圧レベルVNSは、図15の発振回路150の周波数制御電圧(発振制御電圧)に許容される電圧ノイズレベルにより決められる。例えば発振周波数の位相ノイズの許容目標レベルが設定されており、この位相ノイズの許容目標レベルから、周波数制御電圧に許容される電圧ノイズレベルが決められ、電圧レベルVNSが設定される。

図19はPWM変調の変調パターンの例を示す図である。VDY、VDZは、前述したデータDY(=DZ+l)、DZに対応する電圧レベルである。そしてVDY−VDZが、例えば図16のnビット(例えばn=16)のD/A変換におけるLSBの電圧レベルに相当する。そしてPWM変調のm=4ビットのビットパターンに応じて、図19に示すような変調パターンが生成される。

ここでPWM変調のm=4ビットのビットパターンが(1000)である場合には、図19に示すように変調パターンの周波数はfm=256KHzとなり、最も周波数が高くなる。一方、ビットパターンが(1111)の場合には、変調パターンの周波数は、fmmin=fm/N=32KHz(Nは2以上の整数)となり、最も低い周波数になる。そして変調回路90によるリップル電圧には、このfmmin=32KHzの周波数成分が存在するため、このfmmin=32KHzの周波数成分を、フィルター回路120により十分に減衰する必要がある。

例えば図20は本実施形態のフィルター回路120のローパスフィルターの周波数特性の一例である。図20においてfcはフィルター回路120のカットオフ周波数である。例えばフィルター回路120は1次のRCローパスフィルターであり、カットオフ周波数fcは例えば1KHz〜10KHz程度に設定できる。そして図20に示すようにフィルター回路120は、fm=fp=256KHzの周波数成分のみならず、fmmin=32KHzの周波数成分も十分に減衰(例えば−15DB〜25DB程度の減衰)できる周波数特性を有している。このような周波数特性を持たせることで、図19のビットパターン=(1111)に対応するような周波数が低い変調パターンによるリップル電圧の周波数成分についても、十分に減衰できるようになり、位相ノイズ等に対する要求仕様を満足することが可能になる。

このように本実施形態では、変調回路90の変調周波数をfmとし、変調回路90の変調パターンのうち最も周波数が低い変調パターンの周波数をfmmin=fm/N(Nは2以上の整数)とし、フィルター回路120のカットオフ周波数をfcとした場合に、fc<fmminの関係を成り立たせている。例えば変調データのビット数をmとした場合にN=2m−1である。m=4の場合にはN=8である。また図20から明らかなように、チョッパー型の演算増幅器OPA、OPBのチョッピング周波数をfpとした場合に、fc<fmmin<fpの関係が成り立っている。このようにすることで、変調回路90の変調によるリップル電圧と、チョッパー型の演算増幅器OPA、OPBのチョッピングによるリップル電圧を、フィルター回路120のローパスフィルターにより十分に減衰して、位相ノイズ等に対する要求仕様を満足できるようになる。

本実施形態では、チョッパー型の演算増幅器OPA、OPBのチョッピングモードをオン、オフできるようになっている。図21はチョッピングモードをオフにした場合における、図15のVDAとVQの信号波形例である。VDAはD/A変換器100の出力電圧であり、VQはフィルター回路120の出力電圧である。図22はチョッピングモードをオンにした場合における、VDAとVQの信号波形例である。図21、図22において、VLSBはnビットのD/A変換におけるLSB電圧であり、VFは図5で説明したオフセット電圧である。

図21では、変調回路90の変調により、D/A変換器100からの電圧VDAが、B1、B2に示すように変化しているが、この電圧変化によるリップル電圧が、フィルター回路120によりB3、B4に示すように減衰されて平滑化されている。

図22では、変調回路90の変調とチョッパー型の演算増幅器OPA、OPBのチョッピング動作により、D/A変換器100からの電圧VDAが、B5、B6に示すように変化しているが、この電圧変化によるリップル電圧が、フィルター回路120によりB7、B8に示すように減衰されて平滑化されている。

なおD/A変換回路80に変調回路90及びチョッパー型の演算増幅器を設け、fp=fmとしたり、fc<fmmin<fpとする本実施形態の手法では、D/A変換回路の回路構成は図1〜図3等で説明した構成には限定されない。例えばチョッパー型の演算増幅器をインピーダンス変換回路として用いた種々の方式(電荷再分配方式、Δシグマ方式等)のD/A変換回路に対して、本実施形態の手法は適用できる。

5.発振器、電子機器、移動体

図23に、本実施形態の回路装置500を含む発振器400の構成例を示す。図23に示すように、発振器400は、振動子XTALと回路装置500(D/A変換回路80)を含む。振動子XTALと回路装置500は、発振器400のパッケージ410内に実装される。そして振動子XTALの端子と、回路装置500(IC)の端子(パッド)は、パッケージ410の内部配線により電気的に接続される。

図24に、本実施形態の回路装置500(D/A変換回路80)を含む電子機器の構成例を示す。この電子機器は、本実施形態の回路装置500(D/A変換回路80)、振動子XTAL、アンテナANT、通信部510、処理部520を含む。また操作部530、表示部540、記憶部550を含むことができる。振動子XTALと回路装置500により発振器400が構成される。なお電子機器は図24の構成に限定されず、これらの一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

図24の電子機器としては、例えばGPS内蔵時計、生体情報測定機器(脈波計、歩数計等)又は頭部装着型表示装置等のウェアラブル機器や、スマートフォン、携帯電話機、携帯型ゲーム装置、ノートPC又はタブレットPC等の携帯情報端末(移動端末)や、コンテンツを配信するコンテンツ提供端末や、デジタルカメラ又はビデオカメラ等の映像機器や、或いは基地局又はルーター等のネットワーク関連機器などの種々の機器を想定できる。

通信部510(無線回路)は、アンテナANTを介して外部からデータを受信したり、外部にデータを送信する処理を行う。処理部520は、電子機器の制御処理や、通信部510を介して送受信されるデータの種々のデジタル処理などを行う。この処理部520の機能は、例えばマイクロコンピューターなどのプロセッサーにより実現できる。操作部530は、ユーザーが入力操作を行うためのものであり、操作ボタンやタッチパネルディスプレイをなどにより実現できる。表示部540は、各種の情報を表示するものであり、液晶や有機ELなどのディスプレイにより実現できる。記憶部550は、データを記憶するものであり、RAMやROMなどの半導体メモリーやHDD(ハードディスクドライブ)などにより実現できる。

図25に、本実施形態の回路装置500(D/A変換回路80)を含む移動体の例を示す。本実施形態の回路装置500(発振器)は、例えば、車、飛行機、バイク、自転車、或いは船舶等の種々の移動体に組み込むことができる。移動体は、例えばエンジンやモーター等の駆動機構、ハンドルや舵等の操舵機構、各種の電子機器(車載機器)を備えて、地上や空や海上を移動する機器・装置である。図25は移動体の具体例としての自動車206を概略的に示している。自動車206には、本実施形態の回路装置500(D/A変換回路80)と振動子を有する発振器(不図示)が組み込まれる。制御装置208は、この発振器により生成されたクロック信号により動作する。制御装置208は、例えば車体207の姿勢に応じてサスペンションの硬軟を制御したり、個々の車輪209のブレーキを制御する。例えば制御装置208により、自動車206の自動運転を実現してもよい。なお本実施形態の回路装置500(D/A変換回路80)や発振器が組み込まれる機器は、このような制御装置208には限定されず、自動車206等の移動体に設けられる種々の機器(車載機器)に組み込むことが可能である。

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また本実施形態及び変形例の全ての組み合わせも、本発明の範囲に含まれる。またD/A変換回路、回路装置、発振器、電子機器、移動体の構成・動作や、D/A変換手法、チョッピング手法、変調手法等も本実施形態で説明したものに限定されず、種々の変形実施が可能である。