JP6904769B2 - Display device - Google Patents

Display device Download PDFInfo

- Publication number

- JP6904769B2 JP6904769B2 JP2017083615A JP2017083615A JP6904769B2 JP 6904769 B2 JP6904769 B2 JP 6904769B2 JP 2017083615 A JP2017083615 A JP 2017083615A JP 2017083615 A JP2017083615 A JP 2017083615A JP 6904769 B2 JP6904769 B2 JP 6904769B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- layer

- insulating layer

- semiconductor layer

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 claims description 339

- 239000004973 liquid crystal related substance Substances 0.000 claims description 78

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 66

- 229910052760 oxygen Inorganic materials 0.000 claims description 66

- 239000001301 oxygen Substances 0.000 claims description 66

- 239000011701 zinc Substances 0.000 claims description 45

- 229920005989 resin Polymers 0.000 claims description 31

- 239000011347 resin Substances 0.000 claims description 31

- 229910052751 metal Inorganic materials 0.000 claims description 28

- 239000002184 metal Substances 0.000 claims description 26

- 229910052738 indium Inorganic materials 0.000 claims description 18

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 claims description 14

- 229910052725 zinc Inorganic materials 0.000 claims description 14

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 claims description 10

- 229910052733 gallium Inorganic materials 0.000 claims description 10

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 claims description 6

- 239000010410 layer Substances 0.000 description 907

- 230000006870 function Effects 0.000 description 138

- 238000000034 method Methods 0.000 description 100

- 239000000463 material Substances 0.000 description 89

- 239000010408 film Substances 0.000 description 69

- 239000000758 substrate Substances 0.000 description 68

- 229910044991 metal oxide Inorganic materials 0.000 description 44

- 230000001965 increasing effect Effects 0.000 description 43

- 150000004706 metal oxides Chemical class 0.000 description 33

- 239000012535 impurity Substances 0.000 description 32

- MWUXSHHQAYIFBG-UHFFFAOYSA-N nitrogen oxide Inorganic materials O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 32

- 239000013078 crystal Substances 0.000 description 31

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 28

- 230000005684 electric field Effects 0.000 description 21

- 230000005669 field effect Effects 0.000 description 21

- 239000010936 titanium Substances 0.000 description 19

- 238000005338 heat storage Methods 0.000 description 18

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 16

- 229910052782 aluminium Inorganic materials 0.000 description 16

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 16

- 229910052719 titanium Inorganic materials 0.000 description 16

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 15

- 239000004020 conductor Substances 0.000 description 15

- 230000001976 improved effect Effects 0.000 description 15

- 238000004519 manufacturing process Methods 0.000 description 14

- 239000000203 mixture Substances 0.000 description 14

- 229910052757 nitrogen Inorganic materials 0.000 description 14

- 229910052581 Si3N4 Inorganic materials 0.000 description 13

- 230000015572 biosynthetic process Effects 0.000 description 13

- 239000001257 hydrogen Substances 0.000 description 13

- 229910052739 hydrogen Inorganic materials 0.000 description 13

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 13

- 206010021143 Hypoxia Diseases 0.000 description 12

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 12

- 229910021417 amorphous silicon Inorganic materials 0.000 description 12

- 238000004364 calculation method Methods 0.000 description 12

- 238000005530 etching Methods 0.000 description 12

- 229910052710 silicon Inorganic materials 0.000 description 12

- 239000010703 silicon Substances 0.000 description 12

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 11

- 238000005229 chemical vapour deposition Methods 0.000 description 11

- 238000009413 insulation Methods 0.000 description 11

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 10

- -1 aluminum nitride nitride Chemical class 0.000 description 10

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 10

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 10

- 125000004429 atom Chemical group 0.000 description 9

- 238000000231 atomic layer deposition Methods 0.000 description 9

- 239000010949 copper Substances 0.000 description 9

- 230000007547 defect Effects 0.000 description 9

- 150000004767 nitrides Chemical class 0.000 description 9

- 239000000126 substance Substances 0.000 description 9

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 8

- 230000005685 electric field effect Effects 0.000 description 8

- 239000007789 gas Substances 0.000 description 8

- 238000010438 heat treatment Methods 0.000 description 8

- 238000012986 modification Methods 0.000 description 8

- 230000004048 modification Effects 0.000 description 8

- 229910052750 molybdenum Inorganic materials 0.000 description 8

- 229910052814 silicon oxide Inorganic materials 0.000 description 8

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 7

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 7

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 7

- 230000008859 change Effects 0.000 description 7

- 229910052802 copper Inorganic materials 0.000 description 7

- 239000002178 crystalline material Substances 0.000 description 7

- 238000009792 diffusion process Methods 0.000 description 7

- 239000011521 glass Substances 0.000 description 7

- 239000011810 insulating material Substances 0.000 description 7

- 239000011733 molybdenum Substances 0.000 description 7

- 230000008569 process Effects 0.000 description 7

- 239000003566 sealing material Substances 0.000 description 7

- 238000012360 testing method Methods 0.000 description 7

- 239000010409 thin film Substances 0.000 description 7

- 229910052721 tungsten Inorganic materials 0.000 description 7

- 239000010937 tungsten Substances 0.000 description 7

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 6

- 230000005540 biological transmission Effects 0.000 description 6

- 239000000969 carrier Substances 0.000 description 6

- 239000011651 chromium Substances 0.000 description 6

- 150000001875 compounds Chemical class 0.000 description 6

- 230000006378 damage Effects 0.000 description 6

- 230000000694 effects Effects 0.000 description 6

- 210000001508 eye Anatomy 0.000 description 6

- 229910021389 graphene Inorganic materials 0.000 description 6

- 229910010272 inorganic material Inorganic materials 0.000 description 6

- 239000011159 matrix material Substances 0.000 description 6

- 230000003071 parasitic effect Effects 0.000 description 6

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 6

- 238000012545 processing Methods 0.000 description 6

- 230000035882 stress Effects 0.000 description 6

- 229910052715 tantalum Inorganic materials 0.000 description 6

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 6

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 6

- 239000004925 Acrylic resin Substances 0.000 description 5

- 229920000178 Acrylic resin Polymers 0.000 description 5

- 102100040862 Dual specificity protein kinase CLK1 Human genes 0.000 description 5

- 229910045601 alloy Inorganic materials 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 229910021529 ammonia Inorganic materials 0.000 description 5

- 229910002804 graphite Inorganic materials 0.000 description 5

- 239000010439 graphite Substances 0.000 description 5

- 229910052735 hafnium Inorganic materials 0.000 description 5

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 5

- 150000002431 hydrogen Chemical class 0.000 description 5

- 229910052759 nickel Inorganic materials 0.000 description 5

- 230000003287 optical effect Effects 0.000 description 5

- 239000012466 permeate Substances 0.000 description 5

- 229920001721 polyimide Polymers 0.000 description 5

- 229920000642 polymer Polymers 0.000 description 5

- 239000002096 quantum dot Substances 0.000 description 5

- 239000002356 single layer Substances 0.000 description 5

- 125000006850 spacer group Chemical group 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 5

- 101000749294 Homo sapiens Dual specificity protein kinase CLK1 Proteins 0.000 description 4

- 229910052779 Neodymium Inorganic materials 0.000 description 4

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 4

- 239000004642 Polyimide Substances 0.000 description 4

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 4

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 4

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 4

- 229910052804 chromium Inorganic materials 0.000 description 4

- 238000004891 communication Methods 0.000 description 4

- 229920001940 conductive polymer Polymers 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 4

- 239000003822 epoxy resin Substances 0.000 description 4

- 229910052732 germanium Inorganic materials 0.000 description 4

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 4

- 229910003437 indium oxide Inorganic materials 0.000 description 4

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 4

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 4

- 239000011147 inorganic material Substances 0.000 description 4

- 230000010354 integration Effects 0.000 description 4

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 4

- 239000002159 nanocrystal Substances 0.000 description 4

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 4

- 239000010955 niobium Substances 0.000 description 4

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 4

- 238000005192 partition Methods 0.000 description 4

- 229910052698 phosphorus Inorganic materials 0.000 description 4

- 239000011574 phosphorus Substances 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 229920000647 polyepoxide Polymers 0.000 description 4

- 239000002994 raw material Substances 0.000 description 4

- 229910052709 silver Inorganic materials 0.000 description 4

- 239000004332 silver Substances 0.000 description 4

- 238000003860 storage Methods 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- 238000011282 treatment Methods 0.000 description 4

- 229910001930 tungsten oxide Inorganic materials 0.000 description 4

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 4

- UWCWUCKPEYNDNV-LBPRGKRZSA-N 2,6-dimethyl-n-[[(2s)-pyrrolidin-2-yl]methyl]aniline Chemical compound CC1=CC=CC(C)=C1NC[C@H]1NCCC1 UWCWUCKPEYNDNV-LBPRGKRZSA-N 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- 102100040858 Dual specificity protein kinase CLK4 Human genes 0.000 description 3

- 101000749298 Homo sapiens Dual specificity protein kinase CLK4 Proteins 0.000 description 3

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 3

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 3

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 3

- 230000001133 acceleration Effects 0.000 description 3

- 230000009471 action Effects 0.000 description 3

- 229910052786 argon Inorganic materials 0.000 description 3

- 229910052799 carbon Inorganic materials 0.000 description 3

- 238000000576 coating method Methods 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 238000013461 design Methods 0.000 description 3

- 230000006866 deterioration Effects 0.000 description 3

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 3

- 230000009977 dual effect Effects 0.000 description 3

- 230000005611 electricity Effects 0.000 description 3

- 238000005401 electroluminescence Methods 0.000 description 3

- 238000010894 electron beam technology Methods 0.000 description 3

- 239000000945 filler Substances 0.000 description 3

- 238000007667 floating Methods 0.000 description 3

- 229910001195 gallium oxide Inorganic materials 0.000 description 3

- 230000001939 inductive effect Effects 0.000 description 3

- 239000011777 magnesium Substances 0.000 description 3

- 239000011572 manganese Substances 0.000 description 3

- 238000005259 measurement Methods 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 239000002245 particle Substances 0.000 description 3

- 230000002093 peripheral effect Effects 0.000 description 3

- 239000004417 polycarbonate Substances 0.000 description 3

- 229920000515 polycarbonate Polymers 0.000 description 3

- 239000004800 polyvinyl chloride Substances 0.000 description 3

- 229920000915 polyvinyl chloride Polymers 0.000 description 3

- 229920002050 silicone resin Polymers 0.000 description 3

- 239000003381 stabilizer Substances 0.000 description 3

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 3

- 229910052718 tin Inorganic materials 0.000 description 3

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 3

- 229910001868 water Inorganic materials 0.000 description 3

- 229910052726 zirconium Inorganic materials 0.000 description 3

- 229910018137 Al-Zn Inorganic materials 0.000 description 2

- 229910018573 Al—Zn Inorganic materials 0.000 description 2

- PAYRUJLWNCNPSJ-UHFFFAOYSA-N Aniline Chemical compound NC1=CC=CC=C1 PAYRUJLWNCNPSJ-UHFFFAOYSA-N 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- 229910052684 Cerium Inorganic materials 0.000 description 2

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 2

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- HBBGRARXTFLTSG-UHFFFAOYSA-N Lithium ion Chemical compound [Li+] HBBGRARXTFLTSG-UHFFFAOYSA-N 0.000 description 2

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 2

- 239000004983 Polymer Dispersed Liquid Crystal Substances 0.000 description 2

- 239000004793 Polystyrene Substances 0.000 description 2

- KAESVJOAVNADME-UHFFFAOYSA-N Pyrrole Chemical compound C=1C=CNC=1 KAESVJOAVNADME-UHFFFAOYSA-N 0.000 description 2

- YTPLMLYBLZKORZ-UHFFFAOYSA-N Thiophene Chemical compound C=1C=CSC=1 YTPLMLYBLZKORZ-UHFFFAOYSA-N 0.000 description 2

- 238000002441 X-ray diffraction Methods 0.000 description 2

- 238000010521 absorption reaction Methods 0.000 description 2

- 239000004760 aramid Substances 0.000 description 2

- 229920003235 aromatic polyamide Polymers 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 210000005252 bulbus oculi Anatomy 0.000 description 2

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical compound [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 2

- 239000000460 chlorine Substances 0.000 description 2

- 229910052801 chlorine Inorganic materials 0.000 description 2

- 230000003098 cholesteric effect Effects 0.000 description 2

- 239000011248 coating agent Substances 0.000 description 2

- 238000004040 coloring Methods 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 239000002274 desiccant Substances 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 230000018109 developmental process Effects 0.000 description 2

- 239000005038 ethylene vinyl acetate Substances 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 239000005262 ferroelectric liquid crystals (FLCs) Substances 0.000 description 2

- 239000011737 fluorine Substances 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 125000001153 fluoro group Chemical group F* 0.000 description 2

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 229910000449 hafnium oxide Inorganic materials 0.000 description 2

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 150000002484 inorganic compounds Chemical class 0.000 description 2

- 238000010030 laminating Methods 0.000 description 2

- 229910052747 lanthanoid Inorganic materials 0.000 description 2

- 150000002602 lanthanoids Chemical class 0.000 description 2

- 229910001416 lithium ion Inorganic materials 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 229910052748 manganese Inorganic materials 0.000 description 2

- 150000002739 metals Chemical class 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- PLDDOISOJJCEMH-UHFFFAOYSA-N neodymium(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Nd+3].[Nd+3] PLDDOISOJJCEMH-UHFFFAOYSA-N 0.000 description 2

- 229910052758 niobium Inorganic materials 0.000 description 2

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 2

- 229910052756 noble gas Inorganic materials 0.000 description 2

- 150000002894 organic compounds Chemical class 0.000 description 2

- 125000000962 organic group Chemical group 0.000 description 2

- 239000011368 organic material Substances 0.000 description 2

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 2

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 2

- 125000004430 oxygen atom Chemical group O* 0.000 description 2

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 2

- 239000005011 phenolic resin Substances 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 2

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 2

- 229920006122 polyamide resin Polymers 0.000 description 2

- 229920000139 polyethylene terephthalate Polymers 0.000 description 2

- 239000005020 polyethylene terephthalate Substances 0.000 description 2

- 229920002223 polystyrene Polymers 0.000 description 2

- 229920001343 polytetrafluoroethylene Polymers 0.000 description 2

- 239000004810 polytetrafluoroethylene Substances 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- 238000005546 reactive sputtering Methods 0.000 description 2

- 238000005001 rutherford backscattering spectroscopy Methods 0.000 description 2

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 229910010271 silicon carbide Inorganic materials 0.000 description 2

- 238000004528 spin coating Methods 0.000 description 2

- 238000005477 sputtering target Methods 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- 229920001187 thermosetting polymer Polymers 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- LEONUFNNVUYDNQ-UHFFFAOYSA-N vanadium atom Chemical compound [V] LEONUFNNVUYDNQ-UHFFFAOYSA-N 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- 229910052727 yttrium Inorganic materials 0.000 description 2

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 2

- 239000011787 zinc oxide Substances 0.000 description 2

- 235000014692 zinc oxide Nutrition 0.000 description 2

- 229910001928 zirconium oxide Inorganic materials 0.000 description 2

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- 239000004986 Cholesteric liquid crystals (ChLC) Substances 0.000 description 1

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 1

- 102100040844 Dual specificity protein kinase CLK2 Human genes 0.000 description 1

- 102100040856 Dual specificity protein kinase CLK3 Human genes 0.000 description 1

- 229910052692 Dysprosium Inorganic materials 0.000 description 1

- 229910052691 Erbium Inorganic materials 0.000 description 1

- 229910052693 Europium Inorganic materials 0.000 description 1

- 229910052688 Gadolinium Inorganic materials 0.000 description 1

- 206010052128 Glare Diseases 0.000 description 1

- 239000005264 High molar mass liquid crystal Substances 0.000 description 1

- 229910052689 Holmium Inorganic materials 0.000 description 1

- 101000749291 Homo sapiens Dual specificity protein kinase CLK2 Proteins 0.000 description 1

- 101000749304 Homo sapiens Dual specificity protein kinase CLK3 Proteins 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- 229910052765 Lutetium Inorganic materials 0.000 description 1

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 1

- 239000004677 Nylon Substances 0.000 description 1

- 206010034972 Photosensitivity reaction Diseases 0.000 description 1

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004962 Polyamide-imide Substances 0.000 description 1

- 239000004743 Polypropylene Substances 0.000 description 1

- 229910052777 Praseodymium Inorganic materials 0.000 description 1

- 229910052772 Samarium Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- 229910002808 Si–O–Si Inorganic materials 0.000 description 1

- 239000004990 Smectic liquid crystal Substances 0.000 description 1

- 229910020833 Sn-Al-Zn Inorganic materials 0.000 description 1

- 229910020868 Sn-Ga-Zn Inorganic materials 0.000 description 1

- 229910020994 Sn-Zn Inorganic materials 0.000 description 1

- 229910009069 Sn—Zn Inorganic materials 0.000 description 1

- NINIDFKCEFEMDL-UHFFFAOYSA-N Sulfur Chemical compound [S] NINIDFKCEFEMDL-UHFFFAOYSA-N 0.000 description 1

- 238000003917 TEM image Methods 0.000 description 1

- 229910052771 Terbium Inorganic materials 0.000 description 1

- 239000004974 Thermotropic liquid crystal Substances 0.000 description 1

- 229910052775 Thulium Inorganic materials 0.000 description 1

- 229910052769 Ytterbium Inorganic materials 0.000 description 1

- YKTSYUJCYHOUJP-UHFFFAOYSA-N [O--].[Al+3].[Al+3].[O-][Si]([O-])([O-])[O-] Chemical compound [O--].[Al+3].[Al+3].[O-][Si]([O-])([O-])[O-] YKTSYUJCYHOUJP-UHFFFAOYSA-N 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 229920000122 acrylonitrile butadiene styrene Polymers 0.000 description 1

- 238000011276 addition treatment Methods 0.000 description 1

- 230000032683 aging Effects 0.000 description 1

- 125000000217 alkyl group Chemical group 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 125000003118 aryl group Chemical group 0.000 description 1

- 230000002238 attenuated effect Effects 0.000 description 1

- 230000003190 augmentative effect Effects 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 1

- 229910052790 beryllium Inorganic materials 0.000 description 1

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 1

- 239000011230 binding agent Substances 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 229910052795 boron group element Inorganic materials 0.000 description 1

- 239000005380 borophosphosilicate glass Substances 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- QHIWVLPBUQWDMQ-UHFFFAOYSA-N butyl prop-2-enoate;methyl 2-methylprop-2-enoate;prop-2-enoic acid Chemical compound OC(=O)C=C.COC(=O)C(C)=C.CCCCOC(=O)C=C QHIWVLPBUQWDMQ-UHFFFAOYSA-N 0.000 description 1

- 239000006229 carbon black Substances 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 239000002041 carbon nanotube Substances 0.000 description 1

- 229910021393 carbon nanotube Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000001913 cellulose Substances 0.000 description 1

- 229920002678 cellulose Polymers 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 150000001925 cycloalkenes Chemical class 0.000 description 1

- 238000007872 degassing Methods 0.000 description 1

- 230000001934 delay Effects 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000003795 desorption Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 229910003460 diamond Inorganic materials 0.000 description 1

- 239000010432 diamond Substances 0.000 description 1

- 229910001882 dioxygen Inorganic materials 0.000 description 1

- 239000004815 dispersion polymer Substances 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- KBQHZAAAGSGFKK-UHFFFAOYSA-N dysprosium atom Chemical compound [Dy] KBQHZAAAGSGFKK-UHFFFAOYSA-N 0.000 description 1

- 239000003792 electrolyte Substances 0.000 description 1

- 238000001962 electrophoresis Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- UYAHIZSMUZPPFV-UHFFFAOYSA-N erbium Chemical compound [Er] UYAHIZSMUZPPFV-UHFFFAOYSA-N 0.000 description 1

- 125000002573 ethenylidene group Chemical group [*]=C=C([H])[H] 0.000 description 1

- OGPBJKLSAFTDLK-UHFFFAOYSA-N europium atom Chemical compound [Eu] OGPBJKLSAFTDLK-UHFFFAOYSA-N 0.000 description 1

- 230000005284 excitation Effects 0.000 description 1

- 230000001747 exhibiting effect Effects 0.000 description 1

- 238000007687 exposure technique Methods 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 210000000744 eyelid Anatomy 0.000 description 1

- 238000011049 filling Methods 0.000 description 1

- 239000012530 fluid Substances 0.000 description 1

- UIWYJDYFSGRHKR-UHFFFAOYSA-N gadolinium atom Chemical compound [Gd] UIWYJDYFSGRHKR-UHFFFAOYSA-N 0.000 description 1

- 238000004868 gas analysis Methods 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 230000005283 ground state Effects 0.000 description 1

- 210000003128 head Anatomy 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- KJZYNXUDTRRSPN-UHFFFAOYSA-N holmium atom Chemical compound [Ho] KJZYNXUDTRRSPN-UHFFFAOYSA-N 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- RHZWSUVWRRXEJF-UHFFFAOYSA-N indium tin Chemical compound [In].[Sn] RHZWSUVWRRXEJF-UHFFFAOYSA-N 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- XEEYBQQBJWHFJM-UHFFFAOYSA-N iron Substances [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 229910052746 lanthanum Inorganic materials 0.000 description 1

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 230000007774 longterm Effects 0.000 description 1

- OHSVLFRHMCKCQY-UHFFFAOYSA-N lutetium atom Chemical compound [Lu] OHSVLFRHMCKCQY-UHFFFAOYSA-N 0.000 description 1

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 1

- 239000000395 magnesium oxide Substances 0.000 description 1

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 1

- 230000005389 magnetism Effects 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 229910021645 metal ion Inorganic materials 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 239000011156 metal matrix composite Substances 0.000 description 1

- 239000013081 microcrystal Substances 0.000 description 1

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 1

- 230000000116 mitigating effect Effects 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 239000002121 nanofiber Substances 0.000 description 1

- 239000002105 nanoparticle Substances 0.000 description 1

- 229910052754 neon Inorganic materials 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- 239000001272 nitrous oxide Substances 0.000 description 1

- 229920001778 nylon Polymers 0.000 description 1

- 238000007645 offset printing Methods 0.000 description 1

- 239000012788 optical film Substances 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- 230000035699 permeability Effects 0.000 description 1

- 238000001782 photodegradation Methods 0.000 description 1

- 230000036211 photosensitivity Effects 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 239000000049 pigment Substances 0.000 description 1

- 229910052696 pnictogen Inorganic materials 0.000 description 1

- 229920003229 poly(methyl methacrylate) Polymers 0.000 description 1

- 229920006350 polyacrylonitrile resin Polymers 0.000 description 1

- 229920002312 polyamide-imide Polymers 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229920001225 polyester resin Polymers 0.000 description 1

- 239000004645 polyester resin Substances 0.000 description 1

- 239000011112 polyethylene naphthalate Substances 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920001155 polypropylene Polymers 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920001296 polysiloxane Polymers 0.000 description 1

- 229920005990 polystyrene resin Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 229920005749 polyurethane resin Polymers 0.000 description 1

- 239000000843 powder Substances 0.000 description 1

- PUDIUYLPXJFUGB-UHFFFAOYSA-N praseodymium atom Chemical compound [Pr] PUDIUYLPXJFUGB-UHFFFAOYSA-N 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 239000000047 product Substances 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000002207 retinal effect Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- KZUNJOHGWZRPMI-UHFFFAOYSA-N samarium atom Chemical compound [Sm] KZUNJOHGWZRPMI-UHFFFAOYSA-N 0.000 description 1

- 238000005488 sandblasting Methods 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 230000035807 sensation Effects 0.000 description 1

- 230000008054 signal transmission Effects 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- BSWGGJHLVUUXTL-UHFFFAOYSA-N silver zinc Chemical compound [Zn].[Ag] BSWGGJHLVUUXTL-UHFFFAOYSA-N 0.000 description 1

- 238000009751 slip forming Methods 0.000 description 1

- 239000006104 solid solution Substances 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 239000007858 starting material Substances 0.000 description 1

- 125000001424 substituent group Chemical group 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 229910052717 sulfur Inorganic materials 0.000 description 1

- 239000011593 sulfur Substances 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- 230000002277 temperature effect Effects 0.000 description 1

- GZCRRIHWUXGPOV-UHFFFAOYSA-N terbium atom Chemical compound [Tb] GZCRRIHWUXGPOV-UHFFFAOYSA-N 0.000 description 1

- 238000007736 thin film deposition technique Methods 0.000 description 1

- 229930192474 thiophene Natural products 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- 239000011800 void material Substances 0.000 description 1

- 239000013585 weight reducing agent Substances 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

- NAWDYIZEMPQZHO-UHFFFAOYSA-N ytterbium Chemical compound [Yb] NAWDYIZEMPQZHO-UHFFFAOYSA-N 0.000 description 1

Images

Description

本明細書等で開示する発明の一態様は、物、方法、または、製造方法に関する。または、本明細書等で開示する発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物(コンポジション・オブ・マター)に関する。特に、表示装置および表示装置の作製方法に関する。 One aspect of the invention disclosed in the present specification and the like relates to a product, a method, or a manufacturing method. Alternatively, one aspect of the invention disclosed herein and the like relates to a process, machine, manufacture, or composition of matter. In particular, the present invention relates to a display device and a method for manufacturing the display device.

なお、本明細書等において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。表示装置(液晶表示装置、発光表示装置など)、投影装置、照明装置、電気光学装置、蓄電装置、記憶装置、半導体回路、撮像装置および電子機器などは、半導体装置と言える場合がある。もしくは、これらは半導体装置を有すると言える場合がある。 In the present specification and the like, the semiconductor device refers to all devices that can function by utilizing the semiconductor characteristics. Display devices (liquid crystal display devices, light emitting display devices, etc.), projection devices, lighting devices, electro-optical devices, power storage devices, storage devices, semiconductor circuits, image pickup devices, electronic devices, and the like may be said to be semiconductor devices. Alternatively, they may be said to have semiconductor devices.

液晶表示装置や発光表示装置に代表される表示装置において、軽量化、狭額縁化を達成するための手段の一つとして、画素回路と共に、駆動回路の少なくとも一部を同一基板上に作製することが知られている。更なる狭額縁化を達成するためには駆動回路の縮小が求められている。 In display devices typified by liquid crystal display devices and light emitting display devices, as one of the means for achieving weight reduction and narrowing of the frame, at least a part of the drive circuit is manufactured on the same substrate together with the pixel circuit. It has been known. In order to achieve a further narrowing of the frame, it is required to reduce the drive circuit.

また、特に据え置き型の表示装置では、画面サイズが対角30インチ以上と大型化する傾向にあり、対角60インチ以上さらには、対角120インチ以上の画面サイズも視野に入れた開発が行われている。加えて、画面の解像度も、フルハイビジョン(画素数1920×1080、または「2K」などとも言われる。)、ウルトラハイビジョン(画素数3840×2160、または「4K」などとも言われる。)、スーパーハイビジョン(画素数7680×4320、または「8K」などとも言われる。)と高精細化の傾向にある。 In addition, especially for stationary display devices, the screen size tends to increase to 30 inches or more diagonally, and development is being carried out with a view to screen sizes of 60 inches or more diagonally and 120 inches or more diagonally. It has been. In addition, the screen resolution is also full high definition (also referred to as 1920 × 1080 pixels or “2K”), ultra high definition (also referred to as 3840 × 2160 pixels or “4K”), super high definition. (The number of pixels is 7680 x 4320, or it is also called "8K".) There is a tendency for higher definition.

駆動回路はCMOS(Complementary Metal Oxide Semiconductor)回路で構成することが一般的である。一方で、生産性の向上や狭額縁化を実現するため、nチャネル型トランジスタのみ、またはpチャネル型トランジスタのみで構成する駆動回路も検討されている。このような構成の回路を「単極性回路」ともいう。例えば、特許文献1では、シフトレジスタを単極性回路で構成する技術が開示されている。

The drive circuit is generally composed of a CMOS (Complementary Metal Oxide Sensor) circuit. On the other hand, in order to improve productivity and narrow the frame, a drive circuit composed of only n-channel transistors or only p-channel transistors is also being studied. A circuit having such a configuration is also referred to as a "unipolar circuit". For example,

また、トランジスタに適用可能な半導体材料として金属酸化物が注目されている。金属酸化物の中には半導体特性を示すものがある。例えば、酸化亜鉛、またはIn−Ga−Zn系酸化物などの金属酸化物を用いてトランジスタを作製する技術が特許文献2に開示されている。

Further, metal oxides are attracting attention as semiconductor materials applicable to transistors. Some metal oxides exhibit semiconductor properties. For example,

本発明の一態様は、狭額縁の表示装置を提供することを課題の一つとする。または、表示品位が良好な表示装置を提供することを課題の一つとする。または、消費電力の少ない表示装置を提供することを課題の一とする。または、生産性の良好な表示装置を提供することを課題の一とする。または、信頼性が良好な表示装置を提供することを課題の一つとする。または、新規な表示装置を提供することを課題の一つとする。または、上記表示装置を備えた電子機器を提供することを課題の一つとする。または、新規な電子機器を提供することを課題の一つとする。 One aspect of the present invention is to provide a display device having a narrow frame. Alternatively, one of the issues is to provide a display device having good display quality. Another issue is to provide a display device with low power consumption. Alternatively, one of the issues is to provide a display device having good productivity. Alternatively, one of the issues is to provide a display device having good reliability. Alternatively, one of the issues is to provide a new display device. Alternatively, one of the issues is to provide an electronic device equipped with the above display device. Alternatively, one of the issues is to provide new electronic devices.

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。 The description of these issues does not prevent the existence of other issues. It should be noted that one aspect of the present invention does not need to solve all of these problems. It should be noted that the problems other than these are naturally clarified from the description of the description, drawings, claims, etc., and it is possible to extract the problems other than these from the description of the description, drawings, claims, etc. Is.

本発明の一態様は、複数の画素を有する表示部と、駆動回路部と、を有し、複数の画素それぞれは、表示素子と、第1のトランジスタと、を有し、駆動回路部は、第2のトランジスタと、第3のトランジスタと、第1の層と、を有し、第2のトランジスタは、第1のトランジスタと電気的に接続され、第3のトランジスタは、第2のトランジスタと電気的に接続され、第2のトランジスタの半導体層および第3のトランジスタの半導体層は、それぞれが、金属元素および酸素を含み、第2のトランジスタの半導体層は、第1の層と重なる領域を有し、第1の層の熱伝導率が0.05W/(m・K)以上0.5W/(m・K)以下であることを特徴とする表示装置である。 One aspect of the present invention includes a display unit having a plurality of pixels and a drive circuit unit, each of the plurality of pixels having a display element and a first transistor, and the drive circuit unit includes a display element and a first transistor. It has a second transistor, a third transistor, and a first layer, the second transistor is electrically connected to the first transistor, and the third transistor is connected to the second transistor. Electrically connected, the semiconductor layer of the second transistor and the semiconductor layer of the third transistor each contain a metal element and oxygen, and the semiconductor layer of the second transistor has a region overlapping the first layer. It is a display device having a thermal conductivity of 0.05 W / (m · K) or more and 0.5 W / (m · K) or less of the first layer.

また、本発明の別の一態様は、複数の画素を有する表示部と、駆動回路部と、を有し、複数の画素それぞれは、表示素子と、第1のトランジスタと、を有し、駆動回路部は、第2のトランジスタと、第3のトランジスタと、容量素子と、第1の層と、を有し、第2のトランジスタのソースまたはドレインの一方は、第1のトランジスタのゲートと電気的に接続され、第3のトランジスタのソースまたはドレインの一方は、第2のトランジスタのゲートと電気的に接続され、容量素子の一方の電極は、第2のトランジスタのゲートと電気的に接続され、容量素子の他方の電極は、第2のトランジスタのソースまたはドレインの一方と電気的に接続され、第2のトランジスタの半導体層および第3のトランジスタの半導体層は、それぞれが、金属元素および酸素を含み、第2のトランジスタの半導体層は、第1の層と重なる領域を有し、第1の層の熱伝導率が0.05W/(m・K)以上0.5W/(m・K)以下であることを特徴とする表示装置である。 Further, another aspect of the present invention includes a display unit having a plurality of pixels and a drive circuit unit, and each of the plurality of pixels has a display element and a first transistor and is driven. The circuit unit has a second transistor, a third transistor, a capacitive element, and a first layer, and one of the source and drain of the second transistor is the gate and electricity of the first transistor. One of the source or drain of the third transistor is electrically connected to the gate of the second transistor, and one electrode of the capacitive element is electrically connected to the gate of the second transistor. The other electrode of the capacitive element is electrically connected to one of the source or drain of the second transistor, and the semiconductor layer of the second transistor and the semiconductor layer of the third transistor are metal elements and oxygen, respectively. The semiconductor layer of the second transistor has a region overlapping with the first layer, and the thermal conductivity of the first layer is 0.05 W / (m · K) or more and 0.5 W / (m · K) or more. ) It is a display device characterized by the following.

また、本発明の別の一態様は、複数の画素を有する表示部と、駆動回路部と、を有し、複数の画素それぞれは、表示素子と、第1のトランジスタと、を有し、駆動回路部は、第2のトランジスタと、第3のトランジスタと、第1の層と、第2の層と、を有し、第2のトランジスタは、第1のトランジスタと電気的に接続され、第3のトランジスタは、第2のトランジスタと電気的に接続され、第2のトランジスタの半導体層および第3のトランジスタの半導体層は、それぞれが、金属元素および酸素を含み、第2のトランジスタの半導体層は、第1の層および第2の層と重なる領域を有し、第3のトランジスタの半導体層は、第1の層と重ならず、かつ、第2の層と重なる領域を有し、第1の層の熱伝導率は、第2の層の熱伝導率よりも小さいことを特徴とする表示装置である。 Further, another aspect of the present invention includes a display unit having a plurality of pixels and a drive circuit unit, and each of the plurality of pixels has a display element and a first transistor and is driven. The circuit unit has a second transistor, a third transistor, a first layer, and a second layer, and the second transistor is electrically connected to the first transistor and has a second layer. The third transistor is electrically connected to the second transistor, and the semiconductor layer of the second transistor and the semiconductor layer of the third transistor each contain a metal element and oxygen, and the semiconductor layer of the second transistor is contained. Has a region that overlaps with the first layer and the second layer, and the semiconductor layer of the third transistor has a region that does not overlap with the first layer and overlaps with the second layer. The display device is characterized in that the thermal conductivity of the first layer is smaller than the thermal conductivity of the second layer.

また、本発明の別の一態様は、複数の画素を有する表示部と、駆動回路部と、を有し、複数の画素それぞれは、表示素子と、第1のトランジスタと、を有し、駆動回路部は、第2のトランジスタと、第3のトランジスタと、容量素子と、第1の層と、第2の層と、を有し、第2のトランジスタのソースまたはドレインの一方は、第1のトランジスタのゲートと電気的に接続され、第3のトランジスタのソースまたはドレインの一方は、第2のトランジスタのゲートと電気的に接続され、容量素子の一方の電極は、第2のトランジスタのゲートと電気的に接続され、容量素子の他方の電極は、第2のトランジスタのソースまたはドレインの一方と電気的に接続され、第2のトランジスタの半導体層および第3のトランジスタの半導体層は、それぞれが、金属元素および酸素を含み、第2のトランジスタの半導体層は、第1の層および第2の層と重なる領域を有し、第3のトランジスタの半導体層は、第1の層と重ならず、かつ、第2の層と重なる領域を有し、第1の層の熱伝導率は、第2の層の熱伝導率よりも小さいことを特徴とする表示装置である。 Further, another aspect of the present invention includes a display unit having a plurality of pixels and a drive circuit unit, and each of the plurality of pixels has a display element and a first transistor and is driven. The circuit unit has a second transistor, a third transistor, a capacitive element, a first layer, and a second layer, and one of the source and drain of the second transistor is the first. One electrode of the capacitive element is electrically connected to the gate of the second transistor, and one of the source or drain of the third transistor is electrically connected to the gate of the second transistor. The other electrode of the capacitive element is electrically connected to one of the source or drain of the second transistor, and the semiconductor layer of the second transistor and the semiconductor layer of the third transistor are respectively. However, if it contains a metal element and oxygen, the semiconductor layer of the second transistor has a region overlapping the first layer and the second layer, and the semiconductor layer of the third transistor overlaps the first layer. The display device is characterized in that it has a region overlapping with the second layer, and the thermal conductivity of the first layer is smaller than the thermal conductivity of the second layer.

第1の層の厚さは、0.01μm以上5.0μm以下、好ましくは0.01μm以上2.0μm以下とすればよい。 The thickness of the first layer may be 0.01 μm or more and 5.0 μm or less, preferably 0.01 μm or more and 2.0 μm or less.

第1の層は蓄熱層として機能する。例えば、第1の層として、アクリル樹脂、エポキシ樹脂、フェノール樹脂、シリコーン樹脂、ポリイミド、ポリカーボネイト、またはポリスチレンなどの樹脂材料などを用いることができる。 The first layer functions as a heat storage layer. For example, as the first layer, a resin material such as an acrylic resin, an epoxy resin, a phenol resin, a silicone resin, a polyimide, a polycarbonate, or polystyrene can be used.

また、上記金属元素は、インジウム、ガリウム、または亜鉛の少なくとも一であることが好ましい。上記半導体層は、金属酸化物の一種である酸化物半導体であることが好ましい。 Further, the metal element is preferably at least one of indium, gallium, or zinc. The semiconductor layer is preferably an oxide semiconductor which is a kind of metal oxide.

本発明の一態様によれば、狭額縁の表示装置を提供することができる。または、表示品位が良好な表示装置を提供することができる。または、消費電力の少ない表示装置を提供することができる。または、生産性の良好な表示装置を提供することができる。または、信頼性が良好な表示装置を提供することができる。または、新規な表示装置を提供することができる。または、上記表示装置を備えた電子機器を提供することができる。または、新規な電子機器を提供することができる。 According to one aspect of the present invention, it is possible to provide a display device having a narrow frame. Alternatively, it is possible to provide a display device having good display quality. Alternatively, it is possible to provide a display device with low power consumption. Alternatively, it is possible to provide a display device having good productivity. Alternatively, it is possible to provide a display device having good reliability. Alternatively, a new display device can be provided. Alternatively, an electronic device provided with the above display device can be provided. Alternatively, a new electronic device can be provided.

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。 The description of these effects does not preclude the existence of other effects. It should be noted that one aspect of the present invention does not have to have all of these effects. It should be noted that the effects other than these are naturally clarified from the description of the description, drawings, claims, etc., and it is possible to extract the effects other than these from the description of the description, drawings, claims, etc. Is.

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する場合がある。 The embodiment will be described in detail with reference to the drawings. However, the present invention is not limited to the following description, and it is easily understood by those skilled in the art that the form and details thereof can be variously changed without departing from the spirit and scope of the present invention. Therefore, the present invention is not construed as being limited to the description of the embodiments shown below. In the configuration of the invention described below, the same reference numerals may be used in common between different drawings for the same parts or parts having similar functions, and the repeated description thereof may be omitted.

また、図面などにおいて示す各構成の、位置、大きさ、範囲などは、発明の理解を容易とするため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面などに開示された位置、大きさ、範囲などに限定されない。例えば、実際の製造工程において、エッチングなどの処理により層やレジストマスクなどが意図せずに目減りすることがあるが、発明の理解を容易とするため、省略して示すことがある。 In addition, the position, size, range, etc. of each configuration shown in the drawings may not represent the actual position, size, range, etc. in order to facilitate understanding of the invention. Therefore, the disclosed invention is not necessarily limited to the position, size, range, etc. disclosed in the drawings and the like. For example, in an actual manufacturing process, layers, resist masks, and the like may be unintentionally reduced due to processing such as etching, but they may be omitted for the sake of easy understanding of the invention.

また、特に上面図(「平面図」ともいう。)や斜視図などにおいて、発明の理解を容易とするため、一部の構成要素の記載を省略する場合がある。また、一部の隠れ線などの記載を省略する場合がある。 Further, in order to facilitate understanding of the invention, in particular, in a top view (also referred to as a “plan view”) or a perspective view, the description of some components may be omitted. In addition, some hidden lines may be omitted.

本明細書等において、「第1」、「第2」などの序数詞は、構成要素の混同を避けるために付すものであり、工程順または積層順など、なんらかの順番や順位を示すものではない。また、本明細書等において序数詞が付されていない用語であっても、構成要素の混同を避けるため、特許請求の範囲において序数詞が付される場合がある。また、本明細書等において付された序数詞と、特許請求の範囲において付された序数詞が異なる場合がある。また、本明細書等において序数詞が付されている用語であっても、特許請求の範囲などにおいて序数詞を省略する場合がある。 In the present specification and the like, ordinal numbers such as "first" and "second" are added to avoid confusion of components, and do not indicate any order or order such as process order or stacking order. In addition, even terms that do not have ordinal numbers in the present specification and the like may have ordinal numbers within the scope of claims in order to avoid confusion of components. In addition, the ordinal numbers given in the present specification and the like may differ from the ordinal numbers given in the claims. Further, even if the terms have ordinal numbers in the present specification and the like, the ordinal numbers may be omitted in the scope of claims.

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって設けられている場合なども含む。 Further, in the present specification and the like, the terms "electrode" and "wiring" do not functionally limit these components. For example, an "electrode" may be used as part of a "wiring" and vice versa. Further, the terms "electrode" and "wiring" include the case where a plurality of "electrodes" and "wiring" are integrally provided.

なお、チャネル長とは、例えば、トランジスタの上面図において、半導体(またはトランジスタがオン状態のときに半導体の中で電流の流れる部分)とゲート電極とが互いに重なる領域、またはチャネルが形成される領域(「チャネル形成領域」ともいう。)における、ソース(ソース領域またはソース電極)とドレイン(ドレイン領域またはドレイン電極)との間の距離をいう。なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル長は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。 The channel length is, for example, a region in which a semiconductor (or a portion in which a current flows in the semiconductor when the transistor is on) and a gate electrode overlap each other in a top view of a transistor, or a region in which a channel is formed. The distance between the source (source region or source electrode) and the drain (drain region or drain electrode) in (also referred to as “channel forming region”). In one transistor, the channel length does not always take the same value in all regions. That is, the channel length of one transistor may not be fixed to one value. Therefore, in the present specification, the channel length is set to any one value, the maximum value, the minimum value, or the average value in the region where the channel is formed.

チャネル幅とは、例えば、半導体(またはトランジスタがオン状態のときに半導体の中で電流の流れる部分)とゲート電極とが互いに重なる領域、またはチャネルが形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。なお、一つのトランジスタにおいて、チャネル幅がすべての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル幅は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。 The channel width is, for example, the source and the drain facing each other in the region where the semiconductor (or the part where the current flows in the semiconductor when the transistor is on) and the gate electrode overlap each other, or the region where the channel is formed. The length of the part that is being used. In one transistor, the channel width does not always take the same value in all regions. That is, the channel width of one transistor may not be fixed to one value. Therefore, in the present specification, the channel width is set to any one value, the maximum value, the minimum value, or the average value in the region where the channel is formed.

なお、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネル幅(以下、「実効的なチャネル幅」ともいう。)と、トランジスタの上面図において示されるチャネル幅(以下、「見かけ上のチャネル幅」ともいう。)と、が異なる場合がある。例えば、ゲート電極が半導体層の側面を覆う場合、実効的なチャネル幅が、見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつゲート電極が半導体の側面を覆うトランジスタでは、半導体の側面に形成されるチャネル形成領域の割合が大きくなる場合がある。その場合は、見かけ上のチャネル幅よりも、実効的なチャネル幅の方が大きくなる。 Depending on the structure of the transistor, the channel width in the region where the channel is actually formed (hereinafter, also referred to as “effective channel width”) and the channel width shown in the top view of the transistor (hereinafter, “apparently”). (Also called the channel width of)) and may be different. For example, when the gate electrode covers the side surface of the semiconductor layer, the effective channel width may be larger than the apparent channel width, and the influence thereof may not be negligible. For example, in a transistor that is fine and has a gate electrode covering the side surface of the semiconductor, the proportion of the channel forming region formed on the side surface of the semiconductor may be large. In that case, the effective channel width is larger than the apparent channel width.

このような場合、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるためには、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。 In such a case, it may be difficult to estimate the effective channel width by actual measurement. For example, in order to estimate the effective channel width from the design value, it is necessary to assume that the shape of the semiconductor is known. Therefore, if the shape of the semiconductor is not known accurately, it is difficult to accurately measure the effective channel width.

そこで、本明細書では、見かけ上のチャネル幅を、「囲い込みチャネル幅(SCW:Surrounded Channel Width)」と呼ぶ場合がある。また、本明細書では、単にチャネル幅と記載した場合には、囲い込みチャネル幅または見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅、囲い込みチャネル幅などは、断面TEM像などを解析することなどによって、値を決定することができる。 Therefore, in the present specification, the apparent channel width may be referred to as "surrounded channel width (SCW)". Further, in the present specification, when simply referred to as a channel width, it may refer to an enclosed channel width or an apparent channel width. Alternatively, in the present specification, the term "channel width" may refer to an effective channel width. The values of the channel length, channel width, effective channel width, apparent channel width, enclosed channel width, and the like can be determined by analyzing a cross-sectional TEM image or the like.

なお、トランジスタの電界効果移動度や、チャネル幅当たりの電流値などを計算して求める場合、囲い込みチャネル幅を用いて計算する場合がある。その場合には、実効的なチャネル幅を用いて計算する場合とは異なる値をとる場合がある。 When calculating the electric field effect mobility of a transistor, the current value per channel width, or the like, the enclosed channel width may be used for calculation. In that case, the value may be different from that calculated using the effective channel width.

また、本明細書等において、フォトリソグラフィ法によりレジストマスクを形成し、その後にエッチング工程(除去工程)を行う場合は、特段の説明がない限り、当該レジストマスクは、エッチング工程終了後に除去するものとする。 Further, in the present specification and the like, when a resist mask is formed by a photolithography method and then an etching step (removal step) is performed, the resist mask is removed after the etching step is completed unless otherwise specified. And.

なお、「膜」という言葉と、「層」という言葉とは、場合によっては、または、状況に応じて、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。 The word "membrane" and the word "layer" can be interchanged with each other in some cases or depending on the situation. For example, it may be possible to change the term "conductive layer" to the term "conductive layer". Alternatively, for example, it may be possible to change the term "insulating film" to the term "insulating layer".

また、本明細書等において、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子である。そして、ドレイン(ドレイン端子、ドレイン領域またはドレイン電極)とソース(ソース端子、ソース領域またはソース電極)の間にチャネル領域を有しており、チャネル形成領域を介して、ソースとドレインとの間に電流を流すことができるものである。なお、本明細書等において、チャネル領域とは、電流が主として流れる領域をいう。 Further, in the present specification and the like, a transistor is an element having at least three terminals including a gate, a drain, and a source. Then, a channel region is provided between the drain (drain terminal, drain region or drain electrode) and the source (source terminal, source region or source electrode), and between the source and drain via the channel forming region. It is capable of passing an electric current. In the present specification and the like, the channel region refers to a region in which a current mainly flows.

また、本明細書等に示すトランジスタは、特に断りがない場合、エンハンスメント型(ノーマリーオフ型)の電界効果トランジスタとする。また、本明細書等に示すトランジスタは、特に断りがない場合、nチャネル型のトランジスタとする。よって、そのしきい値電圧(「Vth」ともいう。)は、特に断りがない場合、0Vよりも大きいものとする。 Further, the transistor shown in the present specification and the like shall be an enhancement type (normally off type) field effect transistor unless otherwise specified. Further, the transistor shown in the present specification and the like shall be an n-channel type transistor unless otherwise specified. Therefore, the threshold voltage (also referred to as “Vth”) is assumed to be larger than 0V unless otherwise specified.

なお、本明細書等において、バックゲートを有するトランジスタのVthとは、特に断りがない場合、バックゲートの電位をソースまたはゲートと同電位としたときのVthをいう。 In the present specification and the like, the Vth of a transistor having a back gate means the Vth when the potential of the back gate is the same as that of the source or the gate, unless otherwise specified.

また、本明細書等において、特に断りがない場合、オフ電流とは、トランジスタがオフ状態(非導通状態、遮断状態、ともいう)にあるときのドレイン電流(「Id」ともいう。)をいう。オフ状態とは、特に断りがない場合、nチャネル型トランジスタでは、ソースを基準とした時のゲートとソースの間の電位差(「ゲート電圧」または「Vg」ともいう。)がしきい値電圧よりも低い状態、pチャネル型トランジスタでは、Vgがしきい値電圧よりも高い状態をいう。例えば、nチャネル型のトランジスタのオフ電流とは、VgがVthよりも低いときのドレイン電流を言う場合がある。 Further, in the present specification and the like, unless otherwise specified, the off current means a drain current (also referred to as “Id”) when the transistor is in an off state (also referred to as a non-conducting state or a cutoff state). .. Unless otherwise specified, the off state means that in an n-channel transistor, the potential difference between the gate and the source (also referred to as “gate voltage” or “Vg”) with respect to the source is greater than the threshold voltage. In the case of a p-channel transistor, Vg is higher than the threshold voltage. For example, the off-current of an n-channel transistor may refer to the drain current when Vg is lower than Vth.

トランジスタのオフ電流は、Vgに依存する場合がある。従って、トランジスタのオフ電流がI以下である、とは、トランジスタのオフ電流がI以下となるVgの値が存在することを言う場合がある。トランジスタのオフ電流は、所定のVgにおけるオフ状態、所定の範囲内のVgにおけるオフ状態、または、十分に低減されたオフ電流が得られるVgにおけるオフ状態、等におけるオフ電流を指す場合がある。 The off current of the transistor may depend on Vg. Therefore, the fact that the off-current of the transistor is I or less may mean that there is a value of Vg in which the off-current of the transistor is I or less. The off-current of a transistor may refer to an off-current in a predetermined Vg, an off-state in a Vg within a predetermined range, an off-state in a Vg in which a sufficiently reduced off-current can be obtained, and the like.

一例として、Vthが0.5Vであり、Vgが0.5Vにおけるドレイン電流が1×10−9Aであり、Vgが0.1Vにおけるドレイン電流が1×10−13Aであり、Vgが−0.5Vにおけるドレイン電流が1×10−19Aであり、Vgが−0.8Vにおけるドレイン電流が1×10−22Aであるようなnチャネル型トランジスタを想定する。当該トランジスタのドレイン電流は、Vgが−0.5Vにおいて、または、Vgが−0.5V乃至−0.8Vの範囲において、1×10−19A以下であるから、当該トランジスタのオフ電流は1×10−19A以下である、と言う場合がある。当該トランジスタのドレイン電流が1×10−22A以下となるVgが存在するため、当該トランジスタのオフ電流は1×10−22A以下である、と言う場合がある。 As an example, when Vth is 0.5V and Vg is 0.5V, the drain current is 1 × 10 -9 A, when Vg is 0.1V, the drain current is 1 × 10 -13 A, and Vg is −. Assume an n-channel transistor having a drain current of 1 × 10 -19 A at 0.5 V and a drain current of 1 × 10 -22 A at Vg of −0.8 V. Since the drain current of the transistor is 1 × 10 -19 A or less when Vg is −0.5 V or Vg is in the range of −0.5 V to −0.8 V, the off current of the transistor is 1. It may be said that it is × 10-19 A or less. Since there is Vg in which the drain current of the transistor is 1 × 10-22 A or less, it may be said that the off current of the transistor is 1 × 10-22 A or less.

トランジスタのオフ電流は、温度に依存する場合がある。本明細書において、オフ電流は、特に記載がない場合、室温(RT:Room Temperature)、60℃、85℃、95℃、または125℃におけるオフ電流を表す場合がある。または、当該トランジスタが含まれる半導体装置等の信頼性が保証される温度、または、当該トランジスタが含まれる半導体装置等が使用される温度(例えば、5℃以上35℃以下の温度)におけるオフ電流、を表す場合がある。トランジスタのオフ電流がI以下である、とは、RT、60℃、85℃、95℃、125℃、当該トランジスタが含まれる半導体装置の信頼性が保証される温度、または、当該トランジスタが含まれる半導体装置等が使用される温度(例えば、5℃以上35℃以下の温度)、におけるトランジスタのオフ電流がI以下となるVgの値が存在することを指す場合がある。 The off current of the transistor may depend on the temperature. In the present specification, the off-current may represent an off-current at room temperature (RT: Room Temperature), 60 ° C., 85 ° C., 95 ° C., or 125 ° C., unless otherwise specified. Alternatively, an off-current at a temperature at which the reliability of the semiconductor device or the like containing the transistor is guaranteed, or a temperature at which the semiconductor device or the like containing the transistor is used (for example, a temperature of 5 ° C. or higher and 35 ° C. or lower). May represent. The off-current of a transistor is I or less, which means RT, 60 ° C., 85 ° C., 95 ° C., 125 ° C., a temperature at which the reliability of the semiconductor device including the transistor is guaranteed, or the transistor is included. It may indicate that there is a value of Vg at which the off current of the transistor is I or less at the temperature at which the semiconductor device or the like is used (for example, the temperature of 5 ° C. or higher and 35 ° C. or lower).

トランジスタのオフ電流は、ソースを基準とした時のドレインとソースの間の電圧(以下、「Vd」ともいう。)に依存する場合がある。本明細書において、オフ電流は、特に記載がない場合、Vdが0.1V、0.8V、1V、1.2V、1.8V、2.5V、3V、3.3V、10V、12V、16V、または20Vにおけるオフ電流を表す場合がある。または、当該トランジスタが含まれる半導体装置等の信頼性が保証されるVd、または、当該トランジスタが含まれる半導体装置等において使用されるVdにおけるオフ電流、を表す場合がある。トランジスタのオフ電流がI以下である、とは、Vdが0.1V、0.8V、1V、1.2V、1.8V、2.5V、3V、3.3V、10V、12V、16V、20V、当該トランジスタが含まれる半導体装置の信頼性が保証されるVd、または、当該トランジスタが含まれる半導体装置等において使用されるVd、におけるトランジスタのオフ電流がI以下となるVgの値が存在することを指す場合がある。 The off-current of the transistor may depend on the voltage between the drain and the source (hereinafter, also referred to as “Vd”) with respect to the source. In the present specification, the off current has Vd of 0.1V, 0.8V, 1V, 1.2V, 1.8V, 2.5V, 3V, 3.3V, 10V, 12V, 16V unless otherwise specified. , Or may represent off-current at 20V. Alternatively, it may represent Vd in which the reliability of the semiconductor device or the like including the transistor is guaranteed, or the off-current in Vd used in the semiconductor device or the like including the transistor. When the off current of the transistor is I or less, Vd is 0.1V, 0.8V, 1V, 1.2V, 1.8V, 2.5V, 3V, 3.3V, 10V, 12V, 16V, 20V. , Vd in which the reliability of the semiconductor device including the transistor is guaranteed, or Vd used in the semiconductor device including the transistor, and the value of Vg in which the off current of the transistor is I or less exists. May point to.

上記オフ電流の説明において、ドレインをソースと読み替えてもよい。つまり、オフ電流は、トランジスタがオフ状態にあるときのソースを流れる電流を言う場合もある。 In the above description of the off-current, the drain may be read as the source. That is, the off-current may refer to the current flowing through the source when the transistor is in the off state.

また、本明細書等では、オフ電流と同じ意味で、リーク電流と記載する場合がある。また、本明細書等において、オフ電流とは、例えば、トランジスタがオフ状態にあるときに、ソースとドレインとの間に流れる電流を指す場合がある。 Further, in the present specification and the like, it may be described as a leak current in the same meaning as an off current. Further, in the present specification and the like, the off current may refer to, for example, the current flowing between the source and the drain when the transistor is in the off state.

また、本明細書等において、高電源電位VDD(以下、単に「VDD」または「H電位」ともいう。)とは、低電源電位VSSよりも高い電位の電源電位を示す。また、低電源電位VSS(以下、単に「VSS」または「L電位」ともいう。)とは、高電源電位VDDよりも低い電位の電源電位を示す。また、接地電位をVDDまたはVSSとして用いることもできる。例えばVDDが接地電位の場合には、VSSは接地電位より低い電位であり、VSSが接地電位の場合には、VDDは接地電位より高い電位である。 Further, in the present specification and the like, the high power supply potential VDD (hereinafter, also simply referred to as “VDD” or “H potential”) indicates a power supply potential having a potential higher than that of the low power supply potential VSS. Further, the low power supply potential VSS (hereinafter, also simply referred to as “VSS” or “L potential”) indicates a power supply potential having a potential lower than that of the high power supply potential VDD. The ground potential can also be used as VDD or VSS. For example, when VDD is the ground potential, VSS is a potential lower than the ground potential, and when VSS is the ground potential, VDD is a potential higher than the ground potential.

また、一般に「電圧」とは、ある電位と基準の電位(例えば、接地電位(GND電位)またはソース電位など)との電位差のことを示す場合が多い。また、「電位」は相対的なものであり、基準となる電位によって配線等に与える電位が変化する場合がある。よって「電圧」と「電位」は互いに言い換えることが可能な場合がある。なお、本明細書等では、明示される場合を除き、VSSを基準の電位とする。 Further, in general, the "voltage" often indicates a potential difference between a certain potential and a reference potential (for example, a ground potential (GND potential) or a source potential). Further, the "potential" is relative, and the potential given to the wiring or the like may change depending on the reference potential. Therefore, "voltage" and "potential" may be paraphrased with each other. In this specification and the like, VSS is used as a reference potential unless otherwise specified.

なお、本明細書等において「上」や「下」の用語は、構成要素の位置関係が直上または直下で、かつ、直接接していることを限定するものではない。例えば、「絶縁層A上の電極B」の表現であれば、絶縁層Aの上に電極Bが直接接して設けられている必要はなく、絶縁層Aと電極Bとの間に他の構成要素を含むものを除外しない。 In addition, the terms "upper" and "lower" in the present specification and the like do not limit the positional relationship of the components to be directly above or directly below and to be in direct contact with each other. For example, in the case of the expression "electrode B on the insulating layer A", it is not necessary that the electrode B is provided in direct contact with the insulating layer A, and another configuration is provided between the insulating layer A and the electrode B. Do not exclude those that contain elements.

また、本明細書において、「平行」とは、明示されている場合を除き、二つの直線が−10°以上10°以下の角度で配置されている状態をいう。従って、−5°以上5°以下の場合も含まれる。また、「略平行」とは、明示されている場合を除き、二つの直線が−30°以上30°以下の角度で配置されている状態をいう。また、「垂直」および「直交」とは、明示されている場合を除き、二つの直線が80°以上100°以下の角度で配置されている状態をいう。従って、85°以上95°以下の場合も含まれる。また、「略垂直」とは、明示されている場合を除き、二つの直線が60°以上120°以下の角度で配置されている状態をいう。 Further, in the present specification, "parallel" means a state in which two straight lines are arranged at an angle of −10 ° or more and 10 ° or less, unless otherwise specified. Therefore, the case of −5 ° or more and 5 ° or less is also included. Further, "substantially parallel" means a state in which two straight lines are arranged at an angle of -30 ° or more and 30 ° or less, unless otherwise specified. Further, "vertical" and "orthogonal" mean a state in which two straight lines are arranged at an angle of 80 ° or more and 100 ° or less, unless otherwise specified. Therefore, the case of 85 ° or more and 95 ° or less is also included. Further, "substantially vertical" means a state in which two straight lines are arranged at an angle of 60 ° or more and 120 ° or less, unless otherwise specified.

なお、本明細書等において、計数値および計量値に関して「同一」、「同じ」、「等しい」または「均一」(これらの同意語を含む)などと言う場合は、明示されている場合を除き、プラスマイナス20%の誤差を含むものとする。 In the present specification and the like, when the count value and the measured value are referred to as "same", "same", "equal" or "uniform" (including synonyms thereof), unless otherwise specified. , Plus or minus 20% error shall be included.

(実施の形態1)

本実施の形態では、本発明の一態様の表示装置100について、図面を用いて説明する。

(Embodiment 1)

In the present embodiment, the

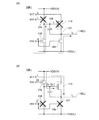

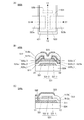

<表示装置の構成例>

図1(A)は、FPC145(Flexible printed circuit)が接続された表示装置100の正面図である。図1(B)は、表示装置100の構成を説明するブロック図である。図2および図3は、ともに、図1(A)にA1−A2の一点鎖線で示す部位に相当する断面概略図である。図2および図3は、駆動回路部104aの一部と、表示部102の一部を示している。また、図2は表示素子として液晶素子を用いる液晶表示装置の一例を示している。図2に示す表示装置100は、FFS(Fringe Field Switching)モードで動作する液晶素子を例示している。また、図3は表示素子として発光素子を用いる発光表示装置の一例を示している。

<Display device configuration example>

FIG. 1A is a front view of a

表示装置100は、表示部102、駆動回路部104a、駆動回路部104b、および駆動回路部103を有する。駆動回路部104aおよび駆動回路部104bは、例えば走査線駆動回路として機能できる。また、駆動回路部103は、例えば信号線駆動回路として機能できる。なお、駆動回路部104a、および駆動回路部104bは、どちらか一方のみを設けて、他方を設けなくてもよい。また、表示部102を挟んで駆動回路部103と向き合う位置に、何らかの回路を設けてもよい。

The

なお、駆動回路部104a、駆動回路部104b、および駆動回路部103の総称として、「駆動回路」、「周辺回路」または「周辺駆動回路」という場合がある。

The

また、表示装置100は、各々が略平行に配設され、且つ、駆動回路部104a、および/または駆動回路部104bによって電位が制御されるn本(nは2以上の整数)の配線162と、各々が略平行に配設され、且つ、駆動回路部103によって電位が制御されるm本(mは2以上の整数)の配線163と、を有する。さらに、表示部102はn行m列のマトリクス状に配設された複数の画素110を有する。画素110は、画素回路および表示素子を有する。

Further, the

i行目(iは1以上n以下の整数)に配置された複数の画素110は、i本目の配線162と電気的に接続される。j列目(jは1以上m以下の整数)に配置された複数の画素110は、j本目の配線163と電気的に接続される。なお、本明細書等では、i本目の配線162を配線162_iと記す。また、本明細書等では、j本目の配線163を配線163_jと記す。

The plurality of

表示部102、駆動回路部104a、駆動回路部104b、および駆動回路部103は、第1の基板101上に設けられている。また、表示部102、駆動回路部104a、および駆動回路部104bを囲むようにして、シール材4005が設けられている。また、表示部102、駆動回路部104a、および駆動回路部104bの上に第2の基板106が設けられている。よって表示部102、駆動回路部104a、および駆動回路部104bは、第1の基板101とシール材105と第2の基板106とによって、表示素子と共に封止されている。

The

また、駆動回路部103は、別途用意された基板上に単結晶半導体または多結晶半導体で形成されている。駆動回路部103は、第1の基板101上のシール材105によって囲まれている領域とは異なる領域に実装されている。表示部102、駆動回路部104a、駆動回路部104b、および駆動回路部103に与えられる各種信号および電位は、FPC145から供給されている。

Further, the

なお、駆動回路部103の接続方法は、特に限定されるものではなく、ワイヤボンディング、COG(Chip On Glass)法、TCP(Tape Carrier Package)法、COF(Chip On Film)法などを用いることができる。図1(A)は、COG法により駆動回路部103を実装する例である。

The connection method of the

また、本明細書などにおいて、表示装置とは、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含むIC等を実装した状態にあるモジュールとを含む場合がある。 Further, in the present specification and the like, the display device may include a panel in which the display element is sealed and a module in which an IC or the like including a controller is mounted on the panel.

〔断面構成例〕