JP6882007B2 - Image processing device and its control method and program - Google Patents

Image processing device and its control method and program Download PDFInfo

- Publication number

- JP6882007B2 JP6882007B2 JP2017029227A JP2017029227A JP6882007B2 JP 6882007 B2 JP6882007 B2 JP 6882007B2 JP 2017029227 A JP2017029227 A JP 2017029227A JP 2017029227 A JP2017029227 A JP 2017029227A JP 6882007 B2 JP6882007 B2 JP 6882007B2

- Authority

- JP

- Japan

- Prior art keywords

- image data

- unit

- pixels

- pixel

- cpu

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Compression Or Coding Systems Of Tv Signals (AREA)

- Compression Of Band Width Or Redundancy In Fax (AREA)

Description

本発明は、画像データの符号化技術に関するものである。 The present invention relates to an image data coding technique.

近年、デジタルカメラ等の画像処理装置で扱う画像の多画素化に伴って、処理すべき画像のデータ量も増加している。1つの画像に対し画像処理回路が単純なフィルタ処理を行う場合であっても、その回路には処理対象の画像の水平1ライン分の画素を保持するラインメモリが必要になり、回路規模が増大してしまう。そのため、ラインメモリを節約するために、処理すべき画像を分割して処理している。また、データ量の増大は、メモリ帯域を圧迫して、動画のフレームレートや静止画の連写枚数を下げることになる。そこで、分割処理した画像を一時的にメモリに保持する場合、分割画像データに対して圧縮する技術が特許文献1、特許文献2に提案されている。特許文献1では、分割画像を複数のサブブロックラインに分割して、サブブロックライン毎に圧縮し、元画像サイズと圧縮率に基づいてメモリの書き込みアドレスを決定することが提案されている。特許文献2では、画像データの分割する位置をランダムにしてライン毎に処理し、圧縮する画素単位に合わせるために、分割画像の端にダミー領域を付加することが提案されている。

In recent years, as the number of pixels of an image handled by an image processing device such as a digital camera has increased, the amount of image data to be processed has also increased. Even when the image processing circuit performs simple filtering on one image, the circuit requires a line memory that holds pixels for one horizontal line of the image to be processed, and the circuit scale increases. Resulting in. Therefore, in order to save line memory, the image to be processed is divided and processed. In addition, an increase in the amount of data puts pressure on the memory bandwidth and reduces the frame rate of moving images and the number of continuous shots of still images. Therefore, when the divided image is temporarily stored in the memory, a technique of compressing the divided image data has been proposed in

しかしながら、特許文献1に開示されている技術では、サブブロックライン毎に圧縮するため、分割画像の水平サイズがサブブロックラインの整数倍ではない場合、サブブロックとしての不足分の画素を付加する必要がある。つまり、本来処理する必要のない画素までを処理して圧縮することとなり、処理性能と圧縮効率低下の要因となる。このため、係る問題に対して対策が望まれていた。また、特許文献2に開示されている技術では、ダミー領域を付加するため、圧縮効率低下の要因となるため、それに対する対策が望まれていた。

However, in the technique disclosed in

本発明は上記の問題点に鑑み、処理性能と圧縮符号化効率の低下を抑制する技術を提供しようとするもいのである。 In view of the above problems, the present invention is intended to provide a technique for suppressing a decrease in processing performance and compression coding efficiency.

この課題を解決するため、例えば本発明の画像処理装置は以下の構成を備える。すなわち、

画像データを符号化する画像処理装置であって、

符号化対象の画像データを、複数の分割画像データに分割する分割手段と、

連続する所定数の画素データを単位として符号化する符号化手段と、

前記符号化手段を制御し、前記分割手段で得られた分割画像データそれぞれの符号化を行わせる制御手段とを有し、

前記制御手段は、

前記符号化手段による符号化対象の分割画像データのサイズが前記単位の整数倍であるか否かを判定する判定手段と、

該判定手段が、前記符号化対象の分割画像データのサイズが前記単位の整数倍ではないと判定した場合、前記単位の整数倍とするための不足する画素を追加する追加手段とを有し、

前記追加手段は、

前記分割画像データの境界から所定の距離までの領域に対して所定の解析を行い、当該領域が低周波成分を表す領域であるか否かを判定する解析手段を有し、

前記解析手段により前記領域が低周波成分を表しているとの解析結果を得た場合、前記境界の内側に位置する画素のコピーを追加する画素として生成し、

前記解析手段により前記領域が低周波成分を表していないとの解析結果を得た場合、所定の乱数で生成した画素を、追加する画素として生成することを特徴とする。

In order to solve this problem, for example, the image processing apparatus of the present invention has the following configuration. That is,

An image processing device that encodes image data.

A dividing means for dividing the image data to be encoded into a plurality of divided image data, and

A coding means that encodes a predetermined number of consecutive pixel data as a unit, and

It has a control means for controlling the coding means and for encoding each of the divided image data obtained by the dividing means.

The control means

A determination means for determining whether or not the size of the divided image data to be encoded by the coding means is an integral multiple of the unit.

It said determining means, when the size of the divided image data of the encoding target is determined not to be an integral multiple of the unit, possess an additional means for adding the missing pixel for an integer multiple of said unit,

The additional means

It has an analysis means for performing a predetermined analysis on a region from the boundary of the divided image data to a predetermined distance and determining whether or not the region represents a low frequency component.

When the analysis result obtained that the region represents a low frequency component by the analysis means, a copy of the pixel located inside the boundary is generated as a pixel to be added.

When an analysis result that the region does not represent a low frequency component is obtained by the analysis means, a pixel generated by a predetermined random number is generated as an additional pixel .

本発明によれば、画像データの符号化に係る処理性能と圧縮効率の低下を抑制できる。 According to the present invention, it is possible to suppress a decrease in processing performance and compression efficiency related to image data coding.

以下、添付図面に従って本発明に係る実施形態を詳細に説明する。なお以下では、本実施形態における画像処理装置を撮像装置の一部として実装されるものとして説明する。また撮像装置がデジタルカメラとして説明するが、デジタルビデオカメラ、スマートフォン、カメラ付き携帯電話、車載カメラ等の撮像装置を採用することも可能である。 Hereinafter, embodiments according to the present invention will be described in detail with reference to the accompanying drawings. In the following, the image processing device according to the present embodiment will be described as being mounted as a part of the image pickup device. Further, although the image pickup device will be described as a digital camera, it is also possible to adopt an image pickup device such as a digital video camera, a smartphone, a camera-equipped mobile phone, or an in-vehicle camera.

[第1の実施形態]

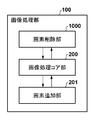

図1は第1の実施形態に係るデジタルカメラの構成の一例を示すブロック図である。デジタルカメラは、画像処理部100、圧縮部101、データ転送部102、データバス103、制御バス104、メモリ制御部105、メモリ106、不揮発性メモリ制御部107、不揮発性メモリ108、CPU109を有する。なお、図示していないが、デジタルカメラは、受光した被写体像を電気信号に変換して画像データを作成するCCDやCMOSセンサ等の撮像素子、撮像素子からのアナログ信号をデジタル信号に変換するAD変換器、画像データを例えばJPEGやMPEG形式などに圧縮または圧縮されたデータを伸張する圧縮伸張部、さらには、ユーザが操作する操作部なども有する。

[First Embodiment]

FIG. 1 is a block diagram showing an example of the configuration of the digital camera according to the first embodiment. The digital camera includes an

画像処理部100は、データ転送部102と接続され、不図示の撮像素子による撮像して得られた画像データをデータ転送部102を介して入力し、画像処理して、その処理結果をデータ転送部102あるいは圧縮部101へ出力する。この画像処理部100は、図2に示すように、画像処理コア部200と画素追加部201から構成される。画像処理コア部200は、画素補正、黒レベル補正、シェーディング補正、傷補正、倍率色収差補正、ガンマ補正、輝度・色生成処理、幾何変形、ノイズリダクション、画像のリサイズ(拡縮)などの複数の処理を実行し、画像データに対して適切な画像処理を施すブロックである。画素追加部201は、画像処理コア部200で処理した画像データあるいはデータ転送部102から転送された画像データに対して、コピー画素あるいはランダムな値(乱数)の画素を、CPU109より設定された画素数分、追加するブロックである。

The

画素追加の例を、図3(A),(B)を用いて説明する。図3(A)、(B)は、画像データの1水平ラインを示しており、斜線部が追加される画素を意味している。図3(A)は、Bayer配列の画像データ、図3(B)はYUV422フォーマットの画像データである。Bayer配列の場合、境界位置に線対称に2画素単位でコピーを行われる。YUV422フォーマットの場合、境界位置に線対称に、Y画素は端からコピーし、UV画素は2画素単位でコピーする。なお、図3(A),(B)で示した画素追加は一例であり、端以外からコピーしても良いし、コピーするのではなく、ランダムな値を画素として追加することも可能とする。 An example of adding pixels will be described with reference to FIGS. 3A and 3B. 3 (A) and 3 (B) show one horizontal line of image data, and mean a pixel to which a shaded portion is added. FIG. 3A is image data of the Bayer array, and FIG. 3B is image data of the YUV422 format. In the case of the Bayer array, copying is performed line-symmetrically at the boundary position in units of 2 pixels. In the case of the YUV422 format, the Y pixel is copied from the end and the UV pixel is copied in units of 2 pixels in line symmetry at the boundary position. Note that the addition of pixels shown in FIGS. 3A and 3B is an example, and it is possible to copy from a position other than the end, or to add a random value as a pixel instead of copying. ..

圧縮部101は、画像処理部100で処理した画像データを符号化対象として入力し、水平方向に連続する予め設定された所定数の画素(実施形態では32画素とする)といったサブブロックの単位で、差分パルス符号変調(DPCM)方式で圧縮符号化する。なお、符号化単位であるサブブロックの画素数は、32画素に限らず、64画素単位であっても良く、そのサイズ(画素数)は特に問わない。また、符号化方式は別の方式で行っても構わない。

The

データ転送部102は、データ転送を行う複数のDirect Memory Accessコントローラ(DMAC)を有し、その中にはメモリ106への書き込み用のWRDMACと、読出用のRDDMACが含まれる。画像データは、WRDMACによってバス103に出力し、メモリ制御部105を介してメモリ106に一時記憶される。メモリ106に一時記憶された画像データは、RDDMACによってメモリ106からバス103に出力され、画像処理部100にデータを出力される。バス103は、データバスであり、バス104は制御バスである。

The

メモリ制御部105は、CPU109或いはデータ転送部102からの指示に応じて、メモリ106にデータを書き込んだり、メモリ106からデータを読み出したりする。メモリ106は、所定枚数の静止画像や所定時間の動画像、音声等のデータやCPU109の動作用の定数、プログラム等を格納するのに十分な記憶容量を備える記憶装置であり、DRAMなどから構成される。

The

不揮発性メモリ制御部107は、CPU109からの指示に応じて、不揮発性メモリ108にデータを書き込んだり、不揮発性メモリ108からデータを読み出したりする。不揮発性メモリ108は、電気的に消去・記録可能なメモリであり、例えばEEPROM等が用いられる。不揮発性メモリ108には、CPU109の動作用の定数、プログラム等が記憶される。

The non-volatile

CPU109は、デジタルカメラの動作制御を司るマイクロコンピュータなどで構成され、デジタルカメラを構成する各機能ブロックに対して様々な指示を行ったり、各種の制御処理を実行する。例えば、CPU109は、バス104を介して接続された画像処理部100、データ転送部102、メモリ制御部105、不揮発性メモリ制御部107を制御する。CPU109は、前述した不揮発性メモリ108に記録されたプログラムを実行することで、本実施形態の各処理を実現する。また、CPU109は、画像データの分割処理時の分割サイズを決定する。ここで、実施形態におけるCPU109での画像の分割例を図4に、その分割サイズの決定処理手順を図5に示す。

The

図4を参照して、実施形態における画像分割処理を説明する。実施形態における画像分割処理は、符号化対象の画像データの水平方向の中央位置に分割画像データを決定し、その後で水平方向の両端部に向かって他の分割画像データを決定していく。同図において、画像データ400は、撮像して得た符号化前の画像を示している。実施形態では、この画像を破線で示すように3分割して、分割画像データ401、404、406を生成する。点線ブロック403、405、408及び参照符号を付していない他の点線ブロックは、圧縮部101による圧縮処理単位であるサブブロックを示しており、そのサブブロックの水平方向のサイズは、画像処理部100内に設けられたラインメモリのサイズの容量に依存している。

The image division process in the embodiment will be described with reference to FIG. In the image division processing in the embodiment, the divided image data is determined at the center position in the horizontal direction of the image data to be encoded, and then the other divided image data is determined toward both ends in the horizontal direction. In the figure, the

斜線部402、407は、画素追加部201で追加する画素を示す。なお、図4は3分割であるが、分割数に限定されるものでなく、3分割以上でも良いのものとする。

The shaded

次に、図4に示す画像データの分割サイズの決定処理を行うCPU109の処理手順を、図5のフローチャートに従って説明する。

Next, the processing procedure of the

S500にてCPU109は、分割画像データ404の水平方向のサイズを、点線ブロック405が切りよく収まるように決定する。

In S500, the

例えば、実施形態では、サブブロックの水平方向のサイズは32画素としているので、分割画像データ404の水平方向のサイズは32画素の整数倍である。具体的には、CPU109は、以下の数式(1)、(2)が成り立つように分割画像データ404の水平方向のサイズb1を算出する。

b1%n1 = 0 …(1)

m1≧b1 …(2)

ここで、X%Yは、整数Xを整数Yで除算した際の余りを返す関数である。また、b1は分割画像データ404の水平画素数、m1は遅延ラインに格納できる画素数、n1はサブブロック(点線ブロック403)の水平方向画素数である。

For example, in the embodiment, since the horizontal size of the subblock is 32 pixels, the horizontal size of the divided

b1% n1 = 0 ... (1)

m1 ≧ b1 ... (2)

Here, X% Y is a function that returns the remainder when the integer X is divided by the integer Y. Further, b1 is the number of horizontal pixels of the divided

つまり、分割画像データ404は、サブブロックの整数倍であり、尚且つ、分割画像データは遅延ラインの容量以下である。処理のオーバーヘッドを最少にし、効率良く処理するためには、上記条件を満たす、最大のb1を求めることである。なお、m1は画像処理コア部200の遅延ラインに格納できる画素数のため固定値となり、n1もサブブロック画素の単位のため固定値となる。

That is, the divided

S501には、CPU109は、分割画像データ401のサイズ及び分割画像データ406のサイズを決定する。具体的には、以下の数式(3)、(4)、(5)が成り立つように分割画像データ401の水平方向のサイズa1と、分割画像データ406の水平方向のサイズc1を算出する。

k1=a1+b1+c1 …(3)

m1≧a1 …(4)

m1≧c1 …(5)

ここで、k1は画像データ400の水平画素数であり、a1は分割画像データ401の水平画素数、c1は分割画像データ406の水平画素数である。なお、分割画像データ401の水平画素数a1、分割画像データ406の水平画素数c1はa1=c1としても良いし、a1>c1やa1<c1としても良く、本実施形態のデジタルカメラのシステムに応じた値に設定可能である。

In S501, the

k1 = a1 + b1 + c1 ... (3)

m1 ≧ a1… (4)

m1 ≧ c1 ... (5)

Here, k1 is the number of horizontal pixels of the

S502にて、CPU109は、分割画像データ401の水平画素数a1が、サブブロックの水平方向画素数n1で割り切れるか否か(又は、n1の整数倍か)を判定する。CPU109は、割り切れると判定した場合には処理をS504へ進め、割り切れないと判定した場合には処理をS503へ進める。また、割り切れる場合は、分割画像データ401の端部への追加する画素を表す、図4の斜線部402の水平画素数は0となる。つまり、斜線部402は不要、言い換えれば、画素追加部201による画素の追加処理は無いことを意味する。

In S502, the

S503にて、CPU109は、斜線部402の画素数、つまり画素追加部201が追加する画素数d1を次式(6)に従って算出し、処理をS504に進める。

d1=(a1/n1+1)*n1−a1 …(6)

なお、式(6)における“/”は、小数点以下を切り捨てる除算記号である。ここで、算出するd1は、遅延ラインの画素数の整数倍に満たない不足分ということができる。

In S503, the

d1 = (a1 / n1 + 1) * n1-a1 ... (6)

In addition, "/" in equation (6) is a division sign which truncates after the decimal point. Here, it can be said that d1 to be calculated is a shortage that is less than an integral multiple of the number of pixels of the delay line.

また、S503にて、CPU109は、追加する画素をコピー画素にするかランダム画素にするかの決定処理(追加画素決定処理)を行う。この追加画素決定処理は、図6のフロー図を用いて後述する。

Further, in S503, the

S504にてCPU109は、分割画像データ406の水平画素数c1が、サブブロックの水平方向画素数n1で割り切れるかどうか判定する。CPU109は、割り切れると判定した場合、この分割サイズ決定処理を終了する。CPU109は、割り切れないと判定した場合、処理をS505に進める。なお、割り切れる場合は、画素追加部201による画素の追加処理は無い。

In S504, the

S505にて、CPU109は、図4の斜線部407の画素数、つまり画素追加部201で追加する画素数を、ステップ503と同様の方法で算出する。

In S505, the

次に図6のフロー図を用いて、CPU109の追加画素決定処理を説明する。

Next, the additional pixel determination process of the

S600にて、CPU109は、画像の端に付加する画素をコピー画素を用いるコピーモードかどうかを判定する。CPU109はコピーモードが設定されていると判断した場合、S601へ処理を進める。CPU109は、コピーモードが設定されていないと判断した場合、処理をS602に進める。コピーモードは、本実施例のデジタルカメラのモードで低画質記録モード、あるいは高圧縮率モードをユーザにより、不図示の操作部から選択されていることを示している。また、本実施例のデジタルカメラのモードで明示的にコピーモードをユーザに選択した場合や、画像処理コア部200で処理する前に画素追加部201で画素を追加する場合などである。画像処理コア部200で処理する前にコピー画素にする利点としては、画像処理コア部200がフィルタ処理する時に必要とするフィルタタップ長の画素を画像処理コア部200の内部の画像処理でコピーする必要がなくなる点が挙げられる。さらには、画像処理コア部200でコピー画素をフィルタ処理した画素をサブブロック画素の単位となるように保持して置くことで、画像処理コア部200の処理後に画素追加の必要がなくなる。さらには、画像の端を単なるコピー画素にした場合、コピー画素を多く含むことでサブブロックの圧縮効率が上がり、付近のサブブロックの圧縮率と乖離し、その乖離が画質に影響を与える可能性があるが、フィルタ処理した画素を用いることで、付近のサブブロックの圧縮率と乖離することがなくなり、サブブロック毎の画質差を抑えることが出来る。

In S600, the

S601にて、CPU109は、追加画素をコピー画素にして、追加画素決定処理を終える。

In S601, the

S602にて、CPU109は、分割左端画像(又は分割右端画像)の左端側(右端側)から画像の内側に向かって予め設定された距離までの領域(or範囲)内に存在する画素の画素値を解析し、その解析結果に基づき低周波成分の度合いを求める。そして、S603には、CPU109は、低周波成分を多く含んでいるか否かを判定する。

In S602, the

例えば、CPU109は、その範囲内に存在する画素の隣り合う画素の差の絶対値を求め、差の絶対値が閾値以下であれば低周波成分と判断する。なお、これは一例であって、これ以外の論理に従って判断しても構わない。

For example, the

S603にて、CPU109は、低周波成分を多く含んでいると判定した場合、処理はS601に進める。一方、CPU109は、低周波成分が少ない(高周波成分が多い)と判定した場合、処理をS604に進める。

If the

S604にて、CPU109は、追加画素をランダムに発生するものとして決定し、この追加画素決定処理を終える。なお、追加する画素に対して全てランダム画素にしても良いし、追加する画素に対して同じランダム画素を用いても良い。

In S604, the

追加画素決定処理で低周波成分であればコピー画素にして、低周波成分以外はランダム画素にするのは、サブブロック単位で圧縮するため、付近のサブブロックと近い圧縮率で圧縮した方が、圧縮率の差異による画質差を抑えることが可能となるためである。 If it is a low frequency component in the additional pixel determination process, it is made into a copy pixel, and if it is not a low frequency component, it is made into a random pixel because it is compressed in subblock units, so it is better to compress it at a compression rate close to that of nearby subblocks. This is because it is possible to suppress the difference in image quality due to the difference in compression rate.

この後、圧縮部101は、画像処理部100からの分割画像データを入力しては、サブブロック単位に圧縮符号化処理を行っていくことになる。生成された符号化データは、データ転送部102を介して、メモリ106に格納されることになる。

After that, the

以上説明したように、第1の実施形態によれば、分割中央画像サイズを任意と決めた場合と比べて、分割画像のサイズが圧縮のサブブロックの整数倍となるので、圧縮時にサブブロック画素の単位に合わせる必要がなく、符号化処理がスムースを行うことが可能になり、符号化処理性能と圧縮効率の低下を抑制できる。また、分割数が多くなればなるほど、本実施形態の効果は顕著となってくる。 As described above, according to the first embodiment, the size of the divided image is an integral multiple of the compression subblock as compared with the case where the division center image size is determined to be arbitrary. It is not necessary to adjust to the unit of, and the coding process can be performed smoothly, and the deterioration of the coding process performance and the compression efficiency can be suppressed. Further, as the number of divisions increases, the effect of this embodiment becomes more remarkable.

以上、第1の実施形態に基づき具体的に説明したが、上記実施形態に限定されるものではなく、その要旨を逸脱しない範囲において種々の変更が可能であることは言うまでもない。 Although the above has been specifically described based on the first embodiment, it is needless to say that the description is not limited to the above embodiment and various changes can be made without departing from the gist thereof.

[第2の実施形態]

次に、第2の実施形態について説明する。なお、ここでは、前述した第1の実施形態と異なる部分のみを説明し、同一の部分については、同一の符号を付すなどして詳細な説明を省略する。

[Second Embodiment]

Next, the second embodiment will be described. Here, only the parts different from those of the first embodiment described above will be described, and the same parts will be designated by the same reference numerals and detailed description thereof will be omitted.

図7は、画像データ700を、点線を境界に、分割画像データ701、703に2分割する例である。点線ブロック702、705、及び図番を付加していない点線ブロックは、圧縮部101で圧縮処理するサブブロックを示している。斜線部704は、画素追加部201で追加する画素領域を示している。

FIG. 7 is an example in which the

次に、CPU109による、図7に示す画像データの分割サイズの決定方法を、図8のフローチャートに従って説明する。

Next, a method of determining the division size of the image data shown in FIG. 7 by the

S800にて、CPU109は、分割左端画像データ701の水平方向のサイズを、点線ブロック702が切りよく収まるように決定する。つまり、サブブロック画素の単位が32画素であれば、分割画像データ701の水平方向のサイズを32画素の整数倍にする。

In S800, the

次に、CPU109は、S801にて、以下の数式(7)、(8)が成り立つように分割右端画像データ703のサイズb2を算出する。

b2%n2=0 …(7)

m2≧b2 …(8)

ここで、b2は分割左端画像データ701の水平画素数、m2は遅延ラインに格納できる画素数、n2はサブブロックの水平方向画素数(点線ブロック702の水平画素数)である。なお、m2は画像処理コア部200の遅延ラインに格納できる画素数のため固定値となり、n2もサブブロック画素の単位のため固定値となる。b2は、本実施形態のデジタルカメラのシステムに応じて、数式(7)、(8)を満たす最大値とすると効率が良い。

Next, the

b2% n2 = 0 ... (7)

m2 ≧ b2… (8)

Here, b2 is the number of horizontal pixels of the split left

S801にて、CPU109は、分割画像データ703のサイズを決定し、S802へ処理を進める。具体的には、以下の数式(9)、(10)が成り立つように分割画像データ703のサイズc2を算出する。

k2=b2+c2 …(9)

m2≧c2 …(10)

ここで、k2は画像データ700の水平画素数、c2は分割右端画像データ703の水平画素数である。

In S801, the

k2 = b2 + c2 ... (9)

m2 ≧ c2… (10)

Here, k2 is the number of horizontal pixels of the

S802にて、CPU109は、分割右端画像データ703の水平画素数c2が、サブブロックのサイズn2で割り切れるかどうか判定する。CPU109は、割り切れると判定した場合には、分割サイズ決定処理を終了する。また、CPU109は、割り切れないと判定した場合は、S803に処理を進める。なお、c2がn2で割り切れる場合、斜線部704の水平画素数は0となり、画素の追加処理は不要となる。

In S802, the

S803にて、CPU109は、斜線部704が表す画素数、つまり画素追加部201で追加する画素数d2を、次式(11)より算出する。

d2=(c2/n2+1)*n2−c2 ・・・(11)

また、追加する画素をコピー画素にするかランダム画素にするかを図6に示す追加画素決定処理にて決定する。

In S803, the

d2 = (c2 / n2 + 1) * n2-c2 ... (11)

Further, whether the pixel to be added is a copy pixel or a random pixel is determined by the additional pixel determination process shown in FIG.

以上説明したように、本第2の実施形態によれば、第1の実施形態の作用効果に加えて、追加する画素数を判定する分割画像は、分割右端画像の1つとなり、その判定に係る処理及び画素追加処理が簡略化され、処理性能と圧縮効率の低下を更に抑制できる。 As described above, according to the second embodiment, in addition to the effects of the first embodiment, the divided image for determining the number of pixels to be added is one of the divided right end images, and the determination is made. Such processing and pixel addition processing are simplified, and deterioration of processing performance and compression efficiency can be further suppressed.

なお、上記第2の実施形態に基づき具体的に説明したが、本発明は、前記実施形態に限定されるものではなく、その要旨を逸脱しない範囲において種々の変更が可能である。 Although specifically described based on the second embodiment, the present invention is not limited to the above embodiment, and various modifications can be made without departing from the gist thereof.

[第3の実施形態]

次に、第3の実施形態について説明する。なお、ここでは、上記第1の実施形態と異なる部分のみを説明し、同一の部分については、同一の符号を付すなどして詳細な説明を省略する。

[Third Embodiment]

Next, a third embodiment will be described. Here, only the parts different from those of the first embodiment will be described, and the same parts will be designated by the same reference numerals and detailed description thereof will be omitted.

図9は第3の実施形態に係るデジタルカメラの構成の一例を示すブロック図であり、図1に対して伸長部(復号部)900を追加した構成である。 FIG. 9 is a block diagram showing an example of the configuration of the digital camera according to the third embodiment, and is a configuration in which an extension unit (decoding unit) 900 is added to FIG.

伸長部900は、メモリ106に記憶されている圧縮部101で圧縮された画像データを、データ転送部102を介して読み込む。そして、伸長部900は、読み込んだ圧縮画像データを圧縮部101で圧縮したサブブロック画素の単位で伸長(復号)して、伸長結果である画像データを画像処理部100へ渡す。

The

図10は、本第3の実施形態における画像処理部100の内部構成図である。図2に対して、画素削除部1000を追加された点が異なる。この画素削除部1000は、入力された画像データの任意の場所の画素を削除して、削除後の画像データを画像処理コア部200へ渡す。なお、画素削除部1000は、伸長部900内に設けられるようにしても良い。

FIG. 10 is an internal configuration diagram of the

図11は、画像データ1100を、図示の点線を境界に分割画像データ1101、1105、1107に3分割した図である。点線ブロック1104、1106、1110及び図番を付加していない点線ブロックは、圧縮部101で圧縮処理するサブブロックの水平方向のサイズ(圧縮符号化単位)を示すものである。斜線部1102、1108及びクロス斜線部1103、1109は、画素追加部201で追加する画素を示す。なお、図11は3分割であるが、分割数は3以上でも構わない。

FIG. 11 is a diagram in which the

本第3の実施形態における分割画像サイズ決定は、図5のフローに沿って決定するものとするが、画素追加部201により追加する画素は、図12に示す追加画素決定処理で決定される。

The division image size determination in the third embodiment is determined according to the flow of FIG. 5, but the pixels to be added by the

図12に係るプログラムは、不揮発性メモリ108に格納されており、CPU109が実行するものでもある。以下、同図に従ってCPU109による追加画素決定処理を説明する。

The program according to FIG. 12 is stored in the

S1200にて、CPU109は、追加する画素の内、伸長部900で伸長して画像処理する際にフィルタ処理で必要な画素分をコピー画素として決定する。なお、図11の斜線部1102、1108がコピー画素領域を示している。つまり、圧縮時に必要なサブブロック画素の単位に合わせるための画素を、次の画像処理コア部200でフィルタ処理するための左端、右端を予めコピー画素にしておく。これにより、ランダム画素にした時と比べて、次の画像処理時にコピー画素を追加する必要がなくなるため、処理性能の向上がはかれる。

In S1200, the

S1201にて、CPU109は、追加する画素のうち、ステップ1200で決定したコピー画素数以外をランダム画素として決定し、この追加画素決定処理を終える。なお、図11のクロス斜線部1103、1109がランダム画素を示しており、伸長部900で伸長後、画素削除部1000で削除する領域である。つまり、クロス斜線部1103、1109は、画像処理コア部200では処理しない画素となるため、無駄な画素を処理する必要がなくなるため、処理性能の低下を抑制できる。

In S1201, the

以上説明したように、本第3の実施形態によれば、分割画像サイズが、圧縮のサブブロック画素の単位となることで、圧縮時にサブブロック画素の単位に合わせる必要がなくなるため、余分な画素の処理が不要となり、処理性能と圧縮効率の低下を抑制できる。また、分割数が多くなればなるほど、本実施形態の効果は顕著となってくる。さらには、次の画像処理でフィルタ処理を行う場合には、フィルタ処理で使用する画素を圧縮時にコピー画素にすることで処理性能の向上をはかり、伸長後にフィルタ処理で不要な画素をカットすることで処理性能の低下を抑制することもできる。 As described above, according to the third embodiment, since the divided image size is the unit of the subblock pixel of compression, it is not necessary to match the unit of the subblock pixel at the time of compression, so that extra pixels are used. Processing is not required, and deterioration of processing performance and compression efficiency can be suppressed. Further, as the number of divisions increases, the effect of this embodiment becomes more remarkable. Furthermore, when filtering is performed in the next image processing, the processing performance is improved by making the pixels used in the filtering processing copy pixels at the time of compression, and unnecessary pixels are cut by the filtering after decompression. It is also possible to suppress a decrease in processing performance.

以上、第3の実施形態に基づき具体的に説明したが、本発明は、前記実施形態に限定されるものではなく、その要旨を逸脱しない範囲において種々の変更が可能であることは言うまでもない。 Although the present invention has been specifically described above based on the third embodiment, it is needless to say that the present invention is not limited to the above-described embodiment and various modifications can be made without departing from the gist thereof.

[第4の実施形態]

次に第4の実施形態を説明する。図13は第4の実施形態に係るデジタルカメラの構成の一例を示すブロック図である。図示のように、本装置は、画像処理部1300、RDDMAC1301、WRDMAC1302、圧縮部1303、伸長部1304、データバス1305、制御バス1306、メモリ制御部1307、メモリ1308、不揮発性メモリ1309、不揮発性メモリ1310、CPU1311を有する。また、図示していないが、受光した被写体像を電気信号に変換して画像データを作成するCCDやCMOSセンサ等の撮像素子、撮像素子からのアナログ信号をデジタル信号に変換するAD変換器、画像データを例えばJPEGやMPEG形式などに圧縮または圧縮されたデータを伸張する圧縮伸張部、ユーザが操作する操作部なども有する。

[Fourth Embodiment]

Next, a fourth embodiment will be described. FIG. 13 is a block diagram showing an example of the configuration of the digital camera according to the fourth embodiment. As shown in the figure, this apparatus includes an

画像処理部1300は、RDDMAC1301、伸長部1304、WRDMAC1302、圧縮部1303と接続される。画像処理部1300は、RDDMAC1301から画像データを入力し、画像処理して、処理結果をWRDMAC1302あるいは圧縮部1303へ出力する。

The

画像処理部1300は、図14に示すように、画像処理コア部1400と画素圧縮単位決定部1401を含む。画像処理コア部1400は、画素補正、黒レベル補正、シェーディング補正、傷補正、倍率色収差補正ガンマ補正や輝度・色生成処理、幾何変形、ノイズリダクション、拡縮といったリサイズなどの複数の処理を実行し、画像データに対して適切な画像処理を施すブロックである。画素圧縮単位決定部1401は、圧縮部1303が画像データを水平方向にサブブロックの単位に分割して圧縮する時のサブブロックの画素数を決定する。詳細な説明は、図15、図16を用いて後術する。なお、画素圧縮単位決定部1401は、圧縮部1303の中に持つ構成としても良い。

As shown in FIG. 14, the

RDDMAC1301は、データの読み込み転送を行う複数のDMA(Direct Memory Access)コントローラで構成され、図17に示すように、RDDMACコア部1700と画素伸長単位決定部1701を含む。メモリ1308に一時記憶された画像データは、RDDMACコア部1700によって、そのメモリ1308からデータバス1305を介してRDDMAC1301に出力され、画像処理部1300あるいは伸長部1304に転送される。画素伸長単位決定部1701は、伸長する画像データのサブブロックの画素数を算出する。詳細な説明は、図18のフロー図を用いて後術する。なお、画素伸長単位決定部1701は、伸長部1304の中に含まれる構成としても良い。

The

WRDMAC1302は、メモリ1308へのデータの書き込み転送を行う複数のDMAコントローラで構成される。画像データは、WRDMAC1302によってデータバス1305に出力され、メモリ制御部1307を介してメモリ1308に一時記憶される。

The

圧縮部1303は、画像処理部1300で処理した画像データに対して、水平方向に例えば32画素といったサブブロックの画素数単位に、差分パルス符号変調(DPCM)方式で圧縮するブロックである。なお、サブブロックの画素数は、画素圧縮単位決定部1401で決定される。圧縮方式は別の方式で行っても良いものとする。

The

伸長部1304は、メモリ1308に記憶されている、圧縮部1303で圧縮された画像データを、RDDMAC1301を介して読み込む。そして、伸長部1304は、読み込んだ圧縮画像データを、圧縮されたサブブロックの画素数単位に伸長して、伸長結果である画像データを画像処理部1300へ渡す。なお、サブブロックの画素数は、画素伸長単位決定部1701で決定される。

The

データバス1305は、画像データを転送するためのバスであり、制御バス1306は、CPU1311から画像処理部1300、RDDMAC1301、WRDMAC1302、圧縮部1303、伸長部1304へアクセスする制御バスである。

The

メモリ制御部1307は、CPU1311或いはRDDMAC1301、WRDMAC1302からの指示に応じて、メモリ1308にデータを書き込んだり、メモリ1308からデータを読み出したりする。メモリ1308は、所定枚数の静止画像や所定時間の動画像、音声等のデータやCPU1311の動作用の定数、プログラム等を格納するのに十分な記憶容量を備える記憶装置であり、DRAMなどから構成される。

The

不揮発性メモリ制御部1309は、CPU1311からの指示に応じて、不揮発性メモリ1310にデータを書き込んだり、不揮発性メモリ1310からデータを読み出したりする。不揮発性メモリ1310は、電気的に消去・記録可能なメモリであり、例えばEEPROM等が用いられる。不揮発性メモリ1310には、CPU1311の動作用の定数、プログラム等が記憶される。

The non-volatile

CPU1311は、デジタルカメラの動作制御を司るマイクロコンピュータなどで構成され、デジタルカメラを構成する各機能ブロックに対して様々な指示を行ったり、各種の制御処理を実行する。CPU1311は、制御バス1306を介して接続された画像処理部1300、RDDMAC1301、WRDMAC1302、圧縮部1303、伸長部1304、メモリ制御部1307、不揮発性メモリ制御部1309を制御する。CPU109は、前述した不揮発性メモリ1310に記録されたプログラムを実行することで、本実施形態の各処理を実現する。また、CPU1311は、画像データの分割処理時の分割サイズを決定する。なお、CPU1311による画像の分割例を図15に示す。

The

図15は、画像データ1500を、図示の点線を境界に、分割画像データ1501、1504、1507に3分割した例を示している。点線ブロック1502、1505、1508は、圧縮部1303で圧縮処理するサブブロックを示し、それらの水平方向の画素数は同一である。

FIG. 15 shows an example in which the

また、分割画像データ1501の右端に位置する点線ブロック1503の水平方向の画素数は、分割画像データ1501の水平画素数から、点線ブロック1503より左側に位置する全サブブロックの画素数の総和を引いた値である。

Further, the number of pixels in the horizontal direction of the dotted

分割画像データ1501の水平方向の画素数をNとし、符号化処理単位の水平方向の画素数をSとしたとき、次式の関係を有する。

N=S×i+r

点線ブロック1503は、上記式の端数“r”に相当する部分を表すことになる。なお、rは、Sより小さい値であり、圧縮部1303が有するラインメモリの容量の範囲内の値でもある。

When the number of pixels in the horizontal direction of the divided

N = S × i + r

The dotted

なお、サブブロックの画素数の算出方法は、図16の圧縮単位決定処理のフロー図を用いて後術する。 The method of calculating the number of pixels of the sub-block will be performed later using the flow chart of the compression unit determination process of FIG.

点線ブロック1505、1508及びそれに続く図番を付加してない点線ブロックに示すサブブロックの画素数の考え方は、点線ブロック1502と同様である。そして、分割画像データの右端に位置する点線ブロック1506、1509に示すサブブロックの画素数の考え方は、点線ブロック1503と同様である。

The concept of the number of pixels of the sub-blocks shown in the dotted line blocks 1505 and 1508 and the dotted line blocks to which the subsequent drawing numbers are not added is the same as that of the dotted

図16に従い、CPU1311による、分割画像データ1501を圧縮部1303で圧縮処理する圧縮単位の画素数、つまり、サブブロックの画素数を算出する圧縮単位決定処理のフローを説明する。なお、分割画像データ1501で説明するが、分割画像データ1504、1507も同様に適応される。

A flow of compression unit determination processing for calculating the number of pixels of the compression unit, that is, the number of pixels of the subblock, in which the divided

S1600にて、CPU1311は、分割画像データ1501の点線ブロック1502及びそれに続く図番を付加してない点線ブロック(サブブロック)の先頭画素を処理するか判定する。CPU1311は、先頭画素を処理すると判定した場合、S1601に処理を進める。CPU1311が、先頭以外の画素を処理すると判定した場合には、圧縮単位決定処理を終了する。

In S1600, the

S1601にて、CPU1311は、水平方向の処理画素位置を取得し、S1602に処理を進める。CPU1311は、分割画像データ1501の水平画素数が予めわかっている。そこで、S1602にてCPU1311は、S1601で取得した画素位置より、分割画像データ1501の水平方向の残りの画素数(未符号化画素数でもある)を算出し、S1603へ処理を進める。

In S1601, the

S1603にて、CPU1311は、S1602で算出した残りの画素数と、閾値Aを比較する。CPU1311は、算出した画素数が閾値以上であると判定した場合は、処理をS1604進め、閾値に満たないと判定した場合にはS1605に処理を進める。

In S1603, the

S1605にて、CPU1311は、圧縮単位の画素数を閾値Aとし、圧縮部に画素数を通知し、圧縮単位決定処理を終了する。

In S1605, the

S1605にて、CPU1311は、圧縮単位の画素数をS1601で算出した残りの画素数とし、圧縮部1303に画素数を通知し、圧縮単位決定処理を終了する。

In S1605, the

次に図18に従って、分割画像データ1501を圧縮した画像データについて、伸長部1304で伸長処理する伸長単位の画素数つまり、サブブロックの画素数を算出する伸長単位決定処理を説明する。

Next, according to FIG. 18, for the image data obtained by compressing the divided

なお、分割画像データ1501を圧縮した画像データについて説明するが、分割画像データ1504、1507を圧縮した画像データについても同様に適応される。また、伸長単位決定処理は、圧縮部1303で圧縮した圧縮サブブロックのデータサイズがサブブロック内の画素数換算で固定長となるように圧縮される前提の処理となる。例えば、圧縮前の画素が1画素14bitの場合、サブブロックの画素数が32画素で非圧縮であれば448bit、圧縮した場合は320bitとなり、画素数が8画素で非圧縮であれば112bit、圧縮した場合は80bitとなるように圧縮する。つまり、サブブロック内の画素数に応じて圧縮サブブロックのデータサイズを固定長にすることで、データ量から水平の画素位置を把握することができる。

Although the image data obtained by compressing the divided

S1800にて、CPU1311は、分割画像データ1501を圧縮した画像データにおける点線ブロック(サブブロック)の先頭画素を処理するか判定する。CPU1311が、点線ブロックの先頭画素が処理対象であると判定した場合、S1801に処理を進める。また、CPU1311は、先頭以外の画素が処理対象であると判定した場合には、この伸長単位決定処理を終了する。

In S1800, the

S1801にて、CPU1311は、水平方向の処理位置を取得し、処理をS1802に進める。S1802にて、CPU1311は、水平方向の処理位置から、水平方向の残りの画素数を算出し、S1803に処理を進める。

In S1801, the

S1803にて、CPU1311は、S1802で算出した残りの画素数と、閾値Aを比較する。CPU1311は、算出した画素数が閾値Aより大きいと判定した場合、処理をS1804に進める。また、CPU1311は、算出した画素数が閾値A以下であると判定した場合、S1805に処理を進める。

In S1803, the

S1804にて、CPU1311は、伸長単位の画素数を閾値Aとし、伸長部1304にその画素数を通知し、伸長単位決定処理を終了する。

In S1804, the

S1805にて、CPU1311は、伸長単位の画素数を、S1801で算出した残りの画素数とし、伸長部1304に画素数を通知し、伸長単位決定処理を終了する。

In S1805, the

以上説明したように、本第4の実施形態によれば、分割画像をサブブロックに分ける時に、分割画像の右端のサブブロックの画素数を異ならせることで、処理性能と圧縮効率の低下を抑制できる。また、分割画像の境界データを圧縮する時に、コピー画素やランダム画素を使用しないで圧縮するので、画像境界の符号量と画像境界以外の符号量とが大きくことなることがなくなり、分割境界と分割境界以外の画質差の影響を抑制することもできる。 As described above, according to the fourth embodiment, when the divided image is divided into sub-blocks, the number of pixels of the sub-block at the right end of the divided image is made different, thereby suppressing a decrease in processing performance and compression efficiency. it can. Further, when the boundary data of the divided image is compressed, it is compressed without using copy pixels or random pixels, so that the code amount of the image boundary and the code amount other than the image boundary do not become large, and the divided boundary and the divided image are divided. It is also possible to suppress the influence of image quality differences other than the boundary.

以上、第4の実施形態に基づき具体的に説明したが、本発明は、前記実施形態に限定されるものではなく、その要旨を逸脱しない範囲において種々の変更が可能であることは言うまでもない。 Although the present invention has been specifically described above based on the fourth embodiment, it goes without saying that the present invention is not limited to the above-described embodiment and various modifications can be made without departing from the gist thereof.

[第5の実施形態]

次に、第5の実施形態を説明する。本第5の実施形態では、上述した第4の実施形態と異なる部分のみを説明し、同一の部分については、同一の符号を付すなどして詳細な説明を省略する。

[Fifth Embodiment]

Next, a fifth embodiment will be described. In the fifth embodiment, only the parts different from the fourth embodiment described above will be described, and the same parts will be designated by the same reference numerals and detailed description thereof will be omitted.

図19は、第5の実施形態における画像処理部1300の構成図である。図示の如く、画像処理コア部1400、画素圧縮単位決定部1401、及び、ラインバッファ1900を含み、圧縮部1303と接続される。ラインバッファ1900は、SRAMなどで構成され、水平方向に2ラインの画素データを格納する、ダブルバッファ構成となっている。画素圧縮単位決定部1401は、1ラインの画像データをダブルバッファの一方に格納する処理と、他方から圧縮部1303が圧縮処理する圧縮単位の画素数のサブブロックの画素数を算出し、圧縮部1303へ出力する処理を行う。詳細は、図20、21を用いて説明する。

FIG. 19 is a configuration diagram of the

なお、画素圧縮単位決定部1401とラインバッファ1900は、圧縮部1303の中に持つ構成としても良い。圧縮部1303は、画素圧縮単位決定部1401から通知されるサブブロックの画素数に応じてデータ圧縮処理を行い、サブブロック圧縮後のデータサイズが固定長となるように圧縮を行う。つまり、サブブロック内の画素数が異なっても、圧縮後のデータサイズは固定となる。なお、サブブロック圧縮後のデータサイズは、CPU1311より設定することが可能である。また圧縮時、ヘッダにサブブロック内の画素数を付加する。

The pixel compression

図20は、画像データ2000を、点線境界で、分割画像データ2001、2004、2007に3分割した例を示している。図示の点線ブロック2002、2003、2005、2006、2008、2009及び図番を付加していない点線ブロックは、圧縮部1303で圧縮処理するサブブロックを示すものである。点線ブロック2002とそれに続く図番を付加してない点線ブロックと、右端に位置する点線ブロック2003に示すサブブロックの画素数は、それぞれ異なる。ただし、分割画像データ2001内の画素データによっては、サブブロックの画素数は、同じ画素数となることもある。つまり、サブブロックの画素数が分割画像データ2001の位置によって可変となることを意味している。画素数が可変となるサブブロックの画素数の算出方法は、図21の圧縮単位決定処理のフロー図を用いて後術する。点線ブロック2005、2006、2008、2009に示すサブブロックの画素数の考え方は、点線ブロック2002と同様である。

FIG. 20 shows an example in which the

図21を用いて、CPU1311による、圧縮部1303の圧縮処理単位の画素数、つまり、サブブロックの画素数を算出する処理を説明する。なお、分割画像データ2001を例にして説明するが、分割画像データ2004、2007も同様に適応される。

A process of calculating the number of pixels of the compression processing unit of the

S2100にて、CPU1311は、隣接画素間と差分αn(nは1以上の整数でサブブロック数N−1までの値となる)を取り、ラインバッファ1900の片側A(B)に入力画素を保持し、S2101へ処理を進める。また、ラインバッファ1900の片側Aを奇数行で使用する場合、ラインバッファ1900の他方側Bは偶数行で使用することになる。

In S2100, the

S2101にて、CPU1311は、差分αnと閾値Bを比較する。CPU1311は、差分αnが閾値Bより大きいと判断した場合、S2102へ処理を進める。また、CPU1311は、差分αnが閾値B以下であると判定した場合には、S2107に処理を進める。

In S2101, the

S2102において、CPU1311は、差分αnとサブブロックの画素数Hn(nは1以上の整数でサブブロック数Nまでの値となる)を保持し、サブブロック数Nをカウントアップ(計数)し、S2013へ処理を進める。

In S2102, the

S2103にて、CPU1311は、分割画像データ2001の1ライン分の画素を処理したかを判定する。CPU1311は、1ライン分の画像処理を終えたと判定した場合、処理をS2104へ進める。また、CPU1311は、1ライン分の処理が未終了であると判定した場合、S2107に処理を進める。

In S2103, the

S2014にて、CPU1311は、サブブロック数Nと閾値Cを比較し、サブブロック数Nが閾値Cより大きいか否かを判定する。CPU1311は、サブブロック数Nが閾値Cより大きいと判定した場合、S2105に処理を進める。また、CPU1311は、サブブロック数Nが閾値C以下であると判定した場合、処理をS2106に進める。

In S2014, the

S2105にて、CPU1311は、サブブロック数Nが閾値Cとなるように、差分αnの値が小さい順にサブブロックを結合して、サブブロック数Nを変更する。そして、CPU1311は、処理をS2106に進める。

In S2105, the

S2106にて、CPU1311は、サブブロック数Nを初期化する。そして、CPU1311は、処理をS2107に進める。

In S2106, the

S2107にて、CPU1311は、ラインバッファ1900の片面B(A)、つまり、S2100でデータを溜めていないラインバッファ1900の片面に出力するデータがあるかないかを判定する。CPU1311は、出力すべきデータがあると判断した場合には、S2108に処理を進める。また、出力すべきデータがないと判断した場合には、圧縮単位決定処理を終了する。

In S2107, the

S2108にて、CPU1311は、ラインバッファ1900の片面B(A)に溜めてある画素を圧縮部に出力し、かつサブブロックの先頭になったら、サブブロックの画素数Hnを通知し、圧縮単位決定処理を終了する。

In S2108, the

次に図22を用いて、分割画像データ2001の圧縮画像データについて、伸長部1304で伸長処理する伸長単位の画素数、つまり、サブブロックの画素数を算出する伸長単位決定処理のフローを説明する。なお、分割画像データ2001の圧縮画像データについて説明するが、分割画像データ2004、2007の圧縮画像データについても同様に適応される。

Next, with reference to FIG. 22, the flow of the expansion unit determination processing for calculating the number of pixels of the expansion unit to be expanded by the

S2200にて、CPU1311は、サブブロック圧縮画像データの先頭か否かを判別する。CPU1311が、先頭の画素であると判定した場合、S2201に処理を進める。CPU1311が、先頭の画素ではないと判定した場合には、この伸長単位決定処理を終了する。サブブロック圧縮画像データの先頭かどうかの判定は、分割画像データ2001の先頭データであるかどうかで判定する。あるいは、処理したデータのサイズを累積加算した処理済データサイズと、予めCPU1311で設定したサブブロック圧縮後のデータサイズと等しくなった次のデータかどうかで判定し、先頭データであった場合は、処理済データサイズは初期化する。つまり、圧縮前の分割画像データ2001で説明すると、点線ブロック2002とそれに続く図番を付加してない点線ブロックと、点線ブロック2003に示すサブブロックの先頭かどうかを判定する。

In S2200, the

ステップ2201にて、CPU1311は、サブブロック圧縮画像データのヘッダからサブブロック内の画素数を取得し、その画素数を伸長部1304に通知して、伸長単位決定処理部を終了する。

In step 2201, the

以上説明したように、第5の実施形態によれば、分割画像データの1ライン中のサブブロック数が閾値以下となるように、圧縮するサブブロック内の画素数を可変にすることで、処理性能と圧縮効率の低下を抑制できる。また、分割画像の境界データを圧縮する時に、コピー画素やランダム画素を使用しないで圧縮する。従って、画像境界の符号量と画像境界以外の符号量とが大きくことなることがなくなるため、分割境界と分割境界以外の画質差の影響を抑制できる。さらには、隣接画素の差分からサブブロック内の画素数を決めることで、1画素あたりに割り当てる符号量が均一化されるため、圧縮による画像劣化を抑制できる。 As described above, according to the fifth embodiment, the processing is performed by changing the number of pixels in the subblock to be compressed so that the number of subblocks in one line of the divided image data is equal to or less than the threshold value. It is possible to suppress a decrease in performance and compression efficiency. Further, when compressing the boundary data of the divided image, it is compressed without using copy pixels or random pixels. Therefore, since the code amount of the image boundary and the code amount other than the image boundary do not become large, the influence of the image quality difference between the divided boundary and the image quality other than the divided boundary can be suppressed. Furthermore, by determining the number of pixels in the subblock from the difference between adjacent pixels, the amount of code assigned to each pixel is made uniform, so that image deterioration due to compression can be suppressed.

以上、第5の実施形態に基づき具体的に説明したが、本発明は、前記実施形態に限定されるものではなく、その要旨を逸脱しない範囲において種々の変更が可能であることは言うまでもない。 The present invention has been specifically described above based on the fifth embodiment, but it goes without saying that the present invention is not limited to the above-described embodiment and various modifications can be made without departing from the gist thereof.

(その他の実施例)

本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1つ以上のプロセッサーがプログラムを読出し実行する処理でも実現可能である。また、1以上の機能を実現する回路(例えば、ASIC)によっても実現可能である。

(Other Examples)

The present invention supplies a program that realizes one or more functions of the above-described embodiment to a system or device via a network or storage medium, and one or more processors in the computer of the system or device reads and executes the program. It can also be realized by the processing to be performed. It can also be realized by a circuit (for example, ASIC) that realizes one or more functions.

100…画像処理部、101…圧縮部、102…データ転送部、103…データバス、104…制御バス、105…メモリ制御部、106…メモリ、107…不揮発性メモリ制御部、108…不揮発性メモリ、109…CPU 100 ... image processing unit, 101 ... compression unit, 102 ... data transfer unit, 103 ... data bus, 104 ... control bus, 105 ... memory control unit, 106 ... memory, 107 ... non-volatile memory control unit, 108 ... non-volatile memory , 109 ... CPU

Claims (5)

符号化対象の画像データを、複数の分割画像データに分割する分割手段と、

連続する所定数の画素データを単位として符号化する符号化手段と、

前記符号化手段を制御し、前記分割手段で得られた分割画像データそれぞれの符号化を行わせる制御手段とを有し、

前記制御手段は、

前記符号化手段による符号化対象の分割画像データのサイズが前記単位の整数倍であるか否かを判定する判定手段と、

該判定手段が、前記符号化対象の分割画像データのサイズが前記単位の整数倍ではないと判定した場合、前記単位の整数倍とするための不足する画素を追加する追加手段とを有し、

前記追加手段は、

前記分割画像データの境界から所定の距離までの領域に対して所定の解析を行い、当該領域が低周波成分を表す領域であるか否かを判定する解析手段を有し、

前記解析手段により前記領域が低周波成分を表しているとの解析結果を得た場合、前記境界の内側に位置する画素のコピーを追加する画素として生成し、

前記解析手段により前記領域が低周波成分を表していないとの解析結果を得た場合、所定の乱数で生成した画素を、追加する画素として生成する

ことを特徴とする画像処理装置。 An image processing device that encodes image data.

A dividing means for dividing the image data to be encoded into a plurality of divided image data, and

A coding means that encodes a predetermined number of consecutive pixel data as a unit, and

It has a control means for controlling the coding means and for encoding each of the divided image data obtained by the dividing means.

The control means

A determination means for determining whether or not the size of the divided image data to be encoded by the coding means is an integral multiple of the unit.

It said determining means, when the size of the divided image data of the encoding target is determined not to be an integral multiple of the unit, possess an additional means for adding the missing pixel for an integer multiple of said unit,

The additional means

It has an analysis means for performing a predetermined analysis on a region from the boundary of the divided image data to a predetermined distance and determining whether or not the region represents a low frequency component.

When the analysis result obtained that the region represents a low frequency component by the analysis means, a copy of the pixel located inside the boundary is generated as a pixel to be added.

An image processing apparatus characterized in that when an analysis result that the region does not represent a low frequency component is obtained by the analysis means, pixels generated by a predetermined random number are generated as additional pixels.

符号化対象の画像データを、複数の分割画像データに分割する分割工程と、

連続する所定数の画素データを単位として符号化する符号化工程と、

前記符号化工程を制御し、前記分割工程で得られた分割画像データそれぞれの符号化を行わせる制御工程とを有し、

前記制御工程は、

前記符号化工程による符号化対象の分割画像データのサイズが前記単位の整数倍であるか否かを判定する判定工程と、

該判定工程で、前記符号化対象の分割画像データのサイズが前記単位の整数倍ではないと判定した場合、前記単位の整数倍とするための不足する画素を追加する追加工程とを有し、

前記追加工程は、

前記分割画像データの境界から所定の距離までの領域に対して所定の解析を行い、当該領域が低周波成分を表す領域であるか否かを判定する解析工程を有し、

前記解析工程により前記領域が低周波成分を表しているとの解析結果を得た場合、前記境界の内側に位置する画素のコピーを追加する画素として生成し、

前記解析工程により前記領域が低周波成分を表していないとの解析結果を得た場合、所定の乱数で生成した画素を、追加する画素として生成する

ことを特徴とする画像処理装置の制御方法。 A control method for an image processing device that encodes image data.

A division step of dividing the image data to be encoded into a plurality of divided image data, and

A coding process that encodes a predetermined number of consecutive pixel data as a unit,

It has a control step of controlling the coding step and encoding each of the divided image data obtained in the dividing step.

The control step is

A determination step of determining whether or not the size of the divided image data to be encoded by the coding step is an integral multiple of the unit, and

In the determination step, when the size of the divided image data of the encoding target is determined not to be an integral multiple of the unit, possess an additional step of adding a missing pixel to an integer multiple of said unit,

The additional step is

It has an analysis step of performing a predetermined analysis on a region from the boundary of the divided image data to a predetermined distance and determining whether or not the region represents a low frequency component.

When the analysis result that the region represents a low frequency component is obtained by the analysis step, a copy of the pixel located inside the boundary is generated as an additional pixel.

When an analysis result that the region does not represent a low frequency component is obtained by the analysis step, a pixel generated by a predetermined random number is generated as an additional pixel.

A control method for an image processing device.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017029227A JP6882007B2 (en) | 2017-02-20 | 2017-02-20 | Image processing device and its control method and program |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017029227A JP6882007B2 (en) | 2017-02-20 | 2017-02-20 | Image processing device and its control method and program |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2018137540A JP2018137540A (en) | 2018-08-30 |

| JP2018137540A5 JP2018137540A5 (en) | 2020-03-26 |

| JP6882007B2 true JP6882007B2 (en) | 2021-06-02 |

Family

ID=63365780

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017029227A Expired - Fee Related JP6882007B2 (en) | 2017-02-20 | 2017-02-20 | Image processing device and its control method and program |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6882007B2 (en) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7560920B2 (en) | 2020-11-24 | 2024-10-03 | サクサ株式会社 | Image Processing Device |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPWO2009063554A1 (en) * | 2007-11-13 | 2011-03-31 | 富士通株式会社 | Encoding device and decoding device |

| JP6309092B2 (en) * | 2013-10-25 | 2018-04-11 | メディアテック インコーポレイテッド | Method and apparatus for processing a picture having a picture height that is not evenly divisible by slice height and / or a slice width that is not evenly divisible by pixel group width |

-

2017

- 2017-02-20 JP JP2017029227A patent/JP6882007B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2018137540A (en) | 2018-08-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101241971B1 (en) | Image signal processing apparatus, camera system and image signal processing method | |

| JP4337911B2 (en) | Imaging device, imaging circuit, and imaging method | |

| US10638162B2 (en) | Coding method and decoding processing method | |

| JP4508132B2 (en) | Imaging device, imaging circuit, and imaging method | |

| JP2007036566A (en) | Digital signal encoding and decoding apparatus and method | |

| JP2016508700A (en) | Video camera | |

| US10142604B2 (en) | Imaging apparatus and control method thereof | |

| JP4151684B2 (en) | Encoding apparatus, encoding method, encoding program, and imaging apparatus | |

| KR101263887B1 (en) | Image signal processing apparatus, camera system and image signal processing method | |

| JP6512916B2 (en) | Image pickup apparatus, control method thereof and program | |

| KR100793286B1 (en) | Digital image codec with low use of buffer memory and its control method | |

| WO2007091588A1 (en) | Dynamic image decoding device, decoded image recording device, their method, and program | |

| US7567723B2 (en) | Resolution changing method and apparatus | |

| JP6857970B2 (en) | Image coding device and its control method | |

| WO2007148619A1 (en) | Dynamic image decoding device, decoded image recording device, and their method and program | |

| JP6871727B2 (en) | Imaging equipment, image processing methods, and programs | |

| JP5811879B2 (en) | Image processing apparatus and image processing method | |

| JP6700798B2 (en) | Imaging device and control method thereof | |

| JP6882007B2 (en) | Image processing device and its control method and program | |

| US10497093B2 (en) | Image processing apparatus for minimizing deterioration of image quality of a raw image | |

| JP2021078008A (en) | Image processing apparatus, image processing method and imaging apparatus | |

| JP2010154035A (en) | Distortion correction device | |

| JP7020782B2 (en) | Reproduction device and its control method | |

| JP6486120B2 (en) | Encoding apparatus, encoding apparatus control method, and program | |

| JP4720494B2 (en) | Imaging apparatus, imaging method and program, and recording medium |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200207 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200207 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20210103 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210113 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20210125 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210215 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210312 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210402 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20210506 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6882007 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| LAPS | Cancellation because of no payment of annual fees |