JP6844404B2 - Waveform recorder - Google Patents

Waveform recorder Download PDFInfo

- Publication number

- JP6844404B2 JP6844404B2 JP2017090692A JP2017090692A JP6844404B2 JP 6844404 B2 JP6844404 B2 JP 6844404B2 JP 2017090692 A JP2017090692 A JP 2017090692A JP 2017090692 A JP2017090692 A JP 2017090692A JP 6844404 B2 JP6844404 B2 JP 6844404B2

- Authority

- JP

- Japan

- Prior art keywords

- buffer

- circuit

- digital data

- event

- trigger

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000000872 buffer Substances 0.000 claims description 252

- 238000001514 detection method Methods 0.000 claims description 185

- 238000012545 processing Methods 0.000 claims description 157

- 230000004044 response Effects 0.000 claims description 9

- 238000006243 chemical reaction Methods 0.000 claims description 2

- 230000000630 rising effect Effects 0.000 description 34

- 230000007704 transition Effects 0.000 description 33

- 238000000034 method Methods 0.000 description 24

- 230000008569 process Effects 0.000 description 23

- 238000005259 measurement Methods 0.000 description 11

- 238000010586 diagram Methods 0.000 description 10

- 230000006870 function Effects 0.000 description 3

- 230000002093 peripheral effect Effects 0.000 description 3

- 238000012935 Averaging Methods 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000005070 sampling Methods 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- 230000001960 triggered effect Effects 0.000 description 1

Images

Landscapes

- Recording Measured Values (AREA)

- Analogue/Digital Conversion (AREA)

Description

本発明は、アナログ入力信号の波形データを記録する波形記録装置に関する。 The present invention relates to a waveform recording device that records waveform data of an analog input signal.

デジタルオシロスコープ等として用いられる波形記録装置が従来提案されている(例えば、特許文献1,2)。波形記録装置が様々なイベントを取得、観測及び解析できるようにするために、多くのトリガ機能及び検索機能が提案されている。トリガ機能及び検索機能を実現するためにパルス幅トリガを用いる場合、設定されたトリガレベルでのパルス幅を計数クロックでカウントし、カウントしたパルス幅が予め設定されたパルス幅と一致した場合にトリガ信号が生成される。また、波形データを取り込んだ後に所望のイベントを検索して表示する波形記録装置も提案されている。

Waveform recording devices used as digital oscilloscopes and the like have been conventionally proposed (for example,

パルス幅トリガを用いる波形記録装置では、パルス幅をカウントする計測クロックがアナログ入力信号に同期していないので、パルス幅の1カウント分に相当する誤差を許容する必要がある。パルス幅を高精度で検出するためには高周波数の計測クロックを用いる必要があり、波形記録装置のコストが上昇するという不都合がある。 In the waveform recording device using the pulse width trigger, since the measurement clock for counting the pulse width is not synchronized with the analog input signal, it is necessary to allow an error corresponding to one count of the pulse width. In order to detect the pulse width with high accuracy, it is necessary to use a high frequency measurement clock, which has an inconvenience that the cost of the waveform recording device increases.

また、波形データを取り込んだ後に所望のイベントを検索して表示する波形記録装置では、取り込んだ波形データの中に所望のイベントが存在するとは限らない。特に、稀なイベントを検出する場合、波形データの取込みと検索処理を複数回繰り返す必要があり、所望のイベントを高効率に検出することができないという不都合がある。 Further, in a waveform recording device that searches for and displays a desired event after capturing the waveform data, the desired event does not always exist in the captured waveform data. In particular, when detecting a rare event, it is necessary to repeat the acquisition of waveform data and the search process a plurality of times, and there is an inconvenience that a desired event cannot be detected with high efficiency.

本発明の目的は、コストを上昇させることなく信号の波形に関する所望のイベントを高精度かつ高効率に検出することができる波形記録装置を提供することである。 An object of the present invention is to provide a waveform recording device capable of detecting a desired event related to a signal waveform with high accuracy and high efficiency without increasing the cost.

本発明による波形記録装置は、アナログ入力信号をアナログ・デジタル変換することによって生成されたデジタルデータを一時的に記憶するバッファと、トリガ条件に基づいてアナログ入力信号又はデジタルデータからトリガ信号を生成するトリガ回路と、バッファが記憶動作を開始してから終了するまでの期間をトリガ信号に基づいて制御するバッファ制御回路と、バッファが記憶動作を開始してから終了するまでの期間の終了の際にバッファに記憶されたデジタルデータからイベントが検出された場合にイベント検出信号を生成するイベント検出回路と、デジタルデータを取り込み処理することによって生成された波形データを記憶し、イベント検出信号に応答して波形データの記憶を停止するメモリ回路と、を備える。 The waveform recording device according to the present invention generates a trigger signal from an analog input signal or digital data based on a buffer that temporarily stores digital data generated by analog-digital conversion of the analog input signal and a trigger condition. At the end of the trigger circuit, the buffer control circuit that controls the period from the start to the end of the storage operation of the buffer based on the trigger signal, and the period from the start to the end of the storage operation of the buffer. An event detection circuit that generates an event detection signal when an event is detected from the digital data stored in the buffer, and waveform data generated by capturing and processing the digital data are stored and responded to the event detection signal. It includes a memory circuit for stopping the storage of waveform data.

好適には、バッファは、第1のバッファ及び第2のバッファを有し、トリガ回路は、トリガ条件に基づいてアナログ入力信号又はデジタルデータから第1のトリガ信号及び第2のトリガ信号を生成し、バッファ制御回路は、第1のバッファが記憶動作を開始してから終了するまでの期間を第1のトリガ信号に基づいて制御し、第2のバッファが記憶動作を開始してから終了するまでの期間を第2のトリガ信号に基づいて制御し、第1のバッファが記憶動作を終了してから第2のバッファが記憶動作を開始するまでの期間を、第1のトリガ信号及び前記第2のトリガ信号に基づいて制御し、イベント検出回路は、第1のバッファが記憶動作を開始してから終了するまでの期間の終了の際に第1のバッファに記憶されたデジタルデータ及び第2のバッファが記憶動作を開始してから終了するまでの期間の終了の際に第2のバッファに記憶されたデジタルデータからイベントが検出された場合にイベント検出信号を生成する。 Preferably, the buffer has a first buffer and a second buffer, and the trigger circuit generates a first trigger signal and a second trigger signal from an analog input signal or digital data based on a trigger condition. , The buffer control circuit controls the period from the start to the end of the storage operation of the first buffer based on the first trigger signal, and from the start to the end of the storage operation of the second buffer. The period from the end of the storage operation of the first buffer to the start of the storage operation of the second buffer is controlled based on the first trigger signal and the second trigger signal. The event detection circuit controls based on the trigger signal of the first buffer, and the digital data stored in the first buffer and the second buffer at the end of the period from the start to the end of the storage operation of the first buffer. An event detection signal is generated when an event is detected from the digital data stored in the second buffer at the end of the period from the start to the end of the storage operation of the buffer.

好適には、バッファは、複数のバッファを有し、トリガ回路は、トリガ条件に基づいてアナログ入力信号又は前記デジタルデータから複数のトリガ信号を生成し、バッファ制御回路は、バッファが記憶動作を開始してから終了するまでの期間をトリガ信号に基づいて制御し、複数のバッファのうちの予め決められたバッファが記憶動作を終了してから次のバッファが記憶動作を開始するまでの期間の一つ以上を計測し、イベント検出回路は、複数のバッファが記憶動作を開始してから終了するまでの期間の終了の際に複数のバッファに記憶されたデジタルデータからイベントが検出された場合にイベント検出信号を生成する。 Preferably, the buffer has a plurality of buffers, the trigger circuit generates a plurality of trigger signals from the analog input signal or the digital data based on the trigger condition, and the buffer control circuit starts the storage operation of the buffer. The period from the end to the end is controlled based on the trigger signal, and one of the periods from the end of the storage operation of a predetermined buffer among a plurality of buffers to the start of the storage operation of the next buffer. The event detection circuit measures one or more, and an event is detected when an event is detected from the digital data stored in the multiple buffers at the end of the period from the start to the end of the storage operation of the multiple buffers. Generate a detection signal.

好適には、イベント検出回路は、デジタルデータのレベルと予め決定されたレベルのデジタルデータが検出された期間との少なくとも一方に関連するイベントを検出する。 Preferably, the event detection circuit detects an event related to at least one of the level of digital data and the period during which a predetermined level of digital data is detected.

好適には、メモリ回路は、波形データの記憶を停止するタイミングを、トリガ信号が生成されるタイミングとイベント検出信号が生成されるタイミングとの時間差に基づいて調整する。 Preferably, the memory circuit adjusts the timing at which the storage of the waveform data is stopped based on the time difference between the timing at which the trigger signal is generated and the timing at which the event detection signal is generated.

バッファに一時的に記憶されるデジタルデータをデシメーションしてもよい。 Digital data temporarily stored in the buffer may be decimation.

本発明によれば、コストを上昇させることなく信号の波形に関する所望のイベントを高精度かつ高効率に検出することができる。 According to the present invention, a desired event related to a signal waveform can be detected with high accuracy and high efficiency without increasing the cost.

本発明による波形記録装置の実施の形態を、図面を参照しながら説明する。

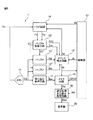

図1は、本発明による波形記録装置の一実施の形態を示す図であり、図2は、図1の一部を詳細に示す図である。図1に示す波形記録装置1は、デジタルオシロスコープ等として用いられ、アナログ入力信号Saが外部から入力される。

An embodiment of the waveform recording apparatus according to the present invention will be described with reference to the drawings.

FIG. 1 is a diagram showing an embodiment of a waveform recording device according to the present invention, and FIG. 2 is a diagram showing a part of FIG. 1 in detail. The

波形記録装置1は、アナログ・デジタル変換器(ADC)11と、バッファ12と、制御部13と、トリガ回路14と、バッファ制御回路15と、イベント検出回路16と、取込み処理回路17と、メモリ回路18と、波形処理及び表示処理回路19と、表示器20と、を備える。

The

制御部13は、例えば、CPUによって構成される。バッファ12、バッファ制御回路15、イベント検出回路16、取込み処理回路17並びに波形処理及び表示処理回路19は、例えば、メモリを内蔵したFPGA(field-programmable gate array)によって構成される。メモリ回路18は、後に説明する波形データDwを記憶するメモリ及びメモリを制御する周辺回路によって構成される。メモリは、例えば、DRAM(dynamic random access memory)によって構成される。周辺回路は、例えば、FPGAによって構成される。表示器20は、例えば、液晶ディスプレイ(LCD)によって構成される。

The

ADC11は、アナログ入力信号SaをデジタルデータDd(例えば、8ビットのデジタル値)に変換し、デジタルデータDdは、バッファ12及び取込み処理回路17に入力される。ADC11のサンプリングレートが1ギガサンプル/秒である場合、デジタルデータDdが1ナノ秒ごとに生成されるが、ADC11の後段のバッファ12並びに取込み処理回路17及びメモリ回路18においてデータ処理を並列化することによって処理速度を低減することができる。例えば、FPGAの内部に設けられた125MHzのシステムクロック(図示せず)を用いた場合、8ナノ秒ごとに8個のデジタルデータDdが並列に処理される。

The

バッファ12は、バッファ制御回路15からの書込み/読出し信号C1に基づいて、デジタルデータDdを一時的に記憶する。本実施の形態では、バッファ12は、書込み/読出し信号C1の立上りによりデジタルデータDdの記憶を開始し、書込み/読出し信号C1の立下りによりデジタルデータDdの記憶を終了し、バッファ12に記憶されたデジタルデータDdをイベント検出回路16に出力する。

The

制御部13は、トリガ条件に関する情報Xtをトリガ回路14に提供する。また、制御部13は、イベントの条件に関する情報Xiをイベント検出回路16に提供する。また、制御部13は、波形データDwの波形処理及び表示処理条件に関する情報Xdを波形処理及び表示処理回路19に提供する。また、制御部13は、メモリ回路18が記憶動作を開始するための指令C2をメモリ回路18に出力する。なお、トリガ条件に関する情報Xt、イベントの条件に関する情報Xi、波形データDwの波形処理及び表示処理条件に関する情報Xd及び指令C2は、例えば、キーボード等の操作部(図示せず)の操作により制御部13に入力される。さらに、制御部13は、後に説明するイベント検出信号Siに応答して、メモリ回路18の記憶動作を終了するとともにメモリ回路18に記憶された波形データDwを読み出すための指令C3をメモリ回路18に出力する。

The

本実施の形態は、イベントの条件に、正パルスの幅及び高さ(最大値)を選択した場合を例にとって説明するが、負パルスを条件にすることも可能である。また、パルスの高さの代わりに平均値等を用いることも可能である。 The present embodiment will be described by taking the case where the width and height (maximum value) of the positive pulse are selected as the condition of the event, but it is also possible to set the condition of the negative pulse. It is also possible to use an average value or the like instead of the pulse height.

本実施の形態では、トリガ条件は、予め設定された閾値レベルThに基づいて検出されるアナログ入力信号Saの立上りエッジ及び立下りエッジである。この場合、トリガ条件に関する情報Xtは、アナログ入力信号Saが閾値レベルThより上になったか否か及びアナログ入力信号Saが閾値レベルThより上になった後に閾値レベルThより下になったか否かの判定を行う旨の条件を含む。 In the present embodiment, the trigger conditions are the rising edge and the falling edge of the analog input signal Sa detected based on the preset threshold level Th. In this case, the information Xt regarding the trigger condition is whether or not the analog input signal Sa is above the threshold level Th and whether or not the analog input signal Sa is above the threshold level Th and then below the threshold level Th. Includes the condition that the judgment is made.

また、本実施の形態では、イベントは、デジタルデータDd(更に詳しくは、後に説明する補間データDh)が閾値レベルThを超えている期間によって規定されるパルス幅Wである。この場合、イベントの条件に関する情報Xiは、デジタルデータDdを補間処理するために用いられる補間倍率H、閾値レベルTh並びに検出すべきパルスのパルス幅W及び最大値Pmを含む。 Further, in the present embodiment, the event is a pulse width W defined by a period during which the digital data Dd (more specifically, the interpolated data Dh described later) exceeds the threshold level Th. In this case, the information Xi regarding the condition of the event includes the interpolation magnification H used for interpolating the digital data Dd, the threshold level Th, the pulse width W of the pulse to be detected, and the maximum value Pm.

トリガ回路14は、予め設定された閾値レベルThに基づいて検出されるアナログ入力信号Saの立上りエッジ及び立下りエッジに応じてトリガ信号T1,T2を生成する。本実施の形態では、トリガ回路14は、アナログ入力信号Saのレベルと閾値レベルThとをコンパレータ(図示せず)を用いて比較し、トリガ回路14に対するディセーブル信号(図示せず)が解除された状態でアナログ入力信号Saが閾値レベルThより上になったときにトリガ信号T1を生成してバッファ制御回路15に送信する(すなわち、トリガ信号T1はローレベルからハイレベルに遷移する。)。また、トリガ回路14は、トリガ回路14に対するディセーブル信号(図示せず)が解除された状態でアナログ入力信号Saが閾値レベルThより上になった後に閾値レベルThより下になったときにトリガ信号T2を生成してバッファ制御回路15に送信する(すなわち、トリガ信号T2はローレベルからハイレベルに遷移する。)。トリガ回路14は、トリガ信号T2をバッファ制御回路15に送信した後にディセーブル状態になる。なお、トリガ回路14は、トリガ信号T1を生成するまではトリガ信号T2を生成しないようにする。また、トリガ信号T1を生成してから所定の時間が経過するまでにアナログ入力信号Saが閾値レベルThより下になった場合には、トリガ回路14は初期化され、トリガ回路14に対するディセーブル信号が解除された状態(すなわち、トリガ信号T1はハイレベルからローレベルに遷移する。)に戻ることによって、無効なイベント検出動作を排除することを可能にする。また、トリガ回路14は、予め設定された閾値レベルThに基づいてデジタルデータDdの立上りエッジ及び立下りエッジを検出し、検出した立上りエッジ及び立下りエッジに応じてトリガ信号T1,T2を生成してもよい。

The

バッファ制御回路15は、デジタルデータDdからイベント(この場合、パルス幅W)を検出するために、バッファ12が記憶動作を開始してから終了するまで期間をトリガ信号T1,T2に基づいて制御する。本実施の形態では、バッファ制御回路15は、トリガ信号T1を受信すると、バッファ12がデジタルデータDdの記憶を開始するために書込み/読出し信号C1をハイレベルにする。また、バッファ制御回路15は、トリガ信号T2を受信すると、デジタルデータDdの記憶を終了してバッファ12に記憶されたデジタルデータDdをイベント検出回路16に出力するために書込み/読出し信号C1をローレベルにする。

The

また、本実施の形態では、バッファ制御回路15は、バッファ12が記憶動作を開始してから終了するまで期間を調整するために、トリガ信号T1,T2が生成された時間の他に種々の要件を考慮する。種々の要件は、例えば、トリガ信号T1の生成からバッファ12の制御までの遅れ時間、トリガ信号T2の生成からバッファ12の制御までの遅れ時間、トリガ信号T1の生成のタイミングとデジタルデータDdのバッファ12への記憶のタイミングとの差、補間処理に必要な余分なデータ数等を含む。種々の要件についての情報を、例えば、操作部の操作を介して制御部13からバッファ制御回路15に提供してもよい。

Further, in the present embodiment, the

イベント検出回路16は、バッファ12が記憶動作を開始してから終了するまで期間の終了の際にバッファ12に記憶されているデジタルデータDdからイベントが検出された場合にイベント検出信号Siを生成する。本実施の形態では、イベント検出回路16は、図2に示すように、イベント検出制御回路16aと、補間処理回路16bと、時間検出処理回路16cと、レベル検出処理回路16dと、イベント判定回路16eと、を有する。

The

イベント検出制御回路16aは、イベントの条件に関する情報Xiが制御部13から提供される。そして、イベント検出制御回路16aは、補間倍率Hについての情報を補間処理回路16bに提供し、閾値レベルThを時間検出処理回路16cに提供し、検出すべきパルスのパルス幅W及び最大値Pmについての情報をイベント判定回路16eに提供する。

In the event

補間処理回路16bは、イベントを検出するためのデジタルデータDdがバッファ12から供給され、補間倍率HでデジタルデータDdの補間処理を行うことによって補間データDhを生成して時間検出処理回路16c及びレベル検出処理回路16dに供給する。補間処理は、一般的なsin(x)/x補間、リニア補間又はこれらの組合せ等を用いることができる。補間倍率Hが100である場合、1ナノ秒ごとのデジタルデータDdは、10ピコ秒ごとの補間データDhに変換される。また、補間処理回路16bは、補間データDhの出力期間に、時間検出信号C11を時間検出処理回路16cに出力する。

The

時間検出処理回路16cは、時間検出信号C11に従って、正スロープ時刻及び負スロープ時刻を検出処理し、レベル検出期間信号C12をレベル検出処理回路16dに出力し、かつ、パルス幅の検出処理結果Dtをイベント判定回路16eに供給する。時間検出処理回路16cは、補間データDhを用いることによって高精度の時間検出が可能になる。時間検出処理においてアナログ入力信号Saのノイズ等に起因する誤測定を防ぐために、一般的に用いられているヒステリシス処理を行ってもよい。また、負スロープ時刻を、後に表示器20に波形を表示する際に時間軸の基準に使用してもよい。

The time

レベル検出処理回路16dは、レベル検出期間信号C12に従って、補間データDhの最大値Lの検出処理結果De(補間データのレベル)を検出処理し、検出処理結果Deをイベント判定回路16eに供給する。

The level

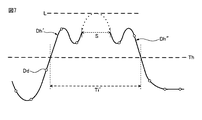

イベント判定回路16eは、バッファ12に記憶されているデジタルデータDdからイベントが検出されたか否かを、検出処理結果Dt及びDe並びにイベント検出条件であるパルス幅W及び最大値Pmに基づいて判定する。図3は、イベント検出回路によって検出される正パルスのイベントの一例を示す図である。図3において、閾値レベルThを横切る正スロープ時刻から負スロープ時刻までの期間Tiは、時間検出処理回路の検出処理結果Dtに対応し、期間Tiにおける補間データDhの最大値Lは、レベル検出処理回路の検出処理結果Deに対応する。イベント判定回路16eは、検出処理結果Dtがパルス幅Wに相当するか否か及び検出処理結果Deが最大値Pmに相当するか否かを判定する。更に詳しくは、イベント判定回路16eは、検出処理結果Dtがパルス幅Wの上限値(例えば、20.1ナノ秒)と下限値(例えば、19.9ナノ秒)の間に存在するか否か及び検出処理結果Deが最大値Pmの上限値と下限値の間に存在するか否かを判定する。

The

図1を参照して、バッファ12に記憶されているデジタルデータDdからイベントが検出された場合、イベント判定回路16eは、イベント検出信号Siを制御部13及びメモリ回路18に供給する。それに対し、バッファ12に記憶されているデジタルデータDdからイベントが検出されなかった場合、イベント判定回路16eは、トリガ回路14に対するディセーブル信号を解除するための解除信号Ssをトリガ回路14に供給する。正スロープ時刻から負スロープ時刻までの期間Tiがパルス幅Wより著しく大きい場合は、時間検出処理回路16cでパルス幅の検出処理結果Dtが正常に検出できない可能性がある。このような場合は、イベント判定回路16eによる判定を待たずに、バッファ制御回路15又は時間検出処理回路16cが解除信号Ssをトリガ回路14に供給してもよい(図示せず)。

With reference to FIG. 1, when an event is detected from the digital data Dd stored in the

取込み処理回路17は、デジタルデータDdの取り込み処理(一定期間ごとのピーク検出及び平均化処理、デシメーション(間引き)等)を行うことによって波形データDwを生成し、生成した波形データDwをメモリ回路18に格納する。デジタルデータDdの取り込み処理を行うための取込みモードを、例えば、操作部の操作を介して制御部13によって選択してもよい。

The

メモリ回路18は、指令C2に応答して波形データDwの記憶動作を開始し、プリトリガ(トリガ発生前)分としてメモリ回路18に記憶すべきデータとして設定された個数分の波形データDwを記憶する。その後、制御部13は、トリガ回路14に対するディセーブル信号を解除する。そして、メモリ回路18は、トリガ回路14に対するディセーブル信号が解除された後も波形データDwの記憶動作を継続し、イベント検出回路16からのイベント検出信号Siを待機する。イベント検出信号Siがイベント検出回路16からメモリ回路18に供給されると、メモリ回路18は、表示器20の表示時間条件に基づいて設定された個数分の波形データDwをポストトリガ(トリガ発生後)分として記憶した後に波形データDwの記憶を停止する。

The

検出されたイベントの時刻を基準にしてメモリ回路18に記憶される波形データDwの個数を制御するために、メモリ回路18は、波形データDwの記憶を停止するタイミングを、トリガ信号T2が生成されるタイミングに基づいて調整するのが好ましい。トリガ信号T2が生成されるタイミングとイベント検出信号Siが生成されるタイミングとの時間差は、例えば、システムクロックでカウントすることによって計測される。また、メモリ回路18に記憶される波形データDwの個数を制御するために、トリガ信号T2が生成されるタイミングとイベント検出信号Siが生成されるタイミングとの時間差を予め予測し、予測した時間差をポストトリガ分として記憶させる波形データDwの個数又はメモリ回路18のオーバーラン(余分な書込み個数)に反映させてもよい。

In order to control the number of waveform data Dw stored in the

メモリ回路18は、指令C3に応答して、波形データDwを読み出し、波形データDwを波形処理及び表示処理回路19に出力する。波形処理及び表示処理回路19は、制御部13から提供された波形データDwの波形処理及び表示処理条件に関する情報Xdに基づいて、波形データDwの波形処理及び表示処理を行う。そして、波形処理及び表示処理回路19は、波形処理及び表示処理が行われた波形データDwdを表示器20に供給し、表示器20は、波形処理及び表示処理が行われた波形データDwdを表示する。

In response to the command C3, the

図4は、図1に示す波形記録装置の波形記録動作を示すフローチャートである。このフローは、波形記録装置1が波形記録動作を開始してからディセーブル期間が解除された後にトリガ信号T1,T2が生成されることを前提にしている。先ず、メモリ回路18は、指令C2に応答して波形データDwの記憶動作を開始する(ステップS1)。この場合、メモリ回路18は、プリトリガ分の波形データDwを記憶してからトリガ回路14に対するディセーブル信号を解除した後も波形データDwの記憶を継続する。

FIG. 4 is a flowchart showing a waveform recording operation of the waveform recording device shown in FIG. This flow is based on the premise that the trigger signals T1 and T2 are generated after the disable period is released after the

次に、トリガ回路14は、トリガ条件(立上りエッジ)に基づいてトリガ信号T1を生成する(ステップS2)。次に、バッファ制御回路15は、トリガ信号T1に応答して書込み/読出し信号C1をハイレベルにし、バッファ12は、書込み/読出し信号C1に応答してデジタルデータDdの記憶を開始する(ステップS3)。

Next, the

次に、トリガ回路14は、トリガ条件(立下りエッジ)に基づいてトリガ信号T2を生成する(ステップS4)。次に、バッファ制御回路15は、トリガ信号T2に応答して書込み/読出し信号C1をローレベルにし、バッファ12は、書込み/読出し信号C1に応答してデジタルデータDdの記憶を終了し、デジタルデータDdを補間処理回路16bに供給する(ステップS5)。

Next, the

次に、補間処理回路16bは、バッファ12から供給されたデジタルデータDdの補間処理を行う(ステップS6)。次に、時間検出処理回路16cは、正スロープ時刻及び負スロープ時刻からパルス幅の検出処理結果Dtを検出処理し、レベル検出処理回路16dは、レベル検出期間信号C12に従って、補間データDhから最大値の検出処理結果Deを検出処理する(ステップS7)。ステップS6及びステップS7は、機能上の手順を説明したものであり、回路動作上は、イベント検出処理する時間を短縮するためにパイプラインで順次処理される。

Next, the

次に、イベント判定回路16eは、バッファ12に記憶されているデジタルデータDdからイベントが検出されたか否かを判定する(ステップS8)。イベントが検出されなかった場合、処理はステップS2に戻る。

Next, the

それに対し、イベントが検出された場合、メモリ回路18は、ポストトリガ分として設定された個数分の波形データDwを記憶した後に波形データDwの記憶を停止する(ステップS9)。次に、波形処理及び表示処理回路19は、メモリ回路18に記憶された波形データDwの波形処理及び表示処理を行い、表示器20は、波形処理及び表示処理が行われた波形データDwdを表示する(ステップS10)。その後、波形記録装置1は処理を終了する。

On the other hand, when an event is detected, the

本実施の形態によれば、メモリ回路18への波形データDwの記憶と並行してバッファ12に記憶されたデジタルデータDdからリアルタイムでイベント検出を行うので、波形記録の中断及び再開の期間の発生を回避することができる。

According to the present embodiment, since the event is detected in real time from the digital data Dd stored in the

また、イベント検出のために用いられるデジタルデータDdはトリガ信号T1,T2の発生タイミングの周辺に限定されるので、高効率のイベント検出が可能である。また、補間データDhを用いたイベント検出を行うことによって、高周波数の計数クロックを用いることなく高精度のイベント検出が可能となり、波形記録装置1のコストの上昇を回避することができる。また、デジタルデータDdの取込み処理から独立したイベント検出が可能となる。さらに、イベント検出の際に時間検出処理及びレベル検出処理を行うことによって、所望のイベントの取得が容易になる。

Further, since the digital data Dd used for event detection is limited to the vicinity of the generation timing of the trigger signals T1 and T2, highly efficient event detection is possible. Further, by performing the event detection using the interpolated data Dh, it is possible to detect the event with high accuracy without using a high frequency counting clock, and it is possible to avoid an increase in the cost of the

さらに、イベントを高精度に検出することが要求されない場合には、バッファ12に記憶するデジタルデータDdをデシメーションすることによって、広いパルス幅を検出することができる。

Further, when it is not required to detect the event with high accuracy, a wide pulse width can be detected by desimating the digital data Dd stored in the

図5は、本発明による波形記録装置の他の実施の形態を示す図であり、図6は、図5の一部を詳細に示す図である。波形記録装置1’は、ADC11と、バッファ12’,12”と、制御部13と、トリガ回路14と、バッファ制御回路15’と、イベント検出回路16’と、取込み処理回路17と、メモリ回路18と、波形処理及び表示処理回路19と、表示器20と、を備える。

FIG. 5 is a diagram showing another embodiment of the waveform recording apparatus according to the present invention, and FIG. 6 is a diagram showing a part of FIG. 5 in detail. The waveform recording device 1'is an

バッファ12’、 バッファ12”、バッファ制御回路15’、イベント検出回路16’、取込み処理回路17並びに波形処理及び表示処理回路19は、例えば、メモリを内蔵したFPGAによって構成される。

The buffer 12', the buffer 12', the buffer control circuit 15', the event detection circuit 16', the

検出すべきイベントであるパルス幅が広くなるに従ってバッファ容量を増大させる必要がある。本実施の形態では、バッファ容量を増大させることなく広いパルス幅を高精度に検出するために、アナログ入力信号Saの立上りエッジ周辺のデジタルデータDdを記憶するバッファ12’及びアナログ入力信号Saの立下がりエッジ周辺のデジタルデータDdを記憶するバッファ12”を用いる。バッファ12’は、第1のバッファの一例であり、バッファ12”は、第2のバッファの一例である。また、バッファ12’及びバッファ12”に記憶するデジタルデータDdのデータ数の情報は、制御部13からバッファ制御回路15’に提供される。

It is necessary to increase the buffer capacity as the pulse width, which is an event to be detected, becomes wider. In the present embodiment, in order to detect a wide pulse width with high accuracy without increasing the buffer capacity, the buffer 12'that stores the digital data Dd around the rising edge of the analog input signal Sa and the standing of the analog input signal Sa. A

バッファ制御回路15’は、広いパルス幅Wを検出するためのデジタルデータDdすなわちアナログ入力信号Saの立上りエッジ周辺のデジタルデータDdをバッファ12’に記憶させるために、バッファ12’が記憶動作を開始してから終了するまでの期間を、トリガ信号T1及び制御部13から提供されたデータ数に基づいて制御する。本実施の形態では、バッファ制御回路15’がトリガ信号T1を受信すると、バッファ制御回路15’は、バッファ12’がデジタルデータDdの記憶を開始するために書込み/読出し信号C1’をハイレベルにする。その後、バッファ制御回路15’は、制御部13から提供されたデータ数をシステムクロックで計数した後に書込み/読出し信号C1’をローレベルにする。バッファ12’は、アナログ入力信号Saの立上りエッジ周辺のデジタルデータDdを記憶した後にデジタルデータDdの記憶を終了し、バッファ12’に記憶されたデジタルデータDdをイベント検出回路16’に出力する。

In the buffer control circuit 15', the buffer 12'starts a storage operation in order to store the digital data Dd for detecting the wide pulse width W, that is, the digital data Dd around the rising edge of the analog input signal Sa in the buffer 12'. The period from the completion to the end is controlled based on the number of data provided by the trigger signal T1 and the

バッファ制御回路15’は、広いパルス幅Wを検出するためのデジタルデータDdすなわちアナログ入力信号Saの立下りエッジ周辺のデジタルデータDdをバッファ12”に記憶させるために、バッファ12”が記憶動作を開始してから終了するまでの期間を、トリガ信号T2及び制御部13から提供されたデータ数に基づいて制御する。本実施の形態では、バッファ制御回路15’がトリガ信号T2を受信すると、バッファ制御回路15’は、バッファ12”がデジタルデータDdの記憶を開始するために書込み/読出し信号C1”をハイレベルにする。その後、バッファ制御回路15’は、制御部13から提供されたデータ数をシステムクロックで計数した後に書込み/読出し信号C1”をローレベルにする。バッファ12”は、アナログ入力信号Saの立下りエッジ周辺のデジタルデータDdを記憶した後にデジタルデータDdの記憶を終了し、バッファ12”に記憶されたデジタルデータDdをイベント検出回路16’に出力する。

In the buffer control circuit 15', the

バッファ制御回路15’は、バッファ12’が記憶を停止してからバッファ12”が記憶を開始するまでの期間を、書込み/読出し信号C1’及び書込み/読出し信号C1”を基にしてシステムクロックを用いて計測する。 The buffer control circuit 15'sets the system clock based on the write / read signal C1'and the write / read signal C1'for the period from when the buffer 12'stops storage to when the buffer 12' starts storage. Use to measure.

また、本実施の形態では、バッファ制御回路15’は、バッファ12’,12”が記憶動作を開始してから終了するまで期間を調整するために、トリガ信号T1,T2が生成された時間の他に種々の要件を考慮する。種々の要件は、例えば、トリガ信号T1の生成からバッファ12’の制御までの遅れ時間、トリガ信号T2の生成からバッファ12”の制御までの遅れ時間、トリガ信号T1の生成のタイミングとデジタルデータDdのバッファ12’への記憶のタイミングとの差、書込み/読出し信号C1’を出力してからバッファ12’が記憶を停止するまでの期間の終了時からバッファ12”の記憶の開始時までの期間、補間処理に必要な余分なデータ数等を含む。種々の要件についての情報を、例えば、操作部の操作を介して制御部13からバッファ制御回路15’に提供してもよい。

Further, in the present embodiment, the buffer control circuit 15'is the time during which the trigger signals T1 and T2 are generated in order to adjust the period from the start to the end of the storage operation of the

図6に示すように、イベント検出回路16’は、イベント検出制御回路16aと、補間処理回路16b’と、時間検出処理回路16c’と、レベル検出処理回路16d’と、イベント判定回路16eと、を有する。

As shown in FIG. 6, the event detection circuit 16' includes an event

バッファ制御回路15’は、バッファ12’が記憶を停止してからバッファ12”が記憶を開始するまでの期間の計測結果Tmを時間検出処理回路16c’に提供する。また、バッファ制御回路15'は、バッファ12'が記憶を停止してからバッファ12"が記憶を開始するまでの期間にレベル検出期間信号C12をレベル検出処理回路16d'に出力する。

The buffer control circuit 15'provides to the time

補間処理回路16b’は、イベントを検出するためのデジタルデータDdがバッファ12’及びバッファ12”から供給され、補間倍率HでデジタルデータDdの補間処理を行うことによって補間データDh’,Dh”を生成して時間検出処理回路16c’に供給する。また、補間処理回路16b’は、補間データDh’の提供期間に時間検出信号C11’を時間検出処理回路16c’に出力し、補間データDh”の提供期間に時間検出信号C11”を時間検出処理回路16c’に出力する。

In the

時間検出処理回路16c’は、時間検出信号C11’に従って、補間データDh’から正スロープ時刻を検出処理し、時間検出信号C11”に従って、補間データDh”から負スロープ時刻を検出処理する。また、時間検出処理回路16c’は、正スロープ時刻及び負スロープ時刻とバッファ制御回路15’から提供された計測結果Tmを演算処理したパルス幅の検出処理結果Dtを、イベント判定回路16eに供給する。時間検出処理回路16c’は、補間データDh’,Dh”及び計測結果Tmを用いることによって高精度の時間検出が可能になる。

The time detection processing circuit 16c'detects and processes the positive slope time from the interpolated data Dh'according to the time detection signal C11', and detects and processes the negative slope time from the interpolated data Dh'according to the time detection signal C11'. Further, the time detection processing circuit 16c'supplyes the pulse width detection processing result Dt obtained by calculating the positive slope time, the negative slope time, and the measurement result Tm provided by the buffer control circuit 15' to the

レベル検出処理回路16d’は、デジタルデータDdがADC11から入力され、レベル検出期間信号C12に従って、デジタルデータDdの最大値の検出処理結果De(デジタルデータのレベル)を検出処理し、イベント判定回路16eに供給する。イベント判定回路16eは、ADC11から入力されたデジタルデータDdを用いることによって、バッファ12’が記憶する期間の終了時からバッファ12”が記憶する期間の開始時までの期間のデジタルデータDdの最大値Lを検出処理することができる。

In the level

図7は、イベント検出回路によって検出されるイベントの他の例を示す図である。イベントが広いパルス幅(例えば、1マイクロ秒)のパルスである場合、バッファ12’の記憶の終了時からバッファ12”の記憶の開始時までの期間Sが設けられる。イベント判定回路16eは、正スロープ時刻から負スロープ時刻までの期間Ti’がパルス幅Wに相当するか否か及びデジタルデータDdの最大値Lが最大値Pmに相当するか否かを判定する。更に詳しくは、イベント判定回路16eは、正スロープ時刻から負スロープ時刻までの期間Ti’が上限値(例えば、1000.1ナノ秒)と下限値(例えば、999.9ナノ秒)の間に存在するか否か及びデジタルデータDdの最大値Lが上限値と下限値の間に存在するか否かを判定する。

FIG. 7 is a diagram showing another example of an event detected by the event detection circuit. When the event is a pulse with a wide pulse width (for example, 1 microsecond), a period S from the end of the storage of the buffer 12'to the start of the storage of the buffer 12' is provided. The

本実施の形態において、最大値Lの検出期間としてバッファ12’の記憶の終了時からバッファ12”の記憶の開始時までの期間Sを設定したが、本実施の形態の変形例として、最大値Lの検出期間を、正スロープ時刻から負スロープ時刻までの期間Ti’に拡張することが可能である。例えば、時間検出処理回路16cが正スロープ時刻以降の補間データDh’及び負スロープ時刻より前の補間データDh”をレベル検出処理回路16d’に提供することによって、レベル検出処理回路16d’は期間Ti’を設定することができる。

In the present embodiment, the period S from the end of the storage of the buffer 12'to the start of the storage of the buffer 12' is set as the detection period of the maximum value L, but as a modification of the present embodiment, the maximum value is set. The detection period of L can be extended to the period Ti'from the positive slope time to the negative slope time. For example, the time

本実施の形態によれば、バッファ12’がアナログ入力信号Saの立上りエッジ周辺のデジタルデータDdを記憶するとともにバッファ12”がアナログ入力信号Saの立下がりエッジ周辺のデジタルデータDdを記憶することによって、バッファ容量を増大させることなく広いパルス幅を高精度に検出することができる。 According to the present embodiment, the buffer 12'stores the digital data Dd around the rising edge of the analog input signal Sa, and the buffer 12' stores the digital data Dd around the falling edge of the analog input signal Sa. , A wide pulse width can be detected with high accuracy without increasing the buffer capacity.

上記実施の形態において、イベントとしてパルス幅を検出する場合について説明したが、パルス幅以外のイベント、例えば、デジタルデータDdのレベルとデジタルデータDdが予め決定されたレベルから検出された期間の少なくとも一方に関連するイベントを検出する場合にも本発明を適用することができる。図8は、イベント検出回路によって検出されるイベントの他の例を示す図である。イベント検出回路16(図1)は、二つの閾値Th’,Th”(Th’<Th”)の間の遷移時間、及び補間データDhの極小値L’と極大値L”によって決定されるヒステリシス量h(極大値L”−極小値L’)によって規定される図8に示すような立上りエッジをイベントとして検出することもできる。この場合、トリガ条件は、予め設定された閾値レベルTh’に基づいて検出されるアナログ入力信号Saの立上りエッジ及び予め設定された閾値レベルTh”に基づいて検出されるアナログ入力信号Saの立上りエッジである。また、トリガ条件に関する情報Xtは、アナログ入力信号Saが閾値レベルTh’より上になったか否か及びアナログ入力信号Saが閾値レベルTh”より上になったか否かの判定を行う旨の条件を含む。 In the above embodiment, the case where the pulse width is detected as an event has been described, but an event other than the pulse width, for example, at least one of the level of the digital data Dd and the period during which the digital data Dd is detected from the predetermined level. The present invention can also be applied to detect events related to. FIG. 8 is a diagram showing another example of an event detected by the event detection circuit. The event detection circuit 16 (FIG. 1) has a hysteresis determined by the transition time between the two threshold values Th', Th'(Th' <Th'), and the minimum value L'and the maximum value L'of the interpolated data Dh. The rising edge as shown in FIG. 8 defined by the quantity h (maximum value L "-minimum value L') can also be detected as an event. In this case, the trigger condition is the rising edge of the analog input signal Sa detected based on the preset threshold level Th'and the rising edge of the analog input signal Sa detected based on the preset threshold level Th'. Further, the information Xt regarding the trigger condition determines whether or not the analog input signal Sa is above the threshold level Th'and whether or not the analog input signal Sa is above the threshold level Th'". Including the conditions of.

イベントに関する情報Xiは、デジタルデータDdを補間処理するために用いられる補間倍率H、閾値レベルTh’,Th”、デジタルデータDdのレベルが閾値レベルTh’から閾値レベルTh”まで上昇するまでに要すべき時間Txを含む。また、イベントに関する情報Xiは、デジタルデータDdのレベルが閾値レベルTh’から閾値レベルTh”まで上昇するまでに検出すべき補間データDhのヒステリシス量Hを含む。 Information about the event Xi is required for the interpolation magnification H used for interpolating the digital data Dd, the threshold level Th', Th ", and the level of the digital data Dd to rise from the threshold level Th'to the threshold level Th". Includes time Tx to be done. Further, the information Xi regarding the event includes a hysteresis amount H of the interpolated data Dh to be detected before the level of the digital data Dd rises from the threshold level Th'to the threshold level Th'.

トリガ回路14は、予め設定された閾値レベルTh’に基づいて検出されるアナログ入力信号Saの立上りエッジ及び予め設定された閾値レベルTh”に基づいて検出されるアナログ入力信号Saの立上りエッジに応答してトリガ信号T1,T2を生成する。この場合、トリガ回路14は、アナログ入力信号Saのレベルと閾値レベルTh’とをコンパレータを用いて比較し、トリガ回路14に対するディセーブル信号が解除された状態でアナログ入力信号Saが閾値レベルTh’より上になったときにトリガ信号T1を生成してバッファ制御回路15に送信する。また、トリガ回路14は、アナログ入力信号Saのレベルと閾値レベルTh”とを別のコンパレータを用いて比較し、トリガ回路14に対するディセーブル信号(図示せず)が解除された状態でアナログ入力信号Saが閾値レベルTh”より上になったときにトリガ信号T2を生成してバッファ制御回路15に送信する。トリガ回路14は、トリガ信号T2をバッファ制御回路15に送信した後にディセーブル状態になる。

The

イベント検出制御回路16aは、補間倍率Hについての情報を補間処理回路16bに提供する。また、イベント検出制御回路16aは、閾値レベルTh’,Th”についての情報を時間検出処理回路16cに提供する。イベント検出制御回路16aは、補間データDhが閾値レベルTh’から閾値レベルTh”まで上昇するまでに要すべき遷移時間Txについての情報をイベント判定回路16eに提供する。さらに、イベント検出制御回路16aは、デジタルデータDdのレベルが閾値レベルTh’から閾値レベルTh”まで上昇するまでに検出すべき補間データDhのヒステリシス量Hについての情報をイベント判定回路16eに提供する。

The event

時間検出処理回路16cは、時間検出信号C11に従って、補間データDhが閾値レベルTh’より上になった時間及び補間データDhが閾値レベルTh”より上になった時間を検出処理し、レベル検出期間信号C12をレベル検出処理回路16dに出力し、遷移時間の検出処理結果Dtをイベント判定回路16eに供給する。

The time

レベル検出処理回路16dは、レベル検出期間信号C12に従って、補間データDhの極小値L’(補間データのレベル)及び極大値L”(補間データのレベル)を検出処理し、補間データDhのヒステリシス量に対応する検出処理結果Deをイベント判定回路16eに供給する。

The level

イベント判定回路16eは、バッファ12に記憶されているデジタルデータDdからイベントが検出されたか否かを、検出処理結果Dt,De、補間データDhが閾値レベルTh’から閾値レベルTh”まで上昇するまでに要すべき遷移時間Tx並びに補間データDhのヒステリシス量Hに基づいて判定する。

The

図8において、補間データDhが閾値レベルTh’を下から上に通過してから閾値レベルTh”を下から上に通過するまでの遷移時間Ti”は時間検出処理回路16cの検出処理結果Dtに対応し、遷移時間Ti”の中で発生する補間データDhの極大値L”と極小値L’の差(ヒステリシス量h)はレベル検出処理回路16dの検出処理結果Deに対応する。

In FIG. 8, the transition time Ti ”from the interpolation data Dh passing the threshold level Th'from the bottom to the top passing the threshold level Th ″ from the bottom to the top is the detection processing result Dt of the time

イベント判定回路16eは、補間データDhの遷移時間Ti”がTxの上限値(例えば、10.1ナノ秒)と下限値(例えば、9.9ナノ秒)の間に存在するか否かを判定する。また、イベント判定回路16eは、ヒステリシス量hが上限値と下限値の間に存在するか否かを判定する。

The

したがって、閾値レベルTh’ 及び閾値レベルTh”に基づいて検出されるアナログ入力信号Saの立上り遷移時間並びに補間データDhが閾値レベルTh’から閾値レベルTh”まで上昇する間に発生する非単調性(ヒステリシス量h)をイベントとして検出することができる。同様に、閾値レベルTh’ 及び閾値レベルTh”に基づいて検出されるアナログ入力信号Saの立下りエッジ遷移時間並びに補間データDhが閾値レベルTh’から閾値レベルTh”まで下降する間に発生する非単調性(ヒステリシス量h)をイベントとして検出することができる。 Therefore, the rising transition time of the analog input signal Sa detected based on the threshold level Th'and the threshold level Th'and the non-monotonicity that occurs while the interpolated data Dh rises from the threshold level Th'to the threshold level Th'. The hysteresis amount h) can be detected as an event. Similarly, the falling edge transition time of the analog input signal Sa detected based on the threshold level Th'and the threshold level Th'and the non-occurrence that occurs while the interpolated data Dh descends from the threshold level Th'to the threshold level Th'. Monotonicity (hysteresis amount h) can be detected as an event.

なお、本実施の形態では、イベント条件にヒステリシス量hを例に説明したが、補間データDhの極小値L’及び極大値L”をイベント条件とすることも可能である。 In the present embodiment, the hysteresis amount h has been described as an example of the event condition, but it is also possible to set the minimum value L'and the maximum value L "of the interpolated data Dh as the event condition.

上記実施の形態において、イベント検出の際に時間検出処理及びレベル検出処理を行う場合について説明したが、イベント検出の際に時間検出処理とレベル検出処理の少なくとも一方を行う場合でも所望のイベントの取得が容易になる。すなわち、イベントがデジタルデータのレベルとデジタルデータが予め決定されたレベルから検出された期間の少なくとも一方に関連する場合でも所望のイベントの取得が容易になる。 In the above embodiment, the case where the time detection process and the level detection process are performed at the time of event detection has been described. However, even when at least one of the time detection process and the level detection process is performed at the time of event detection, a desired event is acquired. Becomes easier. That is, it is easy to obtain the desired event even when the event is related to at least one of the level of the digital data and the period during which the digital data is detected from the predetermined level.

さらに、イベントを高精度に検出することが要求されない場合には、バッファ12に記憶するデジタルデータDdをデシメーションすることによって、長い遷移期間を検出することができる。

Further, when the event is not required to be detected with high accuracy, a long transition period can be detected by desimating the digital data Dd stored in the

図9は、本発明による波形記録装置の他の実施の形態を示す図であり、図10は、図9の一部を詳細に示す図である。波形記録装置1”は、ADC11と、バッファ12a,12b,12c,12dと、制御部13と、トリガ回路14’と、バッファ制御回路15”と、イベント検出回路16”と、取込み処理回路17と、メモリ回路18と、波形処理及び表示処理回路19と、表示器20と、を備える。

FIG. 9 is a diagram showing another embodiment of the waveform recording device according to the present invention, and FIG. 10 is a diagram showing a part of FIG. 9 in detail. The

バッファ12a,12b, 12c,12d、バッファ制御回路15”、イベント検出回路16”、取込み処理回路17並びに波形処理及び表示処理回路19は、例えば、メモリを内蔵したFPGAによって構成される。

The

トリガ回路14’は、予め設定された二つの閾値レベルTh’,Th”(Th’<Th”)に基づいて、アナログ入力信号Saの閾値レベルTh’の立上りエッジに応じてトリガ信号T1’を生成し、閾値レベルTh“の立上りエッジに応じてトリガ信号T2’を生成し、閾値レベルTh”の立下りエッジに応じてトリガ信号T3’を生成し、閾値レベルTh’の立下りエッジに応じてトリガ信号T4’を生成する。本実施の形態で、緩やかなスロープを持つ正パルスのイベント(正スロープの後に負スロープが発生する)を例にとると、トリガ条件に関する情報Xtは、トリガ信号がT1’,T2’,T3’,T4’の順に発生する情報を含む。従って、例えば閾値レベルTh’を超え、かつ、閾値レベルTh”を超えない正のラントパルスがアナログ入力信号Saに入力された場合、すなわち、トリガ信号T1’が発生した後、トリガ信号T2’,T3’が生成されずにトリガ信号T4’が発生する場合には、トリガ回路14’は初期化され、トリガ回路14’に対するディセーブル信号が解除された状態(すなわち、トリガ信号T1’,T2’,T3’,T4’は全てローレベルとする。)に戻ることによって、無効なイベント検出動作を排除することを可能にする。 The trigger circuit 14'sets a trigger signal T1'according to the rising edge of the threshold level Th'of the analog input signal Sa based on two preset threshold levels Th', Th'(Th'<Th'). Generate, generate a trigger signal T2'according to the rising edge of the threshold level Th", generate a trigger signal T3'according to the falling edge of the threshold level Th ", and respond to the falling edge of the threshold level Th'. To generate the trigger signal T4'. In the present embodiment, taking a positive pulse event with a gentle slope (a negative slope occurs after the positive slope) as an example, the information Xt regarding the trigger condition has trigger signals of T1', T2', and T3'. , T4'includes information that occurs in that order. Therefore, for example, when a positive runt pulse that exceeds the threshold level Th'and does not exceed the threshold level Th'is input to the analog input signal Sa, that is, after the trigger signal T1'is generated, the trigger signal T2', When the trigger signal T4'is generated without generating T3', the trigger circuit 14'is initialized and the disable signal for the trigger circuit 14'is released (that is, the trigger signals T1'and T2' are released. , T3'and T4'are all set to the low level.) By returning to the low level, it is possible to eliminate the invalid event detection operation.

本実施の形態によれば、緩やかなスロープを持つパルスイベントに対し、閾値レベルTh’ 及び閾値レベルTh”に基づいて検出されるアナログ入力信号Saの立上り遷移時間並びに立下り遷移時間を高精度で検出するために、アナログ入力信号Saの正スロープにおける閾値レベルTh’の立上りエッジ周辺のデジタルデータDdを記憶するバッファ12aと、閾値レベルTh”の立上りエッジ周辺のデジタルデータDdを記憶するバッファ12bと、アナログ入力信号Saの立下りスロープにおける閾値レベルTh”の立下りエッジ周辺のデジタルデータDdを記憶するバッファ12cと、閾値レベルTh’の立下りエッジ周辺のデジタルデータDdを記憶するバッファ12dと、を用いる。また、バッファ12a,12b,12c,12dに記憶するデジタルデータDdのデータ数の情報は、制御部13からバッファ制御回路15“に提供される。

According to the present embodiment, for a pulse event having a gentle slope, the rising transition time and the falling transition time of the analog input signal Sa detected based on the threshold level Th'and the threshold level Th'are set with high accuracy. In order to detect, a

バッファ制御回路15”は、緩やかな立上りスロープの遷移時間を検出するためのデジタルデータDdすなわちアナログ入力信号Saの閾値レベルTh’の立上りエッジ周辺のデジタルデータDdをバッファ12aに記憶させるために、バッファ12aが記憶動作を開始してから終了するまでの期間を、トリガ信号T1’及び制御部13から提供されたデータ数に基づいて制御する。本実施の形態では、バッファ制御回路15”がトリガ信号T1’を受信すると、バッファ制御回路15”は、バッファ12aがデジタルデータDdの記憶を開始するために書込み/読出し信号C1aをハイレベルにする。その後、バッファ制御回路15”は、制御部13から提供されたデータ数をシステムクロックで計数した後に書込み/読出し信号C1aをローレベルにする。バッファ12aは、アナログ入力信号Saの閾値レベルTh’の立上りエッジ周辺のデジタルデータDdを記憶した後にデジタルデータDdの記憶を終了し、バッファ12aに記憶されたデジタルデータDdをイベント検出回路16”に出力する。

The

バッファ制御回路15”は、緩やかな立上りスロープの遷移時間を検出するためのデジタルデータDdすなわちアナログ入力信号Saの閾値レベルTh”の立上りエッジ周辺のデジタルデータDdをバッファ12bに記憶させるために、バッファ12”が記憶動作を開始してから終了するまでの期間を、トリガ信号T2’及び制御部13から提供されたデータ数に基づいて制御する。本実施の形態では、バッファ制御回路15”がトリガ信号T2’を受信すると、バッファ制御回路15”は、バッファ12bがデジタルデータDdの記憶を開始するために書込み/読出し信号C1bをハイレベルにする。その後、バッファ制御回路15”は、制御部13から提供されたデータ数をシステムクロックで計数した後に書込み/読出し信号C1bをローレベルにする。バッファ12bは、アナログ入力信号Saの閾値レベルTh”の立上りエッジ周辺のデジタルデータDdを記憶した後にデジタルデータDdの記憶を終了し、バッファ12bに記憶されたデジタルデータDdをイベント検出回路16”に出力する。

The

バッファ制御回路15”は、バッファ12aが記憶を停止してからバッファ12bが記憶を開始するまでの期間を、書込み/読出し信号C1a及び書込み/読出し信号C1bを基にしてシステムクロックを用いて計測する。

The

バッファ制御回路15”は、緩やかな立下りスロープの遷移時間を検出するためのデジタルデータDdすなわちアナログ入力信号Saの閾値レベルTh”の立下りエッジ周辺のデジタルデータDdをバッファ12cに記憶させるために、バッファ12cが記憶動作を開始してから終了するまでの期間を、トリガ信号T3’及び制御部13から提供されたデータ数に基づいて制御する。本実施の形態では、バッファ制御回路15”がトリガ信号T3’を受信すると、バッファ制御回路15”は、バッファ12cがデジタルデータDdの記憶を開始するために書込み/読出し信号C1cをハイレベルにする。その後、バッファ制御回路15”は、制御部13から提供されたデータ数をシステムクロックで計数した後に書込み/読出し信号C1cをローレベルにする。バッファ12cは、アナログ入力信号Saの閾値レベルTh”の立下りエッジ周辺のデジタルデータDdを記憶した後にデジタルデータDdの記憶を終了し、バッファ12cに記憶されたデジタルデータDdをイベント検出回路16”に出力する。

The

バッファ制御回路15”は、緩やかな立下りスロープの遷移時間を検出するためのデジタルデータDdすなわちアナログ入力信号Saの閾値レベルTh’の立下りエッジ周辺のデジタルデータDdをバッファ12dに記憶させるために、バッファ12dが記憶動作を開始してから終了するまでの期間を、トリガ信号T4’及び制御部13から提供されたデータ数に基づいて制御する。本実施の形態では、バッファ制御回路15”がトリガ信号T4’を受信すると、バッファ制御回路15”は、バッファ12dがデジタルデータDdの記憶を開始するために書込み/読出し信号C1dをハイレベルにする。その後、バッファ制御回路15”は、制御部13から提供されたデータ数をシステムクロックで計数した後に書込み/読出し信号C1dをローレベルにする。バッファ12dは、アナログ入力信号Saの閾値レベルTh’の立下りエッジ周辺のデジタルデータDdを記憶した後にデジタルデータDdの記憶を終了し、バッファ12dに記憶されたデジタルデータDdをイベント検出回路16”に出力する。

The

バッファ制御回路15”は、バッファ12cが記憶を停止してからバッファ12dが記憶を開始するまでの期間を、書込み/読出し信号C1c及び書込み/読出し信号C1dを基にしてシステムクロックを用いて計測する。

The

また、本実施の形態では、バッファ制御回路15”は、バッファ12a,12b,12c,12dが記憶動作を開始してから終了するまで期間を調整するために、トリガ信号T1’,T2’,T3’,T4’が生成された時間の他に種々の要件を考慮する。種々の要件は、例えば、トリガ信号T1’,T2’,T3’,T4’の生成からバッファ12a,12b,12c,12dの制御までの遅れ時間、トリガ信号T1’,T2’,T3’,T4’の生成のタイミングとデジタルデータDdのバッファ12a,12b,12c,12dへの記憶のタイミングとの差、書込み/読出し信号C1a,C1b,C1c,C1dを出力してからバッファ12a,12b,12c,12dが記憶を停止するまでの期間、補間処理に必要な余分なデータ数等を含む。種々の要件についての情報を、例えば、操作部の操作を介して制御部13からバッファ制御回路15”に提供してもよい。

Further, in the present embodiment, the

図10に示すように、イベント検出回路16”は、イベント検出制御回路16a”と、補間処理回路16b”と、時間検出処理回路16c”と、レベル検出処理回路16d”と、イベント判定回路16e”と、を有する。

As shown in FIG. 10, the

イベント検出制御回路16a”は、補間倍率Hについての情報を補間処理回路16b”に提供し、閾値レベルTh’,Th”を時間検出処理回路16c”に提供し、検出すべきパルスの立上り遷移時間Tr、立下り遷移時間Tf及び最大値Pmについての情報をイベント判定回路16e”に提供する。

The event

バッファ制御回路15”は、バッファ12aが記憶を停止してからバッファ12bが記憶を開始するまでの期間の計測結果Tm’及びバッファ12cが記憶を停止してからバッファ12dが記憶を開始するまでの期間の計測結果Tm”を時間検出処理回路16c”に提供する。また、バッファ制御回路15”は、バッファ12cが記憶を停止してからバッファ12dが記憶を開始するまでの期間にレベル検出期間信号C12をレベル検出処理回路16d”に出力する。

The

補間処理回路16b”は、イベントを検出するためのデジタルデータDdがバッファ12a,12b,12c,12dから供給され、補間倍率HでデジタルデータDdの補間処理を行うことによってそれぞれの補間データDh1,Dh2,Dh3,Dh4を生成して時間検出処理回路16c”に供給する。また、補間処理回路16b”は、それぞれの補間データDh1,Dh2,Dh3,Dh4の提供期間に対応する時間検出信号C11a,C11b,C11c,C11dを時間検出処理回路16c”に出力する。

In the

時間検出処理回路16c”は、時間検出信号C11a,C11bに従って、補間データDh1が閾値レベルTh’より上になった正スロープ開始時刻及び補間データDh2が閾値レベルTh”より上になった正スロープ終了時刻を検出処理する。また、時間検出処理回路16c”は、正スロープ開始時刻及び正スロープ停止時刻とバッファ制御回路15”から提供された計測結果Tm’を演算処理した立上り遷移時間を検出する。同様に、時間検出処理回路16c”は、時間検出信号C11c,C11dに従って、補間データDh3が閾値レベルTh”より下になった負スロープ開始時刻及び補間データDh4が閾値レベルTh’より下になった負スロープ終了時刻を検出処理する。また、時間検出処理回路16c”は、負スロープ開始時刻及び負スロープ停止時刻とバッファ制御回路15”から提供された計測結果Tm”を演算処理した立下り遷移時間を検出する。時間検出処理回路16c”は、立上り遷移時間及び立下り遷移時間からなる検出処理結果Dt”を、イベント判定回路16e”に供給する。時間検出処理回路16c”は、補間データDh1,Dh2,Dh3,Dh4及び計測結果Tm’,Tm”を用いることによって高精度の時間検出が可能になる。

In the time

レベル検出処理回路16d”は、デジタルデータDdがADC11から入力され、レベル検出期間信号C12に従って、デジタルデータDdの最大値の検出処理結果De”(デジタルデータのレベル)を検出処理し、イベント判定回路16e”に供給する。イベント判定回路16e”は、ADC11から入力されたデジタルデータDdを用いることによって、バッファ12bが記憶する期間の終了時からバッファ12cが記憶する期間の開始時までの期間のデジタルデータDdの最大値Lを検出処理することができる。

The level

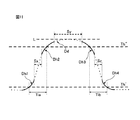

イベント判定回路16e”は、バッファ12a,12b,12c,12dに記憶されているデジタルデータDdからイベントが検出されたか否かを、検出処理結果Dt”及びDe”並びにイベント検出条件であるパルスの立上り遷移時間Tr及び立下り遷移時間Tf及び最大値Pmに基づいて判定する。図11は、イベント検出回路によって検出される緩やかなスロープを持つパルスイベントの例を示す図である。緩やかなスロープを持つパルスイベントの場合、バッファ12aの記憶の終了時からバッファ12bの記憶の開始時までの期間Sx、バッファ12bの記憶の終了時からバッファ12cの記憶の開始時までの期間Sy、バッファ12cの記憶の終了時からバッファ12dの記憶の開始時までの期間Szが設けられる。イベント判定回路16e”は、正スロープが遷移する期間Tiaが立上り遷移時間Trに相当するか否か、負スロープが遷移する期間Tibが立下り遷移時間Tfに相当するか否か、及びデジタルデータDdの最大値Lが最大値Pmに相当するか否かを判定する。

The

本実施の形態によれば、バッファ12a及びバッファ12bがアナログ入力信号Saの立上りスロープの開始周辺及び終了周辺のデジタルデータDdを記憶するとともに、バッファ12c及びバッファ12dがアナログ入力信号Saの立下りスロープの開始周辺及び終了周辺のデジタルデータDdを記憶することによって、バッファ容量を増大させることなく、緩やかなスロープを持つパルスイベントの立上り遷移時間と立下り遷移時間を高精度に検出することができる。

According to the present embodiment, the

上記実施の形態において、バッファを1個、2個又は4個用いる場合について説明したが、バッファを3個又は5個以上用いてもよい。 In the above embodiment, the case where one, two, or four buffers are used has been described, but three or five or more buffers may be used.

1,1’,1” 波形記録装置

11 アナログ・デジタル変換器(ADC)

12,12’,12”,12a,12b,12c,12d バッファ

13 制御部

14,14’ トリガ回路

15,15’,15” バッファ制御回路

16,16’,16” イベント検出回路

16a,16a” イベント検出制御回路

16b,16b’,16b” 補間処理回路

16c,16c’,16c” 時間検出処理回路

16d,16d’,16d” レベル検出処理回路

16e,16e” イベント判定回路

17 取込み処理回路

18 メモリ回路

19 波形処理及び表示処理回路

20 表示器

1,1', 1 "

12, 12', 12 ", 12a, 12b, 12c,

Claims (6)

トリガ条件に基づいて前記アナログ入力信号又は前記デジタルデータからトリガ信号を生成するトリガ回路と、

前記バッファが記憶動作を開始してから終了するまでの期間を前記トリガ信号に基づいて制御するバッファ制御回路と、

前記バッファが記憶動作を開始してから終了するまでの期間の終了の際に前記バッファに記憶されたデジタルデータからイベントが検出された場合にイベント検出信号を生成するイベント検出回路と、

前記デジタルデータを取り込み処理することによって生成された波形データを記憶し、前記イベント検出信号に応答して前記波形データの記憶を停止するメモリ回路と、

を備える波形記録装置。 A buffer that temporarily stores digital data generated by analog-to-digital conversion of analog input signals,

A trigger circuit that generates a trigger signal from the analog input signal or the digital data based on the trigger condition,

A buffer control circuit that controls the period from the start to the end of the storage operation of the buffer based on the trigger signal, and

An event detection circuit that generates an event detection signal when an event is detected from the digital data stored in the buffer at the end of the period from the start to the end of the storage operation of the buffer.

A memory circuit that stores waveform data generated by capturing and processing the digital data and stops storage of the waveform data in response to the event detection signal.

Waveform recording device.

前記トリガ回路は、トリガ条件に基づいて前記アナログ入力信号又は前記デジタルデータから第1のトリガ信号及び第2のトリガ信号を生成し、

前記バッファ制御回路は、前記第1のバッファが記憶動作を開始してから終了するまでの期間を前記第1のトリガ信号に基づいて制御し、前記第2のバッファが記憶動作を開始してから終了するまでの期間を前記第2のトリガ信号に基づいて制御し、前記第1のバッファが記憶動作を終了してから前記第2のバッファが記憶動作を開始するまでの期間を計測し、

前記イベント検出回路は、前記第1のバッファが記憶動作を開始してから終了するまでの期間の終了の際に前記第1のバッファに記憶されたデジタルデータ及び前記第2のバッファが記憶動作を開始してから終了するまでの期間の終了の際に前記第2のバッファに記憶されたデジタルデータからイベントが検出された場合にイベント検出信号を生成する請求項1に記載の波形記録装置。 The buffer has a first buffer and a second buffer.

The trigger circuit generates a first trigger signal and a second trigger signal from the analog input signal or the digital data based on the trigger condition.

The buffer control circuit controls the period from the start of the storage operation of the first buffer to the end of the storage operation based on the first trigger signal, and after the second buffer starts the storage operation. The period until the end is controlled based on the second trigger signal, and the period from the end of the storage operation of the first buffer to the start of the storage operation of the second buffer is measured.

In the event detection circuit, the digital data stored in the first buffer and the second buffer perform the storage operation at the end of the period from the start to the end of the storage operation of the first buffer. The waveform recording device according to claim 1, wherein an event detection signal is generated when an event is detected from the digital data stored in the second buffer at the end of the period from the start to the end.

前記トリガ回路は、トリガ条件に基づいて前記アナログ入力信号又は前記デジタルデータから複数のトリガ信号を生成し、

前記バッファ制御回路は、前記バッファが記憶動作を開始してから終了するまでの期間を前記トリガ信号に基づいて制御し、前記複数のバッファのうちの予め決められたバッファが記憶動作を終了してから次のバッファが記憶動作を開始するまでの期間の一つ以上を計測し、

前記イベント検出回路は、前記複数のバッファが記憶動作を開始してから終了するまでの期間の終了の際に前記複数のバッファに記憶されたデジタルデータからイベントが検出された場合にイベント検出信号を生成する請求項1に記載の波形記録装置。 The buffer has a plurality of buffers and has a plurality of buffers.

The trigger circuit generates a plurality of trigger signals from the analog input signal or the digital data based on the trigger condition.

The buffer control circuit controls the period from the start of the storage operation to the end of the storage operation based on the trigger signal, and a predetermined buffer among the plurality of buffers ends the storage operation. Measure one or more of the period from to the next buffer to the start of storage operation,

The event detection circuit outputs an event detection signal when an event is detected from the digital data stored in the plurality of buffers at the end of the period from the start to the end of the storage operation of the plurality of buffers. The waveform recording device according to claim 1, which is generated.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017090692A JP6844404B2 (en) | 2017-04-28 | 2017-04-28 | Waveform recorder |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017090692A JP6844404B2 (en) | 2017-04-28 | 2017-04-28 | Waveform recorder |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2018189445A JP2018189445A (en) | 2018-11-29 |

| JP2018189445A5 JP2018189445A5 (en) | 2020-03-26 |

| JP6844404B2 true JP6844404B2 (en) | 2021-03-17 |

Family

ID=64478422

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017090692A Active JP6844404B2 (en) | 2017-04-28 | 2017-04-28 | Waveform recorder |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6844404B2 (en) |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4425643A (en) * | 1981-06-08 | 1984-01-10 | Tektronix, Inc. | Multi-speed logic analyzer |

| JPS6193962A (en) * | 1984-10-15 | 1986-05-12 | Anritsu Corp | Oscilloscope with pattern trigger |

| JPS63186153A (en) * | 1987-01-27 | 1988-08-01 | Matsushita Electric Ind Co Ltd | Logic analyzer |

| JPH05264593A (en) * | 1992-03-23 | 1993-10-12 | Yokogawa Electric Corp | Waveform display |

| US7191079B2 (en) * | 2004-03-23 | 2007-03-13 | Tektronix, Inc. | Oscilloscope having advanced triggering capability |

| US7734464B2 (en) * | 2005-05-20 | 2010-06-08 | Tektronix, Inc. | RF autocorrelation signal trigger generator |

| DE102005035394A1 (en) * | 2005-07-28 | 2007-02-15 | Rohde & Schwarz Gmbh & Co Kg | Method and system for digital triggering of signals based on two temporally spaced trigger events |

| US7834780B2 (en) * | 2006-03-20 | 2010-11-16 | Tektronix, Inc. | Waveform compression and display |

| JP2009300112A (en) * | 2008-06-10 | 2009-12-24 | Toshiba Corp | Waveform display device and waveform display method |

| US8374811B2 (en) * | 2009-12-07 | 2013-02-12 | Tektronix, Inc. | High waveform throughput with a large acquisition memory |

-

2017

- 2017-04-28 JP JP2017090692A patent/JP6844404B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2018189445A (en) | 2018-11-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9684066B2 (en) | Light radar signal processing apparatus, systems and methods | |

| US20080174444A1 (en) | Dual acceleration sensor system | |

| US6242900B1 (en) | System for measuring partial discharge using digital peak detection | |

| US7723976B2 (en) | Self-adjusting hold-off trigger | |

| JPS5847661B2 (en) | waveform storage device | |

| JPS5934164A (en) | Corrugated take-in device | |

| US7079060B2 (en) | Test circuit for evaluating characteristic of analog signal of device | |

| US9410989B2 (en) | Oscilloscope with integrated generator and internal trigger | |

| US6586962B2 (en) | Semiconductor device | |

| JP6844404B2 (en) | Waveform recorder | |

| JP2007121189A (en) | Peak detection circuit and radiation measuring apparatus | |

| US20220187351A1 (en) | Waveform measuring method | |

| JP7330400B2 (en) | AD converter | |

| JP2009156790A (en) | Displacement sensor | |

| JPH05119065A (en) | Waveform observation device | |

| JPS59192969A (en) | Digital oscilloscope | |

| JPH07128372A (en) | Signal measuring method | |

| JP2640790B2 (en) | Waveform observation device | |

| JP2005062033A (en) | Time measuring device | |

| JPH01242969A (en) | Signal observing device | |

| JPH04106476A (en) | Waveform measuring apparatus | |

| JPH05276034A (en) | Digitizer | |

| JP2001289891A (en) | Chronometric device | |

| JPH0673227B2 (en) | Magnetic disk characteristics measuring device | |

| JPH06331658A (en) | Digital oscilloscope |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200206 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200217 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20201228 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210126 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20210208 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6844404 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |