[1.パチンコ遊技機の全体構成]

以下、本発明の遊技機としてのパチンコ遊技機について図面を参照して説明する。まず、図1〜図3を参照して実施形態に係るパチンコ遊技機の全体について説明する。図1は実施形態に係るパチンコ遊技機の外枠に対して本体枠を開放し、本体枠に対して扉枠を開放した状態を示す斜視図であり、図2はパチンコ遊技機の正面図であり、図3はパチンコ遊技機の背面図である。

[1. Overall configuration of pachinko gaming machine]

Hereinafter, a pachinko gaming machine as a gaming machine of the present invention will be described with reference to the drawings. First, the entire pachinko gaming machine according to the embodiment will be described with reference to FIGS. 1 to 3. FIG. 1 is a perspective view showing a state in which a main frame is opened to an outer frame of a pachinko gaming machine according to an embodiment and a door frame is opened to the main frame, and FIG. 2 is a front view of the pachinko gaming machine FIG. 3 is a rear view of the pachinko gaming machine.

パチンコ遊技機1は、図1〜図3に示すように、遊技ホールの島設備(図示しない)に設置される外枠2と、外枠2に開閉自在に軸支され前側が開放された箱枠状の本体枠3と、本体枠3に前側から装着固定され遊技媒体としての遊技球が打ち込まれる遊技領域1100を有した遊技盤4と、本体枠3及び遊技盤4の前面を遊技者側から閉鎖するように本体枠3に対して開閉自在に軸支された扉枠5とを備えている。このパチンコ遊技機1の扉枠5には、遊技盤4の遊技領域1100が遊技者側から視認可能となるように形成された遊技窓101と、遊技窓101の下方に配置され遊技球を貯留する皿状の上皿301及び下皿302(図7を参照)と、上皿301に貯留された遊技球を遊技盤4の遊技領域1100内へ打ち込むために遊技者が操作するハンドル装置500と、を備えている。

The pachinko gaming machine 1 is, as shown in FIGS. 1 to 3, an outer frame 2 installed on an island facility (not shown) of the game hall and a box pivotally supported openably and closably on the outer frame 2. A game board 4 having a game area 1100 having a frame-shaped main frame 3 and a main game frame 3 mounted and fixed to the main frame 3 from the front and into which a game ball as a game medium is hit, and the front of the main frame 3 and the game board 4 on the player side And a door frame 5 pivotally supported on the main body frame 3 so as to be closed from the main body frame 3. In the door frame 5 of the pachinko gaming machine 1, a gaming window 101 formed so that the gaming area 1100 of the gaming board 4 can be viewed from the player side, and a gaming ball disposed under the gaming window 101 A tray-shaped upper plate 301 and a lower plate 302 (see FIG. 7), and a handle device 500 operated by the player to drive the gaming balls stored in the upper plate 301 into the gaming area 1100 of the gaming board 4; And.

また、パチンコ遊技機1は、正面視において、外枠2、本体枠3、及び扉枠5がそれぞれ上下方向へ延びた縦長の矩形状に形成されており、それぞれの左右方向の横幅が略同じ寸法とされているとともに、上下方向の縦幅の寸法が、外枠2に対して本体枠3及び扉枠5の寸法が若干短く形成されている。そして、本体枠3及び扉枠5よりも下側の位置において、外枠2の前面に装飾カバー23が取り付けられており、扉枠5及び装飾カバー23によって外枠2の前面が完全に閉鎖されるようになっている。また、外枠2、本体枠3、及び扉枠5は、上端が略揃うようにそれぞれが配置されるとともに、外枠2の左端前側の位置で本体枠3及び扉枠5が回転可能に軸支されており、外枠2に対して本体枠3及び扉枠5の右端が前側へ移動することで開状態となるようになっている。

In front view, the pachinko gaming machine 1 is formed in a vertically long rectangular shape in which the outer frame 2, the main body frame 3 and the door frame 5 extend in the vertical direction, respectively, and the horizontal widths of the respective frames are substantially the same. The dimension of the vertical width in the vertical direction is formed so that the dimensions of the main body frame 3 and the door frame 5 are slightly shorter than the size of the outer frame 2. The decorative cover 23 is attached to the front of the outer frame 2 at a position lower than the body frame 3 and the door frame 5, and the front of the outer frame 2 is completely closed by the door frame 5 and the decorative cover 23. It has become so. Further, the outer frame 2, the main body frame 3 and the door frame 5 are arranged such that the upper ends thereof are substantially aligned, and the main body frame 3 and the door frame 5 are rotatable at a position on the left front side of the outer frame 2. It is supported, and the right end of the main body frame 3 and the door frame 5 is moved forward with respect to the outer frame 2 so as to be in an open state.

また、パチンコ遊技機1は、正面視において、略円形状の遊技窓101を介して遊技球が打ち込まれる遊技領域1100が臨むようになっており、その遊技窓101の下側に前方へ突出するように二つの上皿301及び下皿302が上下に配置されている。また、扉枠5の前面右下隅部には、遊技者が操作するためのハンドル装置500が配置されており、上皿301内に遊技球が貯留されている状態で遊技者がハンドル装置500を回転操作すると、その回転角度に応じた打球強さで上皿301内の遊技球が遊技盤4の遊技領域1100内へ打ち込まれて、遊技をすることができるようになっている。

In front view, the pachinko gaming machine 1 is configured such that the game area 1100 in which the game balls are hit through the substantially circular game window 101 is exposed, and projects forward to the lower side of the game window 101 As such, two upper dishes 301 and lower dishes 302 are disposed up and down. In the front lower right corner of the door frame 5, a handle device 500 for the player to operate is disposed, and the player handles the handle device 500 in a state where the game balls are stored in the upper tray 301. When the rotation operation is performed, the gaming balls in the upper plate 301 are driven into the gaming area 1100 of the gaming board 4 with a hitting strength according to the rotation angle, and it is possible to play a game.

扉枠5の遊技窓101は、透明なガラスユニット590によって閉鎖されており、遊技者から遊技領域1100内を視認することができるものの、遊技者が遊技領域1100内へ手等を挿入して遊技領域1100内の遊技球や障害釘、各種入賞口や役物等に触ることができないようになっている。

Although the game window 101 of the door frame 5 is closed by the transparent glass unit 590, and the player can visually recognize the inside of the game area 1100, the player inserts a hand or the like into the game area 1100 to play a game. It is possible not to touch the game ball or the obstacle nail in the area 1100, the various winning openings, the special effects, and the like.

[2.外枠の全体構成]

次に、遊技ホールの島設備に設置される外枠2について、図4を参照して説明する。図4は外枠の正面斜視図である。外枠2は、図4に示すように、横方向へ延びる上下の上枠板10及び下枠板11と、縦(上下)方向へ延びる左右の側枠板12,13と、それぞれの枠板10,11,12,13の端部を連結する四つの連結部材14と、を備えており、連結部材14で各枠板10,11,12,13同士を連結することで縦長の矩形状(方形状)に組立てられている。外枠2における上枠板10及び下枠板11は、所定厚さの無垢材(例えば、木材、合板、等)により形成されている。なお、上枠板10における左側端部の上面及び前面には、後述する上支持金具20が取り付けられている。

[2. Overall configuration of outer frame]

Next, the outer frame 2 installed on the island facility of the game hall will be described with reference to FIG. FIG. 4 is a front perspective view of the outer frame. The outer frame 2 is, as shown in FIG. 4, upper and lower upper and lower frame plates 10 and 11 extending in the lateral direction, left and right side frame plates 12 and 13 extending in the vertical (vertical) direction, and respective frame plates 10, 11, 12, 13, four connecting members 14 for connecting the end portions, and connecting the frame plates 10, 11, 12, 13 with each other by the connecting members 14 to form a vertically long rectangular ( Square shape). The upper frame plate 10 and the lower frame plate 11 in the outer frame 2 are formed of a solid material (for example, wood, plywood, etc.) of a predetermined thickness. In addition, an upper support fitting 20 described later is attached to the upper surface and the front surface of the left end portion of the upper frame plate 10.

一方、側枠板12,13は、一定断面形状の軽量金属型材(例えば、アルミ合金)とされている。なお、側枠板12,13の外側側面及び内側側面には、上下方向へ延びた複数の溝が形成されており、パチンコ遊技機1を遊技ホールのパチンコ島設備に設置する際等に、作業者の指掛りとなってパチンコ遊技機1を保持し易くすることができるようになっているとともに、外観の意匠性を高められるようになっている。

On the other hand, the side frame plates 12 and 13 are light-weight metal molds (for example, aluminum alloy) having a constant cross-sectional shape. In addition, a plurality of grooves extending in the vertical direction are formed on the outer side surface and the inner side surface of the side frame plates 12 and 13, for example, when installing the pachinko gaming machine 1 in pachinko island facilities of the game hall, etc. The finger of the person makes it easy to hold the pachinko gaming machine 1, and at the same time, the design of the appearance can be enhanced.

外枠2は、上枠板10の左端上面に固定される上支持金具20と、上支持金具20と対向するように配置され左側の側枠板12における下部内側の所定位置に固定される下支持金具21と、下支持金具21の下面を支持するように配置され左右の側枠板12,13を連結するように固定される補強金具22と、補強金具22の前面に固定される装飾カバー23と、を備えている。上支持金具20及び下支持金具21は、本体枠3及び扉枠5を開閉可能に軸支するためのものである。上支持金具20における支持鉤穴20cには、後述する本体枠3における上軸支金具630の軸支ピン633(図5を参照)が着脱自在に係合されるようになっている。下支持金具21における支持突起21dには、後述する本体枠3の本体枠軸支金具644に形成された本体枠軸支が挿入されるようになっており、下支持金具21の支持突起21dを、本体枠3における本体枠軸支金具644の支持穴に挿入した後に、本体枠3の上軸支金具630の軸支ピン633を支持鉤穴20cに係止することにより簡単に本体枠3を開閉自在に軸支することができるようになっている。

The outer frame 2 is disposed so as to face the upper support fitting 20 fixed to the upper surface of the left end of the upper frame plate 10 and the upper support fitting 20 and fixed to a lower inner predetermined position of the left side frame plate 12 A support fitting 21 and a reinforcement fitting 22 arranged to support the lower surface of the lower support fitting 21 and fixed so as to connect the left and right side frame plates 12 and 13, and a decorative cover fixed to the front face of the reinforcement fitting 22 It has 23 and. The upper support fitting 20 and the lower support fitting 21 are for pivotally supporting the main body frame 3 and the door frame 5 so as to be able to open and close. A pivot pin 633 (see FIG. 5) of an upper pivot support 630 of the main body frame 3 described later is detachably engaged with the support hook 20c of the upper support fitting 20. A main frame support formed on a main body frame support bracket 644 of the main body frame 3 described later is inserted into the support protrusion 21 d of the lower support bracket 21, and the support support 21 d of the lower support bracket 21 is After inserting the main frame 3 into the support hole of the main body frame support bracket 644 in the main body frame 3, the main body frame 3 can be easily locked by locking the support pin 633 of the upper shaft support fitting 630 of the main body frame 3 to the support hook hole 20c. It can be pivoted open and close freely.

また、外枠2は、右側の側枠板13の内側に、上下方向に所定距離離反して配置される二つの閉鎖板24,25(図1を参照)が取り付け固定されている。これら閉鎖板24,25は、平面視で略L字状に形成されている。この閉鎖板24,25は、外枠2に対して本体枠3を閉じる際に、本体枠3の開放側辺に沿って取り付けられる錠装置1000(施錠装置)のフック部1054,1065(図1を参照)と係合するものであり、詳細は後述するが、錠装置1000のシリンダ錠1010に鍵を差し込んで一方に回動することにより、フック部1054,1065と閉鎖板24,25との係合が外れて外枠2に対する本体枠3の閉鎖状態を解除することができるものである。

Further, in the outer frame 2, two closing plates 24 and 25 (see FIG. 1) arranged at a predetermined distance apart in the vertical direction are attached and fixed to the inner side of the side frame plate 13 on the right side. The closing plates 24 and 25 are formed in a substantially L shape in plan view. The closing plates 24 and 25 are hook portions 1054 and 1065 of the lock device 1000 (locking device) attached along the open side of the main body frame 3 when the main body frame 3 is closed to the outer frame 2 (FIG. 1). (See below), and the details will be described later, but by inserting a key into the cylinder lock 1010 of the lock device 1000 and turning it to one side, the hook portions 1054, 1065 and the closing plates 24, 25 are The engagement is disengaged, and the closed state of the main body frame 3 with respect to the outer frame 2 can be released.

[3.本体枠の全体構成]

次に、外枠2の前面側に開閉自在に設けられる本体枠3について、図5及び図6を参照して説明する。図5は本体枠の正面斜視図であり、図6は本体枠における基板ユニットの背面斜視図である。本体枠3は、図5に示すように、本体枠3の骨格を形成するとともに前後方向に貫通し遊技盤4を保持するための矩形状の遊技盤保持口601を有した本体枠ベース600と、本体枠ベース600の正面視左側端部の上端及び下端にそれぞれ取り付けられ外枠2に軸支されるとともに扉枠5を軸支するための上軸支金具630及び下軸支金具640と、本体枠ベース600の下部前面に取り付けられ遊技盤4の遊技領域1100内へ遊技球を打ち込むための打球発射装置650と、本体枠ベース600の後側に取り付けられ皿ユニット300の上皿301へ遊技球を払い出すための賞球ユニット700と、本体枠ベース600の前面に取り付けられ本体枠3に対して扉枠5が開いた時に賞球ユニット700から扉枠5の皿ユニット300への遊技球の流れを遮断する球出口開閉ユニット790と、を備えている。

[3. Overall configuration of body frame]

Next, the main body frame 3 provided openably and closably on the front side of the outer frame 2 will be described with reference to FIGS. 5 and 6. FIG. 5 is a front perspective view of the main body frame, and FIG. 6 is a rear perspective view of the substrate unit in the main body frame. As shown in FIG. 5, the main body frame 3 forms a skeleton of the main body frame 3 and has a main frame base 600 having a rectangular game board holding port 601 for penetrating in the front-rear direction and holding the game board 4 An upper shaft support fitting 630 and a lower shaft support bracket 640 mounted on the upper end and the lower end of the left side end of the main body frame base 600 and supported by the outer frame 2 and rotatably supporting the door frame 5; A ball hitting device 650 attached to the lower front of the main frame base 600 for hitting a game ball into the game area 1100 of the game board 4 and a back of the main frame base 600 attached to the upper plate 301 of the dish unit 300 When the door frame 5 is attached to the front of the main body frame base 600 and the door frame 5 is opened to the main body frame 3 from the prize ball unit 700 to the dish unit 300 of the door frame 5 It includes a ball outlet opening and closing unit 790 to shut off the flow of skill sphere, the.

また、本体枠3は、本体枠ベース600の下部後面に取り付けられ遊技盤4を除く扉枠5や本体枠3に備えられた電気的部品を制御するための各種の制御基板や電源基板851等を一纏めにしてユニット化した基板ユニット800と、本体枠ベース600における遊技盤保持口601の後側開口を覆う裏カバー900と、本体枠ベース600の正面視左側端部を被覆する側面防犯板950と、本体枠ベースの正面視右側端部に取り付けられ外枠2に対する本体枠3の開閉施錠、及び本体枠3に対する扉枠5の開閉施錠をする錠装置1000と、を主に備えている。

Further, the main body frame 3 is attached to the lower rear surface of the main body frame base 600, and various control boards for controlling electrical parts provided on the door frame 5 excluding the game board 4 and the main body frame 3 And a back cover 900 covering the rear opening of the game board holding port 601 in the main frame base 600, and a side crime prevention plate 950 covering the left end of the main frame base 600 in a front view And a lock device 1000 attached to the right end of the main frame base in a front view, opening and closing locking of the main frame 3 to the outer frame 2, and locking and closing the door frame 5 to the main frame 3.

[3−1.本体枠ベース]

次に、本体枠ベース600について説明する。本体枠ベース600は、合成樹脂によって一体成形されており、正面視の外形が扉枠5の外形と沿った縦長の矩形状とされているとともに、前後方向に所定量の奥行きを有するように形成されている。本体枠ベース600は、上部から下部へ向かって全体の約3/4の範囲内が前後方向へ矩形状に貫通し遊技盤4の外周を嵌合保持可能な遊技盤保持口601と、本体枠ベース600の正面視左辺を除く前端外周を形成するコ字状の前端枠部602と、前端枠部602の前面から後方へ向かって窪み、扉枠5における扉枠ベース本体110の下端から後方へ突出した扉枠突片110c(図1を参照)、扉枠5の補強ユニット150における上側補強板金151の後方へ突出した上側の屈曲突片167(図1を参照)及び開放側補強板金153の後方へ突出した開放側外折曲突片164(図1を参照)が挿入係合される係合溝603と、を備えている。

[3-1. Body frame base]

Next, the main body frame base 600 will be described. The main body frame base 600 is integrally formed of a synthetic resin, and is formed so as to have a vertically long rectangular shape along the outer shape of the door frame 5 and a predetermined amount of depth in the front-rear direction. It is done. The main unit frame base 600 has a game board holding port 601 capable of fittingly holding the outer periphery of the game board 4 through a rectangular shape penetrating in the front-rear direction within a range of about 3/4 of the whole from the upper part to the lower part; A U-shaped front end frame portion 602 forming the front end outer periphery excluding the front side left side of the base 600 and a recess from the front surface of the front end frame portion 602 rearwardly from the lower end of the door frame base main body 110 in the door frame 5 The protruding door frame protruding piece 110c (see FIG. 1), the upper bent protruding piece 167 (see FIG. 1) protruding rearward of the upper reinforcing sheet metal 151 in the reinforcing unit 150 of the door frame 5, and the open side reinforcing sheet metal 153 And an engaging groove 603 into which the open side outward bent protruding piece 164 (see FIG. 1) protruding rearward is inserted and engaged.

また、本体枠ベース600は、遊技盤保持口601の下側から本体枠ベース600下端まで延出し前端枠部602の前端から所定量後側へ窪み左右方向へ板状に広がった下部後壁部604と、前端枠部602よりも内側で後方へ突出し遊技盤保持口601の内周壁を形成する周壁部605と、を備えている。周壁部605によって、コ字状の前端枠部602の自由端部(正面視で上下の左側端部)同士が連結されるようになっており、本体枠ベース600の外形が枠状となるようになっている。

Further, the main body frame base 600 extends from the lower side of the game board holding port 601 to the lower end of the main body frame base 600 and is recessed downward by a predetermined amount from the front end of the front end frame portion 602 A peripheral wall portion 605 which protrudes rearward inside the front end frame portion 602 and which forms an inner peripheral wall of the game board holding port 601 is provided. The free end portion (upper and lower left end portions in front view) of the U-shaped front end frame portion 602 is connected by the peripheral wall portion 605 so that the outer shape of the main body frame base 600 becomes a frame shape. It has become.

また、本体枠ベース600は、下部後壁部604の上端に遊技盤保持口601の下辺を形成すると共に遊技盤4が載置される遊技盤載置部606と、遊技盤載置部606の左右方向略中央から上方へ突出し遊技盤4における遊技パネル1150のアウト球排出溝と係合する位置決め突起607と、周壁部605における正面視右側内壁の所定位置に形成され遊技盤4の遊技盤止め具1120が止め付けられる遊技盤係止部と、周壁部605の上側内壁から下方へ垂下し下端が遊技盤4の上端と当接可能な板状で左右方向に複数配置された上端規制リブ609と、を備えている。本体枠ベース600の位置決め突起607は、遊技盤4のアウト球排出溝と嵌合することで、遊技盤4の下端が左右方向及び後方向へ移動するのを規制することができるようになっている。また、遊技盤係止部は、遊技盤4の遊技盤止め具1120が係止されることで遊技盤4の正面視右辺が前後方向へ移動するのを規制することができるようになっている。なお、遊技盤4の正面視左辺は、詳細は後述するが、側面防犯板950の位置決め部材956によって前後方向への移動が規制されるようになっている。

In addition, the main frame base 600 forms the lower side of the game board holding port 601 at the upper end of the lower rear wall portion 604 and the game board placement unit 606 on which the game board 4 is placed; Positioning projections 607 that project upward from substantially the center in the left-right direction and engage with the outer ball discharge grooves of the game panel 1150 on the game board 4 and are formed at predetermined positions on the right inner wall of the peripheral wall 605 in front view The game board locking portion to which the tool 1120 is fixed, and the upper end regulating rib 609 hanging down from the upper inner wall of the peripheral wall portion 605 and having a plurality of lower ends arranged in the left and right direction. And have. The positioning projection 607 of the main body frame base 600 can be engaged with the out ball discharge groove of the game board 4 to restrict the movement of the lower end of the game board 4 in the left and right direction and the back direction There is. In addition, the game board locking portion can restrict movement of the right side in a front view of the game board 4 in the front-rear direction by locking the game board fastener 1120 of the game board 4 . In addition, although the details will be described later, the movement of the side crime prevention plate 950 in the front-rear direction is restricted by the positioning member 956 of the game board 4 in a front view.

また、本体枠ベース600は、下部後壁部604が前端枠部602の前面よりも後側へ一段窪んだ位置に形成されており、下部後壁部604の正面視右側前面に、打球発射装置650の発射ソレノイド654がソレノイド収容凹部内に収容されるように前側から打球発射装置650が取り付けられるようになっている。この下部後壁部604の前面に打球発射装置650を取り付けた状態では、打球発射装置650における発射レール660の上端よりも正面視左側に、左方向及び下方へ広がったファール空間626が形成されるようになっている。本実施形態では、本体枠3に対して扉枠5を閉じた状態とすると、ファール空間626の下部にファールカバーユニット540におけるファール球入口542e(図1を参照)が位置するようになっており、ファール空間626を下降した遊技球が、ファールカバーユニット540のファール球入口542eに受けられて、皿ユニット300における下皿302(図7を参照)へ排出されるようになっている。

Further, the main frame base 600 is formed at a position where the lower rear wall portion 604 is recessed one step rearward from the front surface of the front end frame portion 602, and the ball hitting and launching device is on the front right side of the lower rear wall portion 604 in front view. A striking launcher 650 is mounted from the front side so that the 650 launch solenoids 654 are accommodated in the solenoid accommodating recess. With the hitting and launching apparatus 650 attached to the front of the lower rear wall 604, a far space 626 extending leftward and downward is formed on the left side of the firing rail 660 in the hitting and launching apparatus 650 in a front view. It is supposed to be. In the present embodiment, when the door frame 5 is closed with respect to the main body frame 3, the ball entrance 542e (see FIG. 1) of the far cover unit 540 is located below the far space 626. The gaming ball having descended the far space 626 is received by the far ball inlet 542 e of the far cover unit 540 and discharged to the lower plate 302 (see FIG. 7) in the dish unit 300.

また、本体枠ベース600は、正面視で下部後壁部604の左右中央よりも左側に前後方向へ矩形状に貫通する開口部と、開口部の上側及び正面視左右両側に複数形成され前後方向に貫通した透孔615と、を備えている。この本体枠ベース600の開口部は、前側から中継端子板カバー692によって閉鎖されるようになっており、中継端子板カバー692の開口692aを通して、下部後壁部604の後面に取り付けられた基板ユニット800の主扉中継端子板880と周辺扉中継端子板882とが前側へ臨むようになっている。

Also, the main frame base 600 has a plurality of openings formed in a rectangular shape in the front-rear direction on the left side of the lower rear wall 604 in the front-rear direction and a plurality of openings on the upper side and front-rear left and right sides And a through hole 615 penetrating through the The opening of the body frame base 600 is closed from the front side by the relay terminal board cover 692, and the board unit attached to the rear surface of the lower rear wall 604 through the opening 692 a of the relay terminal board cover 692. A main door relay terminal plate 880 and a peripheral door relay terminal plate 882 of 800 are arranged to face the front side.

また、本体枠ベース600は、正面視で下部後壁部604の右端上部に前後方向に貫通した略円形のシリンダ錠貫通穴611の下側前面に、本体枠3に対する扉枠5の開放を検出するための扉枠開放スイッチ618が取り付けられており、本体枠3に対して扉枠5が開かれる(開放される)と、その押圧が解除されて扉枠5の開放を検出することができるようになっている。また、本体枠ベース600は、扉枠開放スイッチ618が取り付けられた位置よりも下側後面に、外枠2に対する本体枠3の開放を検出するための本体枠開放スイッチ619が取り付けられており、外枠2に対して本体枠3が開かれる(開放される)と、その押圧が解除されて本体枠3の開放を検出することができるようになっている。

Further, the main body frame base 600 detects the opening of the door frame 5 with respect to the main body frame 3 on the lower front surface of the substantially circular cylinder lock through hole 611 penetrating in the front-rear direction at the upper right end of the lower rear wall portion 604 in front view When the door frame 5 is opened (opened) with respect to the main body frame 3, the pressing is released and the opening of the door frame 5 can be detected. It is supposed to be. Further, a main body frame open switch 619 for detecting the opening of the main body frame 3 with respect to the outer frame 2 is attached to the main body frame base 600 on the rear side lower than the position where the door frame open switch 618 is attached. When the main body frame 3 is opened (opened) with respect to the outer frame 2, the pressure is released and the opening of the main body frame 3 can be detected.

[3−2.上軸支金具及び下軸支金具]

次に、上軸支金具630及び下軸支金具640について説明する。上軸支金具630及び下軸支金具640は、本体枠ベース600の正面視左端上下後面の金具取付部に、所定のビスを用いてそれぞれ取り付けることで、本体枠3に対して扉枠5を開閉可能に軸支することができるとともに、外枠2に対して本体枠3を開閉可能に軸支させることができるものである。

[3-2. Upper shaft support and lower shaft support]

Next, the upper shaft support 630 and the lower shaft support 640 will be described. The upper shaft bracket 630 and the lower shaft bracket 640 are attached to the bracket mounting portions on the upper left end upper and lower rear surfaces of the main body frame base 600 using a predetermined screw, so that the door frame 5 is fixed to the main body frame 3 The main frame 3 can be pivotally supported on the outer frame 2 so as to be capable of opening and closing.

上軸支金具630は、本体枠ベース600の上側の金具取付部に取り付けられ上下左右方向へ広がる板状の取付部631と、取付部631の上端から前方へ延出する板状の前方延出部632と、前方延出部632の前端付近から上方へ延びだすように突設された軸支ピン633と、軸支ピン633の正面視左側に配置され扉枠5の軸ピン155(図7を参照)が挿入される上下方向に貫通した扉枠軸支穴634と、前方延出部632の正面視左側端部から下方へ垂下し扉枠5の開放側への回動端を規制するストッパと、を備えている。上軸支金具630は、取付部631、前方延出部632、及びストッパが、一枚の金属板を屈曲成形することで一体的に形成されている。

The upper shaft support fitting 630 is a plate-like attachment portion 631 attached to the upper side bracket attachment portion of the main body frame base 600 and extending in the vertical and horizontal directions, and a plate-like front extension extending forward from the upper end of the attachment portion 631 7, a pivot pin 633 projecting upward from near the front end of the front extension 632 and a pivot pin 155 of the door frame 5 disposed on the left side of the pivot pin 633 in a front view. (See above) is inserted downward in the vertical direction through which the door frame shaft support hole 634 is inserted and the pivoting end to the open side of the door frame 5 hanging down from the left end of the front extension portion 632 in front view And a stopper. In the upper shaft support fitting 630, the mounting portion 631, the front extension portion 632, and the stopper are integrally formed by bending a single metal plate.

下軸支金具640は、扉枠5を軸支するための扉枠軸支金具642と、扉枠軸支金具642の下側に配置され外枠2に対して本体枠3を軸支するための本体枠軸支金具644と、を備えている。下軸支金具640における扉枠軸支金具642は、本体枠ベース600の下側の金具取付部に取り付けられ上下左右方向へ広がる板状の取付部と、取付部の下端から前方へ延出する板状の前方延出部642bと、前方延出部642bの前端付近に上下方向へ貫通し扉枠5の軸ピン157(図7を参照)が挿入される扉枠軸支穴642cと、前方延出部642bの正面視左側端部から上方へ立設され扉枠5の開放側への回動端を規制するストッパ642dと、を備えている。この扉枠軸支金具642は、取付部、前方延出部642b、及びストッパ642dが、一枚の金属板を屈曲成形することで一体的に形成されている。

The lower shaft support bracket 640 is disposed on the lower side of the door frame shaft support bracket 642 for supporting the door frame 5 and the door frame shaft support bracket 642 and supports the main frame 3 with respect to the outer frame 2. And a main body frame shaft support bracket 644. The door frame shaft support bracket 642 in the lower shaft support bracket 640 is attached to the lower bracket mounting portion of the main body frame base 600 and extends forward from the lower end of the mounting portion and a plate-shaped mounting portion extending in the vertical and horizontal directions. A plate-like front extension part 642b, a door frame shaft support hole 642c which penetrates vertically in the vicinity of the front end of the front extension part 642b and into which the shaft pin 157 (see FIG. 7) of the door frame 5 is inserted A stopper 642 d is provided to stand upward from a left end in a front view of the extension portion 642 b and to restrict the pivoting end of the door frame 5 to the opening side. In the door frame shaft support fitting 642, the mounting portion, the front extension portion 642b, and the stopper 642d are integrally formed by bending and forming a single metal plate.

また、下軸支金具640における本体枠軸支金具644は、本体枠ベース600の下側の金具取付部に取り付けられ上下左右方向へ広がる板状の取付部と、取付部の下端から前方へ延出する前方延出部644bと、前方延出部644b前端付近に上下方向へ貫通した本体枠軸支穴と、を備えている。本体枠軸支金具644もまた、取付部、及び前方延出部644bが、一枚の金属板を屈曲成形することで一体的に形成されている。

Further, the main frame support bracket 644 in the lower shaft support 640 is attached to the lower bracket mounting portion of the main frame base 600 and extends forward from the lower end of the mounting portion and a plate-like mounting portion extending in the vertical and horizontal directions. A forwardly extending portion 644b is provided, and a body frame shaft support hole vertically penetrates in the vicinity of the front end of the forwardly extending portion 644b. Also in the body frame shaft support bracket 644, the mounting portion and the front extension portion 644b are integrally formed by bending a single metal plate.

下軸支金具640は、扉枠軸支金具642の取付部と本体枠軸支金具644の取付部とが前後方向に重なった(接した)状態とされるとともに、扉枠軸支金具642の前方延出部642bと本体枠軸支金具644の前方延出部644bとが上下方向に所定距離離間した状態で、本体枠ベース600における下側の金具取付部に取り付けられるようになっている。

The lower shaft support bracket 640 is in a state where the mounting portion of the door frame shaft support bracket 642 and the mounting portion of the body frame shaft support bracket 644 overlap (contact) in the front-rear direction. The front extension portion 642 b and the front extension portion 644 b of the main body frame support bracket 644 are attached to the lower metal fitting attachment portion of the main body frame base 600 with a predetermined distance in the vertical direction.

上軸支金具630及び下軸支金具640は、本体枠ベース600に取り付けた状態で、上軸支金具630の軸支ピン633と、下軸支金具640の本体枠軸支穴とが同軸上に位置するようになっており、下軸支金具640における本体枠軸支金具644の本体枠軸支穴が、外枠2における下支持金具21の支持突起21d(図4を参照)に嵌合挿入されるように、本体枠軸支金具644の前方延出部644bを、下支持金具21の支持突出片21c(図4を参照)上に載置した上で、上軸支金具630の軸支ピン633を、外枠2における上支持金具20の支持鉤穴20c(図4を参照)内に挿入することで、本体枠3を外枠2に対して開閉可能に軸支させることができるようになっている。

When the upper shaft support bracket 630 and the lower shaft support bracket 640 are attached to the body frame base 600, the shaft support pin 633 of the upper shaft support bracket 630 and the body frame shaft support hole of the lower shaft support bracket 640 are coaxial. The main frame support hole of the main frame support 644 in the lower support 640 is engaged with the support projection 21d of the lower support 21 in the outer frame 2 (see FIG. 4). The front extension part 644b of the main body frame shaft support bracket 644 is placed on the support projecting piece 21c (see FIG. 4) of the lower support bracket 21 so as to be inserted, and then the shaft of the upper shaft support bracket 630 By inserting the support pin 633 into the support hole 20c (see FIG. 4) of the upper support fitting 20 in the outer frame 2, the main body frame 3 can be pivotally supported on the outer frame 2 so as to be able to open and close. It is supposed to be.

また、上軸支金具630及び下軸支金具640は、本体枠ベース600に取り付けた状態で、上軸支金具630の扉枠軸支穴634と、下軸支金具640の扉枠軸支穴642cとが同軸上に位置するようになっており、下軸支金具640における扉枠軸支金具642の扉枠軸支穴642cに、扉枠5の軸ピン157が挿入されるように扉枠5の下軸支部158(図7を参照)を扉枠軸支金具642の前方延出部642b上に載置した上で、扉枠5の軸ピン155を、上軸支金具630の扉枠軸支穴634に挿入することで、本体枠3に対して扉枠5を開閉可能に軸支することができるようになっている。なお、本実施形態では、扉枠5の上側の軸ピン155は、上下方向へ摺動可能とされており、上軸支金具630の扉枠軸支穴634へ挿入させる際に、軸ピン155を一旦、下方へスライドさせて、扉枠5の上軸支部156と上軸支金具630の前方延出部632とが上下に重なるようにした上で、軸ピン155を上方へスライドさせることで扉枠軸支穴634へ挿入することができるようになっている。

Also, with the upper shaft support 630 and the lower shaft support 640 attached to the body frame base 600, the door frame shaft support hole 634 of the upper shaft support 630 and the door frame support hole of the lower shaft support 640 The door frame is configured such that the shaft pin 157 of the door frame 5 is inserted into the door frame shaft support hole 642 c of the door frame shaft support bracket 642 in the lower shaft support bracket 640 with the position 642 c coaxially positioned. After placing the lower shaft support portion 158 (see FIG. 7) on the front extension portion 642b of the door frame support bracket 642, the shaft pin 155 of the door frame 5 is mounted on the door frame of the upper shaft support fitting 630. The door frame 5 can be pivotally supported on the main body frame 3 so as to be openable and closable by inserting the shaft support hole 634 into the main body frame 3. In the present embodiment, the upper shaft pin 155 of the door frame 5 is slidable in the vertical direction, and the shaft pin 155 is inserted into the door frame shaft support hole 634 of the upper shaft support bracket 630. By sliding the shaft pin 155 upward after the upper shaft support portion 156 of the door frame 5 and the front extension portion 632 of the upper shaft support bracket 630 overlap vertically. It can be inserted into the door frame shaft support hole 634.

[3−3.打球発射装置]

次に、打球発射装置650について説明する。打球発射装置650は、本体枠ベース600における下部後壁部604の前面所定位置に取り付けられる金属板の発射ベース652と、発射ベース652の下部後面に前側へ回転駆動軸654aが突出するように取り付けられる発射ソレノイド654と、発射ソレノイド654の回転駆動軸654aに一体回転可能に固定される打球槌656と、打球槌656の先端に固定される槌先658と、槌先658の移動軌跡上における所定位置を基端として正面視斜め左上へ延出し発射ベース652の前面に取り付けられる発射レール660と、発射レール660の基端上部に発射レール660との間で打球槌656先端の槌先658が通過可能とされると同時に遊技球が通過不能な隙間を形成し発射レール660の基端に遊技球を保持する球止め片662と、球止め片662によって発射レール660の基端に保持された遊技球を打球可能な打球位置よりも打球槌656(槌先658)が発射レール660側へ回動するのを規制するストッパ664と、を備えている。

[3-3. Ball hitting launcher]

Next, the hitting and launching apparatus 650 will be described. The ball hitting and launching apparatus 650 is mounted on a lower base of a lower rear wall 604 of the main frame base 600 at a predetermined position on a front surface of a metal plate, and a rotary drive shaft 654 a protrudes forward on the lower rear surface of the firing base 652. A firing solenoid 654, a hitting ball 656 fixed integrally to the rotational drive shaft 654a of the firing solenoid 654, a tip 658 fixed to the tip of the hitting ball 656, and a predetermined position on the movement locus of the tip 658 The tip end of the hitting ball 656 passes between the firing rail 660 attached to the front end of the firing base 660 and the firing rail 660 attached to the front end of the firing rail 660. A ball stop that holds the game ball at the base end of the firing rail 660 by forming a clearance that the game ball can not pass at the same time as it is made possible 662 and a stopper for restricting the pivoting of the hitting ball 656 (the tip 658) to the side of the firing rail 660 than the hitting position where it is possible to hit the game ball held at the base end of the firing rail 660 by the ball stopper 662 And 664.

この打球発射装置650における発射ソレノイド654は、詳細な図示は省略するが、回転駆動軸654aがハンドル装置500の回転操作角度に応じた強さ(速さ)で往復回動するようになっている。また、打球発射装置650の打球槌656は、発射ソレノイド654の回転駆動軸654aに固定される固定部656aと、固定部656aから緩やかな円弧状に延出し先端が回転駆動軸654aの軸心に対して法線方向を向き先端に槌先658が固定される棹部656bと、棹部656bに対して固定部656aを挟んで反対側へ延出しストッパ664と当接可能なストッパ部656cと、を備えている。打球槌656のストッパ部656cがストッパ664と当接することで、先端の槌先658が打球位置(正面視で反時計周りの方向の回動端)よりも発射レール660側へ回動するのが規制されるようになっている。

Although not shown in detail, the firing solenoid 654 in the hitting and launching apparatus 650 reciprocates and rotates the rotation drive shaft 654a at a strength (speed) according to the rotation operation angle of the handle device 500. . The hitting rod 656 of the hitting and launching apparatus 650 has a fixing portion 656a fixed to the rotation drive shaft 654a of the firing solenoid 654, a gentle arc extending from the fixing portion 656a, and a tip end is at the axial center of the rotation drive shaft 654a. A collar portion 656b to which the tip 658 is fixed at the tip with the normal direction directed, and a stopper portion 656c which can contact the stopper 664 extending to the opposite side across the fixing portion 656a with respect to the collar portion 656b; Is equipped. When the stopper portion 656c of the hitting ball 656 abuts against the stopper 664, the tip of the tip end 658 is pivoted toward the firing rail 660 than the hitting position (rotation end in the counterclockwise direction in front view) It is supposed to be regulated.

打球発射装置650は、本体枠ベース600の下部後壁部604に取り付けた状態においては、発射レール660の上端が左右方向の略中央で下部後壁部604の上端、つまり、遊技盤載置部606(遊技盤保持口601の下辺)よりも下方に位置するようになっており、遊技盤保持口601に保持された遊技盤4における外レール1111の下端との間で、左右方向に所定幅で下方へ広がったファール空間626が形成されるようになっている。そして、打球発射装置650は、発射レール660よりも正面視左側のファール空間626を飛び越えるようにして遊技球を発射することで、遊技盤4の遊技領域1100内へ遊技球を打ち込むことができるようになっている。なお、本体枠3に対して扉枠5を閉じた状態においては、ファール空間626の下部に、扉枠5に取り付けられるファールカバーユニット540のファール球入口542eが位置するようになっており、遊技領域1100内へ打ち込まれずにファール球となった遊技球が、ファール空間626を落下してファール球入口542eへ受け入れられて、下皿302へ排出されるようになっている。

In a state where the striking device firing device 650 is attached to the lower rear wall portion 604 of the main body frame base 600, the upper end of the firing rail 660 is substantially at the center in the lateral direction and the upper end of the lower rear wall portion 604, that is, the game board mounting portion 606 (lower side of the game board holding port 601) is positioned lower than the lower end of the outer rail 1111 of the game board 4 held in the game board holding port 601 and has a predetermined width in the left-right direction A far space 626 is formed to extend downward. And, the ball hitting device 650 can hit the game ball into the game area 1100 of the game board 4 by firing the game ball so as to jump over the far space 626 on the left side of the launch rail 660 in a front view. It has become. In the state where the door frame 5 is closed with respect to the main body frame 3, the ball entry 542e of the far cover unit 540 attached to the door frame 5 is positioned at the lower part of the far space 626. A game ball that has become a foul ball without being driven into the area 1100 falls in the far space 626, is received by the far ball inlet 542e, and is discharged to the lower tray 302.

[3−4.賞球ユニット]

次に、賞球ユニット700について説明する。パチンコ遊技機1を設置するホールにおけるパチンコ島設備において、パチンコ島設備側からパチンコ遊技機1へ供給された遊技球を貯留した上で、所定の払出指示に基づいてパチンコ遊技機1の上皿301へ払い出すものである。この賞球ユニット700は、本体枠ベース600の後面に取り付けられる賞球ベース710と、賞球ベース710の後面上部に取り付けられパチンコ島設備側から供給される遊技球を受けると共に貯留する賞球タンク720と、賞球タンク720の下側に配置され賞球タンク720に貯留された遊技球を整列させて下流側へ送るタンクレールユニット730と、タンクレールユニット730によって整列された遊技球を所定の払出指示に基づいて払い出す賞球装置740と、賞球装置740によって払出された遊技球を皿ユニットの上皿301へ誘導することができると共に上皿301が遊技球で満タンになると払出された遊技球を下皿302側へ分岐誘導することができる満タン分岐ユニット770と、を主に備えている。

[3-4. Prize ball unit]

Next, the winning ball unit 700 will be described. In the pachinko island facility in the hall where the pachinko gaming machine 1 is installed, the gaming balls supplied to the pachinko gaming machine 1 from the pachinko island facility are stored, and then the upper tray 301 of the pachinko gaming machine 1 based on a predetermined payout instruction. It is something to pay out. The prize ball unit 700 is provided with a prize ball base 710 attached to the back surface of the main body frame base 600, and a prize ball tank attached to the top of the back surface of the prize ball base 710 and receiving and storing game balls supplied from the pachinko island facility side. A tank rail unit 730 is arranged below the prize ball tank 720 and arranged in the game ball stored in the prize ball tank 720 and sent downstream, and the game balls aligned by the tank rail unit 730 are predetermined. The prize ball device 740 to pay out based on the payout instruction and the gaming ball paid out by the prize ball device 740 can be guided to the upper plate 301 of the plate unit and the upper plate 301 is paid out when the game ball is full. The game machine is mainly equipped with a full tank branching unit 770 capable of branching and guiding the game ball to the lower plate 302 side.

また、賞球ユニット700は、賞球ベース710の後面に取り付けられる外部端子板784と、外部端子板784の後側を覆う外部端子板カバー786と、を備えている。

In addition, the prize ball unit 700 includes an external terminal board 784 attached to the rear surface of the prize ball base 710, and an external terminal board cover 786 covering the rear side of the external terminal board 784.

[3−4−1.賞球タンク]

賞球タンク720は、底壁部721の外周が外周壁部722で囲まれており、底壁部721上に所定量の遊技球を貯留することができるようになっている。また、賞球タンク720は、底壁部721の上面が、排出口723へ向かって低くなるように傾斜しており、底壁部721上の遊技球が排出口723へ向かって転動するようになっている。

[3-4-1. Prize ball tank]

An outer periphery of the bottom wall portion 721 is surrounded by the outer peripheral wall portion 722 of the award ball tank 720, and a predetermined amount of gaming balls can be stored on the bottom wall portion 721. In addition, the winning ball tank 720 is inclined so that the upper surface of the bottom wall 721 is lowered toward the discharge port 723 so that the gaming balls on the bottom wall 721 roll toward the discharge port 723 It has become.

また、賞球タンク720は、軸部725に回動自在に軸支される二つの球ならし部材727を備えている。この球ならし部材727は、一端側が軸部725に軸支されるようになっていると共に内部に錘を保持しており、自重によって他端側が垂下するようになっている。この球ならし部材727は、後述するタンクレールユニット730内に垂下するようになっており、タンクレールユニット730内を流通する遊技球をならして整列させることができるものである。

Further, the prize ball tank 720 is provided with two ball straightening members 727 pivotally supported by the shaft portion 725 in a rotatable manner. One end side of the ball straightening member 727 is pivotally supported by the shaft portion 725 and a weight is held therein, and the other end side is suspended by its own weight. The ball straightening member 727 is suspended in a tank rail unit 730 described later, and the game balls flowing in the tank rail unit 730 can be leveled and aligned.

[3−4−2.タンクレールユニット]

タンクレールユニット730は、賞球タンク720の下側に配置され左右方向へ長く延びたタンクレール731を備えている。このタンクレール731は、上方が開放された所定深さの樋状で前後方向に遊技球が二列で整列することが可能な幅(奥行)とされ、正面視左側(軸支側)端部が低くなるように底部が傾斜している。

[3-4-2. Tank rail unit]

The tank rail unit 730 includes a tank rail 731 disposed below the award ball tank 720 and elongated in the left-right direction. The tank rail 731 has a bowl-like shape with a predetermined depth open at the top, and has a width (depth) in which the game balls can be aligned in two rows in the front-rear direction. The bottom is sloped so that

また、タンクレールユニット730は、タンクレール731の排出口上部に回転可能に支持される整列歯車732と、整列歯車732の上部を覆う歯車カバー733と、歯車カバー733の正面視右端と連続しタンクレール731の上部を閉鎖する球押え板734と、タンクレール731内に進退可能とされタンクレール731内の遊技球が排出口側へ転動するのを停止させることが可能な球止片735と、を備えている。整列歯車732は、タンクレール731の仕切壁によって二列に仕切られた遊技球の二つの流路と対応するように、前後方向に並んで二つ備えられている。

In addition, the tank rail unit 730 includes an alignment gear 732 rotatably supported at an upper portion of the discharge port of the tank rail 731, a gear cover 733 covering the upper portion of the alignment gear 732, and a tank continuous with the right end of the gear cover 733 in a front view A ball pressure plate 734 for closing the upper portion of the rail 731 and a ball stopper 735 capable of advancing and retracting into the tank rail 731 and stopping rolling of the gaming ball in the tank rail 731 to the discharge port side And. Two alignment gears 732 are provided in line in the front-rear direction so as to correspond to the two flow paths of the game balls divided in two rows by the partition wall of the tank rail 731.

[3−4−3.賞球装置]

賞球装置740は、タンクレールユニット730の排出口から排出供給された遊技球を、所定の払出指示に基づいて皿ユニット300の上皿301へ払い出すためのものである。賞球装置740は、上端に開口し遊技球の外形よりも若干広い幅で上下方向の中央よりもやや下側の位置まで延出する供給通路と、供給通路の下端と連通し所定広さの空間を有した振分空間と、振分空間の背面視左側(開放側)下端と連通し略く字状に曲がって背面視左側面に開口する賞球通路と、振分空間の背面視右側(軸支側)下端と連通し下方へ延出して下端に開口する球抜通路と、を備えている。この供給通路、振分空間、賞球通路、及び球抜通路は、後方へ開放された状態で形成されている。

[3-4-3. Prize ball device]

The prize ball device 740 is for delivering the game balls discharged and supplied from the discharge port of the tank rail unit 730 to the upper plate 301 of the plate unit 300 based on a predetermined payout instruction. The prize ball device 740 is open at the upper end and has a width slightly wider than the outline of the gaming ball and extends to a position slightly lower than the center in the vertical direction, and communicates with the lower end of the supply passage and has a predetermined size. A distribution space having a space, a prize ball passage communicating with the lower end of the distribution space on the rear side (open side) in the rear view and bent in a substantially U shape and opened on the left side in the rear view, a rear view right side of the distribution space And a ball removal passage communicating with the lower end and extending downward and opening at the lower end. The supply passage, the distribution space, the prize ball passage, and the ball removal passage are formed in a state of being opened rearward.

賞球装置740は、払出モータ744の回転軸に一体回転可能に固定されモータ支持板の後側に配置される第1ギアと、第1ギアと噛合する第2ギアと、第2ギアと噛合する第3ギアと、第3ギアとともに一体回転し振分空間内に配置されるスプロケットとしての払出回転体と、払出回転体とは第3ギアを挟んで反対側に一体回転可能に固定され周方向に等間隔で複数(本実施形態では、3つ)の検出スリットが形成された回転検出盤と、を備えるとともに、供給通路内の遊技球の有無を検出するための球切れスイッチ750と、賞球通路内を流下する遊技球を検出するための計数スイッチ751と、払出回転体と一体回転する回転検出盤に形成された検出スリットを検出するための回転角スイッチ752と、回転角スイッチ752を保持する回転角スイッチ基板753と、払出モータ744、球切れスイッチ750、計数スイッチ751、及び回転角スイッチ752と後述する払出制御基板との接続を中継する賞球ケース内基板754と、を備えている。

The prize ball device 740 is engaged with the first gear fixed to the rotation shaft of the payout motor 744 so as to be integrally rotatable and disposed on the rear side of the motor support plate, the second gear meshing with the first gear, and the second gear. The third gear, the payout rotating body as a sprocket integrally rotated with the third gear and disposed in the distribution space, and the payout rotating body are fixed integrally rotatably on the opposite side across the third gear. A ball breakage switch 750 for detecting the presence or absence of a game ball in the supply passage, provided with a rotation detection board on which a plurality of (three in the present embodiment) detection slits are formed at equal intervals in the direction; Counting switch 751 for detecting gaming balls flowing down the prize ball passage, rotation angle switch 752 for detecting a detection slit formed on a rotation detection board integrally rotating with the payout rotating body, and rotation angle switch 752 Hold A rotational angle switch substrate 753 includes payout motor 744, burn out switch 750, a counting switch 751, and the rotation angle prize balls casing substrate 754 that relays the connection between dispensing the below-described control board and the switch 752, the.

スプロケットとしての払出回転体は、周方向に等間隔でそれぞれ1つの遊技球を収容可能な大きさの3つの凹部を備えており、払出回転体が回転することで、供給通路から供給された遊技球が1球ずつ凹部に収容されて、賞球通路又は球抜通路側へ払い出すことができるようになっている。また、払出回転体と一体回転する回転検出盤に形成された3つの検出スリットは、回転検出盤の外周に等分(120度ごと)に形成されるとともに、払出回転体の凹部間と対応する位置にそれぞれ設けられており、検出スリットを回転角スイッチ752によって検出することで、払出回転体の回転位置を検出することができるようになっている。なお、本実施形態では、回転検出盤(払出回転体)の各検出スリット間(120度)の回転は、払出モータ744の18ステップの回転に相当するように設計されている。

The payout rotating body as the sprocket has three recesses each having a size capable of accommodating one game ball at equal intervals in the circumferential direction, and the game is supplied from the supply passage by rotating the payout rotating body The balls are accommodated in the recess one ball at a time, and can be discharged to the prize ball passage or the ball removal passage side. In addition, the three detection slits formed on the rotation detection board that rotates integrally with the payout rotation body are equally divided (every 120 degrees) on the outer periphery of the rotation detection board, and correspond to the recesses of the payout rotation body. The rotational position of the payout rotary body can be detected by detecting the detection slit with the rotational angle switch 752 provided at each position. In the present embodiment, the rotation (120 degrees) between the detection slits of the rotation detection board (dispensing rotor) is designed to correspond to the rotation of 18 steps of the dispensing motor 744.

賞球装置740は、払出モータ744によって払出回転体が背面視反時計周りの方向へ回転させられると、供給通路内の遊技球が、賞球通路へ払出されるようになっており、払出回転体の回転によって賞球通路へ払出された遊技球は、計数スイッチ751によって1球ずつ数えられた上で賞球通路へ受け渡されるようになっている。一方、球抜き操作部材がホールの店員等により操作されると、供給通路内の遊技球が球抜通路へ払出されるようになっており、球抜通路へ払出された遊技球は、球抜通路の下端から後述する満タン分岐ユニット770を介してパチンコ遊技機1の後側外部へと排出することができるようになっている。

In the prize ball device 740, when the payout rotor is rotated in the counterclockwise direction by the payout motor 744, the gaming balls in the supply passage are dispensed to the prize ball passage, and the payout rotation is performed. The game balls paid out to the winning ball passage by the rotation of the body are counted one by one by the counting switch 751 and delivered to the winning ball passage. On the other hand, when the ball removing operation member is operated by a store clerk or the like in the hall, the game balls in the supply passage are paid out to the ball pulling passage, and the game balls paid out to the ball pulling passage are The pachinko gaming machine 1 can be discharged from the lower end of the passage to the rear outside of the pachinko gaming machine 1 through a full tank branching unit 770 described later.

[3−4−4.満タン分岐ユニット]

満タン分岐ユニット770は、全体が後端から前端へ向かうに従って低くなるような箱状に形成されており、後端上部における左右方向の略中央に上方へ向かって開口し賞球装置740の賞球通路を流下してきた遊技球を受ける賞球受口と、賞球受口の下側に配置され左右方向へ広がった分岐空間と、分岐空間における賞球受口の直下から前側へ向かって遊技球を誘導する通常通路と、通常通路を流通した遊技球を前方へ放出し前端の正面視右端に開口した通常球出口774と、分岐空間における賞球受口の直下よりも背面視右側へ離れた位置から前側へ向かって遊技球を誘導する満タン通路と、満タン通路を流通した遊技球を前方へ放出し通常球出口774の正面視左側に開口した満タン球出口776と、を備えている。

[3-4-4. Full Tank Branch Unit]

The full tank branch unit 770 is formed in a box shape that becomes lower as it goes from the rear end to the front end, and opens upward substantially at the center in the left-right direction at the upper rear end. A game is performed from the bottom of the prize ball receptacle in the branch space to the front side from the prize ball receptacle which receives the game ball which has flowed down the ball passage, the branch space which is disposed below the prize ball receptacle and extends laterally The normal passage for guiding the ball, the gaming ball distributed in the normal passage are released forward, and the normal ball outlet 774 opened at the right end of the front view front view And a full ball outlet 776 that is released forward from the full ball passage 774 and is open on the left side of the ball view 774 in a front view. ing.

また、満タン分岐ユニット770は、後端上部の正面視左側端部に上方へ向かって開口し賞球装置740の球抜通路を流下してきた遊技球を受ける球抜受口と、球抜受口に受けられた遊技球を前側へ誘導する球抜通路と、球抜通路を流通した遊技球を前方へ放出し正面視左端で通常球出口774及び満タン球出口776よりも後方の位置で開口した球抜出口と、を備えている。

In addition, the full tank branch unit 770 has a ball outlet port for receiving gaming balls that have been opened upward at the left end in a front view at the rear end upper portion and flowed down the ball outlet passage of the prize ball device 740; A ball extraction passage for guiding the game ball received in the mouth to the front, and a game ball flowing through the ball extraction passage to the front, and at a position rearward of the normal ball outlet 774 and the full ball outlet 776 at the left end in front view And an open ball outlet.

満タン分岐ユニット770は、本体枠3に対して扉枠5を閉じた状態とすると、通常球出口774及び満タン球出口776が、それぞれ扉枠5におけるファールカバーユニット540の第一球入口542a及び第二球入口542c(図1を参照)と対向して連通するようになっており、通常球出口774から放出された遊技球は、ファールカバーユニット540の第一球入口542aを通って皿ユニット300の上皿301へ供給され、満タン球出口776から放出された遊技球は、ファールカバーユニット540の第二球入口542cを通って皿ユニット300の下皿302へ供給されるようになっている。また、球抜出口は、本体枠ベース600における本体枠ベース球抜通路の背面視右側上端と連通するように形成されており、球抜出口から放出された遊技球が本体枠ベース600の本体枠ベース球抜通路へ受け渡されるようになっている。

In the full tank branch unit 770, when the door frame 5 is closed with respect to the main body frame 3, the normal ball outlet 774 and the full tank ball outlet 776 are respectively the first ball inlet 542a of the far cover unit 540 in the door frame 5. And the gaming ball discharged from the ball outlet 774, which is normally in communication with the second ball inlet 542c (see FIG. 1), passes through the first ball inlet 542a of the far cover unit 540. The gaming balls supplied to the upper tray 301 of the unit 300 and discharged from the full ball outlet 776 are supplied to the lower tray 302 of the tray unit 300 through the second ball inlet 542 c of the far cover unit 540. ing. Further, the ball outlet is formed to communicate with the upper end of the main frame base ball removal passage in the main body frame base 600 in the right side in a rear view, and the game ball released from the ball outlet is the main body frame of the body frame base 600 It is delivered to the base ball removal passage.

皿ユニット300の上皿301が遊技球で満タンとなった状態で、更に賞球ユニット700(賞球装置740)から遊技球が払出されると、ファールカバーユニット540の第一球出口から上皿301側へ出られなくなった遊技球が、ファールカバーユニット540の第一球通路内で滞り、やがて、満タン分岐ユニット770における通常球出口774を通して上流の通常通路内も一杯になる。この状態で、賞球受口から分岐空間内へ侵入した遊技球は、通常通路内へ侵入することができず、分岐空間内で横方向へ移動し始め、横方向へ移動した遊技球が満タン通路内へ侵入して、満タン球出口からファールカバーユニット540の第二球入口542c、第二球通路、そして第二球出口を介して皿ユニット300の下皿302へ供給されるようになっている。

When the gaming ball is further paid out from the winning ball unit 700 (the winning ball device 740) with the upper plate 301 of the plate unit 300 being full of gaming balls, the ball is raised from the first ball outlet of the far cover unit 540. The game balls which can not be ejected to the side of the tray 301 stay in the first ball passage of the far cover unit 540, and eventually the normal passage upstream of the full ball branch unit 770 is filled up. In this state, the gaming ball that has entered the branch space from the winning ball receptacle can not normally enter the passage, and starts to move laterally in the branch space, and the gaming ball that has moved laterally is full. It enters into the tan passage and is supplied to the lower tray 302 of the pan unit 300 from the full ball outlet through the second ball inlet 542c of the far cover unit 540, the second ball passage, and the second ball outlet. It has become.

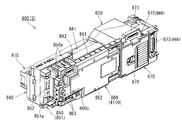

[3−5.基板ユニット]

次に、基板ユニット800について説明する。基板ユニット800は、図6に示すように、本体枠ベース600の下部後壁部の後面に取り付けられる基板ユニットベース810と、基板ユニットベース810の正面視左側後面に取り付けられるスピーカボックス820と、基板ユニットベース810の後面に取り付けられる電源基板ボックスホルダ840と、電源基板ボックスホルダ840の後面に取り付けられ後端がスピーカボックス820の後端と略同一面状となる大きさに形成される電源基板ボックス850と、電源基板ボックス850及びスピーカボックス820の後面に取り付けられる払出制御基板ボックス860と、払出制御基板ボックス860の正面視左側端部を覆うようにスピーカボックス820の後面に取り付けられる端子基板ボックス870と、基板ユニットベース810の前面に取り付けられる主扉中継端子板880及び周辺扉中継端子板882と、を備えている。

[3-5. Substrate unit]

Next, the substrate unit 800 will be described. As shown in FIG. 6, the substrate unit 800 has a substrate unit base 810 attached to the rear surface of the lower rear wall of the main body frame base 600, a speaker box 820 attached to the left rear surface of the substrate unit base 810 in a front view, A power supply substrate box holder 840 attached to the rear surface of the unit base 810 and a power supply substrate box attached to the rear surface of the power supply substrate box holder 840 and having a rear end substantially flush with the rear end of the speaker box 820 850, a dispensing control substrate box 860 attached to the back surface of the power supply substrate box 850 and the speaker box 820, and a terminal substrate box 870 attached to the rear surface of the speaker box 820 so as to cover the left end of the dispensing control substrate box 860 in front view And the substrate unit base A main door relay terminal plate 880 and the peripheral door relay terminal plate 882 is attached to the front surface 10, and a.

電源基板ボックスホルダ840は、正面視で左右中央よりも左側前面に、上方へ開放され遊技盤4のアウト球排出部から排出された下方へ排出された遊技球を受ける排出球受部841と、排出球受部841で受けられた遊技球を下方へ誘導して排出する排出通路842と、排出通路842及び排出球受部841の横(正面視で右側)の前面に前方及び上方へ開放され電源基板ボックスホルダ840の後面全体が前側へ窪んだように形成され電源基板ボックス850の前端を収容可能なボックス収容部と、を備えている。

The power supply substrate box holder 840 is a discharge ball receiving portion 841 receiving the gaming balls discharged upward and discharged downward from the out ball discharging portion of the game board 4 at the front left on the left and right center in front view; It is opened forward and upward at the front of the discharge passage 842 for guiding the gaming ball received by the discharge ball receiving portion 841 downward and discharging it, the side of the discharge passage 842 and the discharge ball receiving portion 841 (right side in front view) And a box accommodating portion formed such that the entire rear surface of the power supply substrate box holder 840 is recessed to the front side and capable of accommodating the front end of the power supply substrate box 850.

また、電源基板ボックスホルダ840は、排出通路842の開放された前端側が基板ユニットベース810の後面によって閉鎖されるようになっているとともに、基板ユニットベース810の開口部が排出通路842へ臨む位置に形成されており、本体枠ベース600における下部後壁部の後面に形成された本体枠ベース球抜通路を流通して基板ユニットベース810の開口部を通って基板ユニットベース810の後側へ流下した遊技球と、遊技盤4のアウト球排出部から排出されて排出球受部841で受けられた遊技球と、を排出通路842を通してパチンコ遊技機1の後側下方へ排出することができるようになっている。

In addition, the open front end side of the discharge passage 842 of the power supply substrate box holder 840 is closed by the rear surface of the substrate unit base 810, and the opening of the substrate unit base 810 faces the discharge passage 842. It is formed, flows through the opening of the substrate unit base 810 through the opening of the substrate unit base 810 and flows down to the rear side of the substrate unit base 810 through the body frame base ball removal passage formed on the rear surface of the lower rear wall portion of the body frame base 600. The game balls and the game balls discharged from the out ball discharge unit of the game board 4 and received by the discharge ball receiving unit 841 can be discharged through the discharge passage 842 to the lower back side of the pachinko gaming machine 1 It has become.

電源基板ボックス850は、前方が開放された横長の箱状に形成されており、その前端開口を閉鎖するように取り付けられた電源基板851を備えている。この電源基板ボックス850は、電源基板851に取り付けられた各種電子部品が収容されるようになっており、上面及び下面に形成された複数のスリット850aを介して、電子部品等からの熱を外部へ放出することができるようになっている。なお、電源基板ボックス850の後面には、電源基板851に取り付けられた電源スイッチ852が臨むようになっている。

The power supply substrate box 850 is formed in a horizontally long box shape whose front is open, and includes a power supply substrate 851 attached so as to close its front end opening. The power supply substrate box 850 is adapted to receive various electronic components attached to the power supply substrate 851, and externally transmits the heat from the electronic components and the like through the plurality of slits 850a formed on the upper surface and the lower surface. It can be released into the A power switch 852 attached to the power supply substrate 851 faces the rear surface of the power supply substrate box 850.

払出制御基板ボックス860は、横長で後方が開放された薄箱状のボックスベース861と、ボックスベース861内へ後側から嵌合し前方が開放された薄箱状のカバー862と、ボックスベース861の後面に取り付けられカバー862によって後面が覆われる払出制御基板4110と、を備えている。また、払出制御基板ボックス860は、背面視左端から外方へ突出しボックスベース861及びカバー862の双方に形成された複数の分離切断部863を備えており、複数の分離切断部863の一箇所でボックスベース861とカバー862とがカシメ固定されている。これによってボックスベース861とカバー862とを分離するためには、分離切断部863を切断しないと分離できないようになっており、払出制御基板ボックス860を開くと、その痕跡が残るようになっている。したがって、払出制御基板ボックス860が不正に開閉させられたか否かが判るようになっている。なお、本実施形態では、検査等のために払出制御基板ボックス860を一回だけ開閉することができるようになっている。

The delivery control board box 860 includes a thin box-like box base 861 that is wide and open to the rear, a thin box-like cover 862 that fits into the box base 861 from the rear side and is open to the front, and a box base 861 And a payout control substrate 4110 attached to the rear surface of the rear cover and covered by the cover 862. Further, the payout control board box 860 is provided with a plurality of separation / cutting portions 863 that protrude outward from the left end in rear view and are formed on both the box base 861 and the cover 862. The box base 861 and the cover 862 are fixed by caulking. Thus, in order to separate the box base 861 and the cover 862, the separation and cutting portion 863 can not be separated without being cut off, and the trace thereof is left when the delivery control substrate box 860 is opened. . Therefore, it can be determined whether or not the dispensing control board box 860 has been illegally opened and closed. In the present embodiment, the delivery control board box 860 can be opened and closed only once for inspection or the like.

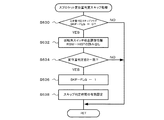

また、払出制御基板ボックス860は、払出制御基板4110に取り付けられた操作スイッチ860a(エラー解除部)、及び検査用出力端子860c等がカバー862を通して後方へ臨むようになっている。また、払出制御基板ボックス860は、主制御基板4100等と接続するための各種接続用の端子が、カバー862を通して後方へ臨むようになっている。なお、操作スイッチ860aは、電源投入時において払出制御基板4110のマイクロプロセッサに内蔵されるRAM、及び主制御基板4100のマイクロプロセッサに内蔵されるRAMをクリアする場合に操作されたり、電源投入後においてエラー報知されている際に、そのエラーを解除するために操作されたりするようになっており、電源投入時におけるRAMクリアを行う機能と、電源投入後(RAMクリアとして機能を奏する期間を経過した後)におけるエラー解除を行う機能と、を有している。この点についての詳細な説明を後述する。

Further, in the payout control board box 860, the operation switch 860a (error release unit) attached to the payout control board 4110, the inspection output terminal 860c, and the like are faced rearward through the cover 862. Further, in the payout control board box 860, terminals for various connections for connecting to the main control board 4100 and the like are arranged to face rearward through the cover 862. The operation switch 860a is operated when clearing the RAM built in the microprocessor of the payout control board 4110 when the power is turned on and the RAM built in the microprocessor of the main control board 4100, or after the power is turned on. When notified of an error, it is operated to clear the error, and the function to clear the RAM when the power is turned on and the time after the power is turned on (a period of playing the function as the RAM clear has passed And the function of canceling the error in A detailed description of this point will be given later.

端子基板ボックス870は、スピーカボックス820の後面に取り付けられる基板ベース871と、基板ベース871の後面に取り付けられ後方へ向かって周辺パネル中継端子872が固定された枠周辺中継端子板868と、基板ベース871の後面に取り付けられ後方へ向かってCRユニット中継端子873が固定された遊技球等貸出装置接続端子板869と、周辺パネル中継端子872とCRユニット中継端子873とが後側へ臨むように基板ベース871の後側を覆う基板カバー874と、を備えている。周辺パネル中継端子872は、パチンコ遊技機1を設置するパチンコ島設備側に備えられたパチンコ遊技機1の稼動状態等を表示するための度数表示器と接続するためのものであり、CRユニット中継端子873は、パチンコ遊技機1と隣接して設置されるCRユニットと接続するためのものである。

Terminal board box 870 has a board base 871 attached to the rear face of speaker box 820, a frame peripheral relay terminal board 868 attached to the rear face of board base 871 and peripheral panel relay terminals 872 fixed backward, and a board base A game ball lending device connection terminal plate 869 attached to the rear surface of the 871 and having the CR unit relay terminal 873 fixed to the rear, the peripheral panel relay terminal 872 and the CR unit relay terminal 873 face the back side And a substrate cover 874 covering the rear side of the base 871. The peripheral panel relay terminal 872 is for connecting to a frequency indicator for displaying the operating state and the like of the pachinko gaming machine 1 provided on the pachinko island facility where the pachinko gaming machine 1 is installed, and CR unit relaying The terminal 873 is for connecting to a CR unit installed adjacent to the pachinko gaming machine 1.

主扉中継端子板880及び周辺扉中継端子板882は、本体枠3に取り付けられる遊技盤4に備えられた周辺制御基板4140や基板ユニット800の払出制御基板4110等と、扉枠5に備えられたハンドル装置500、各装飾基板や操作ユニット400等との接続を中継するためのものである。これら主扉中継端子板880及び周辺扉中継端子板882は、基板ユニットベース810の前面に形成された基板取付部に取り付けることで、本体枠ベース600の前面から前側へ臨むようになっており、扉枠5から延びだした配線を接続することができるようになっている。

The main door relay terminal board 880 and the peripheral door relay terminal board 882 are provided for the peripheral control board 4140 provided on the game board 4 attached to the main body frame 3, the payout control board 4110 for the board unit 800, etc. It is for relaying the connection with the handle device 500, each decoration board, the operation unit 400 and the like. By attaching the main door relay terminal board 880 and the peripheral door relay terminal board 882 to the board attachment portion formed on the front face of the board unit base 810, the front face of the main body frame base 600 is faced frontward, A wire extending from the door frame 5 can be connected.

なお、主扉中継端子板880及び周辺扉中継端子板882は、本体枠ベース600の前面に取り付けられる中継端子板カバー692によってその前側が覆われるようになっているとともに、中継端子板カバー692の開口692aを通して、接続端子のみが前側へ臨むようになっており、本体枠3の前面がすっきりした外観となるようになっている。

The main door relay terminal board 880 and the peripheral door relay terminal board 882 are covered on the front side by a relay terminal board cover 692 attached to the front of the main body frame base 600 and the relay terminal board cover 692 Only the connection terminal faces the front side through the opening 692a, and the front surface of the main body frame 3 has a clean appearance.

また、主扉中継端子板880は、扉枠5側に配置される皿ユニット300における貸球ユニット360の貸球ボタン361、返却ボタン362、貸出残表示部363、ハンドル装置500のポテンショメータ512、タッチスイッチ516、発射停止スイッチ518、及びファールカバーユニット540の満タンスイッチ550と、本体枠3側に配置される払出制御基板4110との接続を中継するためのものである。なお、貸球ユニット360の貸球ボタン361、返却ボタン362、貸出残表示部363、ハンドル装置500のポテンショメータ512、タッチスイッチ516、発射停止スイッチ518、及びファールカバーユニット540の満タンスイッチ550についての説明を後述する。

Further, the main door relay terminal board 880 is a ball lending button 361, a return button 362, a lending remaining display portion 363, a potentiometer 512 of the handle device 500, a touch of the ball lending unit 360 in the bowl unit 300 disposed on the door frame 5 side. The relay 516 relays the connection between the switch 516, the firing stop switch 518, and the full switch 550 of the far cover unit 540, and the payout control board 4110 disposed on the body frame 3 side. In addition, regarding the rental ball button 361 of the rental ball unit 360, the return button 362, the loan remaining display portion 363, the potentiometer 512 of the handle device 500, the touch switch 516, the release stop switch 518, and the full switch 550 of the far cover unit 540. The explanation will be described later.

また、周辺扉中継端子板882は、扉枠5側に配置される各装飾ユニット200,240,280及び皿ユニット300や操作ユニット400に備えられた各装飾基板、及び操作ユニット400に備えられた、ダイヤル駆動モータ414、ダイヤル操作部401や押圧操作部405の操作を各々検出する各種スイッチと、本体枠3側に配置される遊技盤4の周辺制御基板4140との接続を中継するためのものである。なお、扉枠5側に配置される各装飾ユニット200,240,280及び皿ユニット300や操作ユニット400に備えられた各装飾基板、及び操作ユニット400に備えられた、ダイヤル駆動モータ414、ダイヤル操作部401や押圧操作部405の操作を検出する各種スイッチについての説明は後述する。

In addition, the peripheral door relay terminal plate 882 is provided in the decoration units 200, 240, 280 and the decoration unit 200 provided on the door frame 5 side, the dish unit 300, the decoration substrates provided in the operation unit 400, and the operation unit 400. , For relaying the connection between various switches for detecting the operation of the dial drive motor 414, the dial operation unit 401 and the press operation unit 405, and the peripheral control board 4140 of the game board 4 disposed on the main body frame 3 side It is. Note that each decoration unit 200, 240, 280 disposed on the door frame 5 side, each decoration board provided in the plate unit 300 and the operation unit 400, and the dial drive motor 414 provided in the operation unit 400, dial operation Description of various switches for detecting the operation of the unit 401 and the pressing operation unit 405 will be described later.

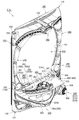

[4.扉枠の全体構成]

次に、本体枠3の前面側に開閉自在に設けられる扉枠5について、図7を参照して説明する。図7は扉枠の斜視図である。扉枠5は、図7に示すように、外形が縦長の矩形状に形成され内周形状がやや縦長の円形状(楕円形状)とされた遊技窓101を有する扉枠ベースユニット100と、扉枠ベースユニット100の前面で遊技窓101の右外周に取り付けられる右サイド装飾ユニット200と、右サイド装飾ユニット200と対向し扉枠ベースユニット100の前面で遊技窓101の左外周に取り付けられる左サイド装飾ユニット240と、扉枠ベースユニット100の前面で遊技窓101の上部外周に取り付けられる上部装飾ユニット280と、右サイド装飾ユニット200及び左サイド装飾ユニット240の下端下側に配置され扉枠ベースユニット100の前面に取り付けられる一対のサイドスピーカカバー290と、を備えている。

[4. Overall configuration of the door frame]

Next, the door frame 5 provided openably and closably on the front side of the main body frame 3 will be described with reference to FIG. FIG. 7 is a perspective view of the door frame. As shown in FIG. 7, the door frame 5 has a door frame base unit 100 having a game window 101 whose outer periphery is formed in a vertically long rectangular shape and whose inner peripheral shape is a slightly vertical circular shape (elliptical shape), A right side decoration unit 200 attached to the right outer periphery of the game window 101 at the front of the frame base unit 100 and a left side attached to the left outer periphery of the game window 101 at the front of the door frame base unit 100 facing the right side decoration unit 200 A decoration unit 240, an upper decoration unit 280 attached to the upper outer periphery of the game window 101 at the front of the door frame base unit 100, a door frame base unit disposed below the lower ends of the right side decoration unit 200 and the left side decoration unit 240 And 100. A pair of side speaker covers 290 attached to the front of the 100.

また、扉枠5は、扉枠ベースユニット100の前面で遊技窓101の下部に取り付けられる皿ユニット300と、皿ユニット300の上部中央に取り付けられる操作ユニット400と、皿ユニット300の右側に取り付けられている上皿側液晶表示装置470、この上皿側液晶表示装置470(第2表示装置)の表示領域を覆うように設けられており接触状態を検知しうる接触面を有する静電容量型のタッチパネル480(接触型入力装置)、皿ユニット300を貫通して扉枠ベースユニット100の右下隅部に取り付けられ遊技球の打込操作をするためのハンドル装置500と、扉枠ベースユニット100を挟んで皿ユニット300の後側に配置され扉枠ベースユニット100の後面に取り付けられるファールカバーユニット540と、ファールカバーユニット540の右側で扉枠ベースユニット100の後面に取り付けられる球送ユニット580と、扉枠ベースユニット100の後側に遊技窓101を閉鎖するように取り付けられるガラスユニット590と、を備えている。なお、タッチパネル480は、本実施形態では4.3インチで分解能10×20のタイプである。このタッチパネル480の接触状態の検知制御を行うタッチパネル駆動基板450が上皿側液晶表示装置470の下方近傍に配置され、皿ユニット300内に収納されている。

Further, the door frame 5 is attached to the dish unit 300 attached to the lower part of the game window 101 at the front of the door frame base unit 100, the operation unit 400 attached to the upper center of the dish unit 300, and the right side of the dish unit 300. Liquid crystal display device 470, and an electrostatic capacitance type liquid crystal display device provided so as to cover the display region of the liquid crystal display device 470 (second display device) and capable of detecting a contact state A touch panel 480 (contact type input device), a handle device 500 for penetrating the dish unit 300 and attached to the lower right corner of the door frame base unit 100 for performing a game ball operation, and sandwiching the door frame base unit 100 A rear cover unit 540 disposed on the rear side of the pan unit 300 and mounted on the rear surface of the door frame base unit 100; Ball feed unit 580 attached to the rear surface of the door frame base unit 100 on the right side of the lens cover unit 540, and a glass unit 590 attached to the rear side of the door frame base unit 100 so as to close the game window 101. ing. In the present embodiment, the touch panel 480 is a 4.3 inch type and 10 × 20 resolution. A touch panel drive substrate 450 for detecting and controlling the contact state of the touch panel 480 is disposed in the vicinity of the lower side of the upper plate liquid crystal display device 470 and is housed in the plate unit 300.

[4−1.扉枠ベースユニット]

次に、扉枠ベースユニット100について説明する。扉枠ベースユニット100は、外形が縦長の矩形状に形成されるとともに、前後方向に貫通し内周が縦長の略楕円形状に形成された遊技窓101を有する扉枠ベース本体110と、扉枠ベース本体110の前面で遊技窓101の上部中央に取り付けられ上部装飾ユニットを固定するための上部ブラケット120と、扉枠ベース本体110の前面で遊技窓101の下端左右両外側に取り付けられる一対のサイドスピーカ130と、扉枠ベース本体110の前面で正面視右下隅部に取り付けられハンドル装置500を支持するためのハンドルブラケットと、を備えている。

[4-1. Door frame base unit]

Next, the door frame base unit 100 will be described. The door frame base unit 100 has a door frame base main body 110 having a game window 101 which is formed in a rectangular shape whose outer shape is vertically long and which is penetrated in the front-rear direction and whose inner periphery is substantially oval in vertical length; An upper bracket 120 attached to the upper center of the game window 101 at the front of the base body 110 for fixing the upper decoration unit, and a pair of sides attached to the lower left and right sides of the game window 101 at the front of the door frame base 110 A speaker 130 and a handle bracket attached to the front lower right corner of the door frame base main body 110 for supporting the handle device 500 are provided.

また、扉枠ベースユニット100は、扉枠ベース本体110の後側に固定される金属製で枠状の補強ユニット150(図1を参照)と、扉枠ベース本体110の後面で遊技窓101の下部を被覆するように取り付けられる防犯カバー180(図1を参照)と、扉枠ベース本体110の後面で遊技窓101の外周の所定位置に回動可能に取り付けられるガラスユニット係止部材190(図1を参照)と、背面視で左右方向の中央より左側(開放側)に配置され遊技窓101の下端に沿って扉枠ベース本体110の後面に取り付けられる発射カバー191(図1を参照)と、発射カバー191の下側で扉枠ベース本体110の後面に取り付けられ後述するハンドル装置500のポテンショメータ512と後述する遊技盤4に備えられた主制御基板4100との接続を中継するハンドル中継端子板192(図1を参照)と、ハンドル中継端子板192の後側を被覆するハンドル中継端子板カバー193(図1を参照)と、左右方向の中央を挟んで発射カバー191やハンドル中継端子板192等とは反対側(背面視で左右方向中央よりも右側(軸支側))に配置され扉枠ベース本体の後面に取り付けられる枠装飾駆動アンプ基板194(図1を参照)と、枠装飾駆動アンプ基板194の後側を被覆する枠装飾駆動アンプ基板カバー195(図1を参照)と、を備えている。

Further, the door frame base unit 100 includes a metal frame-shaped reinforcing unit 150 (see FIG. 1) fixed to the rear side of the door frame base main body 110 and the game window 101 on the rear surface of the door frame base main body 110. A crime prevention cover 180 (see FIG. 1) attached so as to cover the lower part, and a glass unit locking member 190 rotatably attached at a predetermined position on the outer periphery of the game window 101 on the rear surface of the door frame base main body 110 (see FIG. 1 and a launch cover 191 (see FIG. 1) disposed on the left side (open side) from the center in the left-right direction in rear view and attached to the rear face of the door frame base main body 110 along the lower end of the game window 101 Mounted on the rear surface of the door frame base main body 110 below the launch cover 191 and provided on the potentiometer 512 of the handle unit 500 described later and the game board 4 described later A handle relay terminal board 192 (see FIG. 1) relaying connection with 100, a handle relay terminal board cover 193 (see FIG. 1) covering the rear side of the handle relay terminal board 192, and a center in the horizontal direction A frame decoration drive amplifier substrate 194 which is disposed on the opposite side to the launch cover 191, handle relay terminal plate 192, etc. on the opposite side (right side (axial support side) from the center in the horizontal direction in rear view) (See FIG. 1) and a frame ornamental drive amplifier substrate cover 195 (see FIG. 1) covering the rear side of the frame ornamental drive amplifier substrate 194.

枠装飾駆動アンプ基板194は、サイドスピーカ130や左右のサイド装飾ユニット200,240の上部スピーカと電気的に接続されるとともに、後述する遊技盤4に備えられた周辺制御基板4140と電気的に接続されており、周辺制御基板4140から送られた音響信号を増幅して各スピーカ130へ出力する増幅回路を備えている。なお、具体的な図示は省略するが、本実施形態では、各装飾ユニット200,240,280及び皿ユニット300や操作ユニット400に備えられた各装飾基板、操作ユニット400に備えられたダイヤル駆動モータやスイッチ、ハンドル中継端子板192、皿ユニット300の貸球ユニット360等と、払出制御基板4110や周辺制御基板4140等とを電気的に接続する配線が、枠装飾駆動アンプ基板194の背面視で右側(軸支側)の位置に集約して束ねられた上で後方へ延出して本体枠3の主扉中継端子板880や周辺扉中継端子板882に接続されるようになっている。

The frame decoration drive amplifier substrate 194 is electrically connected to the side speakers 130 and the upper speakers of the left and right side decoration units 200 and 240, and is electrically connected to the peripheral control substrate 4140 provided on the game board 4 described later. The amplifier circuit is provided with an amplification circuit that amplifies the acoustic signal sent from the peripheral control board 4140 and outputs the amplified signal to each speaker 130. Although specific illustration is omitted, in the present embodiment, each decoration board provided in each decoration unit 200, 240, 280, dish unit 300 and operation unit 400, and a dial drive motor provided in operation unit 400. Wires for electrically connecting the switches, the handle relay terminal board 192, the ball lending unit 360 of the plate unit 300, etc. with the payout control board 4110, the peripheral control board 4140, etc. After being collected and bundled at the position of the right side (axial support side), it is extended backward and connected to the main door relay terminal board 880 and the peripheral door relay terminal board 882 of the main body frame 3.

[4−1−1.扉枠ベース本体]

扉枠ベース本体110は、合成樹脂によって縦長の額縁状に形成されており、前後方向に貫通し内形が縦長で略楕円形状の遊技窓101が全体的に上方へオフセットするような形態で形成されている。この遊技窓101は、左右側及び上側の内周縁が連続した滑らかな曲線状に形成されているのに対して、下側の内周縁は左右へ延びた直線状に形成されている。また、扉枠ベース本体110における遊技窓101の下側の内周縁には、軸支側(正面視で左側)にファールカバーユニット540の第一球出口を挿通可能な方形状の切欠部が形成され、遊技窓101の下辺の左右両外側に配置されサイドスピーカ130を取り付けて固定するためのスピーカ取付部、正面視で右下隅部に配置され前方へ膨出した前面の右側(開放側)端が後退するように斜めに傾斜しハンドルブラケットを取り付けるためのハンドル取付部、ハンドル取付部の所定位置で前後方向へ貫通しハンドル装置500からの配線が通過可能な配線通過口、ハンドル取付部の上側で前方へ向かって短く延びた筒状に形成され後述するシリンダ錠1010が挿通可能な錠穴116が形成されている。この扉枠ベース本体110は、遊技窓101によって形成される上辺、及び左右の側辺の幅が、後述する補強ユニット150の上側補強板金151、軸支側補強板金152、及び開放側補強板金153の幅と略同じ幅とされており、正面視における扉枠ベース本体の大きさに対して、遊技窓101が可及的に大きく形成されている。

[4-1-1. Door frame base body]

The door frame base main body 110 is formed of a synthetic resin in a vertically elongated frame shape, and is formed in such a form that the game window 101 having a vertically elongated inner shape and a substantially elliptical shape is entirely upwardly offset. It is done. The game window 101 is formed in a smooth curved shape in which the left and right side and upper inner peripheral edges are continuous, while the lower inner peripheral edge is formed in a linear shape extending left and right. In addition, at the lower inner peripheral edge of the game window 101 in the door frame base main body 110, a rectangular notch capable of inserting the first ball outlet of the far cover unit 540 is formed on the shaft support side (left side in front view). Speaker attachment portion for attaching and fixing the side speaker 130, which is disposed on the left and right outside of the lower side of the game window 101, and the right (open side) end of the front which is disposed in the lower right corner in front view and bulges forward. The handle attachment portion for attaching the handle bracket at a slanted angle so as to retract, the wiring passage opening through which the wiring from the handle device 500 can pass in the longitudinal direction at a predetermined position of the handle attachment portion, the upper side of the handle attachment portion The lock hole 116 is formed in a cylindrical shape that extends short in the forward direction and through which a cylinder lock 1010 described later can be inserted. The door frame base main body 110 has an upper side formed by the game window 101, and widths of left and right side sides are the upper reinforcing sheet metal 151, the pivoting side reinforcing sheet metal 152, and the open side reinforcing sheet metal 153 of the reinforcing unit 150 described later. The game window 101 is formed as large as possible with respect to the size of the door frame base main body in a front view.

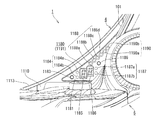

[4−1−2.補強ユニット]

補強ユニット150は、扉枠ベース本体110の上辺部裏面に沿って取り付けられる上側補強板金151(図1を参照)と、扉枠ベース本体110の軸支側辺部裏面に沿って取り付けられる軸支側補強板金152(図1を参照)と、扉枠ベース本体110の開放側辺部裏面に沿って取り付けられる開放側補強板金153(図1を参照)と、扉枠ベース本体110の遊技窓101の下辺裏面に沿って取り付けられる下側補強板金154(図1を参照)と、を備えており、それらが相互にビスやリベット等で締着されて方形状に形成されている。

[4-1-2. Reinforcement unit]

The reinforcement unit 150 is provided with an upper reinforcement sheet metal 151 (see FIG. 1) attached along the upper side back surface of the door frame base main body 110 and a pivot support attached along the back side of the pivoting side of the door frame base main body 110. A side reinforcing sheet metal 152 (see FIG. 1), an opening side reinforcing sheet metal 153 (see FIG. 1) attached along the back surface of the side of the door frame base main body 110, and a game window 101 of the door frame base main body 110. And a lower reinforcing sheet metal 154 (see FIG. 1) attached along the lower surface of the lower side, and they are formed into a square shape by mutually fastening them with a screw or a rivet.

軸支側補強板金152の上下端部に、その上面に上下方向に摺動自在に設けられる軸ピン155を有する上軸支部156と、その下面に軸ピン157を有する下軸支部158と、を一体的に備えている。そして、上下の軸ピン155,157が本体枠3の軸支側上下に形成される上軸支金具630及び下軸支金具640に軸支されることにより、扉枠5が本体枠3に対して開閉自在に軸支されるようになっている。

An upper shaft support portion 156 having a shaft pin 155 slidably provided in the upper and lower directions on the upper surface and a lower shaft support portion 158 having a shaft pin 157 on the lower surface. It is equipped integrally. The upper and lower shaft pins 155 and 157 are pivotally supported by the upper shaft support bracket 630 and the lower shaft support bracket 640 formed on the upper and lower shaft support sides of the main body frame 3, so that the door frame 5 is mounted on the main body frame 3. It is pivotally supported open and close freely.

また、開放側補強板金153の後側下部には、錠装置1000の扉枠用フック部1041と当接するフックカバー165が備えられている。このフックカバー165は、本体枠3に対して扉枠5を閉じる際に、本体枠3の開放側辺に沿って取り付けられる錠装置1000(施錠装置)の扉枠用フック部1041と係合するものであり、錠装置1000のシリンダ錠1010に鍵を差し込んで一方に回動する(本体枠3を外枠2に対して開放する方向と反対方向に回転する)ことにより、扉枠用フック部1041とフックカバー165との係合が外れて本体枠3に対する扉枠5の閉鎖状態を解除することができるものである。

In addition, a hook cover 165 that abuts on the door frame hook portion 1041 of the lock device 1000 is provided at the rear lower portion of the open side reinforcing sheet metal 153. The hook cover 165 engages with the door frame hook portion 1041 of the lock device 1000 (locking device) attached along the open side of the main body frame 3 when the door frame 5 is closed with respect to the main body frame 3 The door frame hook portion is obtained by inserting a key into the cylinder lock 1010 of the lock device 1000 and rotating it in one direction (rotating in the direction opposite to the direction in which the main body frame 3 is opened with respect to the outer frame 2). It is possible to release the closed state of the door frame 5 with respect to the main body frame 3 by disengaging the engagement between the 1041 and the hook cover 165.

[4−2.皿ユニット]

次に、皿ユニット300について説明する。皿ユニット300は、賞球装置740から払出された遊技球を貯留するための上皿301及び下皿302を備えているとともに、上皿301に貯留した遊技球を球送ユニットを介して打球発射装置650へ供給することができるものである。

[4-2. Dish unit]

Next, the plate unit 300 will be described. The dish unit 300 is provided with an upper plate 301 and a lower plate 302 for storing gaming balls paid out from the winning ball device 740, and the gaming balls stored in the upper plate 301 are hit and fired via the ball feeding unit. It can be supplied to the device 650.

皿ユニット300の上皿上部パネル314の形状は、正面視で左方向から中央に向かって前方へ突出するように湾曲状に形成されるとともに、その中央から右方向に向かって直線上に前方へ突出して形成されている。皿ユニット300の上部中央には、操作ユニット400が取り付けられる操作ユニット取付部が形成され、この操作ユニット取付部の右側に上皿側液晶表示装置470を取り付けるための液晶取付部314dが形成される。液晶取付部314dが形成される上皿上部パネル314の形状は、板状に形成されており、この部分を例えば遊技者が手で下に向かって押しつけると下方向にたわむようになっており、その押しつける力が所定の力を超えると、上皿上部パネル314が壊れるようになっている。これは、上皿側液晶表示装置470が高価なものであるため、上皿側液晶表示装置470の画面を遊技者が手を押しつけた際に、その力を上皿上部パネル314で受けることにより上皿上部パネル314をたわませることで上皿側液晶表示装置470が破損しないようにしている。つまり、上皿側液晶表示装置470が破損する前に上皿上部パネル314が先に破損するという構造が採用されている。なお、上皿上部パネル314が破損した場合には、皿ユニット300を交換することとなる。この場合、壊れた上皿上部パネル314から上皿側液晶表示装置470を取り外して交換する皿ユニット300の上皿上部パネル314に取り付けて再利用する。