JP6496401B2 - 仮想マシンを終了する際に現在のプロセッサ命令の結果を公開するためのシステムおよび方法 - Google Patents

仮想マシンを終了する際に現在のプロセッサ命令の結果を公開するためのシステムおよび方法 Download PDFInfo

- Publication number

- JP6496401B2 JP6496401B2 JP2017509643A JP2017509643A JP6496401B2 JP 6496401 B2 JP6496401 B2 JP 6496401B2 JP 2017509643 A JP2017509643 A JP 2017509643A JP 2017509643 A JP2017509643 A JP 2017509643A JP 6496401 B2 JP6496401 B2 JP 6496401B2

- Authority

- JP

- Japan

- Prior art keywords

- execution

- host system

- guest

- guest instruction

- instruction

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims description 44

- 230000004044 response Effects 0.000 claims description 31

- 230000008569 process Effects 0.000 description 23

- 238000013519 translation Methods 0.000 description 11

- 230000014616 translation Effects 0.000 description 11

- 230000009471 action Effects 0.000 description 9

- 238000004590 computer program Methods 0.000 description 8

- 230000006870 function Effects 0.000 description 8

- 238000004891 communication Methods 0.000 description 7

- 238000006243 chemical reaction Methods 0.000 description 6

- 230000007246 mechanism Effects 0.000 description 5

- 230000002265 prevention Effects 0.000 description 5

- 238000013507 mapping Methods 0.000 description 4

- 238000012545 processing Methods 0.000 description 4

- 238000006073 displacement reaction Methods 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 230000003287 optical effect Effects 0.000 description 3

- 238000012546 transfer Methods 0.000 description 3

- 230000001960 triggered effect Effects 0.000 description 3

- 208000035217 Ring chromosome 1 syndrome Diseases 0.000 description 2

- 241000700605 Viruses Species 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 230000001934 delay Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 101100514059 Escherichia coli (strain K12) modE gene Proteins 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 238000007596 consolidation process Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000006378 damage Effects 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 239000000835 fiber Substances 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000009249 intrinsic sympathomimetic activity Effects 0.000 description 1

- 230000001343 mnemonic effect Effects 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/50—Monitoring users, programs or devices to maintain the integrity of platforms, e.g. of processors, firmware or operating systems

- G06F21/55—Detecting local intrusion or implementing counter-measures

- G06F21/554—Detecting local intrusion or implementing counter-measures involving event detection and direct action

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/10—Address translation

- G06F12/1009—Address translation using page tables, e.g. page table structures

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/10—Address translation

- G06F12/1027—Address translation using associative or pseudo-associative address translation means, e.g. translation look-aside buffer [TLB]

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/10—Address translation

- G06F12/109—Address translation for multiple virtual address spaces, e.g. segmentation

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/14—Protection against unauthorised use of memory or access to memory

- G06F12/1458—Protection against unauthorised use of memory or access to memory by checking the subject access rights

- G06F12/1466—Key-lock mechanism

- G06F12/1475—Key-lock mechanism in a virtual system, e.g. with translation means

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/50—Monitoring users, programs or devices to maintain the integrity of platforms, e.g. of processors, firmware or operating systems

- G06F21/52—Monitoring users, programs or devices to maintain the integrity of platforms, e.g. of processors, firmware or operating systems during program execution, e.g. stack integrity ; Preventing unwanted data erasure; Buffer overflow

- G06F21/53—Monitoring users, programs or devices to maintain the integrity of platforms, e.g. of processors, firmware or operating systems during program execution, e.g. stack integrity ; Preventing unwanted data erasure; Buffer overflow by executing in a restricted environment, e.g. sandbox or secure virtual machine

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/50—Monitoring users, programs or devices to maintain the integrity of platforms, e.g. of processors, firmware or operating systems

- G06F21/55—Detecting local intrusion or implementing counter-measures

- G06F21/56—Computer malware detection or handling, e.g. anti-virus arrangements

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F21/00—Security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F21/50—Monitoring users, programs or devices to maintain the integrity of platforms, e.g. of processors, firmware or operating systems

- G06F21/57—Certifying or maintaining trusted computer platforms, e.g. secure boots or power-downs, version controls, system software checks, secure updates or assessing vulnerabilities

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/44—Arrangements for executing specific programs

- G06F9/455—Emulation; Interpretation; Software simulation, e.g. virtualisation or emulation of application or operating system execution engines

- G06F9/45533—Hypervisors; Virtual machine monitors

- G06F9/45558—Hypervisor-specific management and integration aspects

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L63/00—Network architectures or network communication protocols for network security

- H04L63/14—Network architectures or network communication protocols for network security for detecting or protecting against malicious traffic

- H04L63/1441—Countermeasures against malicious traffic

- H04L63/145—Countermeasures against malicious traffic the attack involving the propagation of malware through the network, e.g. viruses, trojans or worms

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/14—Protection against unauthorised use of memory or access to memory

- G06F12/1458—Protection against unauthorised use of memory or access to memory by checking the subject access rights

- G06F12/1483—Protection against unauthorised use of memory or access to memory by checking the subject access rights using an access-table, e.g. matrix or list

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/44—Arrangements for executing specific programs

- G06F9/455—Emulation; Interpretation; Software simulation, e.g. virtualisation or emulation of application or operating system execution engines

- G06F9/45533—Hypervisors; Virtual machine monitors

- G06F9/45558—Hypervisor-specific management and integration aspects

- G06F2009/45587—Isolation or security of virtual machine instances

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/10—Providing a specific technical effect

- G06F2212/1052—Security improvement

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/15—Use in a specific computing environment

- G06F2212/151—Emulated environment, e.g. virtual machine

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/65—Details of virtual memory and virtual address translation

- G06F2212/651—Multi-level translation tables

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/65—Details of virtual memory and virtual address translation

- G06F2212/657—Virtual address space management

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2221/00—Indexing scheme relating to security arrangements for protecting computers, components thereof, programs or data against unauthorised activity

- G06F2221/03—Indexing scheme relating to G06F21/50, monitoring users, programs or devices to maintain the integrity of platforms

- G06F2221/033—Test or assess software

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Computer Security & Cryptography (AREA)

- Software Systems (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Virology (AREA)

- Health & Medical Sciences (AREA)

- General Health & Medical Sciences (AREA)

- Signal Processing (AREA)

- Computer Networks & Wireless Communication (AREA)

- Computing Systems (AREA)

- Memory System Of A Hierarchy Structure (AREA)

- Storage Device Security (AREA)

- Debugging And Monitoring (AREA)

Description

[0001]本出願は、2014年8月18日に出願された、「Systems And Methods for Exposing A Current Processor Instruction Upon Exiting A Virtual Machine(仮想マシンを終了する際に現在のプロセッサ命令を公開するためのシステムおよび方法)」という名称の米国仮特許出願第62/038,476号の出願日の利益を主張するものであり、そのすべての内容は、参照により本明細書に組み込まれている。

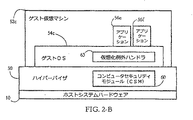

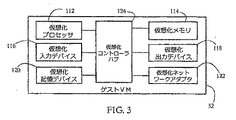

[0025]図1は、本発明のいくつかの実施形態によるホストシステム10の例示的ハードウェア構成を示したものである。ホストシステム10は、企業サーバなどの法人組織の計算デバイス、またはパーソナルコンピュータ、タブレットコンピュータもしくはスマートフォンなどのエンドユーザデバイスを表すことができる。他の例示的ホストシステムは、TV、ゲームコンソール、着用可能計算デバイス、またはメモリおよびプロセッサを有する任意の他の電子デバイスを含む。ホストシステム10を使用して、とりわけ、ブラウザ、文書処理アプリケーションおよび電子通信(例えば電子メール、インスタントメッセージング)アプリケーションなどの一組のソフトウェアアプリケーションが実行され得る。いくつかの実施形態では、ホストシステム10は、ハードウェアの仮想化を支援し、また、以下で示されるように一組の仮想マシンを公開するように構成される。

Claims (21)

- 仮想マシンとコンピュータセキュリティプログラムとを実行するように構成された少なくとも1つのハードウェアプロセッサを備えたホストシステムであって、前記少なくとも1つのハードウェアプロセッサは、

実行のためのゲスト命令を受け取るのに応答して、前記ゲスト命令の前記仮想マシン内での実行によりメモリアクセス許可の違反が生じるかどうかを判定することであって、前記ゲスト命令は、前記少なくとも1つのハードウェアプロセッサに、オペレータのオペランドへの適用の結果を求めるように命令し、前記ゲスト命令の前記違反のない実行は、前記結果の第1の場所への書き込みを生じさせる、判定することと、

前記ゲスト命令の実行により前記違反が生じるかどうかの判定に応答して、前記ゲスト命令の実行により前記違反が生じる場合に、前記結果を前記第1の場所とは異なる第2の場所に書き込むことであって、前記第2の場所は前記コンピュータセキュリティプログラムからアクセス可能である、書き込むことと、

前記結果の前記第2の場所への書き込みに応答して、前記ゲスト命令の実行から前記コンピュータセキュリティプログラムの実行に切り換えることであって、前記コンピュータセキュリティプログラムは、前記違反がコンピュータセキュリティの脅威を示すかどうかを判定するように構成された、切り換えることと

を行うようにさらに構成された、ホストシステム。 - 請求項1に記載のホストシステムであって、前記第1の場所は前記少なくとも1つのハードウェアプロセッサの汎用レジスタである、ホストシステム。

- 請求項1に記載のホストシステムであって、前記第1の場所は前記少なくとも1つのハードウェアプロセッサの制御レジスタである、ホストシステム。

- 請求項1に記載のホストシステムであって、前記第1の場所は前記ホストシステムのメモリのセクションを含む、ホストシステム。

- 請求項1に記載のホストシステムであって、前記結果はメモリアドレスを含む、ホストシステム。

- 請求項1に記載のホストシステムであって、前記結果は前記オペランドを含む、ホストシステム。

- 請求項1に記載のホストシステムであって、前記コンピュータセキュリティプログラムは前記仮想マシン内で実行される、ホストシステム。

- 請求項1に記載のホストシステムであって、前記コンピュータセキュリティプログラムは前記仮想マシン外で実行される、ホストシステム。

- 請求項1に記載のホストシステムであって、前記第2の場所は、前記少なくとも1つのハードウェアプロセッサの所定のレジスタを含む、ホストシステム。

- 請求項1に記載のホストシステムであって、前記第2の場所は、前記ホストシステムのメモリの所定のセクションを含む、ホストシステム。

- 請求項1に記載のホストシステムであって、前記第2の場所は、前記仮想マシンの現在状態を示すデータ構造を含む、ホストシステム。

- 請求項1に記載のホストシステムであって、前記少なくとも1つのハードウェアプロセッサは、前記コンピュータセキュリティプログラムの実行に切り換えるのに応答して、前記結果を前記第2の場所から読み出すようにさらに構成された、ホストシステム。

- 請求項12に記載のホストシステムであって、前記少なくとも1つのハードウェアプロセッサは、前記結果を読み出すのに応答して、前記結果を、前記ゲスト命令に従って定まる宛先に書き込むようにさらに構成された、ホストシステム。

- 請求項1に記載のホストシステムであって、前記コンピュータセキュリティプログラムは、前記少なくとも1つのハードウェアプロセッサにより実行されると、前記少なくとも1つのハードウェアプロセッサに、前記結果を前記第2の場所から読み出し、前記結果を、前記ゲスト命令に従って定まる宛先に書き込むことをさせる命令を含む、ホストシステム。

- 請求項1に記載のホストシステムであって、前記少なくとも1つのハードウェアプロセッサは、前記コンピュータセキュリティプログラムの実行に切り換えるのに応答して、

前記ゲスト命令がアトミック命令であるかどうかを判定し、

それに応答して、前記ゲスト命令がアトミック命令である場合に、前記ゲスト命令を前記仮想マシン内で実行する

ようにさらに構成された、ホストシステム。 - ホストシステムをコンピュータセキュリティの脅威から保護する方法であって、

実行のためのゲスト命令を受け取るのに応答して、前記ホストシステムの少なくとも1つのハードウェアプロセッサが、前記ゲスト命令の実行によりメモリアクセス許可の違反が生じるかどうかを判定するステップであって、前記ゲスト命令は、前記ホストシステムによって公開されるゲスト仮想マシン内で実行され、前記ゲスト命令は、前記少なくとも1つのハードウェアプロセッサに、オペレータのオペランドへの適用の結果を求めるように命令し、前記ゲスト命令の前記違反のない実行は、前記結果の第1の場所への書き込みを生じさせる、ステップと、

前記ゲスト命令の実行により前記違反が生じるかどうかの判定に応答して、前記ゲスト命令の実行により前記違反が生じる場合に、前記少なくとも1つのハードウェアプロセッサが、前記結果を前記第1の場所とは異なる第2の場所に書き込むステップであって、前記第2の場所はコンピュータセキュリティプログラムからアクセス可能である、ステップと、

前記結果の前記第2の場所への書き込みに応答して、前記少なくとも1つのハードウェアプロセッサが、前記ゲスト命令の実行から前記コンピュータセキュリティプログラムの実行に切り換えるステップであって、前記コンピュータセキュリティプログラムは、前記違反がコンピュータセキュリティの脅威を示すかどうかを判定するように構成された、ステップと

を含む方法。 - 請求項16に記載の方法であって、前記コンピュータセキュリティプログラムの実行に切り換えるのに応答して、前記少なくとも1つのハードウェアプロセッサが、前記結果を前記第2の場所から読み出すステップをさらに含む方法。

- 請求項17に記載の方法であって、前記結果を読み出すのに応答して、前記少なくとも1つのハードウェアプロセッサが、前記結果を、前記ゲスト命令に従い定まる宛先に書き込むステップをさらに含む方法。

- ホストシステムの少なくとも1つのハードウェアプロセッサであって、

実行のためのゲスト命令を受け取るのに応答して、前記ゲスト命令の実行によりメモリアクセス許可の違反が生じるかどうかを判定することであって、前記ゲスト命令は、前記ホストシステムによって公開されるゲスト仮想マシン内で実行され、前記ゲスト命令は、前記ホストシステムによって公開されるゲスト仮想マシン内で実行され、前記ゲスト命令は、前記少なくとも1つのハードウェアプロセッサに、オペレータのオペランドへの適用の結果を求めるように命令し、前記ゲスト命令の前記違反のない実行は、前記結果の第1の場所への書き込みを生じさせる、判定することと

前記ゲスト命令の実行により前記違反が生じるかどうかの判定に応答して、前記ゲスト命令の実行により前記違反が生じる場合に、前記結果を前記第1の場所とは異なる第2の場所に書き込むことであって、前記第2の場所はコンピュータセキュリティプログラムからアクセス可能である、書き込むことと、

前記結果の前記第2の場所への書き込みに応答して、前記ゲスト命令の実行からコンピュータセキュリティプログラムの実行に切り換えることであって、前記コンピュータセキュリティプログラムは、前記違反がコンピュータセキュリティの脅威を示すかどうかを判定するように構成された、切り換えることと

を行うように構成された少なくとも1つのハードウェアプロセッサ。 - ホストシステムをコンピュータセキュリティの脅威から保護するためのプログラムであって、前記プログラムは、前記ホストシステムの少なくとも1つのハードウェアプロセッサに、

実行のためのゲスト命令を受け取るのに応答して、前記ゲスト命令の実行によりメモリアクセス許可の違反が生じるかどうかを判定することであって、前記ゲスト命令は、前記ホストシステムによって公開されるゲスト仮想マシン内で実行され、前記ゲスト命令は、前記少なくとも1つのハードウェアプロセッサに、オペレータのオペランドへの適用の結果を求めるように命令し、前記ゲスト命令の前記違反のない実行は、前記結果の第1の場所への書き込みを生じさせる、判定することと、

前記ゲスト命令の実行により前記違反が生じるかどうかの判定に応答して、前記ゲスト命令の実行により前記違反が生じる場合に、前記結果を前記第1の場所とは異なる第2の場所に書き込むことであって、前記第2の場所はコンピュータセキュリティプログラムからアクセス可能である、書き込むことと、

前記結果の前記第2の場所への書き込みに応答して、前記ゲスト命令の実行から前記コンピュータセキュリティプログラムの実行に切り換えることであって、前記コンピュータセキュリティプログラムは、前記違反がコンピュータセキュリティの脅威を示すかどうかを判定するように構成された、切り替えることと

を行わせる、プログラム。 - 請求項20に記載のプログラムを格納したコンピュータ可読記憶媒体。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201462038476P | 2014-08-18 | 2014-08-18 | |

| US62/038,476 | 2014-08-18 | ||

| US14/489,820 US9672354B2 (en) | 2014-08-18 | 2014-09-18 | Systems and methods for exposing a result of a current processor instruction upon exiting a virtual machine |

| US14/489,820 | 2014-09-18 | ||

| PCT/RO2015/050009 WO2016118033A2 (en) | 2014-08-18 | 2015-08-11 | Systems and methods for exposing a result of a current processor instruction upon exiting a virtual machine |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2017526071A JP2017526071A (ja) | 2017-09-07 |

| JP2017526071A5 JP2017526071A5 (ja) | 2018-04-05 |

| JP6496401B2 true JP6496401B2 (ja) | 2019-04-03 |

Family

ID=55302381

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017509643A Active JP6496401B2 (ja) | 2014-08-18 | 2015-08-11 | 仮想マシンを終了する際に現在のプロセッサ命令の結果を公開するためのシステムおよび方法 |

Country Status (12)

| Country | Link |

|---|---|

| US (2) | US20160048679A1 (ja) |

| EP (2) | EP3183660A2 (ja) |

| JP (1) | JP6496401B2 (ja) |

| KR (2) | KR102116571B1 (ja) |

| CN (2) | CN106575236A (ja) |

| AU (2) | AU2015378729B2 (ja) |

| CA (2) | CA2954510A1 (ja) |

| ES (1) | ES2732876T3 (ja) |

| IL (2) | IL249849A0 (ja) |

| RU (2) | RU2017104753A (ja) |

| SG (2) | SG11201700794SA (ja) |

| WO (2) | WO2016118032A2 (ja) |

Families Citing this family (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9756074B2 (en) * | 2013-12-26 | 2017-09-05 | Fireeye, Inc. | System and method for IPS and VM-based detection of suspicious objects |

| US20150205962A1 (en) * | 2014-01-23 | 2015-07-23 | Cylent Systems, Inc. | Behavioral analytics driven host-based malicious behavior and data exfiltration disruption |

| GB2532415A (en) | 2014-11-11 | 2016-05-25 | Ibm | Processing a guest event in a hypervisor-controlled system |

| US9940455B2 (en) * | 2015-02-25 | 2018-04-10 | International Business Machines Corporation | Programming code execution management |

| US10726127B1 (en) | 2015-06-30 | 2020-07-28 | Fireeye, Inc. | System and method for protecting a software component running in a virtual machine through virtual interrupts by the virtualization layer |

| US10395029B1 (en) | 2015-06-30 | 2019-08-27 | Fireeye, Inc. | Virtual system and method with threat protection |

| US10642753B1 (en) | 2015-06-30 | 2020-05-05 | Fireeye, Inc. | System and method for protecting a software component running in virtual machine using a virtualization layer |

| US10216927B1 (en) | 2015-06-30 | 2019-02-26 | Fireeye, Inc. | System and method for protecting memory pages associated with a process using a virtualization layer |

| US11113086B1 (en) | 2015-06-30 | 2021-09-07 | Fireeye, Inc. | Virtual system and method for securing external network connectivity |

| US10033759B1 (en) | 2015-09-28 | 2018-07-24 | Fireeye, Inc. | System and method of threat detection under hypervisor control |

| US10121004B2 (en) * | 2015-10-07 | 2018-11-06 | Electronics And Telecommunications Research Institute | Apparatus and method for monitoring virtual machine based on hypervisor |

| US10135701B2 (en) * | 2016-02-19 | 2018-11-20 | At&T Intellectual Property I, L.P. | Context-aware virtualized control decision support system for providing quality of experience assurance for internet protocol streaming video services |

| US20210026950A1 (en) * | 2016-03-07 | 2021-01-28 | Crowdstrike, Inc. | Hypervisor-based redirection of system calls and interrupt-based task offloading |

| US20210049292A1 (en) * | 2016-03-07 | 2021-02-18 | Crowdstrike, Inc. | Hypervisor-Based Interception of Memory and Register Accesses |

| US10635479B2 (en) * | 2016-12-19 | 2020-04-28 | Bitdefender IPR Management Ltd. | Event filtering for virtual machine security applications |

| US10613897B1 (en) * | 2016-12-21 | 2020-04-07 | Ca, Inc. | Systems and methods for creating program-specific execution environments |

| US10243746B2 (en) | 2017-02-27 | 2019-03-26 | Red Hat, Inc. | Systems and methods for providing I/O state protections in a virtualized environment |

| US9935818B1 (en) | 2017-05-02 | 2018-04-03 | At&T Intellectual Property I, L.P. | Diagnostic traffic generation for automatic testing and troubleshooting |

| US10936353B2 (en) * | 2017-05-16 | 2021-03-02 | Dell Products L.P. | Systems and methods for hypervisor-assisted hardware accelerator offloads in a virtualized information handling system environment |

| US10546120B2 (en) * | 2017-09-25 | 2020-01-28 | AO Kaspersky Lab | System and method of forming a log in a virtual machine for conducting an antivirus scan of a file |

| US10698783B2 (en) * | 2018-01-09 | 2020-06-30 | Vmware, Inc. | Virtualization detection in a computing system |

| US11003777B2 (en) | 2018-04-16 | 2021-05-11 | International Business Machines Corporation | Determining a frequency at which to execute trap code in an execution path of a process executing a program to generate a trap address range to detect potential malicious code |

| US10810304B2 (en) * | 2018-04-16 | 2020-10-20 | International Business Machines Corporation | Injecting trap code in an execution path of a process executing a program to generate a trap address range to detect potential malicious code |

| JP7035787B2 (ja) * | 2018-05-14 | 2022-03-15 | 富士通株式会社 | 演算処理装置および演算処理装置の制御方法 |

| KR102067735B1 (ko) * | 2018-06-20 | 2020-01-17 | 연세대학교 산학협력단 | 가상화 시스템의 메모리 관리 장치 및 그 방법 |

| US11385918B2 (en) * | 2019-01-23 | 2022-07-12 | Vmware, Inc. | Dynamic discovery of internal kernel functions and global data |

| US11347869B2 (en) * | 2019-03-08 | 2022-05-31 | International Business Machines Corporation | Secure interface control high-level page management |

| US11206128B2 (en) | 2019-03-08 | 2021-12-21 | International Business Machines Corporation | Secure paging with page change detection |

| US11403409B2 (en) | 2019-03-08 | 2022-08-02 | International Business Machines Corporation | Program interruptions for page importing/exporting |

| US11221869B2 (en) | 2020-03-25 | 2022-01-11 | Red Hat, Inc. | Memory efficient host virtual address management for hypercalls |

| US11886351B2 (en) | 2020-03-25 | 2024-01-30 | Red Hat, Inc. | Memory efficient virtual address management for system calls |

| CN112596921A (zh) * | 2020-12-17 | 2021-04-02 | 海光信息技术股份有限公司 | 系统调用处理方法及处理装置 |

| US20220308867A1 (en) * | 2021-03-26 | 2022-09-29 | Intel Corporation | Apparatus and method for managing unsupported instruction set architecture (isa) features in a virtualized environment |

| US12020059B2 (en) * | 2021-08-30 | 2024-06-25 | International Business Machines Corporation | Inaccessible prefix pages during virtual machine execution |

| US20230334144A1 (en) * | 2022-04-19 | 2023-10-19 | Microsoft Technology Licensing, Llc | Provisioning a security component from a cloud host to a guest virtual resource unit |

Family Cites Families (44)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4985825A (en) * | 1989-02-03 | 1991-01-15 | Digital Equipment Corporation | System for delaying processing of memory access exceptions until the execution stage of an instruction pipeline of a virtual memory system based digital computer |

| US5926646A (en) | 1997-09-11 | 1999-07-20 | Advanced Micro Devices, Inc. | Context-dependent memory-mapped registers for transparent expansion of a register file |

| US5870575A (en) * | 1997-09-22 | 1999-02-09 | International Business Machines Corporation | Indirect unconditional branches in data processing system emulation mode |

| US6625725B1 (en) | 1999-12-22 | 2003-09-23 | Intel Corporation | Speculative reuse of code regions |

| US7451324B2 (en) * | 2002-05-31 | 2008-11-11 | Advanced Micro Devices, Inc. | Secure execution mode exceptions |

| US20030229794A1 (en) * | 2002-06-07 | 2003-12-11 | Sutton James A. | System and method for protection against untrusted system management code by redirecting a system management interrupt and creating a virtual machine container |

| US7124327B2 (en) * | 2002-06-29 | 2006-10-17 | Intel Corporation | Control over faults occurring during the operation of guest software in the virtual-machine architecture |

| US6922760B2 (en) * | 2002-12-05 | 2005-07-26 | Lsi Logic Corporation | Distributed result system for high-performance wide-issue superscalar processor |

| US7111145B1 (en) | 2003-03-25 | 2006-09-19 | Vmware, Inc. | TLB miss fault handler and method for accessing multiple page tables |

| US7620949B2 (en) * | 2004-03-31 | 2009-11-17 | Intel Corporation | Method and apparatus for facilitating recognition of an open event window during operation of guest software in a virtual machine environment |

| US7707341B1 (en) | 2004-05-11 | 2010-04-27 | Advanced Micro Devices, Inc. | Virtualizing an interrupt controller |

| US7370181B2 (en) | 2004-06-22 | 2008-05-06 | Intel Corporation | Single stepping a virtual machine guest using a reorder buffer |

| US7581085B1 (en) | 2005-09-08 | 2009-08-25 | Parallels Software International, Inc. | Fast stub and frame technology for virtual machine optimization |

| US20070106986A1 (en) | 2005-10-25 | 2007-05-10 | Worley William S Jr | Secure virtual-machine monitor |

| US20070136724A1 (en) | 2005-12-12 | 2007-06-14 | Arun Sharma | Transferring registers in transitions between computer environments |

| US20070245117A1 (en) * | 2006-04-12 | 2007-10-18 | Hob Gmbh & Co. Kg | Processor comprising an instruction set and registers for simplified opcode access |

| US7634642B2 (en) | 2006-07-06 | 2009-12-15 | International Business Machines Corporation | Mechanism to save and restore cache and translation trace for fast context switch |

| US8595487B2 (en) | 2006-11-01 | 2013-11-26 | Vmware, Inc. | Virtualization hardware for device driver isolation |

| US7996836B1 (en) | 2006-12-29 | 2011-08-09 | Symantec Corporation | Using a hypervisor to provide computer security |

| US8561060B2 (en) | 2007-04-26 | 2013-10-15 | Advanced Micro Devices, Inc. | Processor and method configured to determine an exit mechanism using an intercept configuration for a virtual machine |

| JP2009009232A (ja) * | 2007-06-26 | 2009-01-15 | Hitachi Ltd | コンピュータとカーネル保護方法並びにコンピュータソフトウエア |

| US8261028B2 (en) | 2007-12-31 | 2012-09-04 | Intel Corporation | Cached dirty bits for context switch consistency checks |

| US8307360B2 (en) | 2008-01-22 | 2012-11-06 | Advanced Micro Devices, Inc. | Caching binary translations for virtual machine guest |

| US8443363B1 (en) * | 2008-05-30 | 2013-05-14 | Symantec Corporation | Coordinated virtualization activities |

| US8201169B2 (en) * | 2009-06-15 | 2012-06-12 | Vmware, Inc. | Virtual machine fault tolerance |

| US8612975B2 (en) | 2009-07-07 | 2013-12-17 | Advanced Micro Devices, Inc. | World switch between virtual machines with selective storage of state information |

| US8707457B2 (en) * | 2010-05-09 | 2014-04-22 | Citrix Systems, Inc. | Methods and systems for forcing an application to store data in a secure storage location |

| US9165136B1 (en) | 2010-10-27 | 2015-10-20 | Amazon Technologies, Inc. | Supervising execution of untrusted code |

| US8578080B2 (en) | 2011-07-01 | 2013-11-05 | Intel Corporation | Secure handling of interrupted events utilizing a virtual interrupt definition table |

| US8984478B2 (en) * | 2011-10-03 | 2015-03-17 | Cisco Technology, Inc. | Reorganization of virtualized computer programs |

| US8694738B2 (en) | 2011-10-11 | 2014-04-08 | Mcafee, Inc. | System and method for critical address space protection in a hypervisor environment |

| US9069586B2 (en) | 2011-10-13 | 2015-06-30 | Mcafee, Inc. | System and method for kernel rootkit protection in a hypervisor environment |

| WO2013089695A1 (en) | 2011-12-14 | 2013-06-20 | Intel Corporation | Method and system for monitoring calls to an application program interface (api) function |

| US20130174144A1 (en) | 2011-12-28 | 2013-07-04 | Ati Technologies Ulc | Hardware based virtualization system |

| US8719546B2 (en) * | 2012-01-04 | 2014-05-06 | Intel Corporation | Substitute virtualized-memory page tables |

| US9336046B2 (en) | 2012-06-15 | 2016-05-10 | International Business Machines Corporation | Transaction abort processing |

| US9361115B2 (en) | 2012-06-15 | 2016-06-07 | International Business Machines Corporation | Saving/restoring selected registers in transactional processing |

| US8966324B2 (en) | 2012-06-15 | 2015-02-24 | International Business Machines Corporation | Transactional execution branch indications |

| US9311101B2 (en) | 2012-06-15 | 2016-04-12 | International Business Machines Corporation | Intra-instructional transaction abort handling |

| KR20150038574A (ko) | 2012-08-03 | 2015-04-08 | 놀쓰캐롤라이나 스테이트 유니버시티 | 타겟 디바이스의 능동 모니터링, 메모리 보호 및 무결성 검증을 위한 방법, 시스템 및 컴퓨터 판독 가능 매체 |

| US9256427B2 (en) * | 2012-12-11 | 2016-02-09 | International Business Machines Corporation | Tracking multiple conditions in a general purpose register and instruction therefor |

| RU2522019C1 (ru) * | 2012-12-25 | 2014-07-10 | Закрытое акционерное общество "Лаборатория Касперского" | Система и способ обнаружения угроз в коде, исполняемом виртуальной машиной |

| US9058415B1 (en) * | 2013-03-15 | 2015-06-16 | Google Inc. | Counting events using hardware performance counters and annotated instructions |

| US9292686B2 (en) | 2014-01-16 | 2016-03-22 | Fireeye, Inc. | Micro-virtualization architecture for threat-aware microvisor deployment in a node of a network environment |

-

2014

- 2014-09-18 US US14/489,801 patent/US20160048679A1/en not_active Abandoned

- 2014-09-18 US US14/489,820 patent/US9672354B2/en active Active

-

2015

- 2015-08-11 RU RU2017104753A patent/RU2017104753A/ru unknown

- 2015-08-11 KR KR1020177004414A patent/KR102116571B1/ko active IP Right Grant

- 2015-08-11 CN CN201580042152.0A patent/CN106575236A/zh active Pending

- 2015-08-11 CA CA2954510A patent/CA2954510A1/en not_active Abandoned

- 2015-08-11 SG SG11201700794SA patent/SG11201700794SA/en unknown

- 2015-08-11 SG SG11201700795VA patent/SG11201700795VA/en unknown

- 2015-08-11 WO PCT/RO2015/050008 patent/WO2016118032A2/en active Application Filing

- 2015-08-11 JP JP2017509643A patent/JP6496401B2/ja active Active

- 2015-08-11 AU AU2015378729A patent/AU2015378729B2/en active Active

- 2015-08-11 RU RU2017104752A patent/RU2686552C2/ru active

- 2015-08-11 CA CA2954604A patent/CA2954604C/en active Active

- 2015-08-11 WO PCT/RO2015/050009 patent/WO2016118033A2/en active Application Filing

- 2015-08-11 ES ES15879117T patent/ES2732876T3/es active Active

- 2015-08-11 CN CN201580042692.9A patent/CN106575237A/zh active Pending

- 2015-08-11 EP EP15879116.0A patent/EP3183660A2/en not_active Withdrawn

- 2015-08-11 EP EP15879117.8A patent/EP3183682B1/en active Active

- 2015-08-11 AU AU2015378728A patent/AU2015378728A1/en not_active Abandoned

- 2015-08-11 KR KR1020177004413A patent/KR20170042602A/ko unknown

-

2016

- 2016-12-29 IL IL249849A patent/IL249849A0/en active IP Right Grant

- 2016-12-29 IL IL249848A patent/IL249848A0/en unknown

Also Published As

| Publication number | Publication date |

|---|---|

| WO2016118033A3 (en) | 2016-10-27 |

| EP3183682A2 (en) | 2017-06-28 |

| WO2016118032A3 (en) | 2016-10-13 |

| EP3183660A2 (en) | 2017-06-28 |

| RU2017104752A3 (ja) | 2019-02-01 |

| SG11201700795VA (en) | 2017-03-30 |

| WO2016118032A8 (en) | 2017-01-05 |

| CN106575236A (zh) | 2017-04-19 |

| EP3183682B1 (en) | 2019-04-03 |

| CA2954604C (en) | 2020-09-29 |

| WO2016118032A2 (en) | 2016-07-28 |

| KR20170042602A (ko) | 2017-04-19 |

| US20160048680A1 (en) | 2016-02-18 |

| KR20170042603A (ko) | 2017-04-19 |

| RU2017104753A (ru) | 2018-09-20 |

| WO2016118033A2 (en) | 2016-07-28 |

| CA2954510A1 (en) | 2016-07-28 |

| IL249849A0 (en) | 2017-03-30 |

| ES2732876T3 (es) | 2019-11-26 |

| CN106575237A (zh) | 2017-04-19 |

| IL249848A0 (en) | 2017-03-30 |

| US20160048679A1 (en) | 2016-02-18 |

| JP2017526071A (ja) | 2017-09-07 |

| AU2015378729A1 (en) | 2017-01-19 |

| US9672354B2 (en) | 2017-06-06 |

| RU2017104752A (ru) | 2018-09-20 |

| CA2954604A1 (en) | 2016-07-28 |

| AU2015378728A1 (en) | 2017-01-19 |

| RU2686552C2 (ru) | 2019-04-29 |

| AU2015378729B2 (en) | 2020-07-09 |

| SG11201700794SA (en) | 2017-03-30 |

| KR102116571B1 (ko) | 2020-06-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6496401B2 (ja) | 仮想マシンを終了する際に現在のプロセッサ命令の結果を公開するためのシステムおよび方法 | |

| US9400885B2 (en) | Computer security systems and methods using virtualization exceptions | |

| US10140448B2 (en) | Systems and methods of asynchronous analysis of event notifications for computer security applications | |

| JP7036821B2 (ja) | 仮想マシンセキュリティ適用例のためのイベントフィルタ処理 | |

| US20160210069A1 (en) | Systems and Methods For Overriding Memory Access Permissions In A Virtual Machine | |

| Shi et al. | Handling anti-virtual machine techniques in malicious software | |

| US20160048458A1 (en) | Computer Security Systems and Methods Using Hardware-Accelerated Access To Guest Memory From Below The Operating System | |

| US9536084B1 (en) | Systems and methods for delivering event-filtered introspection notifications | |

| US9596261B1 (en) | Systems and methods for delivering context-specific introspection notifications | |

| NL2030804B1 (en) | Flexible return and event delivery | |

| Kuznetsov et al. | Privbox: Faster system calls through sandboxed privileged execution | |

| US9531735B1 (en) | Systems and methods for delivering introspection notifications from a virtual machine |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180226 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180226 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190130 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190208 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190308 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6496401 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |