図1は、本実施形態によるワイヤレスセンサノード100の構成例を示す図である。ワイヤレスセンサノード100は、全体制御部101、センサ部102、RF(Radio Frequency)部103、発電電源管理部104、アンテナ105及び発電素子106を有する。発電素子106は、光、温度差又は振動などのエネルギー112を基に発電を行い、電力を発電電源管理部104に供給する。発電電源管理部104は、電力を管理し、全体制御部101、センサ部102及びRF部103に対して、電力を供給する。全体制御部101は、I2C(Inter-Integrated Circuit)、SPI(Serial Peripheral Interface)などのシリアルインターフェースを介して、センサ部102、RF部103及び発電電源管理部104を制御する。センサ部102は、温度、照度、加速度又は圧力などの情報111を検出し、情報111を全体制御部101に出力する。全体制御部101は、RF部103及びアンテナ105を介して、情報111を無線信号113として送信する。また、全体制御部101は、RF部103及びアンテナ105を介して、その他の情報を無線信号113として送受信することができる。

ワイヤレスセンサノード100には電池や商用電源が接続されず、発電素子106は、環境から得られるエネルギー112を基に自己発電する。したがって、ワイヤレスセンサノード100は、徹底的な低消費電力が求められる。ワイヤレスセンサノード100に求められる様々な要求仕様や状況に応じた制御を行うために、全体制御部101は、プログラマビリティが求められるため、MCU(マイクロコントローラユニット)が用いられる。

図2は、全体制御部101の構成例を示す図である。全体制御部101は、処理システムであり、中央処理装置(CPU)201、ポーリング回路202、RAM203、割り込みコントローラ204、バス205、ダイレクトメモリアクセスコントローラ(DMAC)206、第1の周辺回路PH1、第2の周辺回路PH2、第3の周辺回路PH3及び第4の周辺回路PH4を有する。バス205には、ポーリング回路202、RAM203、DMAC206及び周辺回路PH1〜PH4が接続される。バス205は、ポーリング回路202及び周辺回路PH1〜PH4の間に接続される。割り込みコントローラ204は、周辺回路PH1〜PH4の割り込み信号IR1〜IR4及び外部割込み信号IRRを入力し、割り込み信号IRをCPU201及びポーリング回路202に出力する。周辺回路PH1〜PH4は、それぞれ、イネーブル信号ENS1〜ENS4をポーリング回路202に出力する。周辺回路PH1〜PH3は、I2C回路又はSPI回路などのインターフェース回路であり、それぞれ、図1のセンサ部102、RF部103及び発電電源管理部104に接続される。

図3は、各周辺回路PH1〜PH4の一部の構成例を示す図である。周辺回路PH1〜PH4は、それぞれ、アドレスレジスタ301、送信データバッファレジスタ302、受信データバッファレジスタ303、制御レジスタ304、ステータスレジスタ305、論理和(OR)回路306及びセレクタ307を有する。レジスタ301〜305のデータ端子D及びイネーブル端子ENは、論理回路311〜320の32ビット出力データを入力する。レジスタ301〜305は、それぞれ、クロック信号に同期して、データ端子Dの入力データをラッチし、ラッチした32ビットデータを出力端子Qから出力する。セレクタ307は、バス205から入力するアドレスADDRに応じて、レジスタ301〜305の32ビット出力データのうちのいずれかを選択し、32ビットデータRDATAをバス205に出力する。論理和回路306は、ステータスレジスタ305のイネーブル端子ENの32ビットデータの論理和をイネーブル信号ENSとして出力する。

CPU201が周辺回路PH1〜PH3を介してセンサ部102、RF部103及び発電電源管理部104へデータ送信する手順は次の通りである。例として、CPU201が周辺回路PH1を介してセンサ部102へデータ送信する手順を説明する。まず、CPU201は、ポーリング回路202及びバス205を介して、送信先アドレスを周辺回路PH1内のアドレスレジスタ301に書き込む。なお、送信先アドレスは、センサ部102を示すアドレスである。次に、CPU201は、ポーリング回路202及びバス205を介して、送信データを周辺回路PH1内の送信データバッファレジスタ302に書き込む。ここで、送信データは、センサデータ読み出しコマンド等を含む。次に、CPU201は、ポーリング回路202及びバス205を介して、送信の指示を周辺回路PH1内の制御レジスタ304に書き込む。その後、周辺回路PH1は、送信データをセンサ部102に送信する。センサ部102は、送信データに従い、情報111を検出し、周辺回路104、バス205及びポーリング回路202を介して、情報111をCPU201に送信する。

図4は、CPU201、ポーリング回路202、バス205及び周辺回路PH1間の信号を示す図である。周辺回路PH1の場合を例に示すが、周辺回路PH2〜PH4も周辺回路PH1の場合と同様である。リクエスト信号REQは、アクセスリクエスト信号である。アドレス信号ADDRは、アクセス先アドレス信号である。アクセス種類信号WRITEは、リード又はライトのアクセスの種類を示す信号である。ライトデータ信号WDATAは、ライトアクセス時のライトデータ信号である。リードデータ信号RDATAは、リードアクセス時のリードデータ信号である。レディ信号READYは、アクセス完了を示す信号である。

例えば、CPU201が32ビットCPUの場合、信号ADDR、WDATA、RDATAは32ビット信号である。信号REQ、ADDR、WRITE、WDATAは、アクセス元からアクセス先に出力される信号である。信号RDATA及びREADYは、アクセス先からアクセス元に出力される信号である。図4では、最終アクセス先が周辺回路PH1になっているが、CPU201がプログラムコードの読み出しやデータの読み出し、書き込みを行うため、図1のRAM203も最終アクセス先となり得る。また、図4では、CPU201がアクセス元になっているが、図2のDMAC206は、RAM203や周辺回路PH1〜PH4に対して読み出しや書き込みアクセスを行うのでアクセス元になり得る。ただし、DMAC206は、ポーリング処理を行わないので、ポーリング回路202を介する必要がなく、直接バス205に接続される。

ポーリング回路202は、CPU201からリクエスト信号REQ、アドレス信号ADDR、アクセス種類信号WRITE及びライトデータ信号WDATAを入力し、CPU201にレディ信号READY及びリードデータ信号RDATAを出力する。周辺回路PH1は、バス205を介して、ポーリング回路202からリクエスト信号REQ、アドレス信号ADDR、アクセス種類信号WRITE及びライトデータWDATAを入力し、ポーリング回路202にレディ信号READY及びリードデータ信号RDATAを出力する。

次に、通常のCPU201のポーリング処理を説明する。ポーリング対象としている周辺回路PH1は、CPU201から指示された処理が完了したら、32ビットのステータスレジスタ305の最下位ビットの値を0から1に変更する。CPU201は、32ビットのステータスレジスタ305の値を読み出し、最下位ビットの値を抽出する。最下位ビットが1である場合には、周辺回路PH1の処理が完了しているので、CPU201は、次の処理に移る。最下位ビットが0である場合、周辺回路PH1が、まだ処理を完了していないため、CPU201は、次の処理には移れず、再び周辺回路PH1の処理が完了したかを確認する処理を繰り返す。周辺回路PH1の処理実行に時間がかかり、ステータスレジスタ305の最下位ビットがなかなか1に変化しない場合、CPU201は、何度もステータスレジスタ305の最下位ビットを読み出して確認する処理を繰り返すことになる。本実施形態では、このような繰り返し処理をなくすための処理を説明する。本実施形態では、ステータスレジスタ305の最下位ビットを読み出して得られる値は必ず1であることが保証され、1回目の実行で必ず次の処理に進むことができる。以下、その詳細を説明する。

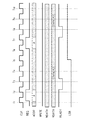

図5はCPU201及びポーリング回路202間の信号を示すタイミングチャートであり、図6はポーリング回路202及びバス205間の信号を示すタイミングチャートであり、図7はバス205及び周辺回路PH1間の信号を示すタイミングチャートである。信号CLKは、クロック信号である。信号LSBは、周辺回路PH1内のステータスレジスタ305内のデータの最下位ビットの信号である。

CPU201が周辺回路PH1内のステータスレジスタ305の最下位ビットに対して読み出しアクセスする例を説明する。すべての信号は、CPU201、ポーリング回路202、バス205及び周辺回路PH1に共通で供給されるクロック信号CLKの立ち上がりエッジで伝達される。CPU201は、ポーリング回路202に対して、図5の時刻T1において、アクセス要求を行ってもよいことを示す信号READY=1であることを確認し、信号REQ=1とするアクセス要求を出力する。それと同時に、CPU201は、ポーリング回路202に対して、アクセス先アドレスの信号ADDR=A’(ステータスレジスタ305の最下位ビットLSBを示すアドレス)、及びアクセス種類が読み出しアクセスであることを示す信号WRITE=0を出力する。

ポーリング回路202は、内部のアドレス信号生成部1001(図10)により、CPU201から入力された信号ADDR=A’を図6の信号ADDR=Aに変換してバス205へ出力する。また、ポーリング回路202は、CPU201から入力された信号REQ及び信号WRITEをそのままバス205へ出力する。

バス205は、ポーリング回路202からの信号REQ及びWRITEにより、CPU201から読み出しアクセスの要求が来ていることを知る。そして、バス205は、信号ADDRからアクセス先を判別し、アクセス先の周辺回路PH1に対して、ポーリング回路202からの信号REQ、ADDR、及びWRITEを出力する。周辺回路PH1は、ステータスレジスタ305の最下位ビットLSBの読み出しデータの準備中であることを示す信号READY=0をバス205に出力する。信号READYは、周辺回路PH1からバス205及びポーリング回路202を介してCPU201に出力される。CPU201は、信号READY=0となっていることから、読み出しアクセスがまだ実行中であることを知る。

時刻T3の後、周辺回路PH1は、アドレス信号ADDR=Aで指定されたステータスレジスタ305の値Data(A)の出力準備ができ、信号RDATA=Data(A)を出力し、それと同時に、信号RDATAが有効データであることを示す信号READY=1を出力する。この時、周辺回路PH1は、CPU201から指示されたセンサデータの読み出し処理が完了していないので、ステータスレジスタ305の最下位ビットLSBの値は0である。したがって、信号RDATAの最下位ビットLSBは0である。信号READY及びRDATAは、周辺回路PH1からバス205を介してポーリング回路202に出力される。

時刻T4では、ポーリング回路202は、クロック信号CLKの立ち上がりエッジで、信号READY=1となっていることから、それと同時に、信号RDATA=Data(A)が入力されていることを知る。ポーリング回路202は、32ビットの信号RDATAのうち、CPU201がポーリング対象として確認したい最下位ビットLSBの値を取り出し、この値がCPU201が期待する1であるかを確認する。最下位ビットLSBが0であるので、ポーリング回路202は、信号READY=0をCPU201に対して継続して出力する。

その所定時間後の時刻T6では、ポーリング回路202は、再び、バス205を介して、周辺回路PH1に対して、信号ADDR=A、信号REQ=1、信号WRITE=0を出力する。なお、時刻T6の前の時刻T5では、周辺回路PH1は、CPU201の指示によるセンサデータの読み出し処理が完了し、ステータスレジスタ305の最下位ビットLSBを0から1に変更する。

時刻T7の後では、周辺回路PH1は、ステータスレジスタ305の最下位ビットLSBの読み出しデータの準備中であることを示す信号READY=0を、バス205及びポーリング回路202を介して、CPU201に出力する。CPU201は、信号READY=0となっていることから、読み出しアクセスがまだ実行中であることを知る。

時刻T8の後、周辺回路PH1は、アドレス信号ADDR=Aで指定されたステータスレジスタ305の値Data(A)の出力準備ができ、信号RDATA=Data(A)を出力し、それと同時に、信号RDATAが有効データであることを示す信号READY=1を出力する。この時、周辺回路PH1は、CPU201から指示されたセンサデータの読み出し処理が完了しているので、ステータスレジスタ305の最下位ビットLSBの値は1である。したがって、信号RDATAの最下位ビットLSBは1である。信号READY及びRDATAは、周辺回路PH1からバス205を介してポーリング回路202に出力される。

時刻T8の後では、ポーリング回路202は、信号READY=1となっていることから、それと同時に、信号RDATA=Data(A)が入力されていることを知る。ポーリング回路202は、32ビットの信号RDATAのうち、CPU201がポーリング対象として確認したい最下位ビットLSBの値を取り出し、この値がCPU201が期待する1であるかを確認する。最下位ビットLSBが1であるので、ポーリング回路202は、CPU201に対して、信号READY=1及び32ビット信号RDATA=1を出力する。CPU201は、信号READY=1となっていることから、読み出しアクセスが終了したことを知る。この時、CPU201が入力する信号RDATAは、必ず1であることが保証されている。CPU201は、ステータスレジスタ305の最下位ビットLSBを読み出して得られる値は必ず1であることが保証され、1回目の実行で必ず次の処理に進むことができる。

以上のように、CPU201は、周辺回路PH1にリードアクセスするために、「1」のリクエスト信号REQ及び周辺回路PH1に対応するアドレス信号ADDRを出力する。周辺回路PH1は、CPU201のリクエスト信号REQに対応する処理が終了していない場合には「0」のレディ信号READYを出力し、CPU201のリクエスト信号REQに対応する処理が終了した場合には「1」のレディ信号REDY及びリードデータ信号RDATAを出力する。なお、信号REQ及びREADYは、それぞれ、「1」が活性化状態を示し、「0」が非活性化状態を示す。

ポーリング回路202は、信号RDATAの最下位ビットLSBが1になるまで、周辺回路PH1に対して、信号REQ=1等の出力を繰り返す。ポーリング回路202は、周辺回路PH1に対して、信号REQ=1等を2回出力しているが、CPU201は、信号REQ=1のアクセス要求を出力してから、実際に要求した信号RDATA=Data(A’)の到着までの1回の読み出しアクセスで期待する値の1を受け取っている。したがって、CPU201が信号REQ=1の読み出し及び確認処理を繰り返し実行する必要がないので、電力消費が抑えられ、プログラムを繰り返しRAM203から読み出すことによるRAM203の電力消費が抑えられる。

図8は、メモリマップを示す図である。以下、ポーリング回路202が、CPU201から入力するアドレス信号ADDRを基にCPU201が32ビットの信号RDATAのうちの何ビット目の値をポーリング処理のチェック対象としているのか、及び期待する値が0と1のどちらなのかを判別する方法を説明する。各レジスタ301〜305は、32ビットでバイトアドレッシング(1バイト=8ビット単位でアドレスが割り振られている)されているものとする。

第1の周辺回路PH1の各種レジスタ301〜305は、アドレス0x40000000から0x40000FFCにマッピングされている。ここで、0xは、16進数を示す。例えば、ステータスレジスタ305のアドレスは0x40000000、制御レジスタ304は0x40000004、受信データバッファレジスタ303は0x40000008などのようにマッピングされる。通常、CPU201がレジスタ301〜305の値を読み出したり、レジスタ301〜305に値を書き込むときは、これらのアドレスを用いてアクセスする。

アドレス0x50000000〜0x5001FFFCは、CPU201が第1の周辺回路PH1のレジスタのあるビットが0であることを期待して、レジスタに読み出しアクセスするときのためのアドレスである。アドレス0x60000000〜0x6001FFFCは、CPU201が第1の周辺回路PH1のレジスタのあるビットが1であることを期待して、レジスタに読み出しアクセスするときのためのアドレスである。

レジスタ領域801aは、第1の周辺回路PH1の通常レジスタ領域である。レジスタ領域801bは、第1の周辺回路PH1の期待値が0のレジスタ領域である。レジスタ領域801cは、第1の周辺回路PH1の期待値が1のレジスタ領域である。レジスタ領域802aは、第2の周辺回路PH2の通常レジスタ領域である。レジスタ領域802bは、第2の周辺回路PH2の期待値が0のレジスタ領域である。レジスタ領域802cは、第2の周辺回路PH2の期待値が1のレジスタ領域である。レジスタ領域804aは、第4の周辺回路PH4の通常レジスタ領域である。レジスタ領域804bは、第4の周辺回路PH4の期待値が0のレジスタ領域である。レジスタ領域804cは、第4の周辺回路PH4の期待値が1のレジスタ領域である。

図9は、第1の周辺回路PH1の通常レジスタ領域801a、期待値が0のレジスタ領域801b、及び期待値が1のレジスタ領域801cの例を示す図である。例えば、通常レジスタ領域801aのアドレスが0x40000000で指定されるレジスタの0ビット目(最下位ビット)Aを値が0であることを期待して読み出しアクセスするときは、CPU201は、信号ADDR=0x50000000をポーリング回路202に出力する。また、通常レジスタ領域801aのアドレスが0x40000000で指定されるレジスタの0ビット目(最下位ビット)Aを値が1であることを期待して読み出しアクセスするときは、CPU201は、信号ADDR=0x60000000をポーリング回路202に出力する。

通常レジスタ領域801aのアドレスが0x40000000で指定されるレジスタの1ビット目Bを値が0であることを期待して読み出しアクセスするときは、CPU201は、信号ADDR=0x50000004をポーリング回路202に出力する。また、通常レジスタ領域801aのアドレスが0x40000000で指定されるレジスタの1ビット目Bを値が1であることを期待して読み出しアクセスするときは、CPU201は、信号ADDR=0x60000004をポーリング回路202に出力する。

通常レジスタ領域801aのアドレスが0x40000FFCで指定されるレジスタの31ビット目(最上位ビット)Cを値が0であることを期待して読み出しアクセスするときは、CPU201は、信号ADDR=0x5001FFFCをポーリング回路202に出力する。また、通常レジスタ領域801aのアドレスが0x40000FFCで指定されるレジスタの31ビット目(最上位ビット)Cを値が1であることを期待して読み出しアクセスするときは、CPU201は、信号ADDR=0x6001FFFCをポーリング回路202に出力する。

ポーリング処理でアクセスしたいレジスタ301〜305の通常レジスタ領域801aのアドレスをAddr_n、ビット位置をBITとすると、このビットが0であることを期待して読み出しアクセスするときに、CPU201が出力するアドレス信号ADDRは、次式で表される。

ADDR=0x50000000+(Addr_n−0x40000000)×32×4+BIT×4

同様に、ポーリング処理でアクセスしたいレジスタ301〜305の通常レジスタ領域801aのアドレスをAddr_n、ビット位置をBITとすると、このビットが1であることを期待して読み出しアクセスするときに、CPU201が出力するアドレス信号ADDRは、次式で表される。

ADDR=0x60000000+(Addr_n−0x40000000)×32×4+BIT×4

図10は、ポーリング回路202の構成例を示す図である。ポーリング回路202は、アドレス信号生成部1001、レディ(READY)信号生成部1002、リードデータ(RDATA)信号生成部1003及びリクエスト(REQ)信号生成部1004を有する。

図11は、図10のアドレス信号生成部1001の構成例を示す図である。アドレス信号生成部1001は、アドレス比較部1101、アドレス変換部1102、アドレス保持部1103及びセレクタ1104を有する。アドレス信号生成部1001は、CPU201からの信号ADDRを変換し、変換した信号ADDRをバス205へ出力する。アドレス比較部1101は、CPU201から入力される32ビットの信号ADDRのうち、上位4ビットが0x5であれば、期待値0のレジスタ領域801bのアクセスと判断し、上位4ビットが0x6であれば、期待値1のレジスタ領域801cのアクセスと判断する。また、アドレス比較部1101は、上記の上位4ビットがそれ以外の値である場合、通常レジスタ領域801aへのアクセス、RAM203へのアクセスなど、ポーリング処理以外のアクセスと判断する。

アドレス比較部1101は、信号ADDRの上位4ビットが0x5又は0x6の場合、CPU201からポーリングのためのアクセス要求が来たことを伝えるため、「1」のポーリングアクセス信号を出力し、それ以外の場合、「0」のポーリングアクセス信号を出力する。また、アドレス比較部1101は、期待値信号として、信号ADDRの上位4ビットが0x5の場合は0を出力し、信号ADDRの上位4ビットが0x6の場合は1を出力する。また、アドレス比較部1101は、信号ADDRの下位7ビットを4で割った値を基にポーリング対象のビット位置を算出し、ビット位置信号を出力する。

アドレス変換部1102は、ポーリングアクセス信号が0の場合は、CPU201からの信号ADDRをそのままアドレス保持部1103及びセレクタ1104に出力する。また、アドレス変換部1102は、ポーリングアクセス信号が1の場合は、以下の手順でアドレスAddr_nを演算し、演算したアドレスAddr_nをアドレス保持部1103及びセレクタ1104に出力する。

(1)アドレス変換部1102は、期待値が0の場合、CPU201から入力される信号ADDRから0x50000000を減算し、期待値が1の場合、CPU201から入力される信号ADDRから0x60000000を減算する。

(2)アドレス変換部1102は、(1)で求めた値を7ビット論理右シフトする。

(3)アドレス変換部1102は、(2)で求めた値に0x40000000を加算する。

上記の手順により、CPU201がポーリング処理で確認したいビットを含むレジスタの通常レジスタ領域801aのアドレスAddr_nを復元できる。アドレス変換部1102は、アドレスAddr_nをアドレス保持部1103及びセレクタ1104に出力する。

アドレス保持部1103は、ポーリングアクセス信号が1の場合は、アドレス変換部1102が生成したアドレスAddr_nを保持する。これにより、周辺回路PH1から読み出したステータスレジスタ305の値が期待する値でないときにポーリング回路202が、ステータスレジスタ305の読み出しアクセスを繰り返し行うことが可能になる。

セレクタ1104は、ポーリングアクセス信号が0の場合は、アドレス変換部1102が出力する信号ADDRをそのままバス205へ出力する。この際、アドレス変換部1102は、アドレス変換を行わず、CPU201からの信号ADDRをそのまま出力している。また、セレクタ1104は、ポーリングアクセス信号が1の場合は、アドレス保持部1103が出力するアドレスAddr_nをバス205へ出力する。

以上のように、アドレス信号生成部1001は、CPU201から入力したアドレス信号ADDRが期待値0及び期待値1のレジスタ領域(第1のアドレス範囲)801b及び801cのアドレスである場合には、CPU201から入力したアドレス信号ADDRを通常レジスタ領域(第2のアドレス範囲)801aのアドレスに変換して、バス205を介して周辺回路PH1にアドレス信号ADDRを出力する。また、アドレス信号生成部1001は、CPU201から入力したアドレス信号ADDRが期待値0及び期待値1のレジスタ領域(第1のアドレス範囲)801b及び801cのアドレスでない場合には、CPU201から入力したアドレス信号ADDRと同じアドレス信号ADDRを、バス205を介して周辺回路PH1に出力する。アドレス保持部1103は、CPU201から入力したアドレス信号ADDRを通常レジスタ領域(第2のアドレス範囲)801aのアドレスに変換したアドレスを保持する。

図12は、図10のREADY信号生成部1002の構成例を示す図である。READY信号生成部1002は、セレクタR1,R2、ビット位置保持部1201、期待値保持部1202、期待値比較部1203、及びポーリング中断判定部1204を有する。READY信号生成部1002は、CPU201へ出力する信号READYを生成する。

ビット位置保持部1201は、ポーリング処理の間、図11のアドレス比較部1101が出力するビット位置信号を保持し、セレクタR1に出力する。セレクタR1は、バス205から入力される32ビットの信号RDATAのうち、ビット位置保持部1201が出力するビット位置信号が示すビット位置の値を選択し、ビット信号として出力する。

期待値保持部1202は、ポーリング処理の間、図11のアドレス比較部1101が出力する期待値信号を保持し、期待値比較部1203へ出力する。期待値比較部1203は、セレクタR1から入力されるビット信号と期待値保持部1202から入力される期待値信号を比較し、両者が一致した場合には「1」の期待値判定信号を出力し、両者が不一致の場合には「0」の期待値判定信号を出力する。ポーリング中断判定部1204は、CPU201へ入力される割り込み信号IRを入力し、CPU201に対して割り込みが発生した場合は、「1」のポーリング中断信号をセレクタR2に出力する。

セレクタR2は、図11のアドレス比較部1101が出力するポーリングアクセス信号、期待値比較部1203が出力する期待値判定信号、ポーリング中断判定部1204が出力するポーリング中断信号に応じて、バス205からの信号READY又は0をCPU201に出力する。セレクタR2が出力する信号は、ポーリング回路202からCPU201へ出力される信号READYである。

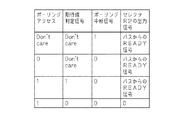

図13は、セレクタR2の動作を説明するための図である。セレクタR2は、ポーリングアクセス信号、期待値判定信号、及びポーリング中断信号に応じて、信号を出力する。セレクタR2は、ポーリング中断信号が1の場合、ポーリングアクセス信号、期待値判定信号の値にかかわらず、バス205からの信号READYを選択して出力する。その理由は後述する。また、セレクタR2は、ポーリング中断信号が0の場合、以下の動作を行う。

ポーリングアクセス信号が0の場合、CPU201はポーリングのためのアクセスでない通常のアクセスを行っているため、セレクタR2は、バス205からの信号READYをそのままCPU201に出力する。

ポーリングアクセス信号が1であり、期待値判定信号が1の場合、CPU201が期待する値が得られているので、セレクタR2は、バス205からの信号READYをそのままCPU201に出力する。この際、ポーリング回路202がバス205を介して周辺回路PH1のステータスレジスタ305の値を読み出す処理は完了しているので、バス205からの信号READYは1となっている。

ポーリングアクセス信号が1であり、期待値判定信号が0の場合、CPU201が期待する値が得られておらず、CPU201には読み出しアクセスが継続しているように見せるため、セレクタR2は、「0」の信号READYをCPU201に出力する。

次に、ポーリング中断信号が1になる条件と、そのときのポーリング回路202の動作を説明する。CPU201がポーリング処理をしているとき、もしポーリング対象のステータスレジスタ305の値が長時間にわたってCPUが期待する値に変化しなかった場合、ポーリング回路202からCPU201へ出力する信号READYは長時間にわたって0のままになる。CPU201から見ると、読み出しアクセスが長時間保留になっているように見える。CPU201がバスアクセスの途中に「1」の割り込み信号IRが入力されたときは、バスアクセスの完了を待ってから割り込み処理に移行する設計であった場合、ポーリング回路202が期待値一致を確認するまで、CPU201にとっては、信号READYが0であり、バスアクセスが完了していないように見える。そのため、CPU201は、割り込み処理に移行するまでに長い間待たされることになる。そこで、CPU201に「1」の割り込み信号IRが入力された場合は、CPU201は、すみやかに現在実行しているプログラムを中断し、割り込み処理プログラムに移行する。

本実施形態では、割り込み処理に移行するまでに長時間の待ち時間が生ずる事態を防ぐために、ポーリング中断判定部1204は、CPU201へ入力される割り込み信号IRを入力し、CPU201に対して割り込みが発生した場合は、ポーリング処理を中断するために「1」のポーリング中断信号を出力する。セレクタR2は、CPU201から見たバスアクセスを完了させるために、バス205からの信号READYをそのままCPU201へ出力する。

このとき、CPU201へ出力される信号RDATAは、ポーリング回路202がもっとも最近読み出したステータスレジスタ305の指定されたビットの値とするため、セレクタR1が出力するビット信号を保持するビット信号保持部1401(図14)を設ける。

以上のように、READY信号生成部1002は、CPU201から入力したアドレス信号ADDRが期待値0及び期待値1のレジスタ領域(第1のアドレス範囲)801b及び801cのアドレスであり、バス205を介して周辺回路PH1から入力したリードデータ信号RDATAがCPU201から入力したアドレス信号ADDRに対応する期待値と同じである場合には、バス205を介して周辺回路PH1から入力したレディ信号READYと同じレディ信号READYをCPU201に出力し、その他の場合には「0」のレディ信号READYをCPU201に出力する。

具体的には、READY信号生成部1002は、CPU201から入力したアドレス信号ADDRが期待値0のレジスタ領域(第3のアドレス範囲)801bのアドレスであり、周辺回路PH1から入力したリードデータ信号RDATAのうちのCPU201から入力したアドレス信号ADDRに対応するビットの値が0である場合には、周辺回路PH1から入力したレディ信号READYと同じレディ信号READYをCPU201に出力する。また、READY信号生成部1002は、CPU201から入力したアドレス信号ADDRが期待値1のレジスタ領域(第4のアドレス範囲)801cのアドレスであり、周辺回路PH1から入力したリードデータ信号RDATAのうちのCPU201から入力したアドレス信号ADDRに対応するビットの値が1である場合には、周辺回路PH1から入力したレディ信号READYと同じレディ信号READYをCPU201に出力する。

また、READY信号生成部1002は、CPU201に入力される割り込み信号IRが「1」(活性化状態)になった場合には、バス205を介して周辺回路PH1から入力したレディ信号READYと同じレディ信号READYをCPU201に出力する。

図14は、図10のRDATA信号生成部1003の構成例を示す図である。RDATA信号生成部1003は、ポーリング回路202からCPU201へ出力する信号RDATAを生成する。RDATA信号生成部1003は、ビット信号保持部1401及びセレクタ1402を有する。ビット信号保持部1401は、図9のレジスタ領域801b及び801cのように、図12のREADY信号生成部1002からのビット信号を最下位ビットとして入力し、上位31ビット分を0で埋め、32ビット信号を生成し、セレクタ1402に出力する。セレクタ1402は、ポーリングアクセス信号が「1」の場合、ビット信号保持部1401が出力する32ビット信号を、信号RDATAとしてCPU201に出力する。また、ポーリングアクセス信号が0の場合、CPU201はポーリング処理のためではないバスアクセスを行っていることになるので、セレクタ1402は、バス205からの信号RDATAをそのままCPU201へ出力する。

以上のように、RDATA信号生成部1003は、CPU201から入力したアドレス信号ADDRが期待値0及び期待値1のレジスタ領域(第1のアドレス範囲)801b及び801cのアドレスである場合には、バス205を介して周辺回路PH1から入力したリードデータ信号RDATAのうちのCPU201から入力したアドレス信号ADDRに対応するビットの信号をリードデータ信号RDATAとしてCPU201に出力する。ビット信号保持部1401は、バス205を介して周辺回路PH1から入力したリードデータ信号RDATAのうちのCPU201から入力したアドレス信号ADDRに対応するビットの信号を保持する。

具体的には、RDATA信号生成部1003は、バス205を介して周辺回路PH1から入力したリードデータ信号RDATAのうちのCPU201から入力したアドレス信号ADDRに対応するビットの信号を下位ビットとし、上位ビットを0で埋めた信号をリードデータ信号RDATAとしてCPU201に出力する。

図15は、図10のREQ信号生成部1004の構成例を示す図である。REQ信号生成部1004は、ポーリング回路202からバス205へ出力する信号REQを生成する。REQ信号生成部1004は、セレクタ1501及び1502を有する。ポーリングアクセス信号が0の場合、CPU201はポーリング処理のためのアクセスではない通常のアクセスを行っているので、セレクタ1501は、CPU201からの信号REQをそのままバス205への信号REQとして出力する。ポーリングアクセス信号が1の場合、セレクタ1501は、以下の動作により、バス205への信号REQを生成する。

セレクタ1501は、ポーリングアクセス信号が1の場合、周辺回路PH1のステータスレジスタ305の1回目のアクセスのために、「1」の信号REQをバス205に出力する。

読み出した周辺回路PH1のステータスレジスタ305の値が期待値と一致せず、2回目以降のステータスレジスタ305の読み出しアクセスを行うための信号REQの出力は、セレクタ1502がアクセスタイミング信号を出力したときに行う。セレクタ1502は、図11のアドレス保持部1103が出力する通常レジスタアドレスを基に、周辺回路PH1〜PH4が出力するイネーブル信号ENS1〜ENS4のうちのいずれかを選択し、アクセスタイミング信号としてセレクタ1501に出力する。例えば、周辺回路PH1〜PH4の通常レジスタ領域のアドレスが図8の構成の時、通常レジスタアドレスが0x40000000〜0x40000FFCの範囲の場合、セレクタ1502は、周辺回路PH1のイネーブル信号ENS1を選択し、アクセスタイミング信号として出力する。

図16は、各周辺回路PH1〜PH4内のイネーブル信号生成部の構成例を示す図である。32個のD型フリップフロップFF1〜FF32は、図3のステータスレジスタ305に対応し、32ビット値を記憶する。論理和回路306は、図3の論理和回路306に対応する。イネーブル信号生成部は、イネーブル信号ENSを生成する。第1の周辺回路PH1内のイネーブル信号生成部が出力するイネーブル信号ENSは、図15の第1の周辺回路PH1が出力するイネーブル信号ENS1に対応する。第2の周辺回路PH2内のイネーブル信号生成部が出力するイネーブル信号ENSは、図15の第2の周辺回路PH2が出力するイネーブル信号ENS2に対応する。第3の周辺回路PH3内のイネーブル信号生成部が出力するイネーブル信号ENSは、図15の第3の周辺回路PH3が出力するイネーブル信号ENS3に対応する。第4の周辺回路PH4内のイネーブル信号生成部が出力するイネーブル信号ENSは、図15の第4の周辺回路PH4が出力するイネーブル信号ENS4に対応する。

ステータスレジスタ305は、イネーブル端子EN付きのD型フリップフロップFF1〜FF32を有する。イネーブル端子EN付きのD型フリップフロップFF1〜FF32は、それぞれ、1ビットの記憶素子であり、イネーブル端子ENの信号が1の時に入力端子Dの値を内部に取り込み、保持し、保持した値を出力端子Qから出力する。したがって、各D型フリップフロップFF1〜FF32のイネーブル端子ENに入力される信号が1のとき、各D型フリップフロップFF1〜FF32の値が書き換わる可能性がある。なお、イネーブル端子ENに1が入力されても、入力端子Dへ入力される値がもともと各D型フリップフロップFF1〜FF32が保持している値と同じ場合は、結果的に、各D型フリップフロップFF1〜FF32の値は書き換わらず、出力端子Qから同じ値が出力され続ける。論理和回路306は、D型フリップフロップ(ステータスレジスタ)FF1〜FF32のイネーブル端子ENの信号の論理和をイネーブル信号ENSとして出力する。イネーブル信号ENSは、図15のイネーブル信号ENS1〜ENS4に対応する。

図15において、セレクタ1502は、通常レジスタアドレスに応じて、イネーブル信号ENS1〜ENS4のいずれかを選択し、アクセスタイミング信号としてセレクタ1501に出力する。セレクタ1501は、ポーリングアクセス信号が1であり、アクセスタイミング信号が1の場合、ポーリング対象の周辺回路PH1〜PH4のステータスレジスタ305の値が変化した可能性があると判断し、2回目以降の読み出しアクセスのための「1」の信号REQをバス205へ出力する。また、セレクタ1501は、ポーリングアクセス信号が1であり、アクセスタイミング信号が0の場合、ポーリング対象の周辺回路PH1〜PH4のステータスレジスタ305の値が変化した可能性がないと判断し、「0」の信号REQをバス205へ出力する。ステータスレジスタ305の値が変化した可能性がないときは、バス205へ「0」の信号REQを出力するので、無駄にステータスレジスタ305の読み出しアクセスを行うことを防ぐことができる。これにより、ポーリング回路202及びバス205の無駄な電力消費を抑え、DMAC206などの他にバス205を使用するモジュールとのバスアクセス競合を防ぐことができる。

以上のように、周辺回路PH1〜PH4は、それぞれ、CPU201のリクエスト信号REQに応じて、イネーブル端子ENを有するステータスレジスタ305からリードデータを読み出す。REQ信号生成部1004は、例えば、周辺回路PH1のステータスレジスタ305のイネーブル端子ENの信号が1になった場合に、周辺回路PH1に「1」のリクエスト信号REQを出力する。なお、イネーブル端子ENの信号は、「1」が活性化状態を示し、「0」が非活性化状態を示す。

具体的には、ステータスレジスタ305は、イネーブル端子ENを有する複数のフリップフロップFF1〜FF32を有する。REQ信号生成部1004は、複数のフリップフロップFF1〜FF32のイネーブル端子ENの信号のうちのいずれかの信号が1になった場合に、周辺回路PH1に「1」のリクエスト信号REQを出力する。

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。