JP6209892B2 - 競合テスト用タイミング調整プログラム、競合テスト用タイミング調整方法および競合テスト用タイミング調整装置 - Google Patents

競合テスト用タイミング調整プログラム、競合テスト用タイミング調整方法および競合テスト用タイミング調整装置 Download PDFInfo

- Publication number

- JP6209892B2 JP6209892B2 JP2013157057A JP2013157057A JP6209892B2 JP 6209892 B2 JP6209892 B2 JP 6209892B2 JP 2013157057 A JP2013157057 A JP 2013157057A JP 2013157057 A JP2013157057 A JP 2013157057A JP 6209892 B2 JP6209892 B2 JP 6209892B2

- Authority

- JP

- Japan

- Prior art keywords

- transaction

- event

- events

- pair

- timing adjustment

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Test And Diagnosis Of Digital Computers (AREA)

Description

以下に添付図面を参照して、開示技術の好適な実施の形態を詳細に説明する。図1は、実施の形態にかかる競合テスト用タイミング調整装置の機能を示すブロック図である。競合テスト用タイミング調整装置100は、イベントテーブル生成部101と、イベントテーブル102と、競合シナリオ生成部103と、を含む。

図2は、イベントテーブルに格納されるイベントテーブル情報を示す図表である。イベントテーブル生成部101は、入力トランザクションの集合の情報110の複数のトランザクション(Tri)をシミュレータによりシミュレーション実行する。このシミュレーション実行時に、イベントテーブル生成部101は、内部イベントのリスト情報111に登録されたイベント(Evj)が発生する時刻(Tk)を一覧化したイベントテーブル情報112をイベントテーブル102に格納する。イベントテーブル情報112は、縦軸が各トランザクションTri、横軸には各イベントEvjを時刻Tk毎に(右方向ほど時刻経過)格納する。

競合シナリオ生成部103は、以下の(1)、(2)の処理を行う。

(1)競合イベントが同時に発生するための時刻調整と、トランザクションの組の優先度の付与。この処理では、イベントテーブル情報112に基づいて、競合点において競合させたいイベントが発生するトランザクションの組を全て生成する。そして、競合させたいイベントが同時に発生するように、トランザクションの開始時刻を決定する。また、他のイベントの競合可能性により、生成したトランザクションの組に優先度を付与する。

図4は、競合シナリオ生成にかかるトランザクション選択例を説明するための図表である。図2と同様のイベントテーブル情報112の例を用い、競合シナリオ生成部103が行う処理例について説明する。ここで、競合点(アービタ等)において競合させたいイベントの組がEv4とEv5であるとする。

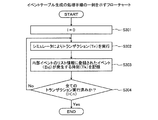

図6は、競合シナリオ生成処理の一例を示すフローチャートである。競合シナリオ生成部103が行う処理内容について説明する。図6は、図5に示した処理の実行後に競合シナリオ生成部103が実行し、選択した1組のトランザクション毎の競合シミュレーションをシミュレータに実行させる。そして、競合が起こるトランザクションの組み合わせを競合シナリオとして生成する。

図7は、競合テスト用タイミング調整装置のハードウェア構成の一例を示すブロック図である。図7において、競合テスト用タイミング調整装置700は、CPU701と、Read−Only Memory(ROM)702と、Random Access Memory(RAM)703と、を含む。また、半導体メモリやディスクドライブ等の記憶部704と、ディスプレイ708と、通信インターフェース(I/F)709と、キーボード710と、マウス711と、スキャナ712と、プリンタ713とを備えてもよい。これらCPU701〜プリンタ713はバス714によってそれぞれ接続されている。

図8は、競合テスト用タイミング調整装置の配置例を示す図である。フォーマル検証ツール801と、シミュレータ802との間のインターフェースとして競合テスト用タイミング調整装置100(競合シナリオ生成部103)が配置される。

図9は、競合点でのタイミング競合の一例を示す図である。コア901には、複数のデータパスが配置され、データパス1(902a)上の複数のブロック(FF1〜FFn)と、データパス2(902b)上の複数のブロック(FF1〜FFm)が配置されている。これらデータパス1,2の入力側からみた奥部のブロックとしてアービタ903が配置されているとする。そして、このアービタ903におけるデータ入力の競合時の動作を検証する場合には、アービタ903の直前のFFnとFFmからのリクエスト(Req)を同時に発生させる必要がある。

コンピュータに、

競合させたい一対のイベントの指定により、前記半導体装置の入力のトランザクションと前記イベントとに基づき、前記一対のイベントに関連する複数の前記トランザクションを1組毎に選択させ、

選択した1組の前記トランザクションに含まれる前記一対のイベントの時刻が一致するように、一方のトランザクションの入力タイミングを調整させ、

入力タイミングが調整された一方のトランザクションに含まれる他のイベントの時刻が、他方のトランザクションに含まれる同一のイベントの時刻と不一致となるかを判断させ、

判断結果として不一致が得られた1組のトランザクションと、調整した前記入力タイミングと、を競合させたい一対のイベントに対するタイミング調整結果として出力させる、

処理を実行させることを特徴とする競合テスト用タイミング調整プログラム。

競合させたい一対のイベントの入力に基づき、前記イベントテーブルを参照して、前記一対のイベントに関連する複数の前記トランザクションを1組毎に選択させることを特徴とする付記1に記載の競合テスト用タイミング調整プログラム。

前記シミュレータのシミュレーション結果に基づき、前記一対のイベントにおける競合条件が満たされた場合に、一対のイベントに対するタイミング調整に関する情報を競合シナリオとして出力させる、

ことを特徴とする付記1〜5のいずれか一つに記載の競合テスト用タイミング調整プログラム。

コンピュータが、

競合させたい一対のイベントの指定により、前記半導体装置の入力のトランザクションと前記イベントとに基づき、前記一対のイベントに関連する複数の前記トランザクションを1組毎に選択し、

選択した1組の前記トランザクションに含まれる前記一対のイベントの時刻が一致するように、一方のトランザクションの入力タイミングを調整し、

入力タイミングが調整された一方のトランザクションに含まれる他のイベントの時刻が、他方のトランザクションに含まれる同一のイベントの時刻と不一致となるかを判断し、

判断結果として不一致が得られた1組のトランザクションと、調整した前記入力タイミングと、を競合させたい一対のイベントに対するタイミング調整結果として出力する、

処理を実行することを特徴とする競合テスト用タイミング調整方法。

前記半導体装置の入力のトランザクションと、前記イベントとを関連付けたイベントテーブルと、

競合させたい一対のイベントの入力に基づき、前記イベントテーブルを参照して、前記一対のイベントに関連する複数の前記トランザクションを1組毎に選択し、

選択した1組の前記トランザクションに含まれる前記一対のイベントの時刻が一致するように、一方のトランザクションの入力タイミングを調整し、

入力タイミングが調整された一方のトランザクションに含まれる他のイベントの時刻が、他方のトランザクションに含まれる同一のイベントの時刻と不一致となるかを判断し、

判断結果として不一致が得られた1組のトランザクションと、調整した前記入力タイミングと、を競合させたい一対のイベントに対するタイミング調整結果として出力する競合シナリオ生成部と、

を有することを特徴とする競合テスト用タイミング調整装置。

をさらに有することを特徴とする付記10に記載の競合テスト用タイミング調整装置。

101 イベントテーブル生成部

102 イベントテーブル

103 競合シナリオ生成部

901 コア

903 アービタ

910 テストベンチ

Claims (10)

- 半導体装置の内部信号を任意のイベントで競合させる競合タイミングを調整する競合テスト用タイミング調整プログラムにおいて、

コンピュータに、

競合させたい一対のイベントの指定により、前記半導体装置の入力のトランザクションと前記イベントとに基づき、前記一対のイベントに関連する複数の前記トランザクションを1組毎に選択させ、

選択した1組の前記トランザクションに含まれる前記一対のイベントの時刻が一致するように、一方のトランザクションの入力タイミングを調整させ、

入力タイミングが調整された一方のトランザクションに含まれる他のイベントの時刻が、他方のトランザクションに含まれる同一のイベントの時刻と不一致となるかを判断させ

、

判断結果として不一致が得られた1組のトランザクションと、調整した前記入力タイミングと、を競合させたい一対のイベントに対するタイミング調整結果として出力させる、

処理を実行させることを特徴とする競合テスト用タイミング調整プログラム。 - 前記半導体装置の入力のトランザクションと、前記イベントとを関連付けたイベントテーブルを生成させ、

競合させたい一対のイベントの入力に基づき、前記イベントテーブルを参照して、前記一対のイベントに関連する複数の前記トランザクションを1組毎に選択させることを特徴とする請求項1に記載の競合テスト用タイミング調整プログラム。 - 前記判断結果として一致が生じた前記一方のトランザクションには低い優先度を付与することを特徴とする請求項1または2に記載の競合テスト用タイミング調整プログラム。

- 前記判断結果として一致が生じた後、前記一対のイベントに関連する前記トランザクションの組が残っていない場合には、一対のイベントに対するタイミング調整が不可であると判断することを特徴とする請求項1〜3のいずれか一つに記載の競合テスト用タイミング調整プログラム。

- 前記トランザクションをシミュレータに実行させ、前記イベントが生じた時刻を前記イベントテーブルに記録させることを特徴とする請求項2に記載の競合テスト用タイミング調整プログラム。

- 前記タイミング調整結果により得られた複数組のトランザクションをシミュレータに出力させ、

前記シミュレータのシミュレーション結果に基づき、前記一対のイベントにおける競合条件が満たされた場合に、一対のイベントに対するタイミング調整に関する情報を競合シナリオとして出力させる、

ことを特徴とする請求項1〜5のいずれか一つに記載の競合テスト用タイミング調整プログラム。 - 前記判断結果として一致が生じた前記一方のトランザクションは、前記イベントテーブルの優先度が低い格納位置に変更させることを特徴とする請求項2または5に記載の競合テスト用タイミング調整プログラム。

- 選択した1組の前記トランザクションに含まれる前記一対のイベントの時刻のうち、時刻が最大値のイベントの時刻が一致するように、一方のトランザクションの入力タイミングを調整させることを特徴とする請求項1〜7のいずれか一つに記載の競合テスト用タイミング調整プログラム。

- 半導体装置の内部信号を任意のイベントで競合させる競合タイミングを調整する競合テスト用タイミング調整方法において、

コンピュータが、

競合させたい一対のイベントの指定により、前記半導体装置の入力のトランザクションと前記イベントとに基づき、前記一対のイベントに関連する複数の前記トランザクションを1組毎に選択し、

選択した1組の前記トランザクションに含まれる前記一対のイベントの時刻が一致するように、一方のトランザクションの入力タイミングを調整し、

入力タイミングが調整された一方のトランザクションに含まれる他のイベントの時刻が、他方のトランザクションに含まれる同一のイベントの時刻と不一致となるかを判断し、

判断結果として不一致が得られた1組のトランザクションと、調整した前記入力タイミングと、を競合させたい一対のイベントに対するタイミング調整結果として出力する、

処理を実行することを特徴とする競合テスト用タイミング調整方法。 - 半導体装置の内部信号を任意のイベントで競合させる競合タイミングを調整する競合テスト用タイミング調整装置において、

前記半導体装置の入力のトランザクションと、前記イベントとを関連付けたイベントテーブルと、

競合させたい一対のイベントの入力に基づき、前記イベントテーブルを参照して、前記一対のイベントに関連する複数の前記トランザクションを1組毎に選択し、

選択した1組の前記トランザクションに含まれる前記一対のイベントの時刻が一致するように、一方のトランザクションの入力タイミングを調整し、

入力タイミングが調整された一方のトランザクションに含まれる他のイベントの時刻が、他方のトランザクションに含まれる同一のイベントの時刻と不一致となるかを判断し、

判断結果として不一致が得られた1組のトランザクションと、調整した前記入力タイミングと、を競合させたい一対のイベントに対するタイミング調整結果として出力する競合シナリオ生成部と、

を有することを特徴とする競合テスト用タイミング調整装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013157057A JP6209892B2 (ja) | 2013-07-29 | 2013-07-29 | 競合テスト用タイミング調整プログラム、競合テスト用タイミング調整方法および競合テスト用タイミング調整装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013157057A JP6209892B2 (ja) | 2013-07-29 | 2013-07-29 | 競合テスト用タイミング調整プログラム、競合テスト用タイミング調整方法および競合テスト用タイミング調整装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015026337A JP2015026337A (ja) | 2015-02-05 |

| JP6209892B2 true JP6209892B2 (ja) | 2017-10-11 |

Family

ID=52490915

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013157057A Expired - Fee Related JP6209892B2 (ja) | 2013-07-29 | 2013-07-29 | 競合テスト用タイミング調整プログラム、競合テスト用タイミング調整方法および競合テスト用タイミング調整装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6209892B2 (ja) |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2908339B2 (ja) * | 1996-08-29 | 1999-06-21 | 日本電気アイシーマイコンシステム株式会社 | 半導体集積回路のシミュレーション方式 |

| JP2001222442A (ja) * | 2000-02-08 | 2001-08-17 | Fujitsu Ltd | パイプライン試験方法、パイプライン試験命令生成方法及びその記憶媒体 |

| US6772370B1 (en) * | 2000-11-03 | 2004-08-03 | Freescale Semiconductor, Inc. | Method and apparatus for generation of pipeline hazard test sequences |

| JP5308098B2 (ja) * | 2008-08-13 | 2013-10-09 | 株式会社日立情報通信エンジニアリング | 情報処理装置試験プログラム及び方法 |

| JP2010244300A (ja) * | 2009-04-06 | 2010-10-28 | Mitsubishi Electric Corp | テストパターン作成手法、シミュレーション方法、情報処理装置およびシミュレーション装置 |

-

2013

- 2013-07-29 JP JP2013157057A patent/JP6209892B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015026337A (ja) | 2015-02-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102412480B1 (ko) | 초기 스테이지 ic 레이아웃 설계용 drc 프로세싱 툴 | |

| US10521536B2 (en) | RTL verification using computational complexity-based property ranking and scheduling | |

| US9129081B2 (en) | Synchronized three-dimensional display of connected documents | |

| JP6693903B2 (ja) | ハードウェア試験装置及びハードウェア試験方法 | |

| CN101877016A (zh) | 对临界尺寸(cd)扫描电镜的cd提取进行建模 | |

| US10969764B2 (en) | Support device, design support method and computer-readable non-transitory medium | |

| JP2006244073A (ja) | 半導体設計装置 | |

| JP5983362B2 (ja) | 試験方法、試験プログラム、および、試験制御装置 | |

| US10083272B2 (en) | Integrated circuit design layout optimizer based on process variation and failure mechanism | |

| US10885258B1 (en) | Fixing ESD path resistance errors in circuit design layout | |

| JP2015166981A (ja) | レイアウト検証方法、検証装置、及び検証プログラム | |

| JP2009230392A (ja) | シミュレーション装置、シミュレーション方法及びプログラム | |

| US9817930B1 (en) | Method, system, and computer program product for verifying an electronic circuit design with a graph-based proof flow | |

| US9672317B2 (en) | Quality of results system | |

| JP6209892B2 (ja) | 競合テスト用タイミング調整プログラム、競合テスト用タイミング調整方法および競合テスト用タイミング調整装置 | |

| US8321825B2 (en) | Method and system for synthesizing relative timing constraints on an integrated circuit design to facilitate timing verification | |

| US9218273B2 (en) | Automatic generation of a resource reconfiguring test | |

| JP2009181292A (ja) | Mc/dcパターン生成装置 | |

| US9230053B2 (en) | Rule generating apparatus and method using lithography simulation | |

| JP2018081354A (ja) | シミュレーション支援装置、シミュレーション支援方法、およびシミュレーション支援プログラム | |

| JP2017120514A (ja) | 半導体設計支援装置、半導体設計支援方法、及び半導体設計支援プログラム | |

| JP5640790B2 (ja) | 検証支援プログラム、検証支援装置、および検証支援方法 | |

| JP5310397B2 (ja) | 動作合成検証補助装置、動作合成検証補助方法、プログラム、及び記録媒体 | |

| JP5278271B2 (ja) | 設計支援プログラム、設計支援装置および設計支援方法 | |

| US11080448B1 (en) | Method and system for formal bug hunting |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160405 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170131 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170207 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170410 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170815 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170828 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6209892 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |