JP6203935B2 - 加算比較選択命令 - Google Patents

加算比較選択命令 Download PDFInfo

- Publication number

- JP6203935B2 JP6203935B2 JP2016501437A JP2016501437A JP6203935B2 JP 6203935 B2 JP6203935 B2 JP 6203935B2 JP 2016501437 A JP2016501437 A JP 2016501437A JP 2016501437 A JP2016501437 A JP 2016501437A JP 6203935 B2 JP6203935 B2 JP 6203935B2

- Authority

- JP

- Japan

- Prior art keywords

- result

- register

- value

- instruction

- vector

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30007—Arrangements for executing specific machine instructions to perform operations on data operands

- G06F9/3001—Arithmetic instructions

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30007—Arrangements for executing specific machine instructions to perform operations on data operands

- G06F9/30021—Compare instructions, e.g. Greater-Than, Equal-To, MINMAX

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30007—Arrangements for executing specific machine instructions to perform operations on data operands

- G06F9/30036—Instructions to perform operations on packed data, e.g. vector, tile or matrix operations

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/30003—Arrangements for executing specific machine instructions

- G06F9/30007—Arrangements for executing specific machine instructions to perform operations on data operands

- G06F9/30036—Instructions to perform operations on packed data, e.g. vector, tile or matrix operations

- G06F9/30038—Instructions to perform operations on packed data, e.g. vector, tile or matrix operations using a mask

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3885—Concurrent instruction execution, e.g. pipeline or look ahead using a plurality of independent parallel functional units

- G06F9/3893—Concurrent instruction execution, e.g. pipeline or look ahead using a plurality of independent parallel functional units controlled in tandem, e.g. multiplier-accumulator

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/37—Decoding methods or techniques, not specific to the particular type of coding provided for in groups H03M13/03 - H03M13/35

- H03M13/39—Sequence estimation, i.e. using statistical methods for the reconstruction of the original codes

- H03M13/41—Sequence estimation, i.e. using statistical methods for the reconstruction of the original codes using the Viterbi algorithm or Viterbi processors

- H03M13/4107—Sequence estimation, i.e. using statistical methods for the reconstruction of the original codes using the Viterbi algorithm or Viterbi processors implementing add, compare, select [ACS] operations

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- Software Systems (AREA)

- General Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- Probability & Statistics with Applications (AREA)

- Mathematical Physics (AREA)

- Mathematical Analysis (AREA)

- Mathematical Optimization (AREA)

- Pure & Applied Mathematics (AREA)

- Computational Mathematics (AREA)

- Error Detection And Correction (AREA)

- Executing Machine-Instructions (AREA)

- Complex Calculations (AREA)

- Advance Control (AREA)

Description

本出願は、参照によりその全体が本明細書に明白に組み込まれている、本出願の譲受人が所有する2013年3月15日に出願した米国仮出願第13/841,878号の優先権を主張するものである。

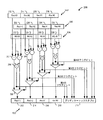

102 第1のレジスタ

104 第2のレジスタ

106 第3のレジスタ

110 プリディケートレジスタ

112 第1の値

114 第2の値

116 第3の値

122 第1の結果

124 第2の結果

126 選択結果

210 プリディケートレジスタ

302 メモリ

308 バスインターフェース

310 命令キャッシュ

311 バス

312 データキャッシュ

314 シーケンサ

316 汎用割り込み

318 命令実行ユニット

320 命令実行ユニット

322 命令実行ユニット

324 命令実行ユニット

326 汎用レジスタファイル

330 バス

332 スーパバイザ制御レジスタ

334 グローバル制御レジスタ

350 超長命令語(VLIW)パケット

352 第2の命令

528 ディスプレイ

530 入力デバイス

526 ディスプレイコントローラ

532 メモリ

536 スピーカ

538 マイク

540 ワイヤレスコントローラ

544 電源

Claims (25)

- 第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令を記憶するメモリを備える装置であって、プロセッサによって前記命令が実行されると、

前記プロセッサによって、前記第1のレジスタからの第1の値を、前記第2のレジスタからの第2の値に加算するようにベクトル加算演算が行われ、

前記第3のレジスタからの第3の値から、前記第2の値を減算するようにベクトル減算演算が行われ、

前記ベクトル加算演算の結果を、前記ベクトル減算演算の結果と比較するようにベクトル比較演算が行われる、

装置。 - 前記プロセッサによって前記命令が実行されると、ベクトル選択演算が行われて、

前記ベクトル比較演算に基づいて、前記ベクトル加算演算の前記結果、または前記ベクトル減算演算の前記結果を選択し、

前記選択結果を用いて前記第1のレジスタを更新する、

請求項1に記載の装置。 - 前記ベクトル加算演算の前記結果が、前記ベクトル減算演算の前記結果より大きいときは、前記ベクトル加算演算の前記結果が選択され、前記ベクトル減算演算の前記結果が、前記ベクトル加算演算の前記結果より大きいときは、前記ベクトル減算演算の前記結果が選択される、請求項2に記載の装置。

- 前記選択結果が前記ベクトル加算演算の前記結果であるときは、デコーダは偶数状態に対応する先行状態への遷移を決定し、前記選択結果が前記ベクトル減算演算の前記結果であるときは、前記デコーダは奇数状態に対応する先行状態への遷移を決定する、請求項3に記載の装置。

- 前記ベクトル加算演算、前記ベクトル減算演算、前記ベクトル比較演算、および前記ベクトル選択演算が、同じ実行サイクルの間に行われる、請求項2に記載の装置。

- 前記命令が記憶位置をさらに特定し、前記ベクトル比較演算の結果は前記記憶位置に記憶される、請求項1に記載の装置。

- 前記記憶位置が前記第1のレジスタに対応する、請求項6に記載の装置。

- 前記第1の値がデコーダのパスメトリック値の第1の組であり、前記第2の値がブランチメトリック値であり、前記第3の値がパスメトリック値の第2の組である、請求項1に記載の装置。

- 前記デコーダがビタビデコーダである、請求項8に記載の装置。

- 前記命令および第2の命令を含む超長命令語(VLIW)パケットが前記メモリからの取り出しのために使用される、請求項1に記載の装置。

- 命令を実行する方法であって、前記方法が

第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する前記命令を受け取るステップと、

プロセッサによって前記命令を実行するステップであって、

前記第1のレジスタからの第1の値を、前記第2のレジスタからの第2の値に加算して、第1の結果を生成するステップと、

前記第3のレジスタからの第3の値から、第2の値を減算して、第2の結果を生成するステップと、

前記第1の結果を前記第2の結果と比較するステップと

を含む、前記命令を実行するステップと

を含む命令を実行する方法。 - 前記命令を実行するステップが、

前記第1の結果を前記第2の結果と比較するステップに基づいて、前記第1の結果または前記第2の結果を選択するステップと、

前記選択結果を用いて前記第1のレジスタを更新するステップと

をさらに含む、請求項11に記載の命令を実行する方法。 - 前記第1の結果が前記第2の結果より大きいときは、前記第1の結果が選択され、前記第2の結果が前記第1の結果より大きいときは、前記第2の結果が選択される、請求項12に記載の命令を実行する方法。

- 前記第1の値を前記第2の値に加算するステップ、前記第3の値から前記第2の値を減算するステップ、前記第1の結果を前記第2の結果と比較するステップ、および前記第1の結果または前記第2の結果を選択するステップが、同じ実行サイクルの間に行われる、請求項13に記載の命令を実行する方法。

- 前記命令が記憶位置をさらに特定し、前記命令を実行するステップが、前記第1の結果を前記第2の結果と比較するステップの結果を前記記憶位置に記憶するステップをさらに含む、請求項11に記載の命令を実行する方法。

- 前記第1の値がデコーダのパスメトリック値の第1の組であり、前記第2の値がブランチメトリック値であり、前記第3の値がパスメトリック値の第2の組である、請求項11に記載の命令を実行する方法。

- 前記デコーダがビタビデコーダである、請求項16に記載の命令を実行する方法。

- 前記命令および第2の命令を含む、超長命令語(VLIW)パケットを受け取るステップをさらに含む、請求項11に記載の命令を実行する方法。

- 第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する命令を記憶するための手段と、

前記命令を実行するための手段であって、

前記第1のレジスタからの第1の値を、前記第2のレジスタからの第2の値に加算して、第1の結果を生成するための手段と、

前記第3のレジスタからの第3の値から、第2の値を減算して、第2の結果を生成するための手段と、

前記第1の結果を、前記第2の結果と比較するための手段と

を備える、前記命令を実行するための手段と

を備える装置。 - 前記加算するための手段がベクトル加算器を含み、前記減算するための手段がベクトル減算器を含み、前記比較するための手段が比較器を含む、請求項19に記載の装置。

- 前記命令を実行するための手段が、同じ実行サイクルの間に、前記第1の値を前記第2の値に加算し、前記第3の値から前記第2の値を減算し、前記第1の結果を前記第2の結果と比較するように構成される、請求項19に記載の装置。

- プロセッサによって実行されたときに、前記プロセッサに、

第1のレジスタ、第2のレジスタ、および第3のレジスタを特定する単一命令を受け取らせ、

前記単一命令を実行させる、

プログラムコードを含む、コンピュータ可読記憶媒体であって、

前記単一命令を実行することは、

前記第1のレジスタからの第1の値を、前記第2のレジスタからの第2の値に加算して、第1の結果を生成し、

前記第3のレジスタからの第3の値から、第2の値を減算して、第2の結果を生成し、

前記第1の結果を前記第2の結果と比較すること

を含む、コンピュータ可読記憶媒体。 - 前記単一命令を実行することが、

前記第1の結果を前記第2の結果と比較することに基づいて、前記第1の結果または前記第2の結果の1つを選択すること、および

前記選択結果を用いて前記第1のレジスタを更新すること

をさらに含む、請求項22に記載のコンピュータ可読記憶媒体。 - 前記第1の値を前記第2の値に加算すること、前記第3の値から前記第2の値を減算すること、前記第1の結果を前記第2の結果と比較すること、および前記第1のレジスタを更新することが、同じ実行サイクルの間に行われる、請求項23に記載のコンピュータ可読記憶媒体。

- 前記単一命令を実行することが、前記第1の結果を前記第2の結果と比較することの結果を記憶位置に記憶することをさらに含む、請求項22に記載のコンピュータ可読記憶媒体。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/841,878 | 2013-03-15 | ||

| US13/841,878 US9389854B2 (en) | 2013-03-15 | 2013-03-15 | Add-compare-select instruction |

| PCT/US2014/024203 WO2014150778A1 (en) | 2013-03-15 | 2014-03-12 | Add-compare-select instruction |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2016517577A JP2016517577A (ja) | 2016-06-16 |

| JP2016517577A5 JP2016517577A5 (ja) | 2017-01-05 |

| JP6203935B2 true JP6203935B2 (ja) | 2017-09-27 |

Family

ID=50483523

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016501437A Expired - Fee Related JP6203935B2 (ja) | 2013-03-15 | 2014-03-12 | 加算比較選択命令 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US9389854B2 (ja) |

| EP (1) | EP2972786B1 (ja) |

| JP (1) | JP6203935B2 (ja) |

| KR (1) | KR101746681B1 (ja) |

| CN (1) | CN105027076B (ja) |

| WO (1) | WO2014150778A1 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN107315717B (zh) | 2016-04-26 | 2020-11-03 | 中科寒武纪科技股份有限公司 | 一种用于执行向量四则运算的装置和方法 |

| CN107315715B (zh) * | 2016-04-26 | 2020-11-03 | 中科寒武纪科技股份有限公司 | 一种用于执行矩阵加/减运算的装置和方法 |

| CN107315563B (zh) * | 2016-04-26 | 2020-08-07 | 中科寒武纪科技股份有限公司 | 一种用于执行向量比较运算的装置和方法 |

| CN110275693B (zh) * | 2018-03-15 | 2023-08-22 | 华为技术有限公司 | 用于随机计算的多加数加法电路 |

| CN116204612A (zh) * | 2022-10-20 | 2023-06-02 | 超聚变数字技术有限公司 | 一种文本相似度计算方法及系统 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5151904A (en) * | 1990-09-27 | 1992-09-29 | The Titan Corporation | Reconfigurable, multi-user viterbi decoder |

| JPH05206873A (ja) * | 1992-01-29 | 1993-08-13 | Sony Corp | 再生装置 |

| JP3198607B2 (ja) * | 1992-03-31 | 2001-08-13 | ソニー株式会社 | 磁気記録再生方法 |

| JP3241210B2 (ja) | 1994-06-23 | 2001-12-25 | 沖電気工業株式会社 | ビタビ復号方法及びビタビ復号回路 |

| US6163581A (en) * | 1997-05-05 | 2000-12-19 | The Regents Of The University Of California | Low-power state-sequential viterbi decoder for CDMA digital cellular applications |

| US5987490A (en) * | 1997-11-14 | 1999-11-16 | Lucent Technologies Inc. | Mac processor with efficient Viterbi ACS operation and automatic traceback store |

| US20020031195A1 (en) * | 2000-09-08 | 2002-03-14 | Hooman Honary | Method and apparatus for constellation decoder |

| US6848074B2 (en) | 2001-06-21 | 2005-01-25 | Arc International | Method and apparatus for implementing a single cycle operation in a data processing system |

| US7661059B2 (en) * | 2001-08-06 | 2010-02-09 | Analog Devices, Inc. | High performance turbo and Viterbi channel decoding in digital signal processors |

| US7043682B1 (en) | 2002-02-05 | 2006-05-09 | Arc International | Method and apparatus for implementing decode operations in a data processor |

| US8140947B2 (en) | 2005-09-30 | 2012-03-20 | Agere Systems Inc. | Method and apparatus for storing survivor paths in a Viterbi detector using systematic pointer exchange |

| US7725516B2 (en) | 2005-10-05 | 2010-05-25 | Qualcomm Incorporated | Fast DCT algorithm for DSP with VLIW architecture |

| US8356160B2 (en) * | 2008-01-15 | 2013-01-15 | International Business Machines Corporation | Pipelined multiple operand minimum and maximum function |

| US8255780B2 (en) * | 2009-02-18 | 2012-08-28 | Saankhya Labs Pvt Ltd. | Scalable VLIW processor for high-speed viterbi and trellis coded modulation decoding |

| CN102122275A (zh) * | 2010-01-08 | 2011-07-13 | 上海芯豪微电子有限公司 | 一种可配置处理器 |

| JP4856288B1 (ja) * | 2010-08-10 | 2012-01-18 | パイオニア株式会社 | インピーダンス整合装置、制御方法 |

| US8694878B2 (en) | 2011-06-15 | 2014-04-08 | Texas Instruments Incorporated | Processor instructions to accelerate Viterbi decoding |

| US10120692B2 (en) | 2011-07-28 | 2018-11-06 | Qualcomm Incorporated | Methods and apparatus for storage and translation of an entropy encoded instruction sequence to executable form |

-

2013

- 2013-03-15 US US13/841,878 patent/US9389854B2/en active Active

-

2014

- 2014-03-12 CN CN201480012927.5A patent/CN105027076B/zh active Active

- 2014-03-12 EP EP14717293.6A patent/EP2972786B1/en active Active

- 2014-03-12 WO PCT/US2014/024203 patent/WO2014150778A1/en not_active Ceased

- 2014-03-12 KR KR1020157029138A patent/KR101746681B1/ko not_active Expired - Fee Related

- 2014-03-12 JP JP2016501437A patent/JP6203935B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2016517577A (ja) | 2016-06-16 |

| EP2972786B1 (en) | 2021-12-01 |

| CN105027076B (zh) | 2018-07-20 |

| EP2972786A1 (en) | 2016-01-20 |

| KR101746681B1 (ko) | 2017-06-13 |

| KR20150132387A (ko) | 2015-11-25 |

| US9389854B2 (en) | 2016-07-12 |

| CN105027076A (zh) | 2015-11-04 |

| US20140281420A1 (en) | 2014-09-18 |

| WO2014150778A1 (en) | 2014-09-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6203935B2 (ja) | 加算比較選択命令 | |

| KR101697548B1 (ko) | Fifo 로드 명령 | |

| CN103748549B (zh) | 用于经频繁调用函数的表调用指令 | |

| KR101585492B1 (ko) | 비터비 패킹 명령 | |

| JP5341194B2 (ja) | リニアフィードバックシフト命令を実行するためのシステムおよび方法 | |

| CN103874982B (zh) | 确定顶部n个或底部n个数据值 | |

| WO2013036950A1 (en) | Instruction packet including multiple instructions having a common destination | |

| CN109313594B (zh) | 用于指令包的奇偶校验 | |

| CN102822794B (zh) | 处理阶层式极长指令包的系统和方法 | |

| US20170046168A1 (en) | Scalable single-instruction-multiple-data instructions | |

| US20130042091A1 (en) | BIT Splitting Instruction | |

| JP2010079841A (ja) | マイクロコンピュータ及びその命令実行方法 | |

| WO2013069551A1 (ja) | デジタル信号プロセッサ、プログラム制御方法、および制御プログラム | |

| JP2002217747A (ja) | ビタビ復号処理装置 | |

| HK1261188B (en) | Parity for instruction packets | |

| HK1261188A1 (en) | Parity for instruction packets |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A529 | Written submission of copy of amendment under article 34 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A529 Effective date: 20150907 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161116 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20161116 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20161116 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20170118 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170306 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170602 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170807 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170830 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6203935 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |