JP6070848B2 - 情報処理装置,データ転送装置,データ転送方法,および制御装置 - Google Patents

情報処理装置,データ転送装置,データ転送方法,および制御装置 Download PDFInfo

- Publication number

- JP6070848B2 JP6070848B2 JP2015531769A JP2015531769A JP6070848B2 JP 6070848 B2 JP6070848 B2 JP 6070848B2 JP 2015531769 A JP2015531769 A JP 2015531769A JP 2015531769 A JP2015531769 A JP 2015531769A JP 6070848 B2 JP6070848 B2 JP 6070848B2

- Authority

- JP

- Japan

- Prior art keywords

- transfer

- data

- output

- destination

- port

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/76—Architectures of general purpose stored program computers

- G06F15/78—Architectures of general purpose stored program computers comprising a single central processing unit

- G06F15/7807—System on chip, i.e. computer system on a single chip; System in package, i.e. computer system on one or more chips in a single package

- G06F15/7825—Globally asynchronous, locally synchronous, e.g. network on chip

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- General Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Computing Systems (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

- Multi Processors (AREA)

- Bus Control (AREA)

Description

なお、関連する技術として、異なる冗長構成が可能なネットワーク転送装置が知られている(例えば、特許文献1参照)。ネットワーク転送装置は、例えば、パケット送信先に接続されたクロスバスイッチに障害が発生すると、パケット送信元からサブクロスバスイッチへのパケット送信を停止することができる。このネットワーク転送装置は、クロスバスイッチ及びサブクロスバスイッチにパケットが存在しなくなると、サブクロスバスイッチ内の出力バッファとポートとの接続を切り替えて、サブクロスバスイッチを予備系のクロスバスイッチと接続することができる。

データの送信元から送信先への転送経路が複数存在し、データ転送装置から2以上の対向LSIのいずれにデータを転送しても送信先にデータが到達する場合には、データ転送装置は、迂回路として他の出力ポートを介してデータ転送を行なうことも考えられる。

ここまで、装置がプロセッサやメモリ、各種コントローラ等のLSI(集積回路)であるものとして説明したが、上述した課題は、これらLSI(集積回路)間の通信に限られるものではない。上述した課題は、装置が、例えばCPUやメモリ等をそなえるシステムボード等のコンピュータ、I/Oボード、ネットワークインタフェース等であり、データ転送装置がこれらの装置間でデータ転送を行なう装置であっても同様に生じ得る。

なお、前記目的に限らず、後述する発明を実施するための形態に示す各構成により導かれる作用効果であって、従来の技術によっては得られない作用効果を奏することも本発明の他の目的の1つとして位置付けることができる。

〔1〕一実施形態

〔1−1〕情報処理システムの構成例

はじめに、図1及び図2を参照して、一実施形態の一例としての情報処理システム1の構成例を説明する。図1は、一実施形態に係る情報処理システム1の一例を示す図であり、図2は、図1に示す情報処理システム1の構成例を示す図である。

装置3は、データを送信する送信元装置、及び、送信元装置から送信されたデータを受信する送信先装置のうちの少なくとも一方の機能をそなえる。図2に示す例では、装置3D〜3Fは送信元装置の機能をそなえ、装置3A〜3Cは送信先装置の機能をそなえる。

送信先装置としての装置3A〜3Cは、クロスバ部20を介して送信元装置3D〜3Fからフレームを受信し、受信したフレームから送信元装置3D〜3Fが送信したデータを取得することができる。

なお、以下、転送経路には、送信元装置3D〜3Fと送信先装置3A〜3Cとの間の1以上のクロスバ2及び1以上のデータパス(転送路)を介した経路が含まれる。転送路としては、システムバスを含む各種バスや、Local Area Network(LAN),ファイバチャネル(Fibre Channel),インフィニバンド(InfiniBand)等のケーブル、または無線通信路等が挙げられる。また、複数の異なる転送経路には、経由するクロスバ2及びデータパスの少なくとも1つが互いに異なる複数の経路が含まれる。さらに、以下、転送先には、クロスバ2の出力ポートに対向する対向LSI、つまりデータパス(転送路)を介して出力ポートに接続される送信先装置3A〜3C又はクロスバ2を含む対向LSIが含まれる。

〔1−2〕クロスバの対比例

ここで、図3及び図4を参照して、図2に示すクロスバ2の説明のために、クロスバ2の対比例としてのクロスバ200A及び200Bについて説明する。図3及び図4は、それぞれ一実施形態に係るクロスバ2の対比例としてのクロスバ200A及び200Bの構成を示す図である。クロスバ200A及び200Bは、図2に示すクロスバ2に代えて情報処理システム1に適用することができる。以下、3入力3出力のクロスバ200A及び200B(図2に示すクロスバA〜C,G〜Iに対応)を例に挙げて説明する。

なお、図3では、図の簡略化のため、受付ポート500、入力ポート600A、出力ポート800、及び接続部900の構成例をそれぞれ1つ図示するが、他の受付ポート500、入力ポート600A、出力ポート800、及び接続部900についても同様である。

ルーティング部700は、各入力ポート600A内の入力キュー610Aと、各出力ポート800内の各出力キュー810との間を接続し、入力キュー610Aからルーティング部700に入力されたフレームを、対応する出力キュー810へ出力する。

クロスバ200Bは、図4に例示するように、図3に示すクロスバ200Aの入力ポート600Aとは異なる入力ポート600Bをそなえる。

入力ポート600Bは、宛先(転送先)ごとに入力キュー610Bをそなえ、受付ポート500から入力されるフレームを、出力ポート800の情報に基づき転送先ごとに入力キュー610Bに振り分けて格納する。各入力キュー610Bは、入力キュー610Aと同様にFIFOのデータ構造とすることができる。なお、入力ポート600B以外の構成はクロスバ200Aと同様であるため、詳細な説明を省略する。

一方、データ転送において固定故障によるエラーが発生した場合、クロスバ200A及び200Bは、LSI間でデータ転送をリトライしても、固定故障への対処がなされなければ、対向LSIへエラーや損失のないデータを転送することは困難な場合がある。また、データ転送においてビジー又はLSI間の輻輳等による混雑が生じている場合にも同様である。つまり、クロスバ200A及び200Bは、データ転送において混雑が生じている対向LSIに対応する入力キュー610A又は610Bからのデータを、空いている他の対向LSIに対応する出力ポート800に切り替えることは難しい。

図2の説明に戻り、情報処理システム1における転送経路の変更手法の説明を行なう。なお、便宜上、図2に示すように、クロスバ2A〜2IをそれぞれクロスバA〜Iと表記し、装置3A〜3Fを装置A〜Fと表記して説明する場合がある。

情報処理システム1は、図2に示すように、データ転送でLSIを通過する転送経路が複数存在するように、LSI間を接続することができる。例えば、複数の装置3は、それぞれ異なる1つのクロスバ2と接続され、複数のクロスバ2は、それぞれ2〜4つの他のクロスバ2と接続される。なお、LSI間(装置3−クロスバ2間、及び2つのクロスバ2間)は、双方向に通信可能に電気的に接続されることが好ましい。つまり、一方のLSIの入力ポートと他方のLSIの出力ポートとが電気的に接続されるとともに、一方のLSIの出力ポートと他方のLSIの入力ポートとが電気的に接続されることが好ましい。

(a)クロスバ2がLSI間のデータ転送を一定回数リトライしてもエラーが解消されない場合。

(c)クロスバ2の出力ポートが、迂回路の出力ポートと比べて混雑している場合。

例えば、図2に示す情報処理システム1において、送信元装置3D〜3Fから送信先装置3A〜3Cへの転送経路が以下の転送経路となるように、管理部4により各クロスバ2のルーティングテーブルが設定されている場合を想定する。

クロスバG−クロスバD間の配線が故障した場合、情報処理システム1は、上記の最短経路を経由してデータを装置Aまで転送することができなくなる。そこで、情報処理システム1(管理部4)は、転送経路が、経由するクロスバ2の数(ホップ数)が最短経路の次に少ない以下のいずれかとなるように変更することで、データを装置Aまで転送することができる。なお、経由するクロスバ2の数が増加し、装置Aまでのデータの到達時間が余計にかかるが、情報処理システム1は、以下の2つ以外の転送経路を選択してもよい。

装置D−クロスバG−クロスバH−クロスバE−クロスバB−クロスバA−装置A

情報処理システム1は、上述した転送経路の変更を行なうために、クロスバGに入力する装置A宛てのフレームを、クロスバDへの転送からクロスバHへの転送に切り替えることができればよい。クロスバHに入力される装置A宛てのフレームは、クロスバHのルーティングテーブルの設定によってクロスバEに転送される。クロスバEに入力される装置A宛てのフレームは、クロスバEのルーティングテーブルの設定によってクロスバD又はクロスバBのいずれかに転送される。このように、各クロスバ2は装置A(送信先装置)宛てのフレームを装置Aに向かうようにルーティングする。つまり、情報処理システム1(管理部4)は、クロスバG−クロスバD間の配線が故障しても、クロスバG以外のルーティングテーブルを変更しなくてよい。

以下、図5及び図6を参照して、一実施形態の一例としての情報処理システム1(特にクロスバ2)の構成例について説明する。図5は、図2に示す情報処理システム1の詳細な構成例を示す図であり、図6は、図5に示すクロスバ2におけるルーティングテーブル53のデータ構造の一例を示す図である。なお、図5では、装置3の図示を省略する。

図5に例示するように、クロスバ2は、受付ポート5、入力ポート6、出力ポート8、及び接続部9をそれぞれ複数(図5の例ではそれぞれ3つ)そなえるとともに、1つのルーティング部7をそなえる。なお、4入力4出力のクロスバ2に一実施形態に係る構成を適用する場合、受付ポート5、入力ポート6、出力ポート8、及び接続部9をそれぞれ4つ設ければよい。以下、便宜上、図5に示すように、入力ポート6を入力ポートA〜Cのいずれかで特定し、入力キュー61を入力キューA〜Cのいずれかで特定し、出力ポート8を出力ポートA〜Cのいずれかで特定して説明する場合がある。また、図5では、図の簡略化のため、受付ポート5、入力ポート6、出力ポート8(出力ポートA)、及び接続部9の構成例をそれぞれ1つ図示するが、他の受付ポート5、入力ポート6、出力ポート8(出力ポートB、C)、及び接続部9についても同様である。

出力ポート8は、LSI間のデータ転送を一定回数リトライしてもエラーが解消されなかったり、フレームを送信したが対向LSIからAcknowledge信号が送られて来ずにタイムアウトした場合等に、対向LSI又は配線に故障が発生したと判断することができる。また、出力ポート8は、フレームの送信頻度が規定値を超えた、又は他出力ポート8よりも高頻度である場合等に、LSI間のデータ転送が混雑していると判断することができる。

接続部9は、配線やケーブル、ソケット等により転送先の対向LSIと接続され、出力ポート8から出力されるフレームを転送する。

受付キュー51は、複数の入力キュー61に格納されるフレームを一括して格納するものであり、受付格納部の一例である。なお、受付キュー51は、出力キュー81と同様に、FIFOのデータ構造とすることができる。受付キュー51としては、出力キュー81と同様、高速なリード/ライト動作が可能な回路が挙げられる。

ここで、図6を参照して、ルーティングテーブル53のデータ構造の一例について説明する。図6に例示するように、ルーティングテーブル53は、データの最終的な送信先(目的地)を入力(エントリ)として、ルーティングテーブル53を保持するクロスバ2のいずれかの出力ポート8の情報が設定されるテーブルである。

迂回用出力ポート8は、第1候補、第2候補の順(優先度の高い順)で、通常用出力ポート8−対向LSI間に故障や混雑が発生した場合に使用される。迂回用出力ポート8が第1候補、第2候補のいずれに設定されるかは、経由するLSIの数等に基づく優先順位に応じて決定されてもよいし、迂回用出力ポート8が使用される場合に他の送信先の出力ポート8との関係で混雑が生じ難い順に決定されてもよい。

以上のように、図6に例示するルーティングテーブル53は、フレームごと(送信先ごと)に、迂回路(転送先)に対応する出力ポート8が設定される。すなわち、ルーティングテーブル53は、フレームの1以上の転送先に関する転送先情報の一例である。より具体的には、図6に例示するルーティングテーブル53は、フレームの送信先装置3A〜3Cに応じた1以上の転送先に関する転送先情報の一例であるといえる。

入力キュー61は、出力キュー81と同様に、FIFOのデータ構造とすることができる。入力キュー61としては、出力キュー81と同様、高速なリード/ライト動作が可能な回路が挙げられる。複数の入力キュー61は、入力されるフレームを自クロスバ2に接続される送信先装置D〜F又はクロスバ2を含む転送先(クロスバ2又は装置3)ごとに格納する複数の格納部の一例である。

(ii)Least Recently Used(LRU)等のアービトレーション(Arbitration;調停)を行なう論理回路。

そこで、一実施形態では、クロスバ2に対して、上記(i)及び(ii)の論理回路を追加せずに、例えばフレーム送信判定回路54と、再送ステートマシン63とを追加することにより、平易な論理回路によって、転送経路の変更を実現することができる。

(I)通常のクロスバ2の動作状態(レジスタ値“3'b000”)において、再送ステートマシン63が出力ポート8から出力ポート閉塞信号を受信する。このとき、出力ポート閉塞信号を出力した出力ポート(以下、閉塞ポートともいう)8に対応する再送ステートマシン63のレジスタ値が“3'b001”に遷移する。

(III)入力ポート6が迂回用出力ポート(以下、代替ポートともいう)8宛ての入力キュー61内のフレームを該当出力ポート8へ送信する。代替ポート8宛ての入力キュー61内のフレームが全て送信され対向LSIへの到達が確認されると、閉塞ポート8に対応する再送ステートマシン63のレジスタ値が“3'b011”に遷移する。

(V)再送ステートマシン63が管理部4へルーティングテーブル53の更新が可能となったことを通知する。閉塞ポート8の再利用をしない場合、管理部4がルーティングテーブル53を更新して閉塞ポート8を代替ポート8に切り替える。一方、閉塞ポート8を再利用する場合、再送ステートマシン63が閉塞ポート8へ閉塞状態を解除させる信号を送信する。最後に、再送ステートマシン63が受付ポート5へフレームの送信を再開させる信号を送信すると、閉塞ポート8に対応する再送ステートマシン63のレジスタ値が“3'b000”(通常状態)に遷移する。

迂回用出力ポート管理回路64は、受付キュー51から入力キュー61に入力されるフレームごとに、ルーティングテーブル53内の迂回用出力ポート8の情報を保持する回路である。迂回用出力ポート管理回路64は、例えば、上記(IV)の処理において、再送ステートマシン63が閉塞ポート8に対応する入力キュー61内のフレームを出力する際に、フレームごとの出力先を通常用出力ポート8から迂回用出力ポート8に変換することができる。迂回用出力ポート管理回路64は、メモリ又はレジスタ等の記憶装置を含むことができる。メモリとしては、例えばRAM等の揮発性メモリが用いられてよい。なお、図5では、1つの入力ポート6内に1つの迂回用出力ポート管理回路64を図示しているが、入力キュー61ごとに迂回用出力ポート管理回路64がそなえられることが好ましい。

ルーティング部7は、各入力ポート6内の各入力キュー61と、各出力ポート8内の各出力キュー81との間を接続し、入力キュー61からルーティング部7に入力されたフレームを、対応する出力キュー81へ出力する。ルーティング部7としては、例えば、入力キュー61−出力キュー81間をデータパス(フレーム転送路)により接続した静的網が挙げられる。なお、ルーティング部7は、入力キュー61−出力キュー81間の距離が長い場合には、複数のデータパスにそれぞれフリップフロップ等を介装し、フレーム間の同期をとるようにしてもよい。

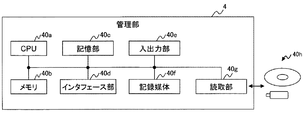

次に、図5〜図8を参照して、一実施形態の一例としての管理部4について説明する。図7は、図5に示す管理部4が保持する管理情報42のデータ構造の一例を示す図であり、図8は、図5に示す管理部4のハードウェア構成例を示す図である。

管理部4は、保持部41をそなえる(図5参照)。保持部41は、図7に示すように、情報処理システム1内の全クロスバ2の全ルーティングテーブル53(図6参照)の情報を管理情報42として保持する。保持部41としては、メモリ又はレジスタ等の記憶装置が挙げられる。メモリとしては、例えばRAM等の揮発性メモリを用いることができる。

このように、管理部4によれば、クロスバ2の動作を継続させたままルーティングテーブル53を更新することができる。また、ルーティングテーブル53の更新後にフレームが入力キュー61から閉塞ポート8へ出力されることを防止できる。

CPU40aは、図8における対応する各ブロック40b〜40gと接続され、種々の制御や演算を行なう処理装置(プロセッサ)の一例である。CPU40aは、メモリ40b、記録媒体40fや40h、又は図示しないRead Only Memory(ROM)等に格納されたプログラムを実行することにより、管理部4における種々の機能を実現することができる。メモリ40bは、種々のデータやプログラムを一時的に格納する記憶装置である。CPU40aは、プログラムを実行する際に、メモリ40bにデータやプログラムを格納し展開する。メモリ40bとしては、例えばRAM等の揮発性メモリが挙げられる。

次に、図9〜図11を参照して、一実施形態の一例としての情報処理システム1の動作例を説明する。

図9は、図5に示すクロスバ2の受付ポート5における再送処理の動作例を説明するフローチャートであり、図10は、図5に示すクロスバ2の入力ポート6における再送処理の動作例を説明するフローチャートである。図11は、図5に示す管理部4におけるルーティングテーブル53の更新処理の動作例を説明するフローチャートである。

はじめに、図9を参照して、受付ポート5における再送処理について説明する。

受付ポート5により出力ポート8から入力ポート6経由で出力ポート閉塞信号が受信されると(ステップS1)、フレーム送信判定回路54により、受付キュー51から入力ポート6へフレームが出力中か否かが判断される(ステップS2)。フレーム出力中である場合(ステップS2のYesルート)、フレーム送信判定回路54により、入力ポート6へ出力中のフレームが最後まで出力されたか否かが判断される(ステップS3)。出力中のフレームが最後まで出力されていない場合(ステップS3のNoルート)、フレーム送信判定回路54により、所定クロック(例えば数クロック;所定時間)待機され(ステップS4)、処理がステップS3に移行する。

〔1−6−2〕入力ポートにおける再送処理の動作例

次に、図10を参照して、入力ポート6における再送処理について説明する。

なお、ステップS13において、閉塞ポート8に対応する再送ステートマシン63は、代替ポート8宛ての入力キュー61に滞留する全フレームの送信が完了したことを検知することができる。或いは、閉塞ポート8に対応する再送ステートマシン63は、代替ポート8に対応する再送ステートマシン63から全フレームの送信が完了したことを通知されてもよい。ステップS13の処理が完了すると、閉塞ポート8に対応する再送ステートマシン63の状態が、閉塞ポート宛て入力キュー内フレーム送信状態(レジスタ値“3'b011”)に遷移する。なお、フレームごとに代替ポート8が設定される場合等、代替ポート8に対応する再送ステートマシン63が複数存在する場合、全代替ポート8について全フレームの送信が完了してから、閉塞ポート8に対応する再送ステートマシン63の状態が遷移する。

なお、ステップS13及びS14において、再送ステートマシン63は、フレームの喪失を防ぐため、送信する全フレームが該当出力ポート8から対向LSIへ正常に到達したことを確認してから、入力キュー61内の送信済フレームを解放することが好ましい。

そして、再送ステートマシン63により、ステップS13及びS14までの処理が完了したことが、ルーティングテーブル更新可能通知信号により管理部4へ通知される(ステップS15)。管理部4では、閉塞ポート8が再利用されない場合、ルーティングテーブル53が更新される(ステップS15)。

次に、図11を参照して、管理部4におけるルーティングテーブル53の更新処理について説明する。

なお、前提として、図11に例示するフローチャートの制御は、閉塞ポート8を再利用しない場合に実行されるものであり、管理部4が出力ポート閉塞信号に基づき閉塞ポート8を再利用すると判断した場合には実行されない。

次いで、管理部4により、再送ステートマシン63からルーティングテーブル更新可能通知信号が受信されると(ステップS22)、管理部4により、ルーティングテーブル53を更新可能か否かが判断される(ステップS23)。例えば、管理部4は、管理情報42を参照し、閉塞ポート8が通常用出力ポートに設定されているエントリに、迂回用出力ポートが有効に設定されているか否かを判断し、迂回用出力ポートが有効に設定されている場合に更新可能と判断することができる。

一方、ステップS23において、ルーティングテーブル53を更新不可能と判断された場合(ステップS23のNoルート)、管理部4により、クロスバ2(例えば再送ステートマシン63)へ致命的なエラーが通知され(ステップS27)、処理が終了する。なお、ルーティングテーブル53の更新が不可能な場合としては、例えば、閉塞ポート8が通常用出力ポートに設定されているエントリに、迂回用出力ポートが設定されていない、又は無効に設定されている場合等が挙げられる。管理部4から致命的なエラーを通知されると、クロスバ2又は情報処理システム1は、システム全体の動作を停止させてもよい。

次に、図12〜図16を参照して、情報処理システム1(特にクロスバ2)の実施例を説明する。

図12は、図5に示す受付ポート5の構成の実施例を示す図であり、図13は、図5に示す入力ポート6の構成の実施例を示す図である。図14は、図13に示す入力ポートにおける入力キュー61の制御手法の一例を説明する図であり、図15は、図13に示す入力ポート6におけるタイミングチャートの一例を示す図である。図16は、図5に示す出力ポート8の構成の実施例を示す図である。

〔1−7−1〕受付ポートの実施例

はじめに、図12を参照して、受付ポート5の実施例について説明する。

(A)入力ポート用クレジット管理情報A2がフレーム送信可能を示す場合。

なお、上記(B)において、出力中のデータがフレームの最後尾であるか否かは、後述する受付キュー51からのフレーム送信管理情報A7により判断される。

保持部52は、ルーティングテーブル53を保持するものであり、図5に示すものと基本的に同様の記憶装置である。ルーティングテーブル53は、送信先ID A8から送信先出力ポート(通常用出力ポート;通常用出力ポートに上書きされた迂回用出力ポートを含む)A9と第1候補の迂回用出力ポートA10とが導き出されるように登録されるテーブルである(図6参照)。送信先ID A8は、受付キュー51から出力されるフレームに含まれる(又はフレームとともに出力される)情報であり、データパス又は他の配線を介してルーティングテーブル53に供給される。

次に、図13〜図15を参照して、入力ポート6の実施例について説明する。

図13に示すように、入力ポート6は、図5に示す入力キュー61、セレクタ62、再送ステートマシン63、及び迂回用出力ポート管理回路64をそなえるとともに、以下の回路をさらにそなえることができる。つまり、入力ポート6は、制御信号生成回路65、クレジット生成回路66、及びエンコーダ67をそなえるとともに、出力ポート8ごとに入力キュー制御部60をそなえることができる。なお、便宜上、図13に示すように、入力キュー制御部60を入力キュー制御部A〜Cのいずれかで特定する場合がある。特に言及しない限り、入力キュー61、セレクタ62、再送ステートマシン63、及び迂回用出力ポート管理回路64の基本的な機能は図5に示すものと同様であるため、重複した説明を省略する。

ライト制御回路601は、入力キュー61へのライト制御を行なう。ライト制御回路601は、例えば、制御信号生成回路65からのフレーム送信制御信号B1を入力されると、入力キュー61における次にライトされるエントリをライトポインタで指示する。なお、ライト動作は上述のようにクレジット管理されるため、入力キュー61がオーバーフローする可能性は低い。

キュー再送エントリ数管理回路605は、入力キュー61で未だ再送される可能性のあるエントリ数を管理する回路である。キュー再送エントリ数管理回路605は、当該エントリ数(キュー再送エントリ数B2)を、クレジット生成回路66及び再送ステートマシン63へ出力することができる。キュー再送エントリ数管理回路605は、例えば、カウンタ等の回路をそなえ、入力キュー61にライトされたら当該回路のカウント値を加算することができる。また、キュー再送エントリ数管理回路605は、フレームを送信した出力ポート8からキューフレーム解放信号B4及び解放フレーム長B5を受信すると、解放フレーム長B5の分だけカウント値を減算することができる。

図14に例示するように、運用中のクロスバ2内の入力キュー61は、空白のエントリ、データ(フレームの一部)を保持するエントリ、並びに、データを入力キュー61から送信済み且つ対向LSIまで正常に到達したことの確認待ちであるエントリを含み得る。空白のエントリはライト制御回路601のライトポインタにより示され、データを保持するエントリは、リード制御回路602のリードポインタにより示され、データを送信済み且つ到達確認待ちのエントリは、再送リードポインタ603により示される。

キュー保持エントリ数管理回路604は、入力キュー61における、データを保持するエントリの数を保持するため、図14に示す例では、キュー保持エントリ数管理回路604のカウント値は1を示す。キュー再送エントリ数管理回路605は、入力キュー61における、データを保持するエントリの数と、データを送信済み且つ到達確認待ちのエントリの数との合計のエントリ数を保持する。従って、図14に示す例では、キュー再送エントリ数管理回路605のカウント値は2を示す。

ここで、図15を参照して、図13に示す入力ポート6における動作例を説明する。

なお、図15は、同一の入力ポート6内の、閉塞ポート8に対応する入力キュー制御部60、代替ポート8のうちの1つに対応する入力キュー制御部60における各信号のタイミングチャートの一例を示す。以下、出力ポート用クレジット管理回路606は、出力ポート用クレジットを受信するとカウント値を加算するものとして説明する。

次いで、図16を参照して、出力ポート8の実施例について説明する。

図16に示すように、出力ポート8は、図5に示す出力キュー81、及びセレクタ82をそなえるとともに、以下の回路をさらにそなえることができる。つまり、出力ポート8は、キューリードリクエスト調停回路83、フレーム送信可否判定回路84、フレーム到達確認管理回路85、及び出力ポート閉塞判定回路86をそなえるとともに、入力ポート6ごとに出力キュー制御部80をそなえることができる。なお、便宜上、図16に示すように、出力キュー制御部80を出力キュー制御部A〜Cのいずれかで特定する場合がある。特に言及しない限り、出力キュー81及びセレクタ82の基本的な機能は図5に示すものと同様であるため、重複した説明を省略する。

ライト制御回路801は、出力キュー81へのライト制御を行なう。ライト制御回路801は、例えば、データパスを通過するフレームに関するフレーム送信制御情報C1を入力されると、出力キュー81における次にライトされるエントリをライトポインタで指示する。なお、ライト動作は上述のようにクレジット管理されるため、出力キュー81がオーバーフローする可能性は低い。

キューリードリクエスト生成回路804は、出力キュー81からフレームをリード可能であることをキューリードリクエスト調停回路83へ伝達するためのキューリードリクエスト信号C2を生成する回路である。キューリードリクエスト生成回路804は、例えば、出力キュー81にフレームが格納されており、且つ対向LSIとの接続部9へ送信するデータパスのセレクタ82が何も選択していない場合に、キューリードリクエスト信号C2を生成することができる。なお、キューリードリクエスト生成回路804は、キュー保持エントリ数管理回路803の値が正である場合に、出力キュー81にフレームが格納されていると判断することができる。また、キューリードリクエスト信号C2には、フレーム長C3が付加されてよく、或いは含まれてもよい。

〔2−1〕第1変形例

一実施形態に係るクロスバ2は、図6に示すような、フレームごと(フレームの送信先ごと)に通常用出力ポート及び迂回用出力ポートが設定されるルーティングテーブル53を保持するものとして説明したが、これに限定されるものではない。例えば、クロスバ2は、ルーティングテーブル53に代えて、図17に示すような、出力ポート8ごとに通常用出力ポート及び迂回用出力ポートが設定されるルーティングテーブル53’を保持してもよい。特に言及しない限り、情報処理システム1の各構成は、図5等に示すものと同様であるため、重複した説明を省略する。

また、ルーティングテーブル53’のデータ構造が簡素化するため、管理部4によるルーティングテーブル53’の更新処理にかかる負荷を低減させることもできる。

〔2−2〕第2変形例

一実施形態に係るクロスバ2は、図6に示すような、迂回用出力ポート8ごとに有効/無効のカラムを持つルーティングテーブル53を保持するものとして説明したが、これに限定されるものではない。例えば、クロスバ2は、ルーティングテーブル53に代えて、図18に示すような、送信先出力ポート8をビット値によって通常用出力ポート8及び迂回用出力ポート8の中から選択可能なルーティングテーブル53”を保持してもよい。特に言及しない限り、情報処理システム1の各構成は、図5等に示すものと同様であるため、重複した説明を省略する。

出力ポート選択ビットのビット値“01”:第1候補の迂回用出力ポート8

出力ポート選択ビットのビット値“10”:第2候補の迂回用出力ポート8

・・・

なお、迂回用出力ポート8の候補数に応じて、出力ポート選択ビットのビット幅を適宜増減してもよい。

従って、第2変形例に係る情報処理システム1によれば、一実施形態と同様の効果を奏することができるほか、管理部4によるルーティングテーブル53”の更新処理にかかる負荷を低減させることができる。

一実施形態に係るクロスバ2は、再送ステートマシン63を各入力ポート6の各入力キュー制御部60内にそなえるものとして説明したが、これに限定されるものではない。

図19は、一実施形態の第3変形例に係る再送ステートマシン63’の構成を示す図である。例えば、クロスバ2は、図19に示す再送ステートマシン63’を入力キュー制御部60の外部にそなえ、入力キュー制御部60と再送ステートマシン63’とを配線で接続することができるほか、ソケットやピン等により接続してもよい。

状態管理部631は、レジスタ等の記憶装置をそなえ、上述した(I)〜(V)の状態を管理する(図10参照)。状態管理部631は、図13に示す出力ポート閉塞信号B7、入力ポート6へのフレーム送信停止信号A5、出力ポート切り替え完了信号B10、及びキュー再送エントリ数B2をそれぞれ入力され、各信号の入力に応じてレジスタ値を変化させる。

出力ポート制御部634は、状態管理部631のレジスタ値が“3'b100”の場合、且つ管理部4によりルーティングテーブル53が更新されなかった場合に、出力ポート8へ出力ポート閉塞解除信号B11を送信する。

このように、第3実施例に係る再送ステートマシン63’によれば、転送経路の変更処理を管理する機能をクロスバ2の外部に設けることができ、再送ステートマシン63’の交換により制御態様(論理)を容易に変更することができる。これにより、情報処理システム1の運用形態や構成の変化に応じた再送ステートマシン63’の更新を、クロスバ2全体を交換するよりも低コストに実現することができる。

以上、本発明の好ましい実施形態について詳述したが、本発明は、かかる特定の実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲内において、種々の変形、変更して実施することができる。

例えば、上述したクロスバ2は、受付ポート5、入力ポート6、出力ポート8、及び接続部9をそれぞれ3つそなえるものとして説明したが、これに限定されるものではなく、それぞれ2つ、又は4つ以上そなえてもよい。また、クロスバ2は、例えば少なくとも入力ポート6を1以上そなえ、出力ポート8を転送先の数だけそなえればよい。さらに、ルーティングテーブル53,53’,53”は、受付ポート5ごとにそなえられなくてもよく、管理部4がそなえる管理情報42と同様のものがクロスバ2にそなえられてもよい。また、セレクタ62は、入力ポート6の外部にそなえられてもよい。

さらに、図10のステップS13及びS14の処理順序は、上述したものに限定されるものではなく、順序を入れ替えてもよい。この場合、再送ステートマシン63のレジスタ値が示す状態も入れ替えればよい。

〔4〕付記

以上の実施形態及び各変形例に関し、更に以下の付記を開示する。

(付記1)

データを送信する送信元装置と、

前記送信元装置から送信された前記データを受信する送信先装置と、

前記送信元装置と前記送信先装置との間に介設され、複数の異なる転送経路のうちのいずれかを介して前記データを前記送信元装置から前記送信先装置へ転送する複数のデータ転送装置と、をそなえ、

前記データ転送装置は、

入力される転送データを自データ転送装置に接続される前記送信先装置または他のデータ転送装置を含む転送先ごとに格納する複数の格納部と、

前記複数の格納部に格納された転送データを、前記複数の転送先のいずれかへ選択的に切り替えて出力する切替部と、

前記切替部から一の転送経路を介した一の転送先へのデータ転送の状態に応じて、前記一の転送先に対応する格納部に格納された前記一の転送先への転送データを、前記複数の異なる転送経路に含まれる他の転送先へ出力するように前記切替部を制御する代替出力処理を行なう制御部と、を有する

ことを特徴とする、情報処理装置。

(付記2)

前記データ転送装置は、

前記転送データの1以上の転送先に関する転送先情報を保持する保持部をさらに有し、

前記一の転送先に対応する格納部に格納された転送データについて前記転送先情報に前記他の転送先が含まれる場合、前記制御部は、前記転送先情報に基づいて、前記代替出力処理を行なう

ことを特徴とする、付記1記載の情報処理装置。

(付記3)

前記転送先情報は、前記転送データの送信先装置に応じた1以上の転送先に関する情報であり、

前記制御部は、前記代替出力処理において、前記一の転送先に対応する格納部に格納された前記一の転送先への複数の転送データを、前記転送データの各々の送信先装置に応じた他の転送先へそれぞれ出力するように前記切替部を制御する

ことを特徴とする、付記2記載の情報処理装置。

(付記4)

前記切替部から前記複数の転送先へのデータ転送の状態に応じて、前記保持部に保持された前記転送先情報を更新する更新部をさらにそなえるとともに、

前記データ転送装置は、

入力される転送データの前記複数の格納部への格納を抑止する抑止部をさらに有し、

前記制御部は、前記代替出力処理を行なうと、前記転送先情報の更新要求を前記更新部へ送信し、

前記更新部は、前記制御部からの更新要求に応じて、前記一の転送先に出力される転送データが前記他の転送先に出力されるように、前記転送先情報を更新する

ことを特徴とする、付記2又は付記3記載の情報処理装置。

(付記5)

前記データ転送装置は、

前記自データ転送装置に接続される転送先ごとにそなえられ、前記転送データを当該転送データの転送先へ出力する複数の出力部をさらに有し、

前記制御部は、前記代替出力処理において、一の出力部から一の転送経路を介した前記一の転送先へのデータ転送の状態に応じて、前記一の出力部に対応する格納部に格納された、前記一の出力部へ出力済みの転送データを含む1以上の転送データを、各転送データに対応する他の出力部へ出力するように前記切替部を制御する

ことを特徴とする、付記1〜4のいずれか1項記載の情報処理装置。

(付記6)

前記データ転送装置は、

前記複数の転送先へのデータ転送の状態に応じて、出力抑止信号を出力する通知部と、

前記複数の格納部に格納される転送データを一括して格納する受付格納部と、

前記受付格納部に格納された転送データを対応する格納部へ順次出力させ、前記通知部から前記一の転送先について前記出力抑止信号を受信すると、前記受付格納部から出力中の転送データの出力が完了してから前記制御部による代替出力処理が完了するまで、前記受付格納部に格納された転送データの前記複数の格納部への出力を抑止させる制御を行なう受付制御部と、をさらに有する

ことを特徴とする、付記1〜5のいずれか1項記載の情報処理装置。

(付記7)

前記制御部は、前記切替部から第1の転送先への転送データの出力状況が第1の条件を満たす場合であって、前記切替部から第2の転送先への転送データの出力状況が第2の条件を満たす場合、前記第1の転送先に対応する格納部に格納された前記第1の転送先への転送データを、前記第2の転送先へ出力するように前記切替部を制御する

ことを特徴とする、付記1〜6のいずれか1項記載の情報処理装置。

(付記8)

データを送信する送信元装置と、前記送信元装置から送信された前記データを受信する送信先装置との間に介設され、複数の異なる転送経路のうちのいずれかを介して前記データを前記送信元装置から前記送信先装置へ転送するデータ転送装置であって、

入力される転送データを自データ転送装置に接続される前記送信先装置または他のデータ転送装置を含む転送先ごとに格納する複数の格納部と、

前記複数の格納部に格納された転送データを、前記複数の転送先のいずれかへ選択的に切り替えて出力する切替部と、

前記切替部から一の転送経路を介した一の転送先へのデータ転送の状態に応じて、前記一の転送先に対応する格納部に格納された前記一の転送先への転送データを、前記複数の異なる転送経路に含まれる他の転送先へ出力するように前記切替部を制御する代替出力処理を行なう制御部と、を有する

ことを特徴とする、データ転送装置。

(付記9)

前記転送データの1以上の転送先に関する転送先情報を保持する保持部をさらに有し、

前記一の転送先に対応する格納部に格納された転送データについて前記転送先情報に前記他の転送先が含まれる場合、前記制御部は、前記転送先情報に基づいて、前記代替出力処理を行なう

ことを特徴とする、付記8記載のデータ転送装置。

(付記10)

前記転送先情報は、前記転送データの送信先装置に応じた1以上の転送先に関する情報であり、

前記制御部は、前記代替出力処理において、前記一の転送先に対応する格納部に格納された前記一の転送先への複数の転送データを、前記転送データの各々の送信先装置に応じた他の転送先へそれぞれ出力するように前記切替部を制御する

ことを特徴とする、付記9記載のデータ転送装置。

(付記11)

前記自データ転送装置に接続される転送先ごとにそなえられ、前記転送データを当該転送データの転送先へ出力する複数の出力部をさらに有し、

前記制御部は、前記代替出力処理において、一の出力部から一の転送経路を介した前記一の転送先へのデータ転送の状態に応じて、前記一の出力部に対応する格納部に格納された、前記一の出力部へ出力済みの転送データを含む1以上の転送データを、各転送データに対応する他の出力部へ出力するように前記切替部を制御する

ことを特徴とする、付記8〜10のいずれか1項記載のデータ転送装置。

(付記12)

前記複数の転送先へのデータ転送の状態に応じて、出力抑止信号を出力する通知部と、

前記複数の格納部に格納される転送データを一括して格納する受付格納部と、

前記受付格納部に格納された転送データを対応する格納部へ順次出力させ、前記通知部から前記一の転送先について前記出力抑止信号を受信すると、前記受付格納部から出力中の転送データの出力が完了してから前記制御部による代替出力処理が完了するまで、前記受付格納部に格納された転送データの前記複数の格納部への出力を抑止させる制御を行なう受付制御部と、をさらに有する

ことを特徴とする、付記8〜11のいずれか1項記載のデータ転送装置。

(付記13)

前記制御部は、前記切替部から第1の転送先への転送データの出力状況が第1の条件を満たす場合であって、前記切替部から第2の転送先への転送データの出力状況が第2の条件を満たす場合、前記第1の転送先に対応する格納部に格納された前記第1の転送先への転送データを、前記第2の転送先へ出力するように前記切替部を制御する

ことを特徴とする、付記8〜12のいずれか1項記載のデータ転送装置。

(付記14)

データを送信する送信元装置と、前記送信元装置から送信された前記データを受信する送信先装置と、前記送信元装置と前記送信先装置との間に介設され、複数の異なる転送経路のうちのいずれかを介して前記データを前記送信元装置から前記送信先装置へ転送する1以上のデータ転送装置と、をそなえる情報処理システムにおけるデータ転送方法であって、

入力される転送データを、自データ転送装置に接続される前記送信先装置または他のデータ転送装置を含む転送先ごとにそなえられる複数の格納部のうちの、当該転送データの転送先に対応する格納部に格納し、

前記複数の格納部に格納された転送データを前記複数の転送先のいずれかへ選択的に切り替えて出力する切替部から一の転送経路を介した一の転送先へのデータ転送の状態を取得し、

取得した前記状態に応じて、前記一の転送先に対応する格納部に格納された前記一の転送先への転送データを、前記複数の異なる転送経路に含まれる他の転送先へ出力するように前記切替部を制御する代替出力処理を行なう

ことを特徴とする、データ転送方法。

(付記15)

前記一の転送先に対応する格納部に格納された転送データについて、保持部に保持された前記転送データの1以上の転送先に関する転送先情報に前記他の転送先が含まれる場合、前記転送先情報に基づいて、前記代替出力処理を行なう

ことを特徴とする、付記14記載のデータ転送方法。

(付記16)

前記転送先情報は、前記転送データの送信先装置に応じた1以上の転送先に関する情報であり、

前記代替出力処理において、前記一の転送先に対応する格納部に格納された前記一の転送先への複数の転送データを、前記転送データの各々の送信先装置に応じた他の転送先へそれぞれ出力するように前記切替部を制御する

ことを特徴とする、付記15記載のデータ転送方法。

(付記17)

入力される転送データの前記複数の格納部への格納を抑止し、

前記転送データの前記複数の格納部への格納が抑止されている場合に、

前記代替出力処理を行ない、

前記一の転送先に出力される転送データが前記他の転送先に出力されるように、前記転送先情報を更新する

ことを特徴とする、付記15又は付記16記載のデータ転送方法。

(付記18)

前記代替出力処理において、前記自データ転送装置に接続される転送先ごとにそなえられ、前記転送データを当該転送データの転送先へ出力する複数の出力部のうちの一の出力部から一の転送経路を介した前記一の転送先へのデータ転送の状態に応じて、前記一の出力部に対応する格納部に格納された、前記一の出力部へ出力済みの転送データを含む1以上の転送データを、各転送データに対応する他の出力部へ出力するように前記切替部を制御する

ことを特徴とする、付記14〜17のいずれか1項記載のデータ転送方法。

(付記19)

前記複数の格納部に格納される転送データを一括して格納する受付格納部に格納された転送データを対応する格納部へ順次出力し、

前記切替部から前記一の転送先へのデータ転送の状態が所定の条件を満たした場合に、前記受付格納部から出力中の転送データの出力が完了すると、前記受付格納部に格納された転送データの前記複数の格納部への出力を抑止し、

前記代替出力処理が完了すると、前記受付格納部に格納された転送データの前記複数の格納部への出力を再開する

ことを特徴とする、付記14〜18のいずれか1項記載のデータ転送方法。

(付記20)

前記切替部から第1の転送先への転送データの出力状況が第1の条件を満たす場合であって、前記切替部から第2の転送先への転送データの出力状況が第2の条件を満たす場合、前記第1の転送先に対応する格納部に格納された前記第1の転送先への転送データを、前記第2の転送先へ出力するように前記切替部を制御する

ことを特徴とする、付記14〜19のいずれか1項記載のデータ転送方法。

(付記21)

データを送信する送信元装置と、前記送信元装置から送信された前記データを受信する送信先装置との間に介設され、複数の異なる転送経路のうちのいずれかを介して前記データを前記送信元装置から前記送信先装置へ転送し、入力される転送データを自データ転送装置に接続される前記送信先装置または他のデータ転送装置を含む転送先ごとに格納する複数の格納部を有するデータ転送装置における制御装置であって、

前記複数の格納部に格納された転送データを、前記複数の転送先のいずれかへ選択的に切り替えて出力する切替部から一の転送経路を介した一の転送先へのデータ転送の状態を管理する状態管理部と、

前記状態管理部が管理する前記データ転送の状態に応じて、前記一の転送先に対応する格納部に格納された前記一の転送先への転送データを、前記複数の異なる転送経路に含まれる他の転送先へ出力するように前記切替部を制御する代替出力制御部と、を有する

ことを特徴とする、制御装置。

2,2A〜2I クロスバ(データ転送装置)

3,3A〜3F 装置

4 管理部(更新部)

5 受付ポート(抑止部)

6 入力ポート

7 ルーティング部

8 出力ポート(出力部)

9 接続部

40a CPU

40b メモリ

40c 記憶部

40d インタフェース部

40e 入出力部

40f,40h 記録媒体

40g 読取部

41,52 保持部

42 管理情報

51 受付キュー(受付格納部)

53,53’,53” ルーティングテーブル(転送先情報)

54 フレーム送信判定回路(受付制御部)

61 入力キュー(格納部)

62 セレクタ(切替部)

63,63’ 再送ステートマシン(制御部,制御装置)

64 迂回用出力ポート管理回路

81 出力キュー

82 セレクタ

86 出力ポート閉塞判定回路(通知部)

Claims (8)

- データを送信する送信元装置と、

前記送信元装置から送信された前記データを受信する送信先装置と、

前記送信元装置と前記送信先装置との間に介設され、複数の異なる転送経路のうちのいずれかを介して前記データを前記送信元装置から前記送信先装置へ転送する1以上のデータ転送装置と、をそなえ、

前記データ転送装置は、

入力される転送データを自データ転送装置に接続される前記送信先装置または他のデータ転送装置を含む転送先ごとに格納する複数の格納部と、

前記複数の格納部に格納された転送データを、前記複数の転送先のいずれかへ選択的に切り替えて出力する切替部と、

前記切替部から一の転送経路を介した一の転送先へのデータ転送の状態に応じて、前記一の転送先に対応する格納部に格納された前記一の転送先への転送データを、前記複数の異なる転送経路に含まれる他の転送先へ出力するように前記切替部を制御する代替出力処理を行なう制御部と、

前記複数の格納部に格納される転送データを一括して格納する受付格納部と、

前記複数の転送先へのデータ転送の状態に応じて、前記受付格納部に格納された転送データの前記複数の格納部への格納を抑止する抑止部と、を有する

ことを特徴とする、情報処理装置。 - 前記データ転送装置は、

前記転送データの1以上の転送先に関する転送先情報を保持する保持部をさらに有し、

前記一の転送先に対応する格納部に格納された転送データについて前記転送先情報に前記他の転送先が含まれる場合、前記制御部は、前記転送先情報に基づいて、前記代替出力処理を行なう

ことを特徴とする、請求項1記載の情報処理装置。 - 前記転送先情報は、前記転送データの送信先装置に応じた1以上の転送先に関する情報であり、

前記制御部は、前記代替出力処理において、前記一の転送先に対応する格納部に格納された前記一の転送先への複数の転送データを、前記転送データの各々の送信先装置に応じた他の転送先へそれぞれ出力するように前記切替部を制御する

ことを特徴とする、請求項2記載の情報処理装置。 - 前記切替部から前記複数の転送先へのデータ転送の状態に応じて、前記保持部に保持された前記転送先情報を更新する更新部をさらにそなえるとともに、

前記制御部は、前記代替出力処理を行なうと、前記転送先情報の更新要求を前記更新部へ送信し、

前記更新部は、前記制御部からの更新要求に応じて、前記一の転送先に出力される転送データが前記他の転送先に出力されるように、前記転送先情報を更新する

ことを特徴とする、請求項2又は請求項3記載の情報処理装置。 - 前記データ転送装置は、

前記複数の転送先へのデータ転送の状態に応じて、出力抑止信号を出力する通知部と、

前記受付格納部に格納された転送データを対応する格納部へ順次出力させ、前記通知部から前記一の転送先について前記出力抑止信号を受信すると、前記受付格納部から出力中の転送データの出力が完了してから前記制御部による代替出力処理が完了するまで、前記受付格納部に格納された転送データの前記複数の格納部への出力を抑止させる制御を行なう受付制御部と、をさらに有する

ことを特徴とする、請求項1〜4のいずれか1項記載の情報処理装置。 - データを送信する送信元装置と、前記送信元装置から送信された前記データを受信する送信先装置との間に介設され、複数の異なる転送経路のうちのいずれかを介して前記データを前記送信元装置から前記送信先装置へ転送するデータ転送装置であって、

入力される転送データを自データ転送装置に接続される前記送信先装置または他のデータ転送装置を含む転送先ごとに格納する複数の格納部と、

前記複数の格納部に格納された転送データを、前記複数の転送先のいずれかへ選択的に切り替えて出力する切替部と、

前記切替部から一の転送経路を介した一の転送先へのデータ転送の状態に応じて、前記一の転送先に対応する格納部に格納された前記一の転送先への転送データを、前記複数の異なる転送経路に含まれる他の転送先へ出力するように前記切替部を制御する代替出力処理を行なう制御部と、

前記複数の格納部に格納される転送データを一括して格納する受付格納部と、

前記複数の転送先へのデータ転送の状態に応じて、前記受付格納部に格納された転送データの前記複数の格納部への格納を抑止する抑止部と、を有する

ことを特徴とする、データ転送装置。 - データを送信する送信元装置と、前記送信元装置から送信された前記データを受信する送信先装置と、前記送信元装置と前記送信先装置との間に介設され、複数の異なる転送経路のうちのいずれかを介して前記データを前記送信元装置から前記送信先装置へ転送する1以上のデータ転送装置と、をそなえる情報処理システムにおけるデータ転送方法であって、

入力される転送データを、自データ転送装置に接続される前記送信先装置または他のデータ転送装置を含む転送先ごとにそなえられる複数の格納部のうちの、当該転送データの転送先に対応する格納部に格納し、

前記複数の格納部に格納された転送データを前記複数の転送先のいずれかへ選択的に切り替えて出力する切替部から一の転送経路を介した一の転送先へのデータ転送の状態を取得し、

取得した前記状態に応じて、前記一の転送先に対応する格納部に格納された前記一の転送先への転送データを、前記複数の異なる転送経路に含まれる他の転送先へ出力するように前記切替部を制御する代替出力処理を行ない、

前記複数の転送先へのデータ転送の状態に応じて、前記複数の格納部に格納される転送データを一括して格納する受付格納部に格納された転送データの前記複数の格納部への格納を抑止する

ことを特徴とする、データ転送方法。 - データを送信する送信元装置と、前記送信元装置から送信された前記データを受信する送信先装置との間に介設され、複数の異なる転送経路のうちのいずれかを介して前記データを前記送信元装置から前記送信先装置へ転送し、入力される転送データを自データ転送装置に接続される前記送信先装置または他のデータ転送装置を含む転送先ごとに格納する複数の格納部を有するデータ転送装置における制御装置であって、

前記複数の格納部に格納された転送データを、前記複数の転送先のいずれかへ選択的に切り替えて出力する切替部から一の転送経路を介した一の転送先へのデータ転送の状態を管理する状態管理部と、

前記状態管理部が管理する前記データ転送の状態に応じて、前記一の転送先に対応する格納部に格納された前記一の転送先への転送データを、前記複数の異なる転送経路に含まれる他の転送先へ出力するように前記切替部を制御する代替出力制御部と、

前記複数の転送先へのデータ転送の状態に応じて、前記複数の格納部に格納される転送データを一括して格納する受付格納部に格納された転送データの前記複数の格納部への格納を抑止する抑止部に対して、前記受付格納部に格納された転送データの前記複数の格納部への格納を再開させる受付格納制御部と、を有する

ことを特徴とする、制御装置。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2013/082343 WO2015083212A1 (ja) | 2013-12-02 | 2013-12-02 | 情報処理装置,データ転送装置,データ転送方法,および制御装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP6070848B2 true JP6070848B2 (ja) | 2017-02-01 |

| JPWO2015083212A1 JPWO2015083212A1 (ja) | 2017-03-16 |

Family

ID=53273010

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015531769A Active JP6070848B2 (ja) | 2013-12-02 | 2013-12-02 | 情報処理装置,データ転送装置,データ転送方法,および制御装置 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP6070848B2 (ja) |

| WO (1) | WO2015083212A1 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11720404B2 (en) * | 2020-07-16 | 2023-08-08 | Samsung Electronics Co., Ltd. | Systems and methods for arbitrating access to a shared resource |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09269937A (ja) * | 1996-03-30 | 1997-10-14 | Nec Corp | プロセッサ間通信におけるパケット送信方法およびその装置 |

| JPH1132057A (ja) * | 1997-07-11 | 1999-02-02 | Nec Corp | スイッチ装置 |

| JP2006039677A (ja) * | 2004-07-22 | 2006-02-09 | Fujitsu Ltd | クロスバ |

-

2013

- 2013-12-02 JP JP2015531769A patent/JP6070848B2/ja active Active

- 2013-12-02 WO PCT/JP2013/082343 patent/WO2015083212A1/ja not_active Ceased

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09269937A (ja) * | 1996-03-30 | 1997-10-14 | Nec Corp | プロセッサ間通信におけるパケット送信方法およびその装置 |

| JPH1132057A (ja) * | 1997-07-11 | 1999-02-02 | Nec Corp | スイッチ装置 |

| JP2006039677A (ja) * | 2004-07-22 | 2006-02-09 | Fujitsu Ltd | クロスバ |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2015083212A1 (ja) | 2015-06-11 |

| JPWO2015083212A1 (ja) | 2017-03-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7558895B2 (en) | Interconnect logic for a data processing apparatus | |

| US8855112B2 (en) | NoC system and input switching device | |

| JP4808514B2 (ja) | 大域的非同期ネットワークオンチップシステムにおける通信ノードアーキテクチャ | |

| EP2741456B1 (en) | Method, device and system for achieving message transmission of pcie switch network | |

| KR100985926B1 (ko) | 메모리 시스템 컴포넌트들 사이에서 신호들을 리라우팅하는시스템 및 방법 | |

| EP0404337B1 (en) | High-speed mesh connected local area network | |

| JP5104465B2 (ja) | 転送装置及びパケット伝送装置 | |

| US7493426B2 (en) | Data communication method and apparatus utilizing programmable channels for allocation of buffer space and transaction control | |

| TWI603205B (zh) | 於晶載網路上之流量控制技術 | |

| TW201944258A (zh) | 異步多時鐘域資料流接合及再同步系統及方法 | |

| US20110235652A1 (en) | Implementing enhanced link bandwidth in a headless interconnect chip | |

| US10423333B2 (en) | System and method for scalable processing of abort commands in a host bus adapter system | |

| JP5842174B2 (ja) | バス制御装置、中継装置およびバスシステム | |

| JP6070848B2 (ja) | 情報処理装置,データ転送装置,データ転送方法,および制御装置 | |

| EP1708076B1 (en) | Storage system and storage control method | |

| KR100936203B1 (ko) | 데이터 처리 장치, 모드 관리 장치 및 모드 관리 방법 | |

| JP6847334B2 (ja) | ネットワーク装置、ネットワークシステム、ネットワーク方法、およびネットワークプログラム | |

| JP2010211458A (ja) | 計算機システム及びi/o制御方法 | |

| JP2017163273A (ja) | 半導体装置、情報処理装置、半導体装置の論理の再構成方法および半導体装置の論理の再構成プログラム | |

| JP5310735B2 (ja) | パケット転送装置、プロセッサ間通信システム、並列プロセッサシステムおよびパケット転送方法 | |

| JP5287975B2 (ja) | 情報処理装置 | |

| JP2008204335A (ja) | 半導体ストレージ装置 | |

| JP5022159B2 (ja) | インタフェース装置、通信装置、通信システム、通信制御方法及び通信制御プログラム | |

| JP6394727B1 (ja) | 制御装置、制御方法、及び、フォールトトレラント装置 | |

| JP2010010897A (ja) | 多重化装置同期化処理装置及び多重化装置同期化処理方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150715 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150715 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160906 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161021 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20161206 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20161219 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6070848 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |