JP6070848B2 - Information processing apparatus, data transfer apparatus, data transfer method, and control apparatus - Google Patents

Information processing apparatus, data transfer apparatus, data transfer method, and control apparatus Download PDFInfo

- Publication number

- JP6070848B2 JP6070848B2 JP2015531769A JP2015531769A JP6070848B2 JP 6070848 B2 JP6070848 B2 JP 6070848B2 JP 2015531769 A JP2015531769 A JP 2015531769A JP 2015531769 A JP2015531769 A JP 2015531769A JP 6070848 B2 JP6070848 B2 JP 6070848B2

- Authority

- JP

- Japan

- Prior art keywords

- transfer

- data

- output

- destination

- port

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000012546 transfer Methods 0.000 title claims description 547

- 230000010365 information processing Effects 0.000 title claims description 75

- 238000000034 method Methods 0.000 title claims description 65

- 230000005540 biological transmission Effects 0.000 claims description 212

- 230000008569 process Effects 0.000 claims description 46

- 238000012545 processing Methods 0.000 claims description 28

- 230000001629 suppression Effects 0.000 claims description 12

- 230000004044 response Effects 0.000 claims description 4

- 230000015654 memory Effects 0.000 description 38

- 230000006870 function Effects 0.000 description 23

- 230000004048 modification Effects 0.000 description 23

- 238000012986 modification Methods 0.000 description 23

- 238000010586 diagram Methods 0.000 description 15

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 11

- 230000007704 transition Effects 0.000 description 11

- 238000012790 confirmation Methods 0.000 description 10

- 230000008859 change Effects 0.000 description 9

- 230000006854 communication Effects 0.000 description 6

- 238000004891 communication Methods 0.000 description 6

- 230000000903 blocking effect Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 230000001360 synchronised effect Effects 0.000 description 3

- 230000010354 integration Effects 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- 235000008694 Humulus lupulus Nutrition 0.000 description 1

- 230000007175 bidirectional communication Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000008030 elimination Effects 0.000 description 1

- 238000003379 elimination reaction Methods 0.000 description 1

- 239000000835 fiber Substances 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/76—Architectures of general purpose stored program computers

- G06F15/78—Architectures of general purpose stored program computers comprising a single central processing unit

- G06F15/7807—System on chip, i.e. computer system on a single chip; System in package, i.e. computer system on one or more chips in a single package

- G06F15/7825—Globally asynchronous, locally synchronous, e.g. network on chip

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- General Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Computing Systems (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

- Multi Processors (AREA)

- Bus Control (AREA)

Description

本件は、情報処理装置,データ転送装置,データ転送方法,および制御装置に関する。 The present invention relates to an information processing device, a data transfer device, a data transfer method, and a control device.

サーバやPersonal Computer(PC)等のコンピュータを用いた情報処理システム(情報処理装置)における装置間の通信において、1つの送信先の装置に対して複数の送信元の装置からデータが転送されることがある。ここで、装置としては、Large Scale Integration(LSI)等の集積回路、例えば、Central Processing Unit(CPU)等のプロセッサやメモリ、Input/Output(I/O)装置、メモリコントローラ、I/Oコントローラ等が挙げられる。以下、装置をLSIともいう。このような情報処理システムでは、複数の装置間を相互に接続するために、転送するデータを選択し調停する機構の一例であるクロスバ等のデータ転送装置が用いられることがある。 In communication between devices in an information processing system (information processing device) using a computer such as a server or a personal computer (PC), data is transferred from a plurality of transmission source devices to one transmission destination device. There is. Here, as the device, an integrated circuit such as a large scale integration (LSI), for example, a processor or memory such as a central processing unit (CPU), an input / output (I / O) device, a memory controller, an I / O controller, or the like Is mentioned. Hereinafter, the apparatus is also referred to as an LSI. In such an information processing system, a data transfer device such as a crossbar, which is an example of a mechanism for selecting and arbitrating data to be transferred, may be used to connect a plurality of devices to each other.

データ転送装置は、複数の送信元からデータを入力された際にどの送信元からのデータを転送するかを選択する制御回路と、制御回路により選択されなかったデータを先入れ先出し(First In First Out;FIFO)で格納するキューとをそなえることができる。

なお、関連する技術として、異なる冗長構成が可能なネットワーク転送装置が知られている(例えば、特許文献1参照)。ネットワーク転送装置は、例えば、パケット送信先に接続されたクロスバスイッチに障害が発生すると、パケット送信元からサブクロスバスイッチへのパケット送信を停止することができる。このネットワーク転送装置は、クロスバスイッチ及びサブクロスバスイッチにパケットが存在しなくなると、サブクロスバスイッチ内の出力バッファとポートとの接続を切り替えて、サブクロスバスイッチを予備系のクロスバスイッチと接続することができる。The data transfer device selects a source from which data is transferred when data is input from a plurality of sources, and first-in first-out (first in first out) data not selected by the control circuit. FIFO) can be provided for storing queues.

As a related technique, a network transfer apparatus capable of different redundant configurations is known (see, for example, Patent Document 1). For example, when a failure occurs in the crossbar switch connected to the packet transmission destination, the network transfer apparatus can stop packet transmission from the packet transmission source to the sub crossbar switch. When there is no packet in the crossbar switch and sub-crossbar switch, this network transfer device can switch the connection between the output buffer and the port in the sub-crossbar switch and connect the sub-crossbar switch to the standby crossbar switch. it can.

また、関連する他の技術として、転送先(出力ポート)ごとに1以上の入力キューをそなえるクロスバが知られている(例えば、特許文献2参照)。このクロスバは、例えば、入力ポートごとに、入力キューが多段に配設され、且つ入力キューがデータ転送先の出力ポートごとに配設された入力キュー群をそなえることができる。 As another related technique, a crossbar having one or more input queues for each transfer destination (output port) is known (see, for example, Patent Document 2). This crossbar can include, for example, an input queue group in which input queues are arranged in multiple stages for each input port, and input queues are arranged for each output port of the data transfer destination.

データ転送装置は、出力ポートに対向する(接続された)対向LSIへのデータ転送において、対向LSI又は対向LSIまでの転送路で発生する障害や混雑等により、対向LSI(転送先)へのデータ転送に失敗する場合がある。

データの送信元から送信先への転送経路が複数存在し、データ転送装置から2以上の対向LSIのいずれにデータを転送しても送信先にデータが到達する場合には、データ転送装置は、迂回路として他の出力ポートを介してデータ転送を行なうことも考えられる。In the data transfer to the counter LSI facing (connected) to the output port, the data transfer device transfers data to the counter LSI (transfer destination) due to a failure or congestion in the transfer path to the counter LSI or the counter LSI. Transfer may fail.

If there are a plurality of transfer paths from the data transmission source to the transmission destination, and the data reaches the transmission destination even if the data transfer device transfers data to any of the two or more opposing LSIs, the data transfer device It is also conceivable to transfer data via another output port as a detour.

しかしながら、上述した転送先(出力ポート)ごとに入力キュー(バッファ)をそなえるデータ転送装置では、迂回路として他の出力ポートを介してもデータ転送を行なうことが困難な場合がある。その理由は、上述したデータ転送装置は、入力キュー及び出力ポートと1つの対向LSIとが対応付けられるため、入力キューに格納されたデータを他の対向LSIに対応する出力ポートに転送することが困難な場合があるためである。 However, in the above-described data transfer apparatus having an input queue (buffer) for each transfer destination (output port), it may be difficult to transfer data via another output port as a detour. The reason is that the data transfer apparatus described above can transfer data stored in the input queue to an output port corresponding to another counter LSI because the input queue and output port are associated with one counter LSI. This is because it may be difficult.

このように、転送先ごとに入力キュー(格納部)を有するデータ転送装置では、データの送信元から送信先への転送経路が複数存在する場合でも、障害や混雑等により、データ転送が困難になる場合があるという課題がある。

ここまで、装置がプロセッサやメモリ、各種コントローラ等のLSI(集積回路)であるものとして説明したが、上述した課題は、これらLSI(集積回路)間の通信に限られるものではない。上述した課題は、装置が、例えばCPUやメモリ等をそなえるシステムボード等のコンピュータ、I/Oボード、ネットワークインタフェース等であり、データ転送装置がこれらの装置間でデータ転送を行なう装置であっても同様に生じ得る。As described above, in a data transfer apparatus having an input queue (storage unit) for each transfer destination, even when there are a plurality of transfer paths from the data transmission source to the transmission destination, data transfer becomes difficult due to a failure or congestion. There is a problem that it may become.

Up to this point, the device has been described as an LSI (integrated circuit) such as a processor, memory, and various controllers. However, the above-described problem is not limited to communication between these LSIs (integrated circuits). The problem described above is that the device is, for example, a computer such as a system board having a CPU and a memory, an I / O board, a network interface, and the like, and the data transfer device is a device that transfers data between these devices. It can occur as well.

1つの側面では、本発明は、データの転送先の故障や混雑等が発生しても、データを確実に転送することを目的とする。

なお、前記目的に限らず、後述する発明を実施するための形態に示す各構成により導かれる作用効果であって、従来の技術によっては得られない作用効果を奏することも本発明の他の目的の1つとして位置付けることができる。In one aspect, an object of the present invention is to reliably transfer data even if a failure or congestion of the data transfer destination occurs.

In addition, the present invention is not limited to the above-described object, and other effects of the present invention can be achieved by the functions and effects derived from the respective configurations shown in the embodiments for carrying out the invention which will be described later. It can be positioned as one of

本件の情報処理装置は、データを送信する送信元装置と、前記送信元装置から送信された前記データを受信する送信先装置と、1以上のデータ転送装置と、をそなえる。前記1以上のデータ転送装置は、前記送信元装置と前記送信先装置との間に介設され、複数の異なる転送経路のうちのいずれかを介して前記データを前記送信元装置から前記送信先装置へ転送する。前記データ転送装置は、複数の格納部と、切替部と、制御部と、受付格納部と、抑止部とを有する。前記複数の格納部は、入力される転送データを自データ転送装置に接続される前記送信先装置または他のデータ転送装置を含む転送先ごとに格納する。前記切替部は、前記複数の格納部に格納された転送データを、前記複数の転送先のいずれかへ選択的に切り替えて出力する。前記制御部は、前記切替部から一の転送経路を介した一の転送先へのデータ転送の状態に応じて、前記一の転送先に対応する格納部に格納された前記一の転送先への転送データを、前記複数の異なる転送経路に含まれる他の転送先へ出力するように前記切替部を制御する代替出力処理を行なう。前記受付格納部は、前記複数の格納部に格納される転送データを一括して格納する。前記抑止部は、前記複数の転送先へのデータ転送の状態に応じて、前記受付格納部に格納された転送データの前記複数の格納部への格納を抑止する。 Present information processing apparatus, a source device that transmits data, a destination device for receiving the data transmitted from the transmission source device, 1 a or more data transfer device, Ru provided with a. The one or more data transfer devices are interposed between the transmission source device and the transmission destination device, and the data is transmitted from the transmission source device to the transmission destination via any one of a plurality of different transfer paths. Transfer to device. The data transfer device includes a plurality of storage units, a switching unit, a control unit, a reception storage unit, and a suppression unit. The plurality of storage units store input transfer data for each transfer destination including the transmission destination device or another data transfer device connected to the own data transfer device . The switching unit, the transfer data stored in said plurality of storage portions, and outputs selectively switches to one of said plurality of transfer destination. The control unit, from said switching unit depending on the state of the data transfer to one destination through one of the transfer path, the transfer destination of the one stored in the storage unit corresponding to the one destination An alternative output process is performed to control the switching unit so that the transfer data is output to other transfer destinations included in the plurality of different transfer paths. The reception storage unit collectively stores transfer data stored in the plurality of storage units. The suppression unit suppresses storage of the transfer data stored in the reception storage unit in the plurality of storage units according to a state of data transfer to the plurality of transfer destinations.

一実施形態によれば、データの転送先の故障や混雑等が発生しても、データを確実に転送することができる。 According to an embodiment, data can be reliably transferred even if a failure or congestion of the data transfer destination occurs.

以下、図面を参照して実施の形態を説明する。

〔1〕一実施形態

〔1−1〕情報処理システムの構成例

はじめに、図1及び図2を参照して、一実施形態の一例としての情報処理システム1の構成例を説明する。図1は、一実施形態に係る情報処理システム1の一例を示す図であり、図2は、図1に示す情報処理システム1の構成例を示す図である。Hereinafter, embodiments will be described with reference to the drawings.

[1] One Embodiment [1-1] Configuration Example of Information Processing System First, a configuration example of an

図1に示すように、情報処理システム1は、クロスバ部20、複数(図1に示す例では6つ)の装置3、及び管理部4をそなえる。

装置3は、データを送信する送信元装置、及び、送信元装置から送信されたデータを受信する送信先装置のうちの少なくとも一方の機能をそなえる。図2に示す例では、装置3D〜3Fは送信元装置の機能をそなえ、装置3A〜3Cは送信先装置の機能をそなえる。As illustrated in FIG. 1, the

The

送信元装置としての装置3D〜3Fは、送信するデータをフレーム(Frame)又はパケット(Packet)(以下、これらをまとめて単にフレームという)単位に分割して送信することができる。このとき、装置3D〜3Fは、送信する各フレームに、送信先装置(3A〜3C)を特定するための情報(宛先情報)を付加することができる。

送信先装置としての装置3A〜3Cは、クロスバ部20を介して送信元装置3D〜3Fからフレームを受信し、受信したフレームから送信元装置3D〜3Fが送信したデータを取得することができる。The devices 3D to 3F serving as the transmission source devices can transmit the data to be transmitted by dividing the data into frames or packets (hereinafter collectively referred to simply as frames). At this time, the devices 3D to 3F can add information (destination information) for specifying the transmission destination devices (3A to 3C) to each frame to be transmitted.

The

装置3としては、LSI等の集積回路、例えば、CPU等のプロセッサや、メモリ、I/O装置、メモリコントローラ、I/Oコントローラ等が挙げられる。また、装置3としては、例えば、CPUやメモリ等をそなえるシステムボードや、I/Oコントローラやカードスロット又は記憶装置等をそなえるI/Oボード等の各種装置、又は、サーバやPC、ストレージ装置等のコンピュータ等も挙げられる。

The

クロスバ部20は、複数の装置3間に介設され、データの送信元装置3D〜3Fから送信されたデータを送信先装置3A〜3Cへ転送する。クロスバ部20は、1以上のクロスバ2(クロスバ群)をそなえることができる。以下、クロスバ部20は、図2に例示するように9つのクロスバ2A〜2I(以下の説明においてクロスバ2A〜2Iを区別しない場合には単に符号2で示す)をそなえるものとして説明する。

The

複数のクロスバ2は、送信元装置3D〜3Fと送信先装置3A〜3Cとの間に介設されるとともに、各々が他の1以上のクロスバ2と相互に通信可能に接続される。そして、複数のクロスバ2は、複数の異なる転送経路のうちのいずれかを介してデータ(フレーム)を送信元装置3D〜3Fから送信先装置3A〜3Cへ転送する。

なお、以下、転送経路には、送信元装置3D〜3Fと送信先装置3A〜3Cとの間の1以上のクロスバ2及び1以上のデータパス(転送路)を介した経路が含まれる。転送路としては、システムバスを含む各種バスや、Local Area Network(LAN),ファイバチャネル(Fibre Channel),インフィニバンド(InfiniBand)等のケーブル、または無線通信路等が挙げられる。また、複数の異なる転送経路には、経由するクロスバ2及びデータパスの少なくとも1つが互いに異なる複数の経路が含まれる。さらに、以下、転送先には、クロスバ2の出力ポートに対向する対向LSI、つまりデータパス(転送路)を介して出力ポートに接続される送信先装置3A〜3C又はクロスバ2を含む対向LSIが含まれる。The plurality of

Hereinafter, the transfer route includes a route through one or

管理部4は、複数のクロスバ2の各々と相互に通信可能に接続され、各クロスバ2がそなえるルーティングテーブルを管理する。管理部4の詳細については、後述する。

〔1−2〕クロスバの対比例

ここで、図3及び図4を参照して、図2に示すクロスバ2の説明のために、クロスバ2の対比例としてのクロスバ200A及び200Bについて説明する。図3及び図4は、それぞれ一実施形態に係るクロスバ2の対比例としてのクロスバ200A及び200Bの構成を示す図である。クロスバ200A及び200Bは、図2に示すクロスバ2に代えて情報処理システム1に適用することができる。以下、3入力3出力のクロスバ200A及び200B(図2に示すクロスバA〜C,G〜Iに対応)を例に挙げて説明する。The

[1-2] Crossbar Comparison The

クロスバ200Aは、図3に例示するように、受付ポート500、入力ポート600A、出力ポート800、及び接続部900をそれぞれ複数(図3の例ではそれぞれ3つ)そなえるとともに、1つのルーティング部700をそなえる。

なお、図3では、図の簡略化のため、受付ポート500、入力ポート600A、出力ポート800、及び接続部900の構成例をそれぞれ1つ図示するが、他の受付ポート500、入力ポート600A、出力ポート800、及び接続部900についても同様である。As illustrated in FIG. 3, the crossbar 200 </ b> A includes a plurality of

In FIG. 3, for simplification of the drawing, one configuration example of each of the

受付ポート500は、メモリ又はレジスタ等の保持部510をそなえる。メモリとしては、例えばRandom Access Memory(RAM)等の揮発性メモリが挙げられる。保持部510は、宛先情報と出力ポート800の番号等の出力ポート800を特定するための情報とが対応付けられたルーティングテーブル520を保持する。受付ポート500は、ルーティングテーブル520を検索して、入力されるフレームに含まれる宛先情報からフレームを出力する出力ポート800を特定し、フレームと特定した出力ポート800の情報とを入力ポート600Aへ出力する。なお、ルーティングテーブル520は、管理部4により登録及び更新されてもよい。

The

入力ポート600Aは、全宛先(転送先)で共通に用いられる入力キュー610Aをそなえ、受付ポート500から入力されるデータを入力キュー610Aに格納する。入力キュー610AはFIFOのデータ構造とすることができる。

ルーティング部700は、各入力ポート600A内の入力キュー610Aと、各出力ポート800内の各出力キュー810との間を接続し、入力キュー610Aからルーティング部700に入力されたフレームを、対応する出力キュー810へ出力する。The

The

出力ポート800は、複数の送信元に対応する複数(図3の例では3つ)の出力キュー810とセレクタ820とをそなえる。出力キュー810は、入力キュー610Aと同様にFIFOのデータ構造とすることができる。出力ポート800は、入力キュー610Aの先頭のフレームを選択し、ルーティング部700を介して出力キュー810に格納する。なお、出力ポート800により入力キュー610Aの先頭のフレームが選択されない場合、当該先頭のフレームも後続のフレームも転送先の出力ポート800に出力されない。

The

接続部900は、配線やケーブル、ソケット等により転送先の対向LSIと接続され、出力ポート800から出力されるフレームを転送する。

クロスバ200Bは、図4に例示するように、図3に示すクロスバ200Aの入力ポート600Aとは異なる入力ポート600Bをそなえる。

入力ポート600Bは、宛先(転送先)ごとに入力キュー610Bをそなえ、受付ポート500から入力されるフレームを、出力ポート800の情報に基づき転送先ごとに入力キュー610Bに振り分けて格納する。各入力キュー610Bは、入力キュー610Aと同様にFIFOのデータ構造とすることができる。なお、入力ポート600B以外の構成はクロスバ200Aと同様であるため、詳細な説明を省略する。The

As illustrated in FIG. 4, the

The

上記のような構成により、クロスバ200Bは、入力キュー610Bの先頭が転送先の数だけ存在することになるため、出力ポート800でのフレームの選択を並列して行なうことができる。従って、クロスバ200Bでは、先頭のフレームが選択されないことにより、他の出力ポート800宛ての後続のフレームが待たされることがないため、図3に示すクロスバ200Aと比較してスループットの向上が期待できる。

With the configuration described above, the

なお、図3及び図4に示す例では、出力ポート800は、複数の出力キュー810をそなえるが、これらの出力キュー810は省略されてもよい。また、クロスバ200A及び200Bは、レイテンシ向上のため、入力ポート600A及び600B内の入力キュー610A及び610B、並びに/又は、出力ポート800内の出力キュー810のエントリが空の場合には、これらのキューをバイパスさせてもよい。

In the example shown in FIGS. 3 and 4, the

ところで、クロスバ200A及び200Bは、出力ポート800の出力キュー810に、対向LSI(転送先)へ出力したデータを保持しておくリトライ機能をそなえ、データ転送においてエラーが発生した場合にデータ転送のリトライを行なうこともできる。エラーが発生する要因としては、LSI間の配線の切断やデータを中継する装置の故障等の継続的な故障(固定故障)、LSIへの中性子ヒット、電磁波、熱等の影響による一時的な故障(間欠故障)等が挙げられる。

By the way, the

クロスバ200A及び200Bは、データ転送において間欠故障によるエラーが発生しても、リトライ機能によりデータ転送をリトライすることで、間欠故障の自然復旧後にデータ転送を成功させてエラーを回避できる場合がある。

一方、データ転送において固定故障によるエラーが発生した場合、クロスバ200A及び200Bは、LSI間でデータ転送をリトライしても、固定故障への対処がなされなければ、対向LSIへエラーや損失のないデータを転送することは困難な場合がある。また、データ転送においてビジー又はLSI間の輻輳等による混雑が生じている場合にも同様である。つまり、クロスバ200A及び200Bは、データ転送において混雑が生じている対向LSIに対応する入力キュー610A又は610Bからのデータを、空いている他の対向LSIに対応する出力ポート800に切り替えることは難しい。Even if an error due to an intermittent failure occurs in the data transfer, the

On the other hand, if an error due to a fixed failure occurs in data transfer, the

クロスバ200Aについては、固定故障及び混雑が生じている場合、以下の機能を持たせることでエラーを回避できる場合がある。例えば、クロスバ200Aは、入力キュー610Aから出力ポート800にフレームを送信しただけでは、当該フレームを入力キュー610Aから解放しないようにすればよい。一例として、クロスバ200Aは、出力ポート800の対向LSIが正しくフレームを受信したことを確認できた場合に、入力キュー610Aから当該フレームを解放すればよい。なお、対向LSIは、例えば、フレームを1つ正しく受信したら受信確認信号(Acknowledge信号)を返信する等の手法により、LSIが正しくフレームを受信したか否かを、クロスバ200Aに通知することができる。

For the

仮に、或る出力ポート800と対向LSIとの間での接続に故障が発生し、クロスバ200Aが正しくフレームを送信できない場合、クロスバ200Aは、故障が発生した経路へのデータ転送を一時停止することができる。そして、管理部4が情報処理システム1全体を停止させることなく動的にルーティングテーブル520を更新し、出力ポート800は、入力キュー610Aで記憶していたフレームを迂回路へ転送すればよい。これにより、クロスバ200Aは、フレームを失わずに目的地へ転送することができる。

If a failure occurs in the connection between a

しかしながら、上述のように、図3に示すクロスバ200Aは、図4に示すクロスバ200Bに比べてスループットが低い。そこで、クロスバ200Bにおいても、上記のクロスバ200Aのように動的にルーティングテーブル520を更新し、迂回路へのフレームの転送を行なわせることが望ましい。しかし、クロスバ200Bでは、入力ポート600Bの入力キュー610Bが転送先ごとに分かれているため、各入力キュー610Bに既に格納されているフレームを迂回路へ転送することは困難である。

However, as described above, the

そこで、一実施形態の一例としての情報処理システム1は、図4に示すクロスバ200Bのように転送先ごとに入力キューを有するスループット向上型のクロスバ2において、動的な転送経路の変更を可能とするものである。すなわち、以下に詳述するように、一実施形態の一例としての情報処理システム1は、クロスバ2を有し、データの送信元から送信先への転送経路が複数存在する場合に、データの転送先の故障や混雑等が発生しても、データを確実に転送することができる。

Therefore, the

〔1−3〕情報処理システムにおける転送経路の変更手法

図2の説明に戻り、情報処理システム1における転送経路の変更手法の説明を行なう。なお、便宜上、図2に示すように、クロスバ2A〜2IをそれぞれクロスバA〜Iと表記し、装置3A〜3Fを装置A〜Fと表記して説明する場合がある。

情報処理システム1は、図2に示すように、データ転送でLSIを通過する転送経路が複数存在するように、LSI間を接続することができる。例えば、複数の装置3は、それぞれ異なる1つのクロスバ2と接続され、複数のクロスバ2は、それぞれ2〜4つの他のクロスバ2と接続される。なお、LSI間(装置3−クロスバ2間、及び2つのクロスバ2間)は、双方向に通信可能に電気的に接続されることが好ましい。つまり、一方のLSIの入力ポートと他方のLSIの出力ポートとが電気的に接続されるとともに、一方のLSIの出力ポートと他方のLSIの入力ポートとが電気的に接続されることが好ましい。[1-3] Transfer Route Changing Method in Information Processing System Returning to the description of FIG. 2, the transfer route changing method in the

As shown in FIG. 2, the

情報処理システム1(クロスバ2)は、例えば下記(a)〜(c)のいずれかの場合に、該当LSI間のデータ転送を止めて、異なる転送経路を経由してデータ転送を行なう(データ転送を継続する)。

(a)クロスバ2がLSI間のデータ転送を一定回数リトライしてもエラーが解消されない場合。The information processing system 1 (crossbar 2) stops data transfer between the corresponding LSIs and performs data transfer via different transfer paths in any of the following cases (a) to (c) (data transfer) Continue).

(A) The error is not resolved even if the

(b)クロスバ2がフレームを出力したにもかかわらず、送信先LSIからフレーム受信完了通知を受信せず、タイムアウトした場合。

(c)クロスバ2の出力ポートが、迂回路の出力ポートと比べて混雑している場合。

例えば、図2に示す情報処理システム1において、送信元装置3D〜3Fから送信先装置3A〜3Cへの転送経路が以下の転送経路となるように、管理部4により各クロスバ2のルーティングテーブルが設定されている場合を想定する。(B) When the

(C) The output port of the

For example, in the

装置D−クロスバG−クロスバD−クロスバA−装置A(最短経路)

クロスバG−クロスバD間の配線が故障した場合、情報処理システム1は、上記の最短経路を経由してデータを装置Aまで転送することができなくなる。そこで、情報処理システム1(管理部4)は、転送経路が、経由するクロスバ2の数(ホップ数)が最短経路の次に少ない以下のいずれかとなるように変更することで、データを装置Aまで転送することができる。なお、経由するクロスバ2の数が増加し、装置Aまでのデータの到達時間が余計にかかるが、情報処理システム1は、以下の2つ以外の転送経路を選択してもよい。Device D-Crossbar G-Crossbar D-Crossbar A-Device A (shortest path)

When the wiring between the crossbar G and the crossbar D fails, the

装置D−クロスバG−クロスバH−クロスバE−クロスバD−クロスバA−装置A

装置D−クロスバG−クロスバH−クロスバE−クロスバB−クロスバA−装置A

情報処理システム1は、上述した転送経路の変更を行なうために、クロスバGに入力する装置A宛てのフレームを、クロスバDへの転送からクロスバHへの転送に切り替えることができればよい。クロスバHに入力される装置A宛てのフレームは、クロスバHのルーティングテーブルの設定によってクロスバEに転送される。クロスバEに入力される装置A宛てのフレームは、クロスバEのルーティングテーブルの設定によってクロスバD又はクロスバBのいずれかに転送される。このように、各クロスバ2は装置A(送信先装置)宛てのフレームを装置Aに向かうようにルーティングする。つまり、情報処理システム1(管理部4)は、クロスバG−クロスバD間の配線が故障しても、クロスバG以外のルーティングテーブルを変更しなくてよい。Device D-Crossbar G-Crossbar H-Crossbar E-Crossbar D-Crossbar A-Device A

Device D-Crossbar G-Crossbar H-Crossbar E-Crossbar B-Crossbar A-Device A

The

以下に詳述する、一実施形態の一例としてクロスバ2(情報処理システム1)は、例えば少なくともクロスバGに適用することで、クロスバG−クロスバD間の配線が故障した場合でも、装置Dから装置Aへのデータの転送経路を変更可能とするものである。なお、図2に示すクロスバA〜Iは全て同様の構成をそなえることができるため、クロスバ2は、任意のクロスバA〜Iに適用されてよい。クロスバA〜Iのすべてにクロスバ2が適用されることにより、いずれのクロスバ2間が故障しても、装置3間の通信の転送経路を変更可能とすることができる。

The crossbar 2 (information processing system 1), which is described in detail below as an example of the embodiment, is applied to at least the crossbar G, for example, so that even if the wiring between the crossbar G and the crossbar D breaks down, the device D to the device The data transfer path to A can be changed. 2 can all have the same configuration, the

〔1−4〕クロスバの構成例

以下、図5及び図6を参照して、一実施形態の一例としての情報処理システム1(特にクロスバ2)の構成例について説明する。図5は、図2に示す情報処理システム1の詳細な構成例を示す図であり、図6は、図5に示すクロスバ2におけるルーティングテーブル53のデータ構造の一例を示す図である。なお、図5では、装置3の図示を省略する。[1-4] Configuration Example of Crossbar Hereinafter, a configuration example of the information processing system 1 (particularly the crossbar 2) as an example of an embodiment will be described with reference to FIGS. 5 and 6. FIG. 5 is a diagram showing a detailed configuration example of the

クロスバ2は、入力されるフレーム(転送データ)を転送先の対向LSIへ転送するデータ転送装置の一例である。データ転送装置としては、集積回路、例えば、LSIやApplication Specific Integrated Circuit(ASIC)、Field Programmable Gate Array(FPGA)等の、クロスバ2としての機能をそなえる電子回路が挙げられる。なお、装置3が上述したCPU、メモリ、I/O装置、各種コントローラ等の装置である場合、クロスバ2としてL1クロスバスイッチが用いられてもよい。以下の説明では、これまでと同様、クロスバ2の出力ポートに対向する(接続された)装置3や他のクロスバ2等をまとめてLSI又は対向LSIという。クロスバ2は、1つの集積回路であってもよいし、複数の集積回路の組み合わせであってもよい。また、クロスバ2は、CPU等のプロセッサやメモリ、I/O装置、各種コントローラ等の集積回路に組み込まれてもよく、実装場所は特に限定されない。なお、装置3がシステムボードやI/Oボード等の装置であってもよく、この場合、クロスバ2としてL2クロスバスイッチが用いられてもよい。

The

以下、3入力3出力のクロスバ2(図2に示すクロスバA〜C,G〜I)を例に挙げて説明するが、4入力4出力のクロスバ2(図2に示すクロスバD〜F)についても同様の構成とすることができる。

図5に例示するように、クロスバ2は、受付ポート5、入力ポート6、出力ポート8、及び接続部9をそれぞれ複数(図5の例ではそれぞれ3つ)そなえるとともに、1つのルーティング部7をそなえる。なお、4入力4出力のクロスバ2に一実施形態に係る構成を適用する場合、受付ポート5、入力ポート6、出力ポート8、及び接続部9をそれぞれ4つ設ければよい。以下、便宜上、図5に示すように、入力ポート6を入力ポートA〜Cのいずれかで特定し、入力キュー61を入力キューA〜Cのいずれかで特定し、出力ポート8を出力ポートA〜Cのいずれかで特定して説明する場合がある。また、図5では、図の簡略化のため、受付ポート5、入力ポート6、出力ポート8(出力ポートA)、及び接続部9の構成例をそれぞれ1つ図示するが、他の受付ポート5、入力ポート6、出力ポート8(出力ポートB、C)、及び接続部9についても同様である。Hereinafter, the

As illustrated in FIG. 5, the

出力ポート8は、複数の送信元に対応する複数(図5の例では3つ)の出力キュー81をそなえるとともに、セレクタ82をそなえる。特に言及しない限り、出力ポート8(出力キュー81及びセレクタ82)の基本的な機能は図4に示す出力ポート800(出力キュー810及びセレクタ820)と同様であるため、重複した説明を省略する。複数の出力ポート8は、転送先2,3ごとにそなえられ、フレームを当該フレームの転送先へ出力する複数の出力部の一例である。

The

また、出力キュー81はリトライ機能をそなえることができる。出力キュー81は、FIFOのデータ構造とすることができる。出力キュー81としては、例えばStatic RAM(SRAM)等の高速な揮発性メモリ、フリップフロップ(Flip Flop)やラッチ等の論理回路等、高速なリード/ライト動作が可能な回路が挙げられる。

出力ポート8は、LSI間のデータ転送を一定回数リトライしてもエラーが解消されなかったり、フレームを送信したが対向LSIからAcknowledge信号が送られて来ずにタイムアウトした場合等に、対向LSI又は配線に故障が発生したと判断することができる。また、出力ポート8は、フレームの送信頻度が規定値を超えた、又は他出力ポート8よりも高頻度である場合等に、LSI間のデータ転送が混雑していると判断することができる。Further, the

The

出力ポート8から対向LSIへのデータ転送においてエラーを検出した場合、出力ポート8は、発生したエラーが間欠故障によるものであることを期待し、複数回のフレームの再送(リトライ)を試みる。規定回数以上再送してもエラーを検出してしまう場合、出力ポート8は、ひとまず固定故障であると判断し、自出力ポート8を閉塞することができる。なお、出力ポート8は、混雑の発生を検出した場合にも、自出力ポート8を閉塞することができる。そして、出力ポート8は、自出力ポート8を閉塞すると、全ての入力ポート6、受付ポート5、及び管理部4に対して、自ポート(出力ポート8)の閉塞を示す出力ポート閉塞信号(出力抑止信号)を出力する。すなわち、出力ポート8(出力キュー81)は、対応する転送先へのデータ転送の状態に応じて、出力抑止信号を出力する。

When an error is detected in the data transfer from the

なお、出力ポート8は、自出力ポート8を再利用するか否かを判断し、出力ポート閉塞信号に再利用の有無の情報を含ませてもよい。出力ポート8は、例えば、エラーが固定故障によるものであると判断した場合に再利用無しと判断してもよく、混雑を検出した場合に再利用有りと判断してもよい。また、エラーが固定故障によるものであっても、故障個所の動的交換によりエラーが解消される見込みがある場合には、再利用有りと判断してもよい。出力ポート8による自出力ポート8の再利用の有無の判断は、これらに限定されるものではなく、種々の条件に基づいて行なわれてよい。例えば、出力ポート8は、検出したエラーの内容や混雑の状況や、情報処理システム1の運用ルール等に基づいて、自出力ポート8の再利用の有無を判断してもよい。

Note that the

なお、出力ポート8は、自出力ポート8の閉塞中に、同期リセットをしてもよい。また、出力ポート8は、入力ポート6から出力ポート閉塞解除信号を受信すると、自出力ポート8の再利用を行なうべく、同期リセットを解除し、再利用にそなえることができる。

接続部9は、配線やケーブル、ソケット等により転送先の対向LSIと接続され、出力ポート8から出力されるフレームを転送する。Note that the

The

受付ポート5は、受付キュー51、保持部52、及びフレーム送信判定回路54をそなえる。特に言及しない限り、受付ポート5の基本的な機能は図4に示す受付ポート500と同様であるため、重複した説明を省略する。

受付キュー51は、複数の入力キュー61に格納されるフレームを一括して格納するものであり、受付格納部の一例である。なお、受付キュー51は、出力キュー81と同様に、FIFOのデータ構造とすることができる。受付キュー51としては、出力キュー81と同様、高速なリード/ライト動作が可能な回路が挙げられる。The

The

保持部52は、宛先情報と出力ポート8の番号等の出力ポート8を特定するための情報とが対応付けられたルーティングテーブル53を保持する。保持部52としては、メモリ又はレジスタ等の記憶装置が挙げられる。メモリとしては、例えばRAM等の揮発性メモリを用いることができる。

ここで、図6を参照して、ルーティングテーブル53のデータ構造の一例について説明する。図6に例示するように、ルーティングテーブル53は、データの最終的な送信先(目的地)を入力(エントリ)として、ルーティングテーブル53を保持するクロスバ2のいずれかの出力ポート8の情報が設定されるテーブルである。The holding

Here, an example of the data structure of the routing table 53 will be described with reference to FIG. As illustrated in FIG. 6, the routing table 53 is set with information of any

具体的には、ルーティングテーブル53は、ルーティングテーブル53のエントリの有効(例えば“0”)又は無効(例えば“1”)を示すビット,データの送信先の宛先情報,及び通常用の出力ポート8の情報を含んでよい。また、ルーティングテーブル53は、迂回路の出力ポート8があるエントリについては、1組以上の迂回用出力ポート8の有効(例えば“0”)又は無効(例えば“1”)を示すビット並びに迂回用の出力ポート8の情報を含んでよい。例えば、送信先Aのエントリは、通常用出力ポート8に出力ポートA、第1候補の迂回用出力ポート8に出力ポートB、第2候補の迂回用出力ポート8に出力ポートCが、それぞれ設定される。

Specifically, the routing table 53 includes a bit indicating validity (for example, “0”) or invalidity (for example, “1”) of the entry of the routing table 53, destination information of the data transmission destination, and the

なお、ルーティングテーブル53において、エントリの有効/無効は、例えば、送信先装置3A〜3Cが通信可能に存在している場合に有効が設定され、故障等により送信先装置3A〜3Cが通信不可能な場合に無効に設定される。迂回用出力ポート8の有効/無効は、対応する迂回用出力ポート8が有効であるか否かを示すものである。

迂回用出力ポート8は、第1候補、第2候補の順(優先度の高い順)で、通常用出力ポート8−対向LSI間に故障や混雑が発生した場合に使用される。迂回用出力ポート8が第1候補、第2候補のいずれに設定されるかは、経由するLSIの数等に基づく優先順位に応じて決定されてもよいし、迂回用出力ポート8が使用される場合に他の送信先の出力ポート8との関係で混雑が生じ難い順に決定されてもよい。In the routing table 53, the validity / invalidity of the entry is set to valid when, for example, the

The

なお、ルーティングテーブル53は、後述する管理部4によって登録及び更新される。

以上のように、図6に例示するルーティングテーブル53は、フレームごと(送信先ごと)に、迂回路(転送先)に対応する出力ポート8が設定される。すなわち、ルーティングテーブル53は、フレームの1以上の転送先に関する転送先情報の一例である。より具体的には、図6に例示するルーティングテーブル53は、フレームの送信先装置3A〜3Cに応じた1以上の転送先に関する転送先情報の一例であるといえる。The routing table 53 is registered and updated by the

As described above, in the routing table 53 illustrated in FIG. 6, the

図5の説明に戻り、フレーム送信判定回路54は、受付キュー51に格納されたフレームを対応する入力キュー61へ順次出力させる。また、フレーム送信判定回路54は、出力ポート8から出力ポート閉塞信号を受信すると、再送ステートマシン63からフレーム送信再開指示信号を受信するまで、受付キュー51に格納されたフレームの複数の入力キュー61への出力を抑止させる制御を行なう。これにより、受付ポート5は、入力キュー61へのフレームの出力途中に出力ポート閉塞信号を受信した場合でも、データ転送の最小単位であるフレームの区切りで入力キュー61へのフレームの出力を停止させることができる。従って、入力ポート6は、後述する転送経路の切り替えをフレームの区切りで行なうことができるため、フレームの破損等によるデータの喪失を回避することができる。

Returning to the description of FIG. 5, the frame

すなわち、フレーム送信判定回路54は、受付キュー51から出力中のフレームの出力が完了してから再送ステートマシン63による再送処理が完了するまで、受付キュー51に格納されたフレームの入力キュー61への出力を抑止させる受付制御部の一例である。また、受付ポート5は、入力されるフレームの複数の入力キュー61への格納を抑止する抑止部の一例である。

That is, the frame

入力ポート6は、3つの入力キュー61、セレクタ62、再送ステートマシン63、及び迂回用出力ポート管理回路64をそなえる。特に言及しない限り、入力ポート6(入力キュー61)の基本的な機能は図4に示す入力ポート600B(入力キュー610B)と同様であるため、重複した説明を省略する。

入力キュー61は、出力キュー81と同様に、FIFOのデータ構造とすることができる。入力キュー61としては、出力キュー81と同様、高速なリード/ライト動作が可能な回路が挙げられる。複数の入力キュー61は、入力されるフレームを自クロスバ2に接続される送信先装置D〜F又はクロスバ2を含む転送先(クロスバ2又は装置3)ごとに格納する複数の格納部の一例である。The

As with the

セレクタ62は、入力ポート6の各入力キュー61の出力側に設けられる。セレクタ62は、複数の入力キュー61に格納されたフレームを、複数の転送先(出力ポート8)のいずれかへ選択的に切り替えて出力する切替部の一例である。セレクタ62としては、例えばバススイッチ等の回路が挙げられる。図5に示す例では、セレクタ62は、出力ポート8ごとに設けられ、個々のセレクタが3つの入力キュー61及び対応する出力ポート8と配線で接続される。これにより、入力キュー61が保持するフレームの転送先が変更されても対応することができる。

The

セレクタ62の選択論理は、フレームごとに出力ポート8を選択させるものとしてもよいが、そのためには、転送経路を変更しなければ不要であった下記の(i)及び(ii)の論理回路が用いられることになる。これらの論理回路がクロスバ2に追加されると、入力ポート6の論理回路が複雑になり、回路の物量や、遅延時間、遅延の発生頻度等も増加する可能性がある。

The selection logic of the

(i)フレームとフレームの区切りの判定を行なう論理回路。

(ii)Least Recently Used(LRU)等のアービトレーション(Arbitration;調停)を行なう論理回路。

そこで、一実施形態では、クロスバ2に対して、上記(i)及び(ii)の論理回路を追加せずに、例えばフレーム送信判定回路54と、再送ステートマシン63とを追加することにより、平易な論理回路によって、転送経路の変更を実現することができる。(I) A logic circuit that determines the separation between frames.

(Ii) A logic circuit that performs arbitration such as Least Recently Used (LRU).

Therefore, in one embodiment, for example, the frame

再送ステートマシン63は、出力ポート8から出力ポート閉塞信号を受信してから受付ポート5へフレーム送信再開指示信号を送信するまで、クロスバ2及び管理部4を制御する論理回路である。なお、図5では、1つの入力ポート6内に1つの再送ステートマシン63を図示しているが、入力キュー61ごとに再送ステートマシン63がそなえられることが好ましい。

The

再送ステートマシン63は、例えば、レジスタ等のビット値(レジスタ値)を用いてクロスバ2の状態を管理し、以下の(I)〜(V)の場合にレジスタ値を変化させる。再送ステートマシン63は、クロスバ2内の各回路や管理部4にレジスタ値を参照させる、又はレジスタ値に応じた指示を行なうことで、各回路や管理部4の制御を実現する。

(I)通常のクロスバ2の動作状態(レジスタ値“3'b000”)において、再送ステートマシン63が出力ポート8から出力ポート閉塞信号を受信する。このとき、出力ポート閉塞信号を出力した出力ポート(以下、閉塞ポートともいう)8に対応する再送ステートマシン63のレジスタ値が“3'b001”に遷移する。For example, the

(I) In the normal operation state of the crossbar 2 (register value “3′b000”), the

(II)再送ステートマシン63が受付ポート5から入力ポート6へのフレーム送信を停止したことを示す信号を受信する。このとき、閉塞ポート8に対応する再送ステートマシン63のレジスタ値が“3'b010”に遷移する。

(III)入力ポート6が迂回用出力ポート(以下、代替ポートともいう)8宛ての入力キュー61内のフレームを該当出力ポート8へ送信する。代替ポート8宛ての入力キュー61内のフレームが全て送信され対向LSIへの到達が確認されると、閉塞ポート8に対応する再送ステートマシン63のレジスタ値が“3'b011”に遷移する。(II) The

(III) The

(IV)入力ポート6が閉塞ポート8宛ての入力キュー61内のフレームをセレクタ62を制御して代替ポート8へ送信する。閉塞ポート8宛ての入力キュー61内のフレームが全て送信され対向LSIへの到達が確認されると、閉塞ポート8に対応する再送ステートマシン63のレジスタ値が“3'b100”に遷移する。

(V)再送ステートマシン63が管理部4へルーティングテーブル53の更新が可能となったことを通知する。閉塞ポート8の再利用をしない場合、管理部4がルーティングテーブル53を更新して閉塞ポート8を代替ポート8に切り替える。一方、閉塞ポート8を再利用する場合、再送ステートマシン63が閉塞ポート8へ閉塞状態を解除させる信号を送信する。最後に、再送ステートマシン63が受付ポート5へフレームの送信を再開させる信号を送信すると、閉塞ポート8に対応する再送ステートマシン63のレジスタ値が“3'b000”(通常状態)に遷移する。(IV) The

(V) The

このように、再送ステートマシン63は、一の転送先に対応する入力キュー61に格納された一の転送先へのフレームを、複数の異なる転送経路に含まれる他の(代替の)転送先へ出力するようにセレクタ62を制御する代替出力処理を行なう制御部の一例である。より具体的に、再送ステートマシン63は、代替出力処理において、一の転送先に対応する入力キュー61に格納された一の転送先への複数のフレームを、フレームの各々の送信先装置3A〜3Cに応じた代替の転送先へそれぞれ出力するようにセレクタ62を制御する。この代替出力処理は、再送ステートマシン63により、セレクタ62(の出力側,例えば一の出力ポート8)から一の転送経路を介した一の転送先(対向LSI)へのデータ転送の状態に応じて行なわれる。

In this way, the

以上のように、一実施形態に係る情報処理システム1(クロスバ2)によれば、データの転送先の故障や混雑等が発生しても、代替の出力ポート8へ転送路(転送先)が変更されるため、データ(フレーム)を送信先まで確実に転送することができる。また、情報処理システム1によれば、固定故障が発生した場合にフレームを送信先まで正しく転送することができる。さらに、情報処理システム1によれば、混雑している場合であっても転送路を空いている迂回路に切り替えることができ、間欠故障が発生した場合でも間欠故障が復旧するまでの間に転送路を迂回路に切り替えることができるため、データ転送の遅延を低減できる。

As described above, according to the information processing system 1 (crossbar 2) according to the embodiment, even if a data transfer destination failure or congestion occurs, a transfer path (transfer destination) is provided to the

また、情報処理システム1によれば、クロスバ2の動作を継続させたまま、入力ポート6ごとにフレームの転送先を代替ポート8へ動的に切り替えることができる。従って、他の入力ポート6に滞留しているフレームが全て送信されるのを待たずに入力ポート6ごとに切り替えを完了させることができるとともに、クロスバ2全体の動作を停止させずに済むため、他の出力ポート8に与える影響を最小限に留めることができる。

Further, according to the

また、上記(IV)において、閉塞ポート8宛ての入力キュー61内のフレームには、一度閉塞ポート8へ出力されたものの、障害等により対向LSIへの到達が確認できていないフレームも含まれ得る。つまり、再送ステートマシン63は、閉塞ポート8に対応する入力キュー61に格納された、閉塞ポート8へ出力済みのフレームを含む1以上のフレームを、各フレームに対応する代替ポート8へ出力することができる。

In (IV), the frame in the

このように、情報処理システム1によれば、閉塞ポート8に対応する入力キュー61に格納された、転送失敗のフレームも含めて、代替ポート8へ出力されるため、転送経路に障害が発生した場合でも、データの喪失を回避することができる。

迂回用出力ポート管理回路64は、受付キュー51から入力キュー61に入力されるフレームごとに、ルーティングテーブル53内の迂回用出力ポート8の情報を保持する回路である。迂回用出力ポート管理回路64は、例えば、上記(IV)の処理において、再送ステートマシン63が閉塞ポート8に対応する入力キュー61内のフレームを出力する際に、フレームごとの出力先を通常用出力ポート8から迂回用出力ポート8に変換することができる。迂回用出力ポート管理回路64は、メモリ又はレジスタ等の記憶装置を含むことができる。メモリとしては、例えばRAM等の揮発性メモリが用いられてよい。なお、図5では、1つの入力ポート6内に1つの迂回用出力ポート管理回路64を図示しているが、入力キュー61ごとに迂回用出力ポート管理回路64がそなえられることが好ましい。As described above, according to the

The bypass output

このように、再送ステートマシン63は、ルーティングテーブル53から代替ポート8の情報を取得した迂回用出力ポート管理回路64と協働して、閉塞ポート8に対応する入力キュー61に格納されたフレームを代替ポート8へ出力することができる。換言すれば、再送ステートマシン63は、障害等が検出された一の転送先に対応する入力キュー61に格納されたフレームについて、ルーティングテーブル53に代替の転送先(代替ポート8)が含まれる場合、代替出力処理を行なうものであるといえる。

In this way, the

つまり、情報処理システム1によれば、ルーティングテーブル53の設定によって代替ポート8を任意の出力ポート8とすることができ、また、フレームごとに異なる代替ポート8、つまり異なる迂回路に転送することも可能となる。従って、代替ポート8への切り替えの自由度が上がり、耐障害性を向上させることができる。

ルーティング部7は、各入力ポート6内の各入力キュー61と、各出力ポート8内の各出力キュー81との間を接続し、入力キュー61からルーティング部7に入力されたフレームを、対応する出力キュー81へ出力する。ルーティング部7としては、例えば、入力キュー61−出力キュー81間をデータパス(フレーム転送路)により接続した静的網が挙げられる。なお、ルーティング部7は、入力キュー61−出力キュー81間の距離が長い場合には、複数のデータパスにそれぞれフリップフロップ等を介装し、フレーム間の同期をとるようにしてもよい。That is, according to the

The

〔1−5〕管理部の構成例

次に、図5〜図8を参照して、一実施形態の一例としての管理部4について説明する。図7は、図5に示す管理部4が保持する管理情報42のデータ構造の一例を示す図であり、図8は、図5に示す管理部4のハードウェア構成例を示す図である。

管理部4は、保持部41をそなえる(図5参照)。保持部41は、図7に示すように、情報処理システム1内の全クロスバ2の全ルーティングテーブル53(図6参照)の情報を管理情報42として保持する。保持部41としては、メモリ又はレジスタ等の記憶装置が挙げられる。メモリとしては、例えばRAM等の揮発性メモリを用いることができる。[1-5] Configuration Example of Management Unit Next, the

The

管理部4は、管理情報42、及び受付ポート5のルーティングテーブル53のそれぞれについて、登録及び更新を行なうことができる。管理部4は、例えば、各クロスバ2の出力ポート8からの出力ポート閉塞信号を受信した後、又はルーティングテーブル53を更新する前に、管理情報42を更新することができる。また、管理部4は、例えば、管理情報42の更新が完了すると、再送ステートマシン63からのルーティングテーブル更新可能通知信号に応じて、管理情報42に対してした更新と同様の内容で、ルーティングテーブル53を更新する。そして、管理部4は、ルーティングテーブル53を更新すると、出力ポート切り替え完了信号を再送ステートマシン63へ送信する。つまり、管理部4は、更新要求に応じて、一の転送先(例えば閉塞ポート8に接続された転送先)に出力されるフレームが代替の転送先(例えば代替ポート8に接続された転送先)に出力されるように、ルーティングテーブル53を更新する。

The

管理情報42又はルーティングテーブル53の更新において、管理部4は、閉塞ポート8が迂回用出力ポートに設定されているエントリに対し、当該閉塞ポート8の迂回用出力ポートを無効に設定し、迂回用出力ポートとして使用されないようにすることができる。また、管理部4は、閉塞ポート8が通常用出力ポートに設定されているエントリに対し、迂回用出力ポートを通常用出力ポートに上書きして元の迂回用出力ポートを無効に設定することができる。これらの設定により、管理部4は、迂回用出力ポートを通常用出力ポートに切り替えることができる。

In the update of the

なお、管理部4は、閉塞した出力ポート8を再利用する場合、ルーティングテーブル53及び管理情報42の更新を行なわなくてよい。閉塞中の出力ポート8を再利用するか否かの判断は、管理部4で再利用の有無を判断可能な実装とした上で、管理部4が決定することができる。管理部4による再利用の有無の判断材料としては、例えば、管理部4に再利用する場合/しない場合のいずれかに固定するモードを設けたり、出力ポート8からの出力ポート閉塞信号を再利用する場合/しない場合の2種類にすること等が挙げられる。なお、管理部4は、出力ポート切り替え完了信号を、ルーティングテーブル53を更新した場合/していない場合の2種類にしてもよい。これにより、管理部4は、閉塞ポート8の再利用をしないと判断した場合に、ルーティングテーブル53を更新していないことを再送ステートマシン63へ通知することができる。

The

以上のように、管理部4は、セレクタ62(複数の出力ポート8の各々)から複数の転送先へのデータ転送の状態に応じて、受付ポート5の保持部52に保持されたルーティングテーブル53を更新する更新部の一例である。

このように、管理部4によれば、クロスバ2の動作を継続させたままルーティングテーブル53を更新することができる。また、ルーティングテーブル53の更新後にフレームが入力キュー61から閉塞ポート8へ出力されることを防止できる。As described above, the

Thus, according to the

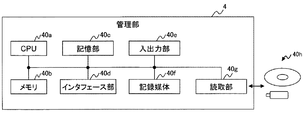

上述した管理部4の動作は、例えば情報処理システム1のファームウェア等のソフトウェアによる処理によって実現されてもよい。例えば、管理部4は、図8に示すように、CPU40a、メモリ40b、記憶部40c、インタフェース部40d、入出力部40e、記録媒体40f、及び読取部40gをそなえることができる。

CPU40aは、図8における対応する各ブロック40b〜40gと接続され、種々の制御や演算を行なう処理装置(プロセッサ)の一例である。CPU40aは、メモリ40b、記録媒体40fや40h、又は図示しないRead Only Memory(ROM)等に格納されたプログラムを実行することにより、管理部4における種々の機能を実現することができる。メモリ40bは、種々のデータやプログラムを一時的に格納する記憶装置である。CPU40aは、プログラムを実行する際に、メモリ40bにデータやプログラムを格納し展開する。メモリ40bとしては、例えばRAM等の揮発性メモリが挙げられる。The operation of the

The

記憶部40cは、種々のデータやプログラム等を格納するハードウェアである。記憶部40cとしては、例えばHard Disk Drive(HDD)等の磁気ディスク装置、Solid State Drive(SSD)等の半導体ドライブ装置、フラッシュメモリ等の不揮発性メモリ等の各種デバイスが挙げられる。インタフェース部40dは、有線又は無線による、ネットワークや他の装置との接続及び通信の制御等を行なう。入出力部40eは、例えばマウスやキーボード等の入力装置、及びディスプレイやプリンタ等の出力装置の少なくとも一方を含んでよい。入出力部40eは、入力装置により管理部4のオペレータ(管理者)等の操作による動作命令を受け付ける一方、管理部4による動作結果を出力装置に表示(出力)することができる。

The

記録媒体40fは、例えばフラッシュメモリやROM等の記憶装置であり、種々のデータやプログラムを記録することができる。読取部40gは、コンピュータ読取可能な記録媒体40hに記録されたデータやプログラムを読み出す装置である。記録媒体40f及び40hの少なくとも一方には、本実施形態に係る管理部4の各種機能の全部もしくは一部を実現する管理(更新)プログラムが格納されてもよい。例えば、CPU40aは、記録媒体40fから読み出したプログラム、又は、読取部40gを介して記録媒体40hから読み出したプログラムを、メモリ40b等の記憶装置に展開して実行することができる。これにより、管理部4としてのコンピュータ(CPU40a,情報処理装置,各種端末を含む)は、本実施形態に係る管理部4の機能を実現することができる。

The

なお、記録媒体40hとしては、例えばフレキシブルディスク、Compact Disc(CD)、Digital Versatile Disc(DVD)、ブルーレイディスク等の光ディスクや、Universal Serial Bus(USB)メモリ等のフラッシュメモリが挙げられる。なお、CDとしては、CD−ROM、CD-Recordable(CD−R)、CD-Rewritable(CD−RW)等が挙げられる。また、DVDとしては、DVD−ROM、DVD−RAM、DVD−R、DVD−RW、DVD+R、DVD+RW等が挙げられる。

Examples of the

なお、上述した各ブロック40a〜40g間はバスで相互に通信可能に接続される。また、管理部4の上述したハードウェア構成例は例示である。例えば、管理部4は、図8に示すハードウェアの少なくとも一部を情報処理システム1と共用してもよい。一例として、管理部4は、CPU40aやメモリ40bに代えて、情報処理システム1の装置3の一例としてのCPUやメモリを用いてもよい。また、管理部4及び情報処理システム1内でのハードウェアの増減や分割、任意の組み合わせでの統合等は、適宜行なわれてもよい。

The

〔1−6〕情報処理システムの動作例

次に、図9〜図11を参照して、一実施形態の一例としての情報処理システム1の動作例を説明する。

図9は、図5に示すクロスバ2の受付ポート5における再送処理の動作例を説明するフローチャートであり、図10は、図5に示すクロスバ2の入力ポート6における再送処理の動作例を説明するフローチャートである。図11は、図5に示す管理部4におけるルーティングテーブル53の更新処理の動作例を説明するフローチャートである。[1-6] Operation Example of Information Processing System Next, an operation example of the

FIG. 9 is a flowchart for explaining an operation example of the retransmission processing in the

〔1−6−1〕受付ポートにおける再送処理の動作例

はじめに、図9を参照して、受付ポート5における再送処理について説明する。

受付ポート5により出力ポート8から入力ポート6経由で出力ポート閉塞信号が受信されると(ステップS1)、フレーム送信判定回路54により、受付キュー51から入力ポート6へフレームが出力中か否かが判断される(ステップS2)。フレーム出力中である場合(ステップS2のYesルート)、フレーム送信判定回路54により、入力ポート6へ出力中のフレームが最後まで出力されたか否かが判断される(ステップS3)。出力中のフレームが最後まで出力されていない場合(ステップS3のNoルート)、フレーム送信判定回路54により、所定クロック(例えば数クロック;所定時間)待機され(ステップS4)、処理がステップS3に移行する。[1-6-1] Example of Retransmission Process at Reception Port First, the retransmission process at the

When the

一方、ステップS2においてフレーム出力中ではない場合(ステップS2のNoルート)、又は、ステップS3において出力中のフレームが最後まで出力された場合(ステップS3のYesルート)、処理がステップS5に移行する。ステップS5では、フレーム送信判定回路54により、入力ポート6へのフレーム送信が停止され、入力ポート6に対して、入力ポート6へのフレーム送信を停止したことを示すフレーム送信停止信号が送信される。

On the other hand, if the frame is not being output in step S2 (No route in step S2), or if the frame being output has been output to the end in step S3 (Yes route in step S3), the process proceeds to step S5. . In step S5, the frame

次いで、受付ポート5により入力ポート6からフレーム送信を再開することを示すフレーム送信再開指示信号が受信されると、フレーム送信判定回路54により、受付キュー51から入力ポート6へのフレーム送信が再開され(ステップS6)、処理が終了する。

〔1−6−2〕入力ポートにおける再送処理の動作例

次に、図10を参照して、入力ポート6における再送処理について説明する。Next, when the frame transmission restart instruction signal indicating that frame reception is resumed from the

[1-6-2] Operation Example of Retransmission Process at Input Port Next, the retransmission process at the

なお、前提として、再送ステートマシン63が管理する状態が、出力ポート8でエラーや混雑が検出されていない通常状態(レジスタ値“3'b000”)であるものとする。また、以下の図10のフローチャートの制御は、複数の再送ステートマシン63のうちの、閉塞ポート8に対応する入力キュー61を制御する(閉塞ポート8に対応する)再送ステートマシン63により実行されるものとする。つまり、代替ポート8宛ての入力キュー61を制御する(代替ポート8に対応する)再送ステートマシン63は、図10に示すように状態を変化させなくてよい。

It is assumed that the state managed by the

入力ポート6により出力ポート8から出力ポート閉塞信号が受信されると(ステップS11)、閉塞ポート8に対応する再送ステートマシン63の状態が、対入力ポートフレーム送信停止移行状態(レジスタ値“3'b001”)に遷移する。また、入力ポート6により、受付ポート5からフレームの送信を停止したことを示す信号が受信される(ステップS12)。ステップS12の処理が完了すると、閉塞ポート8に対応する再送ステートマシン63の状態が、代替ポート宛て入力キュー内フレーム送信状態(レジスタ値“3'b010”)に遷移する。

When the output port block signal is received from the

次に、入力ポート6により、閉塞ポート8の代替ポート8宛ての入力キュー61に滞留しているフレームが、当該フレームの転送先に対応する出力ポート8へ送信される(ステップS13)。ステップS13の処理は、代替ポート8に対応する再送ステートマシン63によるセレクタ62の制御により行なわれる。

なお、ステップS13において、閉塞ポート8に対応する再送ステートマシン63は、代替ポート8宛ての入力キュー61に滞留する全フレームの送信が完了したことを検知することができる。或いは、閉塞ポート8に対応する再送ステートマシン63は、代替ポート8に対応する再送ステートマシン63から全フレームの送信が完了したことを通知されてもよい。ステップS13の処理が完了すると、閉塞ポート8に対応する再送ステートマシン63の状態が、閉塞ポート宛て入力キュー内フレーム送信状態(レジスタ値“3'b011”)に遷移する。なお、フレームごとに代替ポート8が設定される場合等、代替ポート8に対応する再送ステートマシン63が複数存在する場合、全代替ポート8について全フレームの送信が完了してから、閉塞ポート8に対応する再送ステートマシン63の状態が遷移する。Next, the frame staying in the

In step S13, the

次いで、閉塞ポート8に対応する再送ステートマシン63により、セレクタ62が制御され、閉塞ポート8宛ての入力キュー61に滞留しているフレームが迂回路(転送先)に対応する出力ポート8へ送信される(ステップS14)。

なお、ステップS13及びS14において、再送ステートマシン63は、フレームの喪失を防ぐため、送信する全フレームが該当出力ポート8から対向LSIへ正常に到達したことを確認してから、入力キュー61内の送信済フレームを解放することが好ましい。Next, the

In steps S13 and S14, the

ステップS14の処理が実行されると、閉塞ポート8に対応する再送ステートマシン63の状態がルーティングテーブル更新可能状態(レジスタ値“3'b100”)に遷移する。

そして、再送ステートマシン63により、ステップS13及びS14までの処理が完了したことが、ルーティングテーブル更新可能通知信号により管理部4へ通知される(ステップS15)。管理部4では、閉塞ポート8が再利用されない場合、ルーティングテーブル53が更新される(ステップS15)。When the process of step S14 is executed, the state of the

Then, the

また、再送ステートマシン63により、管理部4から出力ポート切り替え完了信号が受信されると(ステップS16)、再送ステートマシン63により、新たな出力ポート8が再利用予定の閉塞中の出力ポート8であるか否かが判断される(ステップS17)。新たな出力ポート8が再利用予定である場合(ステップS17のYesルート)、再送ステートマシン63により、出力ポート閉塞解除信号が閉塞中の出力ポート8へ送信されて閉塞状態が解除され(ステップS18)、処理がステップS19に移行する。つまり、再送ステートマシン63は、ルーティングテーブル更新可能状態において、故障装置の動的交換や混雑解消などの理由により、閉塞ポート8を再利用する場合、出力ポート8の閉塞状態を解除する。

When the

なお、再送ステートマシン63は、出力ポート8の故障又は混雑等により転送経路を変更したい場合、ルーティングテーブル53を更新するために、ステップS15においてルーティングテーブル更新可能通知信号を送信することができる。一方、再送ステートマシン63は、閉塞ポート8を再利用する場合、ルーティングテーブル更新可能通知信号を送信しなくてもよい(ステップS15及びS16を省略できる)が、管理部4に再利用の有無を判断させる場合には、当該信号を送信してもよい。

Note that the

ステップS19では、再送ステートマシン63により、受付ポート5へフレーム送信再開指示信号が送信されて、入力キュー61から出力ポート8へのフレーム送信(通常制御)が再開され、処理が終了する。なお、新たな出力ポート8が再利用予定ではない場合(ステップS17のNoルート)、処理がステップS19に移行する。ステップS19の処理が完了すると、閉塞ポート8に対応する再送ステートマシン63の状態が、通常状態(レジスタ値“3'b000”)に遷移する。

In step S19, the

〔1−6−3〕管理部におけるルーティングテーブルの更新処理の動作例

次に、図11を参照して、管理部4におけるルーティングテーブル53の更新処理について説明する。

なお、前提として、図11に例示するフローチャートの制御は、閉塞ポート8を再利用しない場合に実行されるものであり、管理部4が出力ポート閉塞信号に基づき閉塞ポート8を再利用すると判断した場合には実行されない。[1-6-3] Operation Example of Routing Table Update Processing in Management Unit Next, the update processing of the routing table 53 in the

As a premise, the control of the flowchart illustrated in FIG. 11 is executed when the blocked

管理部4により出力ポート8から出力ポート閉塞信号が受信されると、管理情報42における迂回用出力ポートのうちの閉塞ポート8に対応するビットが有効から無効に更新される(ステップS21)。

次いで、管理部4により、再送ステートマシン63からルーティングテーブル更新可能通知信号が受信されると(ステップS22)、管理部4により、ルーティングテーブル53を更新可能か否かが判断される(ステップS23)。例えば、管理部4は、管理情報42を参照し、閉塞ポート8が通常用出力ポートに設定されているエントリに、迂回用出力ポートが有効に設定されているか否かを判断し、迂回用出力ポートが有効に設定されている場合に更新可能と判断することができる。When the

Next, when the

ステップS23において、ルーティングテーブル53を更新可能と判断された場合(ステップS23のYesルート)、管理部4により、管理情報42が更新される(ステップS24)。例えば、管理部4は、管理情報42における閉塞ポート8が通常用出力ポートに設定されているエントリの通常用出力ポートの番号を、第n(nは1以上の整数)候補の(例えば第1候補)の迂回用出力ポートの番号で上書きする。これにより、管理部4は、管理情報42を更新することができる。なお、管理部4は、複数の迂回用出力ポートが存在する場合、第2〜第n候補の順位をそれぞれ繰り上げ(シフトさせ)、第1〜第(n−1)候補に変更することができる。また、管理部4は、第n候補が第(n−1)候補に繰り上がるため、第n候補に設定された迂回用出力ポートを無効に設定することができる。

If it is determined in step S23 that the routing table 53 can be updated (Yes route in step S23), the

そして、管理部4により、ステップS21及びS24で更新した管理情報42が用いられ、クロスバ2のルーティングテーブル53が更新される(ステップS25)。また、ルーティングテーブル53の更新が完了すると、管理部4により、再送ステートマシン63へ出力ポート切り替え完了信号が送信され(ステップS26)、処理が終了する。

一方、ステップS23において、ルーティングテーブル53を更新不可能と判断された場合(ステップS23のNoルート)、管理部4により、クロスバ2(例えば再送ステートマシン63)へ致命的なエラーが通知され(ステップS27)、処理が終了する。なお、ルーティングテーブル53の更新が不可能な場合としては、例えば、閉塞ポート8が通常用出力ポートに設定されているエントリに、迂回用出力ポートが設定されていない、又は無効に設定されている場合等が挙げられる。管理部4から致命的なエラーを通知されると、クロスバ2又は情報処理システム1は、システム全体の動作を停止させてもよい。Then, the management information updated in steps S21 and S24 is used by the

On the other hand, when it is determined in step S23 that the routing table 53 cannot be updated (No route in step S23), the

〔1−7〕実施例

次に、図12〜図16を参照して、情報処理システム1(特にクロスバ2)の実施例を説明する。

図12は、図5に示す受付ポート5の構成の実施例を示す図であり、図13は、図5に示す入力ポート6の構成の実施例を示す図である。図14は、図13に示す入力ポートにおける入力キュー61の制御手法の一例を説明する図であり、図15は、図13に示す入力ポート6におけるタイミングチャートの一例を示す図である。図16は、図5に示す出力ポート8の構成の実施例を示す図である。[1-7] Embodiment Next, an embodiment of the information processing system 1 (particularly the crossbar 2) will be described with reference to FIGS.

FIG. 12 is a diagram showing an example of the configuration of the

なお、以下の説明では、受付ポート5、入力ポート6、出力ポート8、及び接続部9の構成をそれぞれ1つ図示するが、他の受付ポート5、入力ポート6、出力ポート8、及び接続部9についても同様である。

〔1−7−1〕受付ポートの実施例

はじめに、図12を参照して、受付ポート5の実施例について説明する。In the following description, one configuration of each of the

[1-7-1] Example of Accepting Port First, an example of the accepting

図12に示すように、受付ポート5は、図5に示す受付キュー51、保持部52、フレーム送信判定回路54をそなえるとともに、クレジット管理回路55及びリード制御回路56をそなえることができる。特に言及しない限り、受付キュー51、保持部52、及びフレーム送信判定回路54の基本的な機能は図5に示すものと同様であるため、重複した説明を省略する。

As shown in FIG. 12, the

クレジット管理回路55は、入力ポート6の入力キュー61に空きがあるか否か、つまり受付キュー51から入力キュー61へのフレームの送信が可能か否かを判定する回路である。なお、以下の説明において、クレジットは、送信先のキュー(例えば入力キュー61)に格納されたデータが出力されてキューに空きができたことを示す信号とすることができる。クレジットの単位は、フレームごとに設定されてもよいし、フレームをいくつかのクロックで分割した単位に設定されてもよく、また、それらの併用であってもよい。

The

クレジット管理回路55は、例えば、カウンタ等の回路をそなえ、入力ポート6から入力ポート用クレジットA1を受信すると当該回路のカウント値を加算(又は減算)し、受付キュー51からフレームをリードしたらカウント値を減算(又は加算)する。クレジット管理回路55は、カウント値が正(又は入力キュー61がFullでない)ならば、フレームを入力ポート6へ送信することが可能であると判断することができる。そして、クレジット管理回路55は、判断結果を、入力ポート用クレジット管理情報A2としてフレーム送信判定回路54へ伝達する。

For example, the

フレーム送信判定回路54は、図5に示すものと基本的に同様の機能を有する回路であり、図9に示すフローチャートの少なくとも一部を実現する。フレーム送信判定回路54は、下記(A)及び(B)の双方の条件を満たす場合に、リード制御回路56へフレーム送信許可A3を与える。

(A)入力ポート用クレジット管理情報A2がフレーム送信可能を示す場合。The frame

(A) When the input port credit management information A2 indicates that frame transmission is possible.

(B)接続先のいずれの出力ポート8も閉塞していない、又は、いずれかの出力ポート閉塞信号A4を受信したときにフレームを入力ポート6へ出力中で当該フレームの最後尾までの送信が未完了である場合。

なお、上記(B)において、出力中のデータがフレームの最後尾であるか否かは、後述する受付キュー51からのフレーム送信管理情報A7により判断される。(B) None of the

In (B) above, whether or not the data being output is the end of the frame is determined by frame transmission management information A7 from the

フレーム送信判定回路54は、図9に示すフローチャートに従って、入力ポート6に対して入力ポート6へのフレーム送信停止信号A5を送信する。入力ポート6が管理部4から出力ポート切り替え完了信号B10(図13参照)を受信し、この受信に応じて入力ポート6からフレーム送信再開指示信号A6を受信したら、フレーム送信判定回路54は、停止していたフレーム送信を再開する。

The frame

リード制御回路56は、フレーム送信判定回路54からフレーム送信許可A3を与えられ、且つ、受付キュー51にフレームが格納されている場合、受付キュー51からのリード動作を制御し、データパスを通じて入力ポート6へ出力する。

保持部52は、ルーティングテーブル53を保持するものであり、図5に示すものと基本的に同様の記憶装置である。ルーティングテーブル53は、送信先ID A8から送信先出力ポート(通常用出力ポート;通常用出力ポートに上書きされた迂回用出力ポートを含む)A9と第1候補の迂回用出力ポートA10とが導き出されるように登録されるテーブルである(図6参照)。送信先ID A8は、受付キュー51から出力されるフレームに含まれる(又はフレームとともに出力される)情報であり、データパス又は他の配線を介してルーティングテーブル53に供給される。The

The holding

〔1−7−2〕入力ポートの実施例

次に、図13〜図15を参照して、入力ポート6の実施例について説明する。

図13に示すように、入力ポート6は、図5に示す入力キュー61、セレクタ62、再送ステートマシン63、及び迂回用出力ポート管理回路64をそなえるとともに、以下の回路をさらにそなえることができる。つまり、入力ポート6は、制御信号生成回路65、クレジット生成回路66、及びエンコーダ67をそなえるとともに、出力ポート8ごとに入力キュー制御部60をそなえることができる。なお、便宜上、図13に示すように、入力キュー制御部60を入力キュー制御部A〜Cのいずれかで特定する場合がある。特に言及しない限り、入力キュー61、セレクタ62、再送ステートマシン63、及び迂回用出力ポート管理回路64の基本的な機能は図5に示すものと同様であるため、重複した説明を省略する。[1-7-2] Embodiment of Input Port Next, an embodiment of the

As shown in FIG. 13, the

制御信号生成回路65は、フレームを入力キュー制御部60へ振り分けるため、例えばフレーム送信制御情報A11から転送先出力ポート別のフレーム送信制御信号B1を生成する回路である。例えば、制御信号生成回路65は、データパスを通過するフレームのvalid等をフレーム送信制御情報A11として取得する。そして、制御信号生成回路65は、当該フレームが入力される入力キュー制御部60に対して、フレームが入力されることを示すフレーム送信制御信号B1を出力する。

The control

クレジット生成回路66は、いずれの出力ポート8宛てのフレームが到来しても入力キュー61に格納できる状態になったときに、受付ポート5へ入力ポート用クレジットA1を送信する回路である。つまり、クレジット生成回路66は、全ての入力キュー61に空きができたときに、受付ポート5へ入力ポート用クレジットA1を送信する。クレジット生成回路66は、例えば、カウンタ等の回路をそなえる。クレジット生成回路66は、フレーム送信制御情報A11に基づき入力ポート6にフレームが入力されたことを検出すると当該回路のカウント値を加算(又は減算)し、入力ポート用クレジットA1を送信したらカウント値を減算(又は加算)する。また、クレジット生成回路66は、当該回路のカウント値が転送先出力ポート別の各キュー再送エントリ数B2の最大値(又は最小値)より大きく(又は小さく)なった場合に、入力ポート用クレジットA1を送信する。

The

入力キュー制御部60は、フレームの転送先となる出力ポート8ごとに設けられ、各々が、上述した入力キュー61、再送ステートマシン63、及び迂回用出力ポート管理回路64をそなえるとともに以下の回路601〜609をそなえることができる。

ライト制御回路601は、入力キュー61へのライト制御を行なう。ライト制御回路601は、例えば、制御信号生成回路65からのフレーム送信制御信号B1を入力されると、入力キュー61における次にライトされるエントリをライトポインタで指示する。なお、ライト動作は上述のようにクレジット管理されるため、入力キュー61がオーバーフローする可能性は低い。The input

The

リード制御回路602は、入力キュー61からのリード制御を行なう。リード制御回路602は、入力キュー61における次にリードされるエントリをリードポインタで指示する。例えば、入力キュー61にフレームが格納され(キュー保持エントリ数管理回路604の値が正)、送信先出力ポート8の出力ポート用クレジット管理情報B8がフレーム送信可能を示す場合、リード制御回路602はフレームをリード可能となる。送信先出力ポート8は通常用出力ポート8のほかに迂回用出力ポート8である場合もあるため、リード制御回路602は、実際にフレームを送信する出力ポート8に対応する出力ポート用クレジット管理情報B8を選択して、リード可能か否かを判断する。

The

再送リードポインタ603は、フレームを送信した出力ポート8から入力キュー61を解放することを示すキューフレーム解放信号B4及び解放フレーム長B5を受信すると、解放フレーム長B5の分だけポインタを加算する。再送リードポインタ603は、リード制御回路602内のリードポインタを追いかけるように更新される。また、再送リードポインタ603は、キューフレーム解放信号B4とともに、入力キュー制御部60の番号を示す入力ポート制御部番号B6を受信することができる。例えば、再送リードポインタ603は、入力ポート制御部番号B6が自身の制御部番号と一致したら、キューフレーム解放信号B4が自身の制御部60が送信したフレームに関する解放信号であると判断し、ポインタの更新を実行することができる。また、再送リードポインタ603は、出力ポート閉塞信号B7を受信すると、ポインタの値をリード制御回路602のリードポインタに上書きして、リード制御回路602を更新することができる。

When the retransmission read

キュー保持エントリ数管理回路604は、入力キュー61に保持されているエントリ数を管理する回路である。キュー保持エントリ数管理回路604は、例えば、カウンタ等の回路をそなえ、入力キュー61にライトされたら当該回路のカウント値を加算し、入力キュー61からリードされたらカウント値を減算することができる。

キュー再送エントリ数管理回路605は、入力キュー61で未だ再送される可能性のあるエントリ数を管理する回路である。キュー再送エントリ数管理回路605は、当該エントリ数(キュー再送エントリ数B2)を、クレジット生成回路66及び再送ステートマシン63へ出力することができる。キュー再送エントリ数管理回路605は、例えば、カウンタ等の回路をそなえ、入力キュー61にライトされたら当該回路のカウント値を加算することができる。また、キュー再送エントリ数管理回路605は、フレームを送信した出力ポート8からキューフレーム解放信号B4及び解放フレーム長B5を受信すると、解放フレーム長B5の分だけカウント値を減算することができる。The queue holding entry

The queue retransmission entry

キュー再送エントリ数管理回路605は、例えば、入力ポート制御部番号B6が自身の制御部番号と一致したら、キューフレーム解放信号B4が自身の制御部60が送信したフレームに関する解放信号であると判断し、回路のカウント値の更新を実行する。また、キュー再送エントリ数管理回路605は、出力ポート閉塞信号B7を受信すると、回路のカウント値をキュー保持エントリ数管理回路604に上書きして、キュー保持エントリ数管理回路604を更新することができる。

For example, when the input port control unit number B6 matches its own control unit number, the queue retransmission entry

ここで、図14を参照して、入力キュー61の制御に用いられるライトポインタ、リードポインタ、及び再送リードポインタと、キュー保持エントリ数管理回路604及びキュー再送エントリ数管理回路605との関係について説明する。

図14に例示するように、運用中のクロスバ2内の入力キュー61は、空白のエントリ、データ(フレームの一部)を保持するエントリ、並びに、データを入力キュー61から送信済み且つ対向LSIまで正常に到達したことの確認待ちであるエントリを含み得る。空白のエントリはライト制御回路601のライトポインタにより示され、データを保持するエントリは、リード制御回路602のリードポインタにより示され、データを送信済み且つ到達確認待ちのエントリは、再送リードポインタ603により示される。Here, with reference to FIG. 14, the relationship between the write pointer, the read pointer, and the retransmission read pointer used for controlling the

As illustrated in FIG. 14, the

各ポインタは、基本的に入力キュー61の先頭から末尾に向かって動き、末尾に到達すると先頭に戻る。なお、リードポインタは、入力キュー制御部60が出力ポート閉塞信号を受信した場合等に、再送リードポインタ603の値に戻されることがあり、この場合、リードポインタは逆方向(末尾から先頭)に動く。

キュー保持エントリ数管理回路604は、入力キュー61における、データを保持するエントリの数を保持するため、図14に示す例では、キュー保持エントリ数管理回路604のカウント値は1を示す。キュー再送エントリ数管理回路605は、入力キュー61における、データを保持するエントリの数と、データを送信済み且つ到達確認待ちのエントリの数との合計のエントリ数を保持する。従って、図14に示す例では、キュー再送エントリ数管理回路605のカウント値は2を示す。Each pointer basically moves from the head of the

Since the queue holding entry

図13の説明に戻り、出力ポート用クレジット管理回路606は、出力ポート8の出力キュー81に空きがあるか否か、つまり入力キュー61からのフレームの送信が可能か否かを判定する回路である。出力ポート用クレジット管理回路606は、例えば、カウンタ等の回路をそなえ、出力ポート用クレジットB3を受信したら当該回路のカウント値を加算(又は減算)し、入力キュー61からリードされたらカウント値を減算(または加算)することができる。出力ポート用クレジット管理回路606は、カウント値が正(又は出力キュー81がFullでない)ならば、フレームを出力ポート8へ送信することが可能であると判断することができる。そして、出力ポート用クレジット管理回路606は、判断結果を、出力ポート用クレジット管理情報B8としてリード制御回路602へ伝達することができる。

Returning to the description of FIG. 13, the output port

迂回用出力ポート管理回路64は、フレームごとに迂回路を設定する場合、フレームを入力キュー61にライトする度に、ルーティングテーブル53からの迂回用出力ポートA10の情報を保持する回路である。迂回用出力ポート管理回路64は、フレームを送信した出力ポート8からキューフレーム解放信号B4を受信すると、格納する古い迂回用出力ポートA10の情報を解放することができる。

The detour output

再送ステートマシン63は、図5に示すものと基本的に同様の機能を有する回路であり、図10に示すフローチャートの少なくとも一部を実現する。図13に示すように、再送ステートマシン63は、上述した出力ポート閉塞信号B7、入力ポート6へのフレーム送信停止信号A5、出力ポート切り替え完了信号B10、キュー再送エントリ数B2等を入力される。さらに、再送ステートマシン63は、受付ポート5へフレーム送信再開指示信号A6を、管理部4へルーティングテーブル更新可能通知信号B9を、出力ポート8へ出力ポート閉塞解除信号B11を、それぞれ出力する。

The

選択信号生成回路607は、再送ステートマシン63及び迂回用出力ポート管理回路64からの情報に基づき、出力ポート8宛てのデータパス、セレクタ608、及びセレクタ609をそれぞれ選択する選択信号を生成する回路である。ここで、セレクタ608は、入力キュー制御部A〜C内のいずれかのキュー再送エントリ数管理回路605からのキュー再送エントリ数B2を選択し、再送ステートマシン63へ出力することで再送するエントリ数を通知するセレクタである。また、セレクタ609は、入力キュー制御部A〜C内のいずれかの出力ポート用クレジット管理回路606からの出力ポート用クレジット管理情報B8を選択し、リード制御回路602へ出力するセレクタである。

The selection

なお、出力ポート8でエラーや混雑等が検出された場合、閉塞ポート8に対応する再送ステートマシン63は、セレクタ608により代替ポート8に対応するキュー再送エントリ数B2を参照することができる。これにより、閉塞ポート8に対応する再送ステートマシン63は、代替ポート8宛ての入力キュー61に滞留する全フレームの送信が完了したこと(例えばキュー再送エントリ数B2の値が“0”になったこと)を検知することができる。

If an error or congestion is detected at the

選択信号生成回路607は、通常動作(通常状態)で接続する通常用出力ポート8以外の出力ポート8を選択する選択信号を出力する。例えば、選択信号生成回路607からセレクタ62への配線は、入力ポート6に接続される出力ポート8の数より1少ない本数である。一例として、図13に示すように入力ポート6に接続される出力ポート8が3つの場合、セレクタ62への選択信号の配線は2本となる。選択信号生成回路607からの選択信号は、エンコーダ67によりエンコードが行なわれ、出力ポート8宛てに入力ポート制御部番号B12として送信される。ここで送信される入力ポート制御部番号B12は、出力ポート8から入力ポート制御部番号B6として送信され、入力キュー制御部60において、自身の制御部60の入力キュー61を解放するか否かの判断に使用される。

The selection

なお、図13において、セレクタ62の入力側の白丸は、選択信号との交点を示す。セレクタ62は、例えば、アサートされた選択信号に対応する入力側のデータパスを選択して、フレームを出力側のデータパスへ出力することができる。また、セレクタ62は、例えばアサートされた選択信号がない場合には、選択信号と接続されていない残り1つの入力側のデータパスを選択して、フレームを出力側のデータパスへ出力することができる。

In FIG. 13, a white circle on the input side of the

〔1−7−2−1〕入力ポートの動作例

ここで、図15を参照して、図13に示す入力ポート6における動作例を説明する。

なお、図15は、同一の入力ポート6内の、閉塞ポート8に対応する入力キュー制御部60、代替ポート8のうちの1つに対応する入力キュー制御部60における各信号のタイミングチャートの一例を示す。以下、出力ポート用クレジット管理回路606は、出力ポート用クレジットを受信するとカウント値を加算するものとして説明する。[1-7-2-1] Operation Example of Input Port Here, an operation example of the

FIG. 15 is an example of a timing chart of each signal in the input

図15に示すように、タイミングt0では、ある出力ポート(後の閉塞ポート)8に対応する再送ステートマシン63の状態は“3'b000”である。ここで、当該出力ポート8でエラー又は混雑が検出され、出力ポート閉塞信号B7が入力ポート6に入力されたとする。このとき、閉塞ポート8に対応する再送ステートマシン63の状態は、タイミングt1で“3b'001”に遷移する。また、キュー保持エントリ数管理回路604のカウント値“1”は、キュー再送エントリ数管理回路605のカウント値“2”に上書きされる。さらに、出力ポート用クレジット管理回路606のカウント値は、閉塞ポート8への送信を停止するために“3”から“0”にリセットされる。

As shown in FIG. 15, at the timing t0, the state of the

次いで、入力ポート6に受付ポート5からの入力ポート6へのフレーム送信停止信号A5が入力されると、閉塞ポート8に対応する再送ステートマシン63の状態は、タイミングt2で“3b'010”に遷移する。このとき、代替ポート8に対応する入力キュー61内の全フレームの出力が開始され、タイミングt3において、代替ポート8に対応するキュー保持エントリ数管理回路604及び出力ポート用クレジット管理回路606の各カウント値が減算される。また、タイミングt4において、対向LSIへのフレームの到達確認のためにタイミングt3よりも遅れて、代替ポート8に対応するキュー再送エントリ数管理回路605のカウント値が減算される。

Next, when the frame transmission stop signal A5 from the

代替ポート8に対応するキュー再送エントリ数管理回路605のカウント値が“0”になると、閉塞ポート8に対応する再送ステートマシン63の状態は、タイミングt5で“3b'011”に遷移する。このとき、閉塞ポート8に対応する入力キュー61内の全フレームの出力が開始され、タイミングt6において、閉塞ポート8に対応するキュー保持エントリ数管理回路604のカウント値が減算される。また、このとき、閉塞ポート8に対応する入力キュー61からのフレームは、代替ポート8に出力されるため、代替ポート8に対応する出力ポート用クレジット管理回路606のカウント値も減算される。さらに、タイミングt7において、対向LSIへのフレームの到達確認のためにタイミングt6よりも遅れて、閉塞ポート8に対応するキュー再送エントリ数管理回路605のカウント値が減算される。

When the count value of the queue retransmission entry

閉塞ポート8に対応するキュー再送エントリ数管理回路605のカウント値が“0”になると、閉塞ポート8に対応する再送ステートマシン63の状態は、タイミングt8で“3b'100”に遷移する。このとき、当該再送ステートマシン63は、管理部4へルーティングテーブル更新可能通知信号B9を送信する。また、再送ステートマシン63は、管理部4から出力ポート切り替え完了信号を受信すると、受付ポート5へフレーム送信再開指示信号A6を送信する。そして、閉塞ポート8に対応する再送ステートマシン63の状態はタイミングt9で“3b'000”に遷移し、通常状態に戻る。

When the count value of the queue retransmission entry

〔1−7−3〕出力ポートの実施例

次いで、図16を参照して、出力ポート8の実施例について説明する。

図16に示すように、出力ポート8は、図5に示す出力キュー81、及びセレクタ82をそなえるとともに、以下の回路をさらにそなえることができる。つまり、出力ポート8は、キューリードリクエスト調停回路83、フレーム送信可否判定回路84、フレーム到達確認管理回路85、及び出力ポート閉塞判定回路86をそなえるとともに、入力ポート6ごとに出力キュー制御部80をそなえることができる。なお、便宜上、図16に示すように、出力キュー制御部80を出力キュー制御部A〜Cのいずれかで特定する場合がある。特に言及しない限り、出力キュー81及びセレクタ82の基本的な機能は図5に示すものと同様であるため、重複した説明を省略する。[1-7-3] Embodiment of Output Port Next, an embodiment of the

As shown in FIG. 16, the

出力キュー制御部80は、フレームの転送元となる入力ポート6ごとに設けられ、各々が、上述した出力キュー81をそなえるとともに以下の回路801〜805をそなえることができる。

ライト制御回路801は、出力キュー81へのライト制御を行なう。ライト制御回路801は、例えば、データパスを通過するフレームに関するフレーム送信制御情報C1を入力されると、出力キュー81における次にライトされるエントリをライトポインタで指示する。なお、ライト動作は上述のようにクレジット管理されるため、出力キュー81がオーバーフローする可能性は低い。The output

The

リード制御回路802は、出力キュー81からのリード制御を行なう。リード制御回路802は、出力キュー81における次にリードするエントリをリードポインタで指示する。例えば、出力キュー81にフレームが格納され(キュー保持エントリ数管理回路803の値が正)、且つキューリードリクエスト調停回路83からキューリードリクエスト獲得信号C5を受信した場合、リード制御回路802は、フレームをリード可能となる。

The

キュー保持エントリ数管理回路803は、出力キュー81に保持されているエントリ数を管理する回路である。キュー保持エントリ数管理回路803は、例えば、カウンタ等の回路をそなえ、出力キュー81にライトされたら当該回路のカウント値を加算し、出力キュー81からリードされたらカウント値を減算することができる。

キューリードリクエスト生成回路804は、出力キュー81からフレームをリード可能であることをキューリードリクエスト調停回路83へ伝達するためのキューリードリクエスト信号C2を生成する回路である。キューリードリクエスト生成回路804は、例えば、出力キュー81にフレームが格納されており、且つ対向LSIとの接続部9へ送信するデータパスのセレクタ82が何も選択していない場合に、キューリードリクエスト信号C2を生成することができる。なお、キューリードリクエスト生成回路804は、キュー保持エントリ数管理回路803の値が正である場合に、出力キュー81にフレームが格納されていると判断することができる。また、キューリードリクエスト信号C2には、フレーム長C3が付加されてよく、或いは含まれてもよい。The queue holding entry

The queue read

出力ポート用クレジット生成回路805は、出力キュー81に空きがある状態になった場合に、入力ポート6へ出力ポート用クレジットB3を送信する回路である。出力ポート用クレジット生成回路805は、例えば、カウンタ等の回路をそなえ、出力ポート8にフレームが入力されたら当該回路のカウント値を加算(又は減算)し、出力ポート用クレジットB3を送信したらカウント値を減算(又は加算)することができる。

The output port

キューリードリクエスト調停回路83は、各出力キュー制御部80からキューリードリクエストC2及びフレーム長C3を受信し、フレーム送信可否判定回路84からフレーム送信許可C4が出力されると、当該リクエストを調停する。そして、キューリードリクエスト調停回路83は、調停で勝利した制御部80へキューリードリクエスト獲得信号C5を送信し、調停で勝利した制御部80をデータパスのセレクタ82に選択させる入力ポート選択信号C6を出力する回路である。入力ポート選択信号C6は、調停で勝利した制御部80から送信フレーム長C3のデータが出力される間、セレクタ82が勝利した制御部80を選択し続けるように出力されることが好ましい。

The queue read

フレーム送信可否判定回路84は、接続部9へのフレームの送信が可能か否かを判定し、フレームの送信が可能であると判定した場合にフレーム送信許可C4をキューリードリクエスト調停回路83へ出力する回路である。フレーム送信可否判定回路84は、例えば対向LSI等のフレームの転送先の状態に関するフレーム送信可否判定条件に基づいて、判定及びフレーム送信許可の出力を行なうことができる。フレーム送信可否判定回路84の処理は、クレジット管理や、対向LSIの負荷状況等に基づくビジー(busy)管理等、種々の手法により実現することができる。また、フレーム送信可否判定回路84は、フレーム送信を抑止すると判定した場合、出力ポート8からのフレームの送信停止を指示できることが好ましい。

The frame transmission

フレーム到達確認管理回路85は、出力ポート8に接続される対向LSIへのフレームが到達したか否かを確認するための回路である。フレーム到達確認管理回路85は、例えば、キューリードリクエスト調停回路83からのキューリードリクエスト獲得信号C5が有効(例えば“1”)のときに、出力キュー81から送信される情報C7,C8をフレームが送信された順番に記憶することができる。情報C7,C8としては、入力ポート6の情報、リードしたフレームのフレーム長C7、及び入力ポート制御部番号C8等のフレームに関する情報とすることができる。また、フレーム到達確認管理回路85は、対向LSIからのフレーム正常到達確認信号C9を受信すると、記憶する情報C7,C8を古い方から順に解放することができる。また、フレーム到達確認管理回路85は、情報C7,C8に基づいて、入力ポート6宛てに、キューフレーム解放信号B4、フレーム長B5、及び入力ポート制御部番号B6を送信することができる。

The frame arrival

出力ポート閉塞判定回路86は、出力ポート8が、出力ポート8から対向LSIまでの間に故障又は混雑が発生していることを判定して出力ポート8を閉塞する。また、出力ポート閉塞判定回路86は、出力ポート8を閉塞すると、入力ポート6宛てに出力ポート閉塞信号B7を、管理部4宛てに出力ポート閉塞信号C10を、それぞれ送信する回路である。出力ポート閉塞判定回路86は、例えば対向LSI等のフレームの転送先の状態に関する出力ポート閉塞判定条件に基づいて、判定及び出力ポート閉塞信号B7の出力を行なうことができる。つまり、出力ポート閉塞判定回路86は、対応する転送先へのフレームの出力状況(転送状態)を監視し、出力状況が所定の条件を満たした場合に、出力ポート閉塞信号B7,C10を出力するのである。このように、出力ポート閉塞判定回路86は、複数の転送先へのデータ転送の状態に応じて、出力ポート閉塞信号B7,C10を出力する通知部の一例である。

The output port

なお、各出力ポート8は、セレクタ82(自出力ポート8)から転送先へのフレームの出力状況が第1の条件を満たすか否か、例えば送信頻度が第1の閾値を超えるか否かを判断することができる。また、各出力ポート8は、セレクタ82(自出力ポート8)から転送先へのフレームの出力状況が第2の条件を満たすか否か、例えば送信頻度が第1の閾値よりも低い第2の閾値を未満であるか否かを判断することができる。

Each

再送ステートマシン63は、出力状況が第1の条件を満たす第1の転送先(出力ポート8)に対応する入力キュー61に格納された当該第1の転送先へのフレームを、セレクタ62を制御して迂回路へ出力させることができる。例えば、再送ステートマシン63は、第1の転送先に対応する入力キュー61に格納された当該第1の転送先へのフレームを、出力状況が第2の条件を満たす第2の転送先(代替出力ポート8)へ出力するようにセレクタ62を制御することができる。

The

このように、情報処理システム1によれば、閉塞ポート8を閉鎖して代替ポート8に切り替えるだけでなく、出力ポート8に接続される入力ポート6(入力キュー61)ごとにフレームの送信頻度等が監視される。そして、再送ステートマシン63は、特定の入力ポート6(入力キュー61)または全入力ポート6(入力キュー61)からのフレームを、送信頻度の低い転送先(迂回路)に迂回させることができるため、スループットを向上させることができる。

As described above, according to the

出力ポート閉塞判定回路86は、出力ポート8の閉塞中は、出力ポート8内の回路を同期リセットしてもよい。また、出力ポート閉塞判定回路86は、故障の場合は出力ポート閉塞信号B7を全入力ポート8に一斉に送信してもよく、混雑の場合は出力ポート閉塞信号B7を特定の入力ポート8宛てにのみ送信してもよい。さらに、出力ポート閉塞判定回路86は、閉塞した出力ポート8を再利用する場合、入力ポート8から出力ポート閉塞解除信号B11を受信し、出力ポート8内の同期リセットを解除することができる。

The output port

〔2〕変形例

〔2−1〕第1変形例

一実施形態に係るクロスバ2は、図6に示すような、フレームごと(フレームの送信先ごと)に通常用出力ポート及び迂回用出力ポートが設定されるルーティングテーブル53を保持するものとして説明したが、これに限定されるものではない。例えば、クロスバ2は、ルーティングテーブル53に代えて、図17に示すような、出力ポート8ごとに通常用出力ポート及び迂回用出力ポートが設定されるルーティングテーブル53’を保持してもよい。特に言及しない限り、情報処理システム1の各構成は、図5等に示すものと同様であるため、重複した説明を省略する。[2] Modification [2-1] First Modification The

図17は、一実施形態の第1変形例に係るルーティングテーブル53’のデータ構造を示す図である。図17に示すように、ルーティングテーブル53’は、図6に示すルーティングテーブル53と比して、送信先のカラムが省略されている。また、ルーティングテーブル53’のエントリの数は、クロスバ2にそなえられる出力ポート8の数(例えば3つ)に対応する。このように、第1変形例に係る情報処理システム1では、ルーティングテーブル53’により出力ポート8ごとに迂回用出力ポート8が決まる。

FIG. 17 is a diagram illustrating a data structure of the routing table 53 ′ according to the first modification of the embodiment. As shown in FIG. 17, the routing table 53 ′ omits the destination column as compared with the routing table 53 shown in FIG. 6. Further, the number of entries in the routing table 53 ′ corresponds to the number of output ports 8 (for example, three) provided in the

例えば、迂回用出力ポート管理回路64は、自身に対応する出力ポート(通常用出力ポート)8をエントリとして、ルーティングテーブル53’内の迂回用出力ポート8の情報を保持することができる。つまり、迂回用出力ポート管理回路64は、上記(IV)の処理において、再送ステートマシン63が閉塞ポート8に対応する入力キュー61内のフレームを出力する際に、全フレームの出力先を1つの迂回用出力ポート8に変換することができる。一例として、図5に示すクロスバ2において出力ポートAが閉塞ポート8である場合、再送ステートマシン63は、上記(IV)の処理において、入力キュー61内の全てのフレームを、迂回用出力ポートB(第1候補)へ出力することができる(図17参照)。

For example, the detour output

従って、第1変形例に係る情報処理システム1によれば、一実施形態と同様の効果を奏することができるほか、閉塞ポート8及び代替ポート8に該当しない他の出力ポート8が独立して動作できるため、クロスバ2のスループットを向上させることができる。

また、ルーティングテーブル53’のデータ構造が簡素化するため、管理部4によるルーティングテーブル53’の更新処理にかかる負荷を低減させることもできる。Therefore, according to the

Further, since the data structure of the routing table 53 ′ is simplified, it is possible to reduce the load applied to the updating process of the routing table 53 ′ by the

なお、管理部4(保持部41)は、情報処理システム1内の全クロスバ2の全ルーティングテーブル53’(図17参照)の情報を管理情報42として保持すればよい。

〔2−2〕第2変形例

一実施形態に係るクロスバ2は、図6に示すような、迂回用出力ポート8ごとに有効/無効のカラムを持つルーティングテーブル53を保持するものとして説明したが、これに限定されるものではない。例えば、クロスバ2は、ルーティングテーブル53に代えて、図18に示すような、送信先出力ポート8をビット値によって通常用出力ポート8及び迂回用出力ポート8の中から選択可能なルーティングテーブル53”を保持してもよい。特に言及しない限り、情報処理システム1の各構成は、図5等に示すものと同様であるため、重複した説明を省略する。The management unit 4 (holding unit 41) may hold the information of all routing tables 53 ′ (see FIG. 17) of all

[2-2] Second Modification The

図18は、一実施形態の第2変形例に係るルーティングテーブル53”のデータ構造を示す図である。図18に示すように、ルーティングテーブル53”は、図6に示すルーティングテーブル53と比して、各迂回用出力ポート8の有効/無効のカラムが省略されている代わりに、出力ポート選択ビットのカラムが追加されている。例えば、ルーティングテーブル53”では、出力ポート選択ビットのビット値と送信先出力ポート8とを、以下のように対応付けることができる。

18 is a diagram illustrating a data structure of the routing table 53 ″ according to the second modification of the embodiment. As illustrated in FIG. 18, the routing table 53 ″ is compared with the routing table 53 illustrated in FIG. Thus, instead of omitting the valid / invalid column of each

出力ポート選択ビットのビット値“00”:通常用出力ポート8

出力ポート選択ビットのビット値“01”:第1候補の迂回用出力ポート8

出力ポート選択ビットのビット値“10”:第2候補の迂回用出力ポート8

・・・

なお、迂回用出力ポート8の候補数に応じて、出力ポート選択ビットのビット幅を適宜増減してもよい。Output port selection bit value “00”:

Bit value “01” of output port selection bit: first candidate

Bit value “10” of output port selection bit: second candidate

...

Note that the bit width of the output port selection bit may be appropriately increased or decreased according to the number of candidates for the

迂回用出力ポート管理回路64は、一実施形態と同様に、受付キュー51から入力キュー61に入力されるフレームごとに、ルーティングテーブル53”内の迂回用出力ポート8の情報を保持する。ここで、ルーティングテーブル53”では、出力ポート選択ビットのビット値が送信先出力ポート8を示すため、迂回用出力ポート管理回路64は、出力ポート選択ビットに“1”を加算したビット値に対応する迂回用出力ポート8の情報を保持すればよい。

The detour output

また、管理部4は、ルーティングテーブル53”の更新処理において、一実施形態のように通常用出力ポート8を迂回用出力ポート8で上書きして迂回用出力ポート8の有効/無効を書き換える代わりに、出力ポート選択ビットのビット値を書き換えるだけでよい。

従って、第2変形例に係る情報処理システム1によれば、一実施形態と同様の効果を奏することができるほか、管理部4によるルーティングテーブル53”の更新処理にかかる負荷を低減させることができる。Further, in the update process of the routing table 53 ″, the

Therefore, according to the

なお、管理部4(保持部41)は、情報処理システム1内の全クロスバ2の全ルーティングテーブル53”(図18参照)の情報と全クロスバ2の全出力ポート8の有効/無効の情報を管理情報42として保持すればよい。また、管理部4は、ルーティングテーブル53”の更新処理において、再利用しない出力ポート8の出力ポート番号については削除してもよい。

The management unit 4 (holding unit 41) stores information on all routing tables 53 ″ (see FIG. 18) of all

また、第2変形例においては、一実施形態に係るルーティングテーブル53の変形例を説明したが、第1変形例に係るルーティングテーブル53’に対しても、第2変形例を適用することができる。すなわち、図17に示すルーティングテーブル53’に対して、各迂回用出力ポート8の有効/無効のカラムを省略し、代わりに出力ポート選択ビットのカラムを追加してもよい。第1変形例と第2変形例とを組み合わることにより、第1変形例と同様の効果を奏することができるほか、管理部4によるルーティングテーブル53”の更新処理にかかる負荷を第1変形例よりも低減させることができる。

In the second modification, the modification of the routing table 53 according to the embodiment has been described. However, the second modification can be applied to the routing table 53 ′ according to the first modification. . That is, the valid / invalid column of each

〔2−3〕第3変形例

一実施形態に係るクロスバ2は、再送ステートマシン63を各入力ポート6の各入力キュー制御部60内にそなえるものとして説明したが、これに限定されるものではない。

図19は、一実施形態の第3変形例に係る再送ステートマシン63’の構成を示す図である。例えば、クロスバ2は、図19に示す再送ステートマシン63’を入力キュー制御部60の外部にそなえ、入力キュー制御部60と再送ステートマシン63’とを配線で接続することができるほか、ソケットやピン等により接続してもよい。[2-3] Third Modification Although the

FIG. 19 is a diagram illustrating a configuration of a

図19に示すように、第3変形例に係る再送ステートマシン63’は、例えば、状態管理部631、代替出力制御部632、管理部制御部633、出力ポート制御部634、及び受付ポート制御部635をそなえることができる。

状態管理部631は、レジスタ等の記憶装置をそなえ、上述した(I)〜(V)の状態を管理する(図10参照)。状態管理部631は、図13に示す出力ポート閉塞信号B7、入力ポート6へのフレーム送信停止信号A5、出力ポート切り替え完了信号B10、及びキュー再送エントリ数B2をそれぞれ入力され、各信号の入力に応じてレジスタ値を変化させる。As illustrated in FIG. 19, the

The

代替出力制御部632は、状態管理部631のレジスタ値が“3'b011”の場合に、代替出力処理を行なうものであり、例えば、迂回用出力ポート管理回路64が示す代替ポート8に応じたセレクタ62を制御させる信号D1を、選択信号生成回路607へ送信する。換言すれば、代替出力制御部632は、状態管理部631が管理するデータ転送の状態に応じて、一の転送先に対応する入力キュー61に格納された一の転送先へのフレームを、代替の転送先へ出力するように、セレクタ62を制御するものである。

The alternative

管理部制御部633は、状態管理部631のレジスタ値が“3'b100”の場合に、管理部4へルーティングテーブル更新可能通知信号B9を送信する。

出力ポート制御部634は、状態管理部631のレジスタ値が“3'b100”の場合、且つ管理部4によりルーティングテーブル53が更新されなかった場合に、出力ポート8へ出力ポート閉塞解除信号B11を送信する。When the register value of the

When the register value of the

受付ポート制御部635は、受付ポート5へフレーム送信再開指示信号A6を送信する。なお、受付ポート制御部635は、状態管理部631のレジスタ値が“3'b100”の場合、且つ、ルーティングテーブル53が更新された場合又は出力ポート制御部634が出力ポート閉塞解除信号B11を送信した場合に、上記処理を行なう。

このように、第3実施例に係る再送ステートマシン63’によれば、転送経路の変更処理を管理する機能をクロスバ2の外部に設けることができ、再送ステートマシン63’の交換により制御態様(論理)を容易に変更することができる。これにより、情報処理システム1の運用形態や構成の変化に応じた再送ステートマシン63’の更新を、クロスバ2全体を交換するよりも低コストに実現することができる。The reception

As described above, according to the

なお、再送ステートマシン63’は、クロスバ2を制御する制御装置の一例である。当該制御装置には、入力ポート6内又はクロスバ2内の複数の再送ステートマシン63’を集積させてもよく、入力キュー制御部60における迂回用出力ポート管理回路64や選択信号生成回路607等の複数の回路を含めてもよい。また、図19に示す各機能(回路)ブロックは、図5又は図13に示す再送ステートマシン63にそなえられてもよい。

The

〔3〕その他

以上、本発明の好ましい実施形態について詳述したが、本発明は、かかる特定の実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲内において、種々の変形、変更して実施することができる。

例えば、上述したクロスバ2は、受付ポート5、入力ポート6、出力ポート8、及び接続部9をそれぞれ3つそなえるものとして説明したが、これに限定されるものではなく、それぞれ2つ、又は4つ以上そなえてもよい。また、クロスバ2は、例えば少なくとも入力ポート6を1以上そなえ、出力ポート8を転送先の数だけそなえればよい。さらに、ルーティングテーブル53,53’,53”は、受付ポート5ごとにそなえられなくてもよく、管理部4がそなえる管理情報42と同様のものがクロスバ2にそなえられてもよい。また、セレクタ62は、入力ポート6の外部にそなえられてもよい。[3] Others While the preferred embodiments of the present invention have been described in detail above, the present invention is not limited to such specific embodiments, and various modifications and changes can be made without departing from the spirit of the present invention. It can be changed and implemented.

For example, the

また、クロスバ2(受付ポート5、入力ポート6、ルーティング部7、出力ポート8、及び接続部9)の各機能は、任意の組み合わせで統合又は分散してもよい。

さらに、図10のステップS13及びS14の処理順序は、上述したものに限定されるものではなく、順序を入れ替えてもよい。この場合、再送ステートマシン63のレジスタ値が示す状態も入れ替えればよい。The functions of the crossbar 2 (

Furthermore, the processing order of steps S13 and S14 in FIG. 10 is not limited to that described above, and the order may be changed. In this case, the state indicated by the register value of the

さらに、図2に示す情報処理システム1が複数のクロスバ2をそなえるものとして説明したが、これに限定されるものではない。例えば、情報処理システム1は、1つのクロスバ2をそなえてもよい。この場合、クロスバ2と送信先装置3との間には、異なる2以上の転送経路(例えばバス,ケーブル,無線通信路等のうちの同種又は異種の2以上の組み合わせ)が存在すればよい。また、クロスバ2は、送信先装置3への複数の転送先のいずれかへフレームを出力すればよい。

〔4〕付記

以上の実施形態及び各変形例に関し、更に以下の付記を開示する。

(付記1)

データを送信する送信元装置と、

前記送信元装置から送信された前記データを受信する送信先装置と、

前記送信元装置と前記送信先装置との間に介設され、複数の異なる転送経路のうちのいずれかを介して前記データを前記送信元装置から前記送信先装置へ転送する複数のデータ転送装置と、をそなえ、

前記データ転送装置は、

入力される転送データを自データ転送装置に接続される前記送信先装置または他のデータ転送装置を含む転送先ごとに格納する複数の格納部と、

前記複数の格納部に格納された転送データを、前記複数の転送先のいずれかへ選択的に切り替えて出力する切替部と、

前記切替部から一の転送経路を介した一の転送先へのデータ転送の状態に応じて、前記一の転送先に対応する格納部に格納された前記一の転送先への転送データを、前記複数の異なる転送経路に含まれる他の転送先へ出力するように前記切替部を制御する代替出力処理を行なう制御部と、を有する

ことを特徴とする、情報処理装置。

(付記2)

前記データ転送装置は、

前記転送データの1以上の転送先に関する転送先情報を保持する保持部をさらに有し、

前記一の転送先に対応する格納部に格納された転送データについて前記転送先情報に前記他の転送先が含まれる場合、前記制御部は、前記転送先情報に基づいて、前記代替出力処理を行なう

ことを特徴とする、付記1記載の情報処理装置。

(付記3)

前記転送先情報は、前記転送データの送信先装置に応じた1以上の転送先に関する情報であり、

前記制御部は、前記代替出力処理において、前記一の転送先に対応する格納部に格納された前記一の転送先への複数の転送データを、前記転送データの各々の送信先装置に応じた他の転送先へそれぞれ出力するように前記切替部を制御する

ことを特徴とする、付記2記載の情報処理装置。

(付記4)

前記切替部から前記複数の転送先へのデータ転送の状態に応じて、前記保持部に保持された前記転送先情報を更新する更新部をさらにそなえるとともに、

前記データ転送装置は、

入力される転送データの前記複数の格納部への格納を抑止する抑止部をさらに有し、

前記制御部は、前記代替出力処理を行なうと、前記転送先情報の更新要求を前記更新部へ送信し、

前記更新部は、前記制御部からの更新要求に応じて、前記一の転送先に出力される転送データが前記他の転送先に出力されるように、前記転送先情報を更新する

ことを特徴とする、付記2又は付記3記載の情報処理装置。

(付記5)

前記データ転送装置は、

前記自データ転送装置に接続される転送先ごとにそなえられ、前記転送データを当該転送データの転送先へ出力する複数の出力部をさらに有し、

前記制御部は、前記代替出力処理において、一の出力部から一の転送経路を介した前記一の転送先へのデータ転送の状態に応じて、前記一の出力部に対応する格納部に格納された、前記一の出力部へ出力済みの転送データを含む1以上の転送データを、各転送データに対応する他の出力部へ出力するように前記切替部を制御する

ことを特徴とする、付記1〜4のいずれか1項記載の情報処理装置。

(付記6)

前記データ転送装置は、

前記複数の転送先へのデータ転送の状態に応じて、出力抑止信号を出力する通知部と、

前記複数の格納部に格納される転送データを一括して格納する受付格納部と、

前記受付格納部に格納された転送データを対応する格納部へ順次出力させ、前記通知部から前記一の転送先について前記出力抑止信号を受信すると、前記受付格納部から出力中の転送データの出力が完了してから前記制御部による代替出力処理が完了するまで、前記受付格納部に格納された転送データの前記複数の格納部への出力を抑止させる制御を行なう受付制御部と、をさらに有する

ことを特徴とする、付記1〜5のいずれか1項記載の情報処理装置。

(付記7)

前記制御部は、前記切替部から第1の転送先への転送データの出力状況が第1の条件を満たす場合であって、前記切替部から第2の転送先への転送データの出力状況が第2の条件を満たす場合、前記第1の転送先に対応する格納部に格納された前記第1の転送先への転送データを、前記第2の転送先へ出力するように前記切替部を制御する

ことを特徴とする、付記1〜6のいずれか1項記載の情報処理装置。

(付記8)

データを送信する送信元装置と、前記送信元装置から送信された前記データを受信する送信先装置との間に介設され、複数の異なる転送経路のうちのいずれかを介して前記データを前記送信元装置から前記送信先装置へ転送するデータ転送装置であって、

入力される転送データを自データ転送装置に接続される前記送信先装置または他のデータ転送装置を含む転送先ごとに格納する複数の格納部と、

前記複数の格納部に格納された転送データを、前記複数の転送先のいずれかへ選択的に切り替えて出力する切替部と、

前記切替部から一の転送経路を介した一の転送先へのデータ転送の状態に応じて、前記一の転送先に対応する格納部に格納された前記一の転送先への転送データを、前記複数の異なる転送経路に含まれる他の転送先へ出力するように前記切替部を制御する代替出力処理を行なう制御部と、を有する

ことを特徴とする、データ転送装置。

(付記9)

前記転送データの1以上の転送先に関する転送先情報を保持する保持部をさらに有し、

前記一の転送先に対応する格納部に格納された転送データについて前記転送先情報に前記他の転送先が含まれる場合、前記制御部は、前記転送先情報に基づいて、前記代替出力処理を行なう

ことを特徴とする、付記8記載のデータ転送装置。

(付記10)

前記転送先情報は、前記転送データの送信先装置に応じた1以上の転送先に関する情報であり、

前記制御部は、前記代替出力処理において、前記一の転送先に対応する格納部に格納された前記一の転送先への複数の転送データを、前記転送データの各々の送信先装置に応じた他の転送先へそれぞれ出力するように前記切替部を制御する

ことを特徴とする、付記9記載のデータ転送装置。

(付記11)

前記自データ転送装置に接続される転送先ごとにそなえられ、前記転送データを当該転送データの転送先へ出力する複数の出力部をさらに有し、

前記制御部は、前記代替出力処理において、一の出力部から一の転送経路を介した前記一の転送先へのデータ転送の状態に応じて、前記一の出力部に対応する格納部に格納された、前記一の出力部へ出力済みの転送データを含む1以上の転送データを、各転送データに対応する他の出力部へ出力するように前記切替部を制御する

ことを特徴とする、付記8〜10のいずれか1項記載のデータ転送装置。

(付記12)

前記複数の転送先へのデータ転送の状態に応じて、出力抑止信号を出力する通知部と、

前記複数の格納部に格納される転送データを一括して格納する受付格納部と、

前記受付格納部に格納された転送データを対応する格納部へ順次出力させ、前記通知部から前記一の転送先について前記出力抑止信号を受信すると、前記受付格納部から出力中の転送データの出力が完了してから前記制御部による代替出力処理が完了するまで、前記受付格納部に格納された転送データの前記複数の格納部への出力を抑止させる制御を行なう受付制御部と、をさらに有する

ことを特徴とする、付記8〜11のいずれか1項記載のデータ転送装置。

(付記13)

前記制御部は、前記切替部から第1の転送先への転送データの出力状況が第1の条件を満たす場合であって、前記切替部から第2の転送先への転送データの出力状況が第2の条件を満たす場合、前記第1の転送先に対応する格納部に格納された前記第1の転送先への転送データを、前記第2の転送先へ出力するように前記切替部を制御する

ことを特徴とする、付記8〜12のいずれか1項記載のデータ転送装置。

(付記14)

データを送信する送信元装置と、前記送信元装置から送信された前記データを受信する送信先装置と、前記送信元装置と前記送信先装置との間に介設され、複数の異なる転送経路のうちのいずれかを介して前記データを前記送信元装置から前記送信先装置へ転送する1以上のデータ転送装置と、をそなえる情報処理システムにおけるデータ転送方法であって、

入力される転送データを、自データ転送装置に接続される前記送信先装置または他のデータ転送装置を含む転送先ごとにそなえられる複数の格納部のうちの、当該転送データの転送先に対応する格納部に格納し、

前記複数の格納部に格納された転送データを前記複数の転送先のいずれかへ選択的に切り替えて出力する切替部から一の転送経路を介した一の転送先へのデータ転送の状態を取得し、

取得した前記状態に応じて、前記一の転送先に対応する格納部に格納された前記一の転送先への転送データを、前記複数の異なる転送経路に含まれる他の転送先へ出力するように前記切替部を制御する代替出力処理を行なう

ことを特徴とする、データ転送方法。

(付記15)

前記一の転送先に対応する格納部に格納された転送データについて、保持部に保持された前記転送データの1以上の転送先に関する転送先情報に前記他の転送先が含まれる場合、前記転送先情報に基づいて、前記代替出力処理を行なう

ことを特徴とする、付記14記載のデータ転送方法。

(付記16)

前記転送先情報は、前記転送データの送信先装置に応じた1以上の転送先に関する情報であり、

前記代替出力処理において、前記一の転送先に対応する格納部に格納された前記一の転送先への複数の転送データを、前記転送データの各々の送信先装置に応じた他の転送先へそれぞれ出力するように前記切替部を制御する

ことを特徴とする、付記15記載のデータ転送方法。

(付記17)

入力される転送データの前記複数の格納部への格納を抑止し、

前記転送データの前記複数の格納部への格納が抑止されている場合に、

前記代替出力処理を行ない、

前記一の転送先に出力される転送データが前記他の転送先に出力されるように、前記転送先情報を更新する

ことを特徴とする、付記15又は付記16記載のデータ転送方法。

(付記18)

前記代替出力処理において、前記自データ転送装置に接続される転送先ごとにそなえられ、前記転送データを当該転送データの転送先へ出力する複数の出力部のうちの一の出力部から一の転送経路を介した前記一の転送先へのデータ転送の状態に応じて、前記一の出力部に対応する格納部に格納された、前記一の出力部へ出力済みの転送データを含む1以上の転送データを、各転送データに対応する他の出力部へ出力するように前記切替部を制御する

ことを特徴とする、付記14〜17のいずれか1項記載のデータ転送方法。

(付記19)

前記複数の格納部に格納される転送データを一括して格納する受付格納部に格納された転送データを対応する格納部へ順次出力し、

前記切替部から前記一の転送先へのデータ転送の状態が所定の条件を満たした場合に、前記受付格納部から出力中の転送データの出力が完了すると、前記受付格納部に格納された転送データの前記複数の格納部への出力を抑止し、

前記代替出力処理が完了すると、前記受付格納部に格納された転送データの前記複数の格納部への出力を再開する

ことを特徴とする、付記14〜18のいずれか1項記載のデータ転送方法。

(付記20)

前記切替部から第1の転送先への転送データの出力状況が第1の条件を満たす場合であって、前記切替部から第2の転送先への転送データの出力状況が第2の条件を満たす場合、前記第1の転送先に対応する格納部に格納された前記第1の転送先への転送データを、前記第2の転送先へ出力するように前記切替部を制御する

ことを特徴とする、付記14〜19のいずれか1項記載のデータ転送方法。

(付記21)

データを送信する送信元装置と、前記送信元装置から送信された前記データを受信する送信先装置との間に介設され、複数の異なる転送経路のうちのいずれかを介して前記データを前記送信元装置から前記送信先装置へ転送し、入力される転送データを自データ転送装置に接続される前記送信先装置または他のデータ転送装置を含む転送先ごとに格納する複数の格納部を有するデータ転送装置における制御装置であって、

前記複数の格納部に格納された転送データを、前記複数の転送先のいずれかへ選択的に切り替えて出力する切替部から一の転送経路を介した一の転送先へのデータ転送の状態を管理する状態管理部と、

前記状態管理部が管理する前記データ転送の状態に応じて、前記一の転送先に対応する格納部に格納された前記一の転送先への転送データを、前記複数の異なる転送経路に含まれる他の転送先へ出力するように前記切替部を制御する代替出力制御部と、を有する

ことを特徴とする、制御装置。

Furthermore, although the

[4] Notes

The following supplementary notes are further disclosed with respect to the above embodiment and each modified example.

(Appendix 1)

A transmission source device for transmitting data; and

A transmission destination device that receives the data transmitted from the transmission source device;

A plurality of data transfer devices that are interposed between the transmission source device and the transmission destination device and transfer the data from the transmission source device to the transmission destination device via any one of a plurality of different transfer paths And

The data transfer device

A plurality of storage units that store input transfer data for each transfer destination including the transmission destination device or other data transfer devices connected to the own data transfer device;

A switching unit that selectively switches and outputs the transfer data stored in the plurality of storage units to any of the plurality of transfer destinations;

According to the state of data transfer from the switching unit to one transfer destination via one transfer path, the transfer data to the one transfer destination stored in the storage unit corresponding to the one transfer destination, A control unit that performs an alternative output process for controlling the switching unit so as to output to another transfer destination included in the plurality of different transfer paths.

An information processing apparatus.

(Appendix 2)

The data transfer device

A holding unit that holds transfer destination information regarding one or more transfer destinations of the transfer data;

When the other transfer destination is included in the transfer destination information for the transfer data stored in the storage unit corresponding to the one transfer destination, the control unit performs the alternative output processing based on the transfer destination information. Do

The information processing apparatus according to

(Appendix 3)

The transfer destination information is information relating to one or more transfer destinations according to a transmission destination device of the transfer data,

In the alternative output process, the control unit is configured to select a plurality of transfer data to the one transfer destination stored in a storage unit corresponding to the one transfer destination according to each transmission destination device of the transfer data. Control the switching unit to output to each other transfer destination

The information processing apparatus according to

(Appendix 4)

According to the state of data transfer from the switching unit to the plurality of transfer destinations, further comprising an update unit for updating the transfer destination information held in the holding unit,

The data transfer device

A deterrence unit for deterring storage of the input transfer data in the plurality of storage units;

The control unit, when performing the alternative output processing, transmits an update request for the transfer destination information to the update unit,

In response to an update request from the control unit, the update unit updates the transfer destination information so that transfer data output to the one transfer destination is output to the other transfer destination.

The information processing apparatus according to

(Appendix 5)

The data transfer device

Provided for each transfer destination connected to the own data transfer device, further comprising a plurality of output units for outputting the transfer data to the transfer destination of the transfer data,

In the alternative output process, the control unit stores in a storage unit corresponding to the one output unit in accordance with a state of data transfer from one output unit to the one transfer destination via one transfer path. The switching unit is controlled to output one or more transfer data including the transfer data already output to the one output unit to another output unit corresponding to each transfer data.

The information processing apparatus according to any one of

(Appendix 6)

The data transfer device

A notification unit that outputs an output suppression signal according to a state of data transfer to the plurality of transfer destinations;

An acceptance storage unit that collectively stores transfer data stored in the plurality of storage units;

When the transfer data stored in the reception storage unit is sequentially output to the corresponding storage unit and the output suppression signal is received for the one transfer destination from the notification unit, the output of the transfer data being output from the reception storage unit A reception control unit that performs control to suppress output of the transfer data stored in the reception storage unit to the plurality of storage units until the alternative output process by the control unit is completed

The information processing apparatus according to any one of

(Appendix 7)

The control unit is a case where the output status of the transfer data from the switching unit to the first transfer destination satisfies the first condition, and the output status of the transfer data from the switch unit to the second transfer destination is When the second condition is satisfied, the switching unit is configured to output transfer data to the first transfer destination stored in the storage unit corresponding to the first transfer destination to the second transfer destination. Control

The information processing apparatus according to any one of

(Appendix 8)

A transmission source device that transmits data and a transmission destination device that receives the data transmitted from the transmission source device, and the data is transmitted via any one of a plurality of different transfer paths. A data transfer device for transferring from a transmission source device to the transmission destination device,