本発明の実施例を以下に説明する。

本発明が適用されたスロットマシンの実施例を図面を用いて説明すると、本実施例のスロットマシン1は、前面が開口する筐体1aと、この筐体1aの側端に回動自在に枢支された前面扉1bと、から構成されている。

本実施例のスロットマシン1の筐体1aの内部には、図2に示すように、外周に複数種の図柄が配列されたリール2L、2C、2R(以下、左リール、中リール、右リール)が水平方向に並設されており、図1に示すように、これらリール2L、2C、2Rに配列された図柄のうち連続する3つの図柄が前面扉に設けられた透視窓3から見えるように配置されている。

リール2L、2C、2Rの外周部には、図3に示すように、それぞれ「黒7」、「網7(図中網掛け7)」、「白7」、「BAR」、「リプレイ」、「プラム」、「スイカ」、「チェリー」、「ベル」、「オレンジ」といった互いに識別可能な複数種類の図柄が所定の順序で、それぞれ21個ずつ描かれている。リール2L、2C、2Rの外周部に描かれた図柄は、前面扉1bのリールパネル1c略中央に設けられた透視窓3において各々上中下三段に表示される。

各リール2L、2C、2Rは、各々対応して設けられリールモータ32L、32C、32R(図4参照)によって回転させることで、各リール2L、2C、2Rの図柄が透視窓3に連続的に変化しつつ表示されるとともに、各リール2L、2C、2Rの回転を停止させることで、透視窓3に3つの連続する図柄が表示結果として導出表示されるようになっている。

リール2L、2C、2Rの内側には、リール2L、2C、2Rそれぞれに対して、基準位置を検出するリールセンサ33L、33C、33Rと、リール2L、2C、2Rを背面から照射するリールLED55と、が設けられている。また、リールLED55は、リール2L、2C、2Rの連続する3つの図柄に対応する12のLEDからなり、各図柄をそれぞれ独立して照射可能とされている。

前面扉1bにおける各リール2L,2C,2Rに対応する位置には、リール2L,2C,2Rを前面側から透視可能とする横長長方形状の透視窓3が設けられており、該透視窓3を介して遊技者側から各リール2L,2C,2Rが視認できるようになっている。

前面扉1bには、メダルを投入可能なメダル投入部4、メダルが払い出されるメダル払出口9、クレジット(遊技者所有の遊技用価値として記憶されているメダル数)を用いて、その範囲内において遊技状態に応じて定められた規定数の賭数のうち最大の賭数(本実施例ではいずれの遊技状態においても3)を設定する際に操作されるMAXBETスイッチ6、クレジットとして記憶されているメダル及び賭数の設定に用いたメダルを精算する(クレジット及び賭数の設定に用いた分のメダルを返却させる)際に操作される精算スイッチ10、ゲームを開始する際に操作されるスタートスイッチ7、リール2L、2C、2Rの回転を各々停止する際に操作されるストップスイッチ8L、8C、8R、演出に用いるための演出用スイッチ56が遊技者により操作可能にそれぞれ設けられている。

尚、本実施例では、回転を開始した3つのリール2L、2C、2Rのうち、最初に停止するリールを第1停止リールと称し、また、その停止を第1停止と称する。同様に、2番目に停止するリールを第2停止リールと称し、また、その停止を第2停止と称し、3番目に停止するリールを第3停止リールと称し、また、その停止を第3停止あるいは最終停止と称する。

また、前面扉1bには、クレジットとして記憶されているメダル枚数が表示されるクレジット表示器11、入賞の発生により払い出されたメダル枚数やエラー発生時にその内容を示すエラーコード等が表示される遊技補助表示器12、賭数が1設定されている旨を点灯により報知する1BETLED14、賭数が2設定されている旨を点灯により報知する2BETLED15、賭数が3設定されている旨を点灯により報知する3BETLED16、メダルの投入が可能な状態を点灯により報知する投入要求LED17、スタートスイッチ7の操作によるゲームのスタート操作が有効である旨を点灯により報知するスタート有効LED18、ウェイト(前回のゲーム開始から一定期間経過していないためにリールの回転開始を待機している状態)中である旨を点灯により報知するウェイト中LED19、後述するリプレイゲーム中である旨を点灯により報知するリプレイ中LED20が設けられた遊技用表示部13が設けられている。

MAXBETスイッチ6の内部には、MAXBETスイッチ6の操作による賭数の設定操作が有効である旨を点灯により報知するBETスイッチ有効LED21(図4参照)が設けられており、ストップスイッチ8L、8C、8Rの内部には、該当するストップスイッチ8L、8C、8Rによるリールの停止操作が有効である旨を点灯により報知する左、中、右停止有効LED22L、22C、22R(図4参照)がそれぞれ設けられている。

また、前面扉1bにおけるストップスイッチ8L、8C、8Rの下方には、スロットマシン1のタイトルや配当表などが印刷された下部パネル1dが設けられている。

前面扉1bの内側には、所定のキー操作により後述するエラー状態及び後述する打止状態を解除するためのリセット操作を検出するリセットスイッチ23、後述する設定値の変更中や設定値の確認中にその時点の設定値が表示される設定値表示器24、後述のBB終了時に打止状態(リセット操作がなされるまでゲームの進行が規制される状態)に制御する打止機能の有効/無効を選択するための打止スイッチ36a、後述のBB終了時に自動精算処理(クレジットとして記憶されているメダルを遊技者の操作によらず精算(返却)する処理)に制御する自動精算機能の有効/無効を選択するための自動精算スイッチ36b、メダル投入部4から投入されたメダルの流路を、筐体1a内部に設けられた後述のホッパータンク34a(図2参照)側またはメダル払出口9側のいずれか一方に選択的に切り替えるための流路切替ソレノイド30、メダル投入部4から投入され、ホッパータンク34a側に流下したメダルを検出する投入メダルセンサ31を有するメダルセレクタ(図示略)、前面扉1bの開放状態を検出するドア開放検出スイッチ25(図4参照)が設けられている。

筐体1a内部には、図2に示すように、前述したリール2L、2C、2R、リールモータ32L、32C、32R、各リール2L、2C、2Rのリール基準位置をそれぞれ検出可能なリールセンサ33L、33C、33R(図4参照)からなるリールユニット2、外部出力信号を出力するための外部出力基板1000、メダル投入部4から投入されたメダルを貯留するホッパータンク34a、ホッパータンク34aに貯留されたメダルをメダル払出口9より払い出すためのホッパーモータ34b、ホッパーモータ34bの駆動により払い出されたメダルを検出する払出センサ34cからなるホッパーユニット34、電源ボックス100が設けられている。

ホッパーユニット34の側部には、ホッパータンク34aから溢れたメダルが貯留されるオーバーフロータンク35が設けられている。オーバーフロータンク35の内部には、貯留された所定量のメダルを検出可能な高さに設けられた左右に離間する一対の導電部材からなる満タンセンサ35aが設けられており、導電部材がオーバーフロータンク35内に貯留されたメダルを介して接触することにより導電したときに内部に貯留されたメダル貯留量が所定量以上となったこと、すなわちオーバーフロータンクが満タン状態となったことを検出できるようになっている。

電源ボックス100の前面には、設定変更状態または設定確認状態に切り替えるための設定キースイッチ37、通常時においてはエラー状態や打止状態を解除するためのリセットスイッチとして機能し、設定変更状態においては後述する内部抽選の当選確率(出玉率)の設定値を変更するための設定スイッチとして機能するリセット/設定スイッチ38、電源をon/offする際に操作される電源スイッチ39が設けられている。

本実施例のスロットマシン1においてゲームを行う場合には、まず、メダルをメダル投入部4から投入するか、あるいはクレジットを使用して賭数を設定する。クレジットを使用するにはMAXBETスイッチ6を操作すれば良い。遊技状態に応じて定められた規定数の賭数が設定されると、入賞ラインLN(図1参照)が有効となり、スタートスイッチ7の操作が有効な状態、すなわち、ゲームが開始可能な状態となる。本実施例では、規定数の賭数として遊技状態に関わらず3枚が定められて規定数の賭数が設定されると入賞ラインLNが有効となる。尚、遊技状態に対応する規定数のうち最大数を超えてメダルが投入された場合には、その分はクレジットに加算される。

入賞ラインとは、各リール2L、2C、2Rの透視窓3に表示された図柄の組み合わせが入賞図柄の組み合わせであるかを判定するために設定されるラインである。本実施例では、図1に示すように、リール2Lの中段、リール2Cの中段、リール2Rの中段、すなわち中段に水平方向に並んだ図柄に跨って設定された入賞ラインLNのみが入賞ラインとして定められている。尚、本実施例では、1本の入賞ラインのみを適用しているが、複数の入賞ラインを適用しても良い。

また、本実施例では、入賞ラインLNに入賞を構成する図柄の組み合わせが揃ったことを認識しやすくするために、入賞ラインLNとは別に、無効ラインLM1〜4を設定している。無効ラインLM1〜4は、これら無効ラインLM1〜4に揃った図柄の組み合わせによって入賞が判定されるものではなく、入賞ラインLNに特定の入賞を構成する図柄の組み合わせが揃った際に、無効ラインLM1〜4のいずれかに入賞ラインLNに揃った場合に入賞となる図柄の組み合わせ(例えば、ベル−ベル−ベル)が揃う構成とすることで、入賞ラインLNに特定の入賞を構成する図柄の組み合わせが揃ったことを認識しやすくするものである。本実施例では、図1に示すように、リール2Lの上段、リール2Cの上段、リール2Rの上段、すなわち上段に水平方向に並んだ図柄に跨って設定された無効ラインLM1、リール2Lの下段、リール2Cの下段、リール2Rの下段、すなわち下段に水平方向に並んだ図柄に跨って設定された無効ラインLM2、リール2Lの上段、リール2Cの中段、リール2Rの下段、すなわち右下がりに並んだ図柄に跨って設定された無効ラインLM3、リール2Lの下段、リール2Cの中段、リール2Rの上段、すなわち右上がりに並んだ図柄に跨って設定された無効ラインLM4の4種類が無効ラインLMとして定められている。

ゲームが開始可能な状態でスタートスイッチ7を操作すると、各リール2L、2C、2Rが回転し、各リール2L、2C、2Rの図柄が連続的に変動する。この状態でいずれかのストップスイッチ8L、8C、8Rを操作すると、対応するリール2L、2C、2Rの回転が停止し、透視窓3に表示結果が導出表示される。

そして全てのリール2L、2C、2Rが停止されることで1ゲームが終了し、入賞ラインLNに予め定められた図柄の組み合わせ(以下、役とも呼ぶ)が各リール2L、2C、2Rの表示結果として停止した場合には入賞が発生し、その入賞に応じて定められた枚数のメダルが遊技者に対して付与され、クレジットに加算される。また、クレジットが上限数(本実施例では50)に達した場合には、メダルが直接メダル払出口9(図1参照)から払い出されるようになっている。また、入賞ラインLNに、遊技状態の移行を伴う図柄の組み合わせが各リール2L、2C、2Rの表示結果として停止した場合には図柄の組み合わせに応じた遊技状態に移行するようになっている。

また、本実施例におけるスロットマシン1にあっては、ゲームが開始されて各リール2L、2C、2Rが回転して図柄の変動が開始した後、いずれかのストップスイッチ8L、8C、8Rが操作されたときに、当該ストップスイッチ8L、8C、8Rに対応するリールの回転が停止して図柄が停止表示される。ストップスイッチ8L、8C、8Rの操作から対応するリール2L、2C、2Rの回転を停止するまでの最大停止遅延時間は190ms(ミリ秒)である。

リール2L、2C、2Rは、1分間に80回転し、80×21(1リール当たりの図柄コマ数)=1680コマ分の図柄を変動させるので、190msの間では最大で4コマの図柄を引き込むことができることとなる。つまり、停止図柄として選択可能なのは、ストップスイッチ8L、8C、8Rが操作されたときに表示されている図柄と、そこから4コマ先までにある図柄、合計5コマ分の図柄である。

このため、例えば、ストップスイッチ8L、8C、8Rのいずれかが操作されたときに当該ストップスイッチに対応するリールの下段に表示されている図柄を基準とした場合、当該図柄から4コマ先までの図柄を下段に表示させることができるため、リール2L、2C、2R各々において、ストップスイッチ8L、8Rのうちいずれかが操作されたときに当該ストップスイッチに対応するリールの中段に表示されている図柄を含めて5コマ以内に配置されている図柄を入賞ラインLNに表示させることができる。

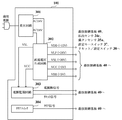

図4は、スロットマシン1の構成を示すブロック図である。スロットマシン1には、図4に示すように、遊技制御基板40、演出制御基板90、電源基板101が設けられており、遊技制御基板40によって遊技状態が制御され、演出制御基板90によって遊技状態に応じた演出が制御され、電源基板101によってスロットマシン1を構成する電気部品の駆動電源が生成され、各部に供給される。

電源基板101には、外部からAC100Vの電源が供給されるとともに、このAC100Vの電源からスロットマシン1を構成する電気部品の駆動に必要な直流電圧が生成され、遊技制御基板40及び遊技制御基板40を介して接続された演出制御基板90に供給されるようになっている。また、後述する遊技制御用マイクロコンピュータ100からサブ制御部91へのコマンド伝送ラインと、遊技制御基板40から演出制御基板90に対して電源を供給する電源供給ラインと、が一系統のケーブル及びコネクタを介して接続されており、これらケーブルと各基板とを接続するコネクタ同士が全て接続されることで演出制御基板90側の各部が動作可能となり、かつ遊技制御用マイクロコンピュータ100からのコマンドを受信可能な状態となる。このため、遊技制御用マイクロコンピュータ100からコマンドを伝送するコマンド伝送ラインが演出制御基板90に接続されている状態でなければ、演出制御基板90側に電源が供給されず、演出制御基板90側のみが動作してしまうことがない。

また、電源基板101には、前述したホッパーモータ34b、払出センサ34c、満タンセンサ35a、設定キースイッチ37、リセット/設定スイッチ38、電源スイッチ39が接続されている。

例えば、電源基板101では、図5に示すように、AC24V、VLP(直流+24V)、VSL(直流+30V)、VDD(直流+12V)、VCC(直流+5V)およびVBB(直流+5V)を生成する。電源基板101は、例えば図5に示すように、変圧回路301と、直流電圧生成回路302と、電源監視回路303と、クリアスイッチ304とを備えて構成されている。また、電源基板101の外部には、スロットマシン1内の各制御基板および機構部品への電力供給を実行または遮断するための電源スイッチ39が設けられている。あるいは、スロットマシン1において、電源スイッチ39は、電源基板101に設けられていてもよい。加えて、電源基板101には、バックアップ電源となるコンデンサが設けられていてもよい。このコンデンサは、例えばVBB(直流+5V)の電源ラインから充電されるものであればよい。

変圧回路301は、例えば商用電源が入力側(一次側)に印加されるトランスや、トランスの入力側に設けられた過電圧保護回路としてのバリスタなどを備えて構成されたものであればよい。ここで、変圧回路301が備えるトランスは、商用電源と電源基板101の内部とを電気的に絶縁するためのものであればよい。変圧回路301は、その出力電圧として、AC24Vを生成する。直流電圧生成回路302は、例えばAC24Vを整流素子で整流昇圧することによってVSLを生成する整流平滑回路を含んでいる。VSLは、ソレノイド駆動用の電源電圧として用いられる。また、直流電圧生成回路302は、例えばAC24Vを整流素子で整流することによってVLPを生成する整流回路を含んでいる。VLPは、クレジット表示器11、遊技補助表示器12、ペイアウト表示器13、1〜3BETLED14〜16、投入要求LED17、スタート有効LED18、ウェイト中LED19、リプレイ中LED20、BETスイッチ有効LED21、左、中、右停止有効LED22L、22C、22R、設定値表示器24等の発光体を点灯するための電源電圧として用いられる。加えて、直流電圧生成回路302は、例えばVSLに基づいてVDDおよびVCCを生成するDC−DCコンバータを含んでいる。このDC−DCコンバータは、例えば1つ又は複数のスイッチングレギュレータと、そのスイッチングレギュレータの入力側に接続された比較的大容量のコンデンサとを含み、外部からスロットマシン1への電力供給が停止したときに、VSL、VDD、VBB等の直流電圧が比較的緩やかに低下するように構成されたものであればよい。VDDは、例えば図4に示すMAXBETスイッチ6、スタートスイッチ7、ストップスイッチ8L、8C、8R、精算スイッチ10、リセットスイッチ23、打止スイッチ36a、自動精算スイッチ36b、投入メダルセンサ31、ドア開放検出スイッチ25、リールセンサ33L、33C、33R、払出センサ34c、満タンセンサ35a、設定キースイッチ37、リセット/設定スイッチ38といった、各種スイッチに供給され、これらのスイッチを作動させるために用いられる。

図5に示すように、VLP、VSL、VDD、VCCおよびVBBは、例えば所定のコネクタや電源ラインを介して、遊技制御基板40へと伝送される。なお、演出制御基板90には、遊技制御基板40を経由して各電圧が供給されればよい。あるいは、演出制御基板90には、遊技制御基板40を経由することなく、電源基板10から直接に各電圧が供給されてもよい。

電源監視回路303は、例えば停電監視リセットモジュールICを用いて構成され、電源断信号を出力する電源監視手段を実現する回路である。例えば、電源監視回路303は、スロットマシン1において用いられる所定電源電圧(一例としてVSL)が所定値(一例として+22V)を超えると、オフ状態(ハイレベル)の電源断信号を出力する。その一方で、所定電源電圧が所定値以下になった期間が、予め決められている時間(一例として56ミリ秒)以上継続したときに、オン状態(ローレベル)の電源断信号を出力する。あるいは、電源監視回路303は、スロットマシン1において用いられる所定電源電圧が所定値以下になると、直ちにオン状態の電源断信号を出力するようにしてもよい。電源断信号は、例えばローレベルとなることでオン状態となりハイレベルとなることでオフ状態となる負論理の電気信号であればよい。電源監視回路303から出力された電源断信号は、例えば電源基板101に搭載された出力ドライバ回路によって増幅された後に所定のコネクタや信号ラインを介して、遊技制御基板40へと伝送される。

電源断信号を出力するための監視対象となる所定電源電圧は、例えば電源電圧VSLといった、スイッチ作動用の電源電圧VDDにおける規定値(一例として+12V)よりも高い電圧であることが好ましい。これにより、スイッチ作動用の電源電圧VDDが低下して各種スイッチ(例えばMAXBETスイッチ6、スタートスイッチ7、ストップスイッチ8L、8C、8R、精算スイッチ10、リセットスイッチ23、打止スイッチ36a、自動精算スイッチ36b、投入メダルセンサ31、ドア開放検出スイッチ25、リールセンサ33L、33C、33R、払出センサ34c、満タンセンサ35a、設定キースイッチ37、リセット/設定スイッチ38など)の動作状態が不安定となる以前に、電源断信号を出力する(オン状態にする)ことで、各種スイッチによる誤検出に基づく遊技制御の進行を防止できる。すなわち、スイッチ作動用の電源電圧VDDが低下すると負論理(ローレベルでオン状態となる)のスイッチ出力がオン状態となるものの、電源電圧VDDよりも早く低下する電源電圧VSLを監視して電力供給の停止を認識することで、スイッチ出力がオン状態となる以前に、電源復旧待ちの状態となってスイッチ出力を検出しない状態となることができる。

電源電圧VSLなどを遊技制御基板40へと伝送する電源ラインには、大容量のコンデンサが接続されていてもよい。これに対して、電源電圧VSLを監視対象とするために電源監視回路303へと伝送する入力ラインには、このようなコンデンサが接続されていなくてもよい。この場合、監視対象となる電源監視回路303への入力ラインにおける電源電圧VSLは、コンデンサが接続された電源ラインにおける電源電圧VSLより早く低下する。すなわち、監視対象の電源電圧VSLが低下し始めた後でも、所定期間は、ソレノイドやモータなどに供給される電源ラインにおける電源電圧VSLの供給状態が維持される。したがって、監視対象となる電源電圧VSLが低下し始める場合でも、所定期間は、ソレノイドやモータなどを駆動可能な状態とすることができる。また、電源ラインにおける電源電圧VSLが低下し始める前に、電力供給の停止を認識することができる。

なお、ソレノイド駆動用の電源電圧VSLに代えて、例えば発光体点灯用の電源電圧VLPといった、スイッチ作動用の電源電圧VDDにおける規定値よりも高い任意の電源電圧を監視対象として、電源断信号を出力するようにしてもよい。また、外部からスロットマシン1に供給される電力の供給停止を検出するための条件としては、スロットマシン1において用いられる所定電源電圧が所定値以下になったことに限られず、外部からの電力が途絶えたことを検出できる任意の条件であればよい。例えば、AC24V等の交流波そのものを監視して交流波が途絶えたことを検出条件としてもよいし、交流波をデジタル化した信号を監視して、デジタル信号が平坦になったことをもって交流波が途絶えたことの検出条件としてもよい。

電源監視回路303は、例えば所定電源電圧(一例としてVCC)が所定値(一例として+4.5V)以下になったときに、リセット信号を出力してもよい。リセット信号は、例えばローレベルとなることでオン状態となる電気信号であればよい。電源監視回路303から出力されたリセット信号は、例えば電源基板101に搭載された出力ドライバ回路によって増幅された後に所定のコネクタや信号ラインを介して、遊技制御基板40へと伝送される。演出制御基板90には、遊技制御基板40を経由してリセット信号が伝送されればよい。あるいは、演出制御基板90に対しても、遊技制御基板40を経由せずにリセット信号が直接に伝送されるようにしてもよい。さらに、リセット信号を出力する回路は、電源監視回路303とは別個に設けられたウォッチドッグタイマ内蔵IC、あるいはシステムリセットICなどを用いて構成されてもよい。

スロットマシン1への電力供給が停止するときには、電源監視回路303が、電源断信号を出力(ローレベルに設定)してから所定期間が経過したときに、リセット信号を出力(ローレベルに設定)する。ここでの所定期間は、例えば図4に示す遊技制御基板40に搭載されている遊技制御用マイクロコンピュータ100が、所定の電源断処理を実行するのに十分な時間であればよい。すなわち、電源監視回路303は、給電中信号としての電源断信号を出力した後、遊技制御用マイクロコンピュータ100が所定の電源断処理を実行完了してから、動作停止信号としてのリセット信号を出力(ローレベルに設定)する。電源監視回路303から出力されたリセット信号を受信した遊技制御用マイクロコンピュータ100は、動作停止状態となり、各種の制御処理の実行が停止される。また、スロットマシン1への電力供給が開始され、例えば所定電源電圧(一例としてVCC)が所定値(一例として+4.5V)を超えたときに、電源監視回路303はリセット信号の出力を停止(ハイレベルに設定)する。

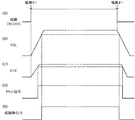

図6は、スロットマシン1への電力供給が開始されたときと、電力供給が停止するときにおける、AC24V、VSL、VCC、リセット信号および電源断信号の状態を、模式的に示すタイミング図である。図6に示すように、スロットマシン1への電力供給が開始されたときに、VSLおよびVCCは徐々に規定値(直流+30Vおよび直流+5V)に達する。このとき、VCCが第1の所定値(例えば+4.5V)を超えると、電源監視回路303はリセット信号の出力を停止(ハイレベルに設定)してオフ状態とする。また、VSLが第2の所定値(例えば+22V)を超えると、電源監視回路303は電源断信号の出力を停止(ハイレベルに設定)してオフ状態とする。他方、スロットマシン1への電力供給が停止するときに、VSLおよびVCCは徐々に低下する。このとき、VSLが第2の所定値(+22V)にまで低下すると、電源監視回路303は電源断信号をオン状態として出力(ローレベルに設定)する。また、VCCが第1の所定値(+4.5V)にまで低下すると、電源監視回路303はリセット信号をオン状態として出力(ローレベルに設定)する。

図5に示す電源基板10が備えるクリアスイッチ304は、例えば押しボタン構造を有し、押下などの操作に応じてクリア信号を出力する。クリア信号は、例えば押下などの操作に応じてローレベルとなることでオン状態となる電気信号であればよい。あるいは、クリア信号は、例えば押下などの操作に応じてハイレベルとなることでオン状態となる電気信号であってもよい。クリアスイッチ304から出力されたクリア信号は、例えば所定のコネクタや信号ラインを介して、遊技制御基板40へと伝送される。また、クリアスイッチ304の操作がなされていないときには、クリア信号の出力を停止(ハイレベルあるいはローレベルに設定)する。なお、クリアスイッチ304は、押しボタン構造以外の他の構成(例えばスライドスイッチ構造やトグルスイッチ構造、ダイヤルスイッチ構造など)であってもよい。

遊技制御基板40には、前述したMAXBETスイッチ6、スタートスイッチ7、ストップスイッチ8L、8C、8R、精算スイッチ10、リセットスイッチ23、打止スイッチ36a、自動精算スイッチ36b、投入メダルセンサ31、ドア開放検出スイッチ25、リールセンサ33L、33C、33Rが接続されているとともに、電源基板101を介して前述した払出センサ34c、満タンセンサ35a、設定キースイッチ37、リセット/設定スイッチ38が接続されており、これら接続されたスイッチ類の検出信号が入力されるようになっている。

また、遊技制御基板40には、前述したクレジット表示器11、遊技補助表示器12、ペイアウト表示器13、1〜3BETLED14〜16、投入要求LED17、スタート有効LED18、ウェイト中LED19、リプレイ中LED20、BETスイッチ有効LED21、左、中、右停止有効LED22L、22C、22R、設定値表示器24、流路切替ソレノイド30、リールモータ32L、32C、32Rが接続されているとともに、電源基板101を介して前述したホッパーモータ34bが接続されており、これら電気部品は、遊技制御基板40に搭載された後述の遊技制御用マイクロコンピュータ100の制御に基づいて駆動されるようになっている。

遊技制御基板40には、遊技制御用マイクロコンピュータ100、外部メモリ(SRAM)50、制御用クロック生成回路42、乱数用クロック生成回路43、スイッチ回路44、モータ駆動回路45、ソレノイド駆動回路46、LED駆動回路47が搭載されている。

遊技制御用マイクロコンピュータ100は、1チップマイクロコンピュータにて構成され、CPU505、ROM506、RAM507、I/Oポート41dを備えている。遊技制御用マイクロコンピュータ100は、ROM506に記憶された制御プログラムを実行して、遊技の進行に関する処理を行うととともに、遊技制御基板40に搭載された制御回路の各部を直接的または間接的に制御する。尚、この実施例では、遊技制御用マイクロコンピュータ100は、SRAM50などの外部デバイスに対して16ビットまたは32ビットでのバスアクセスのみ可能である。

ここで、制御用クロック生成回路42は、遊技制御用マイクロコンピュータ100の外部にて、所定周波数の発振信号となる制御用クロックCCLKを生成する。制御用クロック生成回路42により生成された制御用クロックCCLKは、例えば図5に示すような遊技制御用マイクロコンピュータ100の制御用外部クロック端子EXCを介してクロック回路502に供給される。乱数用クロック生成回路43は、遊技制御用マイクロコンピュータ100の外部にて、制御用クロックCCLKの発振周波数とは異なる所定周波数の発振信号となる乱数用クロックRCKを生成する。乱数用クロック生成回路43により生成された乱数用クロックRCKは、例えば遊技制御用マイクロコンピュータ100の乱数用外部クロック端子ERCを介して乱数回路509A、509B(図7を参照)などに供給される。一例として、乱数用クロック生成回路43により生成される乱数用クロックRCKの発振周波数は、制御用クロック生成回路42により生成される制御用クロックCCLKの発振周波数以下となるようにすればよい。あるいは、乱数用クロック生成回路43により生成される乱数用クロックRCKの発振周波数は、制御用クロック生成回路42により生成される制御用クロックCCLKの発振周波数よりも高周波となるようにしてもよい。

スイッチ検出回路44は、遊技制御基板40に直接または電源基板101を介して接続されたスイッチ類から入力された検出信号を取り込んで遊技制御用マイクロコンピュータ100に伝送する。モータ駆動回路45は、遊技制御用マイクロコンピュータ100から出力されたモータ駆動信号をリールモータ32L、32C、32Rに伝送する。ソレノイド駆動回路46は、遊技制御用マイクロコンピュータ100から出力されたソレノイド駆動信号を流路切替ソレノイド30に伝送する。LED駆動回路は、遊技制御用マイクロコンピュータ100から出力されたLED駆動信号を遊技制御基板40に接続された各種表示器やLEDに伝送する。

図7は、遊技制御基板40に搭載された遊技制御用マイクロコンピュータ100の構成例を示している。図7に示す遊技制御用マイクロコンピュータ100は、例えば1チップマイクロコンピュータであり、外部バスインタフェース501と、クロック回路502と、固有情報記憶回路503と、リセットコントローラ504Aと、割込みコントローラ504Bと、CPU(Central Processing Unit)505と、ROM(Read Only Memory)506と、RAM(Random Access Memory)507と、タイマ回路508と、16ビットの乱数回路509Aと、8ビットの乱数回路509Bと、フリーランカウンタ509Cと、PIP(Parallel Input Port)510と、シリアル通信回路511と、アドレスデコード回路512とを備えて構成される。

図8は、遊技制御用マイクロコンピュータ100におけるアドレスマップの一例を示している。図8に示すように、アドレス0000H〜アドレス2FFFHの領域は、ROM506に割り当てられ、ユーザプログラムエリアとプログラム管理エリアとを含んでいる。なお、添字Hは、16進数であることを示しており、以下の説明でも同様である。図9(A)は、ROM506におけるプログラム管理エリアの主要部分について、用途や内容の一例を示している。アドレスF000H〜アドレスF3FFHの領域は、RAM507に割り当てられたワークエリアであり、I/Oマップやメモリマップに割り付けることができる。アドレスFE00H〜アドレスFEBFHの領域は、遊技制御用マイクロコンピュータ100の内蔵レジスタに割り当てられる内蔵レジスタエリアである。図9(B)は、内蔵レジスタエリアの主要部分について、用途や内容の一例を示している。

プログラム管理エリアは、CPU505がユーザプログラムを実行するために必要な情報を格納する記憶領域である。図9(A)に示すように、プログラム管理エリアには、ヘッダKHDR、リセット設定KRES、割込み初期設定KIIS、16ビット乱数初期設定第1KRL1〜16ビット乱数初期設定第3KRL3、8ビット乱数初期設定第1KRS1、8ビット乱数初期設定第2KRS2、セキュリティ時間設定KSESなどが、含まれている。

プログラム管理エリアに記憶されるヘッダKHDRは、遊技制御用マイクロコンピュータ100における内部データの読出設定を示す。図10(A)は、ヘッダKHDRにおける設定データと動作との対応関係を例示している。ここで、遊技制御用マイクロコンピュータ100では、ROM読出防止機能と、バス出力マスク機能とを設定可能である。ROM読出防止機能は、遊技制御用マイクロコンピュータ100が備えるROM506の記憶データについて、読出動作を許可または禁止する機能であり、読出禁止に設定された状態では、ROM506の記憶データを読み出すことができない。バス出力マスク機能は、外部バスインタフェース501に接続された外部装置から遊技制御用マイクロコンピュータ100の内部データに対する読出要求があった場合に、外部バスインタフェース501におけるアドレスバス出力、データバス出力および制御信号出力にマスクをかけることにより、外部装置から内部データの読み出しを不能にする機能である。図10(A)に示すように、ヘッダKHDRの設定データに対応して、ROM読出防止機能やバス出力マスク機能の動作組合せが異なるように設定される。図10(A)に示す設定データのうち、ROM読出が許可されるとともに、バス出力マスクが有効となる設定データは、バス出力マスク有効データともいう。また、ROM読出が禁止されるとともに、バス出力マスクが有効となる設定データ(全て「00H」)は、ROM読出禁止データともいう。ROM読出が許可されるとともに、バス出力マスクが無効となる設定データは、バス出力マスク無効データともいう。

プログラム管理エリアに記憶されるリセット設定KRESは、遊技制御用マイクロコンピュータ100におけるリセット動作の設定を示す。図10(B)は、リセット設定KRESにおける設定内容の一例を示している。リセット設定KRESのビット番号[7]は、遊技制御用マイクロコンピュータ100において内部リセットが発生したときの動作を設定する設定データである。遊技制御用マイクロコンピュータ100における内部リセットは、例えばリセットコントローラ504Aに設けられたウォッチドッグタイマ520からタイムアウト信号が出力されることや、指定エリア外走行禁止(IAT)が発生したことなど、所定の要因により発生するリセットである。

図10(B)に示す例において、リセット設定KRESのビット番号[7]におけるビット値が“0”である場合には、内部リセットが発生したときのリセット動作がユーザリセットに設定される。ユーザリセットが実行される場合には、例えば割り込みコントローラ504B、CPU505、タイマ回路508、フリーランカウンタ509C、PIP510、シリアル通信回路511が初期化され、ユーザプログラムのリセットアドレス(ROM506のアドレス0000H)からユーザプログラムを再実行する。一方、リセット設定KRESのビット番号[7]におけるビット値が“1”である場合には、内部リセットが発生したときのリセット動作がシステムリセットに設定される。システムリセットが実行される場合には、例えば16ビットの乱数回路509Aや8ビットの乱数回路509Bなどを含めた、遊技制御用マイクロコンピュータ100におけるすべての内部回路が初期化され、ユーザプログラムのリセットアドレスからユーザプログラムを再実行する。

リセット設定KRESのビット番号[6]は、リセットコントローラ504Aに設けられたウォッチドッグタイマ520の起動方法を設定する設定データである。図10(B)に示す例において、リセット設定KRESのビット番号[6]におけるビット値が“0”である場合には、遊技制御用マイクロコンピュータ100の動作状態がセキュリティモードからユーザモードに移行することで、ウォッチドッグタイマ520が自動的に起動される。これに対して、そのビット値が“1”である場合には、遊技制御用マイクロコンピュータ100のCPU505がROM506から読み出した制御コードに基づくユーザプログラム(ゲーム制御用の初期設定プログラムおよび遊技制御処理プログラム)を実行することで、ソフトウェアによりウォッチドッグタイマ520を起動させる。このように、ROM506のプログラム管理エリアに記憶されるリセット設定KRESのビット番号[6]におけるビット値を“1”とする設定データを予め記憶させておくことで、ユーザプログラムの実行によるソフトウェアにて、所定のWDT起動制御コードによりウォッチドッグタイマ520を起動してリセット動作を有効化することや、所定のWDT停止制御コードによりウォッチドッグタイマ520を停止してリセット動作を無効化することができる。

リセット設定KRESのビット番号[5−4]は、ウォッチドッグタイマ520のタイムアウト時間を設定するために用いられる基準クロックを設定する設定データである。図10(B)に示す例においては、リセット設定KRESのビット番号[5−4]におけるビット値が“00”、“01”、“10”、“11”のいずれであるかに応じて、周期が異なる基準クロックの設定が行われる。リセット設定KRESのビット番号[3−0]は、ビット番号[5−4]におけるビット値に対応する設定周期との乗算に用いられることで、ウォッチドッグタイマ520のタイムアウト時間を設定する設定データである。図10(B)に示す例においては、リセット設定KRESのビット番号[3−0]におけるビット値が“0000”である場合に、ウォッチドッグタイマ520による監視時間の計測を禁止してウォッチドッグ不使用とする。一方、それらのビット値が“1000”である場合には、設定周期に「8」を乗算することで、ウォッチドッグタイマ520のタイムアウト時間が設定される。また、それらのビット値が“1111”である場合には、設定周期に「15」を乗算することで、ウォッチドッグタイマ520のタイムアウト時間が設定される。

このように、リセット設定KRESのビット番号[5−4]およびビット番号[3−0]におけるビット値を設定することにより、ウォッチドッグタイマ520により計測される監視時間は、予め定められた複数種類のうちから設定することができる。図10(B)に示す例では、リセット設定KRESのビット番号[5−4]におけるビット値が“11”でビット番号[3−0]におけるビット値が“1111”である場合に、監視時間として設定可能な最長時間が設定される。一例として、内部システムクロックSCLKの周波数が10.0MHzである場合には、約50.33秒が最長の監視時間となる。他の一例として、内部システムクロックSCLKの周波数が12.0MHzである場合には、約41.94秒が最長の監視時間となる。

プログラム管理エリアに記憶される割込み初期設定KIISは、遊技制御用マイクロコンピュータ100にて発生するマスカブル割込みの取扱いに関する初期設定を示す。図11(A)は、割込み初期設定KIISにおける設定内容の一例を示している。

割込み初期設定KIISのビット番号[7−4]では、割込みベクタの上位4ビットを設定する。割込み初期設定KIISのビット番号[3−0]では、マスカブル割込み要因の優先度の組合せを設定する。図11(A)に示す例において、割込み初期設定KIISのビット番号[3−0]により「00H」〜「02H」のいずれかが指定されれば、タイマ回路508からのマスカブル割込み要因を最優先とする優先度の組合せが設定される。これに対して、「03H」または「04H」のいずれかが指定されれば、シリアル通信回路511からのマスカブル割込み要因を最優先とする優先度の組合せが設定される。また、「05H」または「06H」のいずれかが指定されれば、乱数回路509A、509Bなどからのマスカブル割込み要因を最優先とする優先度の組合せが設定される。なお、同一回路からのマスカブル割込み要因を最優先とする優先度の組合せでも、指定値が異なる場合には、最優先となるマスカブル割込み要因の種類や第2順位以下における優先度の組合せなどが異なっている。

プログラム管理エリアに記憶される16ビット乱数初期設定第1KRL1〜16ビット乱数初期設定第3KRL3は、16ビットの乱数回路509Aに対する初期設定を示す。図11(B)は、16ビット乱数初期設定第1KRL1における設定内容の一例を示している。図11(C)は、16ビット乱数初期設定第3KRL3における設定内容の一例を示している。この実施の形態において、16ビットの乱数回路509Aは、4つのチャネルch0〜ch3の16ビット疑似乱数を、独立して発生することができる。

16ビット乱数初期設定第1KRL1のビット番号[7]は、チャネルch1の16ビット乱数を発生させるために、16ビットの乱数回路509Aを起動させる方法を設定する16ビット乱数チャネルch1用の乱数回路起動設定データである。図11(B)に示す例において、16ビット乱数初期設定第1KRL1のビット番号[7]におけるビット値が“0”である場合には、チャネルch1の16ビット乱数における最大値をユーザプログラム(ソフトウェア)で指定したときに、チャネルch1の16ビット乱数を発生させるための回路が起動される。これに対して、そのビット値が“1”である場合には、遊技制御用マイクロコンピュータ100の動作状態がセキュリティモードからユーザモードに移行することで、チャネルch1の16ビット乱数を発生させるための回路が自動的に起動される。

16ビット乱数初期設定第1KRL1のビット番号[6]は、チャネルch1の16ビット乱数を発生させるときに、乱数値となる数値データの更新用となる乱数更新クロックRGK(図17を参照)を、内部システムクロックSCLKとするか、乱数用クロックRCKの2分周(RCK/2)とするかを設定する16ビット乱数チャネルch1用の乱数更新クロック設定データである。図11(B)に示す例において、16ビット乱数初期設定第1KRL1のビット番号[6]におけるビット値が“0”である場合には、内部システムクロックSCLKを乱数更新クロックRGKに用いる設定となる一方、“1”である場合には、乱数用クロックRCKの2分周(RCK/2)を乱数更新クロックRGKに用いる設定となる。

16ビット乱数初期設定第1KRL1のビット番号[5−4]は、チャネルch1の16ビット乱数を発生させるときに、乱数更新規則を変更するか否かや、変更する場合における変更方式を設定する16ビット乱数チャネルch1用の乱数更新規則設定データである。図11(B)に示す例において、16ビット乱数初期設定第1KRL1のビット番号[5−4]におけるビット値が“00”である場合には、乱数更新規則を変更しない設定となり、“01”である場合には、乱数更新規則をソフトウェアにより変更する設定となり、“10”である場合には、2周目から乱数更新規則を自動で変更する設定となり、“11”である場合には、1周目から乱数更新規則を自動で変更する設定となる。

図11(B)に示す例において、16ビット乱数初期設定第1KRL1のビット番号[3]、[2]、[1−0]はそれぞれ、16ビット乱数チャネルch0用の乱数回路起動設定データ、乱数更新クロック設定データ、乱数更新規則設定データとなっている。すなわち、16ビット乱数初期設定第1KRLのビット番号[3−0]は、そのビット番号[7−4]によりチャネルch1の16ビット乱数について初期設定を行う場合と同様に、チャネルch0の16ビット乱数について初期設定を行うための設定データである。

なお、16ビット乱数初期設定第2KRL2のビット番号[7]、[6]、[5−4]はそれぞれ、16ビット乱数チャネルch3用の乱数回路起動設定データ、乱数更新クロック設定データ、乱数更新規則設定データとなっている。16ビット乱数初期設定第2KRL2のビット番号[3]、[2]、[1−0]はそれぞれ、16ビット乱数チャネルch2用の乱数回路起動設定データ、乱数更新クロック設定データ、乱数更新規則設定データとなっている。

16ビット乱数初期設定第3KRL3のビット番号[7]とビット番号[6]は、チャネルch3の16ビット乱数となる数値データでのスタート値を設定する16ビット乱数チャネルch3用の乱数スタート値設定データである。図11(C)に示す例において、16ビット乱数初期設定第3KRL3のビット番号[7]におけるビット値が“0”である場合には、スタート値が所定のデフォルト値である「0000H」に設定される一方、“1”である場合には、遊技制御用マイクロコンピュータ100ごとに付与された固有の識別情報であるIDナンバーに基づく値がスタート値に設定される。また、図11(C)に示す例では、16ビット乱数初期設定第3KRL3のビット番号[6]におけるビット値が“0”である場合には、システムリセット毎にスタート値を変更しない設定となる一方、“1”である場合には、システムリセット毎にスタート値を変更する設定となる。

なお、スタート値をIDナンバーに基づく値に設定する場合には、IDナンバーに所定のスクランブル処理を施す演算や、IDナンバーを用いた加算・減算・乗算・除算などの演算の一部または全部を実行して、算出された値をスタート値に用いるようにすればよい。また、16ビット乱数初期設定第3KRL3のビット番号[6]におけるビット値が“1”である場合には、システムリセット毎に所定のフリーランカウンタ(例えば図7に示すフリーランカウンタ509C)におけるカウント値に基づいて設定される値をスタート値に用いるようにすればよい。さらに、16ビット乱数初期設定第3KRL3のビット番号[7]とビット番号[6]におけるビット値がともに“1”である場合には、IDナンバーとフリーランカウンタにおけるカウント値とに基づいて設定される値をスタート値に用いるようにすればよい。

16ビット乱数初期設定第3KRL3のビット番号[5]とビット番号[4]は、チャネルch2の16ビット乱数となる数値データでのスタート値を設定する16ビット乱数チャネルch2用の乱数スタート値設定データである。すなわち、16ビット乱数初期設定第3KRL3のビット番号[5]とビット番号[4]は、そのビット番号[7]とビット番号[6]によりチャネルch3の16ビット乱数について初期設定を行う場合と同様に、チャネルch2の16ビット乱数について初期設定を行うための設定データである。16ビット乱数初期設定第3KRL3のビット番号[3]とビット番号[2]は、16ビット乱数チャネルch1用の乱数スタート値設定データである。16ビット乱数初期設定第3KRL3のビット番号[1]とビット番号[0]は、16ビット乱数チャネルch0用の乱数スタート値設定データである。

プログラム管理エリアに記憶される8ビット乱数初期設定第1KRS1および8ビット乱数初期設定第2KRS2は、8ビットの乱数回路509Bに対する初期設定を示す。この実施の形態において、8ビットの乱数回路509Bは、4つのチャネルch0〜ch3の8ビット疑似乱数を、独立して発生することができる。8ビット乱数初期設定第1KRS1は、8ビット乱数チャネルch1用の乱数回路起動設定データ、乱数更新クロック設定データ、乱数更新規則設定データと、8ビット乱数チャネルch0用の乱数回路起動設定データ、乱数更新クロック設定データ、乱数更新規則設定データとを含んでいる。8ビット乱数初期設定第2KRS2は、8ビット乱数チャネルch3用の乱数回路起動設定データ、乱数更新クロック設定データ、乱数更新規則設定データと、8ビット乱数チャネルch2用の乱数回路起動設定データ、乱数更新クロック設定データ、乱数更新規則設定データとを含んでいる。すなわち、8ビット乱数初期設定第1KRS1および8ビット乱数初期設定第1KRS2は、16ビット乱数初期設定第1KRL1および16ビット乱数初期設定第2KRL2によりチャネルch0〜チャネルch3の16ビット乱数について初期設定を行う場合と同様に、チャネルch0〜チャネルch3の8ビット乱数について初期設定を行うための設定データである。

プログラム管理エリアに記憶されるセキュリティ時間設定KSESは、電源投入時における遊技制御用マイクロコンピュータ100の動作状態であるセキュリティモードとなる時間(セキュリティモード時間)を延長するための設定を示す。ここで、遊技制御用マイクロコンピュータ100の動作状態がセキュリティモードであるときには、所定のセキュリティチェック処理が実行されて、ROM506の記憶内容が変更されたか否かが検査される。図12は、セキュリティ時間設定KSESにおける設定内容の一例を示している。

セキュリティ時間設定KSESのビット番号[7−6]は、セキュリティモード時間をシステムリセット毎にランダムな時間分延長する場合の時間設定を示す。図12に示す例において、セキュリティ時間設定KSESのビット番号[7−6]におけるビット値が“00”であれば、ランダムな時間延長を行わない設定となる。これに対して、そのビット値が“01”であればショートモードの設定となり、“10”であればミドルモードの設定となり、“11”であればロングモードの設定となる。ここで、ショートモードやミドルモード、あるいはロングモードが指定された場合には、例えば遊技制御用マイクロコンピュータ100に内蔵されたフリーランカウンタのカウント値を、システムリセットの発生時に遊技制御用マイクロコンピュータ100が備える所定の内蔵レジスタ(可変セキュリティモード時間用レジスタ)に格納する。そして、初期設定時に可変セキュリティ時間用レジスタの格納値をそのまま用いること、あるいは、その格納値を所定の演算関数(例えばハッシュ関数)に代入して得られた値を用いることなどにより、セキュリティモード時間を延長する際の延長時間がランダムに決定されればよい。

一例として、内部システムクロックSCLKの周波数が10.0MHzである場合には、ショートモードにおいて0〜816μs(マイクロ秒)の範囲で延長時間がランダムに決定され、ミドルモードにおいて0〜26.112ms(ミリ秒)の範囲で延長時間がランダムに決定され、ロングモードにおいて0〜835.584msの範囲で延長時間がランダムに決定される。また、他の一例として、内部システムクロックSCLKの周波数が12.0MHzである場合には、ショートモードにおいて0〜510μsの範囲で延長時間がランダムに決定され、ミドルモードにおいて0〜16.32msの範囲で延長時間がランダムに決定され、ロングモードにおいて0〜522.24msの範囲で延長時間がランダムに決定される。

可変セキュリティモード時間用レジスタは、例えば遊技制御用マイクロコンピュータ100のRAM507におけるバックアップ領域といった、主基板11におけるバックアップ箇所と共通のバックアップ電源を用いてバックアップされるものであればよい。あるいは、可変セキュリティモード時間用レジスタは、RAM507におけるバックアップ領域などに用いられるバックアップ電源とは別個に設けられた電源によりバックアップされてもよい。こうして、可変セキュリティモード時間用レジスタがバックアップ電源によってバックアップされることで、電力供給が停止した場合でも、所定期間は可変セキュリティモード時間用レジスタの格納値が保存されることになる。なお、フリーランカウンタにおけるカウント値を読み出して可変セキュリティモード時間用レジスタに格納するタイミングは、システムリセットの発生時に限定されず、予め定められた任意のタイミングとしてもよい。あるいは、フリーランカウンタをバックアップ電源によってバックアップしておき、初期設定時にフリーランカウンタから読み出した格納値を用いてセキュリティモード時間を延長する際の延長時間がランダムに決定されてもよい。

また、セキュリティ時間設定KSESのビット番号[7−6]におけるビット値によりショートモード、ミドルモード、ロングモードのいずれかを設定するとともに、セキュリティ時間設定KSESのビット番号[4−0]におけるビット値を“0001”以外とすることにより固定時間に加える延長時間を設定することもできる。この場合には、ビット番号[4−0]におけるビット値に対応した延長時間と、ビット番号[7−6]におけるビット値に基づいてランダムに決定された延長時間との双方が、固定時間に加算されて、遊技制御用マイクロコンピュータ100がセキュリティモードとなるセキュリティモード時間が決定されることになる。

図7に示す遊技制御用マイクロコンピュータ100が備える外部バスインタフェース501は、遊技制御用マイクロコンピュータ100を構成するチップの外部バスと内部バスとのインタフェース機能や、アドレスバス、データバスおよび各制御信号の方向制御機能などを有するバスインタフェースである。例えば、外部バスインタフェース501は、遊技制御用マイクロコンピュータ100に外付けされた外部メモリや外部入出力装置などに接続され、これらの外部装置との間でアドレス信号やデータ信号、各種の制御信号などを送受信するものであればよい。この実施の形態において、外部バスインタフェース501には、内部リソースアクセス制御回路501Aが含まれている。

内部リソースアクセス制御回路501Aは、外部バスインタフェース501を介した外部装置から遊技制御用マイクロコンピュータ100の内部データに対するアクセスを制御して、例えばROM506に記憶されたゲーム制御用プログラム(遊技制御処理プログラム)や固定データといった、内部データの不適切な外部読出を制限するための回路である。ここで、外部バスインタフェース501には、例えばインサーキットエミュレータ(ICE;InCircuit Emulator)といった回路解析装置が、外部装置として接続されることがある。

一例として、ROM506のプログラム管理エリアに記憶されたヘッダKHDRの内容に応じて、ROM506における記憶データの読み出しを禁止するか許可するかを切り替えられるようにする。例えば、ヘッダKHDRがバス出力マスク無効データとなっている場合には、外部装置によるROM506の読み出しを可能にして、内部データの外部読出を許可する。これに対して、ヘッダKHDRがバス出力マスク有効データとなっている場合には、例えば外部バスインタフェース501におけるアドレスバス出力、データバス出力および制御信号出力にマスクをかけることなどにより、外部装置からROM506の読み出しを不能にして、内部データの外部読出を禁止する。この場合、外部バスインタフェース501に接続された外部装置から内部データの読み出しが要求されたときには、予め定められた固定値を出力することで、外部装置からは内部データを読み出すことができないようにする。また、ヘッダKHDRがROM読出禁止データとなっている場合には、ROM506自体を読出不能として、ROM506における記憶データの読み出しを防止してもよい。そして、例えば製造段階のROMでは、ヘッダKHDRをROM読出禁止データとすることで、ROM自体を読出不能としておき、開発用ROMとするのであればバス出力マスク無効データをヘッダKHDRに書き込むことで、外部装置による内部データの検証を可能にする。これに対して、量産用ROMとするのであればバス出力マスク有効データをヘッダKHDRに書き込むことで、CPU505などによる遊技制御用マイクロコンピュータ100の内部におけるROM506の読み出しは可能とする一方で、外部装置によるROM506の読み出しはできないようにすればよい。

他の一例として、内部リソースアクセス制御回路501Aは、ROM506における記憶データの一部または全部といった、遊技制御用マイクロコンピュータ100の内部データの読み出しが、外部バスインタフェース501に接続された外部装置から要求されたことを検出する。この読出要求を検出したときに、内部リソースアクセス制御回路501Aは、遊技制御用マイクロコンピュータ100の内部データの読み出しを許可するか否かの判定を行う。例えば、ROM506における記憶データの一部または全部に暗号化処理が施されているものとする。この場合、内部リソースアクセス制御回路501Aは、外部装置からの読出要求がROM506に記憶された暗号化処理プログラムや鍵データ等に対する読出要求であれば、この読出要求を拒否して、遊技制御用マイクロコンピュータ100の内部データの読み出しを禁止する。外部バスインタフェース501では、ROM506の記憶データが出力される出力ポートと、内部バスとの間にスイッチ素子を設け、内部リソースアクセス制御回路501Aが内部データの読み出しを禁止した場合には、このスイッチ素子をオフ状態とするように制御すればよい。このように、内部リソースアクセス制御回路501Aは、外部装置からの読出要求が所定の内部データ(例えばROM506の所定領域)の読み出しを要求するものであるか否かに応じて、内部データの読み出しを禁止するか許可するかを決定するようにしてもよい。

あるいは、内部リソースアクセス制御回路501Aは、内部データの読出要求を検出したときに、所定の認証コードが外部装置から入力されたか否かを判定してもよい。この場合には、例えば内部リソースアクセス制御回路501Aの内部あるいはROM506の所定領域に、認証コードとなる所定のコードパターンが予め記憶されていればよい。そして、外部装置から認証コードが入力されたときには、この認証コードを内部記憶された認証コードと比較して、一致すれば読出要求を受容して、遊技制御用マイクロコンピュータ100の内部データの読み出しを許可する。これに対して、外部装置から入力された認証コードが内部記憶された認証コードと一致しない場合には、読出要求を拒否して、遊技制御用マイクロコンピュータ100の内部データの読み出しを禁止する。このように、内部リソースアクセス制御回路501Aは、外部装置から入力された認証コードが内部記憶された認証コードと一致するか否かに応じて、内部データの読み出しを禁止するか許可するかを決定するようにしてもよい。これにより、検査機関などが予め知得した正しい認証コードを用いて、遊技制御用マイクロコンピュータ100の内部データを損なうことなく読み出すことができ、内部データの正当性を適切に検査することなどが可能になる。

さらに他の一例として、内部リソースアクセス制御回路501Aに読出禁止フラグを設け、読出禁止フラグがオン状態であれば外部装置によるROM506の読み出しを禁止する。その一方で、読出禁止フラグがオフ状態であるときには、外部装置によるROM506の読み出しが許可される。ここで、読出禁止フラグは、初期状態ではオフ状態であるが、読出禁止フラグを一旦オン状態とした後には、読出禁止フラグをクリアしてオフ状態に復帰させることができないように構成されていればよい。すなわち、読出禁止フラグはオフ状態からオン状態に不可逆的に変更することが可能とされている。例えば、内部リソースアクセス制御回路501Aには、読出禁止フラグをクリアしてオフ状態とする機能が設けられておらず、どのような命令によっても読出禁止フラグをクリアすることができないように設定されていればよい。そして、内部リソースアクセス制御回路501Aは、外部装置からROM506における記憶データといった遊技制御用マイクロコンピュータ100の内部データの読み出しが要求されたときに、読出禁止フラグがオンであるか否かを判定する。このとき、読出禁止フラグがオンであれば、外部装置からの読出要求を拒否して、遊技制御用マイクロコンピュータ100の内部データの読み出しを禁止する。他方、読出禁止フラグがオフであれば、外部装置からの読出要求を受容して、遊技制御用マイクロコンピュータ100の内部データの読み出しを許可にする。このような構成であれば、ゲーム制御用の遊技制御処理プログラムを作成してROM506に格納する提供者においては、読出禁止フラグがオフとなっている状態でデバッグの終了したプログラムをROM506から外部装置に読み込むことができる。そして、デバッグの作業が終了した後に出荷する際には、読出禁止フラグをオン状態にセットすることにより、それ以後はROM506の外部読出を制限することができ、スロットマシン1の使用者などによるROM506の読出を防止することができる。このように、内部リソースアクセス制御回路501Aは、読出禁止フラグといった内部フラグがオフであるかオンであるかに応じて、内部データの読み出しを禁止するか許可するかを決定するようにしてもよい。

なお、読出禁止フラグを不可逆に設定するのではなく、オン状態からオフ状態に変更することも可能とする一方で、読出禁止フラグをオン状態からオフ状態に変更して内部データの読み出しが許可されるときには、ROM506の記憶データを消去(例えばフラッシュ消去など)することにより、ROM506の外部読出を制限するようにしてもよい。

遊技制御用マイクロコンピュータ100が備えるクロック回路502は、例えば制御用外部クロック端子EXCに入力される発振信号を2分周することなどにより、内部システムクロックSCLKを生成する回路である。この実施の形態では、制御用外部クロック端子EXCに制御用クロック生成回路111が生成した制御用クロックCCLKが入力される。クロック回路502により生成された内部システムクロックSCLKは、例えばCPU505といった、遊技制御用マイクロコンピュータ100において遊技の進行を制御する各種回路に供給される。また、内部システムクロックSCLKは、乱数回路509A、509Bにも供給される。さらに、内部システムクロックSCLKは、クロック回路502に接続されたシステムクロック出力端子CLKOから、遊技制御用マイクロコンピュータ100の外部へと出力されてもよい。なお、内部システムクロックSCLKは、遊技制御用マイクロコンピュータ100の外部へは出力されないことが望ましい。このように、内部システムクロックSCLKの外部出力を制限することにより、遊技制御用マイクロコンピュータ100の内部回路(CPU505など)の動作周期を外部から特定することが困難になり、乱数値となる数値データをソフトウェアにより更新する場合に、乱数値の更新周期が外部から特定されてしまうことを防止できる。

遊技制御用マイクロコンピュータ100が備える固有情報記憶回路503は、例えば遊技制御用マイクロコンピュータ100の内部情報となる複数種類の固有情報を記憶する回路である。一例として、固有情報記憶回路503は、ROMコード、チップ個別ナンバー、IDナンバーといった3種類の固有情報を記憶する。ROM506コードは、ROM506の所定領域における記憶データから生成される4バイトの数値であり、生成方法の異なる4つの数値が準備されればよい。チップ個別ナンバーは、遊技制御用マイクロコンピュータ100の製造時に付与される4バイトの番号であり、遊技制御用マイクロコンピュータ100を構成するチップ毎に異なる数値を示している。IDナンバーは、遊技制御用マイクロコンピュータ100の製造時に付与される8バイトの番号であり、遊技制御用マイクロコンピュータ100を構成するチップ毎に異なる数値を示している。ここで、チップ個別ナンバーはユーザプログラムから読み取ることができる一方、IDナンバーはユーザプログラムから読み取ることができないように設定されていればよい。なお、固有情報記憶回路503は、例えばROM506の所定領域を用いることなどにより、ROM506に含まれるようにしてもよい。あるいは、固有情報記憶回路503は、例えばCPU505の内蔵レジスタを用いることなどにより、CPU505に含まれるようにしてもよい。

遊技制御用マイクロコンピュータ100が備えるリセットコントローラ504Aは、遊技制御用マイクロコンピュータ100の内部や外部にて発生する各種リセットを制御するためのものである。リセットコントローラ504Aが制御するリセットには、システムリセットとユーザリセットが含まれている。システムリセットは、外部システムリセット端子XSRSTに一定の期間にわたりローレベル信号が入力されたときに発生するリセットである。ユーザリセットは、ウォッチドッグタイマ(WDT)のタイムアウト信号が発生したことや、指定エリア外走行禁止(IAT)が発生したことなど、所定の要因により発生するリセットである。

リセットコントローラ504Aは、図9(B)に示すような遊技制御用マイクロコンピュータ100が備える内蔵レジスタのうち、内部情報レジスタCIF(アドレスFE25H)を用いて、直前に発生したリセット要因の管理や、16ビット乱数および乱数用クロックRCKにおける異常の記録を可能にする。図13(A)は、内部情報レジスタCIFの構成例を示している。図13(B)は、内部情報レジスタCIFに格納される内部情報データの各ビットにおける設定内容の一例を示している。

内部情報レジスタCIFのビット番号[7−4]に格納される内部情報データCIF7〜CIF4は、チャネルch3〜チャネルch0の16ビット乱数に対応して、乱数値の更新動作における異常の有無を示す乱数更新異常指示である。図13(B)に示す例では、チャネルch3〜チャネルch0の16ビット乱数について更新動作の異常が検知されないときに、内部情報データCIF7〜CIF4のそれぞれにおけるビット値が“0”となる。一方、16ビット乱数の更新動作に異常が検知されたときには、その異常が検知されたチャネルに対応して、内部情報データCIF7〜CIF4のいずれかにおけるビット値が“1”となる。より具体的には、16ビット乱数の更新動作に異常を検知したチャネルが、チャネルch3であれば内部情報データCIF7が“1”となり、チャネルch2であれば内部情報データCIF6が“1”となり、チャネルch1であれば内部情報データCIF5が“1”となり、チャネルch0であれば内部情報データCIF4が“1”となる。

内部情報レジスタCIFのビット番号[3]に格納される内部情報データCIF3は、乱数用クロックRCKにおける周波数異常の有無を示す乱数用クロック異常指示である。図13(B)に示す例では、乱数用クロックRCKの周波数異常が検知されないときに、内部情報データCIF3のビット値が“0”となる一方、周波数異常が検知されたときには、そのビット値が“1”となる。内部情報レジスタCIFのビット番号[2]に格納される内部情報データCIF2は、直前に発生したリセット要因がシステムリセットであるか否かを示すシステムリセット指示である。図13(B)に示す例では、直前のリセット要因がシステムリセットではないときに(システムリセット未発生)、内部情報データCIF2のビット値が“0”となる一方、システムリセットであるときには(システムリセット発生)、そのビット値が“1”となる。内部情報データCIF2を用いた動作の第1例として、電源投入時に遊技制御用マイクロコンピュータ100のCPU505などが内部情報データCIF2のビット値をチェックして、そのビット値が“1”(セット)でなければ、通常の電源投入ではないと判断する。このときには、例えば演出制御基板90に向けて所定の演出制御コマンドを伝送させることなどにより、スロットマシン1における電源投入直後に大当り遊技状態とすることを狙った不正信号の入力行為が行われた可能性がある旨を、演出装置などにより報知させてもよい。また、内部情報データCIF2を用いた動作の第2例として、スロットマシン1が電源投入時にのみ確変状態を報知し、通常時には確変状態を報知しない場合に、電源投入時に遊技制御用マイクロコンピュータ100のCPU505などが内部情報データCIF2のビット値をチェックして、そのビット値が“1”(セット)でなければ、遊技状態の報知を行わないようにしてもよい。

内部情報レジスタCIFのビット番号[1]に格納される内部情報データCIF1は、直前に発生したリセット要因がリセットコントローラ504Aに内蔵されたウォッチドッグタイマ(WDT)520のタイムアウトによるユーザリセットであるか否かを示すウォッチドッグタイムアウト指示である。図13(B)に示す例では、直前のリセット要因がウォッチドッグタイマ520のタイムアウトによるユーザリセットではないときに(タイムアウト未発生)、内部情報データCIF1のビット値が“0”となる一方、ウォッチドッグタイマ520のタイムアウトによるユーザリセットであるときに(タイムアウト発生)、そのビット値が“1”となる。内部情報レジスタCIFのビット番号[0]に格納される内部情報データCIF0は、直前に発生したリセット要因が指定エリア外走行禁止(IAT)によるユーザリセットであるか否かを示すIAT発生指示である。図13(B)に示す例では、直前のリセット要因が指定エリア外走行の発生によるユーザリセットではないときに(IAT発生なし)、内部情報データCIF0のビット値が“0”となる一方、指定エリア外走行の発生によるユーザリセットであるときに(IAT発生あり)、そのビット値が“1”となる。

リセットコントローラ504Aには、ウォッチドッグタイマ520が内蔵されている。ウォッチドッグタイマ520は、遊技制御用マイクロコンピュータ100がユーザプログラムを正常に実行できなくなって所定の監視時間が経過した場合に、遊技制御用マイクロコンピュータ100をリセット状態にして再起動させるためのタイムアウト信号を出力する。なお、ウォッチドッグタイマ520は、遊技制御用マイクロコンピュータ100に内蔵される一方で、リセットコントローラ504Aには外付けされるようにしてもよい。あるいは、ウォッチドッグタイマ520を遊技制御用マイクロコンピュータ100に外付けした構成であってもよい。

図14は、ウォッチドッグタイマ520の構成例を示している。ウォッチドッグタイマ520は、ROM506のプログラム管理エリアに記憶されるリセット設定KRESのビット番号[6]におけるビット値により、その起動方法が設定される。この実施の形態では、ウォッチドッグタイマ520をユーザプログラムの実行によるソフトウェアでウォッチドッグタイマ520を起動してリセット動作を有効化するために、リセット設定KRESのビット番号[6]におけるビット値を予め“1”とする設定データを記憶させておく。また、ウォッチドッグタイマ520により計測される監視時間としてのタイムアウト時間が、設定可能な複数の監視時間のうちで最長時間となるように、リセット設定KRESのビット番号[5−4]におけるビット値を予め“11”とする設定データとともに、リセット設定KRESのビット番号[3−0]におけるビット値を予め“1111”とする設定データを記憶させておく。

図14に示すウォッチドッグタイマ520は、WDT制御回路533と、カウントクロック生成回路535と、16ビットアップカウンタ536と、出力制御回路537とを備えている。WDT制御回路533は、ウォッチドッグタイマ520の動作を制御する回路である。WDT制御回路533は、プログラム管理エリアのリセット設定KRESなどに基づいて、ウォッチドッグタイマ520を動作させるために、カウントクロック生成回路535により生成される基準クロックの設定や、16ビットアップカウンタ536におけるタイムアウト時間の設定を行う。

また、WDT制御回路533は、図9(B)に示すような遊技制御用マイクロコンピュータ100が備える内蔵レジスタのうち、WDTスタートレジスタWST(アドレスFE23H)に所定のWDT起動制御コードが設定されることにより、ユーザプログラムの実行によるソフトウェアで、ウォッチドッグタイマ520を起動してリセット動作を有効化すること、またはウォッチドッグタイマ520を停止してリセット動作を無効化することを、切替可能に制御する。図15(A)は、WDTスタートレジスタWSTの構成例を示している。図15(B)は、WDTスタートレジスタWSTに格納されるWDTスタートデータによる設定内容の一例を示している。

図15(A)および(B)に示す例において、WDTスタートレジスタWSTに「CCH」がCPU505によって書き込まれたときに、ウォッチドッグタイマ520を起動してタイムアウト時間の経過によるリセット動作を有効化する。一方、WDTスタートレジスタWSTに「33H」がCPU505によって書き込まれたときには、ウォッチドッグタイマ520を停止してタイムアウト時間の経過によるリセット動作を無効化する。このように、WDT起動制御コードとなる「CCH」の値を示すデータがWDTスタートレジスタWSTに書き込まれることにより、ウォッチドッグタイマ520が起動する。一方、WDT停止制御コードとなる「33H」の値を示すデータがWDTスタートレジスタWSTに書き込まれることにより、ウォッチドッグタイマ520が停止する。

さらに、WDT制御回路533は、図9(B)に示すような遊技制御用マイクロコンピュータ100が備える内蔵レジスタのうち、WDTクリアレジスタWCL(アドレスFE24H)に所定のWDTクリアデータが設定されることにより、ウォッチドッグタイマ520のカウントクリアおよびリスタートを実行する。図16(A)は、WDTクリアレジスタWCLの構成例を示している。図16(B)は、WDTクリアレジスタWCLに格納されるWDTクリアデータによる設定内容の一例を示している。

図16(A)および(B)に示す例において、WDTクリアレジスタWCLに「55H」がCPU505によって書き込まれ、次に「AAH」がCPU505によって書き込まれたときに、WDT制御回路533が16ビットアップカウンタ536のカウント値をクリアしてカウント動作をリスタートさせる。こうして、ウォッチドッグタイマ520における監視時間となるタイムアウト時間の計測は、WDTクリアレジスタWCLに「55H」と「AAH」という値が異なるWDTクリアデータが順次に書き込まれることにより、初期化して再開することができる。なお、「55H」と「AAH」からなるWDTクリアデータは、2バイト連続して書き込む必要はないが、この順番に書き込むことは必要になる。

カウントクロック生成回路535は、内部システムクロックSCLKを用いて、タイムアウト時間を設定するための基準クロックを生成する。16ビットアップカウンタ536は、カウントクロック生成回路535により生成された基準クロックをカウントする。そのカウント値がタイムアウト時間に対応する所定値に達したときには、出力制御回路537によりタイムアウト信号が出力される。一方、タイムアウト時間が経過するより前に、CPU505がWDTクリアレジスタWCLにWDTクリアデータを所定順序で書き込んだときには、16ビットアップカウンタ535におけるカウント値のクリアおよびリスタートが行われる。例えばCPU505が無限ループとなる処理を実行して、遊技制御用マイクロコンピュータ100の動作状態が待機状態に移行するときには、ウォッチドッグタイマ520を起動してタイムアウト時間の経過によるリセット動作を有効化する。このときには、WDTクリアレジスタWCLにWDTクリアデータが書き込まれないことから、16ビットアップカウンタ535のカウント値が所定値に達してタイムアウトが発生する。出力制御回路537は、16ビットアップカウンタ535からのタイムアウト信号を、リセットコントローラ504Aのリセット回路などに出力する。

遊技制御用マイクロコンピュータ100が備える割込みコントローラ504Bは、遊技制御用マイクロコンピュータ100の内部や外部にて発生する各種割込み要求を制御するためのものである。割込みコントローラ504Bが制御する割込みには、ノンマスカブル割込みNMIとマスカブル割込みINTが含まれている。ノンマスカブル割込みNMIは、CPU505の割込み禁止状態でも無条件に受け付けられる割込みであり、外部ノンマスカブル割込み端子XNMI(入力ポートPI6と兼用)に一定の期間にわたりローレベル信号が入力されたときに発生する割込みである。マスカブル割込みINTは、CPU505の設定命令により、割込み要求の受け付けを許可/禁止できる割込みであり、優先順位設定による多重割込みの実行が可能である。マスカブル割込みINTの要因としては、外部マスカブル割込み端子XINT(入力ポートPI5と兼用)に一定の期間にわたりローレベル信号が入力が入力されたこと、タイマ508に含まれるタイマ回路にてタイムアウトが発生したこと、シリアル通信回路511にてデータ受信またはデータ送信による割込み要因が発生したこと、乱数回路509A、509Bにて乱数値となる数値データの取込による割込み要因が発生したことなど、複数種類の割込み要因が予め定められていればよい。

割込みコントローラ504Bは、図9(B)に示すような遊技制御用マイクロコンピュータ100が備える内蔵レジスタのうち、割込みマスクレジスタIMR(アドレスFE26H)、割込み待ちモニタレジスタIRR(アドレスFE27H)、割込み中モニタレジスタISR(アドレスFE28H)などを用いて、割込みの制御やリセットの管理を行う。割込みマスクレジスタIMRは、互いに異なる複数の要因によるマスカブル割込みINTのうち、使用するものと使用しないものとを設定するレジスタである。割込み待ちモニタレジスタIRRは、割込み初期設定KIISにより設定されたマスカブル割込み要因のそれぞれについて、マスカブル割込み要求信号の発生状態を確認するレジスタである。割込み中モニタレジスタISRは、割込み初期設定KIISにより設定されたマスカブル割込み要因のそれぞれについて、マスカブル割込み要求信号の処理状態を確認するレジスタである。

遊技制御用マイクロコンピュータ100が備えるCPU505は、ROM506から読み出した制御コードに基づいてユーザプログラム(ゲーム制御用の遊技制御処理プログラム)を実行することにより、スロットマシン1における遊技制御を実行する制御用CPUである。こうした遊技制御が実行されるときには、CPU505がROM506から固定データを読み出す固定データ読出動作や、CPU505がRAM507に各種の変動データを書き込んで一時記憶させる変動データ書込動作、CPU505がRAM507に一時記憶されている各種の変動データを読み出す変動データ読出動作、CPU505が外部バスインタフェース501やPIP510、シリアル通信回路511などを介して遊技制御用マイクロコンピュータ100の外部から各種信号の入力を受け付ける受信動作、CPU505が外部バスインタフェース501やシリアル通信回路511などを介して遊技制御用マイクロコンピュータ100の外部へと各種信号を出力する送信動作等も行われる。

このように、遊技制御用マイクロコンピュータ100では、CPU505がROM506に格納されているプログラムに従って制御を実行するので、以下、遊技制御用マイクロコンピュータ100(またはCPU505)が実行する(又は処理を行う)ということは、具体的には、CPU505がプログラムに従って制御を実行することである。このことは、遊技制御基板40以外の他の基板に搭載されているマイクロコンピュータについても同様である。

遊技制御用マイクロコンピュータ100が備えるROM506には、ユーザプログラム(ゲーム制御用の遊技制御処理プログラム)を示す制御コードや固定データ等が記憶されている。また、ROM506には、セキュリティチェックプログラム506Aが記憶されている。CPU505は、スロットマシン1の電源投入やシステムリセットの発生に応じて遊技制御用マイクロコンピュータ100がセキュリティモードに移行したときに、ROM506に記憶されたセキュリティチェックプログラム506Aを読み出し、ROM506の記憶内容が変更されたか否かを検査するセキュリティチェック処理を実行する。なお、セキュリティチェックプログラム506Aは、ROM506とは異なる内蔵メモリに記憶されてもよい。また、セキュリティチェックプログラム506Aは、例えば外部バスインタフェース501を介して遊技制御用マイクロコンピュータ100に外付けされた外部メモリの記憶内容を検査するセキュリティチェック処理に対応したものであってもよい。

遊技制御用マイクロコンピュータ100が備えるRAM507は、ゲーム制御用のワークエリアを提供する。ここで、RAM507の少なくとも一部は、電源基板101において作成されるバックアップ電源によってバックアップされているバックアップRAMであればよい。すなわち、スロットマシン1への電力供給が停止しても、所定期間はRAM507の少なくとも一部の内容が保存される。

遊技制御用マイクロコンピュータ100が備えるタイマ回路508は、例えば8ビットのプログラマブルタイマを3チャネル(PTC0−PTC2)内蔵して構成され、リアルタイム割込みの発生や時間計測を可能とする。各プログラマブルタイマPTC0−PTC2は、内部システムクロックSCLKに基づいて生成されたカウントクロックの信号変化(例えばハイレベルからローレベルへと変化する立ち下がりタイミング)などに応じて、タイマ値が更新されるものであればよい。

遊技制御用マイクロコンピュータ100は、乱数回路として、例えば16ビット乱数となる数値データを生成する乱数回路509Aと、8ビット乱数となる数値データを生成する乱数回路509Bとを備えている。この実施の形態では、遊技制御基板40の側において、内部抽選用の乱数値を示す数値データが、カウント(更新)可能に制御されればよい。なお、遊技効果を高めるために、これら以外の乱数値が用いられてもよい。こうした遊技の進行を制御するために用いられる乱数は、遊技用乱数ともいう。

CPU505は、乱数回路509A、509Bから抽出した数値データに基づき、例えばRAM507の所定領域(遊技制御カウンタ設定部など)に設けられたランダムカウンタといった、乱数回路509A、509Bとは異なるランダムカウンタを用いて、ソフトウェアによって各種の数値データを加工あるいは更新することで、乱数値の一部または全部を示す数値データをカウントするようにしてもよい。あるいは、CPU505は、乱数回路509A、509Bを用いることなく、例えば遊技制御カウンタ設定部に設けられたランダムカウンタのみを用いて、ソフトウェアによって乱数値を示す数値データの一部をカウント(更新)するようにしてもよい。一例として、ハードウェアとなる16ビットの乱数回路509AからCPU505により抽出された数値データを、ソフトウェアにより加工することで、内部抽選用の乱数値を示す数値データが更新され、それ以外の乱数値MR2〜MR5を示す数値データは、CPU505がランダムカウンタなどを用いてソフトウェアにより更新すればよい。

あるいは、CPU505は、16ビットの乱数回路509Aから抽出した数値データに基づき、ランダムカウンタを用いることで、あるいはランダムカウンタを用いることなく、内部抽選用の乱数値を示す数値データをカウントする。内部抽選用の乱数値は、各役への入賞を許容するかどうかを決定するための乱数値である。例えば、内部抽選用用の乱数値は、「0」〜「65535」の範囲の値をとる。

図17は、16ビットの乱数回路509Aのうち、チャネルch0に対応する回路構成の一例を示すブロック図である。図17に示すように、チャネルch0に対応して16ビット乱数を生成するための回路は、乱数更新クロック選択回路551、乱数生成回路553A、乱数起動設定回路553B、スタート値設定回路553C、乱数列変更回路554A、乱数列変更設定回路554B、最大値比較回路555、ハードラッチセレクタ558A、ハードラッチ乱数値レジスタ559A、ソフトラッチ乱数値レジスタ559Sを備えて構成される。

乱数更新クロック選択回路551は、例えば16ビット乱数初期設定第1KRL1のビット番号[2](チャネルch0の場合)におけるビット値が“0”であるか“1”であるかに応じて、内部システムクロックSCLKまたは乱数用クロックRCKの2分周(RCK/2)を選択して、乱数更新クロックRGKとして出力する。乱数更新クロック選択回路551から出力された乱数更新クロックRGKは、乱数生成回路553Aのクロック端子に入力されて、乱数生成回路553Aにおけるカウント値の歩進に用いられる。

なお、乱数更新クロック選択回路551によって選択された内部システムクロックSCLKまたは乱数用クロックRCKの2分周(RCK/2)が、所定のクロック用フリップフロップのクロック端子に入力されてもよい。クロック用フリップフロップでは、逆相出力端子(反転出力端子)がデータ入力端子に接続されている。そして、正相出力端子(非反転出力端子)から乱数更新クロックRGKを出力する一方で、逆相出力端子(反転出力端子)からラッチ用クロックを出力する。この場合、クロック用フリップフロップは、クロック端子に入力されるクロック信号における信号状態が所定の変化をしたときに、正相出力端子(非反転出力端子)および逆相出力端子(反転出力端子)からの出力信号における信号状態を変化させる。例えば、クロック用フリップフロップは、クロック信号の信号状態がローレベルからハイレベルへと変化する立ち上がりのタイミング、あるいは、クロック信号の信号状態がハイレベルからローレベルへと変化する立ち下がりのタイミングのうち、いずれか一方のタイミングにて、データ入力端子における入力信号を取り込む。このとき、正相出力端子(非反転出力端子)からは、データ入力端子にて取り込まれた入力信号が反転されることなく出力される一方で、逆相出力端子(反転出力端子)からは、データ入力端子にて取り込まれた入力信号が反転されて出力される。こうして、クロック用フリップフロップの正相出力端子(非反転出力端子)からはクロック信号における発振周波数の1/2となる発振周波数を有する乱数更新クロックRGKが出力される一方、逆相出力端子(反転出力端子)からは乱数更新クロックRGKの逆相信号(反転信号)、すなわち乱数更新クロックRGKと同一周波数で乱数更新クロックRGKとは位相がπ(=180°)だけ異なるラッチ用クロックが出力される。

乱数用クロックRCKの発振周波数と、制御用クロック生成回路111によって生成される制御用クロックCCLKの発振周波数とは、互いに異なる周波数となっており、また、いずれか一方の発振周波数が他方の発振周波数の整数倍になることがない。一例として、制御用クロックCCLKの発振周波数が11.0MHzである一方で、乱数用クロックRCKの発振周波数は9.7MHzであればよい。そのため、乱数更新クロックRGKやラッチ用クロックはいずれも、CPU505に供給される制御用クロックCCLKとは異なる周期で信号状態が変化する発振信号となる。すなわち、クロック用フリップフロップは、乱数用クロック生成回路112によって生成された乱数用クロックRCKに基づき、カウント値を更新するための乱数更新クロックRGKや、複数の乱数取得用クロックとなるラッチ用クロックとして、制御用クロックCCLKや内部システムクロックSCLK(制御用クロックCCLKを2分周したもの)とは異なる周期で信号状態が変化する発振信号を生成する。

乱数生成回路553Aは、例えば16ビットのカウンタなどから構成され、乱数更新クロック選択回路551から出力される乱数更新クロックRGKなどの入力に基づき、数値データを更新可能な所定の範囲において所定の初期値から所定の最終値まで循環的に更新する回路である。例えば乱数生成回路553Aは、所定のクロック端子への入力信号である乱数更新クロックRGKにおける立ち下がりエッジに応答して、「0」から「65535」までの範囲内で設定された初期値から「65535」まで1ずつ加算するように数値データをカウントアップして行く。そして、「65535」までカウントアップした後には、「0」から初期値よりも1小さい最終値となる数値まで1ずつ加算するようにカウントアップすることで、数値データを循環的に更新する。

乱数起動設定回路553Bは、例えば16ビット乱数初期設定第1KRL1のビット番号[3](チャネルch0の場合)におけるビット値が“0”であるか“1”であるかに応じて異なる乱数生成開始条件が成立したときに、16ビット乱数の生成動作を開始させる設定を行う。より具体的には、対応するビット値が“0”である場合には、16ビット乱数における最大値をユーザプログラム(ソフトウェア)で指定したときに、乱数生成回路553Aを起動して16ビット乱数の生成動作を開始させる。一方、対応するビット値が“1”である場合には、遊技制御用マイクロコンピュータ100の動作状態がセキュリティモードからユーザモードに移行したときに、乱数生成回路553Aを起動して16ビット乱数の生成動作を開始させる。

スタート値設定回路553Cは、例えば16ビット乱数初期設定第3KRL3のビット番号[1−0](チャネルch0の場合)におけるビット値に応じて、乱数生成回路553Aにより生成されるカウント値におけるスタート値を設定する。例えば、スタート値設定回路553Cは、対応するビット値が“00”または“01”であればスタート値をデフォルト値である「0000H」に設定し、そのビット値が“00”であればシステムリセットごとにスタート値の変更を行わない一方、そのビット値が“01”であればシステムリセットごとにスタート値の変更を行う。また、対応するビット値が“10”または“11”であればスタート値をIDナンバーに基づく値に設定し、そのビット値が“10”であればシステムリセットごとにスタート値の変更を行わない一方、そのビット値が“11”であればシステムリセットごとにスタート値の変更を行う。

システムリセットごとにスタート値の変更を行う場合には、初期設定時にフリーランカウンタ509Cのカウント値をそのまま用いること、あるいは、そのカウント値を所定の演算関数(例えばハッシュ関数)に代入して得られた値を用いることなどにより、スタート値がランダムに決定されればよい。フリーランカウンタ509Cは、例えば遊技制御用マイクロコンピュータ100のRAM507におけるバックアップ領域といった、遊技制御基板40におけるバックアップ箇所と共通のバックアップ電源を用いてバックアップされるものであればよい。あるいは、フリーランカウンタ509Cは、RAM507におけるバックアップ領域などに用いられるバックアップ電源とは別個に設けられた電源によりバックアップされてもよい。こうして、フリーランカウンタ509Cがバックアップ電源によってバックアップされることで、電力供給が停止した場合でも、所定期間はフリーランカウンタ509Cにおけるカウント値が保存されることになる。

フリーランカウンタ509Cがバックアップ電源によってバックアップされるものに限定されず、例えばシステムリセットの発生時にフリーランカウンタ509Cのカウント値を所定の内蔵レジスタ(例えば乱数スタート値用レジスタ)に格納し、この内蔵レジスタがバックアップ電源によってバックアップされるようにしてもよい。そして、初期設定時に乱数スタート値用レジスタの格納値をそのまま用いること、あるいは、その格納値を所定の演算関数に代入して得られた値を用いることなどにより、スタート値がランダムに決定されてもよい。この場合、フリーランカウンタ509Cにおけるカウント値を読み出して乱数スタート値用レジスタに格納するタイミングは、システムリセットの発生時に限定されず、予め定められた任意のタイミングとしてもよい。フリーランカウンタ509Cは、乱数回路509A、509Bに内蔵されて数値データのスタート値をランダムに決定するために用いられる専用のフリーランカウンタであってもよい。すなわち、フリーランカウンタ509Cは、セキュリティ時間を延長する際に延長時間のランダムな決定に用いられるフリーランカウンタとは別個の構成として設けられたものであってもよい。あるいは、フリーランカウンタ509Cとして、遊技制御用マイクロコンピュータ100には内蔵されるが乱数回路509A、509Bの外部に設けられて、セキュリティ時間を延長する際に延長時間のランダムな決定に用いられるフリーランカウンタと共通のものを用いてもよい。この場合には、数値データのスタート値を決定する処理と、セキュリティ時間中の延長時間をランダムに決定する処理とにおいて、例えばカウント値を代入する演算関数を互いに異ならせること、あるいは、一方の決定処理ではカウント値をそのまま用いるのに対して他方の決定処理ではカウント値を所定の演算関数に代入して得られた値を用いることなどにより、スタート値の決定手法と延長時間の決定手法とを異ならせてもよい。

フリーランカウンタ509Cは、例えば8ビットのプログラマブルカウンタを4チャネル(PCC0−PCC3)内蔵してもよい。各プログラマブルカウンタPCC0−PCC3は、内部システムクロックSCLKの信号変化、あるいは、プログラマブルカウンタPCC0−PCC3のいずれかにおけるタイムアウトの発生などに応じて、カウント値が更新されるものであればよい。

フリーランカウンタ509Cは、乱数回路509A、509Bに内蔵されてもよいし、乱数回路509A、509Bには内蔵されないものの遊技制御用マイクロコンピュータ100の内部回路に含まれてもよい。また、フリーランカウンタ509Cは、セキュリティ時間を延長する際の延長時間をシステムリセット毎にランダムに決定するために用いられるフリーランカウンタと、同一のカウンタであってもよいし、別個に設けられたカウンタであってもよい。

乱数列変更回路554Aは、乱数生成回路553Aにより生成された数値データの順列を所定の乱数更新規則に従った順列に変更可能とする回路である。例えば、乱数列変更回路554Aは、乱数生成回路553Aから出力される数値データにおけるビットの入れ替えや転置などのビットスクランブル処理を実行する。また、乱数列変更回路554Aは、例えばビットスクランブル処理に用いるビットスクランブル用キーやビットスクランブルテーブルを変更することなどにより、数値データの順列を変更することができる。

乱数列変更設定回路554Bは、例えば16ビット乱数初期設定第1KRL1のビット番号[1−0](チャネルch0の場合)におけるビット値などに応じて、乱数列変更回路554Bにおける乱数更新規則を変更する設定を行うための回路である。例えば、乱数列変更設定回路554Bは、対応するビット値が“00”であれば乱数更新規則を変更しない設定とする一方、そのビット値が“01”であればソフトウェアでの変更要求に応じて乱数更新規則を変更し、そのビット値が“10”であれば2周目から自動で乱数更新規則を変更する。また、そのビット値が“11”であれば1周目から自動で乱数更新規則を変更する。

乱数列変更回路554Bは、16ビット乱数初期設定第1KRL1などにおいて対応するビット値が“01”でありソフトウェアによる乱数更新規則の変更を行う場合に、図9(B)に示すような遊技制御用マイクロコンピュータ100が備える内蔵レジスタのうち、乱数列変更レジスタRDSC(アドレスFE73H)を用いて、乱数更新規則の変更を制御する。図18(A)は、チャネルch0の16ビット乱数に対応した乱数列変更レジスタRDSCの構成例を示している。図18(B)は、乱数列変更レジスタRDSCに格納される乱数列変更要求データの設定内容を示している。乱数列変更レジスタRDSCのビット番号[0]に格納される乱数列変更要求データRDSC0は、乱数更新規則をソフトウェアにより変更する場合に、乱数列の変更要求の有無を示している。図18(B)に示す例では、ソフトウェアにより乱数列の変更要求がないときに、乱数列変更要求データRDSC0のビット値が“0”となる一方、乱数列の変更要求があったときには、そのビット値が“1”となる。

図19は、乱数更新規則をソフトウェアにより変更する場合の動作例を示している。この場合、乱数生成回路553Aから出力されるカウント値順列RCNが所定の初期値から所定の最終値まで循環的に更新されたときに、乱数列変更要求データRDSC0が“1”であることに応答して、乱数更新規則を変更する。図19に示す動作例では、始めに乱数列変更回路554Aから出力される乱数列RSNが、「0→1→…→65535」となっている。この後、CPU505がROM506に格納されたユーザプログラムを実行することによって、所定のタイミングで乱数列変更レジスタRDSCのビット番号[0]に“1”が書き込まれたものとする。

そして、16ビット乱数初期設定第1KRL1のビット番号[1−0]が“01”であることに対応して、乱数列変更設定回路554Bが乱数列変更要求データRDSC0を読み出し、そのビット値が“1”であることに応答して、乱数更新規則を変更するための設定を行う。このとき、乱数列変更設定回路554Bは、乱数生成回路553Aから出力されたカウント値順列RCNが所定の最終値に達したことに応じて、例えば予め用意された複数種類の乱数更新規則のいずれかを選択することなどにより、乱数更新規則を変更する。図19に示す動作例では、乱数列変更回路554Aが乱数生成回路553Aから出力されたカウント値順列RCNにおける最終値に対応する数値データ「65535」を出力した後、乱数列変更要求データRDSC0に応じて乱数更新規則を変更する。その後、乱数列変更回路554Aは、変更後の乱数更新規則に従った乱数列RSNとして、「65535→65534→…→0」を出力する。乱数列変更レジスタRDSCは、乱数列変更設定回路554Bにより乱数列変更要求データRDSC0が読み出されたときに初期化される。そのため、再び乱数列変更レジスタRDSCのビット番号[0]にビット値“1”が書き込まれるまでは、乱数列変更回路554Aから出力される乱数列RSNが、「65535→65534→…→0」となる。

CPU505がROM506に格納されたユーザプログラムを実行することによって、乱数列変更レジスタRDSCのビット番号[0]に再びビット値“1”が書き込まれると、乱数更新規則が再度変更される。図19に示す動作例では、乱数列変更回路554Aが乱数列RSNにおける最終値に対応する数値データ「0」を出力したときに、乱数列変更要求データRDSC0としてビット値“1”が書き込まれたことに応じて乱数更新規則を変更する。その後、乱数列変更回路554Aは、変更後の乱数更新規則に従った乱数列RSNとして、「0→2→…→65534→1→…→65535」を出力する。

図20は、乱数更新規則を自動で変更する場合の動作例を示している。この場合、乱数生成回路553Aから出力されるカウント値順列RCNが所定の初期値から所定の最終値まで循環的に更新されたことに応じて、乱数列変更設定回路554Bが自動的に乱数更新規則を変更する。図20に示す動作例では、始めに乱数列変更回路554Aから出力される乱数列RSNが、「0→1→…→65535」となっている。

そして、乱数列変更回路554Aから出力された乱数列RSNが所定の最終値に達したときに、乱数列変更設定回路554Bは、予め用意された複数種類の更新規則のうちから予め定められた順序に従って更新規則を選択することにより、更新規則を変更するようにしてもよい。あるいは、乱数列変更設定回路554Bは、複数種類の更新規則のうちから任意の更新規則を選択することにより、更新規則を変更するようにしてもよい。図20に示す動作例では、1回目の乱数更新規則の変更により、乱数列変更回路554Aから出力される乱数列RSNが、「65535→65534→…→0」となる。その後、2回目の乱数更新規則の変更により、乱数列変更回路554Aから出力される乱数列RSNは、「0→2→…→65534→1→…→65535」となる。図20に示す動作例では、3回目の乱数更新規則の変更により、乱数列変更回路554Aから出力される乱数列RSNは、「65534→0→…→32768」となる。4回目の乱数更新規則の変更が行われたときには、乱数列変更回路554Aから出力される乱数列RSNが、「16383→49151→…→49150」となる。5回目の乱数更新規則の変更が行われたときには、乱数列変更回路554Aから出力される乱数列RSNが、「4→3→…→465531」となる。

このように、乱数列変更回路554Aは、乱数生成回路553Aから出力されたカウント値順列RCNを、乱数列変更設定回路554Bの設定により予め定められた乱数更新規則に基づいて変更することで、数値データを所定手順により更新した乱数列RSNを出力することができる。

最大値比較回路555は、予めユーザ設定された乱数の最大値と、乱数列変更回路554Aから出力される乱数列RSNを比較し、最大値より大きい出力値があった場合に、乱数生成回路553Aに対しリセットとリスタートを指示する。最大値比較回路555は、図9(B)に示すような遊技制御用マイクロコンピュータ100が備える内蔵レジスタのうち、乱数最大値設定レジスタRMX(アドレスFE67−FE72H)を用いて、乱数最大値を設定する。図21(A)および(B)は、乱数最大値設定レジスタRMXのうち、チャネルch0の16ビット乱数に対応した乱数最大値設定レジスタRL0MXの構成例を示している。CPU505は、例えばユーザプログラムによって予め指定された乱数の最大値を示す乱数最大値設定データを、乱数最大値設定レジスタRL0MXなどに書き込む。乱数最大値設定レジスタRL0MXに乱数最大値設定データが書き込まれたときには、チャネルch0の16ビット乱数について最大値が設定される。16ビット乱数の最大値は、例えば「256」〜「65535」の範囲で任意の値を設定できればよい。例えば16ビット乱数初期設定第1KRL1のビット番号[3](チャネルch0の場合)におけるビット値が“0”である場合には、16ビット乱数について最大値の設定が可能になり、その最大値を設定することで、16ビット乱数の生成動作をユーザプログラム(ソフトウェア)で開始させることができる。

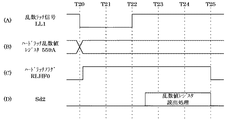

ハードラッチセレクタ558Aは、乱数ラッチ信号LL1として出力する信号を、PIP510の入力ポートPI0〜入力ポートPI5における入力信号のうちから選択する。ハードラッチセレクタ558Aは、図9(B)に示すような遊技制御用マイクロコンピュータ100が備える内蔵レジスタのうち、ハードラッチ選択レジスタRLS(アドレスFE5B−FE61H)に含まれるハードラッチ選択レジスタRL0LS0を用いて、乱数ラッチ信号LL1として出力する信号を選択する。図22(A)は、ハードラッチ選択レジスタRL0LS0として用いられるハードラッチ選択レジスタRL0LSの構成例を示している。図22(B)は、ハードラッチ選択レジスタRL0LSに格納されるハードラッチ選択データの各ビットにおける設定内容の一例を示している。

ハードラッチ選択レジスタRL0LSのビット番号[3]に格納されるハードラッチ選択データRL03LSは、ハードウェアによる乱数値の取込条件を示している。図22(B)に示す例では、ハードラッチ選択データRL03LSのビット値が“0”である場合に、対応するハードラッチ乱数値レジスタ(例えばハードラッチ乱数値レジスタ559A)の格納値を読み出すことにより、次の値をラッチ可能に設定する。一方、ラッチ選択データRL03LSのビット値が“1”である場合には、対応するハードラッチ乱数値レジスタの格納値を読み出さなくても、次の値をラッチ可能に設定する。

ハードラッチ選択レジスタRL0LSのビット番号[2−0]に格納されるハードラッチ選択データRL02LS〜RL00LSは、対応する乱数ラッチ信号(例えば乱数ラッチ信号LL1、LL2のいずれか)として出力する信号の外部端子入力を選択するための設定データである。図22(B)に示す例では、ラッチ選択データRL02LS〜RL00LSの値に応じて、入力ポートPI0〜入力ポートPI5のいずれかにおける入力を、外部端子入力として選択することができる。

この実施の形態では、入力ポートPI0にスタートスイッチ7からの検出信号SS1が入力される。ハードラッチセレクタ558Aは、ハードラッチ選択レジスタRL0LS0の格納値に基づいて、入力ポートPI0に入力されたスタートスイッチ7からの検出信号SS1を選択し、乱数ラッチ信号LL1として出力する。なお、乱数ラッチ信号LL1は、第1のラッチ用クロックと同期して出力されるようにしてもよい。

スタートスイッチ7からの検出信号SS1は、スタートスイッチ7から直接伝送されるものに限定されない。一例として、スタートスイッチ7からの出力信号がオン状態となっている時間を計測し、計測した時間が所定の時間(例えば3ミリ秒)になったときに、スタートスイッチ7からの検出信号SS1を出力するタイマ回路を設けてもよい。

ハードラッチ乱数値レジスタ559Aはそれぞれ、最大値比較回路555から出力された乱数列RSNにおける数値データを乱数値として格納するレジスタである。ハードラッチ乱数値レジスタ559Aはいずれも16ビット(2バイト)のレジスタであり、例えばチャネルch0に対応してそれぞれ16ビットの乱数値を格納することができる。

ハードラッチ乱数値レジスタ559Aは、ハードラッチセレクタ558Aから供給される乱数ラッチ信号LL1がオン状態となったことに応答して、最大値比較回路555から出力された乱数列RSNにおける数値データを乱数値として取り込んで格納する。ハードラッチ乱数値レジスタ559Aは、CPU505から供給されるレジスタリード信号がオン状態となったときに、読出可能(イネーブル)状態となり、格納されている数値データを内部バス等に出力してもよい。これに対して、レジスタリード信号がオフ状態であるときには、常に同じ値(例えば「65535H」など)を出力して、読出不能(ディセーブル)状態としてもよい。また、ハードラッチ乱数値レジスタ559Aは、乱数ラッチ信号LL1がオン状態である場合に、レジスタリード信号を受信不可能な状態となるようにしてもよい。さらに、ハードラッチ乱数値レジスタ559Aは、乱数ラッチ信号LL1がオン状態となるより前にレジスタリード信号がオン状態となっている場合に、乱数ラッチ信号LL1を受信不可能な状態となるようにしてもよい。

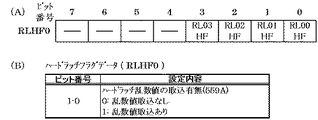

ハードラッチ乱数値レジスタ559Aは、図9(B)に示すような遊技制御用マイクロコンピュータ100が備える内蔵レジスタのうち、乱数ハードラッチフラグレジスタRHF(アドレスFE82−FE84H)と、乱数割込み制御レジスタRIC(アドレスFE64−FE66H)とを用いて、乱数ラッチ時の動作管理や割込み制御を可能にする。乱数ハードラッチフラグレジスタRHFは、ハードラッチ乱数値レジスタ559Aに対応して、乱数値となる数値データがラッチされたか否かを示す乱数ラッチフラグを格納するレジスタである。例えば、乱数ハードラッチフラグレジスタRHFでは、ハードラッチ乱数値レジスタ559Aに対応した乱数ラッチフラグの状態(オンまたはオフ)を示すデータが格納される。ハードラッチ乱数値レジスタ559Aに数値データが取り込まれて格納されたときには、対応する乱数ラッチフラグがオン状態となることで、新たな数値データの格納が制限されてもよい。この場合、ハードラッチ乱数値レジスタ559Aに格納された数値データが読み出されたときに、対応する乱数ラッチフラグがオフ状態となることで、新たな数値データの格納が許可されればよい。乱数割込み制御レジスタRICは、ハードラッチ乱数値レジスタ559Aに乱数値となる数値データがラッチされたときに発生する割込みの許可/禁止を設定するレジスタである。

図23(A)は、乱数ハードラッチフラグレジスタRHFの構成例を示している。図23(B)は、乱数ハードラッチフラグレジスタRHFに格納されるハードラッチフラグRLHF0となる各ビットにおける設定内容の一例を示している。乱数ハードラッチフラグレジスタRHFのビット番号[1−0]に格納されるハードラッチフラグデータRL01HF、RL00HFは、ハードラッチ乱数値レジスタRL0HV0となるハードラッチ乱数値レジスタ559Aに数値データが取り込まれたか否かを示す乱数ラッチフラグとなる。図23(B)に示す例では、ハードラッチ乱数値レジスタRL0HV0(559A)に数値データが取り込まれていないときに(乱数値取込なし)、ハードラッチフラグデータRL01HF、RL00HFのビット値がいずれも“0”となって乱数ラッチフラグがオフ状態にクリアされる一方、数値データが取り込まれたときには(乱数値取込あり)、それらのビット値が“1”となって乱数ラッチフラグがオン状態にセットされる。

図22(A)および(B)に示すハードラッチ選択レジスタRL0LSのビット番号[3]におけるビット値が“0”である場合には、各乱数ラッチフラグがオンであるときに、それらの乱数ラッチフラグと対応付けられたハードラッチ乱数値レジスタRL0HV0(559A)における新たな数値データの格納が制限(禁止)される。すなわち、ハードラッチ乱数値レジスタRL0HV0(559A)に数値データが取り込まれたか否かを示すハードラッチフラグデータRL01HF、RL00HFのビット値がいずれも“1”となって乱数ラッチフラグがオン状態であるときには、ハードラッチ乱数値レジスタRL0HV0(559A)に格納された数値データを変更することができず、新たな数値データの格納(取り込み)が制限(禁止)される。これに対して、各乱数ラッチフラグがオフであるときには、それらの乱数ラッチフラグと対応付けられたハードラッチ乱数値レジスタRL0HV0(559A)における新たな数値データの格納が許可される。すなわち、ハードラッチフラグデータRL01HF、RL00HFのビット値がいずれも“0”となって乱数ラッチフラグがオフ状態であるときには、ハードラッチ乱数値レジスタRL0HV0(559A)に格納された数値データを変更することができ、新たな数値データの格納(取り込み)が許可される。

なお、ハードラッチフラグデータRL03HF〜RL00HFのビット値は、“0”となることで対応する乱数ラッチフラグがオフ状態にクリアされる一方で“1”となることでオン状態にセットされる正論理のものに限定されず、“1”となることで対応する乱数ラッチフラグがオフ状態となる一方で“0”となることでオン状態となる負論理のものであってもよい。すなわち、各乱数ラッチフラグは、対応するハードラッチ乱数値レジスタRL0HV0(559A)に数値データが格納されたときにオン状態となり新たな数値データの格納が制限(禁止)される一方で、対応するハードラッチ乱数値レジスタRL0HV0(559A)の読み出しが行われたときにオフ状態となり新たな数値データの格納が許可されるものであればよい。

図24(A)は、乱数割込み制御レジスタRICに含まれるチャネルch0の16ビット乱数に対応したハードラッチ割込み制御レジスタRLIC0の構成例を示している。図24(B)は、ハードラッチ割込み制御レジスタRLIC0に格納されるハードラッチ割込み制御データの各ビットにおける設定内容の一例を示している。ハードラッチ割込み制御レジスタRLIC0のビット番号[1−0]に格納されるハードラッチ割込み制御データRL01IE、RL00IEは、ハードラッチ乱数値レジスタRL0HV0となるハードラッチ乱数値レジスタ559Aに数値データが取り込まれたときに発生する割込みを、許可するか禁止するかの割込み制御設定を示している。図24(B)に示す例では、ハードラッチ乱数値レジスタRL0HV0(559A)への取込時における割込みを禁止する場合に(割込み禁止)、ハードラッチ割込み制御データRL01IE、RL00IEのビット値をいずれも“0”とする一方、この割込みを許可する場合には(割込み許可)、それらのビット値を“1”とする。

ソフトラッチ乱数値レジスタ559Sは、最大値比較回路555から出力された乱数列RSNにおける数値データを、ユーザプログラム(ソフトウェア)により乱数値として格納するレジスタである。ソフトラッチ乱数値レジスタ559Sは、16ビット(2バイト)のレジスタであり、例えばチャネルch0に対応して16ビットの乱数値を格納することができればよい。

ソフトラッチ乱数値レジスタ559Sには、図9(B)に示すような遊技制御用マイクロコンピュータ100が備える内蔵レジスタのうち、乱数ソフトラッチレジスタRDSL(アドレスFE74H)を用いて、乱数ソフトラッチ信号が入力される。図25(A)は、チャネルch0に対応した乱数ソフトラッチレジスタRDSLの構成例を示している。図25(B)は、乱数ソフトラッチレジスタRDSLに格納される乱数ソフトラッチデータの設定内容を示している。乱数ソフトラッチレジスタRDSLのビット番号[0]に格納される乱数ソフトラッチデータRDSL0は、チャネルch0の16ビット乱数をソフトウェアによりラッチする場合に、乱数値のラッチ要求の有無を示している。図25(B)に示す例では、ソフトウェアにより乱数値のラッチ要求がないときに、乱数ソフトラッチデータRDSL0のビット値が“0”となる一方、ソフトウェアにより乱数値のラッチ要求があったときには、そのビット値が“1”となる。

ソフトラッチ乱数値レジスタ559Sは、乱数ソフトラッチレジスタRDSLに格納される乱数ソフトラッチデータRDSL0のビット値が“1”となったことに応答して、最大値比較回路555から出力された乱数列RSNにおける数値データを乱数値として取り込んで格納する。ソフトラッチ乱数値レジスタ559Sは、図9(B)に示すような遊技制御用マイクロコンピュータ100が備える内蔵レジスタのうち、乱数ソフトラッチフラグレジスタRDSF(アドレスFE75H)を用いて、乱数ラッチ時の動作管理を可能にする。乱数ソフトラッチフラグレジスタRDSFは、ソフトラッチ乱数値レジスタ559Sに乱数値となる数値データがラッチされたか否かを示す乱数ソフトラッチフラグを格納するレジスタである。図26(A)は、乱数ソフトラッチフラグレジスタRDSFの構成例を示している。図26(B)は、乱数ソフトラッチフラグレジスタRDSFに格納されるソフトラッチフラグデータの設定内容を示している。乱数ソフトラッチフラグレジスタRDSFのビット番号[0]に格納されるソフトラッチフラグデータRDSF0は、チャネルch0の16ビット乱数がソフトラッチ乱数値レジスタRL0SVとなるソフトラッチ乱数値レジスタ559Sに取り込まれたか否かを示す乱数ソフトラッチフラグとなる。

図26(B)に示す例では、ソフトラッチ乱数値レジスタRL0SVに数値データが取り込まれていないときに(乱数値取込なし)、ソフトラッチフラグデータRDSF0のビット値が“0”となって乱数ソフトラッチフラグがオフ状態にクリアされる一方、数値データが取り込まれたときには(乱数値取込あり)、そのビット値が“1”となって乱数ソフトラッチフラグがオン状態にセットされる。乱数ソフトラッチフラグがオンであるときには、ソフトラッチ乱数値レジスタRL0SVにおける新たな数値データの格納が制限(禁止)される。すなわち、ソフトラッチ乱数値レジスタRL0SVに数値データが取り込まれたか否かを示すソフトラッチフラグデータRDSF0のビット値が“1”となって乱数ソフトラッチフラグがオン状態であるときには、ソフトラッチ乱数値レジスタRL0SVに格納された数値データを変更することができず、新たな数値データの格納(取り込み)が制限(禁止)される。これに対して、乱数ソフトラッチフラグがオフであるときには、ソフトラッチ乱数値レジスタRL0SVにおける新たな数値データの格納が許可される。すなわち、ソフトラッチフラグデータRDSF0のビット値が“0”となって乱数ソフトラッチフラグがオフ状態であるときには、ソフトラッチ乱数値レジスタRL0SVに格納された数値データを変更することができ、新たな数値データの格納(取り込み)が許可される。

16ビットの乱数回路509Aでは、チャネルch1〜ch3についてもチャネルch0と同様に、独立して16ビット乱数を発生させるための回路が設けられていればよい。なお、チャネルch0に対応して16ビット(2バイト)のハードラッチ乱数値レジスタ559Aが2つ設けられる一方、チャネルch1〜ch3のそれぞれに対応して16ビット(2バイト)のハードラッチ乱数値レジスタが1つだけ設けられてもよい。

8ビットの乱数回路509Bには、チャネルch0〜ch3のそれぞれに対応して、8ビット乱数を独立して発生させるための回路が設けられていればよい。例えば、チャネルch0に対応して8ビット乱数を生成するための回路は、図17に示した回路を、8ビット乱数の生成に適合するように構成したものであればよく、乱数更新クロック選択回路、乱数生成回路、乱数起動設定回路、乱数列変更回路、乱数列変更設定回路、最大値比較回路、ハードラッチセレクタ、ハードラッチ乱数値レジスタ、ソフトラッチ乱数値レジスタを備えて構成されればよい。

図7に示す構成例では、乱数回路509A、509Bが遊技制御用マイクロコンピュータ100に内蔵されている。これに対して、乱数回路509A、509Bは、遊技制御用マイクロコンピュータ100とは異なる乱数回路チップとして、遊技制御用マイクロコンピュータ100に外付けされるものであってもよい。この場合、スタートスイッチ7からの検出信号SS1をスイッチ回路114の内部にて分岐し、一方を遊技制御用マイクロコンピュータ100が備えるPIP510の入力ポートPI0へと入力させて、他方を乱数回路509Aが備えるハードラッチセレクタ558Aの入力端子へと入力させればよい。遊技制御用マイクロコンピュータ100との間では、例えば遊技制御用マイクロコンピュータ100が備えるクロック回路502からシステムクロック出力端子CLKOを介して出力された内部システムクロックSCLKを乱数回路509Aが備える乱数更新クロック選択回路551やクロック用フリップフロップへと入力させたり、遊技制御用マイクロコンピュータ100が備える外部バスインタフェース501に接続されたアドレスバスやデータバス、制御信号線などを介して、ハードラッチ乱数値レジスタRL0HV0やハードラッチ乱数値レジスタRL0HV1に格納された数値データの読み出しなどが行われたりすればよい。

また、乱数回路509A、509Bが遊技制御用マイクロコンピュータ100に外付けされる場合にも、各乱数ラッチフラグの状態(オン/オフ)に応じて、ハードラッチ乱数値レジスタRL0HV0やハードラッチ乱数値レジスタRL0HV1への新たな数値データの格納が制限(禁止)あるいは許可されるようにすればよい。図9(B)に示す内蔵レジスタのうち、例えばハードラッチ選択レジスタRLSや乱数割込み制御レジスタRIC、乱数最大値設定レジスタRMX、乱数列変更レジスタRDSC、乱数ソフトラッチレジスタRDSL、乱数ソフトラッチフラグレジスタRDSF、ソフトラッチ乱数値レジスタRSV、乱数ハードラッチフラグレジスタRHF、ハードラッチ乱数値レジスタRHVといった、乱数回路509A、509Bが使用する各種レジスタは、遊技制御用マイクロコンピュータ100には内蔵されず、遊技制御用マイクロコンピュータ100に外付けされた乱数回路509A、509Bに内蔵されるようにしてもよい。この場合、遊技制御用マイクロコンピュータ100のCPU505は、例えば外部バスインタフェース501などを介して、乱数回路509A、509Bに内蔵された各種レジスタの書き込みや読み出しを行うようにすればよい。

図7に示す遊技制御用マイクロコンピュータ100が備えるPIP510は、例えば8ビット幅の入力専用ポートであり、専用端子となる入力ポートPI0〜入力ポートPI4と、機能兼用端子となる入力ポートPI5〜入力ポートPI7とを含んでいる。入力ポートPI5は、割り込みコントローラ504Bに接続される外部マスカブル割込み端子XINTと兼用される。入力ポートPI6は、割り込みコントローラ504Bに接続される外部ノンマスカブル割込み端子XNMIと兼用される。入力ポートPI7は、シリアル通信回路511が使用する受信端子RX0と兼用される。入力ポートPI5〜入力ポートPI7の使用設定は、プログラム管理エリアに記憶される機能設定により指示される。

PIP510は、遊技制御用マイクロコンピュータ100が備える内蔵レジスタのうちの入力ポートレジスタなどを用いて、入力ポートPI0〜入力ポートPI7の状態管理等を行う。入力ポートレジスタは、入力ポートPI0〜入力ポートPI7のそれぞれに対応して、外部信号の入力状態を示すビット値が格納されるレジスタである。

遊技制御用マイクロコンピュータ100が備えるシリアル通信回路511は、例えば全二重、非同期、標準NRZ(Non Return to Zero)フォーマットで通信データを取扱う回路である。一例として、シリアル通信回路511は、外部回路との間にて双方向でシリアルデータを送受信可能な第1チャネル送受信回路と、外部回路との間にて単一方向でシリアルデータを送信のみが可能な第2チャネル送信回路とを含んでいればよい。シリアル通信回路511が備える第2チャネル送信回路は、演出制御基板90に搭載されたサブ制御部91との間における単一方向(送信のみ)のシリアル通信に使用されてもよい。これにより、演出制御基板12の側から主基板11に対する信号入力を禁止して、不正行為を防止することができる。

シリアル通信回路511では、例えばオーバーランエラー、ブレークコードエラー、フレーミングエラー、パリティエラーといった、4種類のエラーが通信データの受信時に発生することがあり、いずれかのエラーが発生したときに、受信割込みを発生させることができればよい。オーバーランエラーは、受信済みの通信データがユーザプログラムによってリードされるより前に、次の通信データを受信してしまった場合に発生するエラーである。ブレークコードエラーは、通信データの受信中に所定のブレークコードが検出されたとき発生するエラーである。フレーミングエラーは、受信した通信データにおけるストップビットが“0”である場合に発生するエラーである。パリティエラーは、パリティ機能を使用する設定とした場合、受信した通信データのパリティが、予め指定したパリティと一致しない場合に発生するエラーである。

シリアル通信回路511は、第1割込み制御回路と、第2割込み制御回路とを含んでいてもよい。第1割込み制御回路は、シリアル通信回路511に含まれる第1チャネル送受信回路における割込み発生因子を管理して、通信割込み要求を制御するための回路である。第1割込み制御回路が制御する割込みには、第1チャネル送信割込みと、第1チャネル受信割込みとがある。第1チャネル送信割込みには、送信完了による割込みや、送信データエンプティによる割込みが含まれている。第1チャネル受信割込みには、受信データフルによる割込みや、ブレークコードエラー、オーバーランエラー、フレーミングエラー、パリティエラーといった受信時エラーの発生による割込みが含まれている。第2割込み制御回路は、シリアル通信回路511に含まれる第2チャネル受信回路における割込み発生因子を管理して、通信割込み要求を制御するための回路である。第2割込み制御回路が制御する割込みは、第2チャネル送信割込みである。第2チャネル送信割込みには、送信完了による割込みや、送信データエンプティによる割込みが含まれている。

遊技制御用マイクロコンピュータ100が備えるアドレスデコード回路512は、遊技制御用マイクロコンピュータ100の内部における各機能ブロックのデコードや、外部装置用のデコード信号であるチップセレクト信号のデコードを行うための回路である。チップセレクト信号により、遊技制御用マイクロコンピュータ100の内部回路、あるいは、周辺デバイスとなる外部装置を、選択的に有効動作させて、CPU505からのアクセスが可能となる。

遊技制御用マイクロコンピュータ100が備えるROM506には、ゲームの進行を制御するために用いられる各種の選択用データ、テーブルデータなどが格納される。例えば、ROM506には、CPU505が各種の判定や決定、設定を行うために用意された複数の判定テーブルや決定テーブル、設定テーブルなどを構成するデータが記憶されている。また、ROM506には、CPU505が遊技制御基板40から各種の制御コマンドとなる制御信号を送信するために用いられる複数のコマンドテーブルを構成するテーブルデータなどが記憶されている。

遊技制御用マイクロコンピュータ100が備えるRAM507には、スロットマシン1における遊技の進行などを制御するために用いられる各種のデータを保持する領域として、例えば遊技制御用データ保持エリアが設けられている。RAM507としては、例えばDRAMが使用されており、記憶しているデータ内容を維持するためのリフレッシュ動作が必要になる。CPU505には、このリフレッシュ動作を行うためのリフレッシュレジスタが内蔵されている。例えば、リフレッシュレジスタは8ビットからなり、そのうち下位7ビットはCPU505がROM506から命令フェッチする毎に自動的にインクリメントされる。したがって、リフレッシュレジスタにおける格納値の更新は、CPU505における1命令の実行時間毎に行われることになる。

尚、この実施例では、後述するように、遊技制御用マイクロコンピュータ100には、外部メモリとしてSRAM50が接続されており、このSRAM50は、少なくとも一部が、バックアップ電源によってバックアップされているバックアップRAMである。すなわち、スロットマシンへの電力供給が停止しても、所定期間はSRAM50の少なくとも一部の内容が保存される。尚、本実施例では、SRAM50の全ての領域がバックアップRAMとされており、スロットマシンへの電力供給が停止しても、所定期間はSRAM50の全ての内容が保存される。尚、この実施例において、バックアップRAMとしてのSRAM50には、例えば、電源断が発生したときに、後述する内部抽選に関する制御で用いるデータや、メダルの払出に関する制御で用いるデータ、リールの回転及び停止に関する制御で用いるデータ、コマンドの入出力に関する制御で用いるデータなどが格納される。

遊技制御用マイクロコンピュータ100は、サブ制御部91に各種のコマンドを送信する。遊技制御用マイクロコンピュータ100からサブ制御部91へ送信されるコマンドは一方向のみで送られ、サブ制御部91から遊技制御用マイクロコンピュータ100へ向けてコマンドが送られることはない。

遊技制御用マイクロコンピュータ100は、遊技制御基板40に接続された各種スイッチ類の検出状態が入力ポートから入力される。そして遊技制御用マイクロコンピュータ100は、これら入力ポートから入力される各種スイッチ類の検出状態に応じて段階的に移行する基本処理を実行する。

また、遊技制御用マイクロコンピュータ100は、割込の発生により基本処理に割り込んで割込処理を実行できるようになっている。本実施例では、一定時間間隔(本実施例では、約0.56ms)毎に後述するタイマ割込処理(メイン)を実行する。尚、タイマ割込処理(メイン)の実行間隔は、基本処理において制御状態に応じて繰り返す処理が一巡する時間とタイマ割込処理(メイン)の実行時間とを合わせた時間よりも長い時間に設定されており、今回と次回のタイマ割込処理(メイン)との間で必ず制御状態に応じて繰り返す処理が最低でも一巡することとなる。

また、遊技制御用マイクロコンピュータ100は、割込処理の実行中に他の割込を禁止するように設定されているとともに、複数の割込が同時に発生した場合には、予め定められた順位によって優先して実行する割込が設定されている。尚、割込処理の実行中に他の割込要因が発生し、割込処理が終了してもその割込要因が継続している状態であれば、その時点で新たな割込が発生することとなる。

演出制御基板90には、演出用スイッチ56が接続されており、この演出用スイッチ56の検出信号が入力されるようになっている。

演出制御基板90には、スロットマシン1の前面扉1bに配置された液晶表示器51(図1参照)、演出効果LED52、スピーカ53、54、前述したリールLED55等の演出装置が接続されており、これら演出装置は、演出制御基板90に搭載された後述のサブ制御部91による制御に基づいて駆動されるようになっている。

尚、本実施例では、演出制御基板90に搭載されたサブ制御部91により、液晶表示器51、演出効果LED52、スピーカ53、54、リールLED55等の演出装置の出力制御が行われる構成であるが、サブ制御部91とは別に演出装置の出力制御を直接的に行う出力制御部を演出制御基板90または他の基板に搭載し、サブ制御部91が遊技制御用マイクロコンピュータ100からのコマンドに基づいて演出装置の出力パターンを決定し、サブ制御部91が決定した出力パターンに基づいて出力制御部が演出装置の出力制御を行う構成としても良く、このような構成では、サブ制御部91及び出力制御部の双方によって演出装置の出力制御が行われることとなる。

また、本実施例では、演出装置として液晶表示器51、演出効果LED52、スピーカ53、54、リールLED55を例示しているが、演出装置は、これらに限られず、例えば、機械的に駆動する表示装置や機械的に駆動する役モノなどを演出装置として適用しても良い。

演出制御基板90には、遊技制御用マイクロコンピュータ100と同様にサブCPU91a、ROM91b、RAM91c、I/Oポート91dを備えたマイクロコンピュータにて構成され、演出の制御を行うサブ制御部91、演出制御基板90に接続された液晶表示器51の表示制御を行う表示制御回路92、演出効果LED52、リールLED55の駆動制御を行うLED駆動回路93、スピーカ53、54からの音声出力制御を行う音声出力回路94、電源投入時または電源遮断時などの電源が不安定な状態やサブCPU91aからの初期化命令が一定時間入力されないときにサブCPU91aにリセット信号を与えるリセット回路95、演出制御基板90に接続された演出用スイッチ56から入力された検出信号を検出するスイッチ検出回路96、日付情報及び時刻情報を含む時間情報を出力する時計装置97、スロットマシン1に供給される電源電圧を監視し、電圧低下を検出したときに、その旨を示す電圧低下信号をサブCPU91aに対して出力する電断検出回路98、その他の回路等、が搭載されており、サブCPU91aは、遊技制御基板40から送信されるコマンドを受けて、演出を行うための各種の制御を行うとともに、演出制御基板90に搭載された制御回路の各部を直接的または間接的に制御する。

サブ制御部91は、遊技制御用マイクロコンピュータ100と同様に、割込機能を備えており、遊技制御用マイクロコンピュータ100からのコマンド受信時に割込を発生させて、遊技制御用マイクロコンピュータ100から送信されたコマンドを取得し、バッファに格納するコマンド受信割込処理を実行する。また、サブ制御部91は、システムクロックの入力数が一定数に到達する毎、すなわち一定間隔毎に割込を発生させて所定のタイマ割込処理(サブ)を実行する。

また、サブ制御部91は、遊技制御用マイクロコンピュータ100とは異なり、コマンドの受信に基づいて割込が発生した場合には、タイマ割込処理(サブ)の実行中であっても、当該処理に割り込んでコマンド受信割込処理を実行し、タイマ割込処理(サブ)の契機となる割込が同時に発生してもコマンド受信割込処理を最優先で実行するようになっている。

サブ制御部91が備えるRAM91cは、液晶表示やランプ表示、音出力などの各種演出制御用のワークエリアを提供し、ワークRAMとして使用される。

図27(a)に示すように、遊技制御用マイクロコンピュータ100とSRAM50とは、16ビットのアドレスバス、32ビットのデータバス、CS(チップセレクト)信号線、RD(リード)信号線、WR(ライト)信号線を介して接続されている。

ここで、遊技制御用マイクロコンピュータ100によるSRAM50からのデータの読み出し及び遊技制御用マイクロコンピュータ100からSRAM50へのデータの書き込みの際の信号の入出力状況について説明する。

遊技制御用マイクロコンピュータ100がSRAM50からデータを読み出す場合には、図27(b)に示すように、遊技制御用マイクロコンピュータ100は、アドレスバスにてSRAM50から読み出すデータが格納されているアドレスを指定し、その後、SRAMに対応するCS信号をONとし、さらにデータの読出を命令するRD信号をONとする。

CS信号及びRD信号を検知したSRAM50は、アドレスバスにて指定されたアドレス領域に格納されているデータをRD信号がOFFとなるまで、すなわち遊技制御用マイクロコンピュータ100によるデータの取り込みが完了するまでデータバスに出力する。一方、遊技制御用マイクロコンピュータ100は、データバスからのデータの取り込みが完了することでRD信号をOFFとし、その後、CS信号をOFFとしてSRAM50からのデータの読み出しを完了する。

遊技制御用マイクロコンピュータ100がSRAM50にデータを書き込む場合には、図27(c)に示すように、アドレスバスにてデータの格納先となるアドレスを指定するとともに、SRAM50に書き込むデータをデータバスに出力した後、SRAMに対応するCS信号をONとし、さらにデータの書き込みを命令するWR信号をONとする。

CS信号及びWR信号を検知したSRAM50は、データバスからデータを取り込み、取り込んだデータをアドレスバスにて指定されたアドレス領域に書き込む。その後、遊技制御用マイクロコンピュータ100は、SRAM50によるデータバスからのデータの取り込みが完了するのに十分な時間の経過後、WR信号をOFFとし、SRAMに対応するCS信号をOFFとしてSRAM50へのデータの書き込みを完了する。

本実施例のスロットマシン1は、設定値に応じてメダルの払出率が変わるものである。詳しくは、後述する内部抽選において設定値に応じた当選確率を用いることにより、メダルの払出率が変わるようになっている。設定値は1〜6の6段階からなり、6が最も払出率が高く、5、4、3、2、1の順に値が小さくなるほど払出率が低くなる。すなわち設定値として6が設定されている場合には、遊技者にとって最も有利度が高く、5、4、3、2、1の順に値が小さくなるほど有利度が段階的に低くなる。

設定値を変更するためには、設定キースイッチ37をon状態としてからスロットマシン1の電源をonする必要がある。設定キースイッチ37をon状態として電源をonすると、設定値表示器24にRAM507から読み出された設定値が表示値として表示され、リセット/設定スイッチ38の操作による設定値の変更操作が可能な設定変更状態に移行する。設定変更状態において、リセット/設定スイッチ38が操作されると、設定値表示器24に表示された表示値が1ずつ更新されていく(設定6からさらに操作されたときは、設定1に戻る)。そして、スタートスイッチ7が操作されると表示値を設定値として確定する。そして、設定キースイッチ37がoffされると、確定した表示値(設定値)が遊技制御用マイクロコンピュータ100のRAM507に格納され、遊技の進行が可能な状態に移行する。

また、設定値を確認するためには、ゲーム終了後、賭数が設定されていない状態で設定キースイッチ37をon状態とすれば良い。このような状況で設定キースイッチ37をon状態とすると、設定値表示器24にRAM507から読み出された設定値が表示されることで設定値を確認可能な設定確認状態に移行する。設定確認状態においては、ゲームの進行が不能であり、設定キースイッチ37をoff状態とすることで、設定確認状態が終了し、ゲームの進行が可能な状態に復帰することとなる。

本実施例のスロットマシン1においては、遊技制御用マイクロコンピュータ100は、図34で示すタイマ割込処理(メイン)を実行する毎に、電断監視回路303らの電源断信号が検出されているか否かを判定する停電判定処理(図34のSk2)を行い、停電判定処理において電源断信号が検出されていると判定した場合に、図36で示す電断処理(メイン)を実行する。電断処理(メイン)では、後述するように、プログラムモジュール毎に、SRAM50にバックアップフラグをセットするとともに、そのプログラムモジュールで用いられるデータを計算してチェックサムを生成し、生成したチェックサムをSRAM50に格納する処理を行う。尚、チェックサムとは、RAM507の該当する領域(本実施例では、そのプログラムモジュールで使用されるデータが格納されているワークRAM内の全ての領域)の各ビットに格納されている値の排他的論理和として算出される値である。このため、そのプログラムモジュールで使用されるデータが格納されているワークRAM内の全ての領域に格納されたデータに基づいて排他的論理和を求めた値が0であれば、チェックサムは0となり、そのプログラムモジュールで使用されるデータが格納されているワークRAM内の全ての領域に格納されたデータに基づいて排他的論理和を求めた値が1であれば、チェックサムは1となる。

そして、遊技制御用マイクロコンピュータ100は、システムリセットによるかユーザリセットによるかに関わらず、その起動時において、モジュール毎に、外部メモリ(バックアップRAM)内のそのプログラムモジュールで用いられるデータを格納した全ての領域のデータに基づいてチェックサムを計算するとともに、バックアップフラグを確認し、算出したチェックサムがバックアップされているチェックサムの値と一致するとともに、バックアップフラグもセットされていることを条件に、SRAM50に記憶されているデータに基づいて遊技制御用マイクロコンピュータ100やサブ制御部91の処理状態を電断前の状態に復帰させるが、チェックサムの値が一致しない場合やバックアップフラグがセットされていない場合には、RAM異常と判定する。この際、遊技制御用マイクロコンピュータ100がRAM異常と判定した場合には、RAM異常エラーコードをレジスタにセットしてRAM異常エラー状態に制御し、遊技の進行を不能化させるようになっている。尚、RAM異常エラー状態は、通常のエラー状態と異なり、リセットスイッチ23やリセット/設定スイッチ38を操作しても解除されないようになっており、前述した設定変更状態において新たな設定値が設定されるまで解除されることがない。

尚、本実施例では、RAM507に格納されている全てのデータが停電時においてもSRAM50に格納されてバックアップ電源により保持されるとともに、遊技制御用マイクロコンピュータ100は、電源投入時においてSRAM50のデータが正常であると判定した場合に、SRAM50の格納データに基づいて電断前の制御状態に復帰する構成であるが、RAM507に格納されているデータのうち停電時において制御状態の復帰に必要なデータのみをSRAM50にバックアップし、電源投入時においてバックアップされているデータに基づいて電断前の制御状態に復帰する構成としても良い。

また、電源投入時において電断前の制御状態に復帰させる際に、全ての制御状態を電断前の制御状態に復帰させる必要はなく、遊技者に対して不利益とならない最低限の制御状態を復帰させる構成であれば良く、例えば、入力ポートの状態などを全て電断前の状態に復帰させる必要はない。

本実施例のスロットマシン1は、前述のように遊技状態(通常、内部中、BB(RB))に応じて設定可能な賭数の規定数が定められており、遊技状態に応じて定められた規定数の賭数が設定されたことを条件にゲームを開始させることが可能となる。尚、本実施例では、遊技状態に応じた規定数の賭数が設定された時点で、入賞ラインLNが有効化される。

本実施例のスロットマシン1は、全てのリール2L、2C、2Rが停止した際に、有効化された入賞ラインLN(以下では、有効化された入賞ラインLNを単に入賞ラインLNと呼ぶ)に役と呼ばれる図柄の組み合わせが揃うと入賞となる。役は、同一図柄の組み合わせであっても良いし、異なる図柄を含む組み合わせであっても良い。入賞となる役の種類は、遊技状態に応じて定められているが、大きく分けて、メダルの払い出しを伴う小役と、賭数の設定を必要とせずに次のゲームを開始可能となる再遊技役と、遊技者にとって有利な遊技状態への移行を伴う特別役と、がある。以下では、小役と再遊技役をまとめて一般役とも呼ぶ。遊技状態に応じて定められた各役の入賞が発生するためには、後述する内部抽選に当選して、当該役の当選フラグがRAM507に設定されている必要がある。

尚、これら各役の当選フラグのうち、小役及び再遊技役の当選フラグは、当該フラグが設定されたゲームにおいてのみ有効とされ、次のゲームでは無効となるが、特別役の当選フラグは、当該フラグにより許容された役の組み合わせが揃うまで有効とされ、許容された役の組み合わせが揃ったゲームにおいて無効となる。すなわち特別役の当選フラグが一度当選すると、例え、当該フラグにより許容された役の組み合わせを揃えることができなかった場合にも、その当選フラグは無効とされずに、次のゲームへ持ち越されることとなる。

内部抽選は、上記した各役への入賞を許容するか否かを、全てのリール2L、2C、2Rの表示結果が導出表示される以前に(実際には、スタートスイッチ7の検出時)決定するものである。内部抽選では、まず、スタートスイッチ7の検出時に内部抽選用の乱数値(0〜65535の整数)を取得する。詳しくは、RAM507に割り当てられた乱数値格納ワークの値を同じくRAM507に割り当てられた抽選用ワークに設定する。そして、遊技状態及び特別役の持ち越しの有無に応じて定められた各役について、抽選用ワークに格納された数値データと、遊技状態を特定するための遊技状態フラグの値、後述するRTを特定するためのRTフラグの値、賭数及び設定値に応じて定められた各役の判定値数に応じて行われる。

内部抽選では、内部抽選の対象となる役、現在の遊技状態フラグ値、RTフラグ値及び設定値に対応して定められた判定値数を、内部抽選用の乱数値(抽選用ワークに格納された数値データ)に順次加算し、加算の結果がオーバーフローしたときに、当該役に当選したものと判定される。このため、判定値数の大小に応じた確率(判定値数/65536)で役が当選することとなる。

そして、いずれかの役の当選が判定された場合には、当選が判定された役に対応する当選フラグをRAM507に割り当てられた内部当選フラグ格納ワークに設定する。内部当選フラグ格納ワークは、2バイトの格納領域にて構成されており、そのうちの上位バイトが、特別役の当選フラグが設定される特別役格納ワークとして割り当てられ、下位バイトが、一般役の当選フラグが設定される一般役格納ワークとして割り当てられている。詳しくは、特別役が当選した場合には、当該特別役が当選した旨を示す特別役の当選フラグを特別役格納ワークに設定し、一般役格納ワークに設定されている当選フラグをクリアする。また、一般役が当選した場合には、当該一般役が当選した旨を示す一般役の当選フラグを一般役格納ワークに設定する。尚、いずれの役及び役の組み合わせにも当選しなかった場合には、一般役格納ワークのみクリアする。

次に、リール2L、2C、2Rの停止制御について説明する。

遊技制御用マイクロコンピュータ100は、リールの回転が開始したとき、及びリールが停止し、かつ未だ回転中のリールが残っているときに、ROM506に格納されているテーブルインデックス及びテーブル作成用データを参照して、回転中のリール別に停止制御テーブルを作成する。そして、ストップスイッチ8L、8C、8Rのうち、回転中のリールに対応するいずれかの操作が有効に検出されたときに、該当するリールの停止制御テーブルを参照し、参照した停止制御テーブルの滑りコマ数に基づいて、操作されたストップスイッチ8L、8C、8Rに対応するリール2L、2C、2Rの回転を停止させる制御を行う。

テーブルインデックスには、内部抽選による当選フラグの設定状態(以下、内部当選状態と呼ぶ)別に、テーブルインデックスを参照する際の基準アドレスから、テーブル作成用データが格納された領域の先頭アドレスを示すインデックスデータが格納されているアドレスまでの差分が登録されている。これにより内部当選状態に応じた差分を取得し、基準アドレスに対してその差分を加算することで該当するインデックスデータを取得することが可能となる。尚、役の当選状況が異なる場合でも、同一の制御が適用される場合においては、インデックスデータとして同一のアドレスが格納されており、このような場合には、同一のテーブル作成用データを参照して、停止制御テーブルが作成されることとなる。

テーブル作成用データは、停止操作位置に応じた滑りコマ数を示す停止制御テーブルと、リールの停止状況に応じて参照すべき停止制御テーブルのアドレスと、からなる。

リールの停止状況に応じて参照される停止制御テーブルは、全てのリールが回転しているか、左リールのみ停止しているか、中リールのみ停止しているか、右リールのみ停止しているか、左、中リールが停止しているか、左、右リールが停止しているか、中、右リールが停止しているか、によって異なる場合があり、更に、いずれかのリールが停止している状況においては、停止済みのリールの停止位置によっても異なる場合があるので、それぞれの状況について、参照すべき停止制御テーブルのアドレスが回転中のリール別に登録されており、テーブル作成用データの先頭アドレスに基づいて、それぞれの状況に応じて参照すべき停止制御テーブルのアドレスが特定可能とされ、この特定されたアドレスから、それぞれの状況に応じて必要な停止制御テーブルを特定できるようになっている。尚、リールの停止状況や停止済みのリールの停止位置が異なる場合でも、同一の停止制御テーブルが適用される場合においては、停止制御テーブルのアドレスとして同一のアドレスが登録されているものもあり、このような場合には、同一の停止制御テーブルが参照されることとなる。

停止制御テーブルは、停止操作が行われたタイミング別の滑りコマ数を特定可能なデータである。本実施例では、リールモータ32L、32C、32Rに、168ステップ(0〜167)の周期で1周するステッピングモータを用いている。すなわちリールモータ32L、32C、32Rを168ステップ駆動させることでリール2L、2C、2Rが1周することとなる。そして、リール1周に対して8ステップ(1図柄が移動するステップ数)毎に分割した21の領域(コマ)が定められており、これらの領域には、リール基準位置から0〜20の領域番号が割り当てられている。一方、1リールに配列された図柄数も21であり、各リールの図柄に対して、リール基準位置から0〜20の図柄番号が割り当てられているので、0番図柄から20番図柄に対して、それぞれ0〜20の領域番号が順に割り当てられていることとなる。そして、停止制御テーブルには、領域番号別の滑りコマ数が所定のルールで圧縮して格納されており、停止制御テーブルを展開することによって領域番号別の滑りコマ数を取得できるようになっている。

前述のようにテーブルインデックス及びテーブル作成用データを参照して作成される停止制御テーブルは、領域番号に対応して、各領域番号に対応する領域が停止基準位置(本実施例では、透視窓3の下段図柄の領域)に位置するタイミング(リール基準位置からのステップ数が各領域番号のステップ数の範囲に含まれるタイミング)でストップスイッチ8L、8C、8Rの操作が検出された場合の滑りコマ数がそれぞれ設定されたテーブルである。

次に、停止制御テーブルの作成手順について説明すると、まず、リール回転開始時においては、そのゲームの内部当選状態に応じたテーブル作成用データの先頭アドレスを取得する。具体的には、まずテーブルインデックスを参照し、内部当選状態に対応するインデックスデータを取得し、そして取得したインデックスデータに基づいてテーブル作成用データを特定し、特定したテーブル作成用データから全てのリールが回転中の状態に対応する各リールの停止制御テーブルのアドレスを取得し、取得したアドレスに格納されている各リールの停止制御テーブルを展開して全てのリールについて停止制御テーブルを作成する。

また、いずれか1つのリールが停止したとき、またはいずれか2つのリールが停止したときには、リール回転開始時に取得したインデックスデータ、すなわちそのゲームの内部当選状態に応じたテーブル作成用データの先頭アドレスに基づいてテーブル作成用データを特定し、特定したテーブル作成用データから停止済みのリール及び当該リールの停止位置の領域番号に対応する未停止リールの停止制御テーブルのアドレスを取得し、取得したアドレスに格納されている各リールの停止制御テーブルを展開して未停止のリールについて停止制御テーブルを作成する。

次に、遊技制御用マイクロコンピュータ100がストップスイッチ8L、8C、8Rのうち、回転中のリールに対応するいずれかの操作を有効に検出したときに、該当するリールに表示結果を導出させる際の制御について説明すると、ストップスイッチ8L、8C、8Rのうち、回転中のリールに対応するいずれかの操作を有効に検出すると、停止操作を検出した時点のリール基準位置からのステップ数に基づいて停止操作位置の領域番号を特定し、停止操作が検出されたリールの停止制御テーブルを参照し、特定した停止操作位置の領域番号に対応する滑りコマ数を取得する。そして、取得した滑りコマ数分リールを回転させて停止させる制御を行う。具体的には、停止操作を検出した時点のリール基準位置からのステップ数から、取得した滑りコマ数引き込んで停止させるまでのステップ数を算出し、算出したステップ数分リールを回転させて停止させる制御を行う。これにより、停止操作が検出された停止操作位置の領域番号に対応する領域から滑りコマ数分先の停止位置となる領域番号に対応する領域が停止基準位置(本実施例では、透視窓3の下段図柄の領域)に停止することとなる。

本実施例のテーブルインデックスには、一の遊技状態における一の内部当選状態に対応するインデックスデータとして1つのアドレスのみが格納されており、更に、一のテーブル作成用データには、一のリールの停止状況(及び停止済みのリールの停止位置)に対応する停止制御テーブルの格納領域のアドレスとして1つのアドレスのみが格納されている。すなわち一の遊技状態における一の内部当選状態に対応するテーブル作成用データ、及びリールの停止状況(及び停止済みのリールの停止位置)に対応する停止制御テーブルが一意的に定められており、これらを参照して作成される停止制御テーブルも、一の遊技状態における一の内部当選状態、及びリールの停止状況(及び停止済みのリールの停止位置)に対して一意となる。このため、遊技状態、内部当選状態、リールの停止状況(及び停止済みのリールの停止位置)の全てが同一条件となった際に、同一の停止制御テーブル、すなわち同一の制御パターンに基づいてリールの停止制御が行われることとなる。

また、本実施例では、滑りコマ数として0〜4の値が定められており、停止操作を検出してから最大4コマ図柄を引き込んでリールを停止させることが可能である。すなわち停止操作を検出した停止操作位置を含め、最大5コマの範囲から図柄の停止位置を指定できるようになっている。また、1図柄分リールを移動させるのに1コマの移動が必要であるので、停止操作を検出してから最大4図柄を引き込んでリールを停止させることが可能であり、停止操作を検出した停止操作位置を含め、最大5図柄の範囲から図柄の停止位置を指定できることとなる。

本実施例では、いずれかの役に当選している場合には、当選役を入賞ラインLNに4コマの範囲で最大限引き込み、当選していない役が入賞ラインLNに揃わないように引き込む滑りコマ数が定められた停止制御テーブルを作成し、リールの停止制御を行う一方、いずれの役にも当選していない場合には、いずれの役も揃わない滑りコマ数が定められた停止制御テーブルを作成し、リールの停止制御を行う。これにより、停止操作が行われた際に、入賞ラインLNに最大4コマの引込範囲で当選している役を揃えて停止させることができれば、これを揃えて停止させる制御が行われ、当選していない役は、最大4コマの引込範囲でハズシして停止させる制御が行われることとなる。

特別役が前ゲーム以前から持ち越されている状態で小役が当選した場合など、特別役と小役が同時に当選している場合には、当選した小役を入賞ラインLNに4コマの範囲で最大限に引き込むように滑りコマ数が定められているとともに、当選した小役を入賞ラインLNに最大4コマの範囲で引き込めない停止操作位置については、当選した特別役を入賞ラインLNに4コマの範囲で最大限に引き込むように滑りコマ数が定められた停止制御テーブルを作成し、リールの停止制御を行う。これにより、停止操作が行われた際に、入賞ラインLNに最大4コマの引込範囲で当選している小役を揃えて停止させることができれば、これを揃えて停止させる制御が行われ、入賞ラインLNに最大4コマの引込範囲で当選している小役を引き込めない場合には、入賞ラインLNに最大4コマの引込範囲で当選している特別役を揃えて停止させることができれば、これを揃えて停止させる制御が行われ、当選していない役は、4コマの引込範囲でハズシして停止させる制御が行われることとなる。すなわちこのような場合には、特別役よりも小役を入賞ラインLNに揃える制御が優先され、小役を引き込めない場合にのみ、特別役を入賞させることが可能となる。尚、特別役と小役を同時に引き込める場合には、小役のみを引き込み、特別役と同時に小役が入賞ラインLNに揃わないようになっている。

尚、本実施例では、特別役が前ゲーム以前から持ち越されている状態で小役が当選した場合や新たに特別役と小役が同時に当選した場合など、特別役と小役が同時に当選している場合には、当選した特別役よりも当選した小役が優先され、小役が引き込めない場合のみ、特別役を入賞ラインLNに揃える制御を行っているが、特別役と小役が同時に当選している場合に、小役よりも特別役を入賞ラインLNに揃える制御が優先され、特別役を引き込めない場合にのみ、小役を入賞ラインLNに揃える制御を行っても良い。

特別役が前ゲーム以前から持ち越されている状態で再遊技役が当選した場合など、特別役と再遊技役が同時に当選している場合には、停止操作が行われた際に、入賞ラインLNに最大4コマの引込範囲で再遊技役の図柄を揃えて停止させる制御が行われる。尚、この場合、再遊技役を構成する図柄または同時当選する再遊技役を構成する図柄は、リール2L、2C、2Rのいずれについても5図柄以内、すなわち4コマ以内の間隔で配置されており、4コマの引込範囲で必ず任意の位置に停止させることができるので、特別役と再遊技役が同時に当選している場合には、遊技者によるストップスイッチ8L、8C、8Rの操作タイミングに関わらずに、必ず再遊技役が揃って入賞することとなる。すなわちこのような場合には、特別役よりも再遊技役を入賞ラインLNに揃える制御が優先され、必ず再遊技役が入賞することとなる。尚、特別役と再遊技役を同時に引き込める場合には、再遊技役のみを引き込み、再遊技役と同時に特別役が入賞ラインLNに揃わないようになっている。

本実施例において遊技制御用マイクロコンピュータ100は、リール2L、2C、2Rの回転が開始した後、ストップスイッチ8L、8C、8Rの操作が検出されるまで、停止操作が未だ検出されていないリールの回転を継続し、ストップスイッチ8L、8C、8Rの操作が検出されたことを条件に、対応するリールに表示結果を停止させる制御を行うようになっている。尚、リール回転エラーの発生により、一時的にリールの回転が停止した場合でも、その後リール回転が再開した後、ストップスイッチ8L、8C、8Rの操作が検出されるまで、停止操作が未だ検出されていないリールの回転を継続し、ストップスイッチ8L、8C、8Rの操作が検出されたことを条件に、対応するリールに表示結果を停止させる制御を行うようになっている。

尚、本実施例では、ストップスイッチ8L、8C、8Rの操作が検出されたことを条件に、対応するリールに表示結果を停止させる制御を行うようになっているが、リールの回転が開始してから、予め定められた自動停止時間が経過した場合に、リールの停止操作がなされない場合でも、停止操作がなされたものとみなして自動的に各リールを停止させる自動停止制御を行うようにしても良い。この場合には、遊技者の操作を介さずにリールが停止することとなるため、例えば、いずれかの役が当選している場合でもいずれの役も構成しない表示結果を導出させることが好ましい。

図28に示すように、遊技制御用マイクロコンピュータ100のROM506には遊技制御プログラムが格納されている。遊技制御プログラムは、下層に、図33の遊技制御処理におけるSd2にて実行する内部抽選処理に関わる制御を行う内部抽選制御モジュールと、図33の遊技制御処理におけるSd7にて実行する入出力処理(I/Oポートでの入出力に関する処理)に関わる制御を行う入出力制御モジュールと、図33の遊技制御処理におけるSd3にて実行するリール回転処理に関わる制御を行うリール回転制御モジュールと、図33の遊技制御処理におけるSd5にて実行する払出処理に関わる制御を行う払出制御モジュールとを備えている。このように、遊技制御プログラムは、遊技制御用マイクロコンピュータ100で実行する各制御に対応した複数の制御モジュールを含んでいる。よって、他機種に対して、ある機種の制御モジュールのみ(1つ又は複数)を入れ替えれば良い。場合には、その制御モジュールのみを入れ替えれば良く、遊技制御プログラムの変更が容易になる。

次に、本実施例における遊技制御用マイクロコンピュータ100が実行する各種制御内容を、図29〜図36に基づいて以下に説明する。

遊技制御基板40では、電源基板101からの電力供給が開始され遊技制御用マイクロコンピュータ100へのリセット信号がハイレベル(オフ状態)になったことに応じて、遊技制御用マイクロコンピュータ100が起動し、CPU505がROM506から読み出したセキュリティチェックプログラム506Aに基づき、図29のフローチャートに示すようなセキュリティチェック処理が実行される。このとき、遊技制御用マイクロコンピュータ100は、動作状態がセキュリティモードとなり、ROM506に記憶されているゲーム制御用のユーザプログラムは未だ実行されない状態となる。

図29に示すセキュリティチェック処理を開始すると、CPU505は、まず、セキュリティチェック処理が実行されることにより遊技制御用マイクロコンピュータ100がセキュリティモードとなる時間(セキュリティ時間)を決定するための処理を実行する。このとき、CPU505は、ROM506のプログラム管理エリアに記憶されるセキュリティ時間設定KSESのビット番号[5−0]におけるビット値を読み出す(ステップS1)。そして、この読出値に応じた固定延長時間を設定する(ステップS2)。ステップS2の処理では、例えば図12に示すように、セキュリティ時間設定KSESのビット番号[5−0]におけるビット値に応じて異なる固定セキュリティ時間を、固定延長時間として設定すればよい。

ステップS2の処理を実行した後には、セキュリティ時間設定KSESのビット番号[7−6]におけるビット値を読み出す(ステップS3)。そして、この読出値が“00”であるか否かを判定する(ステップS4)。このとき読出値が“00”以外であると判定された場合には(ステップS4;No)、その読出値に対応して決定される可変延長時間を設定する(ステップS5)。ステップS5の処理では、例えば図12に示すように、セキュリティ時間設定KSESのビット番号[7−6]におけるビット値に対応して、ショートモード、ミドルモード、ロングモードのいずれかによる可変セキュリティ時間を、可変延長延長時間として設定すればよい。ステップS2の処理により設定された固定延長時間とステップS5の処理により設定された可変延長時間とを加算して、セキュリティ時間に設定すればよい。ここで、可変設定時間は、セキュリティ時間のうち、セキュリティチェック処理が実行されるごとに変化する時間成分であり、セキュリティ時間設定KSESのビット番号[7−6]におけるビット値が“01”(ショートモード)であるか“10”(ミドルモード)であるか“11”(ロングモード)であるかに応じて異なる所定の時間範囲で変化する。

例えば、システムリセットの発生時に、フリーランカウンタ509Cなどにおけるカウント値が遊技制御用マイクロコンピュータ100に内蔵された可変セキュリティ時間用レジスタに格納される場合には、ステップS5の処理において、可変セキュリティ時間用レジスタの格納値をそのまま用いること、あるいは、その格納値を所定の演算関数(例えばハッシュ関数)に代入して得られた値を用いることなどにより、可変設定時間がシステムリセット毎に所定の時間範囲でランダムに変化するように決定されればよい。こうして、セキュリティ時間設定KSESのビット番号[7−6]におけるビット値が“00”以外の値である場合には、セキュリティチェック処理の実行時間であるセキュリティ時間を、システムリセットの発生等に基づくセキュリティチェック処理が実行されるごとに所定の時間範囲で変化させることができる。

一方、ステップS4にて読出値が“00”であると判定された場合には(ステップS4;Yes)、ステップS5の処理が実行されない。この場合には、ステップS2の処理により設定された固定延長時間をセキュリティ時間に設定すればよい。

その後、ROM506の所定領域に記憶されたセキュリティコードを読み出す(ステップS6)。ここで、ROM506の所定領域には、記憶内容のデータを所定の演算式によって演算した演算結果のセキュリティコードが予め記憶されている。セキュリティコードの生成方法としては、例えばハッシュ関数を用いてハッシュ値を生成するもの、エラー検出コード(CRCコード)を用いるもの、エラー訂正コード(ECCコード)を用いるもののいずれかといった、予め定められた生成方法を使用すればよい。また、ROM506のセキュリティコード記憶領域とは異なる所定領域には、セキュリティコードを演算により特定するための演算式が、暗号化して予め記憶されている。

ステップS6の処理に続いて、暗号化された演算式を復号化して元に戻す(ステップS7)。その後、ステップS7で復号化した演算式により、ROM506の所定領域における記憶データを演算してセキュリティコードを特定する(ステップS8)。このときセキュリティコードを特定するための演算に用いる記憶データは、例えばROM506の記憶データのうち、セキュリティチェックプログラム506Aとは異なるユーザプログラムの一部または全部に相当するプログラムデータ、あるいは、所定のテーブルデータを構成する固定データの一部または全部であればよい。そして、ステップS6にて読み出したセキュリティコードと、ステップS8にて特定されたセキュリティコードとを比較する(ステップS9)。このときには、比較結果においてセキュリティコードが一致したか否かを判定する(ステップS10)。

ステップS10にてセキュリティコードが一致しない場合には(ステップS10;No)、ROM506に不正な変更が加えられたと判断して、CPU505の動作を停止状態(HALT)へ移行させる。これに対して、ステップS10にてセキュリティコードが一致した場合には(ステップS10;Yes)、ステップS2やステップS5の処理に基づいて設定されたセキュリティ時間が経過したか否かを判定する(ステップS11)。そして、セキュリティ時間が経過していなければ(ステップS11;No)、ステップS11の処理を繰り返し実行して、セキュリティ時間が経過するまで待機する。その一方で、ステップS11にてセキュリティ時間が経過したと判定された場合には(ステップS11;Yes)、例えばCPU505に内蔵されたプログラムカウンタの値をROM506におけるユーザプログラムの先頭アドレス(アドレス0000H)に設定することなどにより、起動処理(メイン)の実行を開始する。このときには、ROM506に記憶されたユーザプログラムを構成する制御コードの先頭から遊技制御の実行が開始されることにより、遊技制御用マイクロコンピュータ100の動作状態がセキュリティモードからユーザモードへと移行し、図30〜図32のフローチャートに示す起動処理(メイン)の実行が開始されることになる。

まず、内蔵デバイスや周辺IC、割込モード、スタックポインタ等を初期化した後(Sa1)、Iレジスタ及びIYレジスタの値を初期化する(Sa2)。Iレジスタ及びIYレジスタの初期化により、Iレジスタには、割込発生時に参照する割込テーブルのアドレスが設定され、IYレジスタには、RAM507の格納領域を参照する際の基準アドレスが設定される。これらの値は、固定値であり、起動時には常に初期化されることとなる。また、Sa2の処理では、所定の通信設定レジスタにおける設定を初期化することにより、シリアル通信回路511における動作設定が行われればよい。次いで、SRAM50に接続されているCS信号線が接続された汎用端子に対応する汎用ポートの設定を出力ポートに設定することで(Sa3)、SRAM50のチップセレクト信号の出力を有効化する。Sa3の処理に続いて、タイマ回路508やPIP510の設定が行われてもよい。

その後、例えばPIP510に含まれる所定の入力ポートにおける端子状態をチェックすることなどにより、電源断信号がオフ状態となっているか否かを判定する(Sa35)。スロットマシン1では、電力供給が開始されたときに、VSL(+30V)電源などの各種電源の出力電圧が徐々に規定値へと達する。このとき、Sa35の処理により電源断信号のオフ状態(ハイレベル)を確認することで、CPU505が電源電圧の安定を確認することができる。なお、ノイズ等の影響による誤検出を防止するために、電源断信号の確認を所定回数(例えば5回)連続して実行してもよい。

Sa35にて電源断信号がオン状態(ローレベル)である場合には、リセットコントローラ504Aに設けられたウォッチドッグタイマ520を起動させるための設定を行う(Sa36)。この実施の形態では、図10(B)に示すリセット設定KRESのビット番号[6]におけるビット値を予め“0”となるように設定しておく。これにより、ウォッチドッグタイマ520を起動させてタイムアウトの発生に応じたリセット動作を有効化するか、ウォッチドッグタイマ520を停止させてタイムアウトの発生に応じたリセット動作を無効化するかを、ユーザプログラム(ソフトウェア)により切替可能に設定する。また、リセット設定KRESのビット番号[5−4]におけるビット値を予め“11”となるように設定するとともに、リセット設定KRESのビット番号[3−0]におけるビット値を予め“1111”となるように設定しておく。これにより、ウォッチドッグタイマ520にて計測される監視時間となるタイムアウト時間は、監視時間として設定可能な複数種類のうちで最長時間となる。

このような設定に基づいて、Sa36の処理では、CPU505が図15(A)に示すWDTスタートレジスタWSTに、「CCH」をWDTスタートデータとして書き込む。こうして、Sa35の処理により電源断信号がオン状態であると判定されたときには、ウォッチドッグタイマ520による監視時間の計測を開始させて、タイムアウトの発生によるリセット動作を有効化する。

Sa36の処理によりウォッチドッグタイマ520を起動させた後に、CPU505は、無限ループ処理を繰返し実行することにより制御状態を待機状態に移行させる。こうして待機状態に移行した後には、ウォッチドッグタイマ520のクリアおよびリスタートが行われないことから、監視時間の経過が計測されたときに、タイムアウトの発生によるリセット動作が行われることになる。したがって、スロットマシン1に電力供給が開始されてから所定時間が経過しても電源電圧の安定が確認できず、電源断信号がオン状態のままである場合には、ウォッチドッグタイマ520におけるタイムアウトの発生によるリセット動作を行って、遊技制御用マイクロコンピュータ100を再起動させることができる。

ここで、ウォッチドッグタイマ520にて計測される監視時間となるタイムアウト時間は、監視時間として設定可能な複数種類のうちで最長時間225×TSCLK×15(TSCLKは内部システムクロックSCLKの周期)となるように設定されている。したがって、例えばスロットマシン1における電源スイッチの切断等により電力供給が所定期間にわたり完全に停止したときには、監視時間の経過によりタイムアウトが発生するより先に、遊技制御用マイクロコンピュータ100のCPU505に対する電力供給が停止するので、タイムアウトの発生によるリセット動作が行われないように制限できる。こうして、電源スイッチの切断時などに誤ってリセットされてしまうことを防止できる。

Sa35にて電源断信号がオフ状態(ハイレベル)である場合には、電源基板101に設置されたクリアスイッチ304から伝送されるスイッチ信号(クリア信号)の信号状態などに基づき、クリアスイッチ304がオン操作されたかを判定する(Sa37)。なお、Sa37の処理では、クリアスイッチ304から伝送されるクリア信号を複数回チェックし、連続してオン状態となったときに、クリアスイッチ304がオン操作されたと判定してもよい。例えば、クリア信号の状態がオフ状態であることを1回確認したら、所定時間(例えば0.1秒)が経過した後に、クリア信号の状態をもう1回確認する。このとき、クリア信号がオフ状態であれば、クリア信号がオフ状態である旨の判定を行うようにする。他方、このときにクリア信号の状態がオン状態であれば、所定時間が経過した後に、クリア信号の状態を再び確認するようにしてもよい。なお、クリア信号の状態を再確認する回数は1回であってもよいし、複数回であってもよい。また、2回チェックして、チェック結果が一致していなかったときに、もう一度確認するようにしてもよい。

Sa37にてクリア信号がオン状態であれば、例えばRAM507の所定領域(遊技制御フラグ設定部など)にも受けられたクリアフラグをオン状態にセットする(Sa38)。他方、クリア信号がオフ状態であるときには、Sa38の処理をスキップして、クリアフラグをオフ状態のままとする。

その後、遊技の進行を制御するための遊技制御処理の開始タイミングをソフトウェアの実行により遅延させる遅延処理の設定を行う(Sa39)。具体的な一例として、RAM507の所定領域(遊技制御カウンタ設定部など)に設けられたウェイトカウンタに、初期化ウェイト回数指定値をセットする。続いて、Sa39での設定に基づく遅延処理を開始して、例えばウェイトカウンタにおけるカウント値を1減算するなど、遅延処理の実行に関わる設定の更新を行う(Sa40)。そして、例えばウェイトカウンタにおけるカウント値が所定の遅延終了判定値に達したか否かを判定することなどにより、所定の遅延時間が経過したか否かを判定する(Sa41)。ここで、遅延終了判定値を示すデータは、ROM506などに予め記憶されていればよい。

Sa41にて遅延時間が経過していないときには、Sa40の処理にリターンし、遅延時間が経過しているときには、RAM507(ワークRAM)へのアクセスを許可する(Sa4)。

RAM507(ワークRAM)へのアクセスを許可した後、内部抽選制御モジュールに対するバックアップフラグがSRAM50(バックアップRAM)にセットされているか否かを判定する(Sa5)。この実施例では、図36の電断処理(メイン)におけるSm5,Sm10,Sm15,Sm20において、電源断の発生時に、プログラムモジュール毎に区別してバックアップフラグがセットされる。すなわち、この実施例では、遊技制御用マイクロコンピュータ100が行う処理に関して、バックアップフラグには、内部抽選制御モジュールに対応したバックアップフラグと、入出力制御モジュールに対応したバックアップフラグと、リーチ回転制御モジュールに対応したバックアップフラグと、払出制御モジュールに対応したバックアップフラグとの4種類がある。Sa5では、遊技制御用マイクロコンピュータ100は、まず、内部抽選制御モジュールに対応したバックアップフラグがセットされているか否かを確認する。

内部抽選制御モジュールに対応したバックアップフラグがセットされている場合には、バックアップフラグをクリアする(Sa6)。バックアップフラグをクリアした後、SRAM50(バックアップRAM)の内部抽選制御モジュールで用いるデータが格納されている領域のデータの排他的論理和を求めチェックサムを計算する(Sa7)。この後、計算したチェックサムが、バックアップされているチェックサムと一致するか否かを判定する(Sa8)。尚、この実施例では、図36の電断処理(メイン)におけるSm4,Sm9,Sm14,Sm19において、チェックサムに関しても、電源断の発生時に、モジュール毎に、そのモジュールで使用されるデータの排他的論理和を求めることによって生成され、SRAM50(バックアップRAM)に格納される。すなわち、この実施例では、遊技制御用マイクロコンピュータ100が行う処理に関して、チェックサムには、内部抽選制御モジュールで使用されるデータを用いて算出されたチェックサムと、入出力制御モジュールで使用されるデータを用いて算出されたチェックサムと、リーチ回転制御モジュールで使用されるデータを用いて算出されたチェックサムと、払出制御モジュールで使用されるデータを用いて算出されたチェックサムとの4種類がある。Sa8では、遊技制御用マイクロコンピュータ100は、まず、内部抽選制御モジュールで使用されるデータを用いて算出されたチェックサムがバックアップされているものと一致するか否かを確認する。

チェックサムが一致している場合には、入出力制御モジュールに対応したバックアップフラグがSRAM50(バックアップRAM)にセットされているか否かを判定する(Sa9)。入出力制御モジュールに対応したバックアップフラグがセットされている場合には、バックアップフラグをクリアする(Sa10)。バックアップフラグをクリアした後、SRAM50(バックアップRAM)の入出力制御モジュールで用いるデータが格納されている領域のデータの排他的論理和を求めチェックサムを計算する(Sa11)。この後、計算したチェックサムが、バックアップされているチェックサムと一致するか否かを判定する(Sa12)。

チェックサムが一致している場合には、リール回転制御モジュールに対応したバックアップフラグがSRAM50(バックアップRAM)にセットされているか否かを判定する(Sa14)。リール回転制御モジュールに対応したバックアップフラグがセットされている場合には、バックアップフラグをクリアする(Sa15)。バックアップフラグをクリアした後、SRAM50(バックアップRAM)のリール回転制御モジュールで用いるデータが格納されている領域のデータの排他的論理和を求めチェックサムを計算する(Sa16)。この後、計算したチェックサムが、バックアップされているチェックサムと一致するか否かを判定する(Sa17)。

チェックサムが一致している場合には、払出制御モジュールに対応したバックアップフラグがSRAM50(バックアップRAM)にセットされているか否かを判定する(Sa18)。払出制御モジュールに対応したバックアップフラグがセットされている場合には、バックアップフラグをクリアする(Sa19)。バックアップフラグをクリアした後、SRAM50(バックアップRAM)の払出制御モジュールで用いるデータが格納されている領域のデータの排他的論理和を求めチェックサムを計算する(Sa20)。この後、計算したチェックサムが、バックアップされているチェックサムと一致するか否かを判定する(Sa21)。

Sa8,Sa12,Sa17,Sa21において、1つでもチェックサムが一致していないことを判定した場合、または、Sa5,Sa9,Sa14,Sa18において、1つでもバックアップフラグがセットされていないことを判定した場合には、RAM507(ワークRAM)及びSRAM50(バックアップRAM)の全ての格納領域を初期化する初期化処理を実行した後(Sa29)、設定キースイッチ37がonか否かを判定する(Sa30)。設定キースイッチ37がonであれば、設定変更中であることを示す設定変更中コマンドを生成するとともに、生成した設定変更中コマンドをコマンドバッファに格納する(Sa27)。尚、設定変更中コマンドは、ステップSa27の処理の後、後述するタイマ割込処理におけるステップSk16のコマンド送信処理と同様の処理が実行されることによって直ちに送信される。次いで、図34において説明する遊技制御用マイクロコンピュータ100が一定間隔(0.56msの間隔)で実行するタイマ割込処理(メイン)の割込を許可して(Sa28)、当選役の当選確率の変更などを行う設定変更処理、すなわち設定変更状態に移行する。そして、設定変更処理が終了すると、図33に示す遊技制御処理に移行する。

Sa28の処理では、例えば遊技制御用マイクロコンピュータ100が備えるタイマ回路508のレジスタ設定などを行うことにより、所定時間(例えば2ミリ秒)ごとにタイマ割込みが発生するように遊技制御用マイクロコンピュータ100の内部設定を行う。この後、例えばCPU505がROM506のプログラム管理エリアに記憶されている16ビット乱数初期設定第1KRL1のビット番号[7]やビット番号[3]などにおけるビット値を読み出す。このときには、それぞれのビット値について読出値が“0”であるか否かを判定する。

読出値が“0”であるビット値があった場合には、乱数値となる数値データにおける最大値を設定することにより乱数回路509A、509Bを起動させる設定を行う。例えば図11(B)に示す16ビット乱数初期設定第1KRL1のビット番号[3]におけるビット値を予め“0”となるように設定しておく。この場合、16ビットの乱数回路509Aにおいてチャネルch0の16ビット乱数を発生させる回路は、ユーザプログラム(ソフトウェア)における乱数最大値の設定により起動させることができる。このような設定に基づいて、ステップS46の処理では、CPU505が図21(A)および(B)に示すチャネルch0の16ビット乱数に対応した乱数最大値設定レジスタRL0MXに所定の数値データを乱数最大値として書き込む。こうして、ユーザプログラム(ソフトウェア)における乱数最大値の設定により、チャネルch0に対応した16ビット乱数の発生を開始させる。

読出値が“0”ではなく“1”である場合や、乱数回路509A、509Bを起動させる設定を行った後には、シリアル通信回路の初期設定を行う。

尚、後述するSa25やSa33のステップにおいても、上記に説明したSm25のステップと同様の処理が実行される。

Sa30のステップにおいて設定キースイッチ37がoffであれば、RAM異常を示すエラーコードをレジスタに設定し(Sa31)、RAM異常を示すエラーコマンドを生成し、生成したエラーコマンドをコマンドバッファに格納する(Sa32)。尚、エラーコマンドは、ステップSa32の処理の後、後述するタイマ割込処理におけるステップSk16のコマンド送信処理と同様の処理が実行されることによって直ちに送信される。次いで、図34において説明する遊技制御用マイクロコンピュータ100が一定間隔(0.56msの間隔)で実行するタイマ割込処理(メイン)の割込を許可して(Sa33)、エラー処理、すなわちRAM異常エラー状態に移行する。そして、例えば、遊技店員によってリセット/設定スイッチ38が操作されるなどして、RAM異常エラー状態が解除されると、図33に示す遊技制御処理に移行する。

Sa21において、チェックサムが一致していることを判定した場合には、設定キースイッチ37がonか否かを判定する(Sa23)。設定キースイッチ37がonであれば、RAM507(ワークRAM)及びSRAM50(バックアップRAM)の全ての格納領域を初期化する初期化処理を実行した後(Sa26)、前述したSa27〜Sa28の処理を行い、設定変更処理、すなわち設定変更状態に移行する。そして、設定変更処理が終了すると、図33に示す遊技制御処理に移行する。

Sa23のステップにおいて設定キースイッチ37がoffであれば、各レジスタを電断前の状態、すなわちスタックに保存されている状態に復帰する(Sa24)。そして、復帰コマンドを生成して、生成した復帰コマンドをコマンドバッファに格納し(Sa24a)、図34において説明する遊技制御用マイクロコンピュータ100が一定間隔(0.56msの間隔)で実行するタイマ割込処理(メイン)の割込を許可して(Sa25)、電断前の最後に実行していた処理に戻る。尚、復帰コマンドは、遊技制御用マイクロコンピュータ100のRAM507の特別ワークに割り当てられたコマンド送信用バッファに格納され、後述するタイマ割込処理におけるステップSk16のコマンド送信処理と同様の処理が実行されることによって、停電復旧時に直ちに送信される。電断前に図33に示す遊技制御処理中のいずれかの処理が行われていた場合には、Sa24で復帰されたプログラムカウンタ(PC)の値に基づいて、遊技制御処理のSd1〜Sd7の処理のうち、電断前に行われていた処理に戻る。また、例えば、電断前に図34に示すタイマ割込処理中のいずれかの処理が行われていた場合には、Sa24で復帰されたプログラムカウンタ(PC)の値に基づいて、タイマ割込処理のSk1〜Sk26の処理のうち、電断前に行われていた処理に戻る。

Sa25、Sa28、Sa33の処理が実行されることにより割込み許可状態となった後、例えばタイマ回路508や乱数回路509A、509B、あるいはシリアル通信回路511の一部または全部などにて同時に複数のマスカブル割込み要因が生じたときには、割込み初期設定KIISのビット番号[2−0]におけるビット値による指定に基づき、割込みコントローラ504Bによって優先順位の高い割込み要因が受け付けられる。割込みコントローラ504Bが割込み要因を受け付けたときには、例えばCPU505が備えるIクラス割込み(IRQ)端子などに対して、オン状態の割込み要求信号を出力する。CPU505にてIRQ端子にオン状態の割込み要求信号が入力されたときには、例えば内部レジスタの格納データを確認した結果などに基づき、発生した割込み要因を特定し、特定された割込み要因に対応するベクタアドレスを先頭アドレスとするプログラムを実行することにより、各割込み要因に基づく割込み処理を開始することができる。