JP5658128B2 - Nandフラッシュ・メモリにおける確率論的多層エラー訂正のためのシステム、方法、およびコンピュータ・プログラム - Google Patents

Nandフラッシュ・メモリにおける確率論的多層エラー訂正のためのシステム、方法、およびコンピュータ・プログラム Download PDFInfo

- Publication number

- JP5658128B2 JP5658128B2 JP2011256126A JP2011256126A JP5658128B2 JP 5658128 B2 JP5658128 B2 JP 5658128B2 JP 2011256126 A JP2011256126 A JP 2011256126A JP 2011256126 A JP2011256126 A JP 2011256126A JP 5658128 B2 JP5658128 B2 JP 5658128B2

- Authority

- JP

- Japan

- Prior art keywords

- memory

- layer

- data

- codeword

- error

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

- G06F11/1008—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices

- G06F11/1012—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices using codes or arrangements adapted for a specific type of error

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/29—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes combining two or more codes or code structures, e.g. product codes, generalised product codes, concatenated codes, inner and outer codes

- H03M13/2906—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes combining two or more codes or code structures, e.g. product codes, generalised product codes, concatenated codes, inner and outer codes using block codes

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/37—Decoding methods or techniques, not specific to the particular type of coding provided for in groups H03M13/03 - H03M13/35

- H03M13/3707—Adaptive decoding and hybrid decoding, e.g. decoding methods or techniques providing more than one decoding algorithm for one code

- H03M13/3715—Adaptation to the number of estimated errors or to the channel state

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/37—Decoding methods or techniques, not specific to the particular type of coding provided for in groups H03M13/03 - H03M13/35

- H03M13/3738—Decoding methods or techniques, not specific to the particular type of coding provided for in groups H03M13/03 - H03M13/35 with judging correct decoding

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- Probability & Statistics with Applications (AREA)

- Quality & Reliability (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

- Detection And Correction Of Errors (AREA)

- Error Detection And Correction (AREA)

Description

は、読み取り値がv1であることを条件として、更に各テーブルがファクターの値に基づくことを条件として、真の記憶値がv2であった確率を表す。一実施形態では、重みテーブル1 802における第1のエラー重みベクトルを割り当てるには、MLCレベルL3にある各ページ位置の8近隣(neighbor)数をカウントし、ページ位置におけるデータ値を計算に入れる。このため、例えば、w00は16成分ベクトルであり、成分

は、読み取り値がv1であることを条件とし、更に8近隣値のどれもL3でなかったという事実を条件として、真の記憶値がv2であった確率を表す。一実施形態では、重みテーブル2 804に示したような第2のエラー重みベクトルは、現在のセルと同じビット・ライン上のプログラムしたセル値の分布に基づいて、更に現在のデータ値に基づいて計算される。重みテーブル3 806における第3のエラー・ベクトルは、ページ・プログラム数および現在のデータ値に基づいて計算される。これらのテーブルは、第2の層のECC復号モジュール614による各復号の後に更新され、これによって重みモデルに時間履歴を組み込む。これによって、重みモデルは、他のデバイスとは著しく異なることがある使用中の特定のNANDフラッシュ・デバイスに適合することができる。一実施形態では、各第2の層のECC復号において観察されるエラー頻度をモデルのエラー重みと線形結合して、新しいモデル・エラー重みを形成する。当技術分野において周知の他の技法を用いて、第2の層のECCデコーダの各使用時に観察される経験的な頻度を組み込むことによって、モデルを更新することができる。別の実施形態では、第1の層のECCデコーダの各使用時に観察されるエラーを用いてモデルを更新する。

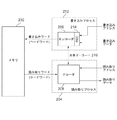

102 CPU

104 メモリ・コントローラ

106、202 メモリ

206 エンコーダ

208 デコーダ

214 受信器

412 第2のECC符号化モジュール

416 エラー訂正キャッシュ

418 第1のECC符号化モジュール

610 第1の層のECC復号モジュール

614 第2の層のECC復号モジュール

616 エラー・モジュール

Claims (19)

- メモリからデータを検索するためのシステムであって、

メモリと通信するデコーダであって、

前記メモリにおけるページ上に記憶されたコードワードを受信することであって、前記コードワードが、データおよび前記データに応じて発生された第1の層のチェック・シンボルを含む、前記受信することと、

前記コードワードが、前記第1の層のチェック・シンボルを用いて訂正することができないエラーを含むと判定することと、

前記判定に応じて、

第2の層のチェック・シンボルを受信することであって、前記第2の層のチェック・シンボルが、前記データに応じて、更に前記コードワードを含む前記ページよりも前に書き込まれた前記メモリにおける他のページの内容に応じて発生される、前記受信することと、

前記第2の層のチェック・シンボルに応じて前記コードワードを訂正することと、

前記訂正したコードワードを出力することと

を含む方法を実行するための前記デコーダ

を備えている、前記システム。 - 前記コードワードを訂正することが更に統計的エラー・モデルに応じて行われる、請求項1に記載のシステム。

- 前記統計的エラー・モデルが前記判定に応じて変更される、請求項2に記載のシステム。

- 前記コードワードを訂正することが更に各セルごとの集合エラー重みベクトルに応じて行われ、前記ベクトルが、前記セルについてのビット・ライン・ディスターバンス・エラー重みベクトル、前記セルについての浮動ゲート結合エラー重みベクトル、および前記セルについての多数のページ・プログラムから導出されたエラー重みベクトルの少なくとも1つから計算される、請求項1に記載のシステム。

- 前記セルについて前記エラー重みベクトルを計算することが更に、前記セルの指定された近隣領域内のセルの内容に応じて行われる、請求項4に記載のシステム。

- 前記統計的エラー・モデルが、前記コードワードおよび前記第2の層のチェック・シンボルを用いて前記コードワードを訂正するためにメッセージ伝達アルゴリズムによって用いられる、請求項2に記載のシステム。

- 前記メモリがマルチ・レベル・セル(MLC)NANDフラッシュ・メモリであり、前記コードワードの前記訂正が更に、2次元データ・パターンに対応したエラー重みを含むルックアップ・テーブル・セットに応じて行われる、請求項1に記載のシステム。

- 前記方法が、

前記コードワードが、前記第1の層のチェック・シンボルを用いて訂正することができないエラーを含まないと判定し、これに応じて、前記コードワードおよび前記第1の層のチェック・シンボルに応じて前記コードワードを訂正すること

を更に含む、請求項1に記載のシステム。 - 前記第2の層のチェック・シンボルの少なくとも1つのサブセットが第2のメモリに記憶されている、請求項1に記載のシステム。

- メモリからデータを検索するための、コンピュータにより実施される方法であって、コンピュータが、

前記メモリにおけるページ上に記憶されたコードワードを受信するステップであって、前記コードワードが、データおよび前記データに応じて発生された第1の層のチェック・シンボルを含む、前記受信するステップと、

前記コードワードが、前記第1の層のチェック・シンボルを用いて訂正することができないエラーを含むと判定するステップと、

前記判定に応じて、

第2の層のチェック・シンボルを受信するステップであって、前記第2の層のチェック・シンボルが、前記データに応じて、更に前記コードワードを含む前記ページよりも前に書き込まれた前記メモリにおける他のページの内容に応じて発生される、当該受信するステップと、

前記第2の層のチェック・シンボルに応じて前記コードワードを訂正するステップと、

前記訂正したコードワードを出力するステップと

を実行することを含む、前記方法。 - 前記メモリがマルチ・レベル・セル(MLC)NANDフラッシュ・メモリであり、前記コードワードの前記訂正が更に、2次元データ・パターンに対応したエラー重みを含むルックアップ・テーブル・セットに応じて行われる、請求項10に記載の方法。

- 前記コンピュータが、

前記コードワードが前記第1の層のチェック・シンボルを用いて訂正することができないエラーを含まないと判定し、これに応じて、前記コードワードおよび前記第1の層のチェック・シンボルに応じて前記コードワードを訂正するステップを実行することをさらに含む、請求項10に記載の方法。 - メモリからデータを検索するためのコンピュータ・プログラムであって、コンピュータに、請求項10〜12のいずれか一項に記載の方法の各ステップを実行させる前記コンピュータ・プログラム。

- システムであって、

メモリおよびエラー訂正キャッシュと通信するエンコーダであって、

データおよび前記メモリにおけるページの書き込みアドレスを受信することであって、前記メモリが前記ページおよび以前に書き込んだページを含む、当該受信することと、

データに応じて第1の層のチェック・シンボルを発生することと、

前記データおよび前記以前に書き込んだページの少なくとも1つの内容に応じて第2の層のチェック・シンボルを発生することと、

前記第1の層のチェック・シンボルおよび前記データをコードワードとして前記ページに記憶することと、

前記データおよび前記第2の層のチェック・シンボルを前記エラー訂正キャッシュに記憶することと

を含む方法を実行するための前記エンコーダを備えている、前記システム。 - 前記メモリおよび前記エラー訂正キャッシュと通信するデコーダであって、

前記コードワードおよび前記第2の層のチェック・シンボルを受信することと、

前記コードワードが、前記第1の層のチェック・シンボルを用いて訂正することができないエラーを含むと判定することと、

前記第2の層のチェック・シンボルに応じて前記コードワードを訂正することと

を含む方法を実行するための前記デコーダを更に備えている、請求項14に記載のシステム。 - 前記第2の層のチェック・シンボルを発生させることが更に低密度パリティ・チェック(LDPC)・コードに応じて行われる、請求項14に記載のシステム。

- 前記第2の層のチェック・シンボルを発生させることが、プログラム可能な数の以前に書き込んだページの内容に応じて行われる、請求項14に記載のシステム。

- 前記メモリがNANDフラッシュ・メモリであり、前記第2の層のチェック・シンボルを発生させることが、現在書き込んでいるページと同じブロック内のプログラム可能な数の以前に書き込んだページに応じて行われ、これらの以前に書き込んだページからのデータが前記エラー訂正キャッシュに記憶されている、請求項14に記載のシステム。

- 以前に書き込んだページの使用数が、メモリ・ブロックをプログラムした回数、前記メモリ・ブロックのシンボル・エラー・レート、および前記メモリの統計的エラー・モデルの少なくとも1つに応じて変更される、請求項14に記載のシステム。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/960004 | 2010-12-03 | ||

| US12/960,004 US8464137B2 (en) | 2010-12-03 | 2010-12-03 | Probabilistic multi-tier error correction in not-and (NAND) flash memory |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2012118979A JP2012118979A (ja) | 2012-06-21 |

| JP2012118979A5 JP2012118979A5 (ja) | 2014-08-14 |

| JP5658128B2 true JP5658128B2 (ja) | 2015-01-21 |

Family

ID=46163424

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011256126A Expired - Fee Related JP5658128B2 (ja) | 2010-12-03 | 2011-11-24 | Nandフラッシュ・メモリにおける確率論的多層エラー訂正のためのシステム、方法、およびコンピュータ・プログラム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8464137B2 (ja) |

| JP (1) | JP5658128B2 (ja) |

Families Citing this family (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8625339B2 (en) * | 2011-04-11 | 2014-01-07 | Grandis, Inc. | Multi-cell per memory-bit circuit and method |

| KR101650130B1 (ko) * | 2010-05-14 | 2016-08-24 | 삼성전자주식회사 | 불휘발성 메모리 장치를 포함하는 저장 장치 및 그것의 카피-백 방법 |

| KR101882853B1 (ko) * | 2011-12-21 | 2018-08-27 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 그 동작 방법 |

| GB201215339D0 (en) * | 2012-08-29 | 2012-10-10 | Ibm | Level placement in solid-state memory |

| US8990668B2 (en) | 2013-03-14 | 2015-03-24 | Western Digital Technologies, Inc. | Decoding data stored in solid-state memory |

| WO2015016880A1 (en) | 2013-07-31 | 2015-02-05 | Hewlett-Packard Development Company, L.P. | Global error correction |

| US20160139988A1 (en) * | 2013-07-31 | 2016-05-19 | Hewlett-Packard Development Company, L.P. | Memory unit |

| US9160371B2 (en) | 2013-09-05 | 2015-10-13 | Kabushiki Kaisha Toshiba | Memory controller, storage device and memory control method |

| US9548762B2 (en) * | 2013-10-07 | 2017-01-17 | Agency For Science, Technology And Research | Normalization factor adaptation for LDPC decoding for hard disk drive systems |

| US9389937B2 (en) * | 2013-11-19 | 2016-07-12 | Lenovo Enterprise Solutions (Singapore) Pte. Ltd. | Managing faulty memory pages in a computing system |

| CN103778030B (zh) * | 2013-12-30 | 2017-09-22 | 上海晨思电子科技有限公司 | 日志子系统写入方法、错误追踪方法及处理器 |

| US9417945B2 (en) | 2014-03-05 | 2016-08-16 | International Business Machines Corporation | Error checking and correction for NAND flash devices |

| GB2529670A (en) * | 2014-08-28 | 2016-03-02 | Ibm | Storage system |

| GB2529669B8 (en) | 2014-08-28 | 2017-03-15 | Ibm | Storage system |

| US10199106B2 (en) | 2014-09-30 | 2019-02-05 | Carnegie Mellon University | Reducing errors caused by inter-cell interference in a memory device |

| US9594629B2 (en) | 2015-06-03 | 2017-03-14 | King Abdulaziz City For Science And Technology | Data error correction from cached error correction information |

| US9710329B2 (en) * | 2015-09-30 | 2017-07-18 | Sandisk Technologies Llc | Error correction based on historical bit error data |

| US10650621B1 (en) | 2016-09-13 | 2020-05-12 | Iocurrents, Inc. | Interfacing with a vehicular controller area network |

| KR102766655B1 (ko) * | 2017-01-23 | 2025-02-12 | 에스케이하이닉스 주식회사 | 사전-검사된 에러율에 따른 적응형 에러정정을 수행하는 메모리장치 및 전자장치와, 메모리장치의 동작방법 |

| WO2020107301A1 (zh) * | 2018-11-29 | 2020-06-04 | 华为技术有限公司 | 一种编码方法、译码方法以及存储控制器 |

| US10853167B2 (en) | 2019-01-28 | 2020-12-01 | Winbond Electronics Corp. | Memory apparatus having hierarchical error correction code layer |

| US11507454B2 (en) * | 2020-10-26 | 2022-11-22 | Oracle International Corporation | Identifying non-correctable errors using error pattern analysis |

| US11528038B2 (en) * | 2020-11-06 | 2022-12-13 | Western Digital Technologies, Inc. | Content aware decoding using shared data statistics |

| US11481271B2 (en) * | 2021-03-16 | 2022-10-25 | Western Digital Technologies, Inc. | Storage system and method for using subcodes and convolutional-based LDPC interleaved coding schemes with read threshold calibration support |

| DE102022127544A1 (de) * | 2022-10-19 | 2024-04-25 | Infineon Technologies Ag | Elektronische Vorrichtung, elektronisches System, Verfahren zum Betreiben einer elektronischen Vorrichtung und Verfahren zum Betreiben eines elektronischen Systems |

| KR20240059345A (ko) | 2022-10-27 | 2024-05-07 | 삼성전자주식회사 | Ecc 디코더 및 이를 포함하는 메모리 컨트롤러 |

Family Cites Families (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5867429A (en) | 1997-11-19 | 1999-02-02 | Sandisk Corporation | High density non-volatile flash memory without adverse effects of electric field coupling between adjacent floating gates |

| US5953255A (en) | 1997-12-24 | 1999-09-14 | Aplus Flash Technology, Inc. | Low voltage, low current hot-hole injection erase and hot-electron programmable flash memory with enhanced endurance |

| US6204159B1 (en) | 1999-07-09 | 2001-03-20 | Advanced Micro Devices, Inc. | Method of forming select gate to improve reliability and performance for NAND type flash memory devices |

| US6469931B1 (en) | 2001-01-04 | 2002-10-22 | M-Systems Flash Disk Pioneers Ltd. | Method for increasing information content in a computer memory |

| US6522580B2 (en) | 2001-06-27 | 2003-02-18 | Sandisk Corporation | Operating techniques for reducing effects of coupling between storage elements of a non-volatile memory operated in multiple data states |

| KR100607992B1 (ko) | 2004-07-09 | 2006-08-02 | 삼성전자주식회사 | 낸드 플래시 메모리의 동작 상태의 감시를 통해 시스템을부팅하기 위한 방법 및 시스템 |

| US7061804B2 (en) | 2004-11-18 | 2006-06-13 | Qualcomm Incorporated | Robust and high-speed memory access with adaptive interface timing |

| US20060282610A1 (en) | 2005-06-08 | 2006-12-14 | M-Systems Flash Disk Pioneers Ltd. | Flash memory with programmable endurance |

| US7436703B2 (en) | 2005-12-27 | 2008-10-14 | Sandisk Corporation | Active boosting to minimize capacitive coupling effect between adjacent gates of flash memory devices |

| US7362615B2 (en) | 2005-12-27 | 2008-04-22 | Sandisk Corporation | Methods for active boosting to minimize capacitive coupling effect between adjacent gates of flash memory devices |

| US8055979B2 (en) | 2006-01-20 | 2011-11-08 | Marvell World Trade Ltd. | Flash memory with coding and signal processing |

| US7453723B2 (en) | 2006-03-01 | 2008-11-18 | Micron Technology, Inc. | Memory with weighted multi-page read |

| US7388781B2 (en) | 2006-03-06 | 2008-06-17 | Sandisk Il Ltd. | Multi-bit-per-cell flash memory device with non-bijective mapping |

| US7971130B2 (en) | 2006-03-31 | 2011-06-28 | Marvell International Ltd. | Multi-level signal memory with LDPC and interleaving |

| JP5142478B2 (ja) | 2006-04-13 | 2013-02-13 | 株式会社東芝 | 半導体記憶装置 |

| WO2007132457A2 (en) | 2006-05-12 | 2007-11-22 | Anobit Technologies Ltd. | Combined distortion estimation and error correction coding for memory devices |

| US7352628B2 (en) | 2006-06-19 | 2008-04-01 | Sandisk Corporation | Systems for programming differently sized margins and sensing with compensations at select states for improved read operations in a non-volatile memory |

| US7376014B2 (en) | 2006-08-18 | 2008-05-20 | Mammen Thomas | Highly reliable NAND flash memory using five side enclosed floating gate storage elements |

| US7805663B2 (en) | 2006-09-28 | 2010-09-28 | Sandisk Corporation | Methods of adapting operation of nonvolatile memory |

| US7818653B2 (en) | 2006-09-28 | 2010-10-19 | Sandisk Corporation | Methods of soft-input soft-output decoding for nonvolatile memory |

| JP5177991B2 (ja) * | 2006-10-25 | 2013-04-10 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| US7904788B2 (en) | 2006-11-03 | 2011-03-08 | Sandisk Corporation | Methods of varying read threshold voltage in nonvolatile memory |

| US7904780B2 (en) | 2006-11-03 | 2011-03-08 | Sandisk Corporation | Methods of modulating error correction coding |

| US8051358B2 (en) * | 2007-07-06 | 2011-11-01 | Micron Technology, Inc. | Error recovery storage along a nand-flash string |

| US8738841B2 (en) * | 2007-12-27 | 2014-05-27 | Sandisk Enterprise IP LLC. | Flash memory controller and system including data pipelines incorporating multiple buffers |

| JP5496198B2 (ja) * | 2008-07-22 | 2014-05-21 | エルエスアイ コーポレーション | フラッシュ・メモリにおいて信号レベルごとに複数のプログラム値をプログラミングするための方法および装置 |

| US20110041005A1 (en) * | 2009-08-11 | 2011-02-17 | Selinger Robert D | Controller and Method for Providing Read Status and Spare Block Management Information in a Flash Memory System |

| JP4660632B2 (ja) * | 2010-07-29 | 2011-03-30 | 株式会社東芝 | 半導体記憶装置 |

-

2010

- 2010-12-03 US US12/960,004 patent/US8464137B2/en active Active

-

2011

- 2011-11-24 JP JP2011256126A patent/JP5658128B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20120144272A1 (en) | 2012-06-07 |

| JP2012118979A (ja) | 2012-06-21 |

| US8464137B2 (en) | 2013-06-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5658128B2 (ja) | Nandフラッシュ・メモリにおける確率論的多層エラー訂正のためのシステム、方法、およびコンピュータ・プログラム | |

| US11256564B2 (en) | Media quality aware ECC decoding method selection to reduce data access latency | |

| US8429468B2 (en) | System and method to correct data errors using a stored count of bit values | |

| US7765426B2 (en) | Emerging bad block detection | |

| US8321757B2 (en) | Method and apparatus for error correction | |

| US9768808B2 (en) | Method for modifying device-specific variable error correction settings | |

| US10475518B2 (en) | Memory system, memory system control method, and program | |

| KR101343262B1 (ko) | 동시 판독 및 기록 메모리 동작을 수행하는 방법 및 장치 | |

| KR101614556B1 (ko) | 에러 정정을 처리하는 방법과, 이의 방법을 사용하는 데이터 저장 디바이스, 호스트 디바이스, 컴퓨터 프로그램을 저장하는 컴퓨터-판독가능한 매체 및 메모리용 제어기 | |

| CN107135006B (zh) | 错误校正电路和错误校正方法 | |

| US20160299812A1 (en) | Device-Specific Variable Error Correction | |

| CN106257594B (zh) | 读取干扰收回策略 | |

| US10230401B2 (en) | Memory controller for a non-volatile memory, memory system and method | |

| US20160299844A1 (en) | Mapping Logical Groups of Data to Physical Locations In Memory | |

| US10157099B2 (en) | Data storage device and data maintenance method thereof | |

| KR20130027138A (ko) | 에러 정정 방법 및 이를 이용하는 메모리 장치 | |

| US20160283319A1 (en) | Data storage device and encoding method thereof | |

| CN110532195A (zh) | 存储器系统的工作负荷分簇及执行其的方法 | |

| US9239751B1 (en) | Compressing data from multiple reads for error control management in memory systems | |

| CN117409845A (zh) | 分组管理方法、存储器存储装置及存储器控制器 | |

| US12487881B2 (en) | Decoding method, memory storage device and memory control circuit unit | |

| CN120255808A (zh) | 存储器管理方法与存储装置 | |

| CN120295580A (zh) | 存储器控制方法与存储装置 | |

| CN117785545A (zh) | 解码方法、存储器存储装置及存储器控制电路单元 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140528 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140610 Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20140610 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20140610 |

|

| RD12 | Notification of acceptance of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7432 Effective date: 20140610 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20140613 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20140707 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140805 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20140806 Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140806 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20141113 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20141113 |

|

| RD14 | Notification of resignation of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7434 Effective date: 20141113 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20141127 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5658128 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |