JP5599057B2 - Package and piezoelectric vibrator - Google Patents

Package and piezoelectric vibrator Download PDFInfo

- Publication number

- JP5599057B2 JP5599057B2 JP2010220138A JP2010220138A JP5599057B2 JP 5599057 B2 JP5599057 B2 JP 5599057B2 JP 2010220138 A JP2010220138 A JP 2010220138A JP 2010220138 A JP2010220138 A JP 2010220138A JP 5599057 B2 JP5599057 B2 JP 5599057B2

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- recess

- electrodes

- base substrate

- side wall

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

Landscapes

- Piezo-Electric Or Mechanical Vibrators, Or Delay Or Filter Circuits (AREA)

Description

この発明は、パッケージおよび圧電振動子に関するものである。 The present invention relates to a package and a piezoelectric vibrator.

例えば、携帯電話や携帯情報端末には、時刻源や制御信号などのタイミング源、リファレンス信号源などとして水晶などを利用した圧電振動子が用いられている。この種の圧電振動子は、様々なものが知られているが、その一つとして、2層構造タイプの表面実装型のパッケージが知られている。 For example, a cellular phone or a portable information terminal uses a piezoelectric vibrator using crystal or the like as a time source, a timing source such as a control signal, or a reference signal source. Various types of piezoelectric vibrators of this type are known. One of them is a two-layer structure type surface-mount package.

このような2層構造タイプのパッケージの1つとして、板状のベース部材(本願の「ベース基板」に相当)と、キャビティを有し、ベース部材と接合して該キャビティを密閉空間とするリッド部材(本願の「リッド基板」に相当)と、ベース部材上に実装される水晶板(本願の「圧電振動子」に相当)と、からなる水晶デバイスが知られている(特許文献1参照)。 As one of such two-layer structure type packages, a lid having a plate-like base member (corresponding to the “base substrate” of the present application) and a cavity, and joining the base member to make the cavity a sealed space There is known a crystal device comprising a member (corresponding to the “lid substrate” of the present application) and a quartz plate (corresponding to the “piezoelectric vibrator” of the present application) mounted on a base member (see Patent Document 1). .

この水晶デバイスのベース部材は、上面に引き出し電極(本願の「引き回し電極」に相当)が形成されており、下面に外部端子(本願の「外部電極」に相当)が形成されている。引き出し電極と外部端子とは、ベース部材を貫通して埋め込まれた金属ピンによる貫通電極によって電気的に接続されている。 The base member of this quartz crystal device has an extraction electrode (corresponding to the “leading electrode” in the present application) formed on the upper surface and an external terminal (corresponding to the “external electrode” in the present application) formed on the lower surface. The lead electrode and the external terminal are electrically connected by a through electrode made of a metal pin embedded through the base member.

ここで、圧電振動片に対向してパッケージ内の電極が配索されている場合、圧電振動片の主面に形成された電極と、パッケージ内の電極との空隙に静電容量が発生する、いわゆる容量結合が発生することが知られている。容量結合が発生すると、圧電振動片は静電容量の影響を受けて正常な発振ができなくなる。これにより、圧電振動子の電気的特性が悪化するおそれがある。 Here, when the electrode in the package is routed facing the piezoelectric vibrating piece, capacitance is generated in the gap between the electrode formed on the main surface of the piezoelectric vibrating piece and the electrode in the package. It is known that so-called capacitive coupling occurs. When capacitive coupling occurs, the piezoelectric vibrating piece is not able to oscillate normally due to the influence of capacitance. Thereby, there exists a possibility that the electrical property of a piezoelectric vibrator may deteriorate.

このため、例えば特許文献1では、ベース基板上の圧電振動片に対向する部位を避けるように、引き出し電極33を平面視で圧電振動片の外形に沿わせて配索している(特許文献1の図2参照)。このようにパッケージ内の電極を配索することで、圧電振動片の励振電極とパッケージ内の電極とが対向するのを回避して容量結合の発生を防止し、圧電振動子の良好な電気的特性を維持しようとしている。

For this reason, for example, in

ところで、近年の電子機器の小型化に伴い、パッケージおよびパッケージ内に搭載される電子部品に対する小型化が要求されている。

しかし、特許文献1のように、平面視で圧電振動片の外形に沿うようにパッケージ内の引き出し電極を配索した場合、圧電振動片の周辺にパッケージ内の電極を配索するためのスペースが必要となる。パッケージ内の電極を配索するためのスペースを確保することによりベース基板の面積が大きくなるため、パッケージの小型化に対する阻害要因となっている。

By the way, with recent miniaturization of electronic devices, miniaturization of packages and electronic components mounted in the packages is required.

However, as in

また、圧電振動片自体を小型化した場合には、一般に圧電振動子のCI値(Crystal Impedance)が上昇することが知られている。したがって、圧電振動子の良好な電気的特性を維持することができないおそれがある。 Further, it is known that when the piezoelectric vibrating piece itself is downsized, the CI value (Crystal Impedance) of the piezoelectric vibrator generally increases. Therefore, there is a possibility that good electrical characteristics of the piezoelectric vibrator cannot be maintained.

そこで本発明は、良好な電気的特性を維持しつつ小型化が可能なパッケージおよび圧電振動子の提供を課題とする。 Accordingly, an object of the present invention is to provide a package and a piezoelectric vibrator that can be reduced in size while maintaining good electrical characteristics.

上記の課題を解決するため、本発明のパッケージは、電子部品を封入するためのキャビティを形成可能な複数の基板を有し、前記複数の基板のうち第1基板に、前記キャビティ用の凹部を形成すると共に、この凹部と前記第1基板の外面側との間を貫通する複数の貫通電極を設けたパッケージであって、前記凹部の側壁に、前記電子部品と前記貫通電極とを電気的に接続するための引き回し電極を配索し、前記貫通電極の一端が前記凹部の前記側壁より突出するように形成されていることを特徴とする。 In order to solve the above problems, a package of the present invention has a plurality of substrates capable of forming a cavity for enclosing an electronic component, and a recess for the cavity is formed in a first substrate among the plurality of substrates. A package provided with a plurality of through electrodes penetrating between the concave portion and the outer surface side of the first substrate, wherein the electronic component and the through electrode are electrically connected to a side wall of the concave portion. A routing electrode for connection is routed , and one end of the through electrode is formed so as to protrude from the side wall of the recess .

本発明によれば、キャビティ用の凹部の側壁に引き回し電極を配索したことで、電子部品の電極と引き回し電極とが対向するのを回避できる。これにより、電子部品と引き回し電極との容量結合の発生を防止し、パッケージの良好な電気的特性を維持できる。また、凹部の側壁に引き回し電極を配索しているので、凹部の底面に引き回し電極を配索するためのスペースが不要となり、パッケージの小型化ができる。したがって、良好な電気的特性を維持しつつ小型化が可能なパッケージを提供できる。 According to the present invention, since the routing electrode is arranged on the side wall of the cavity recess, it is possible to prevent the electrode of the electronic component and the routing electrode from facing each other. As a result, it is possible to prevent the capacitive coupling between the electronic component and the lead-out electrode and maintain the good electrical characteristics of the package. Further, since the routing electrode is routed on the side wall of the recess, a space for routing the routing electrode on the bottom surface of the recess is not required, and the package can be reduced in size. Therefore, it is possible to provide a package that can be reduced in size while maintaining good electrical characteristics.

また、前記凹部の前記側壁で、前記複数の貫通電極のうち少なくとも1つの前記貫通電極の一端と前記引き回し電極とを電気的に接続したことが望ましい。

本発明によれば、凹部の底面に貫通電極と引き回し電極とを電気的に接続するためのスペースが不要となるので、パッケージのさらなる小型化ができる。

Moreover, it is desirable that the one end of at least one of the plurality of through electrodes and the lead-out electrode are electrically connected to the side wall of the recess.

According to the present invention, a space for electrically connecting the through electrode and the lead-out electrode on the bottom surface of the concave portion is not necessary, so that the package can be further reduced in size.

前記少なくとも1つの貫通電極の他端を前記第1基板の下面側に導出し、前記少なくとも1つの貫通電極は、前記第1基板の任意の一側面に投影させた形状が、前記凹部から前記下面に向かうにしたがって、前記第1基板の外側壁から遠ざかるように斜めに形成されていることが望ましい。

本発明によれば、貫通電極が第1基板の外側壁から遠ざかる分、第1基板の底面に向かうに従って外側壁と貫通電極との間の肉厚を厚く確保できる。したがって、貫通電極周辺の第1基板の強度を確保できる。

The other end of the at least one through electrode is led out to the lower surface side of the first substrate, and the shape of the at least one through electrode projected onto any one side surface of the first substrate is from the recess to the lower surface. It is desirable that it be formed obliquely so as to move away from the outer wall of the first substrate as it goes to.

According to the present invention, the thickness between the outer wall and the through electrode can be increased as the through electrode moves away from the outer wall of the first substrate toward the bottom surface of the first substrate. Therefore, the strength of the first substrate around the through electrode can be ensured.

また、前記凹部の底面と、前記凹部の側壁との間の角度をθとしたとき、

前記角度θは、

95°≦θ≦140°

を満たすように設定されていることが望ましい。

本発明によれば、凹部の開口側から見て凹部の各側壁がアンダーカット形状とならない。したがって、凹部の各側壁に対して、引き回し電極の成膜や、フォトリソグラフィによる処理等を容易に行うことができる。

When the angle between the bottom surface of the recess and the side wall of the recess is θ,

The angle θ is

95 ° ≦ θ ≦ 140 °

It is desirable to set so as to satisfy.

According to the present invention, each side wall of the recess is not undercut when viewed from the opening side of the recess. Therefore, it is possible to easily perform the formation of the lead electrode, the processing by photolithography, and the like on each side wall of the recess.

本発明の圧電振動子は、前記パッケージを用いた圧電振動子であって、前記複数の基板をガラスにより形成し、前記凹部の内部に、前記電子部品として圧電振動片が封入されていることを特徴とする。

本発明によれば、良好な電気的特性を維持しつつ小型化が可能な圧電振動子を提供できる。

The piezoelectric vibrator of the present invention is a piezoelectric vibrator using the package, wherein the plurality of substrates are formed of glass, and a piezoelectric vibrating piece is enclosed as the electronic component inside the recess. Features.

ADVANTAGE OF THE INVENTION According to this invention, the piezoelectric vibrator which can be reduced in size can be provided, maintaining a favorable electrical property.

本発明によれば、キャビティ用の凹部の側壁に引き回し電極を配索したことで、電子部品の電極と引き回し電極とが対向するのを回避できる。これにより、電子部品と引き回し電極との容量結合の発生を防止し、パッケージの良好な電気的特性を維持できる。また、本発明によれば凹部の側壁に引き回し電極を配索しているので、凹部の底面に引き回し電極を配索するためのスペースが不要となり、パッケージの小型化ができる。したがって、良好な電気的特性を維持しつつ小型化が可能なパッケージを提供できる。 According to the present invention, since the routing electrode is arranged on the side wall of the cavity recess, it is possible to prevent the electrode of the electronic component and the routing electrode from facing each other. As a result, it is possible to prevent the capacitive coupling between the electronic component and the lead-out electrode and maintain the good electrical characteristics of the package. Further, according to the present invention, since the routing electrode is routed on the side wall of the recess, a space for routing the routing electrode on the bottom surface of the recess is not required, and the package can be reduced in size. Therefore, it is possible to provide a package that can be reduced in size while maintaining good electrical characteristics.

(第1実施形態)

以下、本発明の第1実施形態に係る圧電振動片、圧電振動子および圧電振動子の製造方法を、図面を参照して説明する。

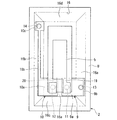

図1から図4に示すように、本実施形態の圧電振動子1は、ベース基板2(第1基板)およびリッド基板3(第2基板)が接合膜23を介して陽極接合され、凹部16に収納された圧電振動片4と、を備えた表面実装型の圧電振動子1である。

(First embodiment)

Hereinafter, a piezoelectric vibrating piece, a piezoelectric vibrator, and a method of manufacturing the piezoelectric vibrator according to the first embodiment of the present invention will be described with reference to the drawings.

As shown in FIGS. 1 to 4, in the

(圧電振動片)

圧電振動片4は、水晶の圧電材料から形成されたATカット型の振動片であり、所定の電圧が印加されたときに振動するものである。

この圧電振動片4は、平面視略矩形で厚さが均一の板状に加工された水晶板17と、水晶板17の両面に対向する位置で配置された一対の励振電極5,6と、励振電極5,6に電気的に接続された引き出し電極19,20と、引き出し電極19,20に電気的に接続されたマウント電極7,8と、を有している。

(Piezoelectric vibrating piece)

The piezoelectric vibrating

The piezoelectric vibrating

励振電極5,6、引き出し電極19,20、マウント電極7,8および側面電極15は、例えば、金(Au)の被膜で形成されている。なお、これらの膜は、クロム(Cr)、ニッケル(Ni)、アルミニウム(Al)やチタン(Ti)などの導電性膜の被膜あるいはこれら導電性膜のいくつかを組み合わせた積層膜により形成されていてもよい。

The

このように構成された圧電振動片4は、金等からなるバンプ11,12を利用して、ベース基板2の上面Uに形成された凹部16の底面16eに、フリップチップボンディングにより接合されている。具体的には、ベース基板2の凹部16にパターニングされた後述する引き回し電極9,10上にバンプ11,12が形成され、そのバンプ11,12上に、一対のマウント電極7,8がそれぞれ接触した状態でフリップチップボンディングにより接合されている。これにより、圧電振動片4は、ベース基板2の凹部16の底面16eからバンプ11,12の厚さ分、浮いた状態で支持されるとともに、マウント電極7,8と引き回し電極9,10とがそれぞれ電気的に接続された状態となっている。

The piezoelectric vibrating

(圧電振動子)

リッド基板3は、ガラス材料、例えばソーダ石灰ガラスからなる陽極接合可能な基板であり、略平板状に形成されている。リッド基板3におけるベース基板2との接合面側には、アルミニウム(Al)やシリコン(Si)等の導電性材料により、陽極接合用の接合膜23がパターニングされている。接合膜23は、ベース基板2に形成された凹部16の周囲を囲むように、ベース基板2の上面Uの形状に沿って形成されている。

(Piezoelectric vibrator)

The

ベース基板2は、ガラス材料、例えばソーダ石灰ガラスからなる基板であり、リッド基板3と同等の外形で略板状に形成されている。ベース基板2の上面Uには、圧電振動片4を収容する凹部16(キャビティ用の凹部)が形成されている。

The

凹部16は、底面16eと、圧電振動片4の幅方向における一方側(図3の右側)に配置された第1側壁16aと、前記幅方向における他方側(図3の左側)に配置された第2側壁16bと、圧電振動片4の基端側(図3の下側)に配置された第3側壁16cと、圧電振動片4の先端側(図3の上側)に配置された第4側壁16dと、により構成されている。

The

上面Uから凹部16の底面16eまでの深さは、圧電振動片4の厚み寸法と、バンプ11,12の厚み寸法とをあわせた寸法よりも深くなるように設定される。

ここで、凹部16の底面16eと、凹部16の各側壁16a,16b,16c,16dとの間の角度θ(図2参照)は、

95°≦θ≦140°・・・(1)

を満たすように設定されている。

すなわち、凹部16の底面16eよりも開口側が広くなるように形成されている。(1)式を満たすように角度θを設定したのは、各側壁16a,16b,16c,16dに引き回し電極9,10を形成する際、スパッタ法や真空蒸着法等による成膜や、フォトリソグラフィによる処理を容易にするためである。

The depth from the upper surface U to the

Here, the angle θ (see FIG. 2) between the

95 ° ≦ θ ≦ 140 ° (1)

It is set to satisfy.

That is, it is formed so that the opening side is wider than the

一般に、凹部16の開口側から成膜する際、各側壁16a,16b,16c,16dに成膜される膜厚は、底面16eに成膜される膜厚の1/tan(180−θ)となる。ここで、例えば、tan(180−θ)≧10の場合、各側壁16a,16b,16c,16dに成膜したい膜厚の10倍の厚さで、底面16eに成膜することになるため、フォトリソグラフィやエッチングが困難となる。したがって、底面16eと各側壁16a,16b,16c,16dとの膜厚差を10倍以内に押えるには、arctan(10)≒85°となるため、θ≧180°−85°、すなわちθは95°以上であることが望ましい。なお、θを140°以下としたのは、一般に、エッチングで各側壁16a,16b,16c,16dを形成したときのθの最大値が130°から140°程度となるためである。

そして、ベース基板2は、凹部16をリッド基板3側に対向させた状態でリッド基板3に対して陽極接合されている。

Generally, when forming a film from the opening side of the

The

(引き回し電極)

ベース基板2の凹部16内には、一対の引き回し電極9,10がパターニングされている。一対の引き回し電極9,10は、後述する貫通電極13,14のうち、一方の貫通電極13と圧電振動片4の一方のマウント電極7とを電気的に接続するとともに、他方の貫通電極14と圧電振動片4の他方のマウント電極8とを電気的に接続するようにパターニングされている。

(Ground electrode)

A pair of lead-out

一方の引き回し電極9は、圧電振動片4のマウント電極7,8側において、凹部16の底面16eと第1側壁16aとにまたがるように、平面視で略矩形状に形成されている。具体的に一方の引き回し電極9は、凹部16の底面16eに形成された底面電極9aと、凹部16の第1側壁16aに形成された側壁電極9bとで構成されている。

底面電極9a上には、バンプ11が形成されている。また、側壁電極9bは、後述の貫通電極13と接続されている。

One lead-out

他方の引き回し電極10は、一方の引き回し電極9に隣接した位置から、圧電振動片4の外形に沿って第2側壁16b上を引き回されており、平面視で略L字状に形成されている。具体的に他方の引き回し電極10は、凹部16の底面16eに形成された底面電極10aと、凹部16の第2側壁16bにおいて、圧電振動片4の基端側から先端側に向かって形成された側壁電極10bと、第2側壁16bにおける圧電振動片4の先端側に形成された接続電極10cと、で構成されている。

The

底面電極10a上には、バンプ12が形成されている。また、接続電極10cは、後述の貫通電極14と接続されている。そして、側壁電極10bは、底面電極10aと貫通電極14とを電気的に接続している。

そして、これら一対の引き回し電極9,10上のバンプ11,12を利用して、圧電振動片4のマウント電極7,8がフリップチップボンディングにより実装される。これにより、圧電振動片4の一方のマウント電極7が、一方の引き回し電極9を介して一方の貫通電極13に導通し、他方のマウント電極8が、他方の引き回し電極10を介して他方の貫通電極14に導通するようになっている。

The

(貫通電極)

ベース基板2には、一対の貫通電極13,14が形成されている。貫通電極13,14は、例えば金(Au)や白金(Pt)、ニッケル(Ni)合金、ハステロイ(登録商標)等の金属材料により形成された導電性の棒状部材である。貫通電極13,14の原料には、ベース基板2の材料であるガラス部材と線膨張係数の差が小さい金属が好適に用いられる。特に、鉄(Fe)を58重量パーセント、ニッケル(Ni)を42重量パーセント含有する合金(42アロイ)で形成することが望ましい。

(Penetration electrode)

A pair of through

貫通電極13,14は、ベース基板2の凹部16の底面16eに対して略垂直になるように配置されている。

また、一方の貫通電極13は、ベース基板2の第1側壁16a側(図3の右側)であって、圧電振動片4の基端側(図3の下側)に配置されており、一端側が第1側壁16aから露出し、他端側が下面Lから露出している。

これに対して、他方の貫通電極14は、ベース基板2の第2側壁16b側(図3の左側)であって、圧電振動片4の先端側(図3の上側)に配置されており、一端側が第2側壁16bから露出し、他端側が下面Lから露出している。

The through

One through

On the other hand, the other through

ベース基板2の下面Lには、一対の貫通電極13,14に対してそれぞれ電気的に接続される外部電極21,22が形成されている。つまり、一方の外部電極21は、一方の貫通電極13および一方の引き回し電極9を介して、圧電振動片4の第1の励振電極5に電気的に接続されている。また、他方の外部電極22は、他方の貫通電極14および他方の引き回し電極10を介して、圧電振動片4の第2の励振電極6に電気的に接続されている。

On the lower surface L of the

このように構成された圧電振動子1を作動させる場合には、ベース基板2に形成された外部電極21,22に対して、所定の駆動電圧を印加する。これにより、圧電振動片4の第1の励振電極5および第2の励振電極6からなる励振電極に電流を流すことができ、所定の周波数で振動させることができる。そして、振動を利用して、制御信号のタイミング源やリファレンス信号源などとして利用することができる。

When the

(圧電振動子の製造方法)

次に、上述した圧電振動子の製造方法を、フローチャートを参照しながら説明する。

図5は、圧電振動子の製造方法のフローチャートである。

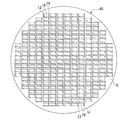

図6は、ベース基板用ウエハに複数の凹部16を形成した状態を示す図である。

図7は、ベース基板用ウエハの上面に接合膜及び引き回し電極をパターニングした状態を示す図である。

図8は、図7の部分拡大図である。

図9は、ウエハ体の分解斜視図である。

ここで、図7から図9に示す点線は、後に行う切断工程で切断する切断線Mを図示している。

本実施形態に係る圧電振動子の製造方法は、主に、圧電振動片作製工程S10と、リッド基板用ウエハ作製工程S20と、ベース基板用ウエハ作製工程S30と、組立工程(S50以降)を有している。そのうち、圧電振動片作製工程S10、リッド基板用ウエハ作製工程S20およびベース基板用ウエハ作製工程S30は、並行して実施することが可能である。

(Piezoelectric vibrator manufacturing method)

Next, a method for manufacturing the above-described piezoelectric vibrator will be described with reference to a flowchart.

FIG. 5 is a flowchart of a method for manufacturing a piezoelectric vibrator.

FIG. 6 is a diagram showing a state in which a plurality of

FIG. 7 is a view showing a state in which the bonding film and the routing electrode are patterned on the upper surface of the base substrate wafer.

FIG. 8 is a partially enlarged view of FIG.

FIG. 9 is an exploded perspective view of the wafer body.

Here, the dotted lines shown in FIG. 7 to FIG. 9 illustrate the cutting line M to be cut in the cutting process to be performed later.

The piezoelectric vibrator manufacturing method according to the present embodiment mainly includes a piezoelectric vibrating piece manufacturing step S10, a lid substrate wafer manufacturing step S20, a base substrate wafer manufacturing step S30, and an assembly step (S50 and subsequent steps). doing. Among them, the piezoelectric vibrating piece producing step S10, the lid substrate wafer producing step S20, and the base substrate wafer producing step S30 can be performed in parallel.

(圧電振動片作製工程S10)

圧電振動片作製工程S10では、図2から図4に示す圧電振動片4を作製する。具体的には、まず水晶のランバート原石を所定の角度でスライスして一定の厚みのウエハとする。続いて、このウエハをラッピングして粗加工した後、ポリッシュなどの鏡面研磨加工を行って、一定の厚みのウエハとする。続いて、ウエハに洗浄などの適切な処理を施した後、該ウエハをフォトリソグラフィ技術によって、金属膜の成膜及びパターニングを行って、励振電極5,6、引き出し電極19,20、マウント電極7,8および側面電極15を形成する。これにより、複数の圧電振動片4を作製する。

(Piezoelectric vibrating piece manufacturing step S10)

In the piezoelectric vibrating piece producing step S10, the piezoelectric vibrating

(リッド基板用ウエハ作製工程S20)

リッド基板用ウエハ作製工程S20では、ソーダ石灰ガラスからなる円板状のリッド基板用ウエハ50を、所定の厚さまで研磨加工して洗浄した後に、エッチングなどにより最表面の加工変質層を除去する(S21)。次いで、リッド基板用ウエハ50におけるベース基板用ウエハ40との合わせ面に導電性材料をパターニングして、接合膜23(図1参照)を形成する接合膜形成工程S22を行う。なお、本実施形態では、接合膜23をリッド基板用ウエハ50に形成しているが、ベース基板用ウエハ40に形成してもかまわない。

(Lid substrate wafer manufacturing step S20)

In the lid substrate wafer manufacturing step S20, the disk-shaped

(ベース基板用ウエハ作製工程S30)

ベース基板用ウエハ作製工程S30は、主にベース基板用ウエハ40に貫通電極13,14を圧入する貫通電極圧入工程S33と、ベース基板用ウエハ40に凹部16を形成する凹部形成工程S35と、ベース基板用ウエハ40に引き回し電極を形成する引き回し電極形成工程S37とを有している。

ベース基板用ウエハ作製工程S30では、図6に示すように、後にベース基板2となるベース基板用ウエハ40を作製する。まず、ソーダ石灰ガラスからなる円板状のベース基板用ウエハ40を、所定の厚さまで研磨加工して洗浄した後に、エッチングなどにより最表面の加工変質層を除去する(S31)。

(Base substrate wafer manufacturing step S30)

The base substrate wafer manufacturing step S30 mainly includes a through electrode press-fitting step S33 for press-fitting the through

In the base substrate wafer manufacturing step S30, as shown in FIG. 6, a

(貫通電極圧入工程S33)

次いで、ベース基板用ウエハ40に貫通電極13,14を圧入する貫通電極圧入工程S33を行う。貫通電極圧入工程S33では、予めベース基板用ウエハ40を加熱して軟化状態とする。そして、後の凹部16の第1側壁16aに対応する位置に貫通電極13を、後の凹部16の第2側壁16bに対応する位置に貫通電極14を圧入する。

(Penetration electrode press-fitting step S33)

Next, a through electrode press-fitting step S33 for press-fitting the through

(凹部形成工程S35)

次に、凹部形成工程S35では、ベース基板用ウエハ40の上面Uに、凹部16を複数形成する。凹部16の形成は、例えば、エッチング加工等によって行う。

具体的な凹部形成工程S35としては、まず、ベース基板用ウエハ40の表面に、金等からなる膜を形成した後、凹部16に対応した部分をヨウ素ヨウ化カリウム水溶液や王水(塩酸と硝酸との混合液)等で除去し、凹部16をエッチングするためのマスクを形成する。続いて、フッ酸等からなる水溶液を使用してベース基板用ウエハ40のエッチングを行う。以上により、底面16eと、各側壁16a,16b,16c,16dとからなる凹部16がベース基板用ウエハ40の上面Uに複数形成される。

(Recess formation step S35)

Next, in the recess forming step S <b> 35, a plurality of

As a specific recess forming step S35, first, a film made of gold or the like is formed on the surface of the

(引き回し電極形成工程S37)

次に、貫通電極13,14にそれぞれ電気的に接続された引き回し電極9,10(図8参照)を複数形成する、引き回し電極形成工程S37を行う。引き回し電極9は、凹部16の底面16eおよび第1側壁16aに形成され、第1側壁16aに形成された側壁電極9bは貫通電極13を覆うように形成される。また、引き回し電極10は、凹部16の底面16eおよび第2側壁16bに形成され、第2側壁16bに形成された接続電極10cは貫通電極14を覆うように形成される。引き回し電極9,10は、スパッタ法や真空蒸着法等により形成された被膜を、フォトリソグラフィ技術によりパターニングして形成される。なお、各引き回し電極9,10は同一の材料で形成されるため、各引き回し電極9,10を同時に形成することができる。

そして、引き回し電極9,10の底面電極9a、10a上に、それぞれ金等からなるバンプ11,12(図4参照)を形成する。なお、図7から図9では、図面の見易さのためバンプの図示を省略している。

(Leading electrode forming step S37)

Next, a lead electrode forming step S37 is performed in which a plurality of

Then, bumps 11 and 12 (see FIG. 4) made of gold or the like are formed on the

(外部電極形成工程S40)

次に、ベース基板用ウエハ40の下面Lに導電性材料をパターニングして、一対の貫通電極13,14にそれぞれ電気的に接続された一対の外部電極21,22(図1参照)を形成する外部電極形成工程S40を行う。この工程により、圧電振動片4は、貫通電極13,14を介して、外部電極21,22と導通する。

外部電極21,22を形成した時点でベース基板用ウエハ作製工程S30が終了する。

(External electrode forming step S40)

Next, a conductive material is patterned on the lower surface L of the

When the

(マウント工程S50以降の圧電振動子組立工程)

次に、ベース基板用ウエハ40の引き回し電極9,10上に、バンプ11,12を介して圧電振動片4を接合するマウント工程S50を行う。具体的には、圧電振動片4をフリップチップボンダの接合ヘッド(不図示)でピックし、バンプ11,12を所定温度に加熱しながら接合ヘッドを振動させ、圧電振動片4をバンプ11,12に押し付ける。これにより、圧電振動片4の水晶板17が、ベース基板用ウエハ40の凹部16の底面16eから浮いた状態で、マウント電極7,8がバンプ11,12にフリップチップボンディングされる。

(Piezoelectric vibrator assembly process after mounting process S50)

Next, a mounting step S50 is performed in which the

圧電振動片4の実装が終了した後、ベース基板用ウエハ40に対してリッド基板用ウエハ50を重ね合わせる重ね合わせ工程S60を行う。具体的には、図示しない基準マークなどを指標としながら、両ウエハ40、50を正しい位置にアライメントする。これにより、ベース基板用ウエハ40の凹部16内に実装された圧電振動片4が、リッド基板用ウエハ50とベース基板用ウエハ40とに収容された状態となる。

After the mounting of the piezoelectric vibrating

重ね合わせ工程S60の後、重ね合わせた両ウエハ40,50を図示しない陽極接合装置に入れ、所定の温度雰囲気で所定の電圧を印加して陽極接合する接合工程S70を行う。具体的には、接合膜23とベース基板用ウエハ40との間に所定の電圧を印加する。すると、接合膜23とベース基板用ウエハ40との界面に電気化学的な反応が生じ、両者がそれぞれ強固に密着して陽極接合される。

After the superposition step S60, the superposed

次に、接合されたウエハ体70を切断線M(図9参照)に沿って切断して小片化する切断工程S80を行う。その結果、互いに陽極接合されたベース基板2とリッド基板3との間に形成された凹部16内に圧電振動片4が封止された、図1に示す2層構造式表面実装型の圧電振動子1を一度に複数製造することができる。

Next, a cutting step S80 is performed in which the bonded

その後、内部の電気特性検査S90を行う。即ち、圧電振動片4の共振周波数、共振抵抗値、ドライブレベル特性(共振周波数及び共振抵抗値の励振電力依存性)などを測定してチェックする。また、絶縁抵抗特性などを併せてチェックする。そして、圧電振動子1の外観検査を行って、寸法や品質などをチェックする。全てのチェックが完了した時点で、圧電振動子1の製造が終了する。

Thereafter, an internal electrical characteristic inspection S90 is performed. That is, the resonance frequency, resonance resistance value, drive level characteristic (excitation power dependence of resonance frequency and resonance resistance value), etc. of the piezoelectric vibrating

(効果)

第1実施形態によれば、凹部16の第1側壁16aおよび第2側壁16bに引き回し電極9,10を配索したことで、圧電振動片4の励振電極5,6等の各電極と引き回し電極9,10とが対向するのを回避できる。これにより、圧電振動片4と引き回し電極9,10との容量結合の発生を防止し、圧電振動子1の良好な電気的特性を維持できる。また、本発明によれば凹部16の第1側壁16aおよび第2側壁16bに引き回し電極9,10を配索しているので、凹部16の底面16eに引き回し電極9,10を配索するためのスペースが不要となり、圧電振動子1の小型化ができる。したがって、良好な電気的特性を維持しつつ小型化が可能な圧電振動子1を提供できる。

(effect)

According to the first embodiment, the

また、第1実施形態によれば、凹部16の第1側壁16aおよび第2側壁16bで貫通電極13,14の一端と引き回し電極9,10とを電気的に接続しているので、凹部16の底面16eに貫通電極13,14と引き回し電極9,10とを電気的に接続するためのスペースが不要となり、圧電振動子1のさらなる小型化ができる。

In addition, according to the first embodiment, the

(第1参考形態、凹部内に突出した貫通電極の削除)

次に、第1参考形態について説明する。

上述の第1実施形態では、図2に示すように、貫通電極13,14の端部が凹部16の各側壁16a,16bから突出していた。しかし、第1参考形態では、貫通電極13,14の端部が各側壁16a,16bと面一になるように形成する点で異なっている。

( First reference form , deletion of the through electrode protruding into the recess)

Next, the first reference embodiment will be described.

In the first embodiment described above, the end portions of the through

第1参考形態では、凹部形成工程S35の後、凹部16の各側壁16a,16bから突出した貫通電極13,14の端部を除去する。具体的には、ヨウ素ヨウ化カリウム水溶液や王水(塩酸と硝酸との混合液)等により貫通電極13,14の端部をエッチングする。これにより、貫通電極13,14の端部が各側壁16a,16bから突出することなく、貫通電極13,14の端部と各側壁16a,16bとを略面一にすることができる。

In the first reference embodiment , after the recess forming step S35, the end portions of the through

(効果)

第1参考形態によれば、貫通電極13,14の端部と各側壁16a,16bとを略面一に形成するので、引き回し電極9,10の側壁電極9b,10bを形成する際に、容易に形成することができる。したがって、貫通電極13,14と、引き回し電極9,10とを容易に接続することができる。

(effect)

According to the first reference embodiment , since the end portions of the through

(第1実施形態の変形例、傾斜した貫通電極)

次に、第1実施形態の変形例について説明する。

図10は、第1実施形態の変形例における圧電振動子1のA−A線に沿った断面図である。

上述の第1実施形態では、図2に示すように、貫通電極13,14が凹部16の底面16eに対して略垂直になるように配置されていた。しかし、第1実施形態の変形例では、貫通電極13,14が底面16eの垂直方向に対し傾斜して配置されている点で異なっている。なお、変形例の貫通電極13および貫通電極14は同様の構成であるため、以下では、貫通電極13についてのみ説明をし、貫通電極14の説明を省略している。また、貫通電極13,14以外の構成は上述した実施形態と同一であるため、詳細な説明を省略している。

( Modification of the first embodiment, inclined through electrode)

Next, a modification of the first embodiment will be described.

FIG. 10 is a cross-sectional view taken along the line AA of the

In the first embodiment described above, the through

図10に示すように、凹部16からベース基板2の下面Lにかけて、貫通電極13はベース基板2の外側壁2aから遠ざかるように配置されている。そして、貫通電極13の外周面と、ベース基板2の外側壁2aとの間隔は、ベース基板2の内側よりもベース基板2の外側のほうが広くなっている。すなわち、貫通電極13とベース基板2の外側壁2aとの間の肉厚は、ベース基板2の外側が厚くなるように貫通電極13を配置している。したがって、第1実施形態の変形例によれば、貫通電極13,14周辺のベース基板2の強度を確保できる。

As shown in FIG. 10, the through

(第2参考形態、凹部形成工程S35)

次に、第2参考形態について説明する。

図11は、第2参考形態の凹部形成工程S35の説明図であり、図11(a)はプレス

前の説明図であり、図11(b)はプレス後の説明図であり、図11(c)は貫通電極1

3,14の先端を除去したときの説明図である。

第1実施形態の凹部形成工程S35では、エッチングにより凹部16を形成していた。

しかし、第2参考形態の凹部形成工程S35では、プレスにより凹部16を形成する点で

第1実施形態と異なっている。以下に、第2参考形態の凹部形成工程S35について説明

をする。なお、第1実施形態と同一の内容については詳細な説明を省略している。また、

貫通電極13を含む断面図を例にして工程を説明しているが、貫通電極14との関係につ

いても同様である。

( 2nd reference form , recessed part formation process S35)

Next, the second reference embodiment will be described.

FIG. 11 is an explanatory diagram of the recess forming step S35 of the second reference embodiment , FIG. 11 (a) is an explanatory diagram before pressing, FIG. 11 (b) is an explanatory diagram after pressing, and FIG. c) Through

It is explanatory drawing when the front-end | tip of 3 and 14 is removed.

In the recess forming step S35 of the first embodiment, the

However, the recess forming step S35 of the second reference embodiment is different from the first embodiment in that the

The process is described by taking a cross-sectional view including the through

第2参考形態の凹部形成工程S35は、図11に示すように、ベース基板用ウエハ40を嵌入可能な受け部80aを有する受型80と、受け部80aに嵌入されたベース基板用ウエハ40を押圧する加圧型85とを用いて行う。

加圧型85は、予め貫通電極13が圧入されたベース基板用ウエハ40に対して押圧する。加圧型85には、凹部16を形成するための凸部85aが設けられている。また、凸部85aの貫通電極13に対応した位置には、逃げ部85bが形成されている。逃げ部85bを設けたのは、プレス時に、傾斜した第1側壁16aから貫通電極の凹部16側の端部が突出して、貫通電極13と加圧型85とが干渉するのを回避するためである。

As shown in FIG. 11, the recess forming step S35 of the second reference embodiment includes a receiving

The pressurizing die 85 presses against the

第2参考形態の凹部形成工程S35は、以下の手順で行われる。

まず、図11(a)に示すように、受型80の受け部80aにベース基板用ウエハ40

をセットし、受型80をベース基板用ウエハ40とともに加熱炉(不図示)に配置する。

そして、所定温度になるように加熱炉を加熱する。

The recess forming step S35 of the second reference form is performed according to the following procedure.

First, as shown in FIG. 11A, the

And the receiving die 80 is placed in a heating furnace (not shown) together with the

And a heating furnace is heated so that it may become predetermined temperature.

続いて、プレス機(不図示)等を利用して加圧型85によってベース基板用ウエハ40を押圧する。この結果、図11(b)に示すように、ベース基板用ウエハ40は座屈変形し、加圧型85と貫通電極13との干渉を回避しつつ、凹部16が形成される。この時点で貫通電極13の凹部16側は、第1側壁16aから突出しており、表面がベース基板用ウエハ40のガラス材料に覆われている。

Subsequently, the

最後に、図11(c)に示すようにヨウ素ヨウ化カリウム溶液や王水(塩酸と硝酸との混合液)等によるエッチングやサンドブラスト等により、貫通電極13のうち、第1側壁16aから突出した部分を除去して、貫通電極13の表面を第1側壁16aから露出させる。以上で、凹部形成工程S35が終了する。

Finally, as shown in FIG. 11C, the penetrating

(効果)

第2参考形態によれば、熱プレスにより、凹部16を精度良く簡単に形成することができる。特に、ベース基板用ウエハ40がガラス部材により形成されている場合に、熱プレスにより凹部16を形成するのが効果的である。

(effect)

According to the second reference embodiment , the

なお、この発明は上述した実施の形態に限られるものではない。

第1実施形態および第2参考形態では、パッケージの内部にATカット型の圧電振動片4を封入した圧電振動子1を例にして説明をした。しかし、これに限られるものではなく、パッケージの内部に音叉型の圧電振動片を封入してもよい。また、圧電振動片以外の素子を封入してもよい。

The present invention is not limited to the embodiment described above.

In the first embodiment and the second reference embodiment , the

第1実施形態および第2参考形態では、ベース基板用ウエハ40に棒状の貫通電極13,14を圧入して配置している。しかし、例えば、ベース基板用ウエハ40に凹部を形成し、凹部に貫通電極13,14を挿入した後、ガラスフリットを充填して焼成することにより、ベース基板用ウエハ40に貫通電極13,14を配置してもよい。ただし、ベース基板用ウエハ40を研磨し、凹部16の第1側壁16a、第2側壁16b、およびベース基板2の下面Lから貫通電極13,14を露出させる必要がある。したがって、作業効率の点で、本実施形態に優位性がある。

In the first embodiment and the second reference embodiment , the bar-shaped through

第1実施形態および第2参考形態では、ベース基板用ウエハ40に貫通電極13,14を圧入した後に、凹部16を形成している。しかし、キャビティ形成後に、貫通電極13,14を圧入してもよい。

In the first embodiment and the second reference embodiment , the

第1実施形態および第2参考形態では、第1側壁16aおよび第2側壁16bに貫通電極13,14を形成していた。しかし、貫通電極13および貫通電極14のいずれか一方のみが、第1側壁16aおよび第2側壁16bのいずれか一方に形成されていてもよい。少なくとも1つの貫通電極が側壁に形成されることで、パッケージサイズを縮小することができる。

In the first embodiment and the second reference embodiment , the through

第1実施形態では、エッチングによりベース基板用ウエハ40に凹部16を形成している。しかし、例えば、サンドブラストにより凹部16を形成してもよい。

In the first embodiment, the

第1実施形態の変形例では、貫通電極13,14がそれぞれ外側壁2a,2bから遠ざかるように斜めに形成していた。しかし、貫通電極13および貫通電極14のいずれか一方のみが、外側壁2a,2bから遠ざかるように斜めに形成してもよい。少なくとも1つの貫通電極が外側壁から遠ざかるように斜めに形成することで、パッケージ強度を向上させることができる。

In the modification of the first embodiment, the through

第1実施形態の変形例では、貫通電極13,14をベース基板用ウエハ40に圧入することで、外側壁2a,2bから遠ざかるように斜めに形成していた。しかし、例えば、第2参考形態のように熱プレスをした際に、ベース基板用ウエハ40を押圧したときの圧力を利用して貫通電極13,14を傾斜させてもよい。

In the modification of the first embodiment, the through

第2参考形態では、予めベース基板用ウエハ40に貫通電極13を圧入して配置した後にプレスにより凹部16を形成している。しかし、凹部16を形成した後に、貫通電極13を圧入して配置してもよい。

In the second reference embodiment , the recessed

第2参考形態では、貫通電極13は棒状に形成されており、凹部16形成後に、第1側壁16aから突出した貫通電極13を除去している。しかし、例えば、貫通電極13の凹部16側の端部を、第1側壁16aに沿わせるように斜めに形成してもよい。これにより、加圧型85に逃げ部85bを形成する必要がなくなるので、加圧型85の命数が向上する。ただし、貫通電極13を簡単に形成できる点で、第2参考形態に優位性がある。

In the second reference embodiment , the through

1・・・圧電振動子(パッケージ) 2・・・ベース基板(第1基板) 2a,2b・・・外側壁 4・・・圧電振動片(電子部品) 9,10・・・引き回し電極 13,14・・・貫通電極 16・・・凹部 16a,16b,16c,16d・・・側壁 16e・・・底面

DESCRIPTION OF

Claims (5)

前記複数の基板のうち第1基板に、前記キャビティ用の凹部を形成すると共に、この凹部と前記第1基板の外面側との間を貫通する複数の貫通電極を設けたパッケージであって、

前記凹部の側壁に、前記電子部品と前記貫通電極とを電気的に接続するための引き回し電極を配索し、

前記貫通電極の一端が前記凹部の前記側壁より突出するように形成されていることを特徴とするパッケージ。 A plurality of substrates capable of forming cavities for enclosing electronic components;

The first substrate among the plurality of substrates is formed with a recess for the cavity and provided with a plurality of through electrodes penetrating between the recess and the outer surface side of the first substrate,

A routing electrode for electrically connecting the electronic component and the through electrode is arranged on the side wall of the recess ,

A package , wherein one end of the through electrode protrudes from the side wall of the recess .

前記凹部の前記側壁で、前記複数の貫通電極のうち少なくとも1つの貫通電極の一端と前記引き回し電極とを電気的に接続したことを特徴とするパッケージ。 The package of claim 1,

A package, wherein one end of at least one through electrode among the plurality of through electrodes and the lead-out electrode are electrically connected to the side wall of the recess.

前記少なくとも1つの貫通電極の他端を前記第1基板の下面側に導出し、

前記少なくとも1つの貫通電極は、前記第1基板の任意の一側面に投影させた形状が、前記凹部から前記下面に向かうにしたがって、前記第1基板の外側壁から遠ざかるように斜めに形成されていることを特徴とするパッケージ。 A package according to claim 2, wherein

The other end of the at least one through electrode is led out to the lower surface side of the first substrate,

The at least one through electrode is formed obliquely so that the shape projected on an arbitrary side surface of the first substrate is away from the outer wall of the first substrate as it goes from the recess to the lower surface. Package characterized by being.

前記凹部の底面と、前記凹部の側壁との間の角度をθとしたとき、

前記角度θは、

95°≦θ≦140°

を満たすように設定されていることを特徴とするパッケージ。 The package according to any one of claims 1 to 3,

When the angle between the bottom surface of the recess and the side wall of the recess is θ,

The angle θ is

95 ° ≦ θ ≦ 140 °

A package characterized by being set to satisfy.

前記複数の基板をガラスにより形成し、

前記凹部の内部に、前記電子部品として圧電振動片を封入したことを特徴とする圧電振動子。 A piezoelectric vibrator using the package according to any one of claims 1 to 4,

Forming the plurality of substrates with glass;

A piezoelectric vibrator comprising a piezoelectric vibrating piece sealed as the electronic component inside the recess.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010220138A JP5599057B2 (en) | 2010-09-30 | 2010-09-30 | Package and piezoelectric vibrator |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010220138A JP5599057B2 (en) | 2010-09-30 | 2010-09-30 | Package and piezoelectric vibrator |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012075053A JP2012075053A (en) | 2012-04-12 |

| JP5599057B2 true JP5599057B2 (en) | 2014-10-01 |

Family

ID=46170778

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010220138A Expired - Fee Related JP5599057B2 (en) | 2010-09-30 | 2010-09-30 | Package and piezoelectric vibrator |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5599057B2 (en) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6164879B2 (en) * | 2013-03-08 | 2017-07-19 | セイコーインスツル株式会社 | Package, piezoelectric vibrator, oscillator, electronic equipment and radio clock |

| JP7247694B2 (en) | 2019-03-25 | 2023-03-29 | セイコーエプソン株式会社 | Vibration devices, oscillators, vibration modules, electronic devices and moving objects |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS575417A (en) * | 1980-06-12 | 1982-01-12 | Citizen Watch Co Ltd | Airtight package for quartz oscillator |

| JPH02137511A (en) * | 1988-11-18 | 1990-05-25 | Nippon Electric Glass Co Ltd | Package for hermetic seal |

| JPH10135771A (en) * | 1996-11-01 | 1998-05-22 | Tdk Corp | Piezoelectric component |

| JP2002151994A (en) * | 2000-11-10 | 2002-05-24 | Citizen Watch Co Ltd | Package structure for crystal vibrator and its manufacturing method |

| JP4267527B2 (en) * | 2003-08-20 | 2009-05-27 | 日本電波工業株式会社 | Crystal oscillator for surface mounting |

| JP4522182B2 (en) * | 2004-07-29 | 2010-08-11 | 京セラ株式会社 | Piezoelectric element storage package, piezoelectric device, and method of manufacturing piezoelectric device |

| JP4586753B2 (en) * | 2006-03-17 | 2010-11-24 | エプソントヨコム株式会社 | Piezoelectric oscillator |

| JP5026323B2 (en) * | 2008-03-31 | 2012-09-12 | シチズンファインテックミヨタ株式会社 | Electronic devices |

| JP2010081416A (en) * | 2008-09-26 | 2010-04-08 | Citizen Finetech Miyota Co Ltd | Electrode structure and electronic device |

| JP5230329B2 (en) * | 2008-09-30 | 2013-07-10 | シチズンファインテックミヨタ株式会社 | Piezoelectric device |

-

2010

- 2010-09-30 JP JP2010220138A patent/JP5599057B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2012075053A (en) | 2012-04-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI496415B (en) | A piezoelectric vibrator, a piezoelectric vibrator, an oscillator, an electronic device, a radio wave, and a method of manufacturing the piezoelectric vibrating plate | |

| JP5880538B2 (en) | Piezoelectric vibrating piece, piezoelectric vibrator, method for manufacturing piezoelectric vibrating piece, and method for manufacturing piezoelectric vibrator | |

| JP2010187333A (en) | Piezoelectric vibrator, method for manufacturing piezoelectric vibrator, and oscillator | |

| JP2010186956A (en) | Method of manufacturing glass-sealed package, manufacturing apparatus for glass-sealed package, and oscillator | |

| JP2007214941A (en) | Piezoelectric vibration chip and piezoelectric device | |

| EP2219291A2 (en) | Method for manufacturing piezoelectric vibrator, piezoelectric vibrator, and oscillator | |

| US8689415B2 (en) | Methods for manufacturing piezoelectric devices | |

| JP5213614B2 (en) | Piezoelectric device and manufacturing method thereof | |

| US8341814B2 (en) | Methods for manufacturing piezoelectric devices | |

| JP5130952B2 (en) | Piezoelectric vibration device and method for manufacturing piezoelectric vibration device | |

| JP5397336B2 (en) | Piezoelectric vibrating piece and piezoelectric vibrator | |

| JP5599057B2 (en) | Package and piezoelectric vibrator | |

| JPWO2010061470A1 (en) | Manufacturing method of wafer and package product | |

| JP6295835B2 (en) | Piezoelectric vibrating piece and piezoelectric device using the piezoelectric vibrating piece | |

| JP2008236514A (en) | Piezoelectric viblation device | |

| CN114208027A (en) | Piezoelectric vibrating plate, piezoelectric vibrating device, and method for manufacturing piezoelectric vibrating device | |

| US9172347B2 (en) | Wafer, method of manufacturing package, and piezoelectric oscillator | |

| JP6123217B2 (en) | Piezoelectric vibrating piece | |

| JP3968782B2 (en) | Electronic component package, piezoelectric vibration device using the package, and method of manufacturing piezoelectric vibration device | |

| JP5263529B2 (en) | Method for manufacturing piezoelectric vibrator | |

| JP5263779B2 (en) | Piezoelectric vibrating piece, piezoelectric vibrator, method of manufacturing piezoelectric vibrator, oscillator, electronic device, and radio timepiece | |

| JP2004357131A (en) | Piezoelectric vibrator | |

| JP4020031B2 (en) | Piezoelectric vibrating piece, piezoelectric device using the piezoelectric vibrating piece, mobile phone device using the piezoelectric device, and electronic equipment using the piezoelectric device | |

| JP5703522B2 (en) | Package, package manufacturing method, piezoelectric vibrator | |

| JP4541983B2 (en) | Piezoelectric vibrator |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130705 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140206 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140212 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140404 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140729 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20140808 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140808 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5599057 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |