[実施の形態1]

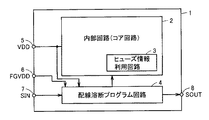

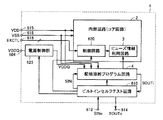

図1は、この発明の実施の形態1に従う半導体装置の全体の構成を概略的に示す図である。図1において、半導体装置1は、所定の機能を実現する内部回路(コア回路)2と、内部回路2の動作状態または動作態様を規定する情報(内部回路に関連する情報)を固定的に記憶する配線溶断プログラム回路4とを含む。

この半導体装置1は、1つの半導体チップ上に形成されてもよく、また他のプロセッサまたはメモリなどの機能ブロックと同一チップ上に集積化されてもよく、この半導体装置は、半導体集積回路装置と等価である。

内部回路2は、電源ノード(パッド)5を介して外部から与えられる電源電圧VDDを動作電源電圧として受け、所定の機能を実現する。この内部回路2は、半導体装置(半導体集積回路装置)1のコア回路であり、たとえばメモリセルアレイを含むメモリ回路であってもよく、またプロセッサなどの処理装置であってもよい。内部回路2は、銅(Cu)の多層配線を用いて内部配線の配置・配線が行なわれていればよい。

この内部回路2においては、ヒューズ情報利用回路3が含まれ、ヒューズ情報利用回路3は、配線溶断プログラム回路4からのプログラム情報(ヒューズ情報)に従ってその動作状態または動作態様が規定される。

たとえばこの内部回路2がメモリ回路の場合、ヒューズ情報利用回路3は不良セル救済のための冗長デコーダを含み、この冗長デコーダが配線溶断プログラム回路4の記憶情報に従って選択的に冗長置換を行なって不良セルの救済を行なう。このヒューズ情報利用回路3は、また、配線溶断プログラム回路4からのプログレシブ情報(ヒューズ情報)に従ってその発生する電圧レベルまたは電流、もしくは抵抗値などのアナログ量が設定されてもよい。

配線溶断プログラム回路4は、複数のヒューズ素子を含み、これらのヒューズ素子の溶断/非溶断により情報を固定的に記憶する。ヒューズ素子FSのヒューズは、多層配線の内の第i層の配線Miにより形成される。

この配線溶断プログラム回路4は、内部回路2と同じ配線およびメタル配線(銅(Cu)配線)のうちの上層のメタル配線を用いてヒューズ素子を実現する。配線溶断プログラム回路4は、電源ノード5からの電源電圧VDDとヒューズ電源ノード(パッド)6を介して外部から与えられるヒューズゲート電源電圧FGVDDを受ける。このヒューズゲート電源電圧FGVDDは、ヒューズ素子プログラム時に、溶断用の電流を流すための制御電圧として利用される。ヒューズゲート電源電圧FGVDDを外部から印加することにより、ヒューズ溶断時にヒューズに供給される溶断電流量を最適値に設定する。

この配線溶断プログラム回路4においては、後に説明するように、複数のヒューズ素子が並列に配列され、これらのヒューズ素子の溶断/非溶断の選択的なプログラムを行なうためにスキャンパスが設けられる。このスキャンパスにおいては、ヒューズ素子に対応してフリップフロップが設けられる。フリップフロップ列で構成されるスキャンパスを介して入力ノード7からのシリアル入力SINを転送し、各ヒューズ素子に対応するフリップフロップにヒューズプログラム情報を設定し、出力ノード8からフリップフロップの記憶情報をシリアル出力SOUTとして出力する。シリアル出力SOUTの用途については、後に説明する。

図2は、配線溶断プログラム回路4の具体的構成の一例を示す図である。図2において、配線溶断プログラム回路4は、各々がヒューズ回路を含みかつ互いに縦続接続される複数のヒューズプログラム回路FPK1−FPKnを含む。これらのヒューズプログラム回路FPK1−FPKnの数は任意である。このヒューズプログラム回路FPK1−FPKnは、同一構成を有するため、図2においては、ヒューズプログラム回路FPK1−FPKn各々において同一または対応する部分には同一参照番号を付す。

ヒューズプログラム回路FPK2−FPKnの各々は、電源電圧VDDを供給するノード(ヒューズ電源ノード)と内部ノードND1の間に接続されるヒューズ素子FSと、内部ノードND1と接地ノードの間に接続される溶断電流供給トランジスタCTrと、溶断電流供給トランジスタCTrの導通を制御する3入力AND回路AG1を含む。AND回路AG1は、内部ヒューズゲート電源電圧FGVD1を動作電源電圧として受ける。

このヒューズゲート電源電圧FGVD1は、電源電圧VDDおよび外部ヒューズゲート電源電圧FGVDDの一方を溶断イネーブル信号CUTENに従って選択する電圧選択回路9から与えられる。溶断イネーブル信号CUTENはk、ヒューズ素子FSの溶断時に活性化される。

ヒューズプログラム回路FPK1−FPKn各々においては、また、プログラムスキャンフリップフロップ(FF)PSRとFS選択スキャンフリップフロップ(FF)FSSRが設けられ、これらのフリップフロップPSRおよびFSSRにより、ヒューズ素子FSの溶断/非溶断を規定するプログラム情報の転送および設定が行なわれる。

AND回路AG1は、対応のFS選択スキャンフリップフロップFSSRの出力信号と対応のプログラムスキャンフリップフロップPSRの出力信号とヒューズカットクロック信号FCCLKとを受ける。

FS選択スキャンフリップフロップFSSRは、前段のヒューズプログラム回路のFS選択スキャンフリップフロップFSSRの出力データを、ヒューズ選択スキャンクロック信号SESCLKに従って取込み次段へ転送する。プログラムスキャンフリップフロップPSRは、入力部に配置されたマルチプレクサ(MUX)SX1を介して与えられるデータを、プログラムスキャンクロック信号PSCLKに従って取込み、次段へ転送する。したがって、FS選択スキャンフリップフロップFSSRは、ヒューズ選択スキャンクロック信号SESCLKに従ってシフト動作を行なってデータを転送するスキャンパスを構成し、また、プログラムスキャンフリップフロップPSRも、プログラムスキャンクロック信号PSCLKに従って順次シフト動作を行なってデータを転送するスキャンパスを構成する。

これらのフリップフロップFSSRおよびPSRの組を、各ヒューズ回路(ヒューズ素子FSと溶断電流供給トランジスタCTrで構成される)に対応して設けることにより、ヒューズ回路のヒューズ素子FSのプログラミング(溶断/非溶断処理)を、選択的にかつ逐次的に1つのヒューズ素子単位で実行することができる。また、少ないパッドを用いて、ヒューズ素子のプログラム情報を各ヒューズ素子に対して転送することができる。

ヒューズプログラム回路FPK2−FPKnの各々は、さらに、ノードND1の電圧レベルに従ってヒューズ素子FSの切断状態を判定する切断判定回路CJCと、プログラムスキャンフリップフロップPSRの出力信号と切断判定回路CJCの出力信号の一方を選択して出力するマルチプレクサSX2を含む。マルチプレクサSX2の出力信号は、また、対応の同じヒューズプログラム回路内に設けられるマルチプレクサSX1へ与えられる。このマルチプレクサSX1は、前段のプログラムスキャンフリップフロップPSRの出力信号と対応のマルチプレクサSX2の出力信号の一方を、スキャン選択信号SCSELに従って選択する。ここで、「切断」と「溶断」とを同じ意味で用いる。

1つのヒューズプログラム回路において2つのマルチプレクサSX1およびSX2を用い、そのデータ転送経路を切換えることにより、以下の効果を得ることができる。マルチプレクサSX1によりマルチプレクサSX2の出力信号を選択してプログラムスキャンフリップフロップPSRへ伝達する。マルチプレクサSX2は、テスト動作時、プログラムフリップフロップ選択信号PRFFSELに従って切断判定回路CJCの出力信号を選択する。この接続態様により、切断判定回路CJCの出力信号は、順次プログラムスキャンフリップフロップPSRを介して転送され、対応のヒューズ素子FSの状態をシリアル出力SOUTとして外部へ読出すことができる。これにより、外部でヒューズ素子FSの切断不良の有無を判定することができる。

また、マルチプレクサSX2において、プログラムスキャンフリップフロップPSRの出力信号を選択し、マルチプレクサSX1においてスキャン選択信号SCSELに従ってマルチプレクサSX2の出力信号を選択する。この接続態様において、ヒューズプログラム回路FPK1−FPKn各々において、プログラムスキャンフリップフロップPSRの保持データをフィードバックしてループ状に転送することができる。したがって、プログラムスキャンクロック信号PSCLKを自走状態に設定することができ(各ヒューズプログラム回路FPK1−FPKnのフリップフロップPSRの保持データが維持され)、クロック信号の制御および設計の自由度が高くなる(タイミング関係の制御が簡略化され、またタイミング関係の自由度が高くなる)。

また、マルチプレクサSX2から、ヒューズ素子FSの溶断/非溶断に応じたプログラム情報FOS1−FOSnが出力される。マルチプレクサSX2の出力信号をマルチプレクサSX1で選択して対応のプログラムスキャンフリップフロップPSRに格納する。この後、マルチプレクサSX1を前段のフリップフロップPSRの出力信号を選択する状態に設定して、プログラムスキャンフリップフロップPSRの列を介して順次格納データを転送する。この転送データを外部のテスタまたはBIST(ビルトインセルフテスト回路)で書込情報と比較する。これにより、マルチプレクサSX2が正常にプログラムフリップフロップ選択信号PRFFSELに従って切換動作を行なっているかをテストすることができる。

初段のヒューズプログラム回路FPK1は、以下の点を除いて、2段以降のヒューズプログラム回路FPK2−FPKnと構成が同じである。すなわち、FSスキャンフリップフロップFSSRおよびプログラムスキャンフリップフロップPSRへは、前段のヒューズプログラム回路の出力信号に代えて、外部のテスタまたは同一チップ上に形成されるBIST(ビルトイン・セルフ・テスト回路)からの切断制御情報CTSCINおよびヒューズプログラム用のスキャン入力SCINがそれぞれ与えられる。

このヒューズプログラム回路FPK1−FPKnの出力信号FOS1−FOSnがヒューズ情報利用回路3の対応の内部状態を設定する回路へ与えられる。

ヒューズ情報利用回路3は、前述のように、メモリ回路における冗長セル置換を行なうための冗長デコーダであってもよく、またアナログ回路の定数を決定する、すなわちアナログ回路の抵抗素子の抵抗値のトリミングまたはトランジスタ素子の駆動電流量の調整または基準電圧レベルの調整)を行なう回路のいずれであってもよい。したがって、ヒューズ情報利用回路3は、これらのヒューズプログラム回路FPK1−FPKnのプログラム情報に従って動作態様または動作状態が設定されればよく、配線溶断プログラム回路において記憶される情報は、内部回路(コア回路)2の内部状態に関連する情報であればよい。

FF選択スキャンフリップフロップFSSRの記憶データに従って、各ヒューズプログラム回路において対応のヒューズ素子FSの切断サイクルが規定される。ヒューズプログラム回路FPK1−FPKnにおいて、順次、プログラムスキャンフリップフロップPSRの格納データおよびヒューズカットクロック信号FCCLKに従って選択的に溶断電流が供給され、書込情報に応じてヒューズ素子FSが選択的に溶断される。

ヒューズ素子FSは、本実施の形態1においては、内部回路(コア回路)に対する電源ノードからの電源電圧VDDが供給される。この構成の場合、ヒューズプログラム回路FPK1−FPKnに対して設けられるヒューズ溶断のための専用のパッドの数を低減することができる。

ヒューズプログラム回路FPK1−FPKnおよび図2においては示されない制御回路のトランジスタとしては、図1に示す内部回路(コア回路)2において用いられるトランジスタと同一構造(ゲート絶縁膜の膜厚および材質が同じ)を用いる。これにより、配線溶断プログラム回路4の占有面積の増大および製造工程の増加を抑制する。

通常、ヒューズ素子FSの溶断のために必要とされる電流(溶断電流)は、20mAから40mAと比較的大きい。しかしながら、後に説明するように、ヒューズプログラム回路FPK1−FPKnにおいては、順次、FS選択スキャンフリップフロップFSSRの記憶情報に従って順次選択的にヒューズ素子のプログラム(溶断)が実行されるため、その消費電流は小さく、電源を、内部回路(コア回路)の電源と共有することができ、パッド数を低減することができる。

ANDゲートAG1に対し、ヒューズゲート電源電圧FGVD1が動作電源電圧として与えられる。ヒューズ溶断時には、ヒューズゲート電源電圧FGVD1として、外部からのヒューズゲート電源電圧FGVDDが選択される。この場合に、単に溶断電流供給トランジスタCTrのゲートを駆動することが要求されるだけであり、AND回路AG1の消費電流は、交流電流(AC電流)を含めてもわずかである。したがって、ヒューズ素子FSが数多く設けられる場合においても、1つのヒューズゲート電源電圧FGVDD供給用のパッド(図1のノード6)を設けることが要求されるだけであり、配線溶断プログラム回路4のレイアウト面積を低減することができる。

また、マルチプレクサSX2を用いてプログラムスキャンフリップフロップPSRの格納データと切断判定回路CJCの出力信号の一方を選択して出力する。したがって、ヒューズ素子FSの切断前に、冗長デコーダなどの対象回路(ヒューズ情報利用回路3)の状態をプログラム情報に従って設定してテストを行なうことができる。たとえばメモリ回路などにおいて、ヒューズ情報利用回路の対象回路が冗長デコーダの場合、外部から順次、冗長アドレスを印加して冗長セル行/列を選択し、冗長デコーダおよび冗長セルが正常であるかのテストを行なうことができる。これにより、不良発生時、ヒューズ素子の切断不良と冗長セル系の不良とを分離することができる。

図2に示す各ヒューズプログラム回路FPK1−FPKnに含まれるスキャンフリップフロップPSRおよびFSSRの構成としては、二相のクロック信号に従ってホールド状態およびスルー状態を繰返す2段のラッチ回路が用いられればよく、その構成としては、任意の構成を利用することができる。

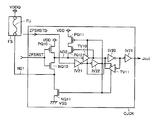

図3は、図2に示すAND回路AG1の構成の一例を示す図である。図3において、AND回路AG1は、内部回路(コア回路)2の電源電圧VDDを動作電源電圧として受ける3入力NANDゲート10と、3入力NANDゲート10の出力信号の振幅を、内部ヒューズゲート電源電圧FGVD1レベルに変換するレベル変換器12と、レベル変換器12の出力信号を反転するインバータ14を含む。このインバータ14の出力信号が、図2に示す溶断電流供給トランジスタCTrのゲートへ与えられ、インバータ14の出力信号に従って溶断電流供給トランジスタCTrのゲート電圧が制御される。

このAND回路AG1において、NANDゲート10に対し、プログラムスキャンフリップフロップPSRと、FS選択スキャンフリップフロップFSSRの出力信号と、ヒューズカットクロック信号FCCLKとが与えられる。これらの信号の振幅は、内部回路(コア回路)の電源電圧VDDのレベルである。NANDゲート10は、これらの与えられた信号に従って電源電圧振幅の信号を生成し、すべての入力信号がHレベルのときにLレベルの信号を出力する。

レベル変換器12およびインバータ14は、電源ノード6aに、内部ヒューズゲート電源電圧FGVD1を動作電源電圧として受け、NANDゲート10の出力信号の振幅を、内部ヒューズゲート電源電圧FGVD1レベルに変換する。

レベル変換器12は、交差結合されるPチャネルMOSトランジスタと、これらのPチャネルMOSトランジスタそれぞれと接地ノードの間にそれぞれ接続され、NANDゲート10の出力信号およびその反転信号を受けるNチャネルMOSトランジスタを含む。NANDゲート10の出力信号がHレベルのとき、レベル変換器12においてインバータ14への出力信号がHレベルとなり、応じて、ヒューズゲート電源電圧FGVD1レベルの信号がインバータ14から出力される。一方、NANDゲート10の出力信号がLレベルのとき、レベル変換器12においてインバータ14への出力信号がLレベルとなり、インバータ14の出力信号が、ヒューズゲート電源電圧FGVD1レベルとなる。

インバータ14は、このレベル変換器12の出力信号を反転し、NANDゲート10の出力信号と反対の論理値の信号を出力する。従って、フリップフロップFSSRおよびPSRからのデータとヒューズカットクロック信号FCCLKが全てHレベルの時に、インバータ14の出力信号がHレベルとなり、溶断電流供給トランジスタCTrがオン状態となり、対応のヒューズ素子が溶断される。

このレベル変換器12およびインバータ14のヒューズゲート電源ノード6aは、図1に示すヒューズゲート電源ノード6にヒューズゲート電源線宅回路9を介して結合される。ヒューズ溶断時には、外部からのヒューズゲート電源電圧FGVDDが選択されて内部ヒューズゲート電源線に伝達される。したがって、ヒューズゲート電源ノード6からの電圧FGVDDの電圧レベルを調整することにより、図2に示す溶断電流供給トランジスタCTrのゲート電圧を調整することができる。応じて、ヒューズ素子FSの溶断電流を調整することができ、ヒューズ素子FSのプログラム時の溶断電流を最適化することができる。

このヒューズ選択スキャンフリップフロップFSSRからの信号がHレベルとなると、対応のヒューズプログラム回路が選択されたことが示される。プログラムスキャンフリップフロップFSRからの信号のHレベル/Lレベルにより、対応のヒューズ素子の溶断/非溶断が設定される。すなわち、プログラムスキャンフリップフロップPSRからの信号がHレベルのときには、対応のヒューズ素子を切断することが指定される。

ヒューズカットクロック信号FCCLKは、所定のパルス幅で与えられる。したがってこのヒューズカットクロック信号FCCLKのパルス幅および印加回数を調整することにより、ヒューズ素子溶断に必要な電流パルス幅および電流パルス印加回数を実現することができる。

電源電圧VDDの投入時においては、内部ヒューズゲート電源電圧FGVD1としてヒューズゲート電源電圧FGVDDが選択される。内部回路電源電圧VDDが安定化すると、たとえばパワーオンリセット信号に従ってリセット信号RSTがワンショットパルスの形態で生成される。このリセット信号RSTが活性化されると、ヒューズプログラム回路FPK1−FPKnのプログラムスキャンフリップフロップPSRおよびFS選択スキャンフリップフロップFSSRの内部ノードがLレベルに設定される。これらの出力信号CTS(1)−CTS(n)およびSC(1)−SC(n)がすべてLレベルに固定される。応じて、AND回路AG1からの出力信号が、Lレベルに初期設定される。この状態においては、溶断電流供給トランジスタCTrが、確実に非導通状態に設定され、電源投入時に非切断状態のヒューズ素子FSを介して貫通電流が流れるのを防止することができる。

また、内部回路電源電圧VDD投入時、ヒューズゲート電源電圧FGVDDは、溶断電流供給トランジスタCTrのしきい値電圧Vthよりも低い電圧レベルに維持される。これは、以下の効果を得るために行なわれる。すなわち、電源投入時においてヒューズゲート電源電圧FGVDDが、溶断電流供給トランジスタCTrのしきい値電圧Vthよりも高い電圧レベルとなると、不安定な状態でAND回路AG1の出力信号がHレベルとなり、溶断電流供給トランジスタCTrが導通する可能性がある。非切断状態のヒューズ素子においては溶断電流供給トランジスタCTrのゲート電圧を、このしきい値電圧Vthよりも低い電圧レベルに設定することにより、非切断状態のヒューズ素子および溶断電流供給トランジスタを介して大きな貫通電流が流れるのを防止する。

また、レベル変換器12において、不安定なNANDゲート10の出力信号に従って内部ノードの電圧レベルが中間電圧レベルとなる場合がある。この場合、ヒューズゲート電源電圧FGVDDを、溶断電流供給トランジスタCTrのしきい値電圧Vthよりも低い電圧レベルに維持することにより、インバータ14の出力信号を、溶断電流供給トランジスタCTrのしきい値電圧Vthよりも低い電圧レベルに維持することができる。これにより、溶断電流供給トランジスタCTrが導通するのを防止することができる。

したがって、電源投入時、リセット信号RSTが活性化されるまで、ヒューズゲート電源電圧FGVDDは、溶断電流供給トランジスタCTrのしきい値電圧Vthよりも低い電圧レベル(例えば接地電圧レベル)に設定して、電源ノードから接地ノードへ大きな電流が流れる状態が生じるのを防止する。

ヒューズゲート電源電圧FGVDDおよび内部回路電源電圧VDDは、先の図1に示すように、半導体装置(半導体集積回路装置)外部から与えられる。したがって、外部の電源制御部において、この電源電圧VDDの供給開始時のパワーオンリセット信号を用いてリセット信号RSTを生成し、配線溶断プログラム回路4の内部を初期設定した後に、ヒューズゲート電源電圧FGVDDを供給する(その電圧レベルを上昇させる)。この電源制御は、プロセッサなどのシーケンスコントローラにより、この電源供給シーケンスが制御されればよい。

図4は、図2に示す切断判定回路CJCの構成の一例を示す図である。図4において、切断判定回路CJCは、ノードND1を電源ノードとして、動作し、ヒューズ素子リセット信号FSRSTを反転するインバータを構成するPチャネルMOSトランジスタPQ1およびNチャネルMOSトランジスタNQ1と、ノードND2と接地ノードの間に直列に接続されるNチャネルMOSトランジスタNQ2およびNQ3と、電源ノードVDDとノードND1の間に接続されるPチャネルMOSトランジスタPQ2を含む。

ノードND1は、ヒューズ素子FSの一端に接続され、ヒューズ素子FSの他方端は、電源電圧VDDを供給する電源ノードに結合される。ここで、ノードとその電圧を同一参照符号で示す。この切断判定回路CJCは、ヒューズ素子リセットディレー信号FSRSTDを受ける2段の縦続接続されるインバータIV10およびIV11と、ノードND2上の信号を活性化時反転するトライステートインバータTV1と、トライステートインバータTV1の出力信号を受ける2段の縦続接続されるインバータIV12およびIV13と、インバータIV12と反平行に接続されるトライステートインバータTV2を含む。

トライステートインバータTV1は、インバータIV10およびIV11の出力信号がそれぞれLレベルおよびHレベルのときに活性化され、ノードND2上の信号を反転する。トライステートインバータTV2は、トライステートインバータTV1と相補的に活性化され、活性化時、インバータIV12の出力信号を反転してインバータIV12の入力に伝達する。すなわち、トライステートインバータTV2は、活性化時、インバータIV12とラッチ回路を構成する。

NチャネルMOSトランジスタNQ2は、トライステートインバータTV1の出力信号をゲートに受け、MOSトランジスタNQ3が、インバータIV11の出力信号をゲートに受ける。PチャネルMOSトランジスタPQ2は、そのゲートに、インバータIV11の出力信号を受ける。インバータIV13から、切断判定回路CJCからの切断判定結果指示信号Joutが出力される。

図5は、図4に示す切断判定回路CJCの動作を示す信号波形図である。以下、図5を参照して、図4に示す切断判定回路CJCの動作について説明する。

ヒューズ素子リセット信号FSRSTおよびヒューズ素子リセットディレー信号FSRSTDがともにLレベルのとき、ノードND2が、ノードND1にMOSトランジスタPQ1を介して電気的に結合される。一方、インバータIV10の出力信号がHレベルであり、また、インバータIV11の出力信号がLレベルである。なお、ここで、電源電圧VDDは安定状態にあるとする。

応じて、MOSトランジスタPQ2が導通状態にあり、ノードND1が電源ノードに電気的に結合される。一方、MOSトランジスタNQ3は非導通状態であり、ノードND2は接地ノードから分離される。したがって、ノードND2もMOSトランジスタPQ1を介して電源電圧VDDレベルに充電される。インバータIV10の出力信号はHレベルであり、トライステートインバータTV1は、出力ハイインピーダンス状態にあり、判定結果出力信号Joutの状態は変化しない。

ヒューズ素子リセット信号FSRSTがHレベルに設定されると、MOSトランジスタPQ1が非導通状態となり、一方、MOSトランジスタNQ1が導通状態となり、ノードND2が接地電圧レベルに駆動される。この状態において、MOSトランジスタPQ1が非導通状態であるため、ノードND1およびND2は、互いに電気的に分離される。

ヒューズ素子リセットディレー信号FSRSTDがヒューズ素子リセット信号FSRSTと同時またはそれより遅れてHレベルに立上がり、インバータIV10およびIV11の出力信号は、それぞれ、LレベルおよびHレベルに駆動される。応じて、MOSトランジスタPQ2が非導通状態となり、一方、MOSトランジスタNQ3が導通状態となる。また、トライステートインバータTV1が活性化され、ノードND2上の接地電圧レベルに従ってその出力信号がHレベルとなり、MOSトランジスタNQ2が導通状態となる。これにより、トライステートインバータTV1およびMOSトランジスタNQ2,NQ3によりラッチ回路が構成され、ノードND2が接地電圧レベルに維持される。

以上の処理により、内部ノードND2の初期設定が行なわれ、また、判定結果出力信号JoutがHレベルとなる。

初期設定完了後、ヒューズ素子リセット信号FSRSTがLレベルに駆動される。このとき、まだ、ヒューズ素子リセットディレー信号FSRSTDはHレベルである。この状態においては、MOSトランジスタNQ1が非導通状態、MOSトランジスタPQ1が導通状態となり、ノードND1およびND2が電気的に結合される。ヒューズ素子FSが非溶断状態のときには、その電流駆動力は、MOSトランジスタNQ2およびNQ3の電流駆動力よりも大きく、ノードND2の電圧レベルが上昇し、応じてトライステートインバータTV1の出力信号がLレベルとなり、応じてMOSトランジスタNQ2が非導通状態となり、ノードND2が電源電圧VDDレベルに駆動される。

一方、ヒューズ素子FSが切断状態のときには、ノードND1がMOSトランジスタPQ1、NQ2およびNQ3を介して放電され、その電圧レベルが接地電圧レベルに維持され、トライステートインバータTV1およびMOSトランジスタNQ2、NQ3により、ノードND2はLレベルに維持され、応じて、判定結果信号JoutもHレベルに維持される。

次に、ヒューズ素子リセットディレー信号FSRSTDがLレベルとなると、インバータIV10およびIV11の出力信号がそれぞれ、HレベルおよびLレベルとなり、トライステートインバータTV1が出力ハイインピーダンス状態となり、また、MOSトランジスタPQ2が導通状態、MOSトランジスタNQ3が非導通状態となる。応じて、ノードND1およびND2が、再びMOSトランジスタPQ2およびPQ1により、電源電圧VDDレベルにプリチャージされる。このときには、トライステートインバータTV1が出力ハイインピーダンス状態であり、ノードND2とインバータIV12およびIV13とは分離され、判定結果出力信号Joutは、その直前の状態に維持される。すなわち、ヒューズ素子FSが切断状態のときにはHレベル、ヒューズ素子FSが非切断状態のときにはLレベルに維持される。

これにより、初期設定後、ヒューズプログラム回路におけるヒューズ素子FSのプログラム状態に応じて、切断判定回路CJCからの出力信号Joutをプログラム情報(ヒューズ素子の状態)に応じた論理レベルに設定することができる。

テストモード時においては、リセット信号FSRSTおよびFSRSTDに従って内部ノードの初期設定を行なった後、ヒューズ素子リセットディレー信号FSRSTDをHレベルに維持し、リセット信号FSRSTのみをLレベルに駆動する。この状態においては、ノードND1およびND2は、ヒューズ素子FSの切断/非切断状態に応じてそれぞれLレベルまたはHレベルに維持される。同様、判定結果出力信号Joutも、トライステートインバータTV1が活性状態にあるため、ヒューズ素子FSの切断/非切断状態に応じた論理レベルに設定される。

このテスト動作時において、ヒューズ素子FSが非切断状態野場合には、ノードND1は、ヒューズ素子FSにより電源電圧VDDレベルに維持される。この場合、ノードND2も、同様、電源電圧VDDレベルに維持されるものの、MOSトランジスタNQ3が、ヒューズ素子リセットディレー信号FSRSTDに従って非導通状態であり、ヒューズ素子FSを介して電源ノードから接地ノードへ至る電流経路は遮断される。したがって、非切断状態のヒューズ素子FSには、バイアス電圧VDDによるストレスの印加は行なわれない。

一方、ヒューズ素子FSが切断状態の場合には、ノードND1は、MOSトランジスタPQ1、NQ2およびNQ3がすべて導通状態となるため、接地電圧レベルとなる。したがって、ヒューズ素子FSが切断状態の場合、ヒューズ素子FSの両端にバイアス電圧が印加され、ヒューズ素子の切断後の破片(FS片)または高抵抗状態のヒューズ配線に対しバイアス電圧が印加される。この印加電圧に従ってエレクトロマイグレーション現象により銅(Cu)原子が移動する。この結果、高抵抗状態のヒューズ素子が低抵抗状態に移行する。

図6は、この切断状態のヒューズ素子の状態を模式的に示す図である。図6において、ヒューズ素子電源ノード5a(電源ノード5に結合される)とノードND1の間に、電圧VDDのストレスが印加される。ヒューズ素子FSが、銅配線の場合、切断破片(FS片)または高抵抗状態の配線中の銅原子が、その電圧印加に従って絶縁膜中を移動する。この絶縁膜中を移動する銅原子により、絶縁膜の絶縁破壊が生じ、配線間短絡などにより、ヒューズプログラム回路が不良となる。また、高抵抗状態にあり、切断状態と判定されるヒューズ素子の抵抗値が低下し、プログラム状態の反転が生じる可能性がある。

したがって、この電圧ストレスを印加することにより、ヒューズ素子FSとして、銅配線を用いた場合の寿命を測定することができる。また、非切断状態のヒューズ素子には電圧ストレスは印加されず、また電流が流れる経路は存在しない。したがって、電圧ストレス印加時においては、このヒューズ素子FSの切断/非切断にかかわらず、電流が流れる経路を遮断して切断状態のヒューズ素子の寿命を測定することができる。

なお、ヒューズ素子リセットディレー信号FSRSTDについては、ノードND1およびND2がヒューズ素子FSの切断/非切断に応じてその電圧レベルが設定される期間が確保されるようにその立下がりタイミングが設定されればよく、その立下りタイミングはヒューズ素子リセット信号FSRSTと同一タイミングであってもよく、またそれよりも遅れてもよい。

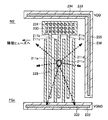

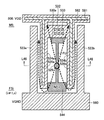

図7は、このヒューズプログラム回路のヒューズ素子下部のトランジスタ配置領域の構造を概略的に示す図である。ヒューズ素子は、後に詳細に説明するように、多層配線構造のうちの上層のメタル配線(Mi)を用いて形成される。したがって、ヒューズ素子下部には、空き領域が形成され、この空き領域において、ヒューズ回路のトランジスタを配置するとともに、他の関連の回路のトランジスタを配置する。

図7において、ヒューズプログラム回路のヒューズ素子下部の領域において、基板領域20の表面に、Nウェル21、Pウェル22およびNウェル23が間をおいて形成される。Nウェル23には、さらに、その表面にPウェル24が形成される。Nウェル21および23には、PチャネルMOSトランジスタ(PMOS)が形成され、Pウェル22および24には、NチャネルMOSトランジスタ(NMOS)が形成される。

これらのNウェル23およびPウェル24がP型基板領域20表面に形成されるトリプルウェル構造の領域において、溶断電流供給トランジスタCTrおよびレベル変換器(インバータバッファを含む)が形成される。Nウェル21およびPウェル22には、対応のヒューズプログラム回路におけるフリップフロップ(FF;PSR,FSSR)等の構成要素およびマルチプレクサなどの回路が形成される。Nウェル21に電源電圧VDDが基板バイアス電圧として印加され、また、Pウェル22には、接地電圧GNDが基板バイアス電圧として印加される。Nウェル23に対しては、内部ヒューズゲート電源電圧FGVD1が基板バイアス電圧として印加され、Pウェル24は、後に説明する仮想接地線VGNDに結合される。P型半導体基板領域20は接地ノードに結合される。

ヒューズゲート電源電圧FGVDDは、電源電圧VDDと別のパッド(電源ノード)から与えられる。このヒューズゲート電源電圧FGVDDは、溶断電流供給トランジスタCTrの駆動する電流を調整するため、その電圧レベルが、電源電圧VDDよりも高い電圧レベルまたは低い電圧レベルに設定される。したがって、これらのNウェル23およびPウェル24を、基板領域20上の他のウェル21および22と分離して設けることにより、ヒューズゲート電源電圧FGVDDの電圧レベルを、他の電源電圧VDDを受ける回路に対して影響を及ぼすことなく調整することができる。

仮想接地線VGNDは、後に詳細に説明するが、各ヒューズプログラム回路のヒューズ回路に含まれる溶断電流供給トランジスタCTrおよびレベルコンバータ(変換器)の接地線として利用される。Pウェル24を仮想接地線VGNDに結合することにより、ヒューズ溶断時に流れる溶断電流により基板ノイズが他の回路領域へ伝搬するのを防止して、回路誤動作を防止する。また、仮想接地線VGNDを利用することにより、ヒューズゲート電源電圧VGVDDの電圧レベルを、電源電圧VDDの電圧レベルと別個に最適値に設定することができる。

この図7に示すトリプルウェル構造は、各ヒューズプログラム回路に共通に配置され、その表面に形成される素子分離領域により、各ヒューズプログラム回路ごとに電気的に分離して設けられる。

図8は、溶断電流駆動トランジスタCTrを駆動する部分に関連する電源系統の構成を示す図である。図8において、ヒューズプログラム回路FPK1−FPKnが設けられる。これらのヒューズプログラム回路FPK1−FPKnは、同一構成を有するため、図8においては、ヒューズプログラム回路FPK1の構成を代表的に示す。

ヒューズ素子FSは、ヒューズFUを含み、このヒューズFUの下部に、ヒューズ回路ブロック40が配置される。このヒューズ回路ブロック40は、レベル変換部12aと、レベル変換部12aの出力信号を反転するインバータバッファ14と、このインバータバッファ14の出力信号に従って選択的に導通する溶断電流供給トランジスタCTrを含む。このヒューズ回路ブロック40の配置領域が、図7に示すNウェル23およびPウェル24の領域に対応し、回路ブロック40の各構成要素のトランジスタがNウェル23およびPウェル24に形成される。

レベル変換部12aは、インバータ12bとともに、先に図3に示すレベル変換器12を構成する。このインバータ12bは、電源電圧VDDを動作電源電圧として受けており、ヒューズFUの下部には配置されない。ヒューズFUの下部に配置される回路ブロック40においては、内部ヒューズゲート電源電圧FGVD1を受けるトランジスタが配置される。

ヒューズプログラム回路FPK1−FPKnに共通に、ヒューズゲート電源線30と、仮想接地線(VGND)32とが設けられる。ヒューズゲート電源線30は、ヒューズ回路ブロック40のPチャネルMOSトランジスタ(符号Pで示す)のソースおよび基板領域に結合される。仮想接地線32は、ヒューズ回路ブロック40のNチャネルMOSトランジスタ(符号Nで示す)のソースおよび基板領域に結合される。仮想接地線32の電位変化に対してバックゲートバイアス効果が生じるのを防止し、また、基板領域と不純物領域の間のPN接合が導通するのを防止する。これにより、仮想接地線32の電圧変化に対し、このヒューズ回路ブロック40の構成要素を安定に動作させる。

ヒューズゲート電源線30に対し、ヒューズゲート電源選択回路9として、切断イネーブル信号CUTENに従って選択的に導通し、導通時、電源電圧VDDをヒューズゲート電源線30に伝達するPチャネルMOSトランジスタ44と、切断イネーブル信号CUTENがHレベルのとき導通し、ヒューズゲート電源ノード6(6a)をヒューズゲート電源線30に結合するCMOSトランスミッションゲート42が設けられる。

CMOSトランスミッションゲート42は、PチャネルMOSトランジスタ42aおよびNチャネルMOSトランジスタ42bを含む。PチャネルMOSトランジスタ42aの基板領域はヒューズゲート電源線30に結合される。このCMOSトランスミッションゲート42において、ヒューズゲート電源電圧FGVDDが、電源電圧VDD以上に昇圧される場合においても、このPチャネルMOSトランジスタ42aのバックゲート(基板領域)−ソース/ドレイン間の接合が導通するのを防止することができ、確実に、電源電圧VDD以上に昇圧されたヒューズゲート電源電圧FGVDDをヒューズゲート電源線30に伝達することができる。

また、ヒューズゲート電源電圧FGVDDが接地電圧レベルであり、ヒューズゲート電源線30がMOSトランジスタ44により電源電圧VDDレベルに設定される場合でも、PチャネルMOSトランジスタ42aのバックゲートは、N型基板領域(21)であり、そのバックゲート(基板領域)−ドレイン間は逆バイアス状態であり、安定にヒューズゲート電源線30は、電源電圧VDDレベルに維持される。

仮想接地線32に対しては、PチャネルMOSトランジスタ45と、NチャネルMOSトランジスタ46a、46bおよび47とが設けられる。PチャネルMOSトランジスタ45は、切断イネーブル信号CUTENがLレベルのとき導通し、仮想接地線32へ電源電圧VDDを伝達する。NチャネルMOSトランジスタ46aおよび46bはそのゲートに電源ノード6aを介してヒューズゲート電源電圧FGVDDをゲートに受け、抵抗素子として機能する。これらのMOSトランジスタ46aおよび46bは、内部回路のトランジスタと同一の構成(ゲート絶縁膜膜厚、ゲート絶縁膜材料およびゲート幅素子長さが同じ)を有するコアトランジスタで構成され、比較的大きな電流駆動力を有する。

NチャネルMOSトランジスタ47は、切断イネーブル信号CUTENがHレベルのとき導通し、仮想接地線32を接地ノードに結合する。このMOSトランジスタ47は、その電流駆動力は比較的小さくされ、通常動作モード時、仮想接地線32上の電位の浮き上がりを防止するために利用される。

ヒューズプログラム回路FPK1における他のフリップフロップおよび切断判定回路等の構成は図2に示す構成と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

これらのヒューズゲート電源線30およびヒューズ仮想接地線32は、一例として多層配線層の第2メタル配線層M2の配線を用いて構成される。ヒューズ素子FSに含まれるヒューズFUは、一例として、ヒューズゲート電源線30およびヒューズ仮想接地線32が形成される第2メタル配線層よりも2層以上上層の配線層の配線を用いて形成される。この配線構造により、ヒューズプログラム回路FPK1−FPKnに共通にヒューズゲート電源線30および仮想接地線32を配置しても、何らヒューズ素子FSの配置には影響は及ぼさない。

図9は、図8に示すヒューズプログラム回路におけるヒューズ素子切断時の内部ヒューズゲート電源電圧FGVD1および仮想接地線電圧VGNDの変化シーケンスを示す図である。以下、図9を参照して、ヒューズ切断時のヒューズゲート電源線30および仮想接地線32上の電圧印加シーケンスについて説明する。

ヒューズ切断前においては、リセット信号FSRSTDおよびFSRSTはともにLレベルである。この場合、図4に示すように、ノードND1がMOSトランジスタPQ2により電源電圧VDDレベルに充電されている。また、切断イネーブル信号CUTENがLレベルであるため、MOSトランジスタ44がオン状態、CMOSトランスミッションゲート42がオフ状態であり、ヒューズゲート電源線30上の電圧FGVD1は、電源電圧VDDレベルである。

ヒューズゲート電源電圧FGVDDは、Lレベルであり、MOSトランジスタ46aおよび46bはともに非導通状態であり、仮想接地線32は、MOSトランジスタ45により電源電圧VDDレベルに維持される。この状態においては、回路ブロック40内において、その両側の電源線30および接地線32がともに電源電圧VDDレベルであり、インバータ14の出力信号GDは、電源電圧VDDレベルである。同様、ヒューズ回路ブロック40における内部配線(第1および第2メタル配線)もすべて電源電圧VDDレベルであり、すなわちヒューズFUの両端それぞれの電圧レベルに等しい電圧レベルに維持される。この条件により、ヒューズ溶断時に生成された配線片(銅原子)の移動を防止する。

ヒューズ切断時、まず、ヒューズ素子リセットディレー信号FSRSTDおよびヒューズ素子リセット信号FSRSTがHレベルとなり、また、切断イネーブル信号CUTENがHレベルとなる。リセット信号RSTは、接地電圧GNDのLレベルに維持される。また、ヒューズゲート電源電圧FGVDDは、接地電圧レベルに維持される。

切断イネーブル信号CUTENに従って、CMOSトランスミッションゲート42が導通し、PチャネルMOSトランジスタ44がオフ状態となり、ヒューズゲート電源線30上の電圧FGVD1が接地電圧レベルに低下する。一方、仮想接地線32は、MOSトランジスタ45、46aおよび46bがすべてオフ状態(非導通状態)となる。一方、MOSトランジスタ47が導通状態(オン状態)となり、この仮想接地線32を小さな電流駆動力で接地電圧レベルに駆動される。

MOSトランジスタ47の電流駆動力は、回路ブロック40内に形成されるトランジスタの電流駆動力よりも十分小さく、仮想接地線32上の電圧VGNDが、接地電圧レベルに低下しても、回路ブロック40内の電源電圧レベルにプリチャージされていた内部配線の電荷の移動によりインバータバッファ14の出力信号GDは、最悪中間電位レベルに変化する(インバータ12bの出力信号は電源電圧VDDレベルまたは接地電圧レベルのいずれか)。この状態において、溶断電流供給トランジスタCTrのゲート電位は中間電位レベルであっても、そのゲート−ソース間電圧は、溶断電流供給トランジスタCTrのしきい値電圧よりも低い電圧レベルである。従って、溶断電流供給トランジスタCTrは、最悪弱い導通状態となるだけであり、ヒューズ回路ブロック40においてリーク電流はほとんど流れない。

また、図4に示すように、切断判定回路CJCにおいては、MOSトランジスタPQ1およびPQ2はオフ状態であり、この切断判定回路CJCからノードND1への電流供給が停止される。

次いで、ヒューズ切断時においてヒューズ電源ノード6aへ供給されるヒューズゲート電源電圧FGVDDが切断電圧レベルに立上げられる。このヒューズゲート電源電圧FGVDDの立上がりに応答して、CMOSトランスミッションゲート42を介してヒューズゲート電源線30上の電圧FGVD1が、ヒューズゲート電源電圧FGVDDのレベルとなる。一方、このヒューズゲート電源電圧FGVDDの電圧レベルが上昇すると、MOSトランジスタ46aおよび46bがオン状態となり、仮想接地線32上の電圧VGNDを大きな電流駆動力により接地GNDレベルに維持する。

非選択ヒューズプログラム回路においては、NANDゲート10の出力信号に従って、最悪中間電圧レベルにあったインバータ14の出力信号GDが、接地電圧GNDレベルに維持される。選択ヒューズプログラム回路においては、NANDゲート10の出力信号に従ってインバータの出力信号GDがヒューズゲート電源電圧FGVDDレベルとなり、溶断電流供給トランジスタCTrが導通し、ヒューズFUに電流が流れ、ヒューズFUの切断が行なわれる。このヒューズゲート電源電圧FGVDDの電圧レベルを調整することにより、溶断電流供給トランジスタCTrを介して流れるヒューズ溶断電流の大きさを調整することができる。

このヒューズ溶断時に大きな電流が流れても、仮想接地線32は、MOSトランジスタ46aおよび46bにより確実に接地電圧レベルに維持され、所望の大きさの溶断電流を、切断対象のヒューズに供給することができる。また、ヒューズ溶断時においては、図4に示す切断判定回路CJCにおいては、MOSトランジスタPQ1およびPQ2がともに非導通状態であり、このヒューズ溶断に対しては何ら影響を及ぼさない。

ヒューズ切断期間が完了すると、ヒューズゲート電源電圧FGVDDが再び接地電圧レベルに駆動され、応じてヒューズゲート電源線30上の電圧FGVD1が接地電圧レベルに低下する。また、仮想接地線32においては、MOSトランジスタ46aおよび46bがオフ状態(非導通状態)となるものの、まだ、切断イネーブル信号CUTENがHレベルであり、MOSトランジスタ47により、高抵抗で接地電圧レベルに維持される。このヒューズゲート電源線30上の電圧FGVD1のレベル低下により、選択ヒューズプログラム回路においては、回路ブロック40内の内部ノードの電圧レベルが電荷の移動により中間電圧レベルとなるかまたは接地電圧レベルに低下する。図8においては、最悪ケースを想定して、選択ヒューズプログラム回路においてインバータバッファ14の出力信号GDが中間電圧レベルに維持される場合を示す。この場合においても、仮想接地線32の電圧VGNDは、接地電圧GNDレベルであり、溶断電流供給トランジスタCTrは、非導通状態を維持し、ヒューズ切断不良時においても、十分にリーク電流を抑制することができる。

非選択ヒューズプログラム回路においては、インバータ14の出力信号GDは接地電圧レベルを維持する。したがって、溶断電流供給トランジスタCTrは、選択/非選択ヒューズプログラムいずれにおいても非導通状態に設定され、ヒューズ電源ノードから仮想接地線へのリーク電流経路は十分に遮断される。

選択ヒューズプログラム回路においてヒューズの切断が完了すると、信号FSRSTD、FSRSTおよびCUTENがLレベルに立下がる。応じて、CMOSトランスミッションゲート42が非導通状態となり、また、PチャネルMOSトランジスタ44がオン状態となり、ヒューズゲート電源線30上の電圧FGVD1が電源電圧VDDレベルに維持される。また、仮想接地線32は、PチャネルMOSトランジスタ45により電源電圧VDDレベルとなる(MOSトランジスタ46a、46bおよび47が、非導通状態)。

したがって、ヒューズ切断時において、実際にヒューズ切断が行なわれるときの動作以外においては、この回路ブロック40内のメタル配線はヒューズFUの両端の電圧レベルと同じであり、切断ヒューズの破片の銅原子の配線への移動を抑制することができる。また、PチャネルMOSトランジスタ44および45を用いて、切断イネーブル信号CUTENに従ってそれらの導通を制御することにより、ヒューズゲート電源線30および仮想接地線32の電圧レベルを、ヒューズ切断動作に応じて容易に変更することができる。

なお、切断イネーブル信号CUTENがHレベルのときに、ヒューズカットクロック信号FCCLKに従ってヒューズFUの切断が行なわれる。非選択ヒューズプログラム回路においては、NANDゲート10の出力信号は、ヒューズカットクロック信号FCCLKの状態に関わらずHレベルである。したがって、切断イネーブル信号CUTENのHレベルの期間により、ヒューズを切断する期間が規定される。

図10は、ヒューズ切断後の判定時の動作を示す信号波形図である。以下、図10および図4を参照して、図8に示すヒューズゲート電源線30および仮想接地線32の電圧変化について説明する。

ヒューズの切断判定前においては、切断イネーブル信号CUTENはLレベルであり、またリセット信号RST、ヒューズ素子リセット信号FSRSTおよびヒューズ素子リセットディレー信号FSRSTDもLレベルである。したがって、ヒューズゲート電源線30上の電圧FGVD1および仮想接地線32上の電圧VGNDは、ともに電源電圧VDDレベルである。従って、インバータバッファ14の出力信号GDは、電源電圧VDDレベルであり、溶断電流供給トランジスタCTrは、ゲートおよびソースおよびドレインが同一電圧レベルにあり、非導通状態にある(ノードND1が、図4に示すMOSトランジスタPQ2により電源電圧レベルに維持される。

次いで、切断イネーブル信号CUTENがHレベルに駆動され、また、リセット信号RSTおよびFSRSTはHレベルに駆動される。応じて、CMOSトランスミッションゲート42が導通し、ヒューズゲート電源線30上の電圧FGVD1がヒューズゲート電源電圧FGVDDと同じ接地電圧GNDレベルに維持される。また、リセット信号RSTにより、ヒューズプログラム回路FPK1−FPKnにおけるフリップフロップPSRおよFSRの出力信号がLレベルとなり、NANDゲート10の出力信号が、全てHレベルとなる。応じて、レベル変換器12aの出力信号が、内部配線の電荷の移動により中間電圧レベルとなり、応じてインバータ14の出力信号GDも中間電圧レベルとなり、最悪ケースにおいて溶断電流供給トランジスタCTrが非導通状態となる(トランジスタCTrのゲートーソース間電圧は、しきい値電圧よりも低い)。

仮想接地線32については、MOSトランジスタ45、46aおよび46bがオフ状態であるものの、MOSトランジスタ47がオン状態である。したがって、非切断状態のヒューズまたは切断判定回路CJCからの初期設定時のMOSトランジスタ(PQ2)からの供給電流により仮想接地線32に供給される電荷は、回路ブロック40を介してヒューズゲート電源線30へ分流され、仮想接地線32の電圧レベルが低下するとともに、MOSトランジスタ47により、この仮想接地線32が接地電圧GNDレベルに維持される。またヒューズゲート電源線30は、接地電圧レベルにヒューズゲート電源電圧FGVDDに従って維持される。

インバータ14の出力信号GDと仮想接地線32の電圧VGNDの差が溶断電流供給トランジスタCTrのしきい値電圧レベル以下となると、溶断電流供給トランジスタCTrは非導通状態となり、リーク電流が低減される。応じて、仮想接地線32の電圧レベルは、MOSトランジスタ47より確実に、接地電圧レベルに維持される。

また、仮想接地線32に対して設けられるMOSトランジスタ46aおよび46bは、それぞれのゲート電圧が接地電圧レベルであり、これらのトランジスタ46aおよび46bを介した仮想接地線32から接地ノードへのリーク電流は十分に抑制される。

次いで、ヒューズリセットディレー信号FSRSTDがHレベルに駆動される。、その後リセット信号RSTおよびFSRSTがLレベルに駆動される。このとき、これらのプログラムスキャンフリップフロップPSRにおいてマルチプレクサSX2を介してリセット前のプログラム情報が再格納されてもよい。ヒューズ素子の切断判定時においは、単に、切断判定回路CJCにおいて判定動作が行なわれるだけであり、スキャンフリップフロップPSRおよびFSRの格納情報は、判定動作に影響を及ぼさない。したがって、これらのスキャンフリップフロップPSRおよびFSRがリセット状態を維持していても特に問題は生じない。

リセット信号RSTおよびFSRSTDのこの状態において、図4に示す切断判定回路CJCにおいてヒューズ素子FSの切断/非切断に応じて内部ノード(ND2)の電圧レベルが変化し、ヒューズの切断/非切断の判定が行なわれる。この判定期間において、仮想接地線32は接地電圧GNDレベルに維持されており、後に説明するような誤判定は生じない。また、仮想接地線32への溶断電流供給トランジスタCTrからの電流供給は停止される。

判定期間が完了すると、ヒューズ素子リセットディレー信号FSRSTDおよび切断イネーブル信号CUTENがLレベルに駆動される。応じて、ヒューズゲート電源線30がMOSトランジスタ44により電源電圧VDDレベルに駆動される。また、仮想接地線32も、MOSトランジスタ45により電源電圧VDDレベルに充電される。応じて、回路ブロック40内の内部ノード(第2メタル配線M2)の電圧レベルも電源電圧VDDレベルに復帰する。

したがって、実際にヒューズの切断が行なわれるとき以外は、ヒューズ回路ブロック40において内部ノード(第2メタル配線)の電圧レベルはヒューズFUの両端の電圧(電源電圧VDDレベル)に維持される。したがってヒューズ切断時以外は、ヒューズFUと第2メタル配線M2が同電位に維持される。ヒューズFUが切断状態であっても、銅(Cu)の破片部または飛散部の銅原子のヒューズ素子FSからの回路ブロック40内の第2メタル配線(M2)の拡散およびヒューズ素子切断破片等による絶縁破壊は、抑制される。

図11は、溶断電流供給トランジスタCTrの断面構造および溶断電流供給トランジスタCTrと切断判定回路CJCの接続態様を概略的に示す図である。この図11に示す切断判定回路CJCの構成は、図4に示す切断判定回路CJCの構成と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

回路ブロック40において、P型半導体基板20表面に、Nウェル23が形成され、このNウェル23表面にPウェル24が形成される。このPウェル24表面に、電流切断トランジスタCTrが形成される。この溶断電流供給トランジスタCTrは、Pウェル24表面に形成される高濃度N型不純物領域50および52と、これらの不純物領域50および52の間の領域上にゲート絶縁膜を介して形成されるゲート電極54とを含む。不純物領域50は、仮想接地線32を介してMOSトランジスタ47に結合される。一方、不純物領域52は、溶断電流供給トランジスタCTrのドレイン領域を構成し、ノードND1およびヒューズ素子FSに接続される。Pウェル24は、仮想接地線32に結合され、ヒューズプログラム回路FPK1−FPKnに含まれる溶断電流供給トランジスタCTrに対し共通に設けられる(溶断電流供給トランジスタごとに、素子分離膜が形成される)。

この構成において、不純物領域52に×印55に示すように接合不良が存在する状態を考える。この場合、ヒューズ素子FSのヒューズFUが非切断状態の場合、ヒューズ素子FSを介してヒューズ電源ノードから不純物領域52を介して電荷がPウェル24に供給される。しかしながら、この場合、切断イネーブル信号CUTENがHレベルのとき、仮想接地線32がMOSトランジスタ47を介して接地ノードに結合されており、接合不良55によりヒューズ電源ノードから供給される電荷は、接地ノードへ放電される。したがって仮想接地線32上の電圧VGNDは、切断イネーブル信号CUTENがHレベル期間において、たとえ接合不良55が存在する場合においても接地電圧GNDレベルに維持される。なおヒューズ素子FSにおいてヒューズFUが切断状態にあり、その抵抗がたとえばMΩオーダーの高抵抗状態とすると、ノードND1は、ほぼ電源ノードから分離され、この切断判定回路CJCの判定ノードND2に対しては、N型不純物領域52とそのPN接合が電気的に接続される状態と言える。ヒューズ素子リセット信号FSRSTをHレベルとした場合、切断判定回路CJCにおいて、PチャネルMOSトランジスタPQ1はオフ状態、MOSトランジスタNQ1がオン状態となり、内部ノードND2は、ノードND1と電気的に分離され、接地電圧レベルのLレベルに低下される。

図10に示すようにヒューズ素子リセットディレー信号FSRSTDがHレベルとなると、トライステートインバータTV1が活性化され、ノードND2の信号電位が反転され、Hレベルとなる。その後、ヒューズ素子リセット信号FSRSTがLレベルとなると、切断判定回路CJCのMOSトランジスタPQ1がオン状態、MOSトランジスタNQ1がオフ状態となる。この状態においては、切断判定回路CJCの内部ノードND2は、ノードND1と電気的に接続され、ノードND1を介してさらにN型不純物領域52へ結合される。しかしながら、この場合、Pウェル24は、仮想接地線32からMOSトランジスタ47を介して接地ノードに結合されており、Pウェル24は接地電圧GNDレベルである。したがって、切断判定回路CJCの内部ノードND2が、トライステートインバータTV1の入力しきい値を超えるレベルにまで充電されることはなく、正確に、切断判定期間においてヒューズ切断状態を示すHレベルの信号がトライステートインバータTV1から出力される。この後、ヒューズ素子リセットディレー信号FSRSTDがLレベルに立下がると、トライステートインバータTV1が出力ハイインピーダンス状態となり、その判定結果信号JoutがHレベルに維持される。

一方、ヒューズFUが非切断状態の低抵抗状態の場合には、ノードND1は、電源電圧VDDレベルとなる。たとえPN接合不良55が存在しても、MOSトランジスタ47の電流駆動力よりもヒューズFUの電流供給力は高く、ノードND1は、電源電圧レベルに維持される。また、溶断電流供給トランジスタCTrは、非導通状態であり、PN接合不良55からのリーク電流は小さく、仮想接地線32の電圧VDNDは判定期間中においてもほぼ接地電圧レベルに維持される。

この場合、切断判定回路CJCにおいては、ノードND2が判定期間中にHレベルにMOSトランジスタPQ1を介して充電され、トライステートインバータTV1の出力信号がLレベルとなる。したがって、ヒューズFUの非切断時には、その判定結果信号JoutはLレベルとなり、正確に、ヒューズ素子FSの切断/非切断の状態に応じた判定結果を出力することができ、正確に切断判定を行なうことができる。

Pウェル24には、複数のヒューズプログラム回路SPK1−SPKnの溶断電流供給トランジスタが共通に設けられる(図示しない素子分離領域は形成される)。これらのヒューズプログラム回路SPK1−SPKnにおいては、ヒューズ素子FSは、切断状態または非切断状態であり、切断状態のヒューズ素子および非切断状態のヒューズ素子が混在する。このような場合においても、切断状態判定時、MOSトランジスタ47をオン状態に設定して、Pウェル24をほぼ接地電圧GNDレベルに維持することにより、正確に、各ヒューズ素子FSの状態を識別することができる。

なお、図8において、仮想接地線32に対し、MOSトランジスタ46aおよび46bが直列に接続されている。しかしながら、この場合、1つのMOSトランジスタが配置され、そのゲートにヒューズゲート電源電圧FDVDDが与えられてもよい。

以上のように、この発明の実施の形態1に従えば、複数のヒューズプログラム回路に共通に設けられる仮想接地線に対し、切断動作時接地電圧レベルに維持するトランジスタを配置しており、切断判定時正確にヒューズ素子の切断/非切断を判定することができる。

また、仮想接地線を接地電圧レベルに維持するMOSトランジスタ(47、46aおよび46b)は、通常動作時には、オフ状態に設定され(ヒューズゲート電源電圧FGVDDは、通常動作モード時には設置電圧レベルに維持される)、仮想接地線は電源電圧VDDレベルに維持される。これにより、ヒューズ素子FSの両端に印加される電圧と同一電圧レベルに、ヒューズ下部に配置されるヒューズ回路ブロック40の配線の電圧レベルを維持することができ、銅原子のマイグレーションによる銅配線の不良を防止することができる。

[実施の形態2]

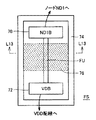

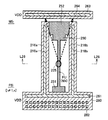

図12は、この発明の実施の形態2に従うヒューズ素子FSの構成を概略的に示す図である。図12において、ヒューズ素子FSは、ヒューズFUを含み、ヒューズFUは、銅(Cu)配線で形成され、第3メタル配線層以上の上層のメタル配線を用いて実現される。本実施の形態2においては、このヒューズ素子FUが第4メタル配線層の配線を用いて形成される。

ヒューズFUは、幅の広い配線ベッド領域VDBを介して図示しない電源線に結合され、またノードベッド領域ND1Bを介してノードND1を実現する配線領域に結合される。ヒューズFU、ベッド領域VDBおよびND1Bを囲むように銅拡散防護壁構造74が配置される。この銅拡散防護壁構造74の構成については後に詳細に説明するが、ヒューズFU上層にヒューズFUの少なくとも溶断部を蔽うように形成される上部拡散防護壁配線76を含む。上部拡散防護壁配線76として、本実施の形態2においては、電源電圧VDDを伝達する電源配線を用い、この電源配線として、第5メタル配線層(M5)の配線を利用する。

このヒューズFUの直上部の配線層においては、配線およびビアは配置されない。銅配線で形成するヒューズFUの溶断時、銅切片が熱拡散により移動するのを、この防護壁構造74により防止し、配線短絡およびヒューズ素子の切断不良が生じるのを抑制する。

ヒューズFU下部に、ヒューズFUを切断するためのトランジスタを配置するトランジスタ配置領域が設けられ、先の図8に示すヒューズ回路ブロック40の各トランジスタが配置される。図12に示すヒューズ素子FSが、ヒューズプログラム回路(FPK)それぞれに対応して並列に整列して配置される。

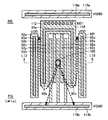

図13は、図12に示すヒューズ素子FSの線L13−L13に沿った断面構造を概略的に示す図である。図13において、P型ウェル(Pウェル)80表面に、間をおいてN型活性領域(不純物領域)84a−84dが互いに間をおいて形成される。このPウェル80下部にディープNウェル82が形成され、Pウェル80が、他の回路形成領域と分離される。Pウェル80は、ヒューズプログラム回路に対して共通に配置される。このPウェル80およびディープNウェル82は、図7に示すP型ウェル領域24に対応する。

不純物領域84a−84dの間のPウェル80表面上に、たとえばポリシリコンで形成されるゲート電極配線86a、86b、…86cが配置される。これらのゲート電極配線86a−86cおよび活性領域(不純物領域)84a−84dにより、ヒューズプログラム回路のヒューズ回路ブロック40(図8参照)に含まれるNチャネルMOSトランジスタ(溶断電流供給トランジスタ)が形成される。すなわち、溶断電流供給トランジスタCTrは、複数の並列に配置される単位MOSトランジスタで構成され、これらの単位MOSトランジスタが、図示の活性領域およびゲート電極配線により形成される。

不純物領域84a−84dは、それぞれコンタクト91a−91dを介して第1メタル配線層M1の配線90a−90dにそれぞれ結合される。第1メタル配線90bおよび90cは、第1ビア93cおよび93dを介して第2メタル配線層M2の配線92cおよび92dに結合される。この第2メタル配線92cおよび92dは、それぞれ仮想接地線に結合され、仮想接地電圧VCNDを受ける。

第1メタル配線90aは、第1ビア93bを介して第2メタル配線92bに結合され、第1メタル配線90dは、第1ビア93eを介し手代2メタル配線92eに結合される。

第2メタル配線層M2において、さらに、第2メタル配線92bおよび92e外部に、第2メタル配線92aおよび92fが配置される。これらの第2メタル配線92aおよび92fは、後に説明するように、電源電圧VDDを伝達する。

第3メタル配線層M3において、第3メタル配線94a、94b、94cおよび94dが互いに間をおいて配置され、それぞれ第2ビア95a、95b、95cおよび95dを介して第2メタル配線92a、92b、92eおよび92fにそれぞれ電気的に接続される。第2メタル配線92cおよび92d上部には、第3メタル配線は配置されない。

第4メタル配線層M4において、第4メタル配線98a、98b、98cおよび98d互いに間をおいて配置され、それぞれ、第3ビア97a、97b、97cおよび97dを介して第3メタル配線94a、94b、94cおよび94dに電気的に接続される。この第4メタル配線M4において、第4メタル配線を用いて形成されるヒューズFUが配置される。このヒューズFU直下部において第3メタル配線層M3においては配線が配置されず、また、第2メタル配線層M2における第2メタル配線92cおよび92dとヒューズFUとは整列しない位置に配置される。

第5メタル配線層M5において、第5メタル配線100a、100b、100cおよび100dが互いに間をおいて配置され、それぞれ第4ビア99a、99b、99cおよび99dを介して第4メタル配線98a、98b、98cおよび98dに電気的に接続される。

第5メタル配線100bおよび100cが、図12に示すノードベッド領域ND1Bに結合され、ノードND1に結合される。

一方、第5メタル配線100a、および100dは、第6ビア101aおよび101bを介して第6配線層M6の第6メタル配線102に結合される。この第6メタル配線102へは、電源電圧VDDが伝達される。この第6メタル配線102は、ヒューズ素子FUの上部にヒューズを蔽うように配置される。したがって、ヒューズFUの直上部および直下部においては、少なくとも2層の配線層の隙間が確保される。ヒューズFUのトリミング領域105は、その溶断電流によるジュール熱により溶断される領域であり、このトリミング領域105から、溶断時の銅原子が熱拡散により移動する。このヒューズトリミング領域周辺にダメージ予想領域107が存在する。このダメージ予想領域107は、ジュール熱によりヒューズが溶断される場合、銅の融点(1000℃以上)にまで温度が上昇し、その内に銅が拡散すると予想される領域である。現実には、熱による絶縁膜の品質劣化が生じることが予想される領域であり、銅原子のマイグレーションによる絶縁不良は生じないと予想される領域である。

銅拡散防護壁構造により、このダメージ予想領域107内において、銅原子の熱拡散による配線短絡(絶縁不良)およびヒューズFUの切断不良が発生するのを抑制する。

このヒューズFUの周辺に配置されるビアおよび配線により、銅(Cu)拡散防止膜を形成し、図12に示す銅拡散防止構造74を実現する。この図12に示す上部拡散防護壁配線76が、図13に示す第6メタル配線102に対応する。この図13に示すように、第6メタル配線層の配線を用いてヒューズFUの上部銅拡散防止膜を形成することにより、ヒューズ素子形成に利用される配線層の数を低減でき、またノードND1を形成する配線100bおよび100cを利用して、ヒューズ上部に防護膜を形成する構成に比べて占有面積を低減することができる。

また、図13に示すように、第5メタル配線100bおよび100c上部の空隙領域を越えた銅の熱拡散は、第5ビア101aおよび101bにより防止される。これにより隣接して配置されるヒューズ素子に対して銅が熱拡散するのを抑制することができる。また、防護壁は第6メタル配線から第2メタル配線までの中間メタル配線およびビアで構成されるプラグと基板領域から第5メタル配線層までの中間メタル配線およびビアとで構成されるプラグとで2重壁構造としており、確実に銅の熱拡散経路を遮断することができる。

なお、各メタル配線層のメタル配線間には、層間絶縁膜が配置され、この層間絶縁膜の配線層毎に銅(Cu)拡散を防止するSiCNなどで構成される銅拡散係数の小さな拡散防止膜が配置される。この銅拡散防止膜を配置することにより、ダメージ領域における銅拡散を抑制し、絶縁膜の劣化を抑制するとともに、絶縁膜中を銅原子が熱拡散するのを抑制する。特に、この銅拡散防止膜は、第2−第5メタル配線層M2−M5に配置されるものであり、電源電圧VDDが印加される配線とノードND1の電圧が印加される配線との間に配置される拡散防止膜は、隣接するヒューズFUが溶断されたことにより拡散した銅原子が拡散するのを防止するために重要となる。

図14は、図13に示すヒューズ素子の第2メタル配線層M2および第2ビアの平面レイアウトを概略的に示す図である。図14において、線L13−L13に沿った断面構造は、図13に示される断面構造となる。以下の図においても同様である。このヒューズ素子FSiは、複数のヒューズ素子が整列して配置されるヒューズボックス内の端部以外に配置されるヒューズ素子である。

図14において、第2メタル配線92aおよび92fは、ヒューズトリミング領域105に関して対向して縦長形状に形成される。これらの第2メタル配線92aおよび92f表面には、同様、縦長形状の第2ビア95aおよび95dが配置される。この縦長形状の第2ビア92aおよび95dは、通常の単位コンタクト形成時のように小単位面積で互いに分離されるのではなく、直線的に連続的に形成される溝形状のビアである。この連続的に延在する溝形状のビアを形成することにより、破線矢印で示す銅(Cu)の拡散経路を遮断する。

第2メタル配線92bおよび92eは、第2メタルベッド配線110に結合される。この第2メタルベッド配線110に対し、また、第2メタル配線92yおよび92zが接続される。これらの第2メタル配線92b、92y、92zおよび92eの間に第2メタル配線92c、92xおよび92dが配置される。第2メタル配線92x−92zは、図13に示す平面レイアウトにおいては、その図示が省略されているものの、溶断電流供給トランジスタ(CTr)の単位トランジスタの数に応じて、これらの第2メタル配線92x−92zが配置される。

第2メタル配線92c、92xおよび92dは、横方向に連続的に延在して配置される第2メタル配線114bに結合される。この第2メタル配線114bは、仮想接地SENに結合され、、仮想接地電圧VGNDを伝達する。この第2メタル配線114b表面に、連続的に延在する溝形状第2ビア116bが形成され、ヒューズボックス外部に対する銅拡散経路が遮断される。

ノードND1を構成するベッド配線110に対して最外部に配置される第2メタル配線92bおよび92e上に溝形状の第2ビア95bおよび95cが配置され、これらの第2ビア95bおよび95cが、第2メタルベッド配線110上において溝形状の第2ビア95xに相互接続される。したがって、U字型の溝形状の第2ビア95b、95cおよび95xにより、トリミング領域105を囲む防護壁が第2メタル配線層において形成される。

第2メタルベッド配線110に対しては、上層配線との電気的接続のために、単位面積を有する第2ビア112が複数個互いに間をおいて配置される。

この第2メタル配線110外部に横方向に連続的に延在する第1メタル配線114aが配置され、その表面に溝形状の第2ビア116aが配置される。この第2メタル配線114aは、仮想接地線に結合され、仮想接地電圧VGNDを伝達する。この第2メタル配線114aおよび溝形状第2ビア116aにより、ベッド配線110を超えて拡散する銅原子の拡散経路を遮断する。

図15は、ヒューズボックス内のヒューズ素子列の端に配置されるヒューズFSnの平面レイアウトを概略的に示す図である。図15に示すヒューズ素子FSnの平面レイアウトは、以下の点において図14に示すヒューズ素子FSiの平面レイアウトと異なる。すなわち、端部のヒューズ素子FSnに対しては、第2メタル配線114aおよび114aが、縦方向に延びる第2メタル配線118に相互接続される。また、溝形状第2ビア116aおよび116bが、だi2メタル配線118表面に形成される縦方向に延びる溝形状第2ビア119により相互接続される。この図15に示すヒューズ素子FSnの他の構成の平面レイアウトは図14に示すヒューズ素子FSiの平面レイアウトと同じであり、対応する部分には同一参照番号を付して、その詳細説明は省略する。

この端部のヒューズ素子FSnにおいては、溝形状の第2ビア119および第2メタル配線118によりその端部領域においてヒューズ素子列外部に、銅(Cu)が熱拡散により伝播するのを防止する。

この図14および図15に示すように、第2メタル配線層において、トリミング領域105からの銅(Cu)の熱拡散経路(図14および図15において破線矢印で示す)の経路は遮断される。この場合、第2メタル配線92aおよび92bの間および第2メタル配線92eおよび92fの間の熱拡散経路は、第2メタル配線92c、92dおよび92x−92zにより確実に遮断される。また、第2メタル配線114b外部に、ヒューズ回路(回路ブロック40)以外のトランジスタを配置しており、第2メタル配線114bおよび溝形状第2ビア116bにより確実に、破線矢印で示す銅の熱拡散経路が遮断され、他回路の配線に対し銅(Cu)を熱拡散するのを確実に防止することができる。

図16は、図14に示すヒューズ素子FSiの平面レイアウトの上層の平面レイアウトを概略的に示す図である。すなわち図16においては、ヒューズ素子FSiの第3メタル配線層M3の配線の配置を示す。この図16においても、線L13−L13に沿った断面構造としては、図13に示す断面構造が得られる。

図16において、第3メタル配線94aおよび94dが縦方向に長い形状に形成され、この第3メタル配線94aおよび94d上に溝形状第3ビア97aおよび97dがそれぞれ連続的に延在して形成される。この第3メタル配線94aおよび94dが、その下部に形成される第3メタル配線120に結合され、また第3ビア97aおよび97dも、この第3メタル配線120上に形成される溝形状の第3ビア121に電気的に接続される。この第3メタル配線120は、図15に示す第2メタル配線114aおよび114b配置領域より内部の位置に配置され、電源電圧VDDを伝達する。この第3メタル配線120は、図15に示す第2メタル配線92aおよび92fに溝形状第2ビアを介して電気的に接続される。

第3メタル配線94bおよび94cが、同様、第3メタル配線94aおよび94dと平行に縦方向に長い形状に形成され、また、これらの第3メタル配線94bおよび94c表面Iに対し、連続的に延在する溝形状第3ビア97b、97cが形成される。この第3メタル配線94bおよび94cは、第3メタルベッド配線122に電気的に接続され、また、溝形状第3ビア97bおよび97cも、第3メタルベッド配線122上に形成される溝形状第3ビア123により電気的に接続される。この第3メタル配線122においても、上層配線との電気接続を取るための単位第3ビアが互いに間をおいて配置される。

第3メタルベッド配線122は、図14に示す第2ビア112を介して第2メタルベッド配線110に電気的に接続される。

ヒューズ素子の上部および下部領域に、第3メタル配線124aおよび124bが横方向に連続的に延在して形成され、それぞれ、図14に示す第3メタル配線114aおよび114bに、第2ビア116aおよび116bを介して電気的に接続される。第3メタル配線124aおよび124bは、仮想接地線を構成し、仮想接地電圧VGNDを伝達する。この第3メタル配線124aおよび124b表面には溝形状ビアは形成されない。この第3メタル配線124aおよび124bが、グローバル仮想接地線(32)として配置され、低抵抗で仮想接地電圧VGNDを伝達する。

図17は、ヒューズ素子列の端部のヒューズ素子FSnの第3メタル配線層のレイアウトを概略的に示す図である。図17に示す端部のヒューズ素子FSnの平面レイアウトは、図16に示すヒューズ素子FSi(i≠1、n)の平面レイアウトと以下の点でその配置が異なる。すなわち、ヒューズ素子列の下部領域および上部領域において横方向に連続的に延在する第3メタル配線124aおよび124bが、縦方向に延びる第3メタル配線125により電気的に接続される。第3メタル配線120は、その終端部120aにおいて配線レイアウトが終端される。この図17に示すヒューズ素子FSnの他の要素の平面レイアウトは図16に示すヒューズ素子FSiの平面レイアウトと同じであり、対応する部分には、同一参照番号を付して、その詳細説明は省略する。

図16および図17に示すように、第3メタル配線層M3においても、ヒューズ素子トリミング領域105からの銅(Cu)の熱拡散経路は、破線矢印で示すように、第3メタル配線94aおよび94bの間の領域および第3メタル配線94cおよび94dの間の隙間領域に存在する。しかしながら、この経路においては、銅の熱拡散経路長以上の間の距離にヒューズに対して十分長い距離が確保されており、この拡散経路による銅(Cu)の隣接ヒューズ素子に対する熱拡散の影響は、十分に抑制することができる。

また、端部のヒューズ素子FSnにおいて第3メタル配線125を配置することにより、ヒューズ素子列(ヒューズボックス)外部に配置される回路に対する銅の熱拡散は、抑制され、外部回路に対する悪影響は確実に回避される。

また、先に説明したように、図16および図17の第3メタル配線124b下側領域の外部に配置される他回路のトランジスタ形成領域に対する銅(Cu)の熱拡散は確実に抑制される。

また、端部のヒューズ素子FSnは、図17に示すように、第2メタル配線120aが、第2メタル配線94dの端部より突出しないように配置される。これにより、第2メタル配線125および120aが電気的に短絡されるのを防止する。

図18は、図16に示すヒューズ素子の上層の第4メタル配線層M4の配線レイアウトを示す図である。図18において、線L13−L13に沿った断面構造は、図13に示す第4メタル配線層および第4ビアおよび下層の断面構造が得られる。

図18において、ヒューズ素子FSiの第4メタル配線層M4において、第4メタル配線98aおよび98dが縦方向に延在して配置され、これらの第4メタル配線98aおよび98d上に、溝形状第4ビア99aおよび99dが直線的に連続的に延在して形成される。この第4メタル配線98aおよび98dに対し、横方向に連続的に延在する第4メタル配線132が設けられ、この第4メタルベッド配線132に対し、溝形状第4ビア138が形成される。第4メタル配線132に、第4メタル配線98aおよび98dが結合され、また第4ビア133に、第4ビア99aおよび99dが結合される。この第4メタル配線132表面に上層配線との電気的接続を取るための、単位第4ビア134が互いに間をおいて複数個整列して配置される。

第4メタル配線132は、電源電圧VDDを伝達し、図16に示す下層の第3メタル配線120に溝形状第3ビアを介して電気的に接続される。

これらの第4メタル配線98aおよび98dの内部に、直線的に延在して第4メタル配線98bおよび98cが配置される。これらの第4メタル98bおよび98c上に、溝形状第4ビア99bおよび99cが配置される。

第4メタル配線98bおよび98cに対し、図16に示す第3メタルベッド配線122に整列して、第4メタルベッド配線135が配置され、第3メタルベッド配線135表面に、溝形状第5ビア136が形成される。第4メタル配線98bおよび98cが、第4メタルベッド配線135に結合され、第4溝形状ビア136が、第4ビア99bおよび99cに結合される。

この第4メタル配線98bおよび98cの内側に、ヒューズFUを構成する第4メタル配線が配置され、このヒューズFUの両端に、第4メタルパッド配線130および131が配置される。第4メタルパッド配線130は、第4メタルベッド配線135に接続され、第4メタルパッド配線131が第4メタル配線132に結合される。これにより、ヒューズFUの両端が、それぞれノードND1および電源ノードに結合される。

図19は、このヒューズ素子列の端のヒューズFSnのレイアウトを概略的に示す図である。この図19においてヒューズ素子FSnにおいては、その端部に第4メタル配線140および溝形状第4ビア141が縦方向に長い矩形形状に形成される。第4メタル配線140は、第4メタル配線138および132に結合され、溝形状第4ビア141が、第4ビア139および133に接続される。したがって端部のヒューズ素子FSnにおいては、端部に第4メタル配線および第4ビアにより防護壁が形成される。この図19に示す配線レイアウトにおいて他の配置は図18に示すヒューズ素子の平面レイアウトと同じであり、図19において、図18に示すヒューズ素子FSiの構成要素と対応する部分には同一参照番号を付し、その詳細説明は省略する。

図18および図19に示すように、ヒューズFUを囲むように、第4メタル配線98a、98b、98cおよび98dが配置され、また溝形状第4ビア99a−99dが配置される。したがって、ヒューズFUのトリミング領域105において配線が溶断された場合、その銅(Cu)の熱拡散経路(破線矢印で示す)がごく一部に存在するだけであり、この破線で示す銅(Cu)の拡散経路長は、その銅の拡散長より十分長く、他配線に対する影響は、十分に抑制される。

なお、ベッド配線132および135それぞれに設けられる複数のビア134および137はそれぞれ、上層配線との電気的接続をとるためのビアである。防護壁としては、溝形状ビアが利用される。

図20は、図18に示すヒューズ素子の平面レイアウトの上層の第5メタル配線層M5の配線レイアウトを示す図である。図20において、線L13−L13に沿った打面構造は、図13に示す第5メタル配線層以下の下層の断面構造が得られる。図20において、第5メタル配線100aおよび100dが縦方向に長く配置され、これらの第5メタル配線100aおよび100d上に、溝形状第5ビア101aおよび101bが連続的に延在して形成される。これらの第5メタル配線100aおよび100bに対し、第5メタル配線140が横方向に連続的に延在して配置され、またこの第5メタル配線140上に溝形状第5ビア141が連続的に延在して配置される。第5メタル配線100aおよび100bが、第5メタル配線140に結合され、溝形状第5ビア101aおよび101bが溝形状第5ビア141に結合される。この第5メタル配線140においては、上層のメタル配線と電気的接続を取るための単位第5ビア142が複数個形成される。

この第5メタル配線100aおよび100bは、図18に示す第4メタル配線98aおよび98dに溝形状第4ビア99aおよび99dを介して電気的に接続される。また、第5メタル配線140は、図18に示す第4メタル配線132にビア133および134を介して電気的に接続される。

第5メタル配線100aおよび100dの内側に、第5メタル配線100bおよび100cがヒューズFUを囲むように直線的に縦方向に延在して配置される。これらの第5メタル配線100bおよび100cに対し第5メタルベッド配線143が配置される。この第5メタルベッド配線143は、図18に示す第4メタルベッド配線135とビア136および137を介して電気的に接続され、また、互いに整列して配置される。

図18に示す第4メタル配線138に整列して第5メタル配線144が形成され、この第5メタル配線144上に溝形状第5ビア145が形成される。第5メタル配線144は、図18に示す第4メタル配線138と溝形状第4ビア139を介して電気的に接続される。

図21は、ヒューズ素子列の端部のヒューズ素子FSnの第5メタル配線層の配線レイアウトを示す図であり、図19に示す配線レイアウトの上層の配線レイアウトを示す図である。図21に示す端部のヒューズ素子FSnの配線レイアウトは、以下の点で、図20に示すヒューズ素子FSiの配線レイアウトと異なる。すなわち、ヒューズ素子列端部のヒューズ素子FSnにおいてさらに、縦方向に長い第5メタル配線146および第5溝形状ビア147が形成される。第5メタル配線146が、それぞれ横方向に連続的に延在する第5メタル配線144および140に結合され、第5ビア147が溝形状第5ビア145および141に結合される。第5メタル配線層M5においても、端部のヒューズ素子FSnにおいては、、第5メタル配線144および140と溝形状第5ビアを、第5メタル配線146および溝形状第5ビア147により終端して、ヒューズボックスの拡散防護壁が形成される。図21に示す平面レイアウトの他の配置は図20に示す平面レイアウトの配置と同じであり、図21において、図20に示す要素と対応する部分には同一参照番号を付し、端部のヒューズ素子FSnの配線レイアウトの詳細説明は省略する。

図20および図21に示すように、ヒューズ素子FUのトリミング領域105においてヒューズFUが溶断され、銅の熱拡散経路が破線矢印に示すように存在する場合、トリミング領域105から直線的に銅原子が熱拡散する経路は遮断され、単に、第5メタル配線100aおよび100bの間および100dおよび100cの間を拡散する経路が存在するだけである。この場合においても、熱拡散経路までのヒューズトリミング領域105からの距離は長く、破線矢印で示す銅の拡散経路長は、銅の熱拡散距離よりも十分長く、隣接ヒューズ素子に対して銅が拡散するのを防止することができる。

図22は、ヒューズ素子FSの第6メタル配線層の配線レイアウトを概略的に示す図である。図22においては、第6メタル配線層M6については、端部のヒューズ素子FSnおよびそれ以外のヒューズ素子FSiについて同じ配線レイアウトであり、図22においては、ヒューズ素子FSとして示す。また、図22においては、ヒューズFUに関連する部分の配線レイアウトを合わせて示す。この図22においても、線L13−L13に沿った断面構造は図13に示す第6メタル配線層以下の断面構造に対応する。

図22において、ヒューズFU上部に、第6メタル配線160(102)が配置される。この第6メタル配線160は、図13に示す上部防護壁配線102に対応する。この第6メタル配線160(102)は、幅の太いべた配線で形成され、ヒューズFUのトリミング領域を覆うように形成される。第6メタル配線160(102)は、第5メタル配線100bおよび100c外側に形成される第6メタル配線150aおよび151aに第6メタル配線152に結合され、また、第6メタル配線150bおよび151bにより横方向に連続して形成される第6メタル配線153に接続される。これらの第6メタル配線152および153は電源電圧VDDを伝達する配線である。第6メタル配線150aおよび150bは、図20に示す第5メタル配線100aと整列して配置され、溝形状第5ビア101aを介してこの第6メタル配線150aおよび150bと第5メタル配線100aが電気的に結合される。第6メタル配線151aおよび151bは、図20に示す第5メタル配線100bと整列して配置され、溝形状第5ビア101bによりこれらの第6メタル配線151aおよび151bと第5メタル配線100aが電気的に結合される。

この図22に示す平面レイアウトにおいて、第6メタル配線(電源線)152および153は複数のヒューズ素子(FS0−FSn)に対し共通に連続的に延在して配置され、また第6メタル配線102も、普通のヒューズ素子に対し共通に配置される。

図20に示す平面レイアウトにおいて、ヒューズ素子FUの両端のベッド配線130および131の部分においては、隙間が形成される。しかしながら、ヒューズ素子トリミング領域(図22には示さず)が、第6メタル配線102により覆われている。ヒューズFUを溶断した場合、ヒューズFUと銅拡散防止膜と層間膜との接触部であるヒューズFUの角の部分の2箇所を起点とし、ヒューズFUの上側にヒューズから離れるようにクラックが発生し、第6メタル配線102にクラックが到達し、このクラック内に銅金属が入り込むことにより、ヒューズFUと第6メタル配線102とが短絡することがある。このとき、ヒューズFUの電位が第6メタル配線102上の電源電圧VDDとなるために、切断判定回路CJCによりトリミング不良の検出が可能となり、不良品としてこのようなクラックが発生したチップ(半導体装置)を製品出荷前に除去可能となる。逆に言うと、もしヒューズ素子トリミング領域が、第6メタル配線102に蔽われていないと、このクラックが発生して銅金属が入り込んだものを、不良検出ができずに、製品として出荷してしまうことになる。その場合、製品出荷されたチップが、その後、チップ動作(半導体装置としての実動作)に伴う電位バイアスまたは熱により経時変化し、クラックに入り込んだ銅金属がヒューズ素子周辺の回路に拡散し、チップに悪影響を与える。

さらに、本発明においては、ヒューズ素子トリミング領域直上において、ヒューズFUの上側に配置されていて最もヒューズFUに近いメタル配線は、第6メタル配線102であり、この第6メタル配線102には、電源電圧VDDが与えられている。それに対して、前述の特許文献1(特開2007−317882号公報)においては、ヒューズ素子トリミング領域直上において、ヒューズFUの上側に配置されていてヒューズに最も近いメタル配線は、ノードND1の電圧に対応する電圧が供給されている。従って、本発明のようにヒューズFUを溶断した場合、上側にクラックが発生し第6メタル配線102にクラックが到達し、このクラック内に銅金属が入り込み、ヒューズFUと第6メタル配線とが短絡した場合、以下のような問題が生じる。すなわち、ヒューズFUの電位が,第6メタル配線上の電圧のような電源電圧VDDとならないため、切断判定回路CJCによりトリミング不良を検出するのが困難となり、不良品としてこのようなチップを製品出荷前に検出除去するのが困難となる。なお、本発明においては、ヒューズFUの細身の直上において、ヒューズFUの上に配置されていてかつヒューズFUに最も近いメタル配線は、第6メタル配線102であり、この第6メタル配線102に電源電圧VDDが供給されるようなレイアウトとなる。

また、第6メタル配線層M6にも銅拡散防止膜が設けられていること、ヒューズ素子(FS0−FSn)のヒューズFUがそれぞれ、第6メタル配線152、151a、150b、151b、153により囲まれているため、図20に示す平面レイアウトに示される破線矢印に示すような直線的に進む経路を介しての第6メタル配線層M6の配線に対する銅拡散が、ヒューズ素子(FS0−FSn)外部の回路に到達するのは防止される。

さらに、ヒューズFU両端のベッド配線130および131の部分においては、隙間が形成されるため、十分に第6メタル配線102の面積を小さくすることができ、製造時のCMPによるディッシングの悪影響を防止することができる。

この図20に示す第6メタル配線(べた配線)160(102)の線幅が太い場合には、銅のCMP(ケミカル・メカニカル・ポリッシング)時に、ディシングという現象が生じ、銅の膜厚が薄くなる場合がある。従って、設計ルールで定められる配線幅に基づいて、ディシングが生じさせないで十分に配線抵抗が小さくなる配線幅を利用する。

[変更例]

図23は、ヒューズ素子FSの第6配線層M6の配線レイアウトの変更例を示す図である。この図23においては、ヒューズFUを覆う部分に、ベタ配線160に代えて、ストライプ状の複数の配線162が上部拡散防護壁配線102として形成される。このストライプ状第6メタル配線162は、それぞれ第6メタル配線150および151を介して両側に配置される第6メタル配線(電源線)152および153に電気的に結合される。

図23に示すヒューズ素子の他の配線レイアウトは図22に示すヒューズ素子FSの配線レイアウトと同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

図23に示すように、ヒューズFUのトリミング領域105の直上部においてストライプ状の配線162を配置しても、図20に示すベタ配線160と、ヒューズ直上部における銅の熱拡散を防止する効果は同じである。隣接ヒューズ素子への銅の熱拡散の防止は、図20および図21に示す溝形状ビア101a、101bとこの第6メタル配線150a、150b、151a、151bまたは150、151により防止している。このストライプ状第6メタル配線162の配線幅を、配線抵抗を小さくする線幅に形成されればよく、図22および図23に示すヒューズFU直上部の第6メタル配線(防護壁配線)の形状は、ディッシングが生じない配線幅でかつ配線抵抗が小さくなるパターンが利用されればよい。

このヒューズ素子においては、ヒューズFUの溶断時の銅の熱拡散を防護する最上層配線として第6メタル配線層の配線を利用している。したがって、第7メタル配線を利用する必要がなく、配線層の数を低減することができる。また、配線層数が低減されるため、防護壁を形成する部分のレイアウト面積を低減することができ、ヒューズ素子の占有面積を低減することができる。

また、図22に示すヒューズ素子の構造について上で説明したのと同様の効果を得ることができる。

[ヒューズ素子の変更例]

図24は、この発明の実施の形態2に従うヒューズ素子の変更例の断面構造を概略的に示す図である。この図24に示すヒューズ素子FSは、以下の点で、図13に示すヒューズ素子の構造とその構造が異なる。すなわち、第1メタル配線層M1の第1メタル配線90bおよび90cが、仮想接地線に結合され、仮想接地電圧VCNDを伝達する。この第1メタル配線90bおよび90c上には、図13に示す第2メタル配線92c、92dは配置されない。第3メタル配線層M3においてヒューズ素子FU(M3)が配置される。すなわち、ヒューズが第3メタル配線層の配線で形成される。この場合、第5メタル配線層M5において、電源電圧VDDを伝達する電源線170が、このヒューズ素子FUのトリミング領域105を覆うように配置される。第4メタル配線層M4において、第4メタル配線98bおよび98cがノードND1に結合される。平面レイアウトにおいては、したがって、ヒューズ素子外部に配置される仮想接地電圧VGNDを伝達するグローバル仮想接地線、および複数のヒューズ素子に共通に設けられて電源電圧VDDを伝達するグローバル電源線が配置される配線層が1つ下層に配置され、また図14に示す第2メタル配線92c、92dおよび92xが配置されない。

図24に示すヒューズ素子の断面構造の他の構成は、図13に示すヒューズ素子の断面構造と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

図24に示す構成においても、ヒューズ素子FU(M3)のトリミング領域105を中心としてダメージ領域107が存在するものの、このダメージ領域107は、銅(Cu)原子の拡散領域であり、銅溶断時の熱により層間絶縁膜が劣化する可能性がある領域である。しかしながら、図24に示す構成においても、ヒューズ素子FU(M3)直上および直下部において、少なくとも2層の配線層分の間隙があり、銅原子の熱拡散による配線短絡等は抑制される。また、上部の電源配線(第5メタル配線)170から、下方向に銅拡散防止膜が連続的に形成され、また基板領域から電源配線方向に向かって第4メタル配線により拡散防止膜が形成され、ヒューズ素子FU(M3)の溶断時の銅拡散を完全に防止する防護壁構造が実現される。また、この場合、第5メタル配線層までの配線が利用されるだけであり、使用される配線層の数を低減することができ、このヒューズ素子のレイアウト面積の低減とともに、最上層の第6メタル配線層を他の配線に利用することができ、配線の自由度が改善される。

ヒューズ素子トリミング領域が、第5メタル配線170により覆われている。ヒューズFUを溶断した場合、ヒューズFUと銅拡散防止膜と層間膜(層間絶縁膜)との接触部であるヒューズFUの角の部分の2箇所を起点として、ヒューズFUの上側にヒューズから離れるようにクラックが発生し、第5メタル配線170にクラックが到達し、このクラック内に銅金属が入り込み、ヒューズFUと第5メタル配線170とが短絡することがある。このとき、ヒューズFUの電位が、第5メタル配線170上の電源電圧VDDとなる。応じて、切断判定回路CJCにより、トリミング不良を検出することが可能となり、不良品として、このチップ(半導体装置)を製品出荷前に検出、除去可能となる。なお、本発明の実施の形態においては、ヒューズFUの細身の直上においてヒューズFUの上側に配置され、かつヒューズFUに最も近いメタル配線は、第5メタル配線170であり、電源電圧VDDが供給されるようなレイアウト構造となる。

図25は、図24に示すヒューズ素子のヒューズ溶断時の電源の接続態様を概略的に示す図である。第5メタル配線層M5に電源電圧VDDを伝達するグローバル電源線170glが配置され、第3メタル配線層M3に形成されるヒューズ素子FU(M3)の一端が、このグローバル電源線170glに中間配線およびビアを介して結合される。一方、このヒューズ素子FU(M3)の他端は、第4メタル配線層M4に形成されるノードベッド配線98ndを結合される。このノードベッド配線98ndは、図24に示す第4メタル配線98bおよび98cが結合されるノードパッド配線に結合される(図24には示さず)。このノードベッド配線98ndが、その下層の基板領域に形成されるドレイン不純物領域84drに結合される。基板領域表面においては、不純物領域84drと平行にソース不純物領域84srが配置される。これらの不純物領域84srおよび84drは、互いに平行に配置されるものの、図25においては、電流の流れる経路を明確にするために、互いに隣接して配置されるように示す。

このソース不純物領域84srは、溶断電流供給トランジスタCTrの単位トランジスタの不純物領域を対応し、ほぼ、図14に示す第2メタル配線92cに対応するように長い形状を有する。このソース不純物領域84srと平行に、第1メタル配線層M1にローカル接地配線90gnが配置される。このローカル接地配線90gnは、図24に示す第1メタル配線90b、90cに対応する。

このローカル接地配線90gnは、第2メタル配線層M2に形成されるグローバル仮想接地線175glに結合され、仮想接地電圧VGNDを受ける。ヒューズ溶断時においては、グローバル電源線170glからヒューズFU(M3)、ノードベッド配線98nd、ドレイン不純物領域84dr、ソース不純物領域84srおよびローカル接地配線90gnを介してグローバル仮想接地配線175glに電流が流れる。この第1メタル配線層M1のメタル配線は、第2メタル配線層M2のメタル配線に比べてその電気的特性が劣り(不純物濃度がストレス耐性を強くするため高くされる)、溶断電流が流れるときの銅エレクトロマイグレーション耐性については、第1メタル配線層M1のメタル配線90gnは、第2メタル配線層のメタル配線層よりも低い。したがって、このヒューズ素子溶断時において、溶断電流供給トランジスタCTrを介して大きな溶断電流が流れるため、このローカル接地配線90gnに大きな電流が流れ、エレクトロマイグレーションにより配線が切断される可能性がある。したがって、この図24に示す構造を利用する場合には、第1メタル配線層M1のローカル接地配線90gn(図24の第1メタル配線90bおよび90c)のエレクトロマイグレーション耐性を正確に評価し、その配線長を見積り、このグローバル仮想接地配線175glからヒューズFU(M3)までに至る電流経路が、第1メタル配線(90gn)でエレクトロマイグレーション耐性により切断される可能性がないことを保障する必要がある。

以上のように、この発明の実施の形態2に従えば、ヒューズの直上および直下に、少なくとも2層の配線層の間をおいて配線を配置するとともに、ヒューズの銅拡散防護壁構造を配置し、さらにヒューズ直上層の配線として電源電圧を伝達する配線を設置している。これにより、ヒューズ素子形成に要する配線層の数を低減することができ、応じて防護壁構造を実現するためのレイアウト面積が低減され、また、製造工程数を低減することができる。

また、防護壁構造としては、最上層の電源線から基板方向に向かって延びる第1の防護壁と基板から電源方向に流れる第2の防護壁とで構成し、この第1の防護壁内部に第2の防護壁構造を形成している。これにより、確実に、ヒューズ溶断時の銅(Cu)の熱拡散経路を遮断することができ、ヒューズ溶断による配線短絡等の影響を確実に防止することができ、正確にヒューズをプログラムすることのできるヒューズ素子を実現することができる。

[実施の形態3]

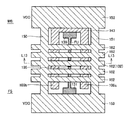

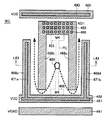

図26は、この発明の実施の形態3に従うヒューズ素子の断面構造を概略的に示す図である。図26において、Pウェル200下部にディープNウェル202が設けられる。このPウェル200およびディープNウェル202が、ヒューズボックス内のヒューズ素子に共通に配置される。ここで、ヒューズボックスは、ヒューズ素子が複数個整列して配置される領域を示す。

Pウェル200表面に互いに間をおいて活性領域(N型不純物領域)204a−204dが配置され、また、隣接ヒューズ素子領域において活性領域204xおよび204yが配置される。不純物領域204aおよび204dは、各々、隣接するヒューズプログラム回路に含まれるヒューズ素子に対する溶断電流供給トランジスタにより共有される。

不純物領域204a−204dの間のPウェル200表面上にゲート絶縁膜を介してゲート電極配線206a、206b、206cが配置される。また、隣接ヒューズ素子領域においても、不純物領域204xおよび204aの間の領域上にゲート電極配線206xが配置され、また、不純物領域204dおよび204yの間の領域上にゲート電極配線206yが配置される。

不純物領域204a−204dおよび204x、204y各々に対応して第1メタル配線層M1の第1メタル配線208a−208d、208xおよび208yが配置される。これらの第1メタル配線208A−208d、208xおよび208yは、それぞれコンタクト210a−210d、210xおよび210yを介して対応の不純物領域204a−204d、204xおよび204yにそれぞれ接続される。

第2メタル配線層M2において、これらの第1メタル配線208a−208d、208xおよび208y各々に対応して第2メタル配線211a−211d、211xおよび211yが配置される。第2メタル配線211a−211d、211xおよび211yは、それぞれ溝形状第1ビア212a−212b、212xおよび212yを介して下層の対応の第1メタル配線208a−208d、208xおよび208yに接続される。第2メタル配線211aおよび211bは、それぞれ仮想接地線に結合され、仮想接地電圧VGNDを伝達する。第2メタル配線211bおよび211cは、それぞれノードND1に接続される。

第3メタル配線層M3においては、第2メタル配線211aおよび211d各々に対応して、第3メタル配線213aおよび213bが配置される。第3メタル配線213aおよび213b下部にはビアは形成されず、第2メタル配線211aおよび211dと第3メタル配線213aおよび213bの間には隙間が存在する。

第4メタル配線層M4において、第3メタル配線213aおよび213bに対応して第4メタル配線214aおよび214bが配置され、それぞれ、溝形状第3ビア215aおよび215bを介して対応の第3メタル配線213aおよび213bに電気的に接続される。

この第4メタル配線層M4の配線を用いて、第4メタル配線214aおよび214bの間にヒューズFU(M4)が形成される。ヒューズFU(M4)と第4メタル配線214aおよび214bの間には十分の距離がとられる。

第5メタル配線層M5において、第4メタル配線214aおよび214bに対応して第5メタル配線216aおよび216bが配置され、それぞれ、溝形状第4ビア217aおよび217bを介して対応の第4メタル配線214aおよび214bに電気的に接続される。

第5メタル配線216aおよび216b各々に対応して溝形状第5ビア218aおよび218bが配置され、これらの第5ビア218aおよび218bは、第6メタル配線層M6の電源配線220に電気的に接続される。この第6メタル配線220で構成される電源線は、複数のヒューズ素子に対して共通に配置されるとともに、ヒューズトリミング領域225を蔽うように配置され、ヒューズに対する上部拡散防護壁配線として機能する。

この図26に示す構成において、ヒューズFU(M4)のトリミング領域225を中心として、ダメージ領域227が存在する。このダメージ領域227は、ヒューズFU(M4)を構成する銅(Cu)溶断時の銅の融点以上に加熱されるため、この影響による劣化が生じる可能性のある領域である。また、各メタル配線層の層間絶縁膜においては、銅拡散防止膜が配置される。

この図26に示す構成においても、第3メタル配線層から第6メタル配線層の配線を用いてヒューズFU(M4)の銅(Cu)に対する拡散防止膜を形成し、銅拡散防護壁構造を実現する。

この図26に示す構成においては、第2メタル配線211bおよび211cがノードND1に接続される構成を利用しており、ヒューズFU(M4)と第2メタル配線211bおよび211cの距離を十分長くすることができ、また、ノードND1を上層の第4または第5メタル配線層に配置する必要がなく、ノードND1を延在させるための配線およびビアを配置する空間を確保する必要がなく、ヒューズのレイアウト面積を低減することができる。

また、ヒューズFU(M4)の溶断時の銅の熱拡散については、防護壁構造により、図26に示す構成における水平方向の銅拡散経路を遮断することができる。

ただし、第3メタル配線層M3の配線213aおよび213bの下部に隙間が存在するため、この領域において銅(Cu)が熱拡散する可能性がある。しかしながら、この場合、第3メタル配線213aおよび213bとヒューズFU(M4)のトリミング領域225の距離を、銅の熱拡散距離を考慮して十分に大きくとることにより、この図26の破線で示す銅が隣接ヒューズに熱拡散するのを防止することができる。

特に、ヒューズボックス内における配線は、回路的に電源電圧VDDレベルと同一電位に維持されるため(実施の形態1参照)、銅の熱拡散距離を十分短い距離に設定することができ、隣接ヒューズ素子領域への銅の熱拡散は確実に抑制することができる。

図27は、図26に示すヒューズ素子FSiの第2メタル配線層および第2ビアの平面レイアウトを概略的に示す図である。このヒューズ素子は、ヒューズボックス内に配置されるヒューズである。また、図27において、線L26−L26が、図26に示す断面構造の断面線である。以下、図28から図36においても、同様線L26−L26は、図26の断面構造の断面線を示す。

図27において、第2メタル配線層M2において、縦方向に長い第2メタル配線211aおよび211dが最外側に配置され、これらの内側に第1メタル配線211bおよび211cが配設される。この図27においては、図26において破線で示す不純物領域に対応して配置される第2メタル配線211u、211v、および211wを併せて示す。第2メタル配線211b、211cおよび211wは、矩形形状の第2メタルパッド配線230に接続され、一方、第2メタル配線211a、211d、211uおよび211vは、横方向に延在する第2メタル配線232に結合される。

第2メタル配線232は仮想接地線に結合され、仮想接地電圧VGNDを伝達する。この第2メタル配線232表面には、溝形状の第2ビア233が配設される。一方、第2メタルベッド配線232は、複数の単位ビア231が整列して配設される。この第2ビア231は上層配線との電気的接続のために設けられ、銅の拡散を防止する目的は特に有していない。

この第2メタルパッド配線230外部に、横方向に連続的に延在する第2メタル配線233が設けられ、この第2メタル配線233は、電源電圧VDDを供給する。第2メタル配線233には溝形状第2ビア234が配置される。溝形状第2ビア233および234は、ヒューズ素子形成領域それぞれに対応して配置されてもよく、複数のヒューズ素子形成領域にわたって連続的に延在するように形成されてもよい。

図28は、ヒューズボックスにおける複数のヒューズFS0−FSnの端部のヒューズ素子FSnの第2メタル配線層の平面レイアウトを示す図である。このヒューズ素子FSnにおいて、以下の点で、そのレイアウトが図27に示すヒューズ素子FSiの平面レイアウトと異なる。すなわち、縦方向に長い第2メタル配線235が形成され、この第2メタル配線235表面上に溝形状第2ビア236が設けられる。この第2メタル配線235は、第2メタル配線233に結合され、また、溝形状第2ビア236が、溝形状第2ビア234に結合される。この場合、第2メタル配線235が電源電圧VDDを伝達し、一方、第2メタル配線232が、仮想接地電圧VGNDを伝達するため、第2メタル配線235および232の間には隙間が存在する。

これらの図27および図28に示すように、トリミング領域(ヒューズ溶断領域)225からの銅の熱拡散経路(図27、図28において破線で示す)は確実に、第2メタル配線で遮断され、またヒューズボックス外部への銅の熱拡散は、第2メタル配線232、233、235および溝形状第2ビア233、234、236により確実に抑制される。

図28に示す端部のヒューズ素子FSnにおいて、第2メタル配線235および232の間に隙間が存在し、ヒューズボックス外部へ銅が拡散する可能性がある。しかしながら、ヒューズトリミング領域225とこの隙間領域との間の距離をどう熱拡散距離よりも大きくとることにより、ヒューズボックス外部への銅の熱拡散を確実に抑制することができる。

これらの図27および図28に示す配置においても、ヒューズの第2メタル配線232外部の領域に、ヒューズプログラム回路の溶断電流供給トランジスタ以外のトランジスタ素子が設置されるため、これらのトランジスタ素子を配置するための配線に対する銅の熱拡散は確実に防止される。

図29は、図26に示すヒューズ素子FSiの第3メタル配線層M3および第3ビアの平面レイアウトを概略的に示す図である。図29においても、図26の断面構造の断面線L26−L26を併せて示す。

図29において、第3メタル配線213aおよび213bが、それぞれ縦方向に長く形成され、第3メタル配線213aおよび213b表面上に溝形状第3ビア215aおよび215bが長く形成される。この第3メタル配線213aおよび213bに対し横方向に連続的に延在する第3メタル配線242が形成され、この第3メタル配線242上にヒューズ素子FSiに対応して溝型第3ビア243が形成される。この第3メタル配線242は電源電圧VDDを伝達し、第3メタル配線213aおよび213bに接続される。また溝型第3ビア243は、それぞれ、第3溝型ビア215aおよび215bに接続される。この第3メタル配線242は、図26に示す第2メタル配線232が配置される領域よりもヒューズに近い内側の領域に配置される。

一方、図27に示す第2メタルパッド配線231に対応して、第3メタルノードベッド配線240が配設される。この第3メタルベッド配線240には、上部配線との電気的接続を取るための単位第3ビア241が複数個整列して配置される。

第3メタル配線242外部に、第2メタル配線232に対応して第3メタル配線244が配置され、この第3メタル配線244表面上に溝形状第3ビアが配置される。第3メタルパッド配線240外部に、図26示す第2メタル配線233に対応して連続的に延在する第3メタル配線245が配置され、この第3メタル配線245表面に、図26に示す溝形状第2ビア234に対応して溝形状第3ビア246が配置される。第3メタル配線245は電源電圧VDDを伝達し、第3メタル配線244は仮想接地線に結合され、仮想接地電圧VGNDを伝達する。

図30は、ヒューズボックス端部のヒューズ素子FSnの第3メタル配線層M3の平面レイアウトを概略的に示す図である。この図30に示すヒューズ素子FSnの平面レイアウトは以下の点で図29に示すヒューズ素子の平面レイアウトと異なる。すなわち、ヒューズボックス端部において縦方向に長い第3メタル配線247が配置され、また縦方向に長く溝形状第3ビア248が形成される。第3メタル配線247が、第3メタル配線245および242にそれぞれ結合され、溝形状第3ビア248が、溝形状第3ビア246および243に接続される。したがって、ヒューズボックス端部においては、第3メタル配線245、247および242と溝形状第3ビア246、248および243により確実に、隙間のない銅拡散防護壁が形成され、ヒューズボックス外部への銅の熱拡散は抑制される。図30に示すヒューズ素子FSnの他の配置は図29に示すヒューズ素子FSiの配置と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

図29および図30に示すように、ヒューズトリミング領域225からの銅原子の伝搬経路は、図において破線矢印で示すように、第3メタル配線213aおよび213bと第3メタルパッド配線240の間の隙間領域だけである。このレイアウトの場合、隣接ヒューズ素子への銅原子の熱拡散が考えられるものの、ヒューズボックス外部への銅原子の熱拡散は確実に抑制される。また、ヒューズボックス内部においては、内部配線は、通常同一電圧(電源電圧VDD)に維持されるため(実施の形態1参照)、銅熱拡散距離は十分小さく、ほぼ、その影響を抑制することができる。

図31は、図26に示すヒューズ素子FSiの第4メタル配線層M4および第4ビアの平面レイアウトを概略的に示す図である。図31においても、図26に示すヒューズ素子の断面構造に対する断面線L26−L26を示す。

図31において、第4メタル配線214aおよび214bが縦方向に長く形成され、また第4メタル配線214aおよび214bに対して溝形状第4ビア217aおよび217bがヒューズ素子形成領域内において連続的に延在して形成される。第4メタル配線214aおよび214bの間に第4メタル配線で形成されるヒューズFU(M4)が配置される。ヒューズFU(M4)の両端に、第4メタルパッド配線250および251が形成される。これらの幅の広いパッド配線250および251により、ヒューズFU(M4)に対して溶断時に電流集中が生じるのを抑制する。

第4メタルパッド配線250に隣接して、図29に示す第3メタルベッド配線241に対応して第5メタルベッド配線252に配置され、これらのパッド配線250およびベッド配線252が結合される。一方、第4メタル配線214aおよび214bと第4メタルパッド配線251に接して、横方向に連続的に延在する第4メタル配線253が配置される。この第4メタル配線253表面上に溝形状第4ビア254が配置される。この第5メタル配線214a、214bおよびパッド配線251が第4メタル配線253に結合され、また溝形状第4ビア254が、第4ビア217aおよび217bに結合される。この第4メタル配線253は、複数のヒューズ素子に共通に配置され、その表面に形成される複数の単位第4ビア255により上層の配線に電気的に結合される。

また、ベッド配線252外部領域に、図図29に示す第3メタル配線245に対応して横方向に連続的に延在する第4メタル配線256が配置され、この第4メタル配線256表面に溝形状第4ビア257が形成される。第4メタル配線253および256は、電源電圧VDDを伝達する。

図32は、ヒューズボックス端部に配置されるヒューズ素子FSnの第4メタル配線層M4および第4ビアのレイアウトを示す図である。この図32に示すヒューズ素子FSnの平面レイアウトは、以下の点で、図31に示すヒューズ素子FSiの平面レイアウトと異なる。すなわち、ヒューズボックス端部において、縦方向に長い第4メタル配線258および溝形状第4ビア259が配置される。この第4メタル配線258は、第4メタル配線256および253に結合され、溝形状第4ビア259が、溝形状第4ビア257および254に結合される。この図32に示す平面レイアウトの他の要素のレイアウトは図31に示すヒューズ素子の平面レイアウトと同じであり、対応する部分には同一参照番号を付して、その詳細説明は省略する。

図31および図32に示すように、第4メタル配線層M4においても、破線矢印で示すヒューズトリミング領域225からの銅の熱拡散経路において、第4メタル配線253およびビア254によりヒューズボックス外部へ到達する拡散経路は遮断される。また図32に示すヒューズ素子FSnにおいても、第4メタル配線258および溝形状第4ビア259により、銅の熱拡散経路が遮断され、ヒューズボックス外部へ銅が熱拡散する経路は遮断される。

また、図31および図32においても、破線矢印で示す銅の熱拡散経路において隣接ヒューズ素子へ銅が熱拡散する可能性はあるものの、ヒューズボックス内の配線は、通常、同一電位に維持されており、この配線層においても、銅の熱拡散距離は、十分短くすることができ、隣接ヒューズ素子への銅の拡散は十分に抑制される。

図33は、図26に示すヒューズ素子の第5メタル配線層M5および第5ビアの平面レイアウトを概略的に示す図である。図33においても、図26に示す断面構造の断面線L26−L26を併せて示す。

図33において、第5メタル配線216aおよび216bが縦方向に延在して配設され、この図31に示す第4メタルベッド配線252上にまで延在して配置される。この第5メタル配線216aおよび216b表面に、溝形状第4ビア218aおよび218bが縦方向に連続的に延在して配置される。この第5メタル配線216aおよび216bに接して、連続的に横方向に延在して第5メタル配線260が配置され、また、第5メタルベッド配線252の外部領域に、連続的に延在して第5メタル配線263が配設される。第5メタル配線260表面に、溝形状第5ビア261が配設され、この第5ビア261は、第5ビア218aおよび218bと連結される。この第5メタル配線260は、図31に示す第4メタル配線253に整列して配置され、これらのメタル配線260および253は、図31に示す第4ビア250および単位ビア255を介して電気的に接続される。この第5メタル配線260においても上層の配線との電気的接続をとるための単位第5ビア262が複数個並列して配置される。

図34は、このヒューズボックス端部のヒューズ素子FSnの第5メタル配線層M5および第5ビアの平面レイアウトを概略的に示す図である。図34に示すヒューズ素子FSnの配線レイアウトは、以下の点で、図33に示すヒューズ素子FSiの平面レイアウトと異なる。すなわち、ヒューズボックス端部において、縦方向に延在して第5メタル配線265が配設され、この第5メタル配線265表面に、第5ビア266が縦方向に連続的に延在して形成される。第5メタル配線265は、第5メタル配線263および260に連結され、第5ビア266が第5ビア264および261に連結される。この図34に示すヒューズ素子FSnの他の構成要素の配置は、図33に示すヒューズ素子FSiの平面レイアウトと同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

図33および図34に破線矢印で示すように、ヒューズトリミング領域255からの銅の熱拡散経路は、第5メタル配線層M5においては、ベッド配線252と第5メタル配線216aおよび216bの間の隙間領域を介して延在する。しかしながら、この場合、上側領域に形成される第5メタル配線263および第5ビア264により、銅の熱拡散経路が遮断され、ヒューズボックス外部への拡散経路は遮断される。一方、トリミング領域225からの銅の熱拡散経路は、その下側領域においては、第5メタル配線260および第5ビア261により遮断される。したがって、ヒューズ素子FSiおよびFSnいずれにおいても、トリミング領域225からの銅原子のヒューズボックス外部への熱拡散経路は遮断される。

図35は、図26に示すヒューズ素子の第6メタル配線層M6の配線レイアウトを概略的に示す図である。図35においては、ヒューズFU(M4)に関連する要素を併せて示す。この第6メタル配線層の配線レイアウトは、ヒューズ素子FSiおよびFSnについて同じであり、図35においては、ヒューズ素子FSとしてこれらのヒューズ素子FSiおよびFSnを示す。また、線L26−L26は、図26に示す断面構造の断面線を示す。

図35において、ヒューズFU(M4)の溶断部(トリミング領域:図35には示さず)上層部に上部拡散防護壁配線220として、幅の広い第6メタル配線270が連続的に延在して配置される。また、図33に示す第5メタル配線263および261に対応して、それぞれ横方向に連続的に延在する第6メタル配線274および272が配設される。これらの第6メタル配線272および274は電源電圧VDDを伝達する幅の広いグローバル電源線である。

この第6メタル配線層の拡散防護壁構造の蓋部分の配線220として、幅の広いベタ配線270は、ヒューズFU(M4)の溶断部分(トリミング領域)に対応する領域にのみトリミング領域を蔽うように配置される。この電源線を構成する第6メタル配線274、270および272は、複数のヒューズ素子に配置されるため、ヒューズボックスにおける端部のヒューズ素子FSnについても同様の配線レイアウトが第6メタル配線層において配置される。

第6メタル配線270は、ヒューズFU(M4)両側において第6メタル配線275a、275bおよび277a、277bにより、それぞれ第6メタル配線274および272に連結される。これらの第6メタル配線275a、275b、277aおよび277bは、それぞれの下部に、図33に示す溝形状第5ビア218aおよび218bが設置されており、下層の第5メタル配線216aおよび216bと電気的に結合される。

図35に示すように、ヒューズFU(M4)両側には、第5メタル配線275a、275b、277a、277bおよび272の銅の熱拡散経路が遮断され、ヒューズ直上領域を超えて熱拡散が生じるのは確実に抑制される。

この平面レイアウトの場合、ヒューズFU(M4)の防護壁構造は、電源線を構成する第6メタル配線274および270および277から基板方向に向かって第3メタル配線層M3にまで延在する中間メタル配線およびビアにより形成されているだけであり、その防護壁構造は、一重側壁構造とされており、ヒューズ素子のレイアウト面積を低減することができる。

また、図26に示すように、この防護壁構造の側壁は、隣接ヒューズ素子間で共有されており、ヒューズ素子のレイアウト面積をより低減することができる。

また、この防護壁220を形成する第6メタル配線270の線幅は、先の実施の形態2の場合と同様、CMPにおける設計ルールを考慮してその配線幅が定められればよい。

本実施の形態においても、ヒューズ素子トリミング領域が、第6メタル配線270により覆われている。ヒューズFUを溶断した場合、ヒューズFUと銅拡散防止膜と層間膜(層間絶縁膜)との接触部であるヒューズFUの角の部分の2箇所を起点として、ヒューズFUの上側にヒューズから離れるようにクラックが発生し、第6メタル配線270にクラックが到達し、このクラック内に銅金属が入り込み、ヒューズFUと第6メタル配線270とが短絡することがある。このとき、ヒューズFUの電位が、第6メタル配線270上の電源電圧VDDとなる。応じて、切断判定回路CJCにより、トリミング不良を検出することが可能となり、不良品として、このチップ(半導体装置)を製品出荷前に検出、除去することが可能となる。なお、本発明の実施の形態においては、ヒューズFUの細身の直上においてヒューズFUの上側に配置され、かつヒューズFUに最も近いメタル配線は、第6メタル配線270であり、電源電圧VDDが供給されるようなレイアウト構造となる。

[第6メタル配線の変更例]

図36は、図26に示すヒューズ素子の第6メタル配線層M6の配線レイアウトの変更例を概略的に示す図である。図36において、ヒューズ素子FU(M4)のトリミング領域225の直上部領域を覆う第6メタル配線220として、ストライブ状の第6メタル配線280が複数個平行して配置される。これらのストライプ状の第6メタル配線280は、ヒューズ配置領域の外部領域において縦方向に延在して配置される第6メタル配線275a,275b、277a、および277bにより第6メタル配線272および274に接続される。図36に示す第6メタル配線層M6の平面レイアウトの他の配置は図35に示すヒューズ素子FSの第6メタル配線層M6の配線レイアウトと同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

図35および図36においてもヒューズ素子FSの線L26−L26に沿って切断すると、図26に示すヒューズ素子の断面構造が得られる。

このストライブ形状の第6メタル配線280を上部拡散防護壁配線220として利用する場合においても、ヒューズFU(M4)のトリミング領域225の直上部にストライプ状配線280が設置されていれば、その熱拡散の遮断効果は、ベタ配線270の場合と同じである。これらの防護壁構造の蓋として機能する第6メタル配線270および280の線幅は、CMPプロセス時のディシングおよび配線抵抗および設計ルールに従って適宜定められれば良い。

本実施の形態においても、ヒューズ素子トリミング領域が、第6メタル配線280により覆われている。ヒューズFUを溶断した場合、ヒューズFUと銅拡散防止膜と層間膜(層間絶縁膜)との接触部であるヒューズFUの角の部分の2箇所を起点として、ヒューズFUの上側にヒューズから離れるようにクラックが発生し、第6メタル配線280にクラックが到達し、このクラック内に銅金属が入り込み、ヒューズFUと第6メタル配線280とが短絡することがある。このとき、ヒューズFUの電位が、第6メタル配線280上の電源電圧VDDとなる。応じて、切断判定回路CJCにより、トリミング不良を検出することが可能となり、不良品として、このチップ(半導体装置)を製品出荷前に検出、除去可能となる。なお、本発明の実施の形態においては、ヒューズFUの細身の直上においてヒューズFUの上側に配置され、かつヒューズFUに最も近いメタル配線は、第6メタル配線280であり、電源電圧VDDが供給されるようなレイアウト構造となる。

[ヒューズ素子の変更例]

図37は、この発明の実施の形態3のヒューズ素子の変更例の断面構造を概略的に示す図である。この図37に示すヒューズ素子の断面構造は、以下の点で、図26に示すヒューズ素子の構造と異なる。すなわち、第1メタル配線層M1において第1メタル配線208aおよび208dが、それぞれ仮想接地電圧VGNDを受け、仮想接地線として機能する。第2メタル配線層M2においては、第1メタル配線208aおよび208dに対応して第2メタル配線290aおよび290bが配設される。これらの第2メタル配線290aおよび290b以外、第2メタル配線層には配線は配置されない。第1メタル配線層M1の第1メタル配線208bおよび208cが、ノードND1に結合される。

第2メタル配線290aおよび290bは溝形状第2ビア291aおよび291bを介して対応して第3メタル配線層M3に配置される第3メタル配線213aおよび213bに電気的に接続される。この第3メタル配線層M3のおいて、第1メタル配線208bおよび208cが配置される領域の間の領域上部にヒューズFU2(M3)を形成する第3メタル配線が配置される。

第4メタル配線層M4におけるレイアウトは、図26に示すものと同じである。しかしながら第5メタル配線層M5においては、第4ビア217aおよび217bが、第5メタル配線292に電気的に接続され、この第5メタル配線292が電源電圧VDDを伝達する。

図37に示す他の構成は、図26に示すヒューズ素子の構成と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

第3メタル配線層M3の配線を用いてヒューズFU2(M3)が形成される。この場合、ヒューズFU2(M3)のトリミング領域295およびダメージ領域297を囲むように一重の防護壁が第2メタル配線層M2の第2メタル配線から第5メタル配線層M5の第5メタル配線292により形成される。また、ヒューズFU2(M3)のダメージ領域297が、配線に到達していないため、ヒューズ溶断時に発生した熱による絶縁膜および配線の劣化が抑制される。

この場合、先の実施の形態2の変更例において説明したように、第1メタル配線208aおよび208bが仮想接地電圧VGNDを伝達するために利用され、またノードND1が、第1メタル配線208bおよび208cが電気的に接続される。したがって、この第1メタル配線層M1のメタル配線は、第2メタル配線層M2のメタル配線よりもその電気的特性が低く、エレクトロマイグレーション耐性が低い。したがって、実施の形態2の変更例の場合と同様、第1メタル配線のエレクトロマイグレーション耐性を評価し、そのヒューズFU2(M3)に対する第1メタル配線208a−208dのそれぞれの配線長を評価し、ヒューズFU2(M3)溶断時の大きな溶断電流により、これらの第1メタル配線208a−208dがエレクトロマイグレーションにより切断される状態が発生するのを抑制する。

この図37に示す構造の場合、ヒューズFU2(M3)の防護壁構造を1配線層分低い状態に設定することができ、配線層数をより低減することができる。

なお、防護壁を構成する配線およびビアについて、ヒューズ配置領域外部に連続的に延在して配置される電源線または仮想接地線に対応して配置されるメタル配線に対して配置される溝形状ビア(261,264等)は、対応のメタル配線と同様複数のヒューズ素子に渡って連続的に延在するように配置されてもよく、各ヒューズ素子毎に分離して配置されてもよい。この配置は、実施の形態2においても同様である。

以上のように、この発明の実施の形態3に従えば、ヒューズ直上部に電源電圧を伝達する電源線を拡散防護壁として配置して、この電源線から半導体基板領域方向に向かってヒューズを取囲むように防護壁構造を形成しており、また、この防護壁を隣接ヒューズ素子で共有している。したがって、ヒューズ素子の配線層数を低減することができ、またレイアウト面積を低減することができる。

なお、図示していないが、本実施の形態においても、平面視において、ヒューズ素子トリミング領域が、第5メタル配線292により覆われている。ヒューズFUを溶断した場合、ヒューズFUと銅拡散防止膜と層間膜(層間絶縁膜)との接触部であるヒューズFUの角の部分の2箇所を起点として、ヒューズFUの上側にヒューズから離れるようにクラックが発生し、第5メタル配線292にクラックが到達し、このクラック内に銅金属が入り込み、ヒューズFUと第5メタル配線292とが短絡することがある。このとき、ヒューズFUの電位が、第5メタル配線292上の電源電圧VDDとなる。応じて、切断判定回路CJCにより、トリミング不良を検出することが可能となり、不良品として、このチップ(半導体装置)を製品出荷前に検出、除去可能となる。なお、本発明の実施の形態においては、ヒューズFUの細身の直上においてヒューズFUの上側に配置され、かつヒューズFUに最も近いメタル配線は、第5メタル配線292であり、電源電圧VDDが供給されるようなレイアウト構造となる。

[実施の形態4]

図38は、この発明の実施の形態4に従うヒューズ素子の平面配置を概略的に示す図である。図38において、複数のヒューズ素子が配設されるヒューズボックスの第4メタル配線層M4の配線および第4ビアのヒューズボックス端部近傍の配置を示す。

図38において、ヒューズFUa−FUcが第4メタル配線層M4の配線で形成され、かつ互いに間をおいて配置される。ヒューズFUa−FUcは、それぞれピッチFPTで整列して配置される。

これらのヒューズFUa−FUcは、それぞれが、一方端において、第4メタルパッド配線301a−301cに結合され、それぞれの他方端部において第4メタルパッド配線302a−302cに結合される。これらの第4メタルパッド配線302a−302Cは、ヒューズFUa−FUcそれぞれに対応して互いに分離して配置される。第4メタルパッド配線301a−301cにそれぞれに連結して第4メタルベッド配線303a−303cが配置され、これらの第4メタルベッド配線303a−303cがノードND1をそれぞれ形成する。これらの第4メタルベッド配線303a−303cもヒューズFUa−FUcそれぞれに対応して互いに分離して配置される。

一方、第4メタルパッド配線302a−302cに共通に、連続的に横方向に延在する第4メタル配線306が配置され、これらの第4パッド配線302a−302cが第4メタル配線306に結合される。この第4メタル配線306は、電源電圧VDDを伝達する電源線を構成する。この第4メタル配線306の外周部には、上層配線との電気的接続のために、複数の単位第4ビア308が整列して配置される。また、拡散防護壁構造を形成するために、第4メタル配線306表面に、連続的に複数のヒューズ素子にわたって延在する溝形状第4ビア307が配置される。

第4メタルベッド配線303a−303c外部領域にまた連続的に横方向に延在する第4メタル配線304が配置され、この第4メタル配線304表面に、溝形状第4ビア305が連続的に形成される。この第4ビアによりヒューズボックス外部に対する銅原子の熱拡散を防止する拡散防護壁構造の一部が形成される。

ヒューズボックス端部において、これらの第4メタル配線304および306を連結するように第4メタル配線309が配置され、また、第4メタル配線309上に、溝形状第4ビア305および307を連結するように第4ビアア310が連続的に延在して形成される。

コア回路の通常動作時等のヒューズ溶断時および電圧ストレス印加テスト以外の状態においては、メタル配線がヒューズボックス内において同一電圧、すなわちノードND1の電圧レベルが電源電圧VDDレベルに維持され、ヒューズFUa−FUc両端部の電圧が、同一電圧レベル(一例として、電源電圧VDDレベル)に設定され、また、他の配線層の配線も同一電圧レベルに設定される。この場合、ヒューズFUa−FUcのトリミング領域311a−311cにおいてヒューズ溶断時に発生した銅片の銅原子の熱拡散距離を、ヒューズピッチFPTよりも小さくすることができ、隣接ヒューズ素子間に銅熱拡散防護壁を配置する必要がなく、ヒューズボックスの占有面積をより低減することができる。

図39は、図38に示す線L39−L39に沿った断面構造を概略的に示す図である。図39においては、この線L39−L39に沿った上層の第5メタル配線層M5および第6メタル配線層M6の配線も併せて示す。

図39において、ヒューズ回路の溶断電流供給トランジスタがPウェル320表面に形成される。このPウェル320下部にはディープNウェル322が配置される。Pウェル320およびディープNウェル322は、複数のヒューズ素子に対する溶断電流供給トランジスタに共通に配置され、特にトランジスタ間を分離するための素子分離領域は配置されていないように示す。しかしながら、溶断電流供給トランジスタCTr毎にPウェル表面に素子分離領域が配置されてもよい。

すなわち、Pウェル320表面に互いに間をおいて不純物領域324a−324dが1つのヒューズ素子FSbに対応する領域に対して配置され、ヒューズ素子FSaおよびFScに対応する領域においてまた不純物領域324xおよび324yが配置される。

図39においては、ヒューズ素子FSbに対し、溶断電流供給トランジスタの単位トランジスタの数を多く示し、ヒューズ素子FSaおよびFScに対する溶断電流供給トランジスタの単位トランジスタの数を少なく示す。しかしながら、これらのヒューズ素子FSaおよびFScにおいても、ヒューズ素子FSbに対する構成と同様、溶断電流供給トランジスタを構成する複数の単位トランジスタが配置される。不純物領域324aがヒューズ素子FSaおよびFSbに対する溶断電流供給トランジスタにより共有され、また不純物領域324dが隣接ヒューズ素子FSbおよびFScの溶断電流供給トランジスタにより共有される。

この不純物領域324x、324a−324dおよび324yの間にPウェル320上にゲート電極326x、326a、326b、326cおよび326yが配置される。

不純物領域324x、324a−324dおよび324yは、それぞれコンタクト328x、328a−328dおよび328yを介して第1メタル配線層M1の第1メタル配線327x、327a−327dおよび327yにそれぞれ接続される。

第2メタル配線層M2においては、第1メタル配線327x、327a−327dおよび327yそれぞれに対応して第2メタル配線330x、330a−330dおよび330yが配置され、これらは、それぞれ第1ビア331x、331a−331dおよび331yを介して対応の第1メタル配線327x、327a−327dおよび327yに結合される。第2メタル配線330aおよび330dが仮想接地線に結合され、仮想接地電圧VGNDを受け、第2メタル配線331bおよび331cがノードND1に結合される。

このヒューズ素子FSa−FScそれぞれにおいては、第4メタル配線層M4の第4メタル配線を用いてヒューズFUa、FUbおよびFUcが互いに間をおいて所定のヒューズピッチFTPで配置される。これらのヒューズFUa−FUcを覆うように第6メタル配線層M6において第6メタル配線334が連続的に延在して配置される。この第6メタル配線334は電源電圧VDDを伝達する。

ヒューズFUa−FUc配置領域おいては、第3メタル配線層M3および第5メタル配線M5においては、配線は配置されず、また、第4メタル配線層M4においても、ヒューズFUa−FUcを形成する配線以外は配置されない。

ヒューズボックス端部において、第6メタル配線334は第5ビア336を介して第5メタル配線層M5の第5メタル配線337に結合される。この第5メタル配線337は、第4ビア310を介して第4メタル配線層M4の第4メタル配線309に結合される。この第4メタル配線309に対応して第3メタル配線層M3および第2メタル配線層M2に第3メタル配線339および第2メタル配線341がそれぞれ配置される。第3メタル配線339は、第3ビア338を介して第4メタル配線309に結合され、また、第2ビア340を介して第2メタル配線341に結合される。これらのビア336、310、338および340は、図38に示すように連続的に延在する溝形状ビアで構成される。

この各メタル配線層M1−M5の間には、銅拡散防止膜CDPが配置される。この銅拡散防止膜CDPは、SiCN(窒化シリコンカーバイド)などで形成され、銅原子の拡散防止機能を有し、層間絶縁膜の各界面に形成される。

この図39に示すように、ヒューズFUa、FUbおよびFUcのトリミング領域311a、311bおよび311cからの熱拡散により層間絶縁膜が損傷を受けるダメージ領域350a、350bおよび350cは、互いに重なり合わないように配置され、また、内部配線の電圧制御により銅の熱拡散距離は、ヒューズピッチFTPよりも十分小さくされる。またヒューズFUa−FUcの直上部および直下部においては、2層の配線層の間隙が生じ、十分に銅の熱拡散による短絡等を防止することができるとともに、熱の閉じ込めを抑制することができる。

また、このヒューズボックス端部において、第2メタル配線層から第6メタル配線層M2−M6の配線と溝形状ビアとにより、銅拡散防護壁構造を実現しており、ヒューズボックス外部に銅が熱拡散するのを抑制することができる。

また、図39に示すように、仮想接地線に結合される配線が隣接ヒューズ素子間で共有されており、ヒューズ素子のレイアウト面積をより低減することができる。また、ヒューズ素子間に銅拡散防護壁構造を配置する必要がなく、より一層、ヒューズ素子のレイアウト面積を低減することができる。

但し、条件としては、この図38および図39に示す構成においては、銅の熱拡散距離を十分に低減するため、通常の回路動作時においては、各配線、特にノードND1は、第6メタル配線334の電圧VDDと同一電圧レベルに設定することが要求される(実施の形態1参照または後述の外部からのヒューズ電源供給の実施の形態参照)。

本実施の形態においては、図示していないが、平面視において、ヒューズ素子トリミング領域が、第6メタル配線334により覆われている。ヒューズFUを溶断した場合、ヒューズFUと銅拡散防止膜と層間膜(層間絶縁膜)との接触部であるヒューズFUの角の部分の2箇所を起点として、ヒューズFUの上側にヒューズから離れるようにクラックが発生し、第6メタル配線334にクラックが到達し、このクラック内に銅金属が入り込み、ヒューズFUと第6メタル配線334とが短絡することがある。このとき、ヒューズFUの電位が、第6メタル配線334上の電源電圧VDDとなる。応じて、切断判定回路CJCにより、トリミング不良を検出することが可能となり、不良品として、このチップ(半導体装置)を製品出荷前に検出、除去可能となる。なお、本発明の実施の形態においては、ヒューズFUの細身の直上においてヒューズFUの上側に配置され、かつヒューズFUに最も近いメタル配線は、第6メタル配線334であり、電源電圧VDDが供給されるようなレイアウト構造となる。

[変更例]

図40は、この発明の実施の形態4に従うヒューズ素子の変更例の断面構造を概略的に示す図である。この図40に示すヒューズ素子の構造は、図39に示すヒューズ素子の構造と以下の点で異なる。すなわち、第1メタル配線層M1において、第1メタル配線327aおよび327dが仮想接地電圧VGNDを伝達する配線として利用され、また第1メタル配線327bおよび327cが、ノードND1に結合される配線として利用される。また、第2メタル配線層M2においては、ヒューズ直下部にはメタル配線は配置されない。一方、第3メタル配線層M3の配線を用いて、ヒューズ素子FUa(M3)−FUc(M3)を形成する。これらのヒューズ素子FUa(M3)FUc(M3)の上層に、第5メタル配線層M5のメタル配線354を配置して上部拡散防護壁配線として利用する。この第5メタル配線354は電源電圧VDDを伝達する。

この第5メタル配線354は、ヒューズボックス端部において、溝形状第4ビア310を介して第4メタル配線層M4のメタル配線309に結合される。また、第2メタル配線層M3の第2メタル配線341は、第1ビア358を介して第1メタル配線層M1のメタル配線359に結合される。これらのヒューズボックス端部において、第5メタル配線層M5から第1メタル配線層M1のメタル配線とそれらの間の溝形状ビアを用いて、銅熱拡散防護壁を形成する。

この図40に示すヒューズの他の構成は、図39に示すヒューズ素子の構成と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

この図40に示すヒューズ素子の場合、仮想接地電圧VGNDが、第1メタル配線層M1の第1メタル配線327aおよび327dを介して伝達される。したがって、先の実施の形態2および3の変更例の構成と同様、ヒューズ溶断時に大きな電流が流れる際のエレクトロマイグレーション耐性を考慮し、その配線長および配線幅を設定する必要がある。第1メタル配線層のメタル配線のエレクトロマイグレーション耐性が保障されれば、このヒューズボックスに使用される配線層の数を1つ低減することができる。

図40に示すヒューズ素子FSa−FScの構成において、ダメージ領域350a−350cが、その上層および下層の第5メタル配線354および第1メタル配線にまで到達するように示す。しかしながら、これらのダメージ領域350a−350cは、ヒューズ溶断時の高熱により層間絶縁膜が劣化する可能性のある領域であり、物理的に損傷を受ける領域と異なり、配線部分にまでダメージ領域が延在しても特に問題は無い。

また、ヒューズボックス内のメタル配線はすべて、通常使用時、例えば電源電圧VDDレベルの同一電圧レベルに維持されるため、銅拡散距離は十分に小さくすることができ、層間絶縁膜および銅拡散防止膜CDPの銅原子拡散による絶縁性の劣化も十分に抑制することができる。

以上のように、この発明の実施の形態4に従えば、ヒューズを等間隔で配置し、隣接ヒューズ間には、銅熱拡散防護壁が設けられていない。ヒューズボックス端部においてのみ、メタル配線およびビアにより上層の電源線から基板領域方向に向かって延在する防護壁構造を形成している。したがって、ヒューズ素子のレイアウト面積を低減することができる。

なお、ヒューズ直上部に形成される電源配線の形状は、実施の形態3に示す構成と同様、トリミング領域311a−311cを蔽うように形成されるベタ配線およびストライプ形状の配線のいずれが利用されてもよい。

また、図に示していないが、本実施の形態においても、平面視において、ヒューズ素子トリミング領域が、第5メタル配線354により覆われている。ヒューズFUを溶断した場合、ヒューズFUと銅拡散防止膜と層間膜(層間絶縁膜)との接触部であるヒューズFUの角の部分の2箇所を起点として、ヒューズFUの上側にヒューズから離れるようにクラックが発生し、第5メタル配線354にクラックが到達し、このクラック内に銅金属が入り込み、ヒューズFUと第5メタル配線354とが短絡することがある。このとき、ヒューズFUの電位が、第5メタル配線354上の電源電圧VDDとなる。応じて、切断判定回路CJCにより、トリミング不良を検出することが可能となり、不良品として、このチップ(半導体装置)を製品出荷前に検出、除去可能となる。なお、本発明の実施の形態においては、ヒューズFUの細身の直上においてヒューズFUの上側に配置され、かつヒューズFUに最も近いメタル配線は、第5メタル配線354であり、電源電圧VDDが供給されるようなレイアウト構造となる。

[実施の形態5]

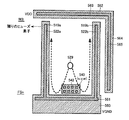

図41は、この発明の実施の形態5に従うヒューズ素子の断面構造を概略的に示す図である。図41において、ヒューズ素子は、Pウェル400上に形成される。このPウェル(半導体基板領域)400の下部に、ウェル分離用のディープNウェル402が形成される。Pウェル400表面に互いに間をおいて不純物領域(活性領域)404a−404dが形成される。これらの不純物領域404a−404dの間の基板領域上にゲート電極406a、406b、406cが図示しないゲート絶縁膜を介して配置される。不純物領域404a−404dおよびゲート電極406a−406cにより、複数の単位トランジスタの並列体で構成される溶断電流供給トランジスタが形成される。

第1メタル配線層M1において、これらの不純物領域404a−404dそれぞれに対応して第1メタル配線407a−407dが形成され、それぞれコンタクト408a−408dを介して対応の不純物領域404a−404dに接続される。

第2メタル配線層M2において、第1メタル配線407a−407dそれぞれに対応して第2メタル配線409a−409dが整列して配置される。これらの第2メタル配線409a−409dは、それぞれ、溝形状の第1ビア410a−410dを介して対応の第1メタル配線407a−407dに接続される。第2メタル配線層M2において、第2メタル配線409bおよび409cが仮想接地線に結合され、仮想接地電圧VGNDを伝達する。

第3メタル配線層M3においては、第2メタル配線409aおよび409dに対応してかつ整列して第3メタル配線411aおよび411bが配設される。これらの第3メタル配線411aおよび411bは、溝形状の第2ビア412aおよび412bを介して対応の第2メタル配線409aおよび409dに電気的に接続される。

第4メタル配線層M4において、第3メタル配線411aおよび411bに対応して第4メタル配線413aおよび413bが配設される。これらの第4メタル配線413aおよび413bの間に、第4メタル配線を用いてヒューズFUが形成される。第4メタル配線413aおよび413bは、それぞれ溝形状の第3ビア414aおよび414bを介して対応の第3メタル配線411aおよび411bに接続される。第3メタル配線層M3においては、ヒューズFUの直下部においては配線は配置されない。

第5メタル配線層M5において、第4メタル配線413aおよび413b各々に対応してかつ整列して第5メタル配線415aおよび415bが配設される。これらの第5メタル配線415aおよび415bの間に、第5メタル配線415cおよび415dが配設される。第5メタル配線415aおよび415bは、それぞれ溝形状の第4ビア416aおよび416bを介して第4メタル配線413aおよび413bに接続される。第5メタル配線415cおよび415dは、溝形状の第5ビア417aおよび417bを介して第6メタル配線層M6の配線420に接続される。この第6メタル配線420は電源電圧VDDを伝達し、ヒューズFUのトリミング領域425上部を覆うように形成される。この電源線を構成する第6メタル配線420は、ベタ配線であってもよく、またストライプ形状の配線であってもよい。第5メタル配線415aおよび415bはノードND1を構成する。

この図41に示すように、ヒューズFUの銅熱拡散経路を遮断する拡散防護壁構造として、ノードND1を構成するメタル配線の内側に電源電圧VDDが伝達される第5メタル配線を配置することにより、防護壁構造のレイアウト面積を低減することができまた、第5メタル配線層において、銅拡散経路を確実に遮断することができる。

図41においても、各メタル配線層の境界部に、銅拡散防止膜CDPが配置され、このヒューズFU溶断時のダメージ領域427における銅拡散を抑制する。このダメージ領域427は、単にヒューズ溶断時に発生する熱により、層間絶縁膜の劣化が生じる可能性がある領域である。

図42は、図41に示すヒューズ素子の第5メタル配線層の配線レイアウトを概略的に示す図である。図42においては、このヒューズFUの関連する部分の配置を併せて示す。また、図42に示す線L41−L41に沿った断面構造が、図41に示す断面構造である。

図42において、ヒューズFUの両端に対向してかつヒューズFUに接続して第4メタルベッド配線422および423が配置される。この第4メタルベッド配線422に対応して、矩形形状の第5メタル配線425が配置され、第5メタル配線425は、ヒューズFU両側に配置される第5メタル配線415aおよび415bに結合される。

第5メタル配線415cおよび415dに対応して横方向に連続的に延在する第5メタル配線426が配置される。第5メタル配線415cおよび415d表面には、連続的に延在する溝形状の第4ビア417aおよび417bが形成される。第5メタル配線415cおよび415dは、第5メタル配線426に接続され、また、第5ビア417aおよび417bが、第5メタル配線426表面に形成される第5ビア427に結合される。この第5メタル配線426は、電源電圧VDDを伝達する電源線を構成する。第5メタル配線426表面には、上層に形成されるグローバル電源線に結合されるために、単位第5ビア428が複数個整列して配置される。

図42に示すように、ヒューズトリミング領域425からの銅熱拡散経路(破線矢印で示す)は、第5メタル配線426方向に対しては完全に遮断することができる。一方、第5メタル配線415aおよび415cの間および第5メタル配線415dおよび415bの間の隙間領域を通って銅熱拡散が生じる可能性がある。しかしながら、この経路は銅の拡散距離よりも十分長く、隣接ヒューズへの銅熱拡散はほぼ抑制することができる。特に、ノードND1および電源線(第5メタル配線)426をともに一例として電源電圧VDDレベルに通常動作時に維持することにより、銅の熱拡散距離は十分小さくすることができ、隣接ヒューズ素子への銅拡散は十分に抑制することができる。

この図41および図42に示すように、ノードN1に接続される配線および溝形状ビアを利用して、拡散防護壁を形成し、この拡散防護壁内部に第5メタル配線および溝形状ビアを配置して上層の第6メタル配線に接続することにより、トリミング領域425の直上部は塞がれた状態となり、銅の熱拡散を確実に抑制することができる。

なお、この図41および図42に示すヒューズ素子の他の配線層の平面レイアウトは、先の図27から図32および図35または図36に示す平面レイアウトと同じである。

以上のように、この発明の実施の形態5に従えば、ヒューズの銅拡散防護壁構造として、ノードN1に接続される防護壁内部に、上部の電源配線に接続されるメタル配線を配置しており、この防護壁構造のレイアウト面積を低減することができ、ヒューズ素子のレイアウト面積を低減することができる。

なお、この図41に示すヒューズの構成においても、第1メタル配線層M1のメタル配線のエレクトロマイグレーション耐性が十分に強いときには、ヒューズFUを、第3メタル配線層M3のメタル配線を用いて形成することができ、各配線を、1層ずつ下の配線層に配置することができる。

なお、本実施の形態においても、図示していないが、平面視において、ヒューズ素子トリミング領域が、第6メタル配線475により覆われている。ヒューズFUを溶断した場合、ヒューズFUと銅拡散防止膜と層間膜(層間絶縁膜)との接触部であるヒューズFUの角の部分の2箇所を起点として、ヒューズFUの上側にヒューズから離れるようにクラックが発生し、第6メタル配線475にクラックが到達し、このクラック内に銅金属が入り込み、ヒューズFUと第6メタル配線475とが短絡することがある。このとき、ヒューズFUの電位が、第6メタル配線475上の電源電圧VDDとなる。応じて、切断判定回路CJCにより、トリミング不良を検出することが可能となり、不良品として、このチップ(半導体装置)を製品出荷前に検出、除去可能となる。なお、本発明の実施の形態においては、ヒューズFUの細身の直上においてヒューズFUの上側に配置され、かつヒューズFUに最も近いメタル配線は、第6メタル配線475であり、電源電圧VDDが供給されるようなレイアウト構造となる。

[実施の形態6]

図43は、この発明の実施の形態6に従うヒューズ素子の断面構造を概略的に示す図である。図43において、ヒューズ素子は、Pウェル450上に形成される。このPウェル450下部には、これまでの実施の形態と同様ディープNウェル452が形成される。ディープNウェル452により、仮想接地線の電圧VGNDを他回路に対して悪影響を及ぼすなく所望の電圧レベルに設定する。

Pウェル450において、隣接ヒューズ素子間の溶断電流供給トランジスタを分離するための素子分離領域は配置されない、Pウェル450表面に、互いに間をおいて不純物領域460a−460d、460xおよび460yが設けられる。不純物領域460aおよび460dは、それぞれ隣接するヒューズ素子領域間で共有される。図43において、この隣接ヒューズ素子領域における不純物領域460xおよび460yを合わせて示す。

これらの不純物領域460x、460a−460d、および460yのPウェル(基板領域)450表面上に図示しないゲート絶縁膜を介してゲート電極配線460x、462a−462dが配置される。

第1メタル配線層M1において、これらの不純物領域460x、460a−460d、および460yそれぞれに対応して第1メタル配線464x、464a−464d、および464yが配置され、それぞれ、コンタクト465x、465a−465dおよび465yを介して対応の不純物領域460x、460a−460d、および460yに結合される。

第2メタル配線層M2において、これらの第1メタル配線464x、464a−464d、および464yそれぞれに対応してかつ整列して第2メタル配線466x、466a−466d、および466yが配置される。これらの第2メタル配線466x、466a−466d、および466yは、それぞれ、溝形状の第1ビア467x、467a−467d、および467yを介して対応の第1メタル配線464x、464a−464d、および464yに結合される。

第3メタル配線層M3において、第2メタル配線466a−466dに対応してかつ整列して第3メタル配線468a−468dが配置される。第3メタル配線468bおよび468cは、それぞれ溝形状の第2ビア469aおよび469bを介して対応の第2メタル配線466bおよび466cに結合される。これらの第3メタル配線468bおよび468cは、ノードND1に接続される。一方、第3メタル配線468aおよび468dは、下層の対応の第2メタル配線466aおよび466dと分離される。第2メタル配線466aおよび466dが、仮想接地線に結合され、仮想接地電圧VGNDを伝達する。

第4メタル配線層M4において、第3メタル配線468aおよび468dに対応してかつ整列して第4メタル配線470aおよび470bが配置される。これらの第4メタル配線470aおよび470bの間の第4メタル配線を用いてヒューズFUが形成される。第4メタル配線470aおよび470bは、それぞれ溝形状の第3ビア471aおよび471bを介して対応の第3メタル配線468aおよび468dに結合される。

第5メタル配線層M5において、第4メタル配線470aおよび470bに対応して第5メタル配線472aおよび472bが配置され、これらの第5メタル配線472aおよび472bは、それぞれ溝形状の第4ビア473aおよび473bを介して対応の整列して配置される下層の第4メタル配線470aおよび470bに結合される。

この第5メタル配線472aおよび472bは、溝形状の第5ビア474aおよび474bを介して、それぞれ、第6メタル配線層M6のメタル配線475に結合される。このメタル配線475は、電源電圧VDDを伝達する電源線であり、ヒューズトリミング領域480を蔽うように配置され、その配線構造はベタ配線であってもよく、またストライプ形状の配線であってもよい。

この図43に示すヒューズ素子の構造においても、各メタル配線層の境界部には、銅拡散防止膜CDPが配置される。ヒューズFUは、トリミング領域480において溶断される。ヒューズ溶断時の熱により、ダメージ領域482に溶断時の高温が伝達され、層間絶縁膜がダメージを受ける可能性がある。しかしながら、ヒューズFUの直上および直下部においては、配線は配置されていないため、配線に対する悪影響は生じない。

ノードND1に結合される第3メタル配線層468bおよび468cを、電源電圧VDDを伝達する第3メタル配線468aおよび468bの内側に配置することにより、隙間のない拡散防護壁構造を実現することができ、ヒューズFU溶断時における銅の熱拡散経路を確実に遮断することができ、隣接ヒューズへの銅熱拡散経路を確実に遮断することができる。拡散防護壁は、隣接ヒューズ素子間で共有される。

図44は、図43に示すヒューズ素子の第3メタル配線層M3の配線レイアウトを概略的に示す図である。図44においては、第4メタル配線層M4の配線で形成されるヒューズFUの配置を破線で併せて示す。この図44に示す線L43−L43に沿った断面構造が、図43に示す断面構造に対応する。

図44において、第3メタル配線468bおよび468cは、それぞれ縦方向に長く延在し、ヒューズFUの第4メタルベッド配線に対応して配置される第4メタルベッド配線485に結合される。第3メタルベッド配線485表面には、複数の単位第3ビア486が整列して配置されており、上層のベッド配線と電気的に接続される。第3メタル配線468bおよび468cに対しては、溝形状のビアは設けられない。

これらの第3メタル配線468bおよび468c外側領域に配置される第3メタル配線468aおよび468dは、それぞれ縦方向に長くヒューズ素子形成領域内に延びるように形成され、連続的に横方向に延在する第3メタル配線487に結合される。この第3メタル配線487上には、連続的に延在して溝形状の第3ビア488が形成され、第3メタル配線468aおよび468d上に形成される溝形状の第3ビア471aおよび471bが、この溝形状第3ビア487と結合される。この第3メタル配線487は、電源電圧VDDを伝達し、最終的に、中間配線およびビアを介して第6メタル配線層M6に配置される電源線に結合される。

この第3メタルベッド配線485外側領域に、連続的に横方向に延在する第3メタル配線489が配置され、この第3メタル配線489表面に溝形状の第3ビア490が形成され、電源電圧VDDを伝達する。

第3メタル配線487外側領域には、第3メタル配線491が横方向に連続的に延在して配置され、仮想接地電圧VGNDを伝達する。この第3メタル配線491表面には、溝形状ビアは形成されず、その下部に形成される第2ビアにより、下層の第2メタル配線に電気的に結合される。

ヒューズFUは、その両端に第4メタルパッド配線485および486がそれぞれ形成され、第3メタルベッド配線485が、対応して配置される第4メタルベッド配線と電気的に結合され、また、パッド配線486は、第3メタル配線487に対応して上層に配置される第4メタルベッド配線を介して電源線に結合される。

図43および図44に示すように、ヒューズFUのトリミング領域480を囲むように、ノードND1に結合される第3メタル配線458bおよび468cを配置することにより、第3メタル配線468aおよび468dと第2メタル配線466aおよび466dとの間に隙間が生じる場合においても、この隙間を介して銅が熱拡散するのを防止することができる。トリミング領域480からの銅の熱拡散経路は、図44の破線矢印で示すように、第3メタル配線468aおよび468bの間、および468cおよび468dの間の領域であり、この経路長は、銅の熱拡散距離よりも十分長く、この経路を介して隣接ヒューズ素子へ、銅が熱拡散するのは確実に抑制される。

したがって、この図43および図44に示すように、隣接ヒューズ素子で銅拡散防護壁を共有する場合においては、この外部の防護壁構造内部にノードN1に接続される防護壁を配置することにより、確実に、銅の熱拡散を、ヒューズ素子面積を増大させることなく抑制することができる。

また、下層接地線VGNDに結合される中間配線およびビアと電源電圧VDDに結合される中間配線およびビアとを縦方向において整列して配置することにより、ヒューズ素子防護壁構造のレイアウト面積を低減することができる。

なお、この図43に示すヒューズ素子の構造においても、第1メタル配線層M1の配線がエレクトロマイグレーション耐性が優れている場合には、ヒューズFUを第3メタル配線層の配線で形成し、この図43に示す各配線を、配線層1層分下部にずらせ、第5メタル配線層M5に形成される電源配線を、ヒューズトリミング領域上部を覆うように構成してもよい。

なお、本実施の形態においても、図示してないが、平面視において、ヒューズ素子トリミング領域が、第6メタル配線475により覆われている。ヒューズFUを溶断した場合、ヒューズFUと銅拡散防止膜と層間膜(層間絶縁膜)との接触部であるヒューズFUの角の部分の2箇所を起点として、ヒューズFUの上側にヒューズから離れるようにクラックが発生し、第6メタル配線475にクラックが到達し、このクラック内に銅金属が入り込み、ヒューズFUと第6メタル配線475とが短絡することがある。このとき、ヒューズFUの電位が、第6メタル配線475上の電源電圧VDDとなる。応じて、切断判定回路CJCにより、トリミング不良を検出することが可能となり、不良品として、このチップ(半導体装置)を製品出荷前に検出、除去可能となる。なお、本発明の実施の形態においては、ヒューズFUの細身の直上においてヒューズFUの上側に配置され、かつヒューズFUに最も近いメタル配線は、第6メタル配線475であり、電源電圧VDDが供給されるようなレイアウト構造となる。

[実施の形態7]

図45は、この発明の実施の形態7に従うヒューズ素子の上から見た平面レイアウトを概略的に示す図である。図45において、ヒューズ素子FSの形成領域は、ヒューズFUと、ヒューズFU両端に配置されるパッド/ベッド配線領域500,502とを含む。パッド/ベッド配線領域500および502は、一方がノードND1に接続され、他方が、電源電圧を供給する電源線に結合される。

ヒューズFUの両側に第1の防護壁構造を形成する第1のサブ防護壁構造504Aおよび50Bが配置され、この第1の防護壁構造の外部に、第2の防護壁構造を形成する第2のサブ防護壁構造506A、506Bおよび506Cがコの字形状に連続的に延在して形成される。この第1の防護壁構造504Aおよび504Bが電源電圧VDDを供給する電源線に結合され、第2の防護壁構造を構成する仮想接地電圧VGNDを伝達する仮想接地線に結合される。これらの防護壁構造504A,504Bおよび506A−506Cにより、ヒューズFU溶断時に生成された銅(Cu)原子の熱拡散の経路を遮断する。

このパッド/ベッド配線領域500外部に、さらにグローバル配線領域508が配置される。このグローバル配線領域508は、複数のヒューズ素子に共通に設けられ、また溝形状ビアと協働してヒューズボックス外部に銅原子が熱拡散するのを防止する防護壁構造を実現する。

また、図45においては明確に示していないが、ヒューズFUの上部(ヒューズトリミング領域上部)には、電源配線を用いて銅拡散防護壁が形成される。

図46は、図45に示す線L46−L46に沿った断面構造を概略的に示す図である。図46において、ヒューズ素子は、Pウェル(半導体基板領域)510表面上に形成される。このPウェル510表面に互いに間をおいて不純物領域512x、512a−512dおよび512yが形成される。不純物領域512aおよび512dは、それぞれ隣接するヒューズ素子間で共有される。不純物領域512a−512dにより、1つのヒューズ素子に対する溶断電流供給トランジスタの単位トランジスタのソース/ドレイン不純物領域が形成され、隣接ヒューズ素子の不純物領域512xおよび512yも、それぞれ対応の溶断電流供給トランジスタのドレイン領域を形成するために利用される。

これらの不純物領域514x、512a−512dおよび512yの間の基板領域表面上にゲート電極配線514x、514a−514cおよび514yが配置される。これらの不純物領域およびゲート電極配線により、溶断電流供給単位トランジスタが実現される。

不純物領域512x、512a−512dおよび512yそれぞれに対応して第1メタル配線層M1において第1メタル配線515x、515a−515dおよび515yが配置される。これらの配線はそれぞれ、コンタクト516x、516a−516dおよび516yを介して対応の不純物領域に接続される。

第2メタル配線層M2において、第1メタル配線515x、515a−515dおよび515yに対応してかつ整列して第2メタル配線517x、517a−517dおよび517yが配置される。これらの第2メタル配線517x、517a−517dおよび517yは、それぞれ溝形状の第1ビア518x、518a−518dおよび518yを介して第1メタル配線515x、515a−515dおよび515yに接続される。第2メタル配線517bおよび517cが、ノードND1に結合され、溶断電流供給トランジスタのドレイン不純物領域512bおよび512cに結合される。隣接ヒューズ素子においても、同様、第2メタル配線517xおよび517yが、対応のヒューズの端部が接続されるノードND1を構成し、ドレイン不純物領域512xおよび512yに結合される。

第3メタル配線層M3においては、第2メタル配線517aおよび517dに対応してかつ整列して第3メタル配線519aおよび519bが配置される。これらの第2メタル配線517bおよび517c上には、第3メタル配線は配設されない。第3メタル配線519aおよび519bは、それぞれ溝形状の第2ビア520aおよび520bを介して下層の第2メタル配線517aおよび517dに結合される。

第4メタル配線層M4において、第3メタル配線519aおよび519bに対応してかつ整列して第4メタル配線521および521bが配設される。また、これらの第4メタル配線521aおよび521bの間に、第4メタル配線を用いてヒューズFUが配設される。

第4メタル配線521aおよび521bは、それぞれ溝形状の第3ビア522aおよび522bを介して下層の第3メタル配線519aおよび519bに結合される。

第5メタル配線M5において、第5メタル配線523aおよび523bがそれぞれ第4メタル配線521aおよび521bに対応してかつ整列して配置され、これらの第5メタル配線523aおよび523bの内側に、第5メタル配線524aおよび524bが配置される。第5メタル配線523aおよび523bは、それぞれ、溝形状の第4ビア525aおよび525bを介して第4メタル配線521aおよび521bに結合される。第5メタル配線524aおよび524bは、それぞれ溝形状の第5ビア526aおよび526bを介して第6メタル配線層M6に形成される第6メタル配線528に結合される。

第5メタル配線523aおよび523bは、仮想接地線に結合され、仮想接地電圧VGNDを伝達する。第6メタル配線528は、電源線に結合され電源電圧VDDを伝達する。この第6メタル配線528は、ヒューズFUのトリミング領域529を蔽うように配置され、上部拡散防護壁配線を構成する。第6メタル配線535は、グローバル電源線を構成し、電源電圧VDDを伝達する。ヒューズFU直上部に形成される第6メタル配線528(図46参照)の形状は、これまでの実施の形態と同様、ベタ配線であってもよく、ストライプ形状の配線であってもよい。

第5メタル配線523aから第1メタル配線515aおよび第5メタル配線523bから第1メタル配線515dが縦方向に連続的に配設され、図45に示す第2防護壁構造506Bおよび506Aを、それぞれ構成する。第5メタル配線524aおよび524bと第5ビア526aおよび526bにより、図45に示す第1防護壁構造504Bおよび504Aが形成される。

この図46に示すように、ヒューズFUのトリミング領域529からの破線矢印で示す銅熱拡散経路は、この上層に形成される第5メタル配線524aおよび524bにより遮断される。したがって、ヒューズFUの銅切片からの銅原子が熱拡散により隣接ヒューズへ伝搬するのを確実に抑制することができる。

この図46においても、各配線層の境界領域においては、層間絶縁膜の間に銅拡散防止膜CDPが配置され、層間絶縁膜を介して銅が熱拡散するのは抑制される。また、防護壁構造506Aおよび506Bは、それぞれ隣接するヒューズ素子間で共有され、ヒューズ素子のレイアウト面積を低減することができる。

図47は、図45に示す線L47−L47に沿った断面構造を概略的に示す図である。この図47に示す断面構造において、図46に示す断面構造の対応する構成要素(メタル配線、ビア、不純物領域等)に対しては、同一参照番号を付し、その詳細説明は省略する。

この図47に示す構造においては、図45に示すパッド/ベッド配線領域500において、第4メタル配線層M4において第4メタルパッド/ベッド配線530が配置される。この第4メタルパッド/ベッド配線530は、複数の単位ビア531を介して第5メタル配線層M5に形成されるパッド/ベッド配線532に結合される。この第5メタルパッド/ベッド配線532は、その上層に形成される第6メタル配線層M6のメタル配線535に単位第5ビア533を介して結合される。

第6メタル配線535は、グローバル電源線を構成し、電源電圧VDDを伝達する。ヒューズFU直上部に形成される第6メタル配線528(図46参照)は、ヒューズFUのトリミング領域529が覆われる構造であればよいため、図47においては、第6メタル配線535と第6メタル配線528とは別の参照番号を付しているが、これらは図示しない第6メタル配線により電気的に結合される。

このヒューズ素子FSの端部においても、第4メタル配線層M4において、第4メタル配線521a、パッド/ベッド配線530および第5メタル配線521bが配置されており、このヒューズ素子外部への銅原子の熱拡散経路は遮断される(図47に示す領域においてはヒューズFUは設けられていないが、ヒューズFUと同一メタル配線層M4において、パッド/ベッド配線530が配置されているため)。

図48は、図46に示す線L48−L48に沿った断面構造を概略的に示す図である。この図48に示す断面構造は、以下の点で、図46に示すヒューズ素子の断面構造とその構造が異なる。すなわち、図45に示すパッド/ベッド配線領域502においてヒューズは配置されず、代わりに、ノードND1を構成するパッド/ベッド配線544が第4メタル配線層M4において配置される。パッド/ベッド配線544は、第3メタル配線層M3に配置される第4メタル中間配線540u−540wに単位ビア542を介してそれぞれ結合される。これらの第4メタル中間配線540u−540wは、第2メタル配線層M2に配置される第2メタル配線517b−517cそれぞれに対応して配置され、それぞれ単位ビア541u−540wを介して対応の第2メタル配線に結合される。このヒューズ素子FS形成領域内においては、溶断電流供給トランジスタが複数の単位トランジスタで形成され、各単位トランジスタのドレイン電極に対応して第3メタル中間配線540(540u−540w)が配置される。図48においては、この単位トランジスタが多く形成されることを示すために、第2メタル配線層M2における第2メタル配線517b、517cよりも多くの第4メタル中間配線540が配置されるように示す。

この図48に示すヒューズ素子の断面構造の他の構造は、図46に示すヒューズ素子の断面構造と同じであり、対応する部分には同一参照番号を付しその詳細説明は省略する。

図48に示すヒューズ素子FSの構造においても、ヒューズが形成される第4メタル配線層M4と同一配線層にパッド/ベッド配線544が形成され、その上部に第5メタル配線523a、523b、524aおよび524bが配置されおり、ヒューズ終端部においても、溝形状ビア525a,525b、526aおよび526bにより、隙間のない防護壁構造が形成されており、ヒューズボックス外部への銅の熱拡散経路を遮断することができる。

また、図46から図48に示すように、隣接ヒューズ素子で第1の防護壁構造を共有しており、また、その内部に第2の防護壁を第5メタル配線層に形成しており、確実に、銅の熱拡散が隣接ヒューズ素子へ生じる経路を遮断することができるとともに、ヒューズ素子の占有面積を低減することができる。

図49は、この図45から図48に示すヒューズ素子の第2メタル配線層の配線レイアウトを概略的に示す図である。この図49において線L46−L46に沿って切断すると図46に示す断面構造の第2メタル配線層の配置が得られ、線L48−L48に沿って切断すると図48に示す第2メタル配線層下部の断面構造が得られる。ヒューズ素子FSiは、ヒューズボックス内において端部以外の位置に配設される。

溶断電流供給トランジスタを構成する単位トランジスタの数が、溶断電流供給トランジスタの電流駆動力に応じて決定されるため、図46から図48に示す溶断電流供給トランジスタのソースおよびドレインノードを構成する第2メタル配線層の配線の数が、図49に示すソース/ドレインノードの第2メタル配線の数と異なる。したがって、この図46から図48の断面構造に示されていない第2メタル配線について、仮想接地線に結合される第2メタル配線を符号517gで示し、ノードND1に結合される第2メタル配線を符号517nで示す。

図49において、第2メタル配線517aおよび517dが、縦方向に連続的に延在してヒューズ素子形成領域内に配置される。第2メタル配線517aおよび517d上に矩形形状の第2ビア520aおよび520bが連続的に縦方向に延在して形成される。この第2メタル配線517aおよび517dに対し、横方向に連続的に延在する第2メタル配線550が形成され、また、この第2メタル配線550表面に横方向に延在する溝形状第2ビア551が形成される。溝形状第2ビア520aおよび520bが溝形状第2ビア551に結合され、また、第2メタル配線517a、517dおよび517gが、第2メタル配線550に結合される。第2メタル配線517gは、溶断電流供給トランジスタの単位トランジスタのソース電極を構成するため、これらの第2メタル配線517g上にはビアは、形成されない。第2メタル配線550は、仮想接地線に結合され、下層接地電圧VGNDを伝達する。

第2メタル配線517bおよび517cが、縦方向に延在して形成され、その端部においてビア541uおよび541wが形成される。同様、第2メタル配線517nにおいても、その端部において単位第2ビア541vが形成される。第2メタル配線517b、517cおよび517nと第2メタル配線517gとは交互に配設される。

この第2メタル配線配置領域外部のグローバル配線領域508に、横方向に連続的に延在する第2メタル配線552が形成され、第2メタル配線552表面上に溝形状第2ビア553が形成される。これらの配線552およびビア553は、電源電圧VDDを伝達する。

図50は、このヒューズ素子FSiが配列されるヒューズボックスの端部のヒューズ素子FSnの平面レイアウトを概略的に示す図である。図50において、ヒューズボックス端部において、第2メタル配線554および溝形状第2ビア555が縦方向に延在して形成される。第2メタル配線554が第2メタル配線552に結合され、溝形状第2ビア555が第2ビア553に結合される。この図50に示すヒューズ素子FSnの他の構成は図49に示すヒューズ素子FSiの構成と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

図49および図50に示すように、第2メタル配線層M2において、破線矢印で示すように、トリミング領域529からの銅の熱伝搬経路はすべて遮断され、特にヒューズボックス外部への銅の熱拡散経路は確実に遮断される。また、第2メタル配線層において溝形状第2ビア520aおよび520bに沿って銅の熱拡散経路が破線矢印で示すように存在するものの、この経路長は、銅の熱拡散距離より十分長く、隣接ヒューズ素子への銅の熱拡散は確実に抑制される。

図51は、図45から図48に示すヒューズ素子の第3メタル配線層M3の配線レイアウトを概略的に示す図である。図51においても、図46および図48に示す断面構造の切断線L46−L46およびL48−L48を併せて示す。

図51において、第3メタル配線519aおよび519bが縦方向に延在して形成され、これらの第3メタル配線519aおよび519b表面上に溝形状第3ビア522aおよび522bが連続的に縦方向に延在して形成される。これらの第3メタル配線519aおよび519bの間に矩形形状の第3メタル中間配線540が配置される。この第3メタル中間配線540は、図48に示す第3メタル中間配線540u,540vおよび540wに対応し、それぞれ第3ビア542が設けられる。この第3メタル中間配線540は、図49に示す第2メタル配線517b,517cおよび517nにそれぞれビア541v,541uおよび541wを介して結合される。この第3メタル中間配線は、下層の第2メタル配線それぞれに対応して分離されて配置されてもよい(配線540u、540v、540w個々に配設してもよい)。ここでは、図面を簡略化するため、矩形形状の中間配線540を示す。

第3メタル配線519aおよび519bに対応して横方向に連続的に延在して第3メタル配線560が形成され、この第3メタル配線560表面に、溝形状第3ビア561が形成される。第3メタル配線519aおよび519bが、第3メタル配線560に結合され、第3ビア522aおよび522bが第3ビア561に結合される。この第3メタル配線560は、仮想接地線に結合され、下層接地電圧VGNDを伝達する。

グローバル配線領域508において、横方向に連続的に延在して第3メタル配線562が配設され、この第3メタル配線562表面上に横方向に連続的に延在する溝形状第3ビア563が配設される。この第3メタル配線560は、電源電圧VDDを伝達する。

図52は、このヒューズボックスにおける端部に配置されるヒューズFSnの第3メタル配線層の配置を概略的に示す図である。このヒューズ素子FSnにおいては、ヒューズボックス端部においてさらに、第3メタル配線564が縦方向に延在して形成され、またこの第3メタル配線564表面上に溝形状第3ビア565が形成される。第3メタル配線564は、ヒューズ素子列に対してヒューズボックス内に連続的に延在して形成される第3メタル配線563に結合され、また、第3ビア565が、第3メタル配線562上に形成される溝形状第3ビア563に結合される。

この第3メタル配線560は、図49および図50に示す第2メタル配線550に溝形状の第2ビアを介して結合され、第3メタル配線562が、図49および図50に示す第2メタル配線552に第2ビア553を介して結合される。