(実施の形態1)

本実施の形態では、本発明の一態様である機能回路の設計システムについて説明する。

まず本実施の形態における機能回路の設計システムについて図1を用いて説明する。図1は、本実施の形態における機能回路の設計システムの構成を示すブロック図である。

図1に示すように、本実施の形態における機能回路の設計システムは、階層化手段101と、第1の論理合成手段102と、第1の配置配線手段103と、第1の置換手段104と、第2の論理合成手段105と、第2の配置配線手段106と、計算手段107と、第2の置換手段108と、を有する。なお、それぞれの手段は、例えばプログラムにより構成することができる。

階層化手段101は、RTL記述109(第1の記述ともいう)のうち、同期の単位回路を示す記述(第2の記述ともいう)をブロック化し、ブロック化した第2の記述を一つの階層としてRTL記述109を階層化されたRTL記述(第3の記述ともいう)に変換する手段である。なお階層化とは、ある回路を示す記述が複数の階層からなる記述に変換されることをいう。具体的には、RTL記述109から指定回路情報110に相当する記述を検索し、指定回路情報110に相当するRTL記述をブロック化し、ブロック化された記述を一つの階層としてRTL記述109を階層化されたRTL記述に変換する。

なお、階層化されたRTL記述はRTL記述109と同一の回路機能を表現しており、さらに階層化されたRTL記述は、上位階層の記述と下位階層の記述に分類される。下位階層の記述はブロック化された第2の記述で構成され、上位階層の記述は下位階層の記述と、その他の回路を示す記述と、下位階層の記述とその他の回路を示す記述との接続関係の記述とで構成される。例えば図2に示すように、上位階層として機能回路201を示す記述がある場合、機能回路201を示す記述のうち、単位回路2021及び単位回路2022を示す記述がブロック化され、それぞれ回路ブロックとして表された単位回路2021及び単位回路2022を示す記述が下位階層の記述となる。なお、本実施の形態において上位階層の記述は、特に指定がなければ機能回路201を示す記述のことをいい、下位階層の記述は、特に指定がなければ単位回路2021及び単位回路2022を示す記述のことをいう。

RTL記述109は、同期回路の設計手法に適したIEEE規格のRTL記述によって回路を表現した記述である。またRTL記述109で表現された回路は、全回路がグローバル・クロックによって駆動するものである。RTL記述109によって表現される回路としては、例えばCPU、画像処理回路、またはメモリなどがあり、これらの回路は一般的にカウンター回路やセレクター回路などの回路の集合体によって構成されている。本書類では、CPU、画像処理回路、またはメモリを示す記述は上位階層の記述であり、カウンター回路またはセレクター回路を示す記述は下位階層の記述である。

指定回路情報110は、RTL記述109から抽出される記述によって示される特定の単位回路(例えば同期式カウンター回路)と同じ回路を示す情報である。なお、指定回路情報110は、階層化手段101を用いてRTL記述109から、指定された回路に該当する箇所を抽出するためのものであるため、指定回路情報110のフォーマットは階層化手段101に対応して設定されることが好ましい。例えば、階層化手段101において、RTL記述109における指定回路情報110の対応箇所をキーワードで検索する場合、指定回路情報110はキーワードにより特定の単位回路を表すというフォーマットになる。

第1の論理合成手段102は、階層化手段101により階層化されたRTL記述の論理合成を行い、ゲートレベルのネットリスト(第1のネットリストともいう)を生成する手段である。論理合成には、チップ面積若しくは遅延時間などの制約条件、または半導体製造技術のライブラリのセルなども用いられる。また、論理合成ツールとしては、例えばCadence Design Systems社製のBuild Gatesなどを用いることができる。

第1の配置配線手段103は、第1の論理合成手段102で生成されたネットリストをもとに配置配線を行い、ゲートレベルのネットリストを生成する手段である。なお、配置配線とは、ネットリストをもとに2次元平面上に回路の配置を行い、さらに2次元平面上で配線を行うことをいう。なお配置配線にはチップ面積、遅延時間などの制約条件や半導体製造技術のライブラリのセルなどを用いることがある。また、第1の配置配線手段103ではタイミング検証も併せて行われ、セットアップ時間やホールド時間などのタイミング情報が第2の置換手段108に出力される。タイミング検証は従来のタイミング検証だけではなく、例えば下位階層の記述に相当する単位回路を構成する回路の素子間に加え、下位階層の記述に相当する単位回路を1つの組み合わせ回路と見なしたタイミング検証も同時に行い、下位階層の記述に相当する単位回路の入出力端子のタイミング情報も第2の置換手段108に出力する。なお、下位階層の記述に相当する単位回路における入出力端子のタイミング情報とは、特に断りがない限りは、順序回路間の遅延情報及び、回路内に負荷されているゲート容量や配線に負荷される寄生容量などのことをいう。

第1の置換手段104は、階層化手段101で階層化された第2の記述を非同期の単位回路を示す記述(第4の記述ともいう)に置換する手段である。なお、第2の記述と第4の記述とは同期回路であるか非同期回路であるかが異なるだけであって表現された回路機能は同一である。

第2の論理合成手段105は、第4の記述の論理合成を行い、ゲートレベルのネットリスト(第2のネットリストともいう)を生成する手段である。論理合成には、チップ面積遅延時間などの制約条件、または半導体製造技術のライブラリのセルなども用いられる。論理合成ツールとしては、例えばCadence Design Systems社製のBuild Gatesなどを用いることができる。

第2の配置配線手段106は、第2の論理合成手段105により生成されたネットリストをもとに配置配線を行う手段である。なお配置配線には、チップ面積及び遅延時間などの制約条件や半導体製造技術のライブラリのセルなども用いることがある。また、第2の配置配線手段106では、配線接続情報やゲート容量や配線に負荷される寄生容量などの回路情報が生成され、計算手段107に出力される。

計算手段107は、シミュレーション手段ともいい、第2の配置配線手段106から入力された配線接続情報やゲート容量や配線に負荷される寄生容量などの回路情報と第2の配置配線手段106から入力されたネットリストを用いてspiceなどの回路シミュレーターで計算(シミュレーションともいう)を行う手段である。その際の計算条件として、例えば入力信号の組み合わせ、入力信号の立ち上がりまたは立ち下がりの傾き、又は出力端の負荷容量を変えて計算を行う。例えば、入力信号の値の組み合わせを4条件、入力信号の立ち上がりまたは立ち下がりの傾きを5条件、出力端の負荷容量を5条件としたとき、計算は4×5×5、すなわち100回行う。この計算により、入力されたネットリストに対する遅延情報が得られ、その結果をデータテーブルとしてファイルに出力する。また、計算手段107では第2の配置配線手段106で行わなかったタイミング検証の代わりにタイミング検証が行われる。タイミング検証とは、動的タイミング検証と静的タイミング検証とに大きく分けられる。

ここで動的タイミング検証と静的タイミング検証の違いについて説明する。動的タイミング検証とは、実際に回路にテストパターンを入力して計算し、その出力状況から回路の動作に異常がないかを確認し、異常がある場合は、適切な動作になるように修正する検証である。

一方、静的タイミング検証とは、配線接続情報やゲート容量や配線に負荷される寄生容量などの回路情報のみから基準となるクロック信号とデータの遅延関係に異常がないかを確認し、異常がある場合は、適切な遅延関係になるように修正する検証である。なお、本明細書中に記載されているタイミング検証とは、特に断りがなければ、静的タイミング検証のことを指す。同期回路の場合は、順序回路間のクリティカルパスの遅延値を計算して、その遅延値と基準となるクロック信号のタイミング(例えば、クロック信号の周期やクロック信号の遅延などを基にした時間)により検証が可能であるので、静的タイミング検証が可能である。しかしながら、非同期回路の場合は基準となるクロック信号が全ての順序回路に供給されていない場合があるので、順序回路間のクリティカルパスの遅延値を計算して、その遅延値と基準となるクロック信号のタイミングにより検証はできない。したがって、非同期回路には動的なタイミング検証が必要となり、計算手段107では、タイミング検証として動的タイミング検証が行われる。なお、計算手段107の一部として市販のセルキャラクタライズツールが用いられる。セルキャラクタライズツールとしては、例えばSILVACO社製のAccuCellなどを用いることができる。

第2の置換手段108は、計算手段107での計算結果をもとに第1の配置配線手段103で配置された回路の一部、例えば下位階層の単位回路のいずれかを選択的に第2の配置配線手段106で配置された回路に置換する手段である。さらに、第2の置換手段108では、置換が完了したレイアウトで再度タイミング検証が行われる。

次に上記設計システムによる機能回路の設計方法について図3を用いて説明する。図3は、本実施の形態における設計システムによる設計方法を示すフローチャートである。

図3に示すように、まず第1のステップ(図3におけるS1)として階層化手段101により階層化処理が行われる。階層化処理では、RTL記述109のうち、指定回路情報110に記載された特定の単位回路に相当する記述がブロック化され、ブロック化された記述を一つの階層として、RTL記述109が階層化されたRTL記述に変換される。

階層化処理後、階層化されたRTL記述を用いた処理と、下位階層の記述であるブロック化された単位回路を示す記述を用いた処理との2通りの処理が行われる。それぞれの処理について以下に説明する。

階層化されたRTL記述を用いた処理については、階層化処理の次に第2のステップ(図3におけるS2)として、第1の論理合成手段102により論理合成処理が行われる。論理合成処理について図4を用いて具体的に説明する。

図4に示すように、まずステップ1(図4におけるS2−1)として論理回路が生成される。ここでは入力されたRTL記述109から、ステートマシンの状態コードの割り当て、フリップフロップの割り付け、及び組み合わせ論理の生成などが行われることによりゲートレベルの論理回路が生成される。

次にステップ2(図4におけるS2−2)として半導体製造プロセスに依存しない範囲で論理の最適化が行われる。具体的には指定した制約条件を満たすように論理ゲート数(チップ面積)と論理段数(遅延時間)などが調整される。例えば、a+a×b=aのようなブール代数の性質を用いた冗長論理の削除、f=(a+b)×(c+d)のような論理をf=a×c+a×d+b×c+b×dのように展開する論理の展開、またはf=a×c+a×d+b×c+b×dのような論理をf=(a+b)×(c+d)のようにする論理の多段化などが行われる。なお、a、b、c、d、及びfはそれぞれ集合を表す。

さらにステップ3(図4におけるS2−3)として全体の論理機能を変えることなく論理の再構成が必要か否か判断される。論理の再構成とは、機能は同じだが構成の異なる論理へ置き換えることをいい、基準となるクロック信号とデータの遅延関係を表すパラメータを所定の値に収束させるためや、回路規模縮小のために行われる。必要であると判断された場合には、ステップ5(図4におけるS2−5)として論理の再構成が行われる。

最後に、ステップ4(図4におけるS2−4)として準備した半導体製造技術のライブラリのセルへのマッピングが行われる。すなわち、論理(ゲート)や順序回路が、準備した半導体製造技術のライブラリのマクロセルに置き換わる。以上の工程をもってゲートレベルのネットリストが生成される。なお、論理合成処理において階層化手段101により階層化されたRTL記述は階層を有したまま保持される。以上が論理合成処理である。

次に第3のステップ(図3におけるS3)として、第1の配置配線手段103により第1の配置配線処理が行われる。第1の配置配線処理について図5を用いて具体的に説明する。図5は本実施の形態における第1の配線処理を示すフローチャート図である。

図5に示すように、まずステップ1(図5におけるS3−1)として第1の論理合成手段102により生成されたゲートレベルのネットリスト、並びにチップ面積及び遅延時間などの制約条件や半導体製造技術のライブラリのセルなどを用いてレイアウトが作成され、ゲートレベルのネットリストが生成される。

次にステップ2(図5におけるS3−2)として、配線接続情報やゲート容量や配線に負荷される寄生容量などの回路データが第2の置換手段108に出力される。

次にステップ3(図5におけるS3−3)としてタイミング検証が行われ、ステップ4(図5におけるS3−4)として機能回路を構成するそれぞれの回路のセットアップ時間やホールド時間などのタイミング情報が第2の置換手段108に出力される。なお、第1の配置配線処理におけるタイミング検証は、従来のタイミング検証だけではなく、例えば下位階層の記述に相当する単位回路を構成する順序回路の素子間に加え、単位回路を1つの組み合わせ回路と見なしたタイミング検証も同時に行われ、単位回路における入出力端子のタイミング情報も第2の置換手段108に出力される。なお、タイミング情報は以下のように出力される。

まず生成されたネットリストを用いて各素子(論理ゲートまたはトランジスタ)の遅延時間情報と配線遅延時間情報をもとに対象回路に相当するグラフが作成される。そして、このグラフから最大遅延時間のパスや最小遅延時間のパスなどが抽出され、併せて当該パスの最大遅延時間や最小遅延時間からタイミング情報が生成される。ここでのグラフとはグラフ理論のグラフをいい、各素子(論理ゲートまたはトランジスタ)のつながり方に着目して抽象化された点とそれを結ぶ線を概念化したものをいう。

以上が第1の配置配線処理である。なお、第1の配置配線処理において、階層化手段による階層化は維持される。また、下位階層の単位回路内の素子同士は、できるだけ近い位置に配置されることが好ましい。

一方、階層化されたRTL記述のうち、下位階層の記述であるブロック化された単位回路を示す記述を用いる処理については、階層化処理の次に第2のステップ(図3におけるS4)として第1の置換処理が行われる。第1の置換処理について以下に説明する。

第1の置換処理では、ブロック化された単位回路を示す記述が、別途作成された非同期の単位回路を示す記述に置換される。このとき別途作成された非同期の単位回路を示す記述と、置換されるブロック化された単位回路を示す記述は同一機能を表す。なお、非同期の単位回路を示す記述は、第1の置換処理時に作成することもでき、また階層化処理の際に用いられる指定回路情報110に予め記載しておき、第1の置換処理時に用いることもできる。以上が第1の置換処理である。

次に第3のステップ(図3におけるS5)として第2の論理合成手段105により非同期の単位回路を示す記述の論理合成処理が行われ、ゲートレベルのネットリストが生成される。論理合成処理の具体的な説明については、上記第2のステップS2における論理合成処理と同じであるため、第2のステップS2における論理合成処理の説明を援用する。

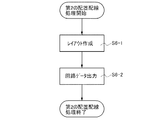

次に第4のステップ(図3におけるS6)として第2の配置配線手段106により第2の配置配線処理が行われる。第2の配置配線処理について図6を用いて具体的に説明する。図6は、本実施の形態における第2の配置配線処理を示すフローチャートである。

図6に示すように、まずステップ1(図6におけるS6−1)として第2の論理合成手段105により生成されたネットリスト、チップ面積、遅延時間などの制約条件、及び半導体製造技術のライブラリのセルなどを用いてレイアウトが作成され、ゲートレベルのネットリストが生成される。

次にステップ2(図6におけるS6−2)として、配線接続情報やゲート容量や配線に負荷される寄生容量などの回路データが計算手段107に出力される。以上が第2の配置配線処理である。

次に第5のステップ(図3におけるS7)として、計算手段107により計算処理が行われる。計算処理では、第2の配置配線手段106から入力された配線接続情報やゲート容量や配線に負荷される寄生容量などの回路情報と第2の配置配線手段106から入力されたネットリストを使用して計算が行われる。この計算により、入力されたネットリストに対する遅延情報が得られ、その結果がデータテーブルとしてファイルに出力される。さらに計算手段107ではタイミング検証が行われる。

第1の配置配線処理及び計算処理が終了したら次のステップ(図3におけるS8)として第2の置換手段108により第2の置換処理が行われる。第2の置換処理について図7を用いて具体的に説明する。図7は本実施の形態における第2の置換手段を示すフローチャートである。

図7に示すように、まずステップ1(図7におけるS8−1)として、計算手段107で得られた出力遅延情報と、第1の配置配線手段103から入力された下位階層の単位回路の入出力端子のタイミング情報をもとに第1の配置配線手段103で配置された下位階層の記述に対応する回路いずれかが選択的に第2の配置配線手段106で配置された非同期の単位回路を示す記述に対応する回路にレイアウト上で置換される。

次にステップ2(図7におけるS8−2)として置換が完了したレイアウトで再度タイミング検証を行う。さらにステップ3(図7におけるS8−3)としてセットアップ時間やホールド時間などが所望のタイミング仕様に合致しているかどうかを調べ、合致しているようなら設計完了となる。なお、タイミング仕様は、タイミング検証の合否判定に使われる値になる。また、合致していない場合は、ステップ4(図7におけるS8−4)として適切に修正される。以上が第2の置換処理である。

上記のように、本発明の一態様である機能回路の設計システムでは、配置配線後に選択的に同期回路が自動的に非同期化されるため、タイミング検証をパスできない場合でも修正が容易であり、設計時間のロスを抑え、設計効率の低下を抑えることができる。また、同期回路を選択的に非同期化するという簡易な方法で回路規模が小さく、また消費電力の小さい機能回路を設計することができる。

(実施の形態2)

本実施の形態では、本発明の一態様である機能回路の設計システムまたは機能回路の設計方法により設計可能な回路を備えたデバイスの例として、半導体装置について説明する。

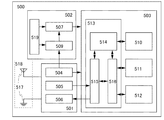

本実施の形態における半導体装置の構成について図8を用いて説明する。図8は、本実施の形態における半導体装置の構成を示すブロック図である。

図8に示すように、半導体装置500は、RF回路501、クロック信号生成回路502、ロジック回路503、及びアンテナ部518におけるアンテナ517により構成されている。なお、図8には示していないが、半導体装置500は、無線通信装置(リーダライタ、または質問器など、無線により通信が可能なもの)などの外部の回路とアンテナ517を介して無線信号の送受信を行っている。なお、データの伝送形式は、一対のコイルを対向配置して相互誘導によって交信を行う電磁結合方式、誘導電磁界によって交信する電磁誘導方式、電波を利用して交信する電波方式の3つに大別され、本実施の形態ではいずれの方式でも適用することができる。

次に各回路の構成について説明する。RF回路501は電源回路504と、復調回路505と、変調回路506と、を有する。また、クロック信号生成回路502は、分周回路507と、カウンター回路509と、基準クロック信号生成回路519と、を有する。また、ロジック回路503は、演算処理を行う機能を有し、コントローラ513と、CPU(中央演算回路ともいう)510と、ROM(Read Only Memory)511と、RAM(Random Access Memory)512と、を有する。

また、コントローラ513は、CPUインターフェース514と、RFインターフェース515と、メモリコントローラ516と、を有する。

また、RF回路501において、電源回路504は、整流回路と、保持容量と、を有し、受信した信号から電源電圧を生成し、その他の回路に供給する機能を有する。また復調回路505は、整流回路と、LPF(ローパスフィルタ)と、を有し、通信信号からコマンドやデータを抽出する機能を有する。変調回路506は、送信データを変調する機能を有し、変調されたデータは、アンテナ517から送信信号として送信される。

次に本実施の形態における半導体装置の動作について説明する。まず、外部の通信装置から送信された信号が半導体装置で受信される。半導体装置に入力された受信信号は、復調回路505で復調された後、コントローラ513におけるRFインターフェース515に出力される。RFインターフェース515に入力された受信信号は、CPUインターフェース514を介してCPU510で演算処理される。また、RFインターフェース515に入力された受信信号により、メモリコントローラ516を介してROM511、RAM512に対するアクセスが行われる。

そして、CPU510による演算処理、ROM511、RAM512におけるデータの入出力後に送信データが生成され、送信データは、信号として変調回路506で変調され、アンテナ517から外部の通信装置に送信される。

本発明の一態様である機能回路の設計システムまたは機能回路の設計方法は、上記半導体装置のロジック回路などの設計に好適である。本発明の一態様である機能回路の設計システムまたは機能回路の設計方法を用いることにより回路規模が小さく、消費電力の低いロジック回路を設計することができる。

さらに上記半導体装置は、様々な用途で使用される。上記半導体装置の使用例について図9を用いて説明する。図9は半導体装置の使用例を示す模式図である。

図9に示すように、半導体装置の用途は広範囲にわたるが、例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類(運転免許証や住民票など、図9(A)参照)、包装用容器類(包装紙やボトルなど、図9(C)参照)、記録媒体(DVDソフトやビデオテープなど、図9(B)参照)、乗り物類(自転車など、図9(D)参照)、身の回り品(鞄や眼鏡など)、食品類、植物類、動物類、人体、衣類、生活用品類、または電子機器(液晶表示装置、EL表示装置、テレビジョン装置、または携帯電話)などの物品、若しくは各物品に取り付ける荷札(図9(E)、図9(F)参照)などに設けて使用することができる。

半導体装置600は、プリント基板に実装、表面に貼る、または埋め込むことにより、物品に固定される。例えば、本であれば紙に埋め込む、または有機樹脂からなるパッケージであれば当該有機樹脂に埋め込み、各物品に固定される。半導体装置600は、小型、薄型、軽量を実現するため、物品に固定した後もその物品自体のデザイン性を損なうことがない。また、紙幣、硬貨、有価証券類、無記名債券類、または証書類などに半導体装置600を設けることにより、認証機能を設けることができ、この認証機能を活用すれば、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、または電子機器などに半導体装置を取り付けることにより、検品システムなどのシステムの効率化を図ることができる。また、乗り物類であっても、半導体装置を取り付けることにより、盗難などに対するセキュリティ性を高めることができる。

以上のように、本発明の一態様により設計した回路を備えた半導体装置は、消費電力を少なくでき、また回路面積を小さくできるため、上記のような硬貨などの小型のものから、電子機器などの大型のものまで、大きさに限定されずに各用途に用いることができる。また、各用途に用いることにより、情報のやりとりに用いられるデータを正確の値のまま維持することができるため、物品の認証性、またはセキュリティ性の信頼性を高めることができる。

なお、本実施の形態は、他の実施の形態と適宜組み合わせることができる。

(実施の形態3)

本実施の形態では、本発明の一態様である機能回路の設計システムまたは機能回路の設計方法により設計可能な回路を備えたデバイスの一例として、表示装置について説明する。

まず本実施の形態における表示装置の構成について図10を用いて説明する。図10は、本実施の形態における表示装置の構成を示すブロック図である。

図10に示すように、本実施の形態における表示装置は、画素部701と、走査線駆動回路702と、信号線駆動回路703と、を有する。

画素部701は、複数の画素704を有し、複数の画素704が行列方向に複数存在する、いわゆるドットマトリクス構造である。それぞれの画素は走査線(図示せず)を介して走査線駆動回路702に電気的に接続され、信号線(図示せず)を介して信号線駆動回路703に電気的に接続される。

走査線駆動回路702は、データを書き込む画素704を選択する回路であり、走査線を介して選択信号を画素に出力する。

信号線駆動回路703は、画素704に書き込むデータを信号として出力する回路であり、信号線を介して走査線駆動回路702により選択された画素704にデータ信号を出力する。

次に本実施の形態における表示装置の走査線駆動回路及び信号線駆動回路の構成の一例について説明する。

まず走査線駆動回路の構成の一例について図11(A)を用いて説明する。図11(A)は、本実施の形態のおける表示装置の走査線駆動回路の構成の一例を示すブロック図である。

図11(A)に示すように図10における走査線駆動回路702は、シフトレジスタ800、レベルシフタ801、バッファ802と、を有する。

シフトレジスタ800にはゲートスタートパルス(GSP)、ゲートクロック信号(GCK)などの信号が入力される。

次に信号線駆動回路の構成の一例について図11(B)を用いて説明する。図11(B)は本実施の形態における表示装置の信号線駆動回路の構成の一例を示す断面図である。

図11(B)に示すように図10における信号線駆動回路703は、シフトレジスタ803、第1のラッチ回路804、第2のラッチ回路805、レベルシフタ806、バッファ807と、を有する。

バッファ807は、信号を増幅させる機能を有し、オペアンプなどを有する。シフトレジスタ803には、スタートパルス(SSP)などの信号が入力され、第1のラッチ回路804にはビデオ信号などのデータ(DATA)が入力される。第2のラッチ回路805にはラッチ(LAT)信号を一時保持することができ、保持されたラッチ信号を一斉に図10における画素部701に出力させる。これを線順次駆動と呼ぶ。そのため、線順次駆動ではなく、点順次駆動を行う画素であれば、第2のラッチ回路805は不要とすることができる。

本発明の一態様は、上記シフトレジスタ800などの設計に好適である。本発明の一態様を用いることにより設計が容易になる。

また、上記表示装置は様々な電子機器の表示部に用いることができる。上記表示装置を搭載した電子機器の具体例について図12を用いて説明する。図12は、本実施の形態における電子機器の構成を示す図である。

図12(A)はディスプレイ装置であり、筐体901、支持台902、表示部903、スピーカー部904、ビデオ入力端子905などを含む。上記表示装置は、表示部903に用いることができる。なお、ディスプレイ装置は、パーソナルコンピュータ用、TV放送受信用、広告表示用などの全てのディスプレイ装置が含まれる。

図12(B)はデジタルスチルカメラであり、本体911、表示部912、受像部913、操作キー914、外部接続ポート915、シャッターボタン916などを含む。上記表示装置は、表示部912に用いることができる。

図12(C)はノート型パーソナルコンピュータであり、本体921、筐体922、表示部923、キーボード924、外部接続ポート925、ポインティングデバイス926などを含む。上記表示装置は、表示部923に用いることができる。

図12(D)はモバイルコンピュータであり、本体931、表示部932、スイッチ933、操作キー934、赤外線ポート935などを含む。上記表示装置は、表示部932に用いることができる。

図12(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)であり、本体941、筐体942、表示部A943、表示部B944、記録媒体(DVDなど)読込部945、操作キー946、スピーカー部947などを含む。表示部A943は主として画像情報を表示し、表示部B944は主として文字情報を表示するが、上記表示装置は、これら表示部A943、表示部B944に用いることができる。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。

図12(F)はゴーグル型ディスプレイ(ヘッドマウントディスプレイ)であり、本体951、表示部952、アーム部953を含む。上記表示装置は、表示部952に用いることができる。

図12(G)はビデオカメラであり、本体961、表示部962、筐体963、外部接続ポート964、リモコン受信部965、受像部966、バッテリー967、音声入力部968、操作キー969、及び接眼部970などを含む。上記表示装置は、表示部962に用いることができる。

図12(H)は携帯電話であり、本体971、筐体972、表示部973、音声入力部974、音声出力部975、操作キー976、外部接続ポート977、アンテナ978などを含む。上記表示装置は、表示部973に用いることができる。なお、表示部973は黒色の背景に白色の文字を表示することにより携帯電話の消費電流を抑えることができる。

以上のように、上記表示装置は、上記のような様々な電子機器の表示部として適用することができる。本発明の一態様により設計した回路を備えた表示装置を表示部として用いることにより、回路面積が小さく、消費電力の小さい電子機器を提供することができる。

なお、本実施の形態は、他の実施の形態と適宜組み合わせることができる。

本実施例では、本発明の一態様である機能回路の設計システムを用いた、カウンター回路を備えた機能回路の設計について説明する。

本実施例におけるカウンター回路を備えた機能回路設計について説明する。なお説明には、図3乃至図7の説明を適宜援用する。

まず階層化手段101を実行し、RTL記述109及び指定回路情報110を用いて階層化処理を行う。このときRTL記述109は、第1の同期式2bitカウンター回路を示す記述と、第2の同期式2bitカウンター回路を示す記述と、その他同期式単位回路を示す記述と、を有し、指定回路情報110を同期式2bitカウンター回路が選択される記載にする。階層化処理により、RTL記述109は第1の同期式2bitカウンター回路を示す記述と、第2の同期式2bitカウンター回路を示す記述と、その他の同期式単位回路を示す記述とがブロック化され、ブロック化された第1の同期式2bitカウンター回路を示す記述、ブロック化された第2の同期式2bitカウンター回路を示す記述、及びブロック化されたその他の同期式単位回路を示す記述を一つの階層の記述としてRTL記述109が階層化されたRTL記述に変換される。なお、階層化されたRTL記述は、階層化される前のRTL記述109と階層の有無のみ異なり、同一の回路機能を表現している。なお、階層化には第1の同期式2bitカウンター回路を示す記述及び第2の同期式2bitカウンター回路を示す記述により示される下位階層の回路と上位階層の回路とのピン情報が必要になるが、ここではRTL記述109に指定回路情報110に該当する記述があるか検索するときに該ピン情報を取得する。

次に階層化されたRTL記述と、チップ面積、遅延時間などの制約条件と、半導体製造技術のライブラリのセルなどを用いて第1の論理合成手段102を実行し、第1の論理合成処理を行う。第1の論理合成処理により、RTL記述109と機能的に等価なゲートレベルのネットリストが生成され、第1の配置配線手段103に出力される。なお、出力されたネットリストでは、第1の同期式2bitカウンター回路を示す記述と、第2の同期式2bitカウンター回路を示す記述とが下位階層として存在し、階層構造が維持される。

次に第1の論理合成手段102から入力されたネットリストと、チップ面積、遅延時間などの制約条件、及び半導体製造技術のライブラリのセルなどを用いて第1の配置配線手段103を実行し、第1の配置配線処理を行う。このとき第1の配置配線処理により、第1の同期式2bitカウンター回路を構成する素子同士がレイアウト上でできる限り近くの位置になるように配置されることが好ましい。また、同様に、第2の同期式2bitカウンター回路を構成する素子同士も、レイアウト上でできる限り近くの位置になるように配置されることが好ましい。その状態でレイアウトが作成され、さらにゲートレベルのネットリストが生成され、生成されたネットリストが第2の置換手段108に出力される。また、配線接続情報やゲート容量や配線に負荷される寄生容量などの回路情報や、下位階層における各単位回路の入出力端子のタイミング情報も第2の置換手段108に出力される。また、下位階層における各単位回路の入出力端子のタイミング情報には、下位階層における各単位回路の遅延状態と、下位階層における各単位回路の入出力端子に負荷されているゲート容量や配線に負荷される寄生容量などが記載されている。

このとき本実施例では、下位階層における各単位回路の入出力端子のタイミング情報において、第1の同期式2bitカウンター回路の入力端子に接続される前段の順序回路と、第1の同期式2bitカウンター回路の出力端子に接続される後段の順序回路との間に所定の値のタイミングマージンがあるとする。所定の値のタイミングマージンがあるとは、前段の順序回路と後段の順序回路のクロック周期に対して、前段の順序回路から後段の順序回路へと接続されるデータ線の遅延が第2の置換処理において非同期回路に置換可能な範囲内にあることをいう。また、このとき下位階層における各単位回路の入出力端子のタイミング情報において、第2の同期式2bitカウンター回路の入力端子に接続される前段の順序回路と、第2の同期式2bitカウンター回路の出力端子に接続される後段の順序回路との間に所定の値のタイミングマージンはないとする。

また、第1の配置配線手段103により出力された下位階層における各単位回路の入出力端子のタイミング情報に含まれる、下位階層における各単位回路の入出力端子に負荷されているゲート容量や配線に負荷される寄生容量などの出力遅延情報において、第1の同期式2bitカウンター回路に該当する箇所では遅延値が一定の範囲内の値であり、第2の同期式2bitカウンター回路に該当する箇所では遅延値が一定の範囲外の値とする。

次に階層化処理後、ブロック化された1の同期式2bitカウンター回路を示す記述、第2の同期式2bitカウンター回路を示す記述、及びその他の同期式機能回路を示す記述を用いて第1の置換手段104を実行し、第1の置換処理を行う。第1の置換処理により、第1の同期式2bitカウンター回路の記述と、第2の同期式2bitカウンター回路の記述とが非同期式2bitカウンター回路の記述に置換され、ファイルに出力される。

次に第1の置換手段104で作成されたファイルと、チップ面積、遅延時間などの制約条件と、半導体製造技術のライブラリのセルなどを用いて第2の論理合成手段105を実行し、第2の論理合成処理を行う。第2の論理合成処理により、ゲートレベルのネットリストが生成され、生成されたネットリストが第2の配置配線手段106に出力される。

次に第2の論理合成手段105から入力されたネットリストと、チップ面積、遅延時間などの制約条件、及び半導体製造技術のライブラリのセルなどを用いて第2の配置配線手段106を実行し、第2の配置配線処理を行う。第2の配置配線処理により、レイアウトが作成され、さらにゲートレベルのネットリストが生成され、生成されたネットリストが計算手段107に出力される。また、配線接続情報やゲート容量や配線に負荷される寄生容量などの回路情報も計算手段107に出力される。

次に第2の配置配線手段106より出力された回路情報と、第2の配置配線手段106から入力されたネットリストとを使用してspiceなどの回路シミュレーターで計算手段107を実行し、計算処理を行う。計算処理により、入力されたネットリストに対する出力遅延情報が得られ、その結果がデータテーブルとしてファイルに出力される。

次に、第2の置換手段108を実行し、第2の置換処理を行う。第2の置換処理により計算手段107から入力されたファイルをもとに、第1の配置配線手段103で配置された回路のいずれかが選択的に第2の配置配線手段106で配置された非同期回路にレイアウト上で置換される。本実施例では、第1の同期式2bitカウンター回路に該当する箇所では、第1の配置配線手段103から入力された第1の同期式2bitカウンター回路の遅延状態と比べ、遅延値が小さくなっているため、第1の同期式2bitカウンター回路が非同期式の2bitカウンター回路に置換される。一方、第2の同期式2bitカウンター回路に該当する箇所では、第1の配置配線手段103から入力された第2の同期式2bitカウンター回路の遅延状態と比べ、遅延値が大きくなっているため、第2の同期式2bitカウンター回路は非同期式2bitカウンター回路に置換されない。

さらに置換が完了したレイアウトで再度タイミング検証を行い、セットアップ時間やホールド時間などが所望のタイミング仕様に合致しているかどうかを調べ、合致しているようなら設計完了となる。

さらに第2の置換処理後のカウンター回路の構成について図13を用いて説明する。図13はカウンター回路の構成を示す上面図である。なお図13では、便宜のため、順序回路間の組み合わせ回路は省略する。

図13(A)は同期式2bitカウンター回路を示している。同期式カウンター回路1001は、順序回路FF1及び順序回路FF2により構成され、順序回路FF2は、入力端子D2が配線を介して順序回路FF1の出力端子Q1に電気的に接続され、クロック信号入力端子CLK2が配線を介して順序回路FF1のクロック信号入力端子CLK1に電気的に接続され、リセット信号入力端子XR2が配線を介して順序回路FF1のリセット信号入力端子XR1に電気的に接続される。

図13(B)は第2の置換処理後のカウンター回路を示している。カウンター回路1002は、順序回路FF1及び順序回路FF2に構成され、順序回路FF2は、入力端子D2が順序回路FF1の出力端子Q1に配線を介して電気的に接続され、クロック信号入力端子CLK2が順序回路FF1の出力端子D1に配線を介して電気的に接続され、リセット信号入力端子XR2が順序回路FF1のリセット信号入力端子XR1に配線を介して電気的に接続される。

上記のように図13(A)に示す同期式2bitカウンター回路は、第2の置換処理により図13(B)に示す2bitカウンター回路に置換される。さらに図13(B)に示す2bitカウンター回路は非同期式カウンター回路である。

上記のように、本発明の一態様である機能回路の設計システムを用いて非同期式カウンター回路を備えた機能回路を設計することができる。