JP5291874B2 - Semiconductor device, shift register, display device - Google Patents

Semiconductor device, shift register, display device Download PDFInfo

- Publication number

- JP5291874B2 JP5291874B2 JP2006281331A JP2006281331A JP5291874B2 JP 5291874 B2 JP5291874 B2 JP 5291874B2 JP 2006281331 A JP2006281331 A JP 2006281331A JP 2006281331 A JP2006281331 A JP 2006281331A JP 5291874 B2 JP5291874 B2 JP 5291874B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- circuit

- gate

- source

- potential

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C19/00—Digital stores in which the information is moved stepwise, e.g. shift registers

- G11C19/28—Digital stores in which the information is moved stepwise, e.g. shift registers using semiconductor elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0286—Details of a shift registers arranged for use in a driving circuit

Landscapes

- Liquid Crystal Display Device Control (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Control Of El Displays (AREA)

- Semiconductor Integrated Circuits (AREA)

- Liquid Crystal (AREA)

- Shift Register Type Memory (AREA)

Abstract

Description

本発明は、半導体装置に関する。特に、トランジスタを用いて構成されるシフトレジスタに関する。また、当該半導体装置を具備する表示装置、及び当該表示装置を具備する電子機器に関する。 The present invention relates to a semiconductor device. In particular, the present invention relates to a shift register including transistors. In addition, the present invention relates to a display device including the semiconductor device and an electronic device including the display device.

なお、ここでいう半導体装置とは、半導体特性を利用することで機能しうる装置全般を指すものとする。 Note that the semiconductor device here refers to all devices that can function by utilizing semiconductor characteristics.

近年、液晶表示装置や発光装置などの表示装置は、液晶テレビなどの大型表示装置の増加から、活発に開発が進められている。特に絶縁体上に非結晶半導体により形成されたトランジスタを用いて、画素回路、及びシフトレジスタ回路等を含む駆動回路(以下、内部回路)を一体形成する技術は、低消費電力化、低コスト化に大きく貢献するため、活発に開発が進められている。絶縁体上に形成された内部回路は、FPC等を介してコントローラIC等に(以下、外部回路という)と接続され、その動作が制御されている。 In recent years, display devices such as liquid crystal display devices and light-emitting devices have been actively developed due to an increase in large display devices such as liquid crystal televisions. In particular, the technology for integrally forming a driver circuit (hereinafter referred to as an internal circuit) including a pixel circuit and a shift register circuit using a transistor formed of an amorphous semiconductor on an insulator reduces power consumption and costs. In order to make a significant contribution to this, development is actively underway. An internal circuit formed on the insulator is connected to a controller IC or the like (hereinafter referred to as an external circuit) via an FPC or the like, and its operation is controlled.

例えば、非結晶半導体により形成されたNチャネル型トランジスタのみを用いて構成されたシフトレジスタ回路が考案されている(例えば、特許文献1)。しかし、特許文献1に示す回路では、非選択期間にシフトレジスタ回路の出力がフローティングになるため、非選択期間にノイズが発生しているという問題があった。

For example, a shift register circuit configured using only N-channel transistors formed of an amorphous semiconductor has been devised (for example, Patent Document 1). However, the circuit disclosed in

この問題を解決するために、非選択期間にシフトレジスタ回路の出力をフローティングにしないシフトレジスタ回路が考案されている(例えば、非特許文献1)。

非特許文献1では、非選択期間に出力と電源との間に直列に接続したトランジスタを常時オンすることによって、電源電圧を出力している。また、シフトレジスタ回路の動作期間の大部分の期間は非選択期間であるため、トランジスタが非選択期間に常時オンしていれば、シフトレジスタ回路の動作期間の大部分の期間でオンすることになる。

In

しかしながら、非結晶半導体により形成されたトランジスタは、オンする時間、印加する電圧に従って、特性が劣化することが知られている。中でも、しきい値電圧が上昇するしきい値電圧シフトは顕著であり、シフトレジスタ回路における誤動作の大きな原因の1つとなる。 However, it is known that the characteristics of a transistor formed using an amorphous semiconductor are deteriorated according to an ON time and an applied voltage. Among them, the threshold voltage shift in which the threshold voltage rises is remarkable, and is one of the major causes of malfunctions in the shift register circuit.

このような問題点に鑑み、本発明は、非選択期間においてもノイズが少なく、且つトランジスタを常時オンすることのない半導体装置、シフトレジスタ回路、及びこのような半導体装置を具備する表示装置、及び当該表示装置を具備する電子機器を提供することを目的とする。 In view of such problems, the present invention provides a semiconductor device, a shift register circuit, and a display device including such a semiconductor device in which noise is low even in a non-selection period and a transistor is not always turned on, and An object is to provide an electronic device including the display device.

本発明の半導体装置は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタとを有し、第1のトランジスタは、ゲートに第1の信号が入力され、ソース又はドレインの一方に所定の電位が入力され、ソース又はドレインの他方は第2のトランジスタのゲート及び第3のトランジスタのソース又はドレインの一方と接続され、第2のトランジスタは、ソース又はドレインの一方に第2の信号が入力され、ソース又はドレインの他方が出力端子に接続され、第3のトランジスタは、ゲートに第3の信号が入力され、ソース又はドレインの他方に所定の電位が入力され、第4のトランジスタは、ゲートに第3の信号が入力され、ソース又はドレインの一方に所定の電位が入力され、ソース又はドレインの他方が出力端子と接続されている。 The semiconductor device of the present invention includes a first transistor, a second transistor, a third transistor, and a fourth transistor, and the first transistor receives a first signal at its gate, A predetermined potential is input to one of the source and the drain, the other of the source and the drain is connected to one of the gate of the second transistor and the source or the drain of the third transistor, and the second transistor The second signal is input to one side, the other of the source or the drain is connected to the output terminal, the third transistor has the third signal input to the gate, and a predetermined potential is input to the other of the source or the drain In the fourth transistor, the third signal is input to the gate, the predetermined potential is input to one of the source and the drain, and the other of the source and the drain There is connected to the output terminal.

本発明のシフトレジスタは、複数の段からなるシフトレジスタであって、シフトレジスタ回路の各段は、前の段からハイレベルの出力信号が入力されることによってオンして、ハイレベル程度の電位を出力する第1のトランジスタと、第1のトランジスタの出力によってオンして、ソースとドレインのうち一方は第1の信号線と接続され、ソースとドレインのうち他方は次の段の第1のトランジスタと接続されている第2のトランジスタと、前の段からローレベルの出力信号が入力され、第2のトランジスタがブートストラップ動作をしていない期間に、第2のトランジスタのゲートにローレベルの電位を一定期間毎に出力する第1の手段と、前の段からローレベルの出力信号が入力され、第2のトランジスタがブートストラップ動作をしていない期間に、第2のトランジスタのソースとドレインのうち他方にローレベルの電位を一定期間毎に出力する第2の手段とを備えることを特徴としている。 The shift register of the present invention is a shift register having a plurality of stages, and each stage of the shift register circuit is turned on when a high-level output signal is input from the previous stage, and has a potential of about a high level. Is turned on by the output of the first transistor and one of the source and the drain is connected to the first signal line, and the other of the source and the drain is the first of the next stage. A low level output signal is input from the previous stage to the second transistor connected to the transistor, and the low level is applied to the gate of the second transistor during a period in which the second transistor is not performing the bootstrap operation. The first means for outputting the potential at regular intervals and the low level output signal from the previous stage are input, and the second transistor performs the bootstrap operation. The period without, is characterized in that it comprises the other of the source and the drain of the second transistor and a second means for outputting a low-level potential at regular intervals.

本発明のシフトレジスタは、上記構成において、第1の手段と第2の手段は第2の信号線によって制御されることを特徴としている。 The shift register of the present invention is characterized in that, in the above structure, the first means and the second means are controlled by the second signal line.

本発明のシフトレジスタは、上記構成において、第1の手段は第2の信号線がハイレベルのときにローレベルの電位を出力し、第2の信号線がローレベルのときになにも出力しない機能を有するに第3のトランジスタを含む回路構成によって実現することを特徴としている。 In the shift register of the present invention having the above structure, the first means outputs a low level potential when the second signal line is at a high level, and outputs nothing when the second signal line is at a low level. It is characterized by being realized by a circuit configuration including a third transistor having a function that does not.

本発明のシフトレジスタは、上記構成において、第2の手段は第2の信号線がハイレベルのときにローレベルの電位を出力し、第2の信号線がローレベルのときになにも出力しない機能を有するに第4のトランジスタを含む回路構成によって実現することを特徴としている。 In the shift register of the present invention having the above structure, the second means outputs a low-level potential when the second signal line is at a high level, and outputs nothing when the second signal line is at a low level. It is characterized by being realized by a circuit configuration including a fourth transistor having a function that does not.

本発明のシフトレジスタは、上記構成において、第1の手段は次の段の出力信号によって制御され、第2の手段は第2の信号線によって制御されることを特徴としている。 The shift register of the present invention is characterized in that, in the above structure, the first means is controlled by the output signal of the next stage, and the second means is controlled by the second signal line.

本発明のシフトレジスタは、上記構成において、第1の手段は次の段の出力がハイレベルのときにローレベルの電位を出力し、次の段の出力がローレベルのときになにも出力しない機能を有するに第5のトランジスタを含む回路構成によって実現することを特徴としている。 In the shift register of the present invention, the first means outputs a low level potential when the output of the next stage is high level, and outputs nothing when the output of the next stage is low level. It is characterized by being realized by a circuit configuration including a fifth transistor having a function that does not.

本発明のシフトレジスタは、上記構成において、第2の手段は第2の信号線がハイレベルのときにローレベルの電位を出力し、第2の信号線がローレベルのときになにも出力しない機能を有するに第6のトランジスタを含む回路構成によって実現することを特徴としている。 In the shift register of the present invention having the above structure, the second means outputs a low-level potential when the second signal line is at a high level, and outputs nothing when the second signal line is at a low level. It is characterized by being realized by a circuit configuration including a sixth transistor having a function that does not.

本発明のシフトレジスタは、上記構成において、第1の手段は第2の信号線によって制御され、第2の手段は第2の信号線、及び第3の信号線によって制御されることを特徴としている。 The shift register of the present invention is characterized in that, in the above structure, the first means is controlled by the second signal line, and the second means is controlled by the second signal line and the third signal line. Yes.

本発明のシフトレジスタは、上記構成において、第1の手段は次の段の出力がハイレベルのときにローレベルの電位を出力し、次の段の出力がローレベルのときになにも出力しない機能を有するに第7のトランジスタを含む回路構成によって実現することを特徴としている。 In the shift register of the present invention, the first means outputs a low level potential when the output of the next stage is high level, and outputs nothing when the output of the next stage is low level. It is characterized by being realized by a circuit configuration including a seventh transistor having a function that does not.

本発明のシフトレジスタは、上記構成において、第2の手段は第2の信号線がハイレベルのときにローレベルの電位を出力し、第2の信号線がローレベルのときになにも出力しない機能を有するに第8のトランジスタを含む回路構成によって実現することを特徴とするシフトレジスタと、第3の信号線がハイレベルのときにローレベルの電位を出力し、第3の信号線がローレベルのときになにも出力しない機能を有するに第9のトランジスタを含む回路構成によって実現することを特徴とするシフトレジスタとを含む回路構成によって実現することを特徴としている。 In the shift register of the present invention having the above structure, the second means outputs a low-level potential when the second signal line is at a high level, and outputs nothing when the second signal line is at a low level. And a shift register characterized by being realized by a circuit configuration including an eighth transistor having a function that does not function, and outputs a low-level potential when the third signal line is at a high level, and the third signal line It is characterized by being realized by a circuit configuration including a shift register characterized by being realized by a circuit configuration including a ninth transistor having a function of not outputting anything at a low level.

本発明のシフトレジスタは、複数の段からなるシフトレジスタであって、シフトレジスタ回路の各段は、前の段からハイレベルの出力信号が入力されることによってオンして、ハイレベル程度の電位を出力する第1のトランジスタと、第1のトランジスタの出力によってオンして、ソースとドレインのうち一方は第1の信号線と接続され、ソースとドレインのうち他方は次の段の第1のトランジスタと接続されている第2のトランジスタと、前の段からローレベルの出力信号が入力され、第2のトランジスタがブートストラップ動作をしていない期間に、第2のトランジスタのゲートにローレベルの電位を一定期間毎に出力する第1の手段と、第2のトランジスタがブートストラップ動作をしていない期間に、第2のトランジスタのソースとドレインのうち他方にローレベルの電位を出力する第3の手段とを備えることを特徴としている。 The shift register of the present invention is a shift register having a plurality of stages, and each stage of the shift register circuit is turned on when a high-level output signal is input from the previous stage, and has a potential of about a high level. Is turned on by the output of the first transistor and one of the source and the drain is connected to the first signal line, and the other of the source and the drain is the first of the next stage. A low level output signal is input from the previous stage to the second transistor connected to the transistor, and the low level is applied to the gate of the second transistor during a period in which the second transistor is not performing the bootstrap operation. A first means for outputting a potential at regular intervals; and a source of the second transistor during a period when the second transistor is not performing a bootstrap operation. It is characterized in that it comprises a third means for outputting the other to the low-level potential of the rain.

本発明のシフトレジスタは、上記構成において、第1の手段は第2の信号線によって制御され、第3の手段は第1の信号、第2の信号、第3の信号、及び第2のトランジスタのゲートの電位の反転信号によって制御されることを特徴としている。 In the shift register of the invention having the above structure, the first means is controlled by the second signal line, and the third means is the first signal, the second signal, the third signal, and the second transistor. It is characterized in that it is controlled by an inverted signal of the gate potential.

本発明のシフトレジスタは、上記構成において、第1の手段は第2の信号線がハイレベルのときにローレベルの電位を出力し、第2の信号線がローレベルのときになにも出力しない機能を有するに第10のトランジスタを含む回路構成によって実現することを特徴としている。 In the shift register of the present invention having the above structure, the first means outputs a low level potential when the second signal line is at a high level, and outputs nothing when the second signal line is at a low level. It is characterized by being realized by a circuit configuration including a tenth transistor having a function not to perform.

本発明のシフトレジスタは、上記構成において、第2の手段は第2の信号線がハイレベルのときにローレベルの電位を出力し、第2の信号線がローレベルのときになにも出力しない機能を有するに第11のトランジスタと、第3の信号線がハイレベルのときにローレベルの電位を出力し、第2の信号線がローレベルのときになにも出力しない機能を有するに第12のトランジスタと、第2のトランジスタのゲートの電位の反転信号がハイレベルのときに第1の信号線の信号を出力し、第2のトランジスタのゲートの電位の反転信号がローレベルのときになにも出力しない機能を有する第13のトランジスタと、第13のトランジスタが第1の信号線の信号を出力して、第1の信号線がハイレベルのときにローレベルの電位を出力し、第1の信号線がローレベル、及び第13のトランジスタがなにも出力しないときになにも出力しない機能を有する第14のトランジスタとを含む回路構成によって実現することを特徴としている。 In the shift register of the present invention having the above structure, the second means outputs a low-level potential when the second signal line is at a high level, and outputs nothing when the second signal line is at a low level. The eleventh transistor and the third signal line have a function of not outputting a low level potential when the third signal line is at a high level, and the eleventh transistor has a function of not outputting anything when the second signal line is at a low level. When the inverted signal of the gate potential of the twelfth transistor and the second transistor is high level, the signal of the first signal line is output, and when the inverted signal of the gate potential of the second transistor is low level A thirteenth transistor having a function of not outputting anything, and a thirteenth transistor outputs a signal of the first signal line, and outputs a low level potential when the first signal line is at a high level. The first faith Line is characterized by realizing the circuit configuration including a fourteenth transistor having a function that does not output anything when the low level, and the thirteenth transistor does not output anything.

本発明のシフトレジスタは、上記構成において、第2のトランジスタのゲートの電位がハイレベルのときにローレベルの電位を出力し、第2のトランジスタのゲートの電位がローレベルのときになにも出力しない機能を有する第15のトランジスタと、一方の端子がハイレベルの電位と接続され、他方の端子が第14のトランジスタの出力と接続さされている抵抗成分を持つ素子とを含む回路構成によって実現することを特徴としている。 The shift register of the present invention has the above structure, and outputs a low-level potential when the gate potential of the second transistor is high, and does nothing when the gate potential of the second transistor is low. By a circuit configuration including a fifteenth transistor having a function of not outputting and an element having a resistance component in which one terminal is connected to a high-level potential and the other terminal is connected to the output of the fourteenth transistor. It is characterized by realizing.

本発明のシフトレジスタは、上記構成において、抵抗成分を持つ素子はダイオード接続された第16のトランジスタであることを特徴とするシフトレジスタ。 The shift register of the present invention is characterized in that, in the above structure, the element having a resistance component is a sixteenth transistor connected in a diode.

本発明のシフトレジスタは、複数の段からなるシフトレジスタであって、シフトレジスタ回路の各段は、前の段からハイレベルの出力信号が入力されることによってオンして、ハイレベル程度の電位を出力する第1のトランジスタと、第1のトランジスタの出力によってオンして、ソースとドレインのうち一方は第1の信号線と接続され、ソースとドレインのうち他方は次の段の第1のトランジスタと接続されている第2のトランジスタと、前の段からローレベルの出力信号が入力され、第2のトランジスタがブートストラップ動作をしていない期間に、第2のトランジスタのゲートにローレベルの電位を出力する第4の手段と、第2のトランジスタがブートストラップ動作をしていない期間に、第2のトランジスタのソースとドレインのうち他方にローレベルの電位を出力する第3の手段とを備えることを特徴としている。 The shift register of the present invention is a shift register having a plurality of stages, and each stage of the shift register circuit is turned on when a high-level output signal is input from the previous stage, and has a potential of about a high level. Is turned on by the output of the first transistor and one of the source and the drain is connected to the first signal line, and the other of the source and the drain is the first of the next stage. A low level output signal is input from the previous stage to the second transistor connected to the transistor, and the low level is applied to the gate of the second transistor during a period in which the second transistor is not performing the bootstrap operation. The fourth means for outputting the potential and the source and drain of the second transistor during the period when the second transistor is not performing the bootstrap operation. It is characterized in that it comprises a third means for outputting a low-level potential to the other.

本発明のシフトレジスタは、上記構成において、第3の手段、及び第4の手段は第1の信号線、第2の信号線、第3の信号線、及び第2のトランジスタのゲートの電位の反転信号によって制御されることを特徴としている。 In the shift register of the present invention, in the above structure, the third means and the fourth means are the first signal line, the second signal line, the third signal line, and the potential of the gate of the second transistor. It is characterized by being controlled by an inversion signal.

本発明のシフトレジスタは、上記構成において、第2の手段は第2の信号線がハイレベルのときにローレベルの電位を出力し、第2の信号線がローレベルのときになにも出力しない機能を有するに第17のトランジスタと、第2のトランジスタのゲートの電位の反転信号がハイレベルのときに第1の信号線の信号を出力し、第2のトランジスタのゲートの電位の反転信号がローレベルのときになにも出力しない機能を有する第18のトランジスタと、第2のトランジスタのゲートの電位の反転信号がハイレベルのときに第3の信号線の信号を出力し、第2のトランジスタのゲートの電位の反転信号がローレベルのときになにも出力しない機能を有する第19のトランジスタと、第18のトランジスタが第1の信号線の信号を出力して、第1の信号線がハイレベルのときにローレベルの電位を出力し、第1の信号線がローレベル、及び第18のトランジスタがなにも出力しないときになにも出力しない機能を有する第20のトランジスタと、第18のトランジスタが第1の信号線の信号を出力して、第1の信号線がハイレベルのときにローレベルの電位を出力し、第1の信号線がローレベル、及び第19のトランジスタがなにも出力しないときになにも出力しない機能を有する第21のトランジスタとを含む回路構成によって実現することを特徴としている。 In the shift register of the present invention having the above structure, the second means outputs a low-level potential when the second signal line is at a high level, and outputs nothing when the second signal line is at a low level. The signal of the first signal line is output when the inverted signal of the gate potential of the seventeenth transistor and the second transistor has a high level, and the inverted signal of the gate potential of the second transistor. The signal of the third signal line is output when the inverted signal of the potential of the gate of the 18th transistor having the function of not outputting anything when the transistor is at the low level and the second transistor is at the high level, The nineteenth transistor having the function of not outputting anything when the inverted signal of the gate potential of the transistor is low level, and the eighteenth transistor output the signal of the first signal line, A twentieth transistor having a function of outputting a low level potential when the signal line is at a high level, a first signal line being at a low level, and a function of not outputting anything when the eighteenth transistor outputs nothing; The eighteenth transistor outputs a signal of the first signal line, and when the first signal line is at a high level, a low level potential is output, the first signal line is at a low level, and the nineteenth This is realized by a circuit configuration including a twenty-first transistor having a function of outputting nothing when the transistor outputs nothing.

本発明のシフトレジスタは、上記構成において、第2のトランジスタのゲート、ソースとドレインのうち他方との間に容量素子を接続することを特徴としている。 The shift register of the present invention is characterized in that, in the above structure, a capacitor is connected between the gate, the source, and the drain of the second transistor.

本発明のシフトレジスタは、上記構成において、第1のトランジスタのゲートは前の段の出力信号が入力され、ソースとドレインのうち一方はハイレベルの電源線と接続され、ソースとドレインのうち他方は第2のトランジスタのゲート接続されていることを特徴としている。 In the shift register of the present invention having the above structure, the output signal of the previous stage is input to the gate of the first transistor, one of the source and the drain is connected to the high-level power supply line, and the other of the source and the drain is connected Is characterized by being connected to the gate of the second transistor.

本発明のシフトレジスタは、上記構成において、第1のトランジスタのゲートは前の段の出力信号が入力され、ソースとドレインのうち一方はハイレベルの電源線と接続され、ソースとドレインのうち他方は第2のトランジスタのゲートと接続されていることを特徴としている。 In the shift register of the present invention having the above structure, the output signal of the previous stage is input to the gate of the first transistor, one of the source and the drain is connected to the high-level power supply line, and the other of the source and the drain is connected Is connected to the gate of the second transistor.

本発明のシフトレジスタは、上記構成において、第1のトランジスタのゲート及びソースとドレインのうち一方は前の段の出力信号が入力され、ソースとドレインのうち他方は第2のトランジスタのゲートと接続されていることを特徴としている。 In the shift register of the present invention, in the above structure, one of the gate, the source, and the drain of the first transistor receives the output signal of the previous stage, and the other of the source and the drain is connected to the gate of the second transistor. It is characterized by being.

本発明のシフトレジスタは、上記構成において、N段目(Nは自然数)に入力される第1の信号線伝達される制御信号と、N+1段目に入力される第1の信号線から伝達される制御信号と、N+2段目に入力される第1の信号線から伝達される制御信号とが120度の位相差を持つことを特徴としている。 The shift register of the present invention is transmitted from the control signal transmitted on the first signal line input to the Nth stage (N is a natural number) and the first signal line input to the N + 1th stage in the above configuration. And the control signal transmitted from the first signal line input at the (N + 2) th stage has a phase difference of 120 degrees.

本発明のシフトレジスタは、上記構成において、N段目(Nは自然数)に入力される第2の信号線から伝達される制御信号と、N+1段目に入力される第2の信号線から伝達される制御信号と、N+2段目に入力される第2の信号線から伝達される制御信号とが120度の位相差を持つことを特徴としている。 In the shift register of the present invention, in the above configuration, the control signal transmitted from the second signal line input to the Nth stage (N is a natural number) and the second signal line input to the N + 1th stage are transmitted. The control signal transmitted from the second signal line input to the (N + 2) th stage has a phase difference of 120 degrees.

本発明のシフトレジスタは、上記構成において、N段目(Nは自然数)に入力される第3の信号線から伝達される制御信号と、N+1段目に入力される第3の信号線から伝達される制御信号と、N+2段目に入力される第3の信号線から伝達される制御信号とが120度の位相差を持つことを特徴としている。 In the shift register of the present invention, in the above configuration, the control signal transmitted from the third signal line input to the Nth stage (N is a natural number) and the third signal line input to the N + 1th stage are transmitted. The control signal transmitted from the third signal line input to the (N + 2) th stage has a phase difference of 120 degrees.

本発明のシフトレジスタは、上記構成において、第1のトランジスタ乃至第21のトランジスタは非結晶半導体によって構成されることを特徴としている。 The shift register of the present invention is characterized in that, in the above structure, the first to twenty-first transistors are formed using an amorphous semiconductor.

本発明のシフトレジスタは、上記構成において、第1の信号線、第2の信号線、及び第3の信号線と、第1のトランジスタ乃至第21のトランジスタとの間に少なくとも1本の電源線を有することを特徴としている。 In the shift register of the present invention, in the above structure, at least one power supply line is provided between the first signal line, the second signal line, the third signal line, and the first to twenty-first transistors. It is characterized by having.

本発明のシフトレジスタは、上記構成において、第2のトランジスタのチャネル領域はU字がたとなっていることを特徴としている。 The shift register of the present invention is characterized in that, in the above structure, the channel region of the second transistor is U-shaped.

本発明のシフトレジスタは、上記構成において、シフトレジスタの出力信号はレベルシフト回路を介して出力することを特徴としている。 The shift register of the present invention is characterized in that, in the above structure, an output signal of the shift register is output via a level shift circuit.

本発明のシフトレジスタは、上記構成において、シフトレジスタに入力される制御信号はレベルシフト回路を介して入力されることを特徴としている。 The shift register according to the present invention is characterized in that, in the above structure, a control signal input to the shift register is input via a level shift circuit.

本発明のシフトレジスタは、上記構成において、シフトレジスタの出力信号によって複数のスイッチング素子を順にオンすることを特徴としている。 The shift register of the present invention is characterized in that, in the above structure, a plurality of switching elements are sequentially turned on by an output signal of the shift register.

本発明の表示装置は、上記構成において、画素と、シフトレジスタを用いて構成されるゲートドライバと、ゲートドライバの出力信号を画素に伝達するゲート信号線と、ビデオ信号を画素に伝達するソース信号線とを少なくとも有し、ゲートドライバの出力信号によって画素を選択し、選択された画素にビデオ信号を書き込むことを特徴している。 The display device of the present invention has the above structure, a pixel, a gate driver using a shift register, a gate signal line for transmitting an output signal of the gate driver to the pixel, and a source signal for transmitting a video signal to the pixel. And a pixel is selected by an output signal of a gate driver, and a video signal is written to the selected pixel.

また、画素は、印加される電圧によって透過率が変わる液晶素子と、ゲート信号線によってオン、オフが制御されるスイッチング素子として動作する第22のトランジスタとを少なくとも有し、オンとなった第22のトランジスタ介して液晶素子にビデオ信号が書き込まれることを特徴としている。 In addition, the pixel includes at least a liquid crystal element whose transmittance changes depending on an applied voltage and a twenty-second transistor that operates as a switching element whose on / off state is controlled by a gate signal line. A video signal is written into the liquid crystal element through the transistor.

本発明の表示装置は、非結晶半導体を用いたトランジスタで構成されるゲートドライバであって、ゲートドライバは対向に配置され、同一のタイミングで同一のゲート信号線を選択することを特徴としている。 The display device of the present invention is a gate driver including transistors using an amorphous semiconductor, wherein the gate drivers are arranged to face each other and select the same gate signal line at the same timing.

本発明によれば、非選択期間において、電源電圧を出力する複数のトランジスタを順にオンすることによって、常時オンするトランジスタを無くすことができるため、トランジスタの特性劣化を抑制することができる。また、非選択期間において、常時、又は一定期間固定電圧を出力することでノイズを減らすことができる。 According to the present invention, in the non-selection period, by sequentially turning on the plurality of transistors that output the power supply voltage, it is possible to eliminate the transistors that are always turned on, and thus it is possible to suppress deterioration in transistor characteristics. Further, noise can be reduced by outputting a fixed voltage at all times or for a certain period in the non-selection period.

本発明の実施形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨、及びその範囲から逸脱することなく、その形態、及び詳細をさまざまに変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施形態の記載内容に限定して解釈されるものではない。 Embodiments of the present invention will be described in detail with reference to the drawings. However, the present invention is not limited to the following description, and it is easily understood by those skilled in the art that modes and details can be variously changed without departing from the spirit and scope of the present invention. . Therefore, the present invention should not be construed as being limited to the description of the embodiments below.

(第1の実施形態)

本実施形態は、非選択期間の出力電圧のノイズを減らすために、一定期間毎にVSSを出力することでノイズを減らすことを特徴とするシフトレジスタ回路の構成、及び動作について、図1乃至図4を参照して説明する。

(First embodiment)

In this embodiment, in order to reduce noise of the output voltage during the non-selection period, the configuration and operation of the shift register circuit is characterized in that the noise is reduced by outputting VSS at regular intervals. This will be described with reference to FIG.

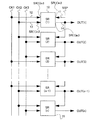

図1に示すように、回路10はn個(nは2以上の自然数)の回路SR(1)〜SR(n)を直列に接続して、シフトレジスタ回路を構成している。

As shown in FIG. 1, the

入力端子11は、1段目の回路10であるSR(1)ではスタートパルスを入力し、2段目以降の回路10は前段の出力端子14からの出力を入力するための入力端子である。入力端子12は、1段目の回路10であるSR(1)ではクロック信号であるCK1、2段目の回路10であるSR(2)ではクロック信号であるCK2、3段目の回路10であるSR(3)ではクロック信号CK3、4段目の回路10であるSR(4)ではCK1というようにCK1、CK2、及びCK3を順に入力する入力端子である。

The

入力端子13は、1段目の回路10であるSR(1)ではCK2、2段目の回路10であるSR(2)ではCK3、3段目の回路10であるSR(3)ではCK1、4段目の回路10であるSR(4)ではCK2というようにCK1、CK2、及びCK3を順に入力する入力端子である。出力端子14は、回路10の出力端子であり、1段目の回路10であるSR(1)ではOUT(1)を出力して、且つ2段目の回路10であるSR(2)の入力端子11にOUT(1)を出力し、2段目の回路10であるSR(2)ではOUT(2)を出力して、且つ3段目の回路10であるSR(3)の入力端子11にOUT(2)を出力する。なお、入力端子11〜14は、それぞれ配線に接続されている。

The

ここで、SSP、CK1、CK2、及びCK3は、HighとLowの2値の値を持つ1ビットの信号である。また、OUT(1)、OUT(2)、OUT(3)、OUT(n−1)、及びOUT(n)も、HighとLowの2値の値を持つ1ビットの出力である。Highは正電源であるVDDと同一の電位であり、Lowは負電源であるVSSと同一の電位である。 Here, SSP, CK1, CK2, and CK3 are 1-bit signals having binary values of High and Low. OUT (1), OUT (2), OUT (3), OUT (n-1), and OUT (n) are also 1-bit outputs having binary values of High and Low. High is the same potential as VDD which is a positive power source, and Low is the same potential as VSS which is a negative power source.

図1のシフトレジスタ回路の動作について、図2に示す本実施形態のタイミングチャートを参照して説明する。 The operation of the shift register circuit of FIG. 1 will be described with reference to the timing chart of the present embodiment shown in FIG.

図2において、SSPは任意のタイミングでパルス幅がCK1、CK2及びCK3の1/3周期となるHighのスタートパルスである。CK1、CK2、及びCK3は3相のクロック信号である。また、図1において、CK3がHighとなるときにSSPもHighとなることが望ましい。nodeP(1)は、後に説明する図3のnodePの電位である。OUT(1)は1段目の回路10であるSR(1)の出力であり、OUT(2)は2段目の回路10であるSR(2)の出力であり、OUT(3)は3段目の回路10であるSR(3)の出力であり、OUT(n−1)はn−1段目の回路10であるSR(n−1)の出力であり、OUT(n)はn段目の回路10であるSR(n)の出力である。

In FIG. 2, SSP is a high start pulse whose pulse width is 1/3 of CK1, CK2 and CK3 at an arbitrary timing. CK1, CK2, and CK3 are three-phase clock signals. Further, in FIG. 1, it is desirable that SSP also becomes High when CK3 becomes High. nodeP (1) is a potential of nodeP in FIG. 3 to be described later. OUT (1) is the output of SR (1) which is the

図2のタイミングチャートに示すように、期間T1においてSSPがHighとなると、期間T2においてOUT(1)がHighとなり、期間T3においてOUT(2)がHighとなる。こうして、SSPの出力をシフトすることによってシフトレジスタ回路を構成している。 As shown in the timing chart of FIG. 2, when SSP becomes High in the period T1, OUT (1) becomes High in the period T2, and OUT (2) becomes High in the period T3. Thus, the shift register circuit is configured by shifting the output of the SSP.

次に、図3を参照して、1段目の回路10の構成について説明する。

Next, the configuration of the first-

図3に示す回路10は、入力端子11、入力端子12、入力端子13、出力端子14、トランジスタ31、トランジスタ32、容量素子33、回路34、回路35から構成されている。なお、入力端子11〜13は、それぞれ配線に接続されている。入力端子11、入力端子12、入力端子13、出力端子14は、図1で説明したものと同様なものとする。トランジスタ31及びトランジスタ32は、Nチャネル型トランジスタであり、非結晶半導体、多結晶半導体、若しくは単結晶半導体によって構成されている。容量素子33は、2つの電極を持つ容量素子である。回路34は、CK2がHighの場合にnodePにLowを出力し、CK2がLowの場合に出力がフローティングになる機能を有する回路である。回路35は、CK2がHighの場合に出力端子14にLowを出力し、CK2がLowの場合に出力がフローティングになる機能を有する回路である。

3 includes an

図3の接続関係について説明する。トランジスタ31のゲートは入力端子11と接続され、ソースとドレインのうち一方はVDDと接続され、ソースとドレインのうち他方は容量素子33の一方の電極、トランジスタ32のゲート及び回路34の出力端子、つまりnodePと接続されている。また、トランジスタ32のソースとドレインのうち一方は入力端子12と接続され、ソースとドレインのうち他方は回路35の出力端子、容量素子33の他方の端子及び出力端子14と接続されている。入力端子13は回路34の入力端子及び回路35の入力端子と接続されている。

The connection relationship in FIG. 3 will be described. The gate of the

図3の動作について、図2に示す本実施形態のタイミングチャートを参照して、期間T1、期間T2及び期間T3に分けて説明する。また、初期状態として、nodeP及びOUT(1)の電位はVSSとする。 The operation of FIG. 3 will be described by dividing it into a period T1, a period T2, and a period T3 with reference to the timing chart of the present embodiment shown in FIG. In addition, as an initial state, the potentials of nodeP and OUT (1) are VSS.

期間T1において、SSPがHigh、CK1がLow、CK2がLow、CK3がHighとなる。このときのトランジスタ31のゲートの電位はVDD、ソースとドレインのうち一方の電位はVDD、ソースとドレインのうち他方の電位はVSSとなるため、当該トランジスタ31がオンして、nodePの電位がVSSから上昇し始める。nodePの電位の上昇は、VDDからトランジスタ31のしきい値電圧分小さい電位となるところで止まり、トランジスタ31はオフする。このときのnodePの電位をVn1とする。また、回路34及び回路35は、CK2がLowとなっているため、出力はフローティングとなる。そのため、nodePには電荷が供給されないため、フローティングとなる。このときのトランジスタ32のゲートの電位はVn1、ソースとドレインのうち一方の電位はVSS、ソースとドレインのうち他方の電位はVSSとなるため、当該トランジスタ32は、オンしている。しかし、ソースとドレインのうち一方の電位とソースとドレインのうち他方の電位とが同電位であり、電荷の移動はないため、電流は流れず、電位も変動しない。そして、容量素子33は出力端子14の電位であるVSSとnodePの電位であるVn1との電位差を保持している。

In the period T1, SSP is High, CK1 is Low, CK2 is Low, and CK3 is High. At this time, the potential of the gate of the

期間T2において、SSPがLow、CK1がHigh、CK2がLow、CK3がLowとなる。このときのトランジスタ31のゲートの電位はVSS、ソースとドレインのうち一方の電位はVDD、ソースとドレインのうち他方の電位はVn1となるため、当該トランジスタ31はオフする。回路34及び回路35は、CK2がLowとなっているため、出力はフローティングとなる。このときのトランジスタ32のゲートの電位はVn1、ソースとドレインのうち一方の電位はVDD、ソースとドレインのうち他方、つまり出力端子14の電位はVSSとなるため、当該トランジスタ32がオンして、出力端子14の電位が上昇し始める。すると、トランジスタ32のゲートと、ソースとドレインのうち他方の間に接続されている容量素子33は、期間T1で保持した電位差をそのまま保持するため、ソースとドレインのうち他方の電位が上昇すると、ゲート電圧も同時に上昇する。このときの、nodePの電位をVn2とする。nodePの電位がVDDとトランジスタ32のしきい値電圧との和まで上昇すると、出力端子14の電位の上昇はCK1と同じVDDになるところで止まる。いわゆる、ブートストラップ動作によって、CK1のHighの電位であるVDDまで、出力端子14の電位を上昇することができる。

In the period T2, SSP is Low, CK1 is High, CK2 is Low, and CK3 is Low. At this time, the potential of the gate of the

期間T3において、SSPがLow、CK1がLow、CK2がHight、CK3がLowとなる。このとき、nodePの電位は、CK2がHighであり、回路34からVSSが出力されるためVSSとなり、OUT(1)の電位も回路35からVSSが出力されるためVSSとなる。このときのトランジスタ31のゲート電位はVSS、ソースとドレインのうち一方の電位はVDD、ソースとドレインのうち他方の電位はVSSとなり、当該トランジスタ31はオフする。トランジスタ32のゲートの電位はVss、ソースとドレインのうち一方の電位はVSS、ソースとドレインのうち他方の電位はVSSとなり、当該トランジスタ32はオフする。

In the period T3, SSP is Low, CK1 is Low, CK2 is High, and CK3 is Low. At this time, the potential of nodeP is VSS because CK2 is High and VSS is output from the

上記説明した期間T1、期間T2、期間T3の動作により、期間T1にSSPが入力されるとOUT(1)が期間T2に出力される。つまり、SSPがクロック信号の1/3周期ずつシフトして出力される回路10をn段接続することにより、シフトレジスタ回路を構成している。

When SSP is input in the period T1, OUT (1) is output in the period T2 by the operations in the above-described periods T1, T2, and T3. In other words, the shift register circuit is configured by connecting n stages of the

図3においては、1段目の回路10であるSR(1)を示したが、n段目の回路10であるSR(n)について図51を参照して説明する。図51において、トランジスタ31、トランジスタ32、容量素子33、回路34、回路35、入力端子11、入力端子12、入力端子13、及び出力端子14は図3で説明したものと同様なものとする。入力端子11から入力される入力信号は前の段の回路10の出力端子14と接続されていることを特徴とする。

In FIG. 3, SR (1) which is the

なお、トランジスタ31のゲート及びトランジスタ32のソースとドレインのうち他方は電源線となる配線(以下、「電源線」と記す)と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線となる配線(以下、「信号線」と記す)と接続してもよい。また、トランジスタ31のソースとドレインのうち他方は信号線と接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。

Note that the other of the gate of the

図3に示したシフトレジスタ回路で用いたトランジスタはNチャネル型トランジスタのみで構成する単極性回路であったが、Pチャネル型トランジスタのみで構成してもよい。もちろん、Pチャネル型トランジスタとNチャネル型トランジスタ組み合わせてもよい。トランジスタを全てPチャネル型トランジスタで構成した場合のシフトレジスタ回路について図55を参照して説明する。 Although the transistor used in the shift register circuit shown in FIG. 3 is a unipolar circuit composed of only N-channel transistors, it may be composed of only P-channel transistors. Of course, a P-channel transistor and an N-channel transistor may be combined. A shift register circuit in which all transistors are P-channel transistors will be described with reference to FIG.

図55に示す回路構成において、正電源VDD、負電源VSS、入力端子11、入力端子12、入力端子13、出力端子14は図3と同様なものを用いることができる。トランジスタ551、及びトランジスタ552はPチャネル型トランジスタであり、非結晶半導体、多結晶半導体、若しくは単結晶半導体によって構成されている。容量素子553は2つの電極を持つ容量素子である。回路554はCK2がLowの場合にnodePにHighを出力し、CK2がHighの場合に出力がフローティングとなる機能を有する回路である。回路555はCK2がLowの場合に出力端子14にHighを出力し、CK2がHighの場合に出力がフローティングとなる機能を有する回路である。

In the circuit configuration shown in FIG. 55, the positive power supply VDD, the negative power supply VSS, the

図55の接続関係について説明する。トランジスタ551のゲートは入力端子11と接続され、ソースとドレインのうち一方は正電源VSSと接続され、ソースとドレインのうち他方は容量素子553の一方の電極、トランジスタ552のゲート及び回路554の出力端子、つまりnodePと接続されている。トランジスタ552のソースとドレインのうち一方は入力端子12と接続され、ソースとドレインのうち他方は回路555の出力端子、容量素子553の他方の電極、及び出力端子14と接続されている。入力端子13は回路554の入力端子、及び回路555の入力端子と接続されている。

The connection relationship in FIG. 55 will be described. The gate of the

なお、トランジスタ551のゲート及びトランジスタ552のソースとドレインのうち他方は電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。また、トランジスタ551のソースとドレインのうち他方は信号線と接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。

Note that the other of the gate of the

図59(a)を参照して、図55に示す回路554の構成の一例について説明する。図59(a)に示す回路554に示すように、入力端子13、及びnodePは図55と同様なものとする。トランジスタ591はPチャネル型トランジスタであり、非結晶半導体、多結晶半導体、若しくは単結晶半導体によって構成されている。

An example of the structure of the

図59(a)の接続関係について説明する。トランジスタ591のゲートは入力端子13と接続され、ソースとドレインのうち一方はVDDと接続され、ソースとドレインのうち他方はnodePと接続されている。

The connection relationship in FIG. 59 (a) will be described. The gate of the

図59(a)の動作について説明する。入力端子13から入力されるCK2がLowの場合に、トランジスタ591はオンして、nodePにVDDを出力し、CK2がHighの場合に、トランジスタ591はオフして、nodePにはなにも出力されない。こうして、回路554は、CK2がLowの場合にHighを出力して、Highの場合にはフローティングになる機能を有する回路を構成している。また、回路構成は説明した回路構成に限らず、同じ機能を有する回路構成であればよい。

The operation of FIG. 59 (a) will be described. When CK2 input from the

なお、トランジスタ591のソースとドレインのうち一方は信号線に接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。また、トランジスタ591のゲートは電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。

Note that one of a source and a drain of the

図59(b)を参照して、図55に示す回路555の構成の一例について説明する。図59(b)に示す回路555に示すように、入力端子13、及び出力端子14は図55と同様なものとする。トランジスタ592はPャネル型トランジスタであり、非結晶半導体、多結晶半導体、若しくは単結晶半導体によって構成されている。

An example of the structure of the

図59(b)の動作について説明する。入力端子13から入力されるCK2がLowの場合に、トランジスタ592はオンして、出力端子14にVDDを出力し、CK2がHighの場合に、トランジスタ592はオフして、出力端子14にはなにも出力されない。こうして、回路555は、CK2がLowの場合にHighを出力して、Highの場合にはフローティングになる機能を有する回路を構成している。また、回路構成は説明した回路構成に限らず、同じ機能を有する回路構成であればよい。

The operation of FIG. 59B will be described. When CK2 input from the

なお、トランジスタ592のソースとドレインのうち一方は信号線に接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。また、トランジスタ592のゲートは電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。

Note that one of a source and a drain of the

次に、図4(a)を参照して、図3に示す回路34の構成の一例について説明する。

Next, an example of the configuration of the

図4(a)に示す回路34において、入力端子13、及びnodePは図3と同様なものとする。トランジスタ41はNチャネル型トランジスタであり、非結晶半導体、多結晶半導体、若しくは単結晶半導体によって構成されている。

In the

図4(a)の接続関係について説明する。トランジスタ41のゲートは入力端子13と接続され、ソースとドレインのうち一方はVSSと接続され、ソースとドレインのうち他方はnodePと接続されている。

The connection relationship in FIG. 4A will be described. The gate of the

図4(a)の動作について説明する。入力端子13から入力されるCK2がHighの場合に、トランジスタ41はオンして、nodePにVSSを出力し、CK2がLowの場合に、トランジスタ41はオフして、nodePにはなにも出力されない。こうして、回路34は、CK2がHighの場合にLowを出力して、Lowの場合にはフローティングになる機能を有する回路を構成している。また、回路構成は説明した回路構成に限らず、同じ機能を有する回路構成であればよい。

The operation of FIG. 4A will be described. When CK2 input from the

なお、トランジスタ41のソースとドレインのうち一方は信号線に接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。また、トランジスタ41のゲートは電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。

Note that one of the source and the drain of the

図4(b)を参照して、図3に示す回路35の構成の一例について説明する。

An example of the configuration of the

図4(b)に示す回路35において、入力端子13、及び出力端子14は図3と同様なものとする。トランジスタ42はNチャネル型トランジスタであり、非結晶半導体、多結晶半導体、若しくは単結晶半導体によって構成されている。

In the

図4(b)の動作について説明する。入力端子13から入力されるCK2がHighの場合に、トランジスタ42はオンして、出力端子14にVSSを出力し、CK2がLowの場合に、トランジスタ42はオフして、出力端子14にはなにも出力されない。こうして、回路35は、CK2がHighの場合にLowを出力して、Lowの場合にはフローティングになる機能を有する回路を構成している。また、回路構成は説明した回路構成に限らず、同じ機能を有する回路構成であればよい。

The operation of FIG. 4B will be described. When CK2 input from the

なお、トランジスタ42のソースとドレインのうち一方は、信号線に接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。もちろん、トランジスタ42のソースとドレインのうち一方をトランジスタ41のソースとドレインのうち一方が接続されたVSSとなる配線と接続してもよい。また、トランジスタ42のゲートは電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。

Note that one of the source and the drain of the

つまり、図3、図4に示す構造は、第1のトランジスタ(トランジスタ31)と、第2のトランジスタ(トランジスタ32)と、第3のトランジスタ(トランジスタ41)と、第4のトランジスタ(トランジスタ42)とを有し、第1のトランジスタは、ソースとドレインのうち一方が第1の配線(VDD)に接続され、ソースとドレインのうち他方が第2のトランジスタのゲート電極と第3のトランジスタのソースとドレインのうち他方に接続され、ゲート電極が第5の配線(入力端子11)に接続され、第2のトランジスタは、ソースとドレインのうち一方が第3の配線(入力端子12)に接続され、ソースとドレインのうち他方が第6の配線(出力端子14)に接続され、第3のトランジスタは、ソースとドレインのうち一方が第2の配線(VSS)に接続され、ソースとドレインのうち他方が第2のトランジスタのゲート電極に接続され、ゲート電極が第4の配線(入力端子13)に接続され、第4のトランジスタは、ソースとドレインのうち一方が第2の配線(VSS)に接続され、ソースとドレインのうち他方が第6の配線(出力端子14)に接続され、ゲート電極が第4の配線(入力端子13)に接続されている。また、第1のトランジスタにおいて、ソースとドレインのうち一方を第5の配線(入力端子11)に接続させた構成とすることも可能である。 That is, the structure shown in FIGS. 3 and 4 includes the first transistor (transistor 31), the second transistor (transistor 32), the third transistor (transistor 41), and the fourth transistor (transistor 42). The first transistor has one of a source and a drain connected to the first wiring (VDD), and the other of the source and the drain is the gate electrode of the second transistor and the source of the third transistor. And the drain are connected to the other, the gate electrode is connected to the fifth wiring (input terminal 11), and the second transistor has one of the source and drain connected to the third wiring (input terminal 12). The other of the source and the drain is connected to the sixth wiring (output terminal 14), and the third transistor has one of the source and the drain connected to the second wiring. The other of the source and drain is connected to the gate electrode of the second transistor, the gate electrode is connected to the fourth wiring (input terminal 13), and the fourth transistor is connected to the line (VSS). One of the drains is connected to the second wiring (VSS), the other of the source and drain is connected to the sixth wiring (output terminal 14), and the gate electrode is connected to the fourth wiring (input terminal 13). Has been. In the first transistor, one of the source and the drain can be connected to the fifth wiring (input terminal 11).

以上のような、シフトレジスタ回路では、CK2がHighになるに従って、nodeP、及び出力端子14にVSSを供給することができる。つまり、非選択期間に、一定期間毎にVSSを入力することによって、ノイズを減らすことができ、且つ定常的にオンするトランジスタがないため、特性が劣化することを抑制することができる。また、最低で4つのトランジスタで動作することがきるため、シフトレジスタ回路全体としての素子数を減らすことができ、絶縁基板上に少ない面積で内部回路を構成することが可能となる。

In the shift register circuit as described above, VSS can be supplied to the node P and the

以下に、本実施形態の変更可能な構成例、及び動作例をいくつか述べる。また、以下で述べる構成例、及び動作例は「課題を解決するための手段」、「発明を実施するための最良の形態」、及び「実施例」について適用可能である。 Hereinafter, some configuration examples and operation examples of the embodiment that can be changed will be described. The configuration examples and operation examples described below can be applied to “means for solving the problems”, “best mode for carrying out the invention”, and “examples”.

図1に示すように、CK1、CK2、及びCK3のクロック信号は、回路10が非選択期間の場合にも入力されているが、スイッチ素子などを設けて、非選択期間の回路10へ入力しなくしてもよい。こうすることで、クロック信号線の負荷が減るため、消費電力を小さくすることができる。

As shown in FIG. 1, the clock signals of CK1, CK2, and CK3 are input even when the

また、図1において、上記説明したシフトレジスタ回路を逆向きに走査させてもよい。例えば、n段目の回路10の出力をn−1段目の回路10に入力すればよい。これを全段で繰り返すことで、逆向きに走査することが可能である。

In FIG. 1, the shift register circuit described above may be scanned in the reverse direction. For example, the output of the

図2に示すように、SSP、CK1、CK2、CK3のパルス幅を1/3周期としたが、パルス幅を1/3周期より少し短くしてもよい。こうすることで、貫通電流などの瞬間的に流れる電流を抑制でき、広い動作条件で動作することができ、且つ消費電力を小さくすることができる。また、ブートストラップ動作を行う回路構成においては、浮遊となるノードが発生するため、正常なブートストラップ動作を行うためにも有利である。 As shown in FIG. 2, the pulse width of SSP, CK1, CK2, and CK3 is set to 1/3 period, but the pulse width may be slightly shorter than 1/3 period. By doing so, current that flows instantaneously such as a through current can be suppressed, operation can be performed under a wide range of operating conditions, and power consumption can be reduced. Further, in a circuit configuration that performs a bootstrap operation, a floating node is generated, which is advantageous for performing a normal bootstrap operation.

図2において、SSPがHighとなる期間は、CK3がHighとなる期間及びパルス幅を同一としたが、これに限るものではない。例えば、制御信号によって、外部回路から内部回路へ信号を伝達する場合に、バッファ回路、信号振幅を変えるレベルシフト回路などによって制御信号どうしの遅延時間が変わる可能性があるためである。 In FIG. 2, the period during which SSP is High is the same as the period during which CK3 is High and the pulse width, but the present invention is not limited to this. For example, when a signal is transmitted from an external circuit to an internal circuit by a control signal, the delay time between the control signals may be changed by a buffer circuit, a level shift circuit that changes the signal amplitude, or the like.

図3において、容量素子33は、ブートストラップ動作をするために接続されており、トランジスタ32のゲートと、ソースとドレインのうち他方との間にブートストラップ動作できるだけのゲートとソース間の容量などがあれば、なくてもよい。また、容量素子33の形成方法はなんでもよい。例えば、半導体層とゲート配線層との間で容量素子を形成してもよいし、非結晶半導体層と配線との間で容量素子を形成してもよい。半導体層とゲート配線層とで容量素子を形成する場合は、ボトムゲートトランジスタ、トップゲート型トランジスタに関らず薄いGI膜(ゲート絶縁膜)を挟んで形成されているため、小さい面積でより多くの容量値を得ることが可能となるため、有利である。

In FIG. 3, a

また、図3において、SSPはトランジスタ31のゲートに入力したが、トランジスタ31のゲートと、ソースとドレインのうち一方とを接続して、そこにSSPを入力してもよい。こうすることで、正電源VDDが必要なくなり電源線を1本減らすことができるため、シフトレジスタ回路を形成するための面積を小さくすることができる。その結果、より高精細、且つ狭額縁な表示装置を提供することが可能となる。

In FIG. 3, the SSP is input to the gate of the

図3に示した回路34及び回路35は、上記で説明したように、CK2がHighの場合にVSSを出力し、CK2がLowの場合にフローティングとなる回路であればよい。また、回路34の入力端子に次の段の回路10の出力を入力してもよいし、同様に回路35の入力端子には次の段の回路10の出力を入力してもよいし、回路34の入力端子、及び回路35の入力端子に次の段の回路10の出力を入力してもよい。次の段の回路10の出力を利用することで、制御信号だけに同期するのではなく実際のシフトレジスタ回路の出力とも同期することができるため、よりシフトレジスタ回路の動作にあった電位の切り替えができるため有利である。

As described above, the

図3に示すように、nodePと、VSS又はVDDの間に容量素子を接続してもよい。容量素子を接続することでより、nodePの電位を安定させることができる。 As shown in FIG. 3, a capacitor may be connected between nodeP and VSS or VDD. By connecting the capacitor, the potential of the node P can be stabilized.

なお、図3において、回路34は必ずしも必要ではない。つまり、回路35によって、一定期間毎にVSSを出力しているため、nodePにノイズがあってもトランジスタ32をオフしていればよいためである。こうすることで、素子数を減らすことができる。そのとき、nodePとVSS、又はVDDの間に容量素子を接続してもよい。

In FIG. 3, the

(第2の実施形態)

本実施形態は、非選択期間の出力電圧のノイズを減らすために、一定時間毎にVSSを出力することでノイズを減らすことを特徴とするシフトレジスタ回路の構成、及び動作について、図2、図5乃至図7を用いて説明する。

(Second Embodiment)

In this embodiment, in order to reduce noise in the output voltage during the non-selection period, the noise is reduced by outputting VSS at regular time intervals, and the configuration and operation of the shift register circuit, which is characterized in that FIG. This will be described with reference to FIGS.

図5に示すように、回路50はn個(nは2以上の自然数)の回路SR(1)〜SR(n)を直列に接続して、シフトレジスタ回路を構成している。

As shown in FIG. 5, the

入力端子51は、1段目の回路50であるSR(1)ではスタートパルスを入力し、2段目以降の回路50であるSR(2)では前段の出力端子55からの出力を入力するための入力端子である。入力端子52は、1段目の回路50であるSR(1)ではクロック信号であるCK1、2段目の回路50であるSR(2)ではクロック信号であるCK2、3段目の回路50であるSR(3)ではクロック信号CK3、4段目の回路50であるSR(4)ではCK1というようにクロック信号を順に入力する入力端子である。入力端子53は、1段目の回路50であるSR(1)ではCK2、2段目の回路50であるSR(2)ではCK3、3段目の回路50であるSR(3)ではCK1、4段目の回路50であるSR(4)ではCK2というようにクロック信号を順に入力する入力端子である。入力端子54は、1段目の回路50であるSR(1)ではCK3、2段目の回路50であるSR(2)ではCK1、3段目の回路50であるSR(3)ではCK2、4段目の回路50であるSR(4)ではCK3というようにクロック信号を順に入力する入力端子である。出力端子55は、回路50の出力端子であり、1段目の回路50あるSR(1)ではOUT(1)を出して、且つ2段目の回路50であるSR(2)の入力端子51にOUT(1)を出力し、2段目の回路50であるSR(2)ではOUT(2)を出力して、且つ3段目の回路50であるSR(3)の入力端子51にOUT(2)を出力する。

The

ここで、SSP、CK1、CK2及びCK3は、HighとLowの2値の値を持つ1ビットの信号である。Highは正電源であるVDDと同一の電位であり、Lowは負電源であるVSSと同一の電位である。ここで、SSP、CK1、CK2及びCK3は、HighとLowの2値の値を持つ1ビットの信号である。また、OUT(1)、OUT(2)、OUT(3)、OUT(n−1)及びOUT(n)も、HighとLowの2値の値を持つ1ビットの出力である。Highは正電源であるVDDと同一の電位であり、Lowは負電源であるVSSと同一の電位である。 Here, SSP, CK1, CK2, and CK3 are 1-bit signals having binary values of High and Low. High is the same potential as VDD which is a positive power source, and Low is the same potential as VSS which is a negative power source. Here, SSP, CK1, CK2, and CK3 are 1-bit signals having binary values of High and Low. OUT (1), OUT (2), OUT (3), OUT (n−1), and OUT (n) are also 1-bit outputs having binary values of High and Low. High is the same potential as VDD which is a positive power source, and Low is the same potential as VSS which is a negative power source.

図5のシフトレジスタ回路の動作について、図2に示す本実施形態のタイミングチャートを参照して説明する。 The operation of the shift register circuit of FIG. 5 will be described with reference to the timing chart of the present embodiment shown in FIG.

SSP、CK1、CK2及びCK3は第1の実施形態と同様のものを用いることができる。なお、nodeP(1)は、後に説明する図6のnodePの電位である。OUT(1)は1段目の回路50であるSR(1)の出力であり、OUT(2)は2段目の回路50であるSR(2)の出力であり、OUT(3)は3段目の回路50であるSR(3)の出力であり、OUT(n−1)はn−1段目の回路50であるSR(n−1)の出力であり、OUT(n)はn段目の回路50であるSR(n)の出力である。

SSP, CK1, CK2, and CK3 can be the same as those in the first embodiment. Note that nodeP (1) is the potential of nodeP in FIG. OUT (1) is the output of SR (1) which is the

図2のタイミングチャートにおいて、期間T1においてSSPがHighとなると、期間T2においてOUT(1)がHighとなり、期間T3においてOUT(2)がHighとなる。こうして、SSPの出力をシフトすることによってシフトレジスタ回路を構成している。 In the timing chart of FIG. 2, when SSP becomes High in the period T1, OUT (1) becomes High in the period T2, and OUT (2) becomes High in the period T3. Thus, the shift register circuit is configured by shifting the output of the SSP.

次に、図6を参照して、1段目の回路50の構成について説明する。

Next, the configuration of the first-

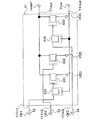

図6に示す回路50は、入力端子51、入力端子52、入力端子53、入力端子54、出力端子55、トランジスタ31、トランジスタ32、容量素子33、回路34、回路35から構成されている。入力端子51、入力端子52、入力端子53、入力端子54、出力端子55は図5で説明したものと同様なものとする。トランジスタ31、トランジスタ32及びnodePは図3で説明したものと同様なものとする。回路61は、CK2がHighの場合にnodePにLowを出力し、CK2がLowの場合に出力がフローティングになる機能を有する回路である。回路62は、CK2及びCK3のいずれかがHighの場合に出力端子55にLowを出力し、CK2及びCK3がLowの場合に出力がフローティングになる機能を有する回路である。

The

図6の接続関係について説明する。トランジスタ31のゲートは入力端子51と接続され、ソースとドレインのうち一方はVDDと接続され、ソースとドレインのうち他方は容量素子33の一方の電極、トランジスタ32のゲート及び回路61の出力端子、つまりnodePと接続されている。トランジスタ32のソースとドレインのうち一方は入力端子52と接続され、ソースとドレインのうち他方は回路62の出力端子、容量素子33の他方の電極及び出力端子55と接続されている。入力端子53は回路61の入力端子及び回路62の入力端子と接続され、入力端子54は回路62の入力端子と接続されている。

The connection relationship in FIG. 6 will be described. The gate of the

図6の動作について、図2に示す本実施形態のタイミングチャートを参照して、期間T1、期間T2、及び期間T3に分けて説明する。また、初期状態として、nodeP、及びOUT(1)の電位はVSSとする。 The operation of FIG. 6 will be described by dividing it into a period T1, a period T2, and a period T3 with reference to the timing chart of the present embodiment shown in FIG. Further, as an initial state, the potentials of nodeP and OUT (1) are VSS.

期間T1において、SSPがHigh、CK1がLow、CK2がLow、CK3がHighとなる。このときのトランジスタ31のゲートの電位はVDD、ソースとドレインのうち一方の電位はVDD、ソースとドレインのうち他方の電位はVSSとなるため、当該トランジスタ31がオンして、nodePの電位がVSSから上昇し始める。nodePの電位の上昇はVDDからトランジスタ31のしきい値電圧分小さい電位となるところで止まり、トランジスタ31はオフする。このときのnodePの電位をVn1とする。回路61は、CK2がLowとなっているため、出力はフローティングとなる。そのため、nodePには電荷が供給されないため、フローティングとなる。回路62は、CK2がLow、CK3がHighとなっているため、Lowを出力する。このときのトランジスタ32のゲート電位はVn1、ソースとドレインのうち一方の電位はVSS、ソースとドレインのうち他方の電位はVSSとなるため、当該トランジスタ32はオンしている。しかし、ソースとドレインのうち一方の電位とソースとドレインのうち他方の電位とが同電位であり、電荷の移動はないため、電流は流れず、電位も変動しない。そして、容量素子33は出力端子55の電位であるVSSとnodePの電位であるVn1との電位差を保持している。

In the period T1, SSP is High, CK1 is Low, CK2 is Low, and CK3 is High. At this time, the potential of the gate of the

期間T2において、SSPがLow、CK1がHigh、CK2がLow、CK3がLowとなる。このときのトランジスタ31のゲートの電位はVSS、ソースとドレインのうち一方の電位はVDD、ソースとドレインのうち他方の電位はVn1となるため、当該トランジスタ31はオフする。回路61ではCK2がLowとなっているため、出力はフローティングとなる。回路62ではCK2がLow、CK3がLowとなっているため、出力はフローティングとなる。このときのトランジスタ32のゲートの電位はVn1、ソースとドレインのうち一方の電位はVDD、ソースとドレインのうち他方、つまり出力端子55の電位はVSSとなるため、当該トランジスタ32はオンして、出力端子55の電位が上昇し始める。すると、トランジスタ32のゲートと、ソースとドレインのうち他方の間に接続されている容量素子33は期間T1で保持した電位差をそのまま保持するため、ソースとドレインのうち他方の電位が上昇すると、ゲート電圧も同時に上昇する。このときの、nodePの電位をVn2とする。nodePの電位がVDDとトランジスタ32のしきい値電圧との和まで上昇すれば、出力端子14の電位の上昇はCK1と同じVDDになるところで止まる。いわゆる、ブートストラップ動作によって、CK1のHighの電位であるVDDまで、出力端子55の電位を上昇することができる。

In the period T2, SSP is Low, CK1 is High, CK2 is Low, and CK3 is Low. At this time, the potential of the gate of the

期間T3において、SSPがLow、CK1がLow、CK2がHigh、CK3がLowとなる。このとき、nodePの電位は、CK2がHighであるため、回路61からVSSが出力されるため、VSSとなり、OUT(1)の電位も回路62からVSSが出力されるため、VSSとなる。このときのトランジスタ31のゲート電位はVSS、ソースとドレインのうち一方の電位はVDD、ソースとドレインのうち他方の電位はVSSとなり、当該トランジスタ31はオフする。トランジスタ32のゲートの電位はVSS、ソースとドレインのうち一方の電位はVSS、ソースとドレインのうち他方の電位はVSSとなり、当該トランジスタ32はオフする。

In the period T3, SSP is Low, CK1 is Low, CK2 is High, and CK3 is Low. At this time, the potential of nodeP becomes VSS because VSS is output from the

上記説明した期間T1、期間T2、期間T3の動作により、期間T1にSSPが入力されるとOUT(1)が期間T2に出力される。つまり、SSPがクロック信号の1/3周期ずつシフトして出力される回路50をn段接続することにより、シフトレジスタ回路を構成している。

When SSP is input in the period T1, OUT (1) is output in the period T2 by the operations in the above-described periods T1, T2, and T3. That is, the shift register circuit is configured by connecting n stages of

図6に示した1段目の回路50を示したが、n段目の回路50を図52を参照して説明する。図52において、トランジスタ31、トランジスタ32、容量素子33、回路61、回路62、入力端子51、入力端子52、入力端子53、入力端子54、及び出力端子55は図6で説明したものと同様なものとする。入力端子51から入力される入力信号は前の段の回路の出力端子55と接続されていることを特徴とする。

Although the first-

なお、トランジスタ31のゲート、及びトランジスタ32のソースとドレインのうち他方は電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。また、トランジスタ31のソースとドレインのうち他方は信号線と接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。

Note that the gate of the

図6に示したシフトレジスタ回路で用いたトランジスタはNチャネル型トランジスタのみで構成する単極性回路であったが、Pチャネル型トランジスタのみで構成してもよい。もちろん、Pチャネル型トランジスタとNチャネル型トランジスタ組み合わせてもよい。トランジスタを全てPチャネル型トランジスタで構成した場合のシフトレジスタ回路を図56を参照して説明する。 Although the transistor used in the shift register circuit shown in FIG. 6 is a unipolar circuit composed of only N-channel transistors, it may be composed of only P-channel transistors. Of course, a P-channel transistor and an N-channel transistor may be combined. A shift register circuit in the case where all transistors are P-channel transistors will be described with reference to FIG.

図56に示す回路構成において、正電源VDD、負電源SS、入力端子51、入力端子52、入力端子53、入力端子54、トランジスタ551、トランジスタ552、及び容量素子553は図55と同様なものを用いることができる。回路561は、CK2がLowの場合にnodePにHighを出力し、CK2がHighの場合に出力がフローティングとなる機能を有する回路である。回路562は、CK2、及びCK3のいずれかがLowの場合にnodePにHighを出力し、CK2、及びCK3がHIghの場合に出力がフローティングとなる機能を有する回路である。

56, the positive power supply VDD, the negative power supply SS, the

図56の接続関係について説明する。トランジスタ551のゲートは入力端子51と接続され、ソースとドレインのうち一方は正電源VSSと接続され、ソースとドレインのうち他方は容量素子553の一方の電極、トランジスタ552のゲート及び回路561の出力端子、つまりnodePと接続されている。トランジスタ552のソースとドレインのうち一方は入力端子52と接続され、ソースとドレインのうち他方は回路562の出力端子、容量素子553の他方の電極及び出力端子55接続されている。入力端子53は回路561の入力端子及び回路562の第1の入力端子と接続され、入力端子54は回路562の第1のトランジスタの第2の入力端子と接続されている。

The connection relationship in FIG. 56 will be described. The gate of the

なお、トランジスタ551のゲート、及びトランジスタ552のソースとドレインのうち他方は電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線又は他の電源線と接続してもよいし、他の信号線と接続してもよい。また、トランジスタ551のソースとドレインのうち他方は信号線と接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。

Note that the other of the gate of the

次に、図60(a)を参照して、図56に示す回路561の構成の一例について説明する。

Next, an example of the configuration of the

図60(a)に示す回路561において、入力端子53、及びnodePは図55と同様なものとする。トランジスタ601はPチャネル型トランジスタであり、非結晶半導体、多結晶半導体、若しくは単結晶半導体によって構成されている。

In the

図60(a)の接続関係について説明する。トランジスタ601のゲートは、入力端子53と接続され、ソースとドレインのうち一方はVDDと接続され、ソースとドレインのうち他方はnodePと接続されている。

The connection relationship in FIG. 60A will be described. The gate of the

図60(a)の動作について説明する。入力端子53から入力されるCK2がLowの場合に、トランジスタ601はオンして、nodePにVDDを出力し、CK2がHighの場合に、トランジスタ601はオフして、nodePにはなにも出力されない。こうして、回路561は、CK2がLowの場合にHighを出力して、Highの場合にはフローティングになる機能を有する回路を構成している。また、回路構成は説明した回路構成に限らず、同じ機能を有する回路構成であればよい。

The operation of FIG. 60A will be described. When CK2 input from the

なお、トランジスタ601のソースとドレインのうち一方は信号線に接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。また、トランジスタ601のゲートは電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。

Note that one of the source and the drain of the

図60(b)を参照して、図56に示す回路562の構成の一例について説明する。

An example of the structure of the

図60(b)に示す回路562において、入力端子53、54、及び出力端子55は図55と同様なものとする。トランジスタ602、603はPャネル型トランジスタであり、非結晶半導体、多結晶半導体、若しくは単結晶半導体によって構成されている。

In the

図60(b)の動作について説明する。入力端子53から入力されるCK2がLowの場合に、トランジスタ602はオンして、出力端子55にVDDを出力し、CK2がHighの場合に、トランジスタ602はオフして、出力端子55にはなにも出力されない。入力端子54から入力されるCK3がLowの場合にトランジスタ603はオンして、出力端子55にVDDを出力し、CK3がHighの場合に出力端子55にはなにも出力されない。こうして、回路562は、CK2、CK3のいずれかががLowの場合にHighを出力して、Highの場合にはフローティングになる機能を有する回路を構成している。また、回路構成は説明した回路構成に限らず、同じ機能を有する回路構成であればよい。

The operation of FIG. 60B will be described. When CK2 input from the

なお、トランジスタ592のソースとドレインのうち一方は信号線に接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。また、トランジスタ592のゲートは電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。

Note that one of a source and a drain of the

次に、図7(a)を参照して、図6に示す回路61の構成の一例について説明する。

Next, an example of the configuration of the

図7(a)に示す回路61に示すように、入力端子53、及びnodePは図6と同様なものとする。トランジスタ71はNチャネル型トランジスタであり、非結晶半導体、多結晶半導体、若しくは単結晶半導体によって構成されている。

As shown in the

図7(a)の接続関係について説明する。トランジスタ71のゲートは入力端子53と接続され、ソースとドレインのうち一方はVSSと接続され、ソースとドレインのうち他方はnodePと接続されている。

The connection relationship in FIG. 7A will be described. The gate of the

図7(a)の動作について説明する。入力端子53から入力されるCK2がHighの場合に、トランジスタ71はオンして、nodePにVSSを出力し、CK2がLowの場合に、トランジスタ71はオフして、nodePにはなにも出力されない。こうして、回路61は、CK2がHighの場合にLowを出力して、Lowの場合にはフローティングになる機能を有する回路を構成している。また、回路構成は説明した回路構成に限らず、同じ機能を有する回路構成であればよい。

The operation of FIG. 7A will be described. When CK2 input from the

なお、トランジスタ71のソースとドレインのうち一方は信号線に接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。また、トランジスタ71のゲートは電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。

Note that one of the source and the drain of the

図7(b)を参照して、図6に示す回路62の構成の一例について説明する。

An example of the configuration of the

図7(b)に示す回路62に示すように、入力端子53、入力端子54及びOUT(1)は図6と同様なものとする。トランジスタ72、及びトランジスタ73はNチャネル型トランジスタであり、非結晶半導体、多結晶半導体、若しくは単結晶半導体によって構成されている。

As shown in the

図7(b)の接続関係について説明する。トランジスタ72のゲートは入力端子53と接続され、ソースとドレインのうち一方はVSSと接続され、ソースとドレインのうち他方は出力端子55と接続されている。トランジスタ73のゲートは入力端子54と接続され、ソースとドレインのうち一方はVSSと接続され、ソースとドレインのうち他方は出力端子55と接続されている。もちろん、トランジスタ72及びトランジスタ73のソースとドレインのうち一方を、トランジスタ71のソースとドレインのうち一方が接続されたVSSとなる配線と接続してもよい。

The connection relationship in FIG. 7B will be described. The gate of the

図7(b)の動作について説明する。入力端子53から入力されるCK2がHighの場合に、トランジスタ72はオンして、OUT(1)にVSSを出力し、CK2がLowの場合に、トランジスタ72はオフしてOUT(1)にはなにも出力されない。また、入力端子54から入力されるCK3がHighの場合に、トランジスタ73はオンして、OUT(1)にVSSを出力し、CK3がLowの場合に、トランジスタ73はオフしてOUT(1)にはなにも出力されない。こうして、回路62は、CK2及びCK3のいずれかがHighの場合にOUT(1)にLowを出力し、CK2及びCK3がLowの場合にはフローティングになる機能を有する回路を構成している。また、回路構成は説明した回路構成に限らず、同じ機能を有する回路構成であればよい。

The operation of FIG. 7B will be described. When CK2 input from the

なお、トランジスタ72のソースとドレインのうち一方、及びトランジスタ73のソースとドレインの一方は信号線に接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。また、トランジスタ72のゲートは電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。また、トランジスタ73のゲートは電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。

Note that one of the source and the drain of the

つまり、図6、図7に示す構造は、第1のトランジスタ(トランジスタ31)と、第2のトランジスタ(トランジスタ32)と、第3のトランジスタ(トランジスタ71)と、第4のトランジスタ(トランジスタ72)と、第5のトランジスタ(トランジスタ73)とを有し、第1のトランジスタは、ソースとドレインのうち一方が第1の配線(VDD)に接続され、ソースとドレインのうち他方が第2のトランジスタのゲート電極と第3のトランジスタのソースとドレインのうち他方に接続され、ゲート電極が第5の配線(入力端子51)に接続され、第2のトランジスタは、ソースとドレインのうち一方が第3の配線(入力端子52)に接続され、ソースとドレインのうち他方が第6の配線(出力端子55)に接続され、第3のトランジスタは、ソースとドレインのうち一方が第2の配線(VSS)に接続され、ソースとドレインのうち他方が第2のトランジスタのゲート電極に接続され、ゲート電極が第4の配線(入力端子53)に接続され、第4のトランジスタは、ソースとドレインのうち一方が第2の配線(VSS)に接続され、ソースとドレインのうち他方が第6の配線(出力端子55)に接続され、ゲート電極が第4の配線(入力端子53)に接続され、第5のトランジスタは、ソースとドレインのうち一方が第2の配線(VSS)に接続され、ソースとドレインのうち他方が第6の配線(出力端子55)に接続され、ゲート電極が第7の配線(入力端子54)に接続されている。また、第1のトランジスタにおいて、ソースとドレインのうち一方を第5の配線(入力端子51)に接続させた構成とすることも可能である。 That is, the structure shown in FIGS. 6 and 7 includes the first transistor (transistor 31), the second transistor (transistor 32), the third transistor (transistor 71), and the fourth transistor (transistor 72). And a fifth transistor (transistor 73). One of the source and drain of the first transistor is connected to the first wiring (VDD), and the other of the source and drain is the second transistor. The gate electrode is connected to the other of the source and drain of the third transistor, the gate electrode is connected to the fifth wiring (input terminal 51), and one of the source and drain of the second transistor is the third one. The other of the source and drain is connected to the sixth wiring (output terminal 55), and the third transistor is connected to the third wiring (input terminal 52). One of the source and drain is connected to the second wiring (VSS), the other of the source and drain is connected to the gate electrode of the second transistor, and the gate electrode is connected to the fourth wiring (input terminal 53). The fourth transistor has one of a source and a drain connected to the second wiring (VSS), and the other of the source and the drain connected to a sixth wiring (output terminal 55), and a gate The electrode is connected to the fourth wiring (input terminal 53), and the fifth transistor has one of the source and the drain connected to the second wiring (VSS), and the other of the source and the drain is the sixth wiring. The gate electrode is connected to the seventh wiring (input terminal 54). In the first transistor, one of a source and a drain can be connected to a fifth wiring (input terminal 51).

以上のような、シフトレジスタ回路では、CK2及びCK3のいずれかがHighになるに従って、出力端子55にVSSを供給することができる。つまり、非選択期間に、一定期間毎にVSSを入力することによって、ノイズを減らすことができ、且つ定常的にオンするトランジスタがないため、特性が劣化することを抑制することができる。また、第1の実施形態に比べ、非選択期間に示すように2倍の期間、VSSを出力端子55に供給することができるため、よりノイズを低減することができる。

In the shift register circuit as described above, VSS can be supplied to the

以下に、本実施形態の変更可能な構成例、及び動作例をいくつか述べる。また、以下で述べる構成例、及び動作例は「課題を解決するための手段」、「発明を実施するための最良の形態」、及び「実施例」について適用可能であり、第1の実施形態で説明した変更可能な構成例、及び動作例を本実施形態に適用することができる。 Hereinafter, some configuration examples and operation examples of the embodiment that can be changed will be described. In addition, the configuration example and the operation example described below are applicable to “means for solving the problem”, “best mode for carrying out the invention”, and “example”, and are described in the first embodiment. The changeable configuration example and operation example described in the above can be applied to the present embodiment.

図6に示すように、nodePと、VSS又はVDDの間に容量素子を接続してもよい。容量素子を接続することでより、nodePの電位を安定させることができる。 As illustrated in FIG. 6, a capacitor may be connected between nodeP and VSS or VDD. By connecting the capacitor, the potential of the node P can be stabilized.

図6に示すように、容量素子33はブートストラップ動作をするために接続されており、トランジスタ32のゲートと、ソースとドレインのうち他方との間にブートストラップ動作できるだけの寄生容量などがあれば、なくてもよい。また、容量素子33の形成方法はどこでもよい。例えば、非結晶半導体層とゲート配線層との間で容量素子を形成してもよいし、半導体層と配線との間で容量素子を形成してもよい。半導体層とゲート配線層とで容量素子を形成する場合は、ボトムゲートトランジスタ、トップゲート型トランジスタに関らず薄いGI膜(ゲート絶縁膜)を挟んで形成されているため、小さい面積でより多くの容量値を得ることが可能となるため、有利である。

As shown in FIG. 6, the

図6に示すように、回路61は必ずしも必要ではない。つまり、回路62によって、一定期間毎にVSSを出力しているため、nodePにノイズがあってもトランジスタ32をオフしていればよいためである。こうすることで、素子数を減らすことができる。そのとき、nodePと、VSS又はVDDの間に容量素子を接続してもよい。

As shown in FIG. 6, the

図6に示した回路62の入力端子に次の段の回路50の出力を入力してもよいし、同様に回路35の入力端子には次の段の回路50の出力を入力してもよいし、回路61の入力端子、及び回路62の入力端子に次の段の回路50の出力を入力してもよい。次の段の回路50の出力を利用することで、制御信号だけに同期するのではなく実際のシフトレジスタ回路の出力とも同期することができるため、よりシフトレジスタ回路の動作にあった電位の切り替えができるため有利である。

The output of the

図6に示すように、nodePとVSS、又はVDDの間に容量素子を接続してもよい。容量素子を接続することでより、nodePの電位を安定させることができる。 As shown in FIG. 6, a capacitor may be connected between nodeP and VSS or VDD. By connecting the capacitor, the potential of the node P can be stabilized.

(第3の実施形態)

本実施形態は、非選択期間の出力電圧のノイズを減らすために、非選択期間においてVSSを出力することでノイズを減らすことを特徴とするシフトレジスタ回路の構成、及び動作について、図2、図5、図8乃至図10を用いて説明する。

(Third embodiment)

In this embodiment, in order to reduce noise in the output voltage during the non-selection period, the noise is reduced by outputting VSS in the non-selection period. 5 and FIG. 8 to FIG.

図5に示すシフトレジスタ回路の構成、及び動作は第2の実施形態で説明したものと同様なものを用いることができる。 The structure and operation of the shift register circuit shown in FIG. 5 can be the same as those described in the second embodiment.

図8を参照して、1段目の回路50であるSR(1)の構成について説明する。図8に示す回路50は、入力端子51、入力端子52、入力端子53、入力端子54、出力端子55、トランジスタ31、トランジスタ32、容量素子33、回路81、回路82、回路83から構成されている。

With reference to FIG. 8, the configuration of SR (1) which is the

入力端子51、入力端子52、入力端子53、入力端子54、出力端子55、トランジスタ31、トランジスタ32、容量素子33は、図5で説明したものと同様なものとする。

The

回路81は、CK2がHighの場合にnodePにLowを出力し、CK2がLowの場合に出力がフローティングになる機能を有する回路である。回路82は、回路83の出力がHighで、且つCK1、CK2及びCK3のいずれかがHighの場合に出力端子55にLowを出力し、CK1、CK2及びCK3がLowの場合に出力がフローティングになる。そして、回路83からの出力がLowで、且つCK2及びCK3のいずれかがHighの場合に出力端子55にLowを出力し、CK2及びCK3がLowの場合に出力がフローティングとなる機能を有する回路である。回路83は、nodePの電位がVDD付近、もしくはそれ以上の場合に回路82にLowを出力し、nodePの電位がVSSの場合に回路82にHighを出力する回路である。

The

図8の接続関係について説明する。トランジスタ31のゲートは入力端子51と接続され、ソースとドレインのうち一方はVDDと接続され、ソースとドレインのうち他方は容量素子33の一方の電極、トランジスタ32のゲート、回路83の入力端子及び回路81の出力端子、つまりnodePと接続されている。トランジスタ32のソースとドレインのうち一方は入力端子52と接続され、ソースとドレインのうち他方は回路82の出力端子、容量素子33の他方の端子、及び出力端子55と接続されている。入力端子52は回路82の入力端子と接続され、入力端子53は回路81の入力端子、及び回路82の入力端子と接続され、入力端子54は回路82の入力端子と接続されている。回路83の出力端子は回路82の入力端子と接続されている。

The connection relationship in FIG. 8 will be described. The gate of the

図8の動作について、図2に示す本実施形態のタイミングチャートを参照して、期間T1、期間T2、及び期間T3に分けて説明する。また、初期状態として、nodeP、及びOUT(1)の電位はVSSとする。 The operation of FIG. 8 will be described by dividing it into a period T1, a period T2, and a period T3 with reference to the timing chart of the present embodiment shown in FIG. Further, as an initial state, the potentials of nodeP and OUT (1) are VSS.

期間T1において、SSPがHigh、CK1がLow、CK2がLow、CK3がHighとなる。このときのトランジスタ31のゲートの電位はVDD、ソースとドレインのうち一方の電位はVDD、ソースとドレインのうち他方の電位はVSSとなるため、当該トランジスタ31がオンして、nodePの電位がVSSから上昇し始める。nodePの電位の上昇はVDDからトランジスタ31のしきい値電圧分小さい電位となるところで止まり、トランジスタ31はオフする。このときのnodePの電位をVn1とする。回路81は、CK2がLowとなっているため、出力はフローティングとなる。そのため、nodePには電荷が供給されないため、フローティングとなる。回路83は、nodePの電位がVn1となるため、回路82の入力端子にLowを出力する。回路82は、回路83の出力がLow、CK1がLow、CK2がLow、CK3がHighとなるため、Lowを出力する。このときのトランジスタ32のゲート電位はVn1、ソースとドレインのうち一方の電位はVSS、ソースとドレインのうち他方の電位はVSSとなるため、当該トランジスタ32はオンしている。しかし、ソースとドレインのうち一方の電位とソースとドレインのうち他方の電位とが同電位であり、電荷の移動はないため、電流は流れず、電位も変動しない。そして、容量素子33には出力端子55の電位であるVSSとnodePの電位であるVn1との電位差を保持している。

In the period T1, SSP is High, CK1 is Low, CK2 is Low, and CK3 is High. At this time, the potential of the gate of the

期間T2において、SSPがLow、CK1がHigh、CK2がLow、CK3がLowとなる。このときのトランジスタ31のゲートの電位はVSS、ソースとドレインのうち一方の電位はVDD、ソースとドレインのうち他方の電位はVn1となるため、当該トランジスタ31はオフする。回路61ではCK2がLowとなっているため、出力はフローティングなる。回路83は、nodePの電位がVn1となるため回路82の入力端子にLowを出力する。回路82は、回路83の出力がLow、CK1がHigh、CK2がLow、CK3がLowとなるため、出力はフローティングとなる。このときのトランジスタ32のゲートの電位はVn1、ソースとドレインのうち一方の電位はVDD、ソースとドレインのうち他方、つまり出力端子55の電位はVSSとなるため、当該トランジスタ32がオンして、出力端子55の電位が上昇し始める。すると、トランジスタ32のゲートと、ソースとドレインのうち他方の間に接続されている容量素子33は期間T1で保持した電位差をそのまま保持するため、ソースとドレインのうち他方の電位が上昇すると、ゲート電圧も同時に上昇する。このときの、nodePの電位をVn2とする。nodePの電位がVDDとトランジスタ32のしきい値電圧との和まで上昇すれば、出力端子55の電位の上昇はCK1の電位と同じVDDになるところで止まる。いわゆる、ブートストラップ動作によって、CK1のHighの電位であるVDDまで、出力端子55の電位を上昇することができる。

In the period T2, SSP is Low, CK1 is High, CK2 is Low, and CK3 is Low. At this time, the potential of the gate of the

期間T3において、SSPがLow、CK1がLow、CK2がHight、CK3がLowとなる。このとき、nodePの電位は、CK2がHighであるため、回路81からVSSが出力されるため、VSSとなり、回路83は回路82の入力端子にHighを出力する。OUT(1)の電位も回路82からVSSが出力されるため、VSSとなる。このときのトランジスタ31のゲート電位はVSS、ソースとドレインのうち一方の電位はVDD、ソースとドレインのうち他方の電位はVSSとなり、当該トランジスタ31はオフする。トランジスタ32のゲートの電位はVSS、ソースとドレインのうち一方の電位はVSS、ソースとドレインのうち他方の電位はVSSとなり、当該トランジスタ32はオフする。

In the period T3, SSP is Low, CK1 is Low, CK2 is High, and CK3 is Low. At this time, the potential of nodeP is VSS because CK <b> 2 is High and VSS is output from the

上記説明した期間T1、期間T2、期間T3の動作により、期間T1にSSPが入力されるとOUT(1)が期間T2に出力される。つまり、SSPがクロック信号の1/3周期ずつシフトして出力される回路50をn段接続することにより、シフトレジスタ回路を構成している。

When SSP is input in the period T1, OUT (1) is output in the period T2 by the operations in the above-described periods T1, T2, and T3. That is, the shift register circuit is configured by connecting n stages of

図8に1段目の回路50を示したが、n段目の回路50を図53を参照して説明する。

Although the

図53において、トランジスタ31、トランジスタ32、容量素子33、回路81、回路82、回路83、入力端子51、入力端子52、入力端子53、入力端子54及び出力端子55は、図8で説明したものと同様なものとする。入力端子51から入力される入力信号は前の段の回路の出力端子55と接続されていることを特徴とする。

53, the

図8に示したシフトレジスタ回路で用いたトランジスタはNチャネル型トランジスタのみで構成する単極性回路であったが、Pチャネル型トランジスタのみで構成してもよい。もちろん、Pチャネル型トランジスタとNチャネル型トランジスタ組み合わせてもよい。トランジスタを全てPチャネル型トランジスタで構成した場合のシフトレジスタ回路を図57を参照して説明する。 Although the transistor used in the shift register circuit shown in FIG. 8 is a unipolar circuit composed of only N-channel transistors, it may be composed of only P-channel transistors. Of course, a P-channel transistor and an N-channel transistor may be combined. A shift register circuit in the case where all transistors are P-channel transistors will be described with reference to FIG.

図57に示す回路構成において、正電源VDD、負電源SS、入力端子51、入力端子52、入力端子53、入力端子54、トランジスタ551、トランジスタ552、及び容量素子553は図55と同様なものを用いることができる。回路571は、CK2がLowの場合にnodePにHighを出力し、CK2がHighの場合に出力がフローティングとなる機能を有する回路である。回路572はCK1、CK2、CK3のうちいずれかがLowのときに出力端子55にHighを出力する回路である。

In the circuit configuration shown in FIG. 57, the positive power supply VDD, the negative power supply SS, the

図57の接続関係について説明する。トランジスタ551のゲートは入力端子51と接続され、ソースとドレインのうち一方は正電源VSSと接続され、ソースとドレインのうち他方は容量素子553の一方の電極、トランジスタ552のゲート及び回路571の出力端子、つまりnodePと接続されている。トランジスタ552のソースとドレインのうち一方は入力端子52と接続され、ソースとドレインのうち他方は回路572の出力端子、容量素子553の他方の電極、及び出力端子55と接続されている。入力端子52は回路572の入力端子と接続されている。入力端子53は回路571の入力端子、及び回路572の第1の入力端子と接続され、入力端子54は回路572の第1のトランジスタの第2の入力端子と接続されている。

The connection relationship in FIG. 57 will be described. The gate of the

なお、トランジスタ551のゲート及びトランジスタ552のソースとドレインのうち他方は電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。また、トランジスタ551のソースとドレインのうち他方は信号線と接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。

Note that the other of the gate of the

次に、図9(a)を参照して、図8に示す回路81の構成の一例について説明する。

Next, an example of the configuration of the

図9(a)に示す回路81において、入力端子53、及びnodePは図8と同様なものとする。トランジスタ91はNチャネル型トランジスタであり、非結晶半導体、多結晶半導体、若しくは単結晶半導体によって構成されている。

In the

図9(a)の接続関係について説明する。トランジスタ91のゲートは入力端子53と接続され、ソースとドレインのうち一方はVSSと接続され、ソースとドレインのうち他方はnodePと接続されている。

The connection relationship in FIG. 9A will be described. The gate of the transistor 91 is connected to the

図9(a)の動作について説明する。入力端子53から入力されるCK2がHighの場合に、トランジスタ91はオンして、nodePにVSSを出力し、CK2がLowの場合に、トランジスタ91はオフして、nodePにはなにも出力されない。こうして、回路81は、CK2がHighの場合にLowを出力して、Lowの場合にはフローティングになる機能を有する回路を構成している。また、回路構成は説明した回路構成に限らず、同じ機能を有する回路構成であればよい。また、Pチャネル型トランジスタで構成した場合の構成例を図61に示す。同業者であれば容易に変更が可能である。

The operation of FIG. 9A will be described. When CK2 input from the

なお、トランジスタ91のソースとドレインのうち一方は信号線に接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。また、トランジスタ91のゲートは電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。 Note that one of the source and the drain of the transistor 91 may be connected to a signal line. For example, the transistor 91 may be connected to a signal line such as CK1, CK2, CK3, or SSP, another signal line, or another power source. You may connect with a line. The gate of the transistor 91 may be connected to a power supply line. For example, the transistor 91 may be connected to a power supply line such as a positive power supply VDD or a negative power supply VSS, or another power supply line, or may be connected to another signal line. Also good.

図9(b)を参照して、図8に示す回路82の構成の一例について説明する。

With reference to FIG. 9B, an example of the configuration of the

図9(b)に示す回路82において、入力端子52、入力端子53、入力端子54及びOUT(1)は図8と同様なものとする。トランジスタ92、トランジスタ93、トランジスタ94及びトランジスタ95はNチャネル型トランジスタであり、非結晶半導体、多結晶半導体、若しくは単結晶半導体によって構成されている。Voutは回路82の出力である。

In the

図9(b)の接続関係について説明する。トランジスタ95のゲートはVoutが接続され、ソースとドレインのうち一方は入力端子52と接続され、ソースとドレインのうち他方はトランジスタ92のゲートと接続されている。トランジスタ92のソースとドレインのうち一方はVSSと接続され、ソースとドレインのうち他方は出力端子55と接続されている。トランジスタ93のゲートは入力端子53と接続され、ソースとドレインのうち一方はVSSと接続され、ソースとドレインのうち他方は出力端子55と接続されている。トランジスタ94のゲートは入力端子54と接続され、ソースとドレインのうち一方はVSSと接続され、ソースとドレインのうち他方は出力端子55と接続されている。

The connection relationship in FIG. 9B will be described. The gate of the

図9(b)の動作について説明する。回路83の出力から入力されるVoutがHighの場合に、トランジスタ95はオンして、トランジスタ92のゲートにCK1を信号を伝達する。VoutがLowの場合に、トランジスタ95はオフして、トランジスタ92のゲートにCK1の信号は伝達されないため、前の状態を保持する。ここで、トランジスタ95がオンして、且つ入力端子52から入力されるCK1がHighの場合に、トランジスタ92はオンして、OUT(1)にVSSを出力し、CK1がLowの場合に、トランジスタ92はオフして、OUT(1)にはなにも出力されない。入力端子53から入力されるCK2がHighの場合に、トランジスタ93はオンして、OUT(1)にVSSを出力し、CK2がLowの場合に、トランジスタ93はオフして、OUT(1)にはなにも出力されない。入力端子54から入力されるCK3がHighの場合に、トランジスタ94がオンして、OUT(1)にVSSが出力され、CK3がLowの場合に、トランジスタ94はオフして、OUT(1)にはなにも出力されない。こうして、回路82は、回路83の出力がHighで、且つCK1、CK2、及びCK3のいずれかがHighの場合に出力端子55にLowを出力し、CK1、CK2、及びCK3がLowの場合に出力がフローティングになる。そして、回路83からの出力がLowで、且つCK2、及びCK3のいずれかがHighの場合に出力端子55にLowを出力し、CK2、及びCK3がLowの場合に出力がフローティングとなる機能を有する回路を構成している。また、回路構成は説明した回路構成に限らず、同じ機能を有する回路構成であればよい。

The operation of FIG. 9B will be described. When Vout input from the output of the

なお、トランジスタ92のソースとドレインのうち一方、トランジスタ93のソースとドレインのうち一方、及びトランジスタ94のソースとドレインのうち一方は信号線に接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。また、トランジスタ95のソースとドレインのうち一方、トランジスタ92のゲート、トランジスタ93のゲート、トランジス94のゲートは電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。

Note that one of the source and the drain of the

次に、図10(a)を参照して、図8に示す回路83の構成の一例について説明する。

Next, an example of the configuration of the

図10(a)に示す回路83おいて、nodeP、Voutは図8と同様なものとする。トランジスタ101はNチャネル型トランジスタであり、非結晶半導体、多結晶半導体、若しくは単結晶半導体によって構成されている。抵抗素子102は、抵抗成分を持つ抵抗素子である。抵抗成分を持っていれば、いかなる線形素子でもよいし、非線形素子でもよい。例えば、ダイオード接続したトランジスタを接続してもよい。

In the

抵抗素子102として、トランジスタを用いた場合の構成例について図48を参照して説明する。nodeP、Vout、トランジスタ101、正電源線VDD、及び負電源VSSは図10と同様なものとする。トランジスタ481はNチャネル型トランジスタであり、非結晶半導体、多結晶半導体、若しくは単結晶半導体によって構成されている。トランジスタ481のソースとドレインのうち一方は正電源VDDと接続され、ソースとドレインのうち他方はVoutと接続され、ゲートはソースとドレインのうち一方と接続されダイオード接続されている。VoutはVSSからオンするトランジスタ101を介して電荷が供給されなければ、VDDからトランジスタ481のしきい値電圧引いた電位なる。こうして、nodePがLowとなるとトランジスタ101はオフしてVoutの電位はVDDからトランジスタ481のしきい値電圧引いた電位となり、nodePがHighとなりトランジスタ101がオンするとVoutの電位はVSSの電位なる。

A structure example in which a transistor is used as the

図10(a)の接続関係について説明する。トランジスタ101のゲートはnodePと接続され、トランジスタ101のソースとドレインのうち一方は抵抗素子102の一方の端子、及びVoutと接続され、ソースとドレインのうち他方はVSSと接続されている。抵抗素子102の他方の端子はVDDと接続されている。

The connection relationship in FIG. 10A will be described. The gate of the

図10(a)の動作について説明する。nodePの電位がVSSとトランジスタ101のしきい値電圧との和の電圧以上だった場合に、トランジスタ101はオンして、VoutにVSSを出力する。nodePの電位がVSSとトランジスタ101のしきい値電圧との和の電圧未満だった場合に、トランジスタ101はオフして、Voutには抵抗素子102を介してVDDが出力される。このように、nodePの電位がVSSとトランジスタ101のしきい値電圧との和の電圧以上だった場合に回路82の入力端子にLowを出力し、nodePの電位がVSSとトランジスタ101のしきい値電圧との和の電圧未満だった場合に回路82の入力端子にHighを出力する機能を有する回路を構成している。また、回路構成は説明した回路構成に限らず、同じ機能を有する回路構成であればよい。また、図62に図10の回路構成をPチャネル型トランジスタを用いた場合の構成例を示す。

The operation of FIG. 10A will be described. When the potential of nodeP is equal to or higher than the sum of VSS and the threshold voltage of the

なお、トランジスタ101のソースとドレインのうち他方は信号線に接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。また、トランジスタ101のゲートは電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。

Note that the other of the source and the drain of the

図10(b)を参照して、図8に示す回路83の構成の別の一例について説明する。

With reference to FIG. 10B, another example of the configuration of the

図10(b)に示す回路83に示すように、nodeP、Voutは図8と同様なものとする。OUT(2)は次の2段目の回路50の出力である。例えば、n段目の回路50だとするとn+1段目の回路50の出力である。トランジスタ102、及びトランジスタ103はNチャネル型トランジスタであり、非結晶半導体、多結晶半導体、若しくは単結晶半導体によって構成されている。容量素子104は2つの電極を持った容量素子である。

As shown in the

図10(b)の接続関係について説明する。トランジスタ102のゲートはOUT(2)と接続され、ソースとドレインのうち一方はVDDと接続され、ソースとドレインのうち他方はトランジスタ103のソースとドレインのうち一方、容量素子104の一方の電極、及びVoutと接続されている。トランジスタ103のゲートはnodeP、ソースとドレインのうち他方はVSSと接続されている。容量素子104の他方の電極はVSSと接続されている。

The connection relationship in FIG. 10B will be described. The gate of the

図10(b)の動作について説明する。nodePの電位がVSSとトランジスタ103のしきい値電圧との和の電圧以上だった場合に、トランジスタ103はオンしてVSSをVoutに出力する。nodePの電位がVSSとトランジスタ103のしきい値電圧との和の電圧以未満だった場合に、トランジスタ103はオフして出力はフローティングとなる。OUT2がHighだった場合に、トランジスタ102はオンしてVoutにVDDとトランジスタ102のしきい値電圧との差の電圧を出力する。OUT2がLowだった場合に、トランジスタ102はオフして出力はフローティングとなる。つまり、nodePの電位がVDD付近、若しくはそれ以上だった場合に、VoutはLowを出力し、nodePの電位がVSSだった場合に、VoutはHighを出力する機能を有する回路を構成している。また、回路構成は説明した回路構成に限らず、同じ機能を有する回路構成であればよい。

The operation of FIG. 10B will be described. When the potential of nodeP is equal to or higher than the sum of VSS and the threshold voltage of the

なお、トランジスタ102のゲート及びトランジスタ103のゲートは電源線と接続してもよく、例えば正電源VDD、負電源VSSなどの電源線、又は他の電源線と接続してもよいし、他の信号線と接続してもよい。また、トランジスタ103のソースとドレインのうち他方は信号線に接続してもよく、例えばCK1、CK2、CK3、SSPなどの信号線、又は他の信号線と接続してもよいし、他の電源線と接続してもよい。

Note that the gate of the

以上のような、シフトレジスタ回路では、非動作期間において、CK1、CK2及びCK3のうちいずれかがHighとなれば、出力端子55にVSSを供給することができる。つまり、非選択期間における出力端子55には常時VSSが供給されているため、電位が安定し、ノイズを無くすことができ、且つ定常的にオンするトランジスタがないため、特性が劣化することを抑制することができる。また、nodePにも一定期間毎にVSSを供給することによって、トランジスタ32を確実にオフすることができる。

In the shift register circuit as described above, VSS can be supplied to the

以下に、本実施形態の変更可能な構成例、及び動作例をいくつか述べる。また、以下で述べる構成例、及び動作例は「課題を解決するための手段」、「発明を実施するための最良の形態」、及び「実施例」について適用可能であり、第1の実施形態で説明した変更可能な構成例、及び動作例を本実施形態に適用することができる。 Hereinafter, some configuration examples and operation examples of the embodiment that can be changed will be described. In addition, the configuration example and the operation example described below are applicable to “means for solving the problem”, “best mode for carrying out the invention”, and “example”, and are described in the first embodiment. The changeable configuration example and operation example described in the above can be applied to the present embodiment.

図9に示すように、トランジスタ92のゲートは、トランジスタ95がオフのとき浮遊となる。そのため、トランジスタ92のゲート容量に電位を保持しているが、保持しきれない場合は、容量素子を接続してもよい。その場合、トランジスタ92のゲートとVDD、又はVSSとの間に容量素子を接続することが望ましい。

As shown in FIG. 9, the gate of the

図10(b)に示すように、Voutに容量素子104が接続されているが、Voutの接続先が十分な容量をもっていれば設けない構成としてもよい。出力であるVoutに接続されている容量素子104を無くすことで、より高速な動作が可能となる。

As shown in FIG. 10B, the

図10(b)に示すように、トランジスタ103のゲートにはnodePが接続されているが、入力端子51を接続してもよい。入力端子51を接続することによって、トランジスタ102とトランジスタ103とが同時にオンする期間がなくなりトランジスタ102、及びトランジスタ103を介した貫通電流がなくなるため、誤動作しにくくなり、且つ消費電力が小さくなる。

As shown in FIG. 10B, the node P is connected to the gate of the

(第4の実施形態)

本実施形態は、非選択期間の出力電圧のノイズを減らすために、一定時間毎にVSSを出力することでノイズを減らすことを特徴とするシフトレジスタ回路の構成、及び動作について、図2、図5、図11及び図12を用いて説明する。

(Fourth embodiment)

In this embodiment, in order to reduce noise in the output voltage during the non-selection period, the noise is reduced by outputting VSS at regular time intervals, and the configuration and operation of the shift register circuit, which is characterized in that FIG. 5 and FIG. 11 and FIG.

図5に示すシフトレジスタ回路の構成、及び動作は第2の実施形態で説明したものと同様なものを用いることができる。 The structure and operation of the shift register circuit shown in FIG. 5 can be the same as those described in the second embodiment.

図11を参照して、1段目の回路50であるSR(1)の構成について説明する。図11に示す回路は、入力端子51、入力端子52、入力端子53、入力端子54、出力端子55、トランジスタ31、トランジスタ32、容量素子33、回路111、回路82、回路83から構成されている。入力端子51、入力端子52、入力端子53、入力端子54、出力端子55、回路82、回路83、トランジスタ31、トランジスタ32、容量素子33、及びnodePは図8で説明したものと同様なものとする。

With reference to FIG. 11, the configuration of SR (1) which is the

回路111は回路83からの出力がHighの場合で、且つCK1、CK2及びCK3のいずれかがHighの場合にnodePにLowを出力し、CK1、CK2及びCK3がLowの場合に出力がフローティングとなる。そして、回路83からの出力がLowの場合で、且つCK2がHighの場合にnodePにLowを出力し、CK2がLowの場合に出力がフローティングとなる機能を有する回路である。

The

図11接続関係について説明する。トランジスタ31のゲートは入力端子51と接続され、ソースとドレインのうち一方はVDDと接続され、ソースとドレインのうち他方は容量素子33の一方の電極、トランジスタ32のゲート、回路83の入力端子及び回路111の出力端子、つまりnodePと接続されている。トランジスタ32のソースとドレインのうち一方は入力端子52と接続され、ソースとドレインのうち他方は回路82の出力端子、容量素子33の他方の電極、及び出力端子55と接続されている。入力端子52は回路82の入力端子及び回路111の入力端子と接続され、入力端子53は回路82の入力端子及び回路111の入力端子と接続され、入力端子54は回路82の入力端子及び回路111の入力端子と接続されている。回路83の出力端子は回路82の入力端子、及び回路111の入力端子と接続されている。

11 will be described. The gate of the

図11の動作について、図2に示す本実施形態のタイミングチャートを参照して、期間T1、期間T2、及び期間T3に分けて説明する。また、初期状態として、nodeP、及びOUT(1)の電位はVSSとする。 The operation of FIG. 11 will be described by dividing it into a period T1, a period T2, and a period T3 with reference to the timing chart of this embodiment shown in FIG. Further, as an initial state, the potentials of nodeP and OUT (1) are VSS.