JP5192732B2 - Semiconductor device and IC label, IC tag, and IC card including the semiconductor device - Google Patents

Semiconductor device and IC label, IC tag, and IC card including the semiconductor device Download PDFInfo

- Publication number

- JP5192732B2 JP5192732B2 JP2007138891A JP2007138891A JP5192732B2 JP 5192732 B2 JP5192732 B2 JP 5192732B2 JP 2007138891 A JP2007138891 A JP 2007138891A JP 2007138891 A JP2007138891 A JP 2007138891A JP 5192732 B2 JP5192732 B2 JP 5192732B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- battery

- signal

- film

- antenna

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

- Charge And Discharge Circuits For Batteries Or The Like (AREA)

Description

本発明は半導体装置に関する。特に、電波を介したデータの送受信及び電力の受信を行う半導体装置に関する。更に、電波を介した半導体装置と当該半導体装置とデータの送受信を行うアンテナ及びリーダライタ、並びに当該半導体装置に電力を供給するためのアンテナ及び充電器、を用いた通信システムに関する。 The present invention relates to a semiconductor device. In particular, the present invention relates to a semiconductor device that transmits and receives data and receives power via radio waves. Further, the present invention relates to a communication system using a semiconductor device via radio waves, an antenna and a reader / writer for transmitting / receiving data to / from the semiconductor device, and an antenna and a charger for supplying power to the semiconductor device.

なお、本明細書でいう半導体装置とは、半導体特性を利用することで機能しうる装置全般を指すものとする。 Note that a semiconductor device in this specification refers to all devices that can function by utilizing semiconductor characteristics.

近年、電磁界または電波等の無線通信を利用した個体識別技術が注目を集めている。特に、無線通信によりデータの交信を行う半導体装置として、RFID(Radio Frequency Identification)タグを利用した個体識別技術が注目を集めている。RFIDタグ(以下、単にRFIDという)は、IC(Integrated Circuit)タグ、ICチップ、RFタグ、無線タグ、電子タグとも呼ばれる。RFIDを用いた個体識別技術は、個々の対象物の生産、管理等に役立てられ始めており、個人認証への応用も期待されている。 In recent years, individual identification technology using wireless communication such as electromagnetic fields or radio waves has attracted attention. In particular, as a semiconductor device that communicates data by wireless communication, an individual identification technique using an RFID (Radio Frequency Identification) tag has attracted attention. An RFID tag (hereinafter simply referred to as RFID) is also called an IC (Integrated Circuit) tag, an IC chip, an RF tag, a wireless tag, or an electronic tag. Individual identification technology using RFID has begun to be used for production and management of individual objects, and is expected to be applied to personal authentication.

RFIDは、電源を内蔵するか、外部から電源供給を受けるかの違いにより、RFIDの情報を含んだ電波または電磁波を送信することが可能なアクティブタイプ(能動タイプ)のRFIDと、外部からの電波または電磁波(搬送波)の電力を利用して駆動するパッシブタイプ(受動タイプ)のRFIDとの二つのタイプに分けることができる(アクティブタイプに関しては特許文献1、パッシブタイプに関しては特許文献2を参照)。このうち、アクティブタイプのRFIDにおいては、RFIDを駆動するための電源を内蔵しており、電源として電池を備えて構成されている。また、パッシブタイプにおいては、RFIDを駆動するための電源として外部からの電波または電磁波(搬送波)を利用しており、電池を備えることのない構成を実現している。

RFID is an active type (active type) RFID capable of transmitting radio waves or electromagnetic waves containing RFID information and external radio waves depending on whether the power supply is built in or externally supplied with power. Alternatively, it can be divided into two types: passive type (passive type) RFID driven using electromagnetic wave (carrier wave) power (see

図31にアクティブタイプのRFIDの具体的な構成についてブロック図を示す。図31のアクティブタイプのRFID3100では、アンテナ回路3101によって受信された通信信号が信号制御回路3102における復調回路3105、増幅回路3106に入力される。通常、13.56MHz、915MHzなどのキャリアをASK変調、PSK変調などの処理をおこなって送られてくる。ここで図31においては、例として13.56MHzの通信信号について示す。図31において、信号を処理するためには基準となるクロック信号が必要であり、ここでは13.56MHzのキャリアをクロックに用いている。増幅回路3106は13.56MHzのキャリアを増幅し、クロックとして論理回路3107に供給する。またASK変調やPSK変調された通信信号は復調回路3105で復調される。復調後の信号も論理回路3107に送られ解析される。論理回路3107で解析された信号はメモリコントロール回路3108に送られ、それに基づき、メモリコントロール回路3108はメモリ回路3109を制御し、メモリ回路3109に記憶されたデータを取り出し論理回路3110に送られる。論理回路3110でそのデータがエンコード処理されたのち増幅回路3111で増幅され、その信号によって、変調回路3112はキャリアに変調をかける。ここで図31における電源は、信号制御回路の外に設けられる電池3103によって電源回路3104を介して供給している。そして電源回路3104は増幅回路3106、復調回路3105、論理回路3107、メモリコントロール回路3108、メモリ回路3109、論理回路3110、増幅回路3111、変調回路3112などに電力を供給する。このようにしてアクティブタイプのRFIDは動作する。

FIG. 31 is a block diagram showing a specific configuration of an active type RFID. In the

図32に、パッシブタイプのRFIDの具体的な構成についてブロック図を示す。図32のパッシブタイプのRFID3200では、アンテナ回路3201によって受信された通信信号が信号制御回路3202における復調回路3205、増幅回路3206に入力される。通常、通信信号は13.56MHz、915MHzなどのキャリアをASK変調、PSK変調などの処理をおこなって送られてくる。図32においては、通信信号として13.56MHzの例について示す。図32において、信号を処理するためには基準となるクロック信号が必要であり、ここでは13.56MHzのキャリアをクロックに用いている。増幅回路3206は13.56MHzのキャリアを増幅し、クロックとして論理回路3207に供給する。またASK変調やPSK変調された通信信号は復調回路3205で復調される。復調後の信号も論理回路3207に送られ解析される。論理回路3207で解析された信号はメモリコントロール回路3208に送られ、それに基づき、メモリコントロール回路3208はメモリ回路3209を制御し、メモリ回路3209に記憶されたデータを取り出し論理回路3210に送られる。論理回路3210でエンコード処理されたのち増幅回路3211で増幅され、その信号によって、変調回路3212はキャリアに変調をかける。一方、整流回路3203に入った通信信号は整流され、電源回路3204に入力される。電源回路3204は増幅回路3206、復調回路3205、論理回路3207、メモリコントロール回路3208、メモリ回路3209、論理回路3210、増幅回路3211、変調回路3212などに電力を供給する。このようにしてパッシブタイプのRFIDは動作する。

しかしながら、図31に示したように、駆動用の電池を備えたアクティブタイプのRFIDを有する半導体装置の場合、個体情報の送受信、信号の送受信に必要な電波の強度設定に応じて、電池は経時的に消耗していき、最終的には個体情報を送受信するのに必要な電力を発生できなくなるといった課題があった。このため、駆動用の電池を備えたアクティブタイプのRFIDを有する半導体装置を使用し続けるためには、電池の残存容量の確認や電池の交換をする作業が必要となるという課題があった。 However, as shown in FIG. 31, in the case of a semiconductor device having an active type RFID equipped with a battery for driving, the battery is used over time according to the intensity setting of radio waves necessary for transmission / reception of individual information and transmission / reception of signals. However, there is a problem that power necessary for transmitting / receiving individual information cannot be generated. For this reason, in order to continue to use a semiconductor device having an active type RFID equipped with a driving battery, there is a problem in that it is necessary to check the remaining capacity of the battery and replace the battery.

また、図32に示したように、駆動するための電源として外部からの電波または電磁波(搬送波)の電力を利用するパッシブタイプのRFIDを有する半導体装置の場合、長距離の信号の送受信、信号の送受信に必要な電力の確保が難しく、良好な送受信状態を実現することが難しいといった課題があった。このため、外部からの電波または電磁波(搬送波)の電力を電源として利用するパッシブタイプのRFIDを有する半導体装置の使用は、電波または電磁波(搬送波)の供給手段であるリーダ/ライタのアンテナから近距離に限られるという課題があった。 Further, as shown in FIG. 32, in the case of a semiconductor device having a passive type RFID that uses electric power of an external radio wave or electromagnetic wave (carrier wave) as a power source for driving, transmission / reception of a long distance signal, There is a problem that it is difficult to secure power necessary for transmission and reception, and it is difficult to realize a good transmission and reception state. For this reason, use of a semiconductor device having a passive type RFID that uses electric power of an external radio wave or electromagnetic wave (carrier wave) as a power source is a short distance from an antenna of a reader / writer that is a means for supplying the radio wave or electromagnetic wave (carrier wave). There was a problem that it was limited to.

そこで本発明は、RFIDを有する半導体装置において、駆動電源としての電池の経時的劣化に伴う電池の残存容量の確認や電池の交換作業をすることなく、個体情報を送受信することができ、且つ駆動するための電源としての外部からの電波または電磁波(搬送波)の電力が十分でない場合であっても定期的な個体情報の送受信の良好な状態を維持する半導体装置を提供することを課題とする。また、加えて、駆動電源から電力が供給される信号制御回路での消費電力を低減し、低消費電力で駆動することのできる半導体装置を提供することを課題とする。 Therefore, the present invention can transmit and receive individual information in a semiconductor device having an RFID without performing confirmation of the remaining capacity of the battery or replacement of the battery due to deterioration of the battery as a driving power source, and driving. It is an object of the present invention to provide a semiconductor device that maintains a good state of regular transmission / reception of individual information even when the power of an external radio wave or electromagnetic wave (carrier wave) is not sufficient as a power source for the purpose. In addition, another object is to provide a semiconductor device that can be driven with low power consumption by reducing power consumption in a signal control circuit to which power is supplied from a drive power supply.

上述の諸問題を解決するため、本発明はRFIDにおける電力を供給するための電源としてバッテリー(ここでは2次電池)を具備する電源供給回路を設けることを特徴とする。そして本発明は、当該電源供給回路のバッテリーに対し無線信号で充電を行うことを特徴とする。また、外部との個体情報の送受信を行う信号制御回路に、電力を供給する電源供給回路においてスイッチ回路を設け、定期的に信号制御回路への電力の供給を制御することを特徴とする。以下、本発明の具体的な構成について示す。 In order to solve the above problems, the present invention is characterized in that a power supply circuit including a battery (here, a secondary battery) is provided as a power supply for supplying power in the RFID. The present invention is characterized in that the battery of the power supply circuit is charged with a radio signal. Further, a switch circuit is provided in a power supply circuit that supplies power to a signal control circuit that transmits and receives individual information to and from the outside, and the supply of power to the signal control circuit is periodically controlled. Hereinafter, a specific configuration of the present invention will be described.

本発明の半導体装置の一は、アンテナ回路と、電源供給回路と、信号制御回路とを有し、電源供給回路は、アンテナ回路からの信号を整流化する整流回路と、整流化された信号により充電されるバッテリーと、スイッチ回路と、低周波信号発生回路と、電源回路を有し、スイッチ回路は、低周波信号発生回路からの信号により、バッテリーから電源回路に供給される電力を制御することで、信号制御回路への電力の供給を制御する構成とする。 One of the semiconductor devices of the present invention includes an antenna circuit, a power supply circuit, and a signal control circuit. The power supply circuit includes a rectifier circuit that rectifies a signal from the antenna circuit, and a rectified signal. It has a battery to be charged, a switch circuit, a low frequency signal generation circuit, and a power supply circuit, and the switch circuit controls power supplied from the battery to the power supply circuit by a signal from the low frequency signal generation circuit. Thus, the power supply to the signal control circuit is controlled.

また、別の本発明の半導体装置の一は、アンテナ回路と、電源供給回路と、信号制御回路とを有し、電源供給回路は、アンテナ回路からの信号を整流化する整流回路と、制御回路と、整流化された信号により充電されるバッテリーと、スイッチ回路と、低周波信号発生回路と、電源回路を有し、信号制御回路は、整流回路からの電力と、バッテリーからの電力とを比較して、スイッチ回路に供給する電力を選択する回路であり、スイッチ回路は、低周波信号発生回路からの信号により、制御回路を介して電源回路に供給される電力を制御することで、信号制御回路への電力の供給を制御する構成とする。 Another semiconductor device of the present invention includes an antenna circuit, a power supply circuit, and a signal control circuit. The power supply circuit rectifies a signal from the antenna circuit, and a control circuit. And a battery charged by the rectified signal, a switch circuit, a low frequency signal generation circuit, and a power supply circuit, and the signal control circuit compares the power from the rectification circuit with the power from the battery. The switch circuit selects the power to be supplied to the switch circuit. The switch circuit controls the power supplied to the power supply circuit via the control circuit according to the signal from the low frequency signal generation circuit, thereby controlling the signal. The power supply to the circuit is controlled.

なお本発明において、バッテリーは、リチウム電池、ニッケル水素電池、ニカド電池、有機ラジカル電池又はキャパシタであってもよい。 In the present invention, the battery may be a lithium battery, a nickel metal hydride battery, a nickel cadmium battery, an organic radical battery, or a capacitor.

なお本発明において、バッテリーは、負極活物質層と、負極活物質層上の固体電解質層と、固体電解質層上の正極活物質層と、正極活物質層上の集電体薄膜とで構成されていてもよい。 In the present invention, the battery includes a negative electrode active material layer, a solid electrolyte layer on the negative electrode active material layer, a positive electrode active material layer on the solid electrolyte layer, and a current collector thin film on the positive electrode active material layer. It may be.

なお本発明において、制御回路は、整流回路からの電力がバッテリーからの電力より小さいときは、バッテリーとスイッチ回路とを接続し、バッテリーからの電力が整流回路からの電力より小さいときは、バッテリーとスイッチ回路とを接続しない回路であってもよい。 In the present invention, the control circuit connects the battery and the switch circuit when the power from the rectifier circuit is smaller than the power from the battery, and when the power from the battery is smaller than the power from the rectifier circuit, A circuit that is not connected to the switch circuit may be used.

なお本発明において、半導体装置はブースターアンテナを有し、アンテナ回路はブースターアンテナを介して外部からの信号を受信するものであってもよい。 In the present invention, the semiconductor device may include a booster antenna, and the antenna circuit may receive an external signal via the booster antenna.

なお本発明において、アンテナ回路は、バッテリーを充電するための電力を受電するための第1のアンテナ回路と、信号制御回路からの信号を送受信するための第2のアンテナ回路で構成されていてもよい。 In the present invention, the antenna circuit may include a first antenna circuit for receiving power for charging the battery and a second antenna circuit for transmitting and receiving signals from the signal control circuit. Good.

なお本発明において、第1のアンテナ回路は、複数のアンテナ回路により構成されていてもよい。 In the present invention, the first antenna circuit may be composed of a plurality of antenna circuits.

なお本発明において、第1のアンテナ回路及び第2のアンテナ回路のいずれか一は、電磁誘導方式により信号を受信する構成であってもよい。 In the present invention, any one of the first antenna circuit and the second antenna circuit may be configured to receive a signal by an electromagnetic induction method.

なお本発明において、低周波信号発生回路は、生成されるクロック信号を分周することにより、スイッチ回路に出力する信号を生成する構成であってもよい。 In the present invention, the low frequency signal generating circuit may be configured to generate a signal to be output to the switch circuit by dividing the generated clock signal.

なお本発明において、信号制御回路は、増幅回路、変調回路、復調回路、論理回路、メモリコントロール回路を有する構成であってもよい。 In the present invention, the signal control circuit may include an amplifier circuit, a modulation circuit, a demodulation circuit, a logic circuit, and a memory control circuit.

なお、本発明において、接続されているとは、電気的に接続されている場合と直接接続されている場合とを含むものとする。したがって、本発明が開示する構成において、所定の接続関係に加え、その間に電気的な接続を可能とする他の素子(例えば、スイッチやトランジスタや容量素子やインダクタや抵抗素子やダイオードなど)が配置されていてもよい。あるいは、間に他の素子を挟まずに、直接接続されて、配置されていてもよい。なお、電気的な接続を可能とする他の素子を間に介さずに接続されていて、直接接続されている場合のみを含む場合であって、電気的に接続されている場合を含まない場合には、直接接続されている、と記載するものとする。なお、電気的に接続されている、と記載する場合は、電気的に接続されている場合と直接接続されている場合とを含むものとする。 Note that in the present invention, the term “connected” includes the case of being electrically connected and the case of being directly connected. Therefore, in the configuration disclosed by the present invention, in addition to a predetermined connection relationship, other elements (for example, a switch, a transistor, a capacitor, an inductor, a resistor, a diode, etc.) that can be electrically connected are arranged. May be. Alternatively, they may be arranged directly connected without interposing another element therebetween. In addition, it is a case where it is connected without interposing other elements that enable electrical connection, and includes only the case where it is directly connected, and does not include the case where it is electrically connected Shall be described as being directly connected. Note that the description of being electrically connected includes the case of being electrically connected and the case of being directly connected.

なお、本発明には、様々な形態のトランジスタを適用することが出来る。よって、適用可能なトランジスタの種類に限定はない。したがって、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ(TFT)、半導体基板やSOI基板を用いて形成されるトランジスタ、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタ、ZnO、a−InGaZnOなどの化合物半導体を用いたトランジスタ、有機半導体やカーボンナノチューブを用いたトランジスタ、その他のトランジスタを適用することができる。なお、非単結晶半導体膜には水素またはハロゲンが含まれていてもよい。また、トランジスタが配置されている基板の種類は、様々なものを用いることができ、特定のものに限定されることはない。従って例えば、単結晶基板、SOI基板、ガラス基板、石英基板、プラスチック基板、紙基板、セロファン基板などを用いて配置することが出来る。また、ある基板でトランジスタを形成し、その後、別の基板にトランジスタを移動させて、別の基板上に配置するようにしてもよい。 Note that various types of transistors can be applied to the present invention. Thus, there is no limitation on the type of applicable transistor. Therefore, a thin film transistor (TFT) using a non-single-crystal semiconductor film typified by amorphous silicon or polycrystalline silicon, a transistor formed using a semiconductor substrate or an SOI substrate, a MOS transistor, a junction transistor, or a bipolar transistor Alternatively, a transistor using a compound semiconductor such as ZnO or a-InGaZnO, a transistor using an organic semiconductor or a carbon nanotube, or another transistor can be used. Note that the non-single-crystal semiconductor film may contain hydrogen or halogen. In addition, various types of substrates on which the transistor is arranged can be used, and the substrate is not limited to a specific type. Therefore, for example, a single crystal substrate, an SOI substrate, a glass substrate, a quartz substrate, a plastic substrate, a paper substrate, a cellophane substrate, or the like can be used. Alternatively, a transistor may be formed using a certain substrate, and then the transistor may be moved to another substrate and placed on another substrate.

また、本発明の半導体装置に適用するトランジスタの構成として、例えば、ゲート本数が2本以上になっているマルチゲート構造を用いてもよい。マルチゲート構造にすることにより、オフ電流の低減や、トランジスタの耐圧を向上させ信頼性を向上することや、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることができる。また、チャネルの上下にゲート電極が配置されている構造でもよい。チャネルの上下にゲート電極が配置されている構造にすることにより、電流値を大きくし、空乏層ができやすくなってS値を小さくすることができる。また、チャネルの上にゲート電極が配置されている構造でもよいし、チャネルの下にゲート電極が配置されている構造でもよいし、正スタガ構造であってもよいし、逆スタガ構造でもよいし、チャネル領域が複数の領域に分かれていてもよいし、並列に接続されていてもよいし、直列に接続されていてもよい。また、チャネル(もしくはその一部)にソース電極やドレイン電極が重なっていてもよい。チャネル(もしくはその一部)にソース電極やドレイン電極が重なっている構造にすることにより、チャネルの一部に電荷がたまって、動作が不安定になることを防ぐことができる。また、LDD領域があってもよい。LDD領域を設けることにより、オフ電流の低減や、トランジスタの耐圧を向上させ信頼性を向上することや、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることができる。 Further, as a transistor structure applied to the semiconductor device of the present invention, for example, a multi-gate structure in which the number of gates is two or more may be used. The multi-gate structure reduces off-current, improves the breakdown voltage of the transistor to improve reliability, and even when the drain-source voltage changes when operating in the saturation region. The current does not change so much, and a flat characteristic can be obtained. Alternatively, a structure in which gate electrodes are arranged above and below the channel may be employed. By adopting a structure in which gate electrodes are arranged above and below the channel, the current value can be increased, a depletion layer can be easily formed, and the S value can be decreased. Further, a structure in which a gate electrode is disposed above a channel, a structure in which a gate electrode is disposed below a channel, a normal staggered structure, or an inverted staggered structure may be employed. The channel region may be divided into a plurality of regions, may be connected in parallel, or may be connected in series. In addition, a source electrode or a drain electrode may overlap with the channel (or a part thereof). By using a structure in which a source electrode or a drain electrode overlaps with a channel (or part of it), it is possible to prevent electric charges from being accumulated in part of the channel and unstable operation. There may also be an LDD region. By providing the LDD region, the off-current can be reduced, the breakdown voltage of the transistor can be improved to improve reliability, and the drain-source current can be changed even when the drain-source voltage changes when operating in the saturation region. Does not change so much, and a flat characteristic can be obtained.

なお、すでに述べたように、本発明の半導体装置に適用するトランジスタは、様々なタイプを用いることができ、様々な基板を用いて形成することができる。したがって、回路の全てが、ガラス基板を用いて形成されていてもよいし、プラスチック基板を用いて形成されていてもよいし、単結晶基板を用いて形成されていてもよいし、SOI基板上を用いて形成されていてもよいし、どのような基板を用いて形成されていてもよい。回路の全てが1つの基板を用いて形成されていることにより、部品点数を減らしてコストを低減し、回路部品との接続点数を減らして信頼性を向上させたりすることができる。あるいは、回路の一部が、ある基板を用いて形成されており、回路の別の一部が、別の基板を用いて形成されていてもよい。つまり、回路の全てが同じ基板上に形成されていなくてもよい。例えば、回路の一部は、ガラス基板上にトランジスタを用いて形成し、回路の別の一部として、単結晶基板を用いてICチップを形成し、そのICチップをCOG(Chip On Glass)でガラス基板上に配置し、回路の他方の一部と接続してもよい。あるいは、そのICチップをTAB(Tape Automated Bonding)やプリント配線板を用いてガラス基板と接続してもよい。このように、回路の一部が同じ基板に形成されていることにより、部品点数を減らしてコストを低減し、回路部品との接続点数を減らして信頼性を向上させたりすることができる。また、駆動電圧が高い部分や駆動周波数が高い部分は、消費電力が大きくなってしまうので、そのような部分は同じ基板に形成しないようにすれば、消費電力の増大を防ぐことができる。 Note that as described above, various types of transistors can be used for the semiconductor device of the present invention, and the transistor can be formed using various substrates. Therefore, the entire circuit may be formed using a glass substrate, a plastic substrate, a single crystal substrate, or an SOI substrate. It may be formed using any substrate, and may be formed using any substrate. Since all the circuits are formed using one substrate, the number of parts can be reduced to reduce the cost, and the number of connection points with circuit parts can be reduced to improve the reliability. Alternatively, a part of the circuit may be formed using a certain substrate, and another part of the circuit may be formed using another substrate. That is, all of the circuits may not be formed on the same substrate. For example, a part of a circuit is formed using a transistor over a glass substrate, an IC chip is formed using a single crystal substrate as another part of the circuit, and the IC chip is formed by COG (Chip On Glass). It may be arranged on a glass substrate and connected to the other part of the circuit. Alternatively, the IC chip may be connected to the glass substrate using TAB (Tape Automated Bonding) or a printed wiring board. As described above, since a part of the circuit is formed on the same substrate, the number of parts can be reduced to reduce the cost, and the number of connection points with the circuit parts can be reduced to improve the reliability. In addition, since the power consumption is high in a portion where the drive voltage is high or a portion where the drive frequency is high, an increase in power consumption can be prevented if such a portion is not formed on the same substrate.

なお、本明細書でいう半導体装置とは、半導体特性を利用することで機能しうる装置全般を指すものとする。 Note that a semiconductor device in this specification refers to all devices that can function by utilizing semiconductor characteristics.

本発明の半導体装置は、バッテリーを具備する電源供給回路を有することを特徴とする。そのため定期的にバッテリーに対し充電を行うことができ、電池の経時的な劣化に伴う個体情報の送受信に用いられる電力の不足を防止することができる。そして、本発明の半導体装置は、バッテリーへの充電に際し、RFIDに設けられたアンテナ回路にて、電力を受電し、当該バッテリーの充電を行うことを特徴とする。そのため、充電器に直接接続することなく、RFIDを駆動するための電源としての外部からの電波または電磁波の電力を利用してバッテリーを充電することができる。その結果、アクティブタイプのRFIDのように電池の残存容量の確認や電池の交換をする作業が発生するといったことなく、使用し続けることが可能になる。加えて、RFIDを駆動するための電力を常にバッテリー内に保持することにより、RFIDが動作するための十分な電力が得られ、リーダ/ライタとの通信距離を伸ばすことができる。 A semiconductor device of the present invention includes a power supply circuit including a battery. For this reason, the battery can be charged periodically, and it is possible to prevent a shortage of electric power used for transmission / reception of individual information due to deterioration of the battery over time. The semiconductor device of the present invention is characterized in that when charging a battery, the antenna circuit provided in the RFID receives power and charges the battery. Therefore, it is possible to charge the battery by using electric power from an external radio wave or electromagnetic wave as a power source for driving the RFID without being directly connected to the charger. As a result, it is possible to continue using the battery without checking the remaining capacity of the battery or replacing the battery as in the case of the active type RFID. In addition, by always holding the power for driving the RFID in the battery, sufficient power for operating the RFID can be obtained, and the communication distance with the reader / writer can be extended.

また、本発明の半導体装置は上記バッテリーを具備することによる利点に加え、外部との個体情報の送受信を行う信号制御回路に電力を供給する電源供給回路において、スイッチ回路を設け、定期的に信号制御回路への電力の供給を制御することを特徴とする。電源供給回路に設けられたスイッチ回路において信号制御回路への電力の供給を制御することにより、RFIDの動作を間欠的におこなうことができる。そのためバッテリーにおける消費電力の低減を図り、さらに無線信号による電力の供給がなくても、長時間の動作を可能にすることができる。 In addition to the advantages provided by the battery, the semiconductor device of the present invention is provided with a switch circuit in a power supply circuit that supplies power to a signal control circuit that transmits / receives individual information to / from the outside. The power supply to the control circuit is controlled. By controlling the power supply to the signal control circuit in the switch circuit provided in the power supply circuit, the RFID operation can be performed intermittently. Therefore, it is possible to reduce power consumption in the battery and to operate for a long time without supplying power by a wireless signal.

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じ物を指し示す符号は異なる図面間において共通とする。

(実施の形態1)

Hereinafter, embodiments of the present invention will be described with reference to the drawings. However, the present invention can be implemented in many different modes, and those skilled in the art can easily understand that the modes and details can be variously changed without departing from the spirit and scope of the present invention. Is done. Therefore, the present invention is not construed as being limited to the description of this embodiment mode. Note that in the structures of the present invention described below, the same reference numeral is used in different drawings.

(Embodiment 1)

本発明の半導体装置の一構成例について、図1、図2に示すブロック図を用いて説明する。なお、本実施の形態では、半導体装置をRFIDタグ(以下、単に「RFID」とも記す)として利用する場合について説明する。 One structural example of the semiconductor device of the present invention will be described with reference to block diagrams shown in FIGS. Note that in this embodiment, the case where a semiconductor device is used as an RFID tag (hereinafter also simply referred to as “RFID”) will be described.

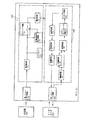

図1の半導体装置(以下、「RFID101」と記す)は、アンテナ回路102、電源供給回路103、信号制御回路104によって構成されている。信号制御回路104は、増幅回路105、復調回路106、論理回路107、メモリコントロール回路108、メモリ回路109、論理回路110、増幅回路111、変調回路112によって構成される。また電源供給回路103は、整流回路113、バッテリー114、低周波信号発生回路115、スイッチ回路116、電源回路117によって構成される。

The semiconductor device in FIG. 1 (hereinafter referred to as “

また、図2には、アンテナ回路102がリーダ/ライタ201からの信号を送受信し、そしてリーダ/ライタ201からの信号を元に充電を行うブロック図について示す。図2において、アンテナ回路102で受信した信号は、電源供給回路103、及び信号制御回路104に入力される。

FIG. 2 is a block diagram in which the

図2において、アンテナ回路102より電源供給回路103に入力される信号は、整流回路113、スイッチ回路116を介して電源回路117に入力される。また図2においてアンテナ回路102で受信する信号は整流回路113を介してバッテリー114に入力され、バッテリー114の充電が行われる。また図2においてアンテナ回路102で受信した信号は整流回路113を介して低周波信号発生回路115に入力される。また、低周波信号発生回路115は、スイッチ回路116のオンとオフを制御する信号を出力する。

In FIG. 2, a signal input from the

また図2において、アンテナ回路102より信号制御回路104に入力される信号は、増幅回路105を介して復調回路106に入力され、復調回路106により復調される。その後信号は論理回路107、メモリコントロール回路108、メモリ回路109、論理回路110、増幅回路111を経て、変調回路112に入力された後、変調回路112により変調され、アンテナ回路102より、リーダ/ライタ201に送信される。

In FIG. 2, a signal input from the

なお、アンテナ回路102は、図4(A)に示すようにアンテナ401、共振容量402によって構成されるものとして説明し、アンテナ401及び共振容量402を併せてアンテナ回路102ということにする。また、整流回路113は、アンテナ回路102が受信する電磁波により誘導される交流信号を整流化、平滑化をすることにより、直流信号に変換する回路であればよい。例えば、図4(B)に示すように、ダイオード404、ダイオード405、平滑容量406によって整流回路407を構成すればよい。

Note that the

図1、図2における電源回路117には、搬送波の信号を整流回路113において整流化し、スイッチ回路116を介して電源回路117に電力供給することができる。バッテリー114より供給された電力は、通信距離が伸びた際にRFID101のアンテナ回路102から十分な電力が得られない際に、バッテリー114より供給される電力によってスイッチ回路116を介して電源回路117へ電力を供給することができる。

In the

また、図1,図2におけるアンテナ回路102に設けられるアンテナの形状についても、特に限定されない。つまり、RFID101におけるアンテナ回路102に適用する信号の伝送方式は、電磁結合方式、電磁誘導方式又はマイクロ波方式等を用いることができる。伝送方式は、実施者が適宜使用用途を考慮して選択すればよく、伝送方式に伴って最適な長さや形状のアンテナを設ければよい。

The shape of the antenna provided in the

例えば、伝送方式として、電磁結合方式又は電磁誘導方式(例えば、13.56MHz帯)を適用する場合には、電界密度の変化による電磁誘導を利用するため、アンテナとして機能する導電膜を輪状(例えば、ループアンテナ)、らせん状(例えば、スパイラルアンテナ)に形成する。 For example, when an electromagnetic coupling method or an electromagnetic induction method (for example, 13.56 MHz band) is applied as a transmission method, a conductive film functioning as an antenna is formed in a ring shape (for example, an electromagnetic induction due to a change in electric field density). , Loop antenna), and spiral (for example, spiral antenna).

また、伝送方式としてマイクロ波方式(例えば、UHF帯(860〜960MHz帯)、2.45GHz帯等)を適用する場合には、信号の伝送に用いる電波の波長を考慮してアンテナとして機能する導電膜の長さや形状を適宜設定すればよく、アンテナとして機能する導電膜を例えば、線状(例えば、ダイポールアンテナ)、平坦な形状(例えば、パッチアンテナ)等に形成することができる。また、アンテナとして機能する導電膜の形状は線状に限られず、電磁波の波長を考慮して曲線状や蛇行形状またはこれらを組み合わせた形状で設けてもよい。 In addition, when a microwave method (for example, UHF band (860 to 960 MHz band), 2.45 GHz band, or the like) is applied as a transmission method, a conductive function that functions as an antenna in consideration of the wavelength of a radio wave used for signal transmission. The length and shape of the film may be set as appropriate, and the conductive film functioning as an antenna can be formed, for example, in a linear shape (for example, a dipole antenna) or a flat shape (for example, a patch antenna). Further, the shape of the conductive film functioning as an antenna is not limited to a linear shape, and may be provided in a curved shape, a meandering shape, or a combination thereof in consideration of the wavelength of electromagnetic waves.

アンテナ回路102とリーダ/ライタ201間で送受信される信号の周波数は、125kHz、13.56MHz、915MHz、2.45GHzなどがあり、それぞれISO規格などが設定される。勿論、アンテナ回路102とリーダ/ライタ201間で送受信される信号の周波数はこれに限定されず、例えばサブミリ波である300GHz以上3THz未満、ミリ波である30GHz以上300GHz未満、マイクロ波である3GHz以上30GHz未満、極超短波である300MHz以上3GHz未満、超短波である30MHz以上300MHz未満、短波である3MHz以上30MHz未満、中波である300KHz以上3MHz未満、長波である30KHz以上300KHz未満、及び超長波である3KHz以上30KHz未満のいずれの周波数も用いることができる。また、アンテナ回路102とリーダ/ライタ201間で送受信される信号は、搬送波を変調した信号である。搬送波の変調方式は、アナログ変調であってもデジタル変調であってよく、振幅変調、位相変調、周波数変調、及びスペクトラム拡散のいずれであってもよい。望ましくは、振幅変調、または、周波数変調にするとよい。

The frequencies of signals transmitted and received between the

ここで、アンテナ回路102に設けるアンテナの形状の一例を図3に示す。例えば、図3(A)に示すように信号制御回路、電源供給回路が設けられたチップ332の周りにアンテナ333を配した構造を取っても良い。また、図3(B)に示すように信号制御回路が設けられたチップ332上に細いアンテナ333を設けた構造をとってもよい。また、図3(C)に示すように信号制御回路が設けられたチップ332に対して、高周波数の電磁波を受信するためのアンテナ333の形状をとってもよい。また、図3(D)に示すように信号制御回路が設けられたチップ332に対して180度無指向性(どの方向からでも同じく受信可能)なアンテナ333での形状をとってもよい。また、図3(E)に示すように、信号制御回路が設けられたチップ332に対して、棒状に長く伸ばしたアンテナ333の形状をとってもよい。アンテナ回路はこれらの形状のアンテナを用いることができる。

Here, an example of the shape of the antenna provided in the

また、図3において、信号制御回路が設けられたチップ332とアンテナとの接続については特に限定されない。例えば、アンテナ333と信号制御回路が設けられたチップ332をワイヤボンディング接続やバンプ接続を用いて接続する、あるいはチップの一部を電極にしてアンテナ333に貼り付けるという方法を取ってもよい。この方式ではACF(anisotropic conductive film;異方性導電性フィルム)を用いてチップ332をアンテナ333に貼り付けることができる。また、アンテナに必要な長さは受信に用いる周波数によって適正な長さが異なる。そのため、一般には波長の整数分の1の長さにし、例えば周波数が2.45GHzの場合は約60mm(1/2波長)、約30mm(1/4波長)とすれば良い。 Further, in FIG. 3, the connection between the chip 332 provided with the signal control circuit and the antenna is not particularly limited. For example, a method may be employed in which the antenna 333 and the chip 332 provided with the signal control circuit are connected using wire bonding connection or bump connection, or a part of the chip is attached to the antenna 333 as an electrode. In this method, the chip 332 can be attached to the antenna 333 by using an ACF (anisotropic conductive film). The length required for the antenna differs depending on the frequency used for reception. For this reason, the length is generally set to 1 / integer of the wavelength. For example, when the frequency is 2.45 GHz, the length may be about 60 mm (1/2 wavelength) and about 30 mm (1/4 wavelength).

また、図5においては、図1,図2に示した構成におけるRFIDにおいて、アンテナ回路を増やした構成について示す。図5に示すように、アンテナ回路102を信号制御回路104用の第1のアンテナ回路301と、電源供給回路103用の第2のアンテナ回路302とに分けてRFID101を設けてもよい。この場合、電源供給回路103に給電するための無線信号は、リーダ/ライタ201から送信される信号とは別に、充電器303より供給される構成が望ましい。第2のアンテナ回路302に送信される無線信号は、リーダ/ライタ201から送受信される信号との混信を避けるため、リーダ/ライタ201から送信される信号と異なる周波数の信号であることが望ましい。

FIG. 5 shows a configuration in which the antenna circuit is increased in the RFID in the configuration shown in FIGS. As shown in FIG. 5, the

なお、図5に示す構成において、第2のアンテナ回路302は、充電器303からの信号の受信に限らず、空間内の他の無線信号を受信し、電源供給回路に信号を供給してもよい。例えばRFID101のバッテリー114を充電するために第2のアンテナ回路302で受信する無線信号(電波)として、携帯電話の中継局の電波(800〜900MHz帯、1.5GHz、1.9〜2.1GHz帯等)、携帯電話から発振される電波、電波時計の電波(40kHz等)、家庭用の交流電源のノイズ(60Hz等)、他のリーダ/ライタ(RFID101と直接やりとりを行わないリーダ/ライタ)から無作為に生じている電波等を利用することができる。

In the configuration illustrated in FIG. 5, the

外部の無線信号を受信してバッテリーの充電を無線で行うことによって、バッテリーを充電するための充電器等を別途必要としないため、より低コストでRFIDを設けることができる。また、第2のアンテナ回路302に設けられるアンテナの形状は、これらの無線信号を受信しやすい長さや形状で設ける。また、上記のような複数種(複数の周波数帯)の電波を受信する場合には、長さや形状の異なるアンテナを含む複数のアンテナ回路を設けることが好ましい。

By receiving an external wireless signal and charging the battery wirelessly, a separate charger or the like for charging the battery is not required, so that the RFID can be provided at a lower cost. In addition, the antenna provided in the

また本発明では、低周波信号発生回路115からの信号によりスイッチ回路116のオンとオフを制御することで、間欠的にRFIDを動作させ消費電力の低減を図っている。一般にRFIDはリーダ/ライタからの信号に対して常時動作しているが、データの内容や、用途によっては必ずしも常時応答しなくとも良い場合もある。本発明では、そのような場合に、RFIDの動作を停止することによって、バッテリーに蓄えた電力の消費を低減することができる。本発明における半導体装置において、常時動作しているのは、図1、図2における低周波信号発生回路115のみである。低周波信号発生回路115はバッテリー114に蓄えられた電力をもとに動作する。

In the present invention, the on / off state of the switch circuit 116 is controlled by a signal from the low-frequency signal generation circuit 115 to operate the RFID intermittently to reduce power consumption. In general, an RFID always operates in response to a signal from a reader / writer. However, depending on the contents of data and application, it may not always be necessary to respond constantly. According to the present invention, in such a case, the consumption of electric power stored in the battery can be reduced by stopping the operation of the RFID. In the semiconductor device of the present invention, only the low frequency signal generation circuit 115 in FIGS. 1 and 2 is always operating. The low frequency signal generation circuit 115 operates based on the electric power stored in the

また本発明において、バッテリーとは、充電することで連続使用時間を回復することができる電池のことをいう。なおバッテリーとしては、厚さ1μm〜数μmのシート状に形成された電池を用いることが好ましく、例えばリチウム電池、好ましくはゲル状電解質を用いるリチウムポリマー電池や、リチウムイオン電池等を用いることで、小型化が可能である。勿論、充電可能な電池であればなんでもよく、ニッケル水素電池、ニカド電池などの充電放電可能な電池であってもよいし、また大容量のコンデンサーなどを用いても良い。 In the present invention, the battery refers to a battery that can recover the continuous use time by charging. As the battery, it is preferable to use a battery formed in a sheet shape having a thickness of 1 μm to several μm. For example, by using a lithium battery, preferably a lithium polymer battery using a gel electrolyte, a lithium ion battery, or the like, Miniaturization is possible. Needless to say, any rechargeable battery may be used, such as a nickel hydride battery or a nickel-cadmium rechargeable battery, or a large-capacity capacitor.

次に図1、図2における電源回路117の例について、図6を用いて説明する。

Next, an example of the

電源回路117は基準電圧回路とバッファ増幅回路で構成される。基準電圧回路は抵抗1000、ダイオード接続のトランジスタ1002、1003によって構成され、トランジスタのVGSの2倍に相当する基準電圧を発生させる。バッファ増幅回路はトランジスタ1005、1006で構成される差動回路、トランジスタ1007、1008によって構成されるカレントミラー回路、電流供給用抵抗1004、トランジスタ1009、抵抗1010によって構成されるソース接地増幅回路より構成される。

The

図6に示す電源回路において、出力端子より流れる電流が大きいときはトランジスタ1009に流れる電流が少なくなり、また、出力端子より流れる電流が小さいときはトランジスタ1009に流れる電流が多くなり、抵抗1010に流れる電流はほぼ一定となるように動作する。また出力端子の電位は基準電圧回路とほぼ同じ値となる。ここでは基準電圧回路とバッファ増幅回路を有する電源回路を示したが、本発明に用いる電源回路は図6に限定されず、他の形式の回路であっても良い。

In the power supply circuit shown in FIG. 6, when the current flowing from the output terminal is large, the current flowing through the

次に、図1、図2に示すRFID101の信号制御回路104に、リーダ/ライタ201よりデータを書き込む際の動作を以下に説明する。アンテナ回路102で受信した信号は、増幅回路105を介して、クロック信号として、論理回路107に入力される。さらに、アンテナ回路102から入力された信号は復調回路106で復調され、データとして論理回路107に入力される。

Next, an operation when data is written from the reader /

論理回路107において、入力されたデータはデコードされる。リーダ/ライタ201がデータを変形ミラー符号、NRZ−L符号などでエンコードして送信するため、それを論理回路107はデコードする。デコードされたデータは、メモリコントロール回路108に送られ、それに従いメモリ回路109にデータが書き込まれる。メモリ回路109は電源が切れても保持できる不揮発性メモリ回路である必要があり、マスクROMなどが使用される。

In the logic circuit 107, the input data is decoded. Since the reader /

また、図1、図2に示すRFID101の信号制御回路104におけるメモリ回路109に記憶されたデータをリーダ/ライタ201が読み出す場合は以下のように動作する。アンテナ回路102で受信した交流信号は、増幅回路105を通して論理回路107に入力され、論理演算が行われる。そして、論理回路107からの信号を用いて、メモリコントロール回路108を制御し、メモリ回路109に記憶されているデータを読み出す。次にメモリ回路109から呼び出されたデータを論理回路110で加工し、増幅回路111で増幅の後、変調回路112を動作させる。データの加工はISO14443、ISO15693、ISO18000などの規格に定められた方式に従い加工されるが、リーダ/ライタとの整合性が確保されれば、上記規格以外であってもかまわない。

When the reader /

変調回路112が動作すると、アンテナ回路102のインピーダンスが変化する。これによって、アンテナ回路102で反射されるリーダ/ライタ201の信号に変化が生じる。この変化をリーダ/ライタが読み取ることによってRFID101のメモリ回路109に記憶されたデータを知ることが可能になる。このような変調方式を負荷変調方式という。

When the modulation circuit 112 operates, the impedance of the

なお、信号制御回路104に設けるトランジスタとして、様々な形態のトランジスタを適用することが出来る。よって、適用可能なトランジスタの種類に限定はない。したがって、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ(TFT)、半導体基板やSOI基板を用いて形成されるトランジスタ、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタ、ZnO、a−InGaZnOなどの化合物半導体を用いたトランジスタ、有機半導体やカーボンナノチューブを用いたトランジスタ、その他のトランジスタを適用することができる。なお、非単結晶半導体膜には水素またはハロゲンが含まれていてもよい。また、信号制御回路104が形成されている基板の種類は、様々なものを用いることができ、特定のものに限定されることはない。従って例えば、単結晶基板、SOI基板、ガラス基板、石英基板、プラスチック基板、紙基板、セロファン基板、石材基板などを用いて形成することが出来る。また、ある基板に信号制御回路104を形成し、その後、別の基板に信号制御回路104を移動させて、別の基板上に配置するようにしてもよい。

Note that various types of transistors can be used as the transistor provided in the

次に、図1、図2に示すRFID101に、外部の無線信号より電力を充電する際の動作を以下に説明する。アンテナ回路102で受信した外部の無線信号は、整流回路113により、半波整流され、そして平滑化される。そして整流回路113から出力される電力は、スイッチ回路116を介して、電源回路117に供給され、余剰電力がバッテリー114に蓄えられる。

Next, an operation when the

また、前述したように、本発明では間欠的にRFIDを動作させることにより、消費電力の低減を図っている。一般にRFIDはリーダ/ライタからの信号に対して常時動作しているが、データの内容や、用途によっては必ずしも常時応答しなくとも良い場合もある。そのような場合に、RFIDの動作を停止することによって、バッテリーに蓄えた電力の消費を低減することができる。本発明において、常時動作しているのは、図1,図2における低周波信号発生回路115のみである。低周波信号発生回路115はバッテリー114に蓄えられた電力をもとに動作する。図7を用いて、低周波信号発生回路の出力波形について説明する。

Further, as described above, in the present invention, power consumption is reduced by intermittently operating the RFID. In general, an RFID always operates in response to a signal from a reader / writer. However, depending on the contents of data and application, it may not always be necessary to respond constantly. In such a case, the consumption of electric power stored in the battery can be reduced by stopping the operation of the RFID. In the present invention, only the low-frequency signal generation circuit 115 in FIGS. 1 and 2 is always operating. The low frequency signal generation circuit 115 operates based on the electric power stored in the

図7には、低周波信号発生回路がスイッチ回路に出力する信号の波形について示している。図7の例では出力波形のデューティ比を1:n(nは整数)にすることによって、消費電力を1/(n+1)程度にすることができる。この信号を元にしてスイッチ回路116を駆動する。スイッチ回路116はバッテリー114と電源回路117を出力信号がハイになっている期間だけ接続し、それによって、その期間だけRFIDを動作させる。

FIG. 7 shows a waveform of a signal output from the low frequency signal generation circuit to the switch circuit. In the example of FIG. 7, the power consumption can be reduced to about 1 / (n + 1) by setting the duty ratio of the output waveform to 1: n (n is an integer). Based on this signal, the switch circuit 116 is driven. The switch circuit 116 connects the

また図8には図1,図2における低周波信号発生回路の具体的な構成例について説明する。図8の低周波信号発生回路115はリングオシレータ820、分周回路821、AND回路822、インバータ823、824によって構成されている。リングオシレータ820の発振信号を分周回路821で分周し、その出力をAND回路822にいれ、AND回路822で低デューティ比の信号を作り出している。さらにAND回路822の出力をインバータ823、インバータ824を介して、トランスミッションゲート825で構成されるスイッチ回路116に入力している。リングオシレータ820は低周波数で発振するリングオシレータであり、たとえば、1kHzで発振させる。

FIG. 8 illustrates a specific configuration example of the low-frequency signal generation circuit in FIGS. 8 includes a

また図9は図8で示した低周波信号発生回路115の各構成から出力される信号のタイミングチャートについて示す。図9において、リングオシレータ820の出力波形、分周回路821の出力波形、AND回路822の出力波形を示したものである。分周回路821を1024分周の分周回路とすれば分周回路の出力信号としては、図9に図示するような順次分周された信号である分周回路出力波形1、分周回路出力波形2、分周回路出力波形3が順次出力されていく。本実施の形態では例として、分周回路821を1024分周の分周回路であるとすると、分周回路821から出力された複数の信号が入力されたAND回路822より出力される信号のデューティ比を1:1024の信号として形成することができる。このときリングオシレータ820の発振周波数が1KHzであれば1つの周期において動作期間は0.5us、非動作期間は512usである。リングオシレータの発振周波数は1KHzに限らず、他の周波数であっても良い。また、分周回路における分周の数も1024に限らず他の値であっても良い。

FIG. 9 is a timing chart of signals output from the components of the low-frequency signal generation circuit 115 shown in FIG. FIG. 9 shows the output waveform of the

そして本発明における低周波信号発生回路から出力される信号は定期的にスイッチ回路116のトランスミッションゲートのオンとオフを制御し、バッテリー114から電源回路への電力の供給を制御することができる。すなわち、バッテリー114から信号制御回路への電力の供給を間欠的に行うことにより、RFIDの低消費電力化を図ることができる。

The signal output from the low frequency signal generation circuit according to the present invention can periodically control on / off of the transmission gate of the switch circuit 116 and control the supply of power from the

本発明のRFIDにおいては、リーダ/ライタからの信号に対し、一定周期の割合で信号を送信することにより消費電力を十分小さく下げることが可能になる。また加えて、RFIDの外部より入力される無線信号をアンテナ回路で受信し、電源供給回路におけるバッテリー内に電力を蓄電することにより、信号制御回路に供給する電力を定期的にアンテナ回路より供給されることなく動作することが可能になる。また、アンテナ回路から受信信号の電力と、バッテリー内に蓄電された電力を制御回路により比較することで、整流回路からの電力の供給か、バッテリーから電源回路への供給かを選択することによりさらなる低消費電力化を図ることができるため好適である。 In the RFID of the present invention, the power consumption can be sufficiently reduced by transmitting a signal at a constant cycle rate relative to the signal from the reader / writer. In addition, the radio signal input from the outside of the RFID is received by the antenna circuit, and the electric power supplied to the signal control circuit is periodically supplied from the antenna circuit by storing the electric power in the battery in the power supply circuit. It becomes possible to operate without. Further, by comparing the power of the received signal from the antenna circuit with the power stored in the battery by the control circuit, it is possible to further select the power supply from the rectifier circuit or the power supply circuit from the battery. This is preferable because low power consumption can be achieved.

以上のように、本発明のRFIDを有する半導体装置は、バッテリーを有することを特徴とする。そのため、従来のように、電池の経時的な劣化に伴う個体情報の送受信にするための電力の不足を防止することができる。そして、本発明の半導体装置は、バッテリーに電力を供給するための信号を受信するアンテナを有することを特徴とする。そのため、充電器に直接接続することなく、RFIDを駆動するための電源を外部の無線信号を利用してバッテリーを充電することができる。その結果、アクティブタイプのRFIDのような電池の残存容量の確認や電池の交換をする作業が発生するといったことなく、使用し続けることが可能になる。加えて、RFIDを駆動するための電力を常にバッテリー内に保持することにより、RFIDが動作するための十分な電力が得られ、リーダ/ライタとの通信距離を伸ばすことができる。 As described above, a semiconductor device having an RFID of the present invention has a battery. As a result, it is possible to prevent a shortage of power for transmitting / receiving individual information associated with deterioration of the battery over time, as in the past. The semiconductor device of the present invention includes an antenna that receives a signal for supplying power to the battery. Therefore, the battery can be charged by using an external wireless signal as a power source for driving the RFID without being directly connected to the charger. As a result, it is possible to continue using the battery without confirming the remaining capacity of the battery or exchanging the battery, such as active type RFID. In addition, by always holding the power for driving the RFID in the battery, sufficient power for operating the RFID can be obtained, and the communication distance with the reader / writer can be extended.

なお、本実施の形態は、本明細書中の他の実施の形態の記載と自由に組み合わせて実施することが可能である。

(実施の形態2)

Note that this embodiment can be implemented in free combination with the description of the other embodiments in this specification.

(Embodiment 2)

本実施の形態では、上記実施の形態1で示したRFIDである半導体装置において、電源供給回路における電源回路に供給される電力として整流回路からの電力とバッテリーからの電力のいずれを用いるかの選択を制御するための制御回路を備えた構成に関して、図面を参照して説明する。なお、本実施の形態において使用する図面に関し、実施の形態1と同じ部分は同じ符号を用いて示す場合がある。

In this embodiment mode, in the semiconductor device that is an RFID shown in

本実施の形態における本発明の半導体装置の一構成例について、図10、図11に示すブロック図を用いて説明する。なお、本実施の形態では、半導体装置をRFIDとして利用する場合について説明する。 One structural example of the semiconductor device of the present invention in this embodiment will be described with reference to block diagrams shown in FIGS. Note that in this embodiment, the case where a semiconductor device is used as an RFID will be described.

図10のRFID101は、アンテナ回路102、電源供給回路103、信号制御回路104によって構成されている。信号制御回路104は、増幅回路105、復調回路106、論理回路107、メモリコントロール回路108、メモリ回路109、論理回路110、増幅回路111、変調回路112によって構成される。また電源供給回路103は、整流回路113、制御回路1001、バッテリー114、低周波信号発生回路115、スイッチ回路116、電源回路117によって構成される。実施の形態1における図1の構成との違いは、制御回路1001が整流回路113とバッテリー114との間にある点にある。

10 includes an

また、図11には、アンテナ回路102とリーダ/ライタ201との間で信号が送受信され、そしてリーダ/ライタ201からの信号を元に充電を行うブロック図について示す。図11において、アンテナ回路102で受信した信号は、電源供給回路103、及び信号制御回路104に入力される。

FIG. 11 illustrates a block diagram in which a signal is transmitted and received between the

図11において、アンテナ回路102より電源供給回路103に入力される信号は、整流回路113、スイッチ回路116を介して電源回路117に入力される。また図11においてアンテナ回路102で受信する信号は整流回路113、制御回路1001を介してバッテリー114に入力され、バッテリー114の充電が行われる。

In FIG. 11, a signal input from the

また図11において、アンテナ回路102より信号制御回路104に入力される信号は、増幅回路105を介して復調回路106に出力され、復調回路106により復調された後、論理回路107、メモリコントロール回路108、メモリ回路109、論理回路110、増幅回路111を経て、変調回路112に入力され、変調回路112により変調された後、アンテナ回路102より、リーダ/ライタ201に送信される。

In FIG. 11, a signal input from the

なお、アンテナ回路102は、実施の形態1で示した図4(A)に示す構成であればよい。また、整流回路113は、実施の形態1で示した図4(B)に示す構成であればよい。

Note that the

また、図10,図11におけるアンテナ回路102については、実施の形態1で述べたアンテナ回路102の説明と同様であるためここでは説明を省略する。

The

なお、アンテナ回路102に設けるアンテナの形状の例としては、実施の形態1で説明した図3の形状を用いれば良く、上述の説明と同様であるためここでは省略する。

Note that as an example of the shape of the antenna provided in the

また、図12においては、図10,図11に示した構成におけるRFIDにおいて、アンテナ回路を増やした構成について示す。図12に示す構成は、実施の形態1で示した図5の構成に対応する。そのため、実施の形態1で示した図5の説明と同様であり、ここでは省略する。

In addition, FIG. 12 shows a configuration in which the antenna circuit is increased in the RFID in the configuration shown in FIGS. The configuration shown in FIG. 12 corresponds to the configuration of FIG. 5 shown in the first embodiment. Therefore, this is the same as the description of FIG. 5 described in

図10、図11における電源回路117の構成については、実施の形態1で述べた電源回路117の説明、及び図6の構成と同様であるためここでは説明を省略する。

The configuration of the

本実施の形態において、電源供給回路103では、整流回路113から出力される電力が、信号制御回路104を動作させるのに必要な電力より十分に大きいときには、整流回路から出力される電力のうち余剰電力をバッテリーに蓄え、整流回路から出力される電力が、信号制御回路を動作させるのに十分でないときには、バッテリーからも電源回路に電力を供給する制御手段を有している。

In the present embodiment, in the

本実施の形態においては、整流回路113に制御回路1001を介してバッテリー114を接続することにより電源回路への電力の制御を実現することができる。整流回路113にバッテリー114を接続することによって、余剰電力をバッテリー114に蓄え、整流回路113から出力される電力が低下した時にはバッテリー114から電源回路117に電力を供給する。

In this embodiment mode, power control to the power supply circuit can be realized by connecting the

また、図10、図11に示す制御回路1001の例について図13を用いて説明する。 An example of the control circuit 1001 illustrated in FIGS. 10 and 11 will be described with reference to FIG.

図13において制御回路1001は整流素子1394、整流素子1395、電圧比較回路1391、スイッチ1392、及びスイッチ1393を有している。

In FIG. 13, the control circuit 1001 includes a

図13において、電圧比較回路1391は、バッテリー114から出力される電圧と整流回路113から出力される電圧とを比較する。整流回路113から出力される電圧がバッテリー114から出力される電圧よりも十分に高いときには、電圧比較回路1391はスイッチ1392をオンにし、スイッチ1393をオフにする。すると、整流回路113から整流素子1394及びスイッチ1392を介してバッテリー114に電流が流れる。一方、整流回路113から出力される電圧がバッテリー114から出力される電圧と比較して十分な高さでなくなると、電圧比較回路1391はスイッチ1392をオフにし、スイッチ1393をオンにする。このとき、整流回路113から出力された電圧がバッテリー114から出力された電圧より高ければ、整流素子1395には電流が流れないが、整流回路113から出力された電圧がバッテリー114から出力された電圧より低ければ、バッテリー114からスイッチ1393及び整流素子1395、スイッチ回路116を介して電源回路117に電流が流れる。

In FIG. 13, the

なお、制御回路1001は本実施の形態で説明した構成に限定されず、他の形式を用いても良い。 Note that the control circuit 1001 is not limited to the structure described in this embodiment mode, and other types may be used.

また、図13においてにおいて説明した電圧比較回路1391の例について図14を用いて説明する。

An example of the

図14に示す構成において、電圧比較回路1391は、バッテリー114から出力される電圧を抵抗素子1403と抵抗素子1404で抵抗分割し、整流回路113から出力される電圧を抵抗素子1401と抵抗素子1402で抵抗分割し、これらの抵抗分割により得られる電位をコンパレーター1405に入力している。コンパレーター1405の出力にはインバータ形式のバッファ回路1406及びバッファ回路1407を直列に接続する。そして、バッファ回路1406の出力は図13におけるスイッチ1393の制御端子に入力され、バッファ回路1407の出力は図13におけるスイッチ1392の制御端子に入力され、図13のスイッチ1392及びスイッチ1393のオンとオフを制御する。なお、図13におけるスイッチ1392及びスイッチ1393は制御端子に入力される信号がHレベルのときオンし、Lレベルのときオフするものとする。

In the configuration illustrated in FIG. 14, the

また図14に示す構成において、抵抗分割して、コンパレーター1405に入力する電圧を調整することにより、バッテリー114から出力される電圧より整流回路113から出力される電圧がどれだけ高くなったら、スイッチ1392をオンにし、スイッチ1393をオフにするかを制御することができる。

Further, in the configuration shown in FIG. 14, when the voltage output from the

なお、電圧比較回路1391は本実施の形態において説明した構成に限定されず、他の形式を用いても良い。

Note that the

また、図10、図11に示すRFID101の信号制御回路104に、リーダ/ライタ201よりデータを書き込む際の動作、RFID101の信号制御回路104におけるメモリ回路109に記憶されたデータをリーダ/ライタ201が呼び出す動作については、実施の形態1において説明した図1、図2における動作と同様であるため本実施の形態においてはその説明を省略する。

The reader /

次に、図10、図11に示すRFID101に、外部の無線信号より電力を充電する際の動作を以下に説明する。アンテナ回路102で受信した外部の無線信号は、整流回路113により、半波整流され、そして平滑化される。

Next, an operation when the

そして制御回路1001において、バッテリー114から出力される電圧と整流回路113から出力される電圧とを比較する。整流回路113から出力される電圧がバッテリー114から出力される電圧よりも十分高ければ、整流回路113とバッテリー114とを接続する。このとき整流回路113から出力される電力はバッテリー114と電源回路117の両方に供給され、余剰電力がバッテリー114に蓄えられる。

Then, the control circuit 1001 compares the voltage output from the

制御回路1001は、整流回路113から出力される電圧がバッテリー114から出力される電圧と比較して十分な高さでなくなると電源回路117とバッテリー114とを接続する。このとき、整流回路113から出力された電圧がバッテリー114から出力された電圧より高いときには、整流回路113から出力される電力が電源回路117に供給され、バッテリーへの充電やバッテリーの電力の消費はない。そして、整流回路113から出力される電圧がバッテリー114から出力される電圧より低くなると、バッテリー114から電源回路に電力を供給する。すなわち、制御回路1001は整流回路113から出力される電圧とバッテリー114から出力される電圧とに応じて電流の方向を制御する。

The control circuit 1001 connects the

また、前述したように、本発明では低周波信号発生回路115の出力信号によりスイッチ回路116のオンとオフを切り替え、間欠的にRFIDを動作させ消費電力の低減を図っている。一般にRFIDは信号に対して常時動作しているが、データの内容や、用途によっては必ずしも常時応答しなくとも良い場合もある。そのような場合に、RFIDの動作を停止することによって、バッテリーに蓄えた電力の消費を低減することができる。 Further, as described above, in the present invention, the switch circuit 116 is turned on and off by the output signal of the low frequency signal generation circuit 115, and the RFID is operated intermittently to reduce power consumption. In general, an RFID always operates with respect to a signal. However, depending on the contents of data and application, there is a case where it is not always necessary to respond. In such a case, the consumption of electric power stored in the battery can be reduced by stopping the operation of the RFID.

なお本実施の形態における低周波信号発生回路の構成及びタイミングチャートについては、実施の形態1で説明した図7、図8、図9、及びその説明箇所と同様であるため、本実施の形態においては説明を省略する。

Note that the configuration and timing chart of the low-frequency signal generation circuit in this embodiment are the same as those in FIGS. 7, 8, and 9 described in

このようにして、本発明のRFIDにおいては、リーダ/ライタからの信号に対し、一定周期で信号を送信することにより消費電力を十分小さく下げることが可能になる。また加えて、RFIDの外部より入力される無線信号をアンテナ回路で受信し、電源供給回路におけるバッテリー内に電力を蓄電することにより、信号制御回路に供給する電力を定期的にアンテナ回路より供給することなくRFIDを動作することが可能になる。また、アンテナ回路から入力される受信信号の電力と、バッテリー内に蓄電された電力を制御回路により比較することで、整流回路から電源回路に電力を供給するか、バッテリーから電源回路に電力を供給するかを選択することにより、さらなるバッテリーにおける消費電力の低減を図ることができるため好適である。 In this way, in the RFID of the present invention, it is possible to sufficiently reduce power consumption by transmitting a signal at a constant period with respect to a signal from a reader / writer. In addition, a radio signal input from the outside of the RFID is received by the antenna circuit, and the electric power supplied to the signal control circuit is periodically supplied from the antenna circuit by storing the electric power in the battery in the power supply circuit. RFID can be operated without any problems. Also, the power of the received signal input from the antenna circuit and the power stored in the battery are compared by the control circuit, so that power is supplied from the rectifier circuit to the power circuit, or power is supplied from the battery to the power circuit. It is preferable to select whether or not to further reduce the power consumption of the battery.

以上のように、本発明のRFIDを有する半導体装置は、バッテリーを有することを特徴とする。そのため、従来問題視されていた電池の経時的な劣化に伴う個体情報の送受信にするための電力の不足を防止することができる。そして、本発明の半導体装置は、バッテリーに電力を供給するための信号を受信するアンテナを有することを特徴とする。そのため、充電器に直接接続することなく、RFIDを駆動するための電源として外部の無線信号を利用してバッテリーを充電することができる。その結果、アクティブタイプのRFIDのように電池の残存容量の確認や電池の交換を行なわずに使用し続けることが可能になる。加えて、RFIDを駆動するための電力を常にバッテリー内に保持することにより、RFIDが動作するための十分な電力が得られ、リーダ/ライタとの通信距離を伸ばすことができる。 As described above, a semiconductor device having an RFID of the present invention has a battery. Therefore, it is possible to prevent a shortage of electric power for transmitting / receiving individual information associated with deterioration of the battery over time, which has been regarded as a problem in the past. The semiconductor device of the present invention includes an antenna that receives a signal for supplying power to the battery. Therefore, the battery can be charged using an external radio signal as a power source for driving the RFID without being directly connected to the charger. As a result, it is possible to continue using the battery without checking the remaining capacity of the battery or replacing the battery as in the active type RFID. In addition, by always holding the power for driving the RFID in the battery, sufficient power for operating the RFID can be obtained, and the communication distance with the reader / writer can be extended.

なお、本実施の形態は、本明細書中の他の実施の形態の記載と自由に組み合わせて実施することが可能である。

(実施の形態3)

Note that this embodiment can be implemented in free combination with the description of the other embodiments in this specification.

(Embodiment 3)

本実施の形態では、上記実施の形態1で示したRFIDを有する半導体装置において、ブースターアンテナ回路(以下、ブースターアンテナという)を有する構成に関して、図面を参照して説明する。なお、本実施の形態において使用する図面に関し、実施の形態1と同じ部分は同じ符号を用いて示す。

In this embodiment, a structure including a booster antenna circuit (hereinafter referred to as a booster antenna) in the semiconductor device including the RFID described in

なお、本実施の形態において述べるブースターアンテナとは、リーダ/ライタからの信号や充電器等の無線信号を受信するアンテナ回路よりも、サイズの大きいアンテナ回路(以下、ブースターアンテナという)のことをいう。アンテナ回路とブースターアンテナを使用する周波数帯域で共振させ、磁界結合させることで、リーダ/ライタまたは充電器より発振された信号を、効率よく目的のRFIDへ伝達させることができるものをいう。ブースターアンテナは磁界を介してコイルアンテナと結合しているため、直接チップアンテナ及び信号制御回路とは接続する必要が無いため好適である。 Note that the booster antenna described in this embodiment refers to an antenna circuit (hereinafter referred to as a booster antenna) that is larger in size than an antenna circuit that receives a signal from a reader / writer or a wireless signal such as a charger. . It means that the signal oscillated from the reader / writer or the charger can be efficiently transmitted to the target RFID by resonating in the frequency band in which the antenna circuit and the booster antenna are used and magnetically coupled. Since the booster antenna is coupled to the coil antenna via a magnetic field, it is preferable that the booster antenna does not need to be directly connected to the chip antenna and the signal control circuit.

本実施の形態におけるRFIDに用いる半導体装置について、図15に示すブロック図を用いて説明する。 A semiconductor device used for the RFID in this embodiment will be described with reference to a block diagram shown in FIG.

図15のRFID101は、アンテナ回路102、ブースターアンテナ1501、電源供給回路103、信号制御回路104によって構成されている。信号制御回路104は、増幅回路105、復調回路106、論理回路107、メモリコントロール回路108、メモリ回路109、論理回路110、増幅回路111、変調回路112によって構成される。また電源供給回路103は、整流回路113、バッテリー114、低周波信号発生回路115、スイッチ回路116、電源回路117によって構成される。また、図15においては、アンテナ回路102とリーダ/ライタ201との間で信号がブースターアンテナを介して送受信され、そしてリーダ/ライタ201からの信号を元に充電が行われることを示したブロック図でもある。実施の形態1における図2の構成との違いは、ブースターアンテナ1501がリーダ/ライタ201とアンテナ回路102との間にある点にある。

15 includes an

図15において、RFID101は、ブースターアンテナ1501がリーダ/ライタ201からの信号を受信し、アンテナ回路102とブースターアンテナ1501との磁界結合によりリーダ/ライタからの信号がアンテナ回路102で受信される。図15において、アンテナ回路102より電源供給回路103に入力される信号は、整流回路113、スイッチ回路116を介して電源回路117に入力される。また図15においてアンテナ回路102で受信する信号は整流回路113を介してバッテリー114に入力され、バッテリー114の充電が行われる。

In FIG. 15, in the

また図15において、アンテナ回路102より信号制御回路104に入力される信号は、増幅回路105を介して復調回路106により復調され、論理回路107、メモリコントロール回路108、メモリ回路109、論理回路110、増幅回路111を経て、変調回路112により変調され、アンテナ回路102より、リーダ/ライタ201に送信される。

In FIG. 15, a signal input from the

なお、アンテナ回路102は、実施の形態1で示した図4(A)に示す構成であればよい。また、整流回路113は、実施の形態1で示した図4(B)に示す構成であればよい。

Note that the

また、図15におけるアンテナ回路102については、実施の形態1で述べたアンテナ回路102の説明と同様であるためここでは説明を省略する。

15 is similar to the description of the

また、本実施の形態においては、アンテナ回路102がブースターアンテナ1501を介して信号を受信する際は、電磁誘導方式により信号の交信が行なわれる。そのため、図15におけるRFID101は、コイル状のアンテナ回路102、ブースターアンテナ1501を有する構成となる。図15において、リーダ/ライタ201のアンテナ回路中のコイル状のアンテナとRFID101のブースターアンテナ1501を近づけると、リーダ/ライタ201におけるアンテナ回路のコイル状のアンテナから交流磁界が発生する。交流磁界がRFID101内のコイル状のブースターアンテナ1501を貫き、電磁誘導によりRFID101内のコイル状のブースターアンテナの端子間(アンテナの一端と他端の間)に起電力が発生する。コイル状のブースターアンテナ1501において電磁誘導による起電力が発生すると共にブースターアンテナ自体から交流磁界が発生する。そして、ブースターアンテナ1501から発生する交流磁界がRFID101内のコイル状のアンテナ回路102を貫き、電磁誘導によりRFID101内のコイル状のアンテナ回路102の端子間(アンテナの一端と他端の間)に起電力が発生する。このようにして、RFID101は、リーダ/ライタ201から信号及び起電力を得ることができる。

In this embodiment, when the

本実施の形態においては、図15のブースターアンテナを具備する構成により、リーダ/ライタ201とRFID101間の信号の送受信についての通信距離を伸ばすことができ、信号のやりとりをより確実にすることができるため好適である。

In the present embodiment, the configuration including the booster antenna of FIG. 15 can increase the communication distance for transmission / reception of signals between the reader /

また、実施の形態1の図5において示したアンテナ回路の如く、リーダ/ライタ201との信号の送受信に第1のアンテナ回路301、充電器303からの無線信号の受信に第2のアンテナ回路302を設け、第1のアンテナ回路301とリーダ/ライタ201との信号の送受信にブースターアンテナを用いる構成としてもよい。その例として図16に第1のアンテナ回路301及び第2のアンテナ回路302及び充電器303を含む構成について示す。アンテナ回路とブースターアンテナを使用する周波数帯域で共振させ、磁界結合させることで、リーダ/ライタ201より発振された信号を、効率よく目的のRFIDへ伝達させることができ好適である。

Further, like the antenna circuit shown in FIG. 5 of

なお図16に示した構成において、ブースターアンテナ1501の同調を第1のアンテナ回路301に限らず、ブースターアンテナ1501が同調する周波数の帯域を変化させることにより他のアンテナと磁界結合させることもできる。例えば図16に示す構成において、ブースターアンテナ1501が充電器303からの信号を受信し第2のアンテナ回路302と磁界結合することで充電器からの信号を第2のアンテナに伝える構成であってもよい。

In the configuration shown in FIG. 16, the tuning of the

なお図16に示した構成において、ブースターアンテナ1501の同調を第1のアンテナ回路301または第2のアンテナ回路302のいずれか一方に限らず、ブースターアンテナ1501が同調する周波数の帯域を広げることにより複数のアンテナと磁界結合させることもできる。例えば、図16に示す構成において、ブースターアンテナ1501がリーダ/ライタ201及び充電器303からの信号を受信し第1のアンテナ回路301及び第2のアンテナ回路302と磁界結合することでリーダ/ライタからの信号及び充電器からの信号を送受信する構成であってもよい。この場合、第1のアンテナ回路301及び第2のアンテナ回路302の同調する周波数を近づけておくことにより、よりブースターアンテナ1501における電磁誘導の効率が上がるため好ましい。よって、第2のアンテナ回路302と充電器303間で送受信される信号の周波数m(mは正の数)は、第1のアンテナ回路301で送受信される信号の周波数をM(Mは正の数)とすると、0.5m<M<1.5mの関係にあり、且つm≠Mを満たす周波数であることが望ましい。前述の効果に加えて、第2のアンテナ回路302に入力される信号の周波数を前述の範囲に設定することにより、第1のアンテナ回路301及び第2のアンテナ回路302の形状を大きく異ならせることなく設計することが可能となり好適である。すなわち、リーダ/ライタ201とRFID101間の信号の送受信及び充電器303とRFID101間の信号の送受信についての通信距離を伸ばすことができ、データのやりとり及びバッテリー114への充電をより確実におこなうことができ好適である。

Note that in the configuration shown in FIG. 16, the tuning of the

また、図15に示すRFID101の信号制御回路104に、リーダ/ライタ201よりデータを書き込む際の動作、RFID101の信号制御回路104におけるメモリ回路109に記憶されたデータをリーダ/ライタ201が呼び出す動作については、リーダ/ライタ201からの信号がブースターアンテナを介してアンテナ回路に入力される以外、実施の形態1において説明した図1、図2における動作と同様であるため本実施の形態においてはその説明を省略する。

Further, an operation for writing data from the reader /

また、図15に示すRFID101に、外部の無線信号より電力を充電する際の動作については、実施の形態1において説明した図1における動作の説明と同様であるため本実施の形態においてはその説明を省略する。

15 is the same as the description of the operation in FIG. 1 described in the first embodiment because the operation when charging the

また、本実施の形態における低周波信号発生回路の構成及びタイミングチャートについては、実施の形態1で説明した図7、図8、図9、及びその説明箇所と同様であるため、本実施の形態においては説明を省略する。

The configuration and timing chart of the low-frequency signal generation circuit in this embodiment are the same as those in FIGS. 7, 8, and 9 described in

なお、本実施の形態においては、実施の形態2で説明した電源供給回路103における制御回路を設ける構成としてもよい。本実施の形態において制御回路を有する構成とすることにより、ブースターアンテナを設ける構成の効果に加えて、アンテナ回路から受信信号の電力と、バッテリー内に蓄電された電力を制御回路により比較することで、整流回路からの電力の供給か、バッテリーから電源回路への供給かを選択することによりさらなるバッテリーにおける消費電力の低減を図ることができるため好適である。

Note that in this embodiment mode, a control circuit in the

以上のように、本発明のRFIDを有する半導体装置は、バッテリーを有することを特徴とする。そのため、従来のように、電池の経時的な劣化に伴う個体情報の送受信にするための電力の不足を防止することができる。そして、本発明の半導体装置は、バッテリーに電力を供給するための信号を受信するアンテナを有することを特徴とする。そのため、充電器に直接接続することなく、RFIDを駆動するための電源を外部からの電波または電磁波の電力を利用してバッテリーを充電することができる。その結果、アクティブタイプのRFIDのような電池の残存容量の確認や電池の交換をする作業が発生するといったことなく、使用し続けることが可能になる。加えて、RFIDを駆動するための電力を常にバッテリー内に保持することにより、RFIDが動作するための十分な電力が得られ、リーダ/ライタとの通信距離を伸ばすことができる。 As described above, a semiconductor device having an RFID of the present invention has a battery. As a result, it is possible to prevent a shortage of power for transmitting / receiving individual information associated with deterioration of the battery over time, as in the past. The semiconductor device of the present invention includes an antenna that receives a signal for supplying power to the battery. For this reason, the battery can be charged by using the power of the radio wave or electromagnetic wave from the outside as a power source for driving the RFID without being directly connected to the charger. As a result, it is possible to continue using the battery without confirming the remaining capacity of the battery or exchanging the battery, such as active type RFID. In addition, by always holding the power for driving the RFID in the battery, sufficient power for operating the RFID can be obtained, and the communication distance with the reader / writer can be extended.

また、前述したように、本発明では低周波信号発生回路115の出力信号によりスイッチ回路116のオンとオフを切り替え、間欠的にRFIDを動作させ消費電力の低減を図っている。一般にRFIDは信号に対して常時動作しているが、データの内容や、用途によっては必ずしも常時応答しなくとも良い場合もある。そのような場合に、RFIDの動作を停止することによって、バッテリーや大容量のコンデンサーにおける消費電力を低減することができる。 Further, as described above, in the present invention, the switch circuit 116 is turned on and off by the output signal of the low frequency signal generation circuit 115, and the RFID is operated intermittently to reduce power consumption. In general, an RFID always operates with respect to a signal. However, depending on the contents of data and application, there is a case where it is not always necessary to respond. In such a case, by stopping the operation of the RFID, power consumption in a battery or a large-capacity capacitor can be reduced.

さらに、本実施の形態の構成においては、実施の形態1の構成に加えて、ブースターアンテナを有することを特徴とする。そのため、RFIDとリーダ/ライタ間のデータの送受信、RFIDと充電器からの充電用の信号の受信に対して、より確実に通信を行うことが可能となるといった利点を有する。 Further, the configuration of this embodiment is characterized by having a booster antenna in addition to the configuration of the first embodiment. Therefore, there is an advantage that more reliable communication can be performed with respect to transmission / reception of data between the RFID and the reader / writer and reception of a signal for charging from the RFID and the charger.

なお、本実施の形態は、本明細書中の他の実施の形態の記載と自由に組み合わせて実施することが可能である。 Note that this embodiment can be implemented in free combination with the description of the other embodiments in this specification.

本実施例では、本発明の無線通信によりデータの送受信をおこなう半導体装置(以下、RFID)におけるバッテリーの例について説明する本明細書において、バッテリーとは、充電することで連続使用時間を回復することができる電池のことをいう。バッテリーとしては、シート状に形成された電池を用いることが好ましく、例えばリチウム電池、好ましくはゲル状電解質を用いるリチウムポリマー電池や、リチウムイオン電池等を用いることで、小型化が可能である。勿論、充電可能な電池であればなんでもよく、ニッケル水素電池、ニカド電池などの充電放電可能な電池であってもよいし、また大容量のコンデンサーなどを用いることもできる。 In this embodiment, an example of a battery in a semiconductor device (hereinafter referred to as RFID) that transmits and receives data by wireless communication according to the present invention will be described. In this specification, a battery is used to recover continuous use time by charging. A battery that can be used. As the battery, a battery formed in a sheet shape is preferably used. For example, a lithium battery, preferably a lithium polymer battery using a gel electrolyte, a lithium ion battery, or the like can be used to reduce the size. Of course, any rechargeable battery may be used, and a chargeable / dischargeable battery such as a nickel metal hydride battery or a nickel-cadmium battery may be used, or a large-capacity capacitor may be used.

本実施例においては、バッテリーとしてリチウムイオン電池の例について説明する。リチウムイオン電池は、ニッカド電池、鉛電池などと比べて、メモリ効果がなく、電流量が大きく取れるなどの利点からが広く用いられている。また、リチウムイオン電池は近年、薄膜化の研究がおこなわれており、厚さ1μm〜数μmのものも作られつつある(以下、薄膜二次電池という)。このような薄膜二次電池をRFIDなどに貼り付けることによってフレキシブルな二次電池として活用できる。 In this embodiment, an example of a lithium ion battery will be described as a battery. Lithium ion batteries are widely used because they have no memory effect and have a large amount of current compared to nickel-cadmium batteries, lead batteries, and the like. In recent years, lithium ion batteries have been studied for thinning, and those having a thickness of 1 μm to several μm are being made (hereinafter referred to as thin film secondary batteries). By sticking such a thin film secondary battery to an RFID or the like, it can be used as a flexible secondary battery.

図17に本発明のバッテリーとして用いることが可能な薄膜二次電池の例を示す。図17に示した例においては、リチウムイオン薄膜電池の断面例である。 FIG. 17 shows an example of a thin film secondary battery that can be used as the battery of the present invention. The example shown in FIG. 17 is a cross-sectional example of a lithium ion thin film battery.

図17の積層構造について説明する。図17の基板7101上に電極となる集電体薄膜7102を成膜する。集電体薄膜7102は負極活物質層7103と密着性がよく、抵抗が小さいことが求められ、アルミニウム、銅、ニッケル、バナジウムなどを用いることができる。次に集電体薄膜7102上に負極活物質層7103を成膜する。一般には酸化バナジウム(V2O5)などが用いられる。次に負極活物質層7103上に固体電解質層7104を成膜する。一般にはリン酸リチウム(Li3PO4)などが用いられる。次に固体電解質層7104上に正極活物質層7105を成膜する。一般にはマンガン酸リチウム(LiMn2O4)などが用いられる。コバルト酸リチウム(LiCoO2)やニッケル酸リチウム(LiNiO2)を用いても良い。次に正極活物質層7105上に電極となる集電体薄膜7106を成膜する。集電体薄膜7106は正極活物質層7105と密着性がよく、抵抗が小さいことが求められ、アルミニウム、銅、ニッケル、バナジウムなどを用いることができる。 The stacked structure in FIG. 17 will be described. A current collector thin film 7102 to be an electrode is formed over the substrate 7101 in FIG. The current collector thin film 7102 is required to have good adhesion to the negative electrode active material layer 7103 and low resistance, and aluminum, copper, nickel, vanadium, or the like can be used. Next, a negative electrode active material layer 7103 is formed over the current collector thin film 7102. In general, vanadium oxide (V 2 O 5 ) or the like is used. Next, a solid electrolyte layer 7104 is formed over the negative electrode active material layer 7103. In general, lithium phosphate (Li 3 PO 4 ) or the like is used. Next, a positive electrode active material layer 7105 is formed over the solid electrolyte layer 7104. Generally, lithium manganate (LiMn 2 O 4 ) or the like is used. Lithium cobaltate (LiCoO 2 ) or lithium nickelate (LiNiO 2 ) may be used. Next, a current collector thin film 7106 to be an electrode is formed over the positive electrode active material layer 7105. The current collector thin film 7106 is required to have good adhesion to the positive electrode active material layer 7105 and low resistance, and aluminum, copper, nickel, vanadium, or the like can be used.

なお、上記集電体薄膜7102、負極活物質層7103、固体電解質層7104、正極活物質層7105、集電体薄膜7106の薄膜層は、スパッタ技術を用いて形成しても良いし、蒸着技術を用いても良い。また集電体薄膜7102、負極活物質層7103、固体電解質層7104、正極活物質層7105、集電体薄膜7106の厚さは0.1μm〜3μmが望ましい。 Note that the current collector thin film 7102, the negative electrode active material layer 7103, the solid electrolyte layer 7104, the positive electrode active material layer 7105, and the current collector thin film 7106 may be formed using a sputtering technique or a vapor deposition technique. May be used. In addition, the thickness of the current collector thin film 7102, the negative electrode active material layer 7103, the solid electrolyte layer 7104, the positive electrode active material layer 7105, and the current collector thin film 7106 is preferably 0.1 μm to 3 μm.

次に以下に充電時、放電時の動作を説明する。充電時には、正極活物質からリチウムがイオンとなって離脱する。そのリチウムイオンは固体電解質層を介して負極活物質に吸収される。このときに、正極活物質から外部へ電子が放出される。 Next, the operation during charging and discharging will be described below. During charging, lithium is released from the positive electrode active material as ions. The lithium ions are absorbed by the negative electrode active material through the solid electrolyte layer. At this time, electrons are emitted from the positive electrode active material to the outside.

また放電時には、負極活物質からリチウムがイオンとなって離脱する。そのリチウムイオンは固体電解質層を介して、正極活物質に吸収される。このとき負極活物質層から外部に電子が放出される。この様にして薄膜二次電池は動作する。 Further, during discharge, lithium is separated from the negative electrode active material as ions. The lithium ions are absorbed by the positive electrode active material through the solid electrolyte layer. At this time, electrons are emitted from the negative electrode active material layer to the outside. In this way, the thin film secondary battery operates.

なお、再度集電体薄膜7102、負極活物質層7103、固体電解質層7104、正極活物質層7105、集電体薄膜7106の薄膜層を重ねて形成することで、より大きい電力の充放電が可能になるため好適である。 Note that by forming the current collector thin film 7102, the negative electrode active material layer 7103, the solid electrolyte layer 7104, the positive electrode active material layer 7105, and the current collector thin film 7106 again, charging and discharging with higher power is possible. This is preferable.

以上のように、薄膜二次電池を形成することで、シート状であり、且つ充放電可能なバッテリーを形成することができる。 As described above, by forming a thin film secondary battery, a sheet-like battery that can be charged and discharged can be formed.

本実施例は、上記の実施の形態および他の実施例と自由に組み合わせることができる。すなわち、定期的にバッテリーに対し充電を行うことにより、従来のように、電池の経時的な劣化に伴う個体情報の送受信にするための電力の不足を防止することができる。そして、本発明の半導体装置は、バッテリーへの充電に際し、RFIDに設けられたアンテナ回路にて、電力を受電し、当該バッテリーの充電を行うことを特徴とする。そのため、充電器に直接接続することなく、RFIDを駆動するための電源を外部からの電波または電磁波の電力を利用してバッテリーを充電することができる。その結果、アクティブタイプのRFIDのような電池の残存容量の確認や電池の交換をする作業が発生するといったことなく、使用し続けることが可能になる。加えて、RFIDを駆動するための電力を常にバッテリー内に保持することにより、RFIDが動作するための十分な電力が得られ、リーダ/ライタとの通信距離を伸ばすことができる。 This embodiment can be freely combined with the above embodiment mode and other embodiments. That is, by periodically charging the battery, it is possible to prevent a shortage of power for transmitting / receiving individual information associated with deterioration of the battery over time, as in the past. The semiconductor device of the present invention is characterized in that when charging a battery, the antenna circuit provided in the RFID receives power and charges the battery. For this reason, the battery can be charged by using the power of the radio wave or electromagnetic wave from the outside as a power source for driving the RFID without being directly connected to the charger. As a result, it is possible to continue using the battery without confirming the remaining capacity of the battery or exchanging the battery, such as active type RFID. In addition, by always holding the power for driving the RFID in the battery, sufficient power for operating the RFID can be obtained, and the communication distance with the reader / writer can be extended.

また、本発明の半導体装置は上記バッテリーを具備することによる利点に加え、外部との個体情報の送受信を行う信号制御回路に電力を供給する電源供給回路において、スイッチ回路を設け、定期的に信号制御回路への電力の供給を制御することを特徴とする。電源供給回路に設けられたスイッチ回路において信号制御回路への電力の供給を制御することにより、RFIDの動作を間欠的におこなうことができる。そのためバッテリーにおける消費電力の低減を図り、さらに無線信号による電力の供給がなくても、長時間の動作を可能にすることができる。 In addition to the advantages provided by the battery, the semiconductor device of the present invention is provided with a switch circuit in a power supply circuit that supplies power to a signal control circuit that transmits / receives individual information to / from the outside. The power supply to the control circuit is controlled. By controlling the power supply to the signal control circuit in the switch circuit provided in the power supply circuit, the RFID operation can be performed intermittently. Therefore, it is possible to reduce power consumption in the battery and to operate for a long time without supplying power by a wireless signal.

本実施例では、上記実施の形態で示した本発明の半導体装置をRFIDとして用いた際の作製方法の一例に関して、図面を参照して説明する。本実施例においては、アンテナ回路、電源供給回路、信号制御回路を同じ基板上に設ける構成について説明する。なお、基板上に一度にアンテナ回路、電源供給回路、信号制御回路を形成し、電源供給回路、信号制御回路を構成するトランジスタを薄膜トランジスタとすることで、小型化を図ることができるため好適である。また、電源供給回路におけるバッテリーとしては上記実施例で説明した薄膜二次電池を用いた例について本実施例では説明する。 In this example, an example of a manufacturing method when the semiconductor device of the present invention described in the above embodiment mode is used as an RFID will be described with reference to drawings. In this embodiment, a structure in which an antenna circuit, a power supply circuit, and a signal control circuit are provided over the same substrate will be described. Note that it is preferable that an antenna circuit, a power supply circuit, and a signal control circuit be formed over the substrate at once, and the transistors constituting the power supply circuit and the signal control circuit be thin film transistors, which can be downsized. . In this embodiment, an example in which the thin film secondary battery described in the above embodiment is used as the battery in the power supply circuit will be described.

なお、本実施例においては、上記実施の形態で述べたアンテナ回路について、その形状及び取り付け位置について述べるに留まるため、単にアンテナと称することにする。 Note that in this example, the antenna circuit described in the above embodiment is simply referred to as an antenna because only the shape and the mounting position thereof are described.

まず、基板1301の一表面に絶縁膜1302を介して剥離層1303を形成し、続けて下地膜として機能する絶縁膜1304と半導体膜1305(例えば、非晶質珪素を含む膜)を積層して形成する(図18(A)参照)。なお、絶縁膜1302、剥離層1303、絶縁膜1304および非晶質半導体膜1305は、連続して形成することができる。

First, a

基板1301は、ガラス基板、石英基板、金属基板(例えばステンレス基板など)、セラミック基板、Si基板等の半導体基板、など、から選択されるものである。他にもプラスチック基板として、ポリエチレンテレフタラート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルフォン(PES)、アクリルなどの基板を選択することもできる。なお、本工程では、剥離層1303は、絶縁膜1302を介して基板1301の全面に設けているが、必要に応じて、基板1301の全面に剥離層を設けた後に、フォトリソグラフィ法により選択的に設けてもよい。

The

絶縁膜1302、絶縁膜1304は、CVD法やスパッタリング法等を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン(SiOxNy)(x>y>0)、窒化酸化シリコン(SiNxOy)(x>y>0)等の絶縁材料を用いて形成する。例えば、絶縁膜1302、1304を2層構造とする場合、第1層目の絶縁膜として窒化酸化シリコン膜を形成し、第2層目の絶縁膜として酸化窒化シリコン膜を形成するとよい。また、第1層目の絶縁膜として窒化シリコン膜を形成し、第2層目の絶縁膜として酸化シリコン膜を形成してもよい。絶縁膜1302は、基板1301から剥離層1303又はその上に形成される素子に不純物元素が混入するのを防ぐブロッキング層として機能し、絶縁膜1304は基板1301、剥離層1303からその上に形成される素子に不純物元素が混入するのを防ぐブロッキング層として機能する。このように、ブロッキング層として機能する絶縁膜1302、1304を形成することによって、基板1301からNaなどのアルカリ金属やアルカリ土類金属が、剥離層1303から剥離層に含まれる不純物元素がこの上に形成する素子に悪影響を与えることを防ぐことができる。なお、基板1301として石英を用いるような場合には絶縁膜1302、1304を省略してもよい。

The insulating

剥離層1303は、金属膜や金属膜と金属酸化膜の積層構造等を用いることができる。金属膜としては、タングステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ニオブ(Nb)、ニッケル(Ni)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)から選択された元素または元素を主成分とする合金材料若しくは化合物材料からなる膜を単層又は積層して形成する。また、これらの材料は、スパッタ法やプラズマCVD法等の各種CVD法等を用いて形成することができる。金属膜と金属酸化膜の積層構造としては、上述した金属膜を形成した後に、酸素雰囲気下またはN2O雰囲気下におけるプラズマ処理、酸素雰囲気下またはN2O雰囲気下における加熱処理を行うことによって、金属膜表面に当該金属膜の酸化物または酸化窒化物を設けることができる。例えば、金属膜としてスパッタ法やCVD法等によりタングステン膜を設けた場合、タングステン膜にプラズマ処理を行うことによって、タングステン膜表面にタングステン酸化物からなる金属酸化膜を形成することができる。また、この場合、タングステンの酸化物は、WOxで表され、Xは2〜3であり、Xが2の場合(WO2)、Xが2.5の場合(W2O5)、Xが2.75の場合(W4O11)、Xが3の場合(WO3)などがある。タングステンの酸化物を形成するにあたり、上記に挙げたXの値に特に制約はなく、エッチングレート等を基に、どの酸化物を形成するかを決めるとよい。他にも、例えば、金属膜(例えば、タングステン)を形成した後に、当該金属膜上にスパッタ法で酸化珪素(SiO2)等の絶縁膜を設けると共に、金属膜上に金属酸化物(例えば、タングステン上にタングステン酸化物)を形成してもよい。また、プラズマ処理として、例えば上述した高密度プラズマ処理を行ってもよい。また、金属酸化膜の他にも、金属窒化物や金属酸化窒化物を用いてもよい。この場合、金属膜に窒素雰囲気下または窒素と酸素雰囲気下でプラズマ処理や加熱処理を行えばよい。

For the

非晶質半導体膜1305は、スパッタリング法、LPCVD法、プラズマCVD法等により、25〜200nm(好ましくは30〜150nm)の厚さで形成する。

The

次に、非晶質半導体膜1305にレーザー光を照射して結晶化を行う。なお、レーザー光の照射と、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法とを組み合わせた方法等により非晶質半導体膜1305の結晶化を行ってもよい。その後、得られた結晶質半導体膜を所望の形状にエッチングして、結晶質半導体膜1305a〜1305fを形成し、当該半導体膜1305a〜1305fを覆うようにゲート絶縁膜1306を形成する(図18(B)参照)。

Next, crystallization is performed by irradiating the

ゲート絶縁膜1306は、CVD法やスパッタリング法等を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン(SiOxNy)(x>y>0)、窒化酸化シリコン(SiNxOy)(x>y>0)等の絶縁材料を用いて形成する。例えば、ゲート絶縁膜1306を2層構造とする場合、第1層目の絶縁膜として酸化窒化シリコン膜を形成し、第2層目の絶縁膜として窒化酸化シリコン膜を形成するとよい。また、第1層目の絶縁膜として酸化シリコン膜を形成し、第2層目の絶縁膜として窒化シリコン膜を形成してもよい。

The

結晶質半導体膜1305a〜1305fの作製工程の一例を以下に簡単に説明すると、まず、プラズマCVD法を用いて、膜厚50〜60nmの非晶質半導体膜を形成する。次に、結晶化を助長する金属元素であるニッケルを含む溶液を非晶質半導体膜上に保持させた後、非晶質半導体膜に脱水素化の処理(500℃、1時間)と、熱結晶化の処理(550℃、4時間)を行って結晶質半導体膜を形成する。その後、レーザー光を照射し、フォトリソグラフィ法を用いることよって結晶質半導体膜1305a〜1305fを形成する。なお、結晶化を助長する金属元素を用いる熱結晶化を行わずに、レーザー光の照射だけで非晶質半導体膜の結晶化を行ってもよい。

An example of a manufacturing process of the

結晶化に用いるレーザー発振器としては、連続発振型のレーザービーム(CWレーザービーム)やパルス発振型のレーザービーム(パルスレーザービーム)を用いることができる。ここで用いることができるレーザービームは、Arレーザー、Krレーザー、エキシマレーザーなどの気体レーザー、単結晶のYAG、YVO4、フォルステライト(Mg2SiO4)、YAlO3、GdVO4、若しくは多結晶(セラミック)のYAG、Y2O3、YVO4、YAlO3、GdVO4に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザー、ガラスレーザー、ルビーレーザー、アレキサンドライトレーザー、Ti:サファイアレーザー、銅蒸気レーザーまたは金蒸気レーザーのうち一種または複数種から発振されるものを用いることができる。このようなレーザービームの基本波、及びこれらの基本波の第2高調波から第4高調波のレーザービームを照射することで、大粒径の結晶を得ることができる。例えば、Nd:YVO4レーザー(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を用いることができる。このときレーザーのパワー密度は0.01〜100MW/cm2程度(好ましくは0.1〜10MW/cm2)が必要である。そして、走査速度を10〜2000cm/sec程度として照射する。なお、単結晶のYAG、YVO4、フォルステライト(Mg2SiO4)、YAlO3、GdVO4、若しくは多結晶(セラミック)のYAG、Y2O3、YVO4、YAlO3、GdVO4に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザー、Arイオンレーザー、またはTi:サファイアレーザーは、連続発振をさせることが可能であり、Qスイッチ動作やモード同期などを行うことによって10MHz以上の発振周波数でパルス発振をさせることも可能である。10MHz以上の発振周波数でレーザービームを発振させると、半導体膜がレーザーによって溶融してから固化するまでの間に、次のパルスが半導体膜に照射される。従って、発振周波数が低いパルスレーザーを用いる場合と異なり、半導体膜中において固液界面を連続的に移動させることができるため、走査方向に向かって連続的に成長した結晶粒を得ることができる。 As a laser oscillator used for crystallization, a continuous wave laser beam (CW laser beam) or a pulsed laser beam (pulse laser beam) can be used. The laser beam that can be used here is a gas laser such as Ar laser, Kr laser, or excimer laser, single crystal YAG, YVO 4 , forsterite (Mg 2 SiO 4 ), YAlO 3 , GdVO 4 , or polycrystalline ( (Ceramics) YAG, Y 2 O 3 , YVO 4 , YAlO 3 , GdVO 4 with one or more of Nd, Yb, Cr, Ti, Ho, Er, Tm, Ta added as dopants Lasers oscillated from one or more of laser, glass laser, ruby laser, alexandrite laser, Ti: sapphire laser, copper vapor laser or gold vapor laser as a medium can be used. By irradiating the fundamental wave of such a laser beam and the second to fourth harmonics of these fundamental waves, a crystal having a large grain size can be obtained. For example, the second harmonic (532 nm) or the third harmonic (355 nm) of an Nd: YVO 4 laser (fundamental wave 1064 nm) can be used. In this case, a laser power density is about 0.01 to 100 MW / cm 2 (preferably 0.1 to 10 MW / cm 2) is required. Then, irradiation is performed at a scanning speed of about 10 to 2000 cm / sec. Note that single crystal YAG, YVO 4 , forsterite (Mg 2 SiO 4 ), YAlO 3 , GdVO 4 , or polycrystalline (ceramic) YAG, Y 2 O 3 , YVO 4 , YAlO 3 , GdVO 4 , dopants Nd, Yb, Cr, Ti, Ho, Er, Tm, Ta as a medium, a laser, Ar ion laser, or Ti: sapphire laser with one or more added as a medium should be continuously oscillated It is also possible to perform pulse oscillation at an oscillation frequency of 10 MHz or more by performing Q switch operation, mode synchronization, or the like. When a laser beam is oscillated at an oscillation frequency of 10 MHz or higher, the semiconductor film is irradiated with the next pulse during the period from when the semiconductor film is melted by the laser to solidification. Therefore, unlike the case of using a pulse laser having a low oscillation frequency, the solid-liquid interface can be continuously moved in the semiconductor film, so that crystal grains continuously grown in the scanning direction can be obtained.

また、ゲート絶縁膜1306は、半導体膜1305a〜1305fに対し前述の高密度プラズマ処理を行い、表面を酸化又は窒化することで形成しても良い。例えば、He、Ar、Kr、Xeなどの希ガスと、酸素、酸化窒素(NO2)、アンモニア、窒素、水素などの混合ガスを導入したプラズマ処理で形成する。この場合のプラズマの励起は、マイクロ波の導入により行うと、低電子温度で高密度のプラズマを生成することができる。この高密度プラズマで生成された酸素ラジカル(OHラジカルを含む場合もある)や窒素ラジカル(NHラジカルを含む場合もある)によって、半導体膜の表面を酸化又は窒化することができる。

Alternatively, the

このような高密度プラズマを用いた処理により、1〜20nm、代表的には5〜10nmの絶縁膜が半導体膜に形成される。この場合の反応は、固相反応であるため、当該絶縁膜と半導体膜との界面準位密度はきわめて低くすることができる。このような、高密度プラズマ処理は、半導体膜(結晶性シリコン、或いは多結晶シリコン)を直接酸化(若しくは窒化)するため、形成される絶縁膜の厚さは理想的には、ばらつきをきわめて小さくすることができる。加えて、結晶性シリコンの結晶粒界でも酸化が強くされることがないため、非常に好ましい状態となる。すなわち、ここで示す高密度プラズマ処理で半導体膜の表面を固相酸化することにより、結晶粒界において異常に酸化反応をさせることなく、均一性が良く、界面準位密度が低い絶縁膜を形成することができる。 By such treatment using high-density plasma, an insulating film with a thickness of 1 to 20 nm, typically 5 to 10 nm, is formed over the semiconductor film. Since the reaction in this case is a solid-phase reaction, the interface state density between the insulating film and the semiconductor film can be extremely low. Such high-density plasma treatment directly oxidizes (or nitrides) a semiconductor film (crystalline silicon or polycrystalline silicon), so that the thickness of the formed insulating film ideally has extremely small variation. can do. In addition, since oxidation is not strengthened even at the crystal grain boundaries of crystalline silicon, a very favorable state is obtained. That is, the surface of the semiconductor film is solid-phase oxidized by the high-density plasma treatment shown here, thereby forming an insulating film with good uniformity and low interface state density without causing an abnormal oxidation reaction at the grain boundaries. can do.

ゲート絶縁膜は、高密度プラズマ処理によって形成される絶縁膜のみを用いても良いし、それにプラズマや熱反応を利用したCVD法で酸化シリコン、酸窒化シリコン、窒化シリコンなどの絶縁膜を堆積し、積層させても良い。いずれにしても、高密度プラズマで形成した絶縁膜をゲート絶縁膜の一部又は全部に含んで形成されるトランジスタは、特性のばらつきを小さくすることができる。 As the gate insulating film, only an insulating film formed by high-density plasma treatment may be used, or an insulating film such as silicon oxide, silicon oxynitride, or silicon nitride is deposited by a CVD method using plasma or thermal reaction. , May be laminated. In any case, a transistor formed by including an insulating film formed by high-density plasma in part or all of the gate insulating film can reduce variation in characteristics.