JP4879515B2 - 表示装置及び電子機器 - Google Patents

表示装置及び電子機器 Download PDFInfo

- Publication number

- JP4879515B2 JP4879515B2 JP2005144874A JP2005144874A JP4879515B2 JP 4879515 B2 JP4879515 B2 JP 4879515B2 JP 2005144874 A JP2005144874 A JP 2005144874A JP 2005144874 A JP2005144874 A JP 2005144874A JP 4879515 B2 JP4879515 B2 JP 4879515B2

- Authority

- JP

- Japan

- Prior art keywords

- emitting element

- light emitting

- switch

- electrode

- pixel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000003990 capacitor Substances 0.000 claims description 55

- 239000010409 thin film Substances 0.000 claims description 55

- 239000010408 film Substances 0.000 description 146

- 239000011229 interlayer Substances 0.000 description 49

- 239000010410 layer Substances 0.000 description 45

- 230000002441 reversible effect Effects 0.000 description 45

- 239000000463 material Substances 0.000 description 37

- 230000006870 function Effects 0.000 description 33

- 239000004065 semiconductor Substances 0.000 description 30

- 230000008859 change Effects 0.000 description 29

- 230000006866 deterioration Effects 0.000 description 28

- 239000000758 substrate Substances 0.000 description 28

- 230000002829 reductive effect Effects 0.000 description 24

- 239000011368 organic material Substances 0.000 description 22

- 238000000034 method Methods 0.000 description 19

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 12

- 238000009499 grossing Methods 0.000 description 11

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 10

- 238000010586 diagram Methods 0.000 description 10

- 229910052710 silicon Inorganic materials 0.000 description 10

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 9

- 238000010438 heat treatment Methods 0.000 description 9

- 229910052751 metal Inorganic materials 0.000 description 9

- 239000002184 metal Substances 0.000 description 9

- 239000010703 silicon Substances 0.000 description 9

- 239000010936 titanium Substances 0.000 description 9

- 239000000956 alloy Substances 0.000 description 8

- 229910045601 alloy Inorganic materials 0.000 description 7

- 230000005281 excited state Effects 0.000 description 7

- 239000011521 glass Substances 0.000 description 7

- 239000012535 impurity Substances 0.000 description 7

- 229910010272 inorganic material Inorganic materials 0.000 description 7

- 239000011147 inorganic material Substances 0.000 description 7

- 238000002161 passivation Methods 0.000 description 7

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 7

- 230000007547 defect Effects 0.000 description 6

- 230000007613 environmental effect Effects 0.000 description 6

- 238000012544 monitoring process Methods 0.000 description 6

- 229910052814 silicon oxide Inorganic materials 0.000 description 6

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 5

- 239000010949 copper Substances 0.000 description 5

- 239000013078 crystal Substances 0.000 description 5

- 230000009977 dual effect Effects 0.000 description 5

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 5

- 239000001257 hydrogen Substances 0.000 description 5

- 229910052739 hydrogen Inorganic materials 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 229910052757 nitrogen Inorganic materials 0.000 description 5

- 230000010355 oscillation Effects 0.000 description 5

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 5

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 4

- CSDREXVUYHZDNP-UHFFFAOYSA-N alumanylidynesilicon Chemical compound [Al].[Si] CSDREXVUYHZDNP-UHFFFAOYSA-N 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 4

- 230000015556 catabolic process Effects 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 230000006378 damage Effects 0.000 description 4

- 230000007423 decrease Effects 0.000 description 4

- 239000007772 electrode material Substances 0.000 description 4

- 238000002347 injection Methods 0.000 description 4

- 239000007924 injection Substances 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 229910052759 nickel Inorganic materials 0.000 description 4

- 239000001301 oxygen Substances 0.000 description 4

- 229910052760 oxygen Inorganic materials 0.000 description 4

- 239000003566 sealing material Substances 0.000 description 4

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 4

- 229910052719 titanium Inorganic materials 0.000 description 4

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 3

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 3

- 230000002238 attenuated effect Effects 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 238000002425 crystallisation Methods 0.000 description 3

- 230000008025 crystallization Effects 0.000 description 3

- 230000005611 electricity Effects 0.000 description 3

- 239000007789 gas Substances 0.000 description 3

- 238000005247 gettering Methods 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 239000010931 gold Substances 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- 238000005192 partition Methods 0.000 description 3

- 238000007789 sealing Methods 0.000 description 3

- -1 specifically Chemical compound 0.000 description 3

- 230000003068 static effect Effects 0.000 description 3

- 125000001424 substituent group Chemical group 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- 229910000838 Al alloy Inorganic materials 0.000 description 2

- 229910004261 CaF 2 Inorganic materials 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 2

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 2

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 2

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- XCJYREBRNVKWGJ-UHFFFAOYSA-N copper(II) phthalocyanine Chemical compound [Cu+2].C12=CC=CC=C2C(N=C2[N-]C(C3=CC=CC=C32)=N2)=NC1=NC([C]1C=CC=CC1=1)=NC=1N=C1[C]3C=CC=CC3=C2[N-]1 XCJYREBRNVKWGJ-UHFFFAOYSA-N 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 2

- 238000006731 degradation reaction Methods 0.000 description 2

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000000605 extraction Methods 0.000 description 2

- 125000001153 fluoro group Chemical group F* 0.000 description 2

- 229910003437 indium oxide Inorganic materials 0.000 description 2

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 230000001678 irradiating effect Effects 0.000 description 2

- 239000011777 magnesium Substances 0.000 description 2

- 230000007257 malfunction Effects 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 239000011733 molybdenum Substances 0.000 description 2

- IBHBKWKFFTZAHE-UHFFFAOYSA-N n-[4-[4-(n-naphthalen-1-ylanilino)phenyl]phenyl]-n-phenylnaphthalen-1-amine Chemical compound C1=CC=CC=C1N(C=1C2=CC=CC=C2C=CC=1)C1=CC=C(C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C3=CC=CC=C3C=CC=2)C=C1 IBHBKWKFFTZAHE-UHFFFAOYSA-N 0.000 description 2

- 125000000962 organic group Chemical group 0.000 description 2

- 239000004033 plastic Substances 0.000 description 2

- 229920003023 plastic Polymers 0.000 description 2

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 2

- 229920000139 polyethylene terephthalate Polymers 0.000 description 2

- 239000005020 polyethylene terephthalate Substances 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 239000002861 polymer material Substances 0.000 description 2

- 229920001709 polysilazane Polymers 0.000 description 2

- 230000000750 progressive effect Effects 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 238000001771 vacuum deposition Methods 0.000 description 2

- BCMCBBGGLRIHSE-UHFFFAOYSA-N 1,3-benzoxazole Chemical class C1=CC=C2OC=NC2=C1 BCMCBBGGLRIHSE-UHFFFAOYSA-N 0.000 description 1

- 229920001621 AMOLED Polymers 0.000 description 1

- OYPRJOBELJOOCE-UHFFFAOYSA-N Calcium Chemical compound [Ca] OYPRJOBELJOOCE-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- 229910015711 MoOx Inorganic materials 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- 206010047571 Visual impairment Diseases 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 239000003513 alkali Substances 0.000 description 1

- 229910052783 alkali metal Inorganic materials 0.000 description 1

- 150000001340 alkali metals Chemical class 0.000 description 1

- 125000000217 alkyl group Chemical group 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 150000001408 amides Chemical class 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 239000002585 base Substances 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 229910052792 caesium Inorganic materials 0.000 description 1

- TVFDJXOCXUVLDH-UHFFFAOYSA-N caesium atom Chemical compound [Cs] TVFDJXOCXUVLDH-UHFFFAOYSA-N 0.000 description 1

- 229910052791 calcium Inorganic materials 0.000 description 1

- 239000011575 calcium Substances 0.000 description 1

- 239000006229 carbon black Substances 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 239000002274 desiccant Substances 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 238000000295 emission spectrum Methods 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 230000001747 exhibiting effect Effects 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 230000005283 ground state Effects 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 239000011344 liquid material Substances 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 230000007774 longterm Effects 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 229910000476 molybdenum oxide Inorganic materials 0.000 description 1

- PQQKPALAQIIWST-UHFFFAOYSA-N oxomolybdenum Chemical compound [Mo]=O PQQKPALAQIIWST-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920001690 polydopamine Polymers 0.000 description 1

- 239000011112 polyethylene naphthalate Substances 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 229910052761 rare earth metal Inorganic materials 0.000 description 1

- 150000002910 rare earth metals Chemical class 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- YYMBJDOZVAITBP-UHFFFAOYSA-N rubrene Chemical compound C1=CC=CC=C1C(C1=C(C=2C=CC=CC=2)C2=CC=CC=C2C(C=2C=CC=CC=2)=C11)=C(C=CC=C2)C2=C1C1=CC=CC=C1 YYMBJDOZVAITBP-UHFFFAOYSA-N 0.000 description 1

- 239000010979 ruby Substances 0.000 description 1

- 229910001750 ruby Inorganic materials 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000007858 starting material Substances 0.000 description 1

- 229910052712 strontium Inorganic materials 0.000 description 1

- CIOAGBVUUVVLOB-UHFFFAOYSA-N strontium atom Chemical compound [Sr] CIOAGBVUUVVLOB-UHFFFAOYSA-N 0.000 description 1

- 229920003002 synthetic resin Polymers 0.000 description 1

- 239000000057 synthetic resin Substances 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 229910052723 transition metal Inorganic materials 0.000 description 1

- 150000003624 transition metals Chemical class 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

- 239000011787 zinc oxide Substances 0.000 description 1

Images

Landscapes

- Electroluminescent Light Sources (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Control Of El Displays (AREA)

Description

"An Innovative Pixel-Driving Scheme for 64-Level Gray-Scale Full-Color Active Matrix OLED Displays" Hajime Akimoto et alSID'02DIGEST P972-975 "A 3.5-inch OLED Display using a 4-TFT Pixel Circuit with an Innovative Pixel Driving Scheme" Hiroshi Kageyama,Hajime Akimoto SID'03DIGEST P96-99

また画素領域と、ドライバとの間に温度補償機能を有する素子が設けられていてもよい。

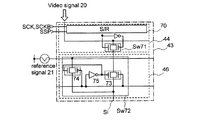

本実施の形態では、画素構成について説明する。

本実施の形態では、通常のCMOS構成のインバータと異なるインバータの構成について説明する。インバータ17は1つの極性のトランジスタを有するように構成することができる。その場合、トランジスタと抵抗素子を設けたり、1つの極性を有するトランジスタを2つ設けてもよい。具体的なインバータを有する画素回路は、図39、図40に示す。

本実施の形態では、図1に示した等価回路を有する画素の画素部のレイアウトの一例について説明する。

本実施の形態では、図3に一例を示した画素部の断面について説明する。

なお、補助配線を保持容量用の配線やインバータ用の電源線と共用することもできる。その結果、配線数を増やすことなく、補助配線を設けることができる。このような構成によって、製造歩留まりを向上させることができる。図43に示す補助配線の構成は、本発明の画素構成のいずれにも適用することができる。

本実施の形態では、上記実施の形態で示した画素部を有する表示パネルの構造を説明する。

本実施の形態では、上記実施の形態で示した画素部を有する表示パネルであって、第1及び第2のゲートドライバを共用する構造を、図12を用いて説明する。

本実施の形態では、逆方向電圧を印加する動作、及びそのための画素構成について説明する。

なお1フレーム期間中、発光素子18の対向電極の電位はV3に固定し、インバータ17のV2より大きくなるように設定する。その結果、消去期間において、発光素子18へ逆方向電圧を印加することができる。つまり、消去用走査線を順に選択し、トランジスタTr2がオンとなるとき、画素へ逆方向電圧を印加することができる。また図20に示す画素では、トランジスタTr2がオンとなるときに加え、ビデオ信号によって発光素子18が非点灯となるときにも逆方向電圧を印加することができる。

本実施の形態では温度補償機能について説明する。

本実施の形態では、モニター用発光素子66から得られる劣化情報について説明する。

η(t)= L0/J0 × f(t) ・・・(1)

ここで、f(t)は、以下のような指数関数で表せることが知られている。

f(t)= exp{−(t/α)β} ・・・(2)

なお、αは中期的、又は長期的な劣化を表すパラメータであり、βは初期劣化を表すパラメータであり、これらは実験的に求めることができる。

L = η(t)× J(t) ・・・(3)

したがって、電圧駆動を行う場合、式(3)でL=L0(=一定)とすることにより、下記式(4)が成り立たなければならない。

L0 = η(t)× J(t) ・・・(4)

J(t)= J0/f(t) ・・・(5)

式(5)は現象的には、「輝度を一定に保つためには、電流効率が低下していくことを考慮し、徐々に電流密度をJ0よりも上げていかなければならない」ことを表している。なぜならば、式(2)より、f(t)は単調減少の関数だからである。

J(t)= C × Vx(t) ・・・(6)

である。xは素子で決まるべき乗であり、Cは定数である。

したがって、式(6)を式(5)に代入し、式(2)を考慮すると、以下の式が成り立つ。

V(t)= Const.×[exp(t/α)β]1/x ・・・(7)

この式(7)が、「電圧駆動するためには電圧がどのように変化すればよいか」を表す式である。Const.は初期の電流密度J0およびxによって決まる定数(Const.=(J0/C)1/x)である。

本実施の形態では、保護回路について説明する。

本実施の形態では、上記実施の形態とは異なる画素構成について説明する。

発光素子を含む画素領域を備えた表示装置を用いた電子機器として、テレビジョン装置(テレビ、テレビジョン受信機)、デジタルカメラ、デジタルビデオカメラ、携帯電話装置(携帯電話機)、PDA等の携帯情報端末、携帯型ゲーム機、モニター、コンピュータ、カーオーディオ等の音響再生装置、家庭用ゲーム機等の記録媒体を備えた画像再生装置等が挙げられる。その具体例について、図34を参照して説明する。

Claims (2)

- 第1のスイッチと、第2のスイッチと、第3のスイッチと、第1の容量素子と、第2の容量素子と、インバータと、発光素子と、電流源と、を有し、

前記インバータは、pチャネル型の薄膜トランジスタと、nチャネル型の薄膜トランジスタとを有し、

前記第1のスイッチの一方の電極は、ビデオ信号または基準信号が入力される第1の配線と電気的に接続され、

前記第1のスイッチの他方の電極は、前記第1の容量素子の一方の電極と電気的に接続され、

前記第1の容量素子の他方の電極は、固定電位が与えられる第2の配線と電気的に接続され、

前記第1のスイッチの他方の電極は、前記第2の容量素子の一方の電極と電気的に接続され、

前記第2の容量素子の他方の電極は、前記pチャネル型の薄膜トランジスタのゲートと電気的に接続され、

前記第2の容量素子の他方の電極は、前記nチャネル型の薄膜トランジスタのゲートと電気的に接続され、

前記pチャネル型の薄膜トランジスタのソースまたはドレインの一方は、第1の電源線と電気的に接続され、

前記pチャネル型の薄膜トランジスタのソースまたはドレインの他方は、前記第2のスイッチの他方の電極と電気的に接続され、

前記nチャネル型の薄膜トランジスタのソースまたはドレインの一方は、第2の電源線と電気的に接続され、

前記nチャネル型の薄膜トランジスタのソースまたはドレインの他方は、前記第2のスイッチの他方の電極と電気的に接続され、

前記第2の容量素子の他方の電極は、前記第2のスイッチの一方の電極と電気的に接続され、

前記nチャネル型の薄膜トランジスタのソースまたはドレインの他方、前記pチャネル型の薄膜トランジスタのソースまたはドレインの他方、及び前記第2のスイッチの他方の電極の電位によって、前記第3のスイッチが制御され、

前記第3のスイッチの一方の電極は、前記電流源と電気的に接続され、

前記第3のスイッチの他方の電極は、前記発光素子と電気的に接続され

前記第1の電源線の電位は、前記第2の電源線の電位に比較して高く、

前記第2の配線として、前記第1の電源線または前記第2の電源線が用いられていることを特徴とする表示装置。 - 請求項1に記載の表示装置を用いた電子機器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005144874A JP4879515B2 (ja) | 2004-05-21 | 2005-05-18 | 表示装置及び電子機器 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004152628 | 2004-05-21 | ||

| JP2004152628 | 2004-05-21 | ||

| JP2005144874A JP4879515B2 (ja) | 2004-05-21 | 2005-05-18 | 表示装置及び電子機器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006011401A JP2006011401A (ja) | 2006-01-12 |

| JP2006011401A5 JP2006011401A5 (ja) | 2008-05-08 |

| JP4879515B2 true JP4879515B2 (ja) | 2012-02-22 |

Family

ID=35778688

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005144874A Expired - Fee Related JP4879515B2 (ja) | 2004-05-21 | 2005-05-18 | 表示装置及び電子機器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4879515B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101477689B1 (ko) * | 2008-07-09 | 2014-12-30 | 삼성디스플레이 주식회사 | 표시장치 |

| JP6217512B2 (ja) | 2014-05-01 | 2017-10-25 | コニカミノルタ株式会社 | 光書込み装置及び画像形成装置 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002333870A (ja) * | 2000-10-31 | 2002-11-22 | Matsushita Electric Ind Co Ltd | 液晶表示装置、el表示装置及びその駆動方法、並びに副画素の表示パターン評価方法 |

| JP4982014B2 (ja) * | 2001-06-21 | 2012-07-25 | 株式会社日立製作所 | 画像表示装置 |

| JP2003208124A (ja) * | 2002-01-10 | 2003-07-25 | Sanyo Electric Co Ltd | 表示装置 |

| JP3854161B2 (ja) * | 2002-01-31 | 2006-12-06 | 株式会社日立製作所 | 表示装置 |

| JP4115763B2 (ja) * | 2002-07-10 | 2008-07-09 | パイオニア株式会社 | 表示装置及び表示方法 |

| JP3832415B2 (ja) * | 2002-10-11 | 2006-10-11 | ソニー株式会社 | アクティブマトリクス型表示装置 |

-

2005

- 2005-05-18 JP JP2005144874A patent/JP4879515B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006011401A (ja) | 2006-01-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7565408B2 (ja) | 表示装置 | |

| JP6756807B2 (ja) | 半導体装置 | |

| US8581805B2 (en) | Display device and driving method thereof | |

| JP5562371B2 (ja) | 半導体装置、表示装置、モジュール、表示モジュール及び電子機器 | |

| JP4884701B2 (ja) | 表示装置 | |

| JP4879515B2 (ja) | 表示装置及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080320 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080320 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110531 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110706 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110802 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110905 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111129 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111130 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4879515 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141209 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141209 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |