JP4771925B2 - 集積回路設計装置及び集積回路設計用プログラム - Google Patents

集積回路設計装置及び集積回路設計用プログラム Download PDFInfo

- Publication number

- JP4771925B2 JP4771925B2 JP2006324227A JP2006324227A JP4771925B2 JP 4771925 B2 JP4771925 B2 JP 4771925B2 JP 2006324227 A JP2006324227 A JP 2006324227A JP 2006324227 A JP2006324227 A JP 2006324227A JP 4771925 B2 JP4771925 B2 JP 4771925B2

- Authority

- JP

- Japan

- Prior art keywords

- information

- layout

- integrated circuit

- evaluation

- regularity

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/39—Circuit design at the physical level

- G06F30/398—Design verification or optimisation, e.g. using design rule check [DRC], layout versus schematics [LVS] or finite element methods [FEM]

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/39—Circuit design at the physical level

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Evolutionary Computation (AREA)

- Geometry (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

Description

従来のレイアウト手法は、集積回路設計装置内部で、半導体集積回路の面積や配線長が各々最小になるようにレイアウトを行うようにしている。

これにより、より規則的に並んだレイアウトを得ることによって、良好な回路特性、配線が容易等の良好な配線性を持つレイアウト結果を得るようにしている。

したがって、半導体集積回路設計装置によって自動で生成されたレイアウトでは、良好な回路特性を得ることができず又、良好な配線を容易に行うことが困難であり、レイアウト設計者に受け入れられないことが多いという問題がある。

また、本発明は、コンピュータを用いて前記集積回路設計装置を構築するのに好適な集積回路設計用プログラムを提供することを課題としている。

また、前記規則構造にはアレイ、ロウ、スライス、ルーム、オブジェクトの中の少なくとも1つが含まれて成り、前記評価手段は、トポロジ的な規則構造に基づく規則性の評価を行う場合、前記規則構造の中の少なくとも1つの規則構造に基づいて評価を行うように構成してもよい。

また、本発明によれば、コンピュータを、レイアウトにおける規則構造を抽出して前記レイアウトの規則性の評価を行う評価手段と、記憶手段に記憶された集積回路の設計に必要な設計情報に基づいて集積回路のレイアウトを最適化する最適化手段とを備え、前記最適化手段は、前記評価手段による規則性の評価を考慮して、前記集積回路のレイアウトを最適化するように機能させることを特徴とする集積回路設計用プログラムが提供される。

また、前記規則構造にはアレイ、ロウ、スライス、ルーム、オブジェクトの中の少なくとも1つが含まれて成り、前記評価手段は、トポロジ的な規則構造に基づく規則性の評価を行う場合、前記規則構造の中の少なくとも1つの規則構造に基づいて評価を行うようにコンピュータを機能させるよう前記集積回路設計用プログラムを構成してもよい。

また、外部から明示的な制約を指定せずに、内部的にレイアウトの規則性を考慮することで、最小限の付加的な制約で規則的なレイアウトを得ることが可能になり、結果として、歩留まり、マッチング特性、配線性等の向上が可能になる。

また、本発明に係る集積回路設計用プログラムは、コンピュータを用いて前記集積回路設計装置を構築することが可能になる。

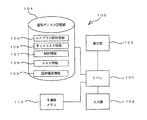

図1において、集積回路設計装置100は、中央処理装置(CPU)101、キーボードやマウス等によって構成された入力部102、液晶表示器等によって構成された表示部103、外部記憶装置を構成する磁気ディスク記憶部104、主記憶装置等を構成する半導体メモリ110を備えている。

また、前記制約情報は回路要素のレイアウトを行う際に必ず満たす必要のある条件を表す情報(制約)であり、前記制約情報には、複数のデバイスやセルによって構成される回路要素を定義した情報(例えば、クラスタ、ペア、シンメトリ)や、各回路要素の位置関係の制約(例えば、複数の回路要素の水平位置関係の制約や垂直位置関係の制約)を表す情報等のレイアウト時に満たすべき情報が含まれている。

また、前記規則構造情報には、規則性を評価するための基準となる、インスタンスの配置構造の種類が記憶されている。本実施の形態では、後述するようなアレイ、ロウ等の規則的な配置構造を定義した情報が含まれている。

前記レイアウト図形情報、ネットリスト情報、制約情報、コスト情報及び規則構造情報は設計情報を構成している。

ここで、CPU101は、レイアウトの位相的表現からレイアウトにおける規則構造を抽出しレイアウトの規則構造をレイアウトの最適化指標として評価する評価手段、及び、レイアウトの最適化を行う最適化手段を構成している。前記最適化手段は、レイアウト最適化を行う際に、制約等の必ず満足すべき条件を満たした上で、位相構造の最適化を行い、これを反映して物理構造(例えば、面積や配線長)の最適化を行う。

また、入力部102は入力手段を構成し、表示部103は表示手段を構成し又、磁気ディスク記憶部104及びメモリ110は記憶手段を構成している。

ここで、レイアウトの規則性とは、個々のインスタンスあるいは複数のインスタンス群が一定の規則でレイアウトされている状態をいう。

例えば、規則性の例として、個々のインスタンスあるいは複数のインスタンス群に対しての、インスタンスのレイアウトの縦及び/又は横方向の整列性(整列性)、インスタンスのレイアウトの回転方向の方向性(方向性)、インスタンスのレイアウトの対称性(X軸対称、Y軸対称、原点対称)(対称性)の3つがある。

本実施の形態では、前記3つの規則性の要素(整列性、方向性、対称性)を、レイアウトトポロジとして下記の規則構造に類型化することによって、レイアウトの規則性の評価を可能にしている。

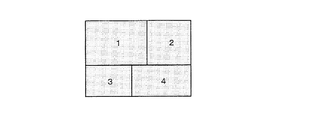

図2に示すように、複数のインスタンスが、マトリクス状にレイアウトされた状態であり、縦及び横が各々同一のピッチ、間隔でレイアウトされている状態である。図2には、9(3×3)個のインスタンス1〜9がアレイ構造にレイアウトされている例を示している。

図3に示すように、複数のインスタンスが、縦又は横が同一ピッチ、同一間隔でレイアウトされている状態である。図3には、複数のインスタンス1〜8が、縦方向が同一ピッチ、同一間隔でレイアウトされており、縦方向3段のロウ構造のレイアウト例を示している。

図4に示すように、任意のインスタンスを直線によって2分割できるようにレイアウトされている状態である。図4には、インスタンス1、2とインスタンス3、4とを横線によって2分割できるように配置されたスライス構造の例を示している。

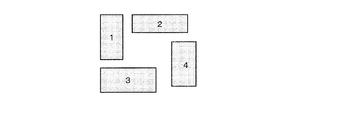

図5に示すように、破線で示すように所定領域を複数の矩形領域(ルーム)に分割し、前記各矩形領域に空きが生じないように、前記各矩形領域に1つのインスタンスを配置した状態であり、スライスを包含する概念である。図5には、所定領域を5つの矩形領域に分割し、各矩形領域内に1つのインスタンス1〜5を配置したルーム構造の例を示している。

図6に示すように、任意のコンパクションを行った後のレイアウト状態であり、各インスタンス1〜4が任意の座標を持つ状態である。

ここで、前記5種類のレイアウトトポロジ(i)〜(v)は、アレイ、ロウ、スライス、ルーム、オブジェクトの順で、規則性の観点からの優先度が低くなる(アレイ>ロウ>スライス>ルーム>オブジェクト)ように設定している。前記優先度に対応する評価値を予め設定しておくことにより、規則性の評価を数値化することができる。

尚、前記規則構造以外にも、図7に示す規則構造「シンメトリ(Symmetry)」のように、複数のインスタンス1〜5が線対称になるように配置した状態も含めるようにしてもよい。

図10は、物理的な構造評価値の1つである局所詰め込み値(局所への詰め込み具合の指標となる値)を説明するための図である。図10において、局所詰め込み値は、局所配置の詰め込み率を向上させるためのコストである。局所詰め込み値は、「ブロック1〜8の面積の総和/ブロック1〜8を囲む最小矩形1001の面積」である。局所詰め込み値は、値が大きいほど空き領域が多いことを示しており、局所詰め込み値が大きいほど、コストが高くなる。

ロウは複数のブロックがマトリクス的に配置された構造であり、水平方向のロウの場合は、各段のブロックの高さは同じであるが、ブロックの幅は異なる。各段でのブロックの幅の最大幅と最小幅の差を、全ての段で加算したものを評価して数値化し(この値を局所均一値という。)、前記局所均一値が小さい程、均一なロウであると判断する。縦方向のロウの場合も、前記同様にして局所均一値を求めて均一性を評価する。

また、図12〜図14は、本発明の実施の形態に係る集積回路設計装置100において、最適化処理の例を示す図である。

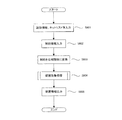

先ず、ユーザ(例えば、半導体集積回路の設計者)が入力部102を操作して設計処理開始の指示を入力すると、CPU101は、磁気ディスク記憶部104に記憶しておいた前記集積回路設計用プログラム及び設計情報をメモリ110に読み込み、前記集積回路設計用プログラムを実行することにより、入力部102からの入力に応じた処理を行うことができる状態になる。

また、CPU101は、制約情報記憶部107から制約情報を読み込んでメモリ110に入力する(ステップS802)。

次にCPU101は、処理ステップS901で得られた解Xに対してトポロジ的な変更やトポロジを保持してのブロック交換を行うことによって、新しい解X’(レイアウトモデル)の作成を行う(ステップS902)。

次にCPU101は、前記解X’に関して、前記トポロジ的な表現からレイアウトの規則性を抽出することにより、トポロジ的な構造評価値を算出する(ステップS903)。

同様に、垂直1列レイアウトをそれぞれ1ブロックに置き換え、そのレイアウトにおいて、連続昇順となる列を抽出したとき、そのレイアウト、垂直列を複数段積み重ねた多段ロウのレイアウトトポロジに対応していると判断できる。

特殊な場合として、積み重ねられた水平1列レイアウトがすべて同じブロック数をもつとき、アレイレイアウトトポロジに対応していると判断できる。同様に、積み重ねられた垂直1列レイアウトがすべて同じブロック数をもつとき、アレイレイアウトトポロジに対応していると判断できる。

先ず、CPU101は、下記のトポロジカル構造評価値及び物理的な構造評価値をコンパクション前(具体的な座標値が確定する前)に算出する。

(1)トポロジ的な構造評価値の算出

(a)アレイトポロジ構造を構成しているブロック数と、各トポロジの行数と列数の比(アスペクト)とから、アスペクトが1に近いアレイの数に比例して大きくなるように算出した値

(c)自己シンメトリ(自分自身に対称)以外の対称トポロジを構成しているブロック数に比例するように算出した値

((a)+(b)+(c))の値をトポロジ的な構造評価値とする。

(d)局所詰め込み値の算出

前記(1)のブロックに対して、「各ブロックの面積の総和/各ブロックを囲む最小矩形の面積」を局所詰め込み値として求める。これにより詰め込み具合を算出する(値が大きいほど空き領域が多く、コストが高い)。

各段でのブロックの幅の最大幅と最小幅の差を、全ての段で加算したものを評価して数値化することにより、局所均一値を算出する。

ここでは、前記(1)の複数列に対して、各列のブロックの最大、最小幅の差を総計したものが大きいほど、均一でなく、コストが高くなる。

((d)+(e))の値を物理的な構造評価値とする。

次に、CPU101は、処理ステップS902で作成した解X’が制約を満たすか否かを判断し、解Xが制約を満足する場合には解X’と解Xとのコスト比較を行い、より適した方の解を選択する(ステップS906)。

(A)制約

制約は必ず守るべき条件であり、例えばブロックの隣接制約や、具体的なブロック名を指定したシンメトリ制約、あるいは寄生成分(抵抗、容量)などの影響を考慮した制約などがあり、これらは、具体的な座標値を求めるコンパクションの前後で、制約をチェックし、許容解か否かを判断する。

このコストは、処理ステップS903、S904で算出された構造評価値に基づくコストであり、これらは前記(A)の制約で明示的に指定されたブロック以外にも適応される。即ち、このコストは、外部から制約として指定されていない場合でも、自動的に算出される。

(C)コンパクション後の面積、配線長などのコスト

このコストは、一般的なブロックの実座標値が確定した後に評価されるコストであり、面積最小、配線長(総配線、特定配線を含む)最小を目標とする。

即ち、CPU101は、処理ステップS906において、新たな解X’が制約を満たし、且つ、新たな解X’と解Xのコスト比較を行うことによって解X’のコストが解Xのコストよりも小さいか否かを判断する。

前記配置改善の終了条件としては、例えば、最適化手法がSA(Simulated Anneiling)法の場合には温度が所定温度(例えば、100度から0度まで)、遺伝的アルゴリズム(GA)法の場合には世代数等である。

CPU101は、処理ステップS908において、配置改善の終了条件が満たされていないと判断した場合には処理ステップS902に戻って前記処理を繰り返し、配置改善の終了条件が満たされたと判断した場合には、得られた集積回路のレイアウトのデータを磁気ディスク記憶部104に記憶し、表示部103あるいは外部の装置に出力する(ステップS805)。

前記の如くして行った最適化処理の一例を図12〜図14に沿って説明する。

図14は、図13の状態から変化して、トポロジのコストが劣化しないという制約の下で、物理的なコストを最適化した状態を示している。ここで、アレイ数は1、総配線長は2が得られており、アレイ数の最大化及び物理的総配線長のコストの最小化が実現されている。

即ち、CPU101は、磁気ディスク記憶部104の規則構造情報記憶部107に記憶された規則構造情報を参照すると共にレイアウト図形情報、ネットリスト情報及び制約情報を用いてレイアウトにおける規則構造を抽出し、前記規則構造を評価し、前記評価を考慮して、レイアウト図形情報、ネットリスト情報等の設計情報を用いて最適化した集積回路のレイアウトを得るようにしている。

また、レイアウト最適化処理において、新たに規則性の指標を組み込みことで、明示的なアライメントなどの制約がなくとも、レイアウト結果が自動的に、アレイ、ロウ、スライス等の規則構造を考慮するようになり、これに従来の面積や配線長のコスト、及び、ペア性、シンメトリ性などの付加的な制約を合わせて自動レイアウトを行うことで、よりアナログ設計者の望む、規則的な、いわばきれいなレイアウトを得ることが可能になる。

また、本発明の実施の形態に係る集積回路設計用プログラムをコンピュータに実行させることにより、コンピュータを用いて前記集積回路設計装置を構築することが可能になる。

また、物理的な規則構造の評価を行って評価値を算出する場合、局所詰め込み値及び局所均一値の中の少なくとも1つを評価して評価値を算出するように構成してもよい。

101・・・評価手段及びレイアウトの最適化を行う最適化手段を構成するCPU

102・・・入力手段を構成する入力部

103・・・表示手段を構成する表示部

104・・・記憶手段を構成する磁気ディスク記憶部

105・・・レイアウト図形情報記憶手段を構成するレイアウト図形情報記憶部

106・・・ネットリスト情報記憶手段を構成するネットリスト情報記憶部

107・・・制約情報記憶手段を構成する制約情報記憶部

108・・・コスト情報記憶手段を構成するコスト情報記憶部

109・・・規則構造情報記憶手段を構成する規則構造情報記憶部

110・・・記憶手段を構成する半導体メモリ

1001・・・最小矩形

Claims (8)

- 集積回路の設計に必要な設計情報を記憶する記憶手段と、

レイアウトにおける規則構造を抽出して前記レイアウトの規則性の評価を行う評価手段と、

前記設計情報に基づいて集積回路のレイアウトを最適化する最適化手段とを備え、

前記設計情報には、前記規則構造を表す規則構造情報、レイアウト図形情報、ネットリスト情報、制約情報及びコスト情報が含まれ、

前記評価手段は、前記規則構造情報を参照すると共に前記レイアウト図形情報、ネットリスト情報及び制約情報を用いて、前記規則構造を抽出して前記規則性の評価を行い、

前記最適化手段は、前記制約情報に含まれる制約を満足させると共に前記評価手段による規則性の評価を考慮して、前記レイアウト図形情報、ネットリスト情報及びコスト情報を用いて、前記集積回路のレイアウトを最適化することを特徴とする集積回路設計装置。 - 前記評価手段は、トポロジ的な規則構造及び物理的な規則構造に基づいて前記規則性の評価を行うことを特徴とする請求項1記載の集積回路設計装置。

- 前記規則構造にはアレイ、ロウ、スライスの中の少なくとも1つが含まれて成り、

前記評価手段は、トポロジ的な規則構造に基づく規則性の評価を行う場合、前記規則構造の中の少なくとも1つの規則構造に基づいて評価を行うことを特徴とする請求項2記載の集積回路設計装置。 - 前記評価手段は、物理的な規則構造に基づく規則性の評価を行う場合、局所詰め込み値及び局所均一値に基づいて評価を行うことを特徴とする請求項2記載の集積回路設計装置。

- コンピュータを、

レイアウトにおける規則構造を抽出して前記レイアウトの規則性の評価を行う評価手段と、

記憶手段に記憶された集積回路の設計に必要な設計情報に基づいて集積回路のレイアウトを最適化する最適化手段とを備え、

前記設計情報には、前記規則構造を表す規則構造情報、レイアウト図形情報、ネットリスト情報、制約情報及びコスト情報が含まれ、

前記評価手段が、前記規則構造情報を参照すると共に前記レイアウト図形情報、ネットリスト情報及び制約情報を用いて、前記規則構造を抽出して前記規則性の評価を行い、

前記最適化手段が、前記制約情報に含まれる制約を満足させると共に前記評価手段による規則性の評価を考慮して、前記レイアウト図形情報、ネットリスト情報及びコスト情報を用いて、前記集積回路のレイアウトを最適化するように機能させることを特徴とする集積回路設計用プログラム。 - 前記評価手段がトポロジ的な規則構造及び物理的な規則構造に基づいて前記規則性の評価を行うようにコンピュータを機能させることを特徴とする請求項5記載の集積回路設計用プログラム。

- 前記規則構造にはアレイ、ロウ、スライスの中の少なくとも1つが含まれて成り、

前記評価手段がトポロジ的な規則構造に基づく規則性の評価を行う場合、前記規則構造の中の少なくとも1つの規則構造に基づいて評価を行うようにコンピュータを機能させることを特徴とする請求項6記載の集積回路設計用プログラム。 - 前記評価手段が物理的な規則構造に基づく規則性の評価を行う場合、局所詰め込み値及び局所均一値に基づいて評価を行うようにコンピュータを機能させることを特徴とする請求項6記載の集積回路設計用プログラム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006324227A JP4771925B2 (ja) | 2006-11-30 | 2006-11-30 | 集積回路設計装置及び集積回路設計用プログラム |

| US11/703,700 US7698663B2 (en) | 2006-11-30 | 2007-02-08 | Apparatus, method and program for designing integrated circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006324227A JP4771925B2 (ja) | 2006-11-30 | 2006-11-30 | 集積回路設計装置及び集積回路設計用プログラム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008140011A JP2008140011A (ja) | 2008-06-19 |

| JP4771925B2 true JP4771925B2 (ja) | 2011-09-14 |

Family

ID=39477355

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006324227A Expired - Fee Related JP4771925B2 (ja) | 2006-11-30 | 2006-11-30 | 集積回路設計装置及び集積回路設計用プログラム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7698663B2 (ja) |

| JP (1) | JP4771925B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW200837588A (en) * | 2007-03-07 | 2008-09-16 | Advanced Analog Technology Inc | Aid design system for analog integrated circuit and the method thereof |

| US9003351B1 (en) | 2014-01-08 | 2015-04-07 | Freescale Semiconductor, Inc. | System and method for reducing power consumption of integrated circuit |

| CN108920746B (zh) * | 2018-05-17 | 2022-07-26 | 佛山市顺德区中山大学研究院 | 一种集成电路布局规划的预压缩方法及系统 |

| US11824009B2 (en) | 2018-12-10 | 2023-11-21 | Preferred Networks, Inc. | Semiconductor device and data transferring method for semiconductor device |

| US20250291990A1 (en) * | 2024-03-13 | 2025-09-18 | Novatek Microelectronics Corp. | Method for learning-based auto placement of analog circuit |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3556260B2 (ja) * | 1993-02-12 | 2004-08-18 | 株式会社東芝 | Lsiの素子配置方法及び装置 |

| JPH0773217A (ja) * | 1993-09-03 | 1995-03-17 | Mitsubishi Electric Corp | 素子自動配置装置 |

| US6557159B1 (en) * | 2000-05-24 | 2003-04-29 | International Business Machines Corporation | Method for preserving regularity during logic synthesis |

| US6598215B2 (en) * | 2001-03-30 | 2003-07-22 | Intel Corporation | Datapath design methodology and routing apparatus |

| JP4597441B2 (ja) * | 2001-09-14 | 2010-12-15 | ルネサスエレクトロニクス株式会社 | アナログセルレイアウト設計装置 |

| JP2004234450A (ja) | 2003-01-31 | 2004-08-19 | Jedat Inc | 半導体集積回路のレイアウト変更処理装置 |

| JP2005062943A (ja) | 2003-08-12 | 2005-03-10 | Jedat Innovation:Kk | 集積回路設計装置 |

| JP2005267291A (ja) * | 2004-03-19 | 2005-09-29 | Shigehisa Nakatake | 集積回路設計装置 |

| JP2006309748A (ja) * | 2005-03-30 | 2006-11-09 | Tokyo Univ Of Agriculture & Technology | 矩形要素配置方法及び矩形要素配置装置並びに矩形要素配置用プログラム |

-

2006

- 2006-11-30 JP JP2006324227A patent/JP4771925B2/ja not_active Expired - Fee Related

-

2007

- 2007-02-08 US US11/703,700 patent/US7698663B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008140011A (ja) | 2008-06-19 |

| US7698663B2 (en) | 2010-04-13 |

| US20080134105A1 (en) | 2008-06-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US12242788B2 (en) | Method and system for generating layout design of integrated circuit | |

| US11544437B2 (en) | System for designing integrated circuit layout and method of making the integrated circuit layout | |

| CN115315703A (zh) | 使用神经网络生成集成电路布局 | |

| US8631374B2 (en) | Cell architecture for increasing transistor size | |

| US8423941B2 (en) | Structural migration of integrated circuit layout | |

| US20100025859A1 (en) | Method for designing semiconductor device, program therefor, and semiconductor device | |

| US8924913B1 (en) | Schematic display of connectivity in an integrated circuit design | |

| CN106997406A (zh) | 布局修正方法及系统 | |

| CN119514474B (zh) | 双面板与多层板印制电路的自动化设计排布与路径规划方法及系统 | |

| TW201923823A (zh) | 積體電路及其設計的方法及其設計系統 | |

| CN120106007B (zh) | 一种基于聚类的时钟树综合方法及系统 | |

| US7698663B2 (en) | Apparatus, method and program for designing integrated circuit | |

| US9275186B2 (en) | Optimization for circuit migration | |

| CN109074412B (zh) | 使用自动焊接和自动克隆的电路中的连接的交互式布线 | |

| Sadeghi et al. | Automatic and simultaneous floorplanning and placement in field-programmable gate arrays with dynamic partial reconfiguration based on genetic algorithm | |

| CN118709635A (zh) | 优化图形密度分布的版图生成方法、装置、介质、程序产品及终端 | |

| US8555232B2 (en) | Wire routing using virtual landing pads | |

| TWI898088B (zh) | 多位元胞元及其形成方法 | |

| Wang et al. | Effective regularity extraction and placement techniques for datapath‐intensive circuits | |

| US20040163067A1 (en) | Method and apparatus for layout of high speed digital logic for datapath portions of microprocessor integrated circuits | |

| US11836000B1 (en) | Automatic global clock tree synthesis | |

| JP4946703B2 (ja) | シミュレーション方法及びプログラム | |

| CN117289937B (zh) | 一种低代码平台中实现布局容器内外数据联动方法及系统 | |

| JP2013084211A (ja) | 半導体装置の自動配置配線プログラム、自動配置配線装置及び自動配置配線方法 | |

| CN120805827B (zh) | 一种计算符合条件的器件数量的方法及系统 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091126 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20091126 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110208 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110329 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110614 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110621 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140701 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4771925 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313115 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |