JP4626148B2 - 復号または署名作成におけるべき乗剰余算の計算方法 - Google Patents

復号または署名作成におけるべき乗剰余算の計算方法 Download PDFInfo

- Publication number

- JP4626148B2 JP4626148B2 JP2004001602A JP2004001602A JP4626148B2 JP 4626148 B2 JP4626148 B2 JP 4626148B2 JP 2004001602 A JP2004001602 A JP 2004001602A JP 2004001602 A JP2004001602 A JP 2004001602A JP 4626148 B2 JP4626148 B2 JP 4626148B2

- Authority

- JP

- Japan

- Prior art keywords

- processing unit

- mod

- randomized

- unit

- public key

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/60—Methods or arrangements for performing computations using a digital non-denominational number representation, i.e. number representation without radix; Computing devices using combinations of denominational and non-denominational quantity representations, e.g. using difunction pulse trains, STEELE computers, phase computers

- G06F7/72—Methods or arrangements for performing computations using a digital non-denominational number representation, i.e. number representation without radix; Computing devices using combinations of denominational and non-denominational quantity representations, e.g. using difunction pulse trains, STEELE computers, phase computers using residue arithmetic

- G06F7/723—Modular exponentiation

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2207/00—Indexing scheme relating to methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F2207/72—Indexing scheme relating to groups G06F7/72 - G06F7/729

- G06F2207/7219—Countermeasures against side channel or fault attacks

- G06F2207/7223—Randomisation as countermeasure against side channel attacks

- G06F2207/7233—Masking, e.g. (A**e)+r mod n

Description

n=pq (式1)

ed=1 mod Phi(n) (式2)

という関係が成り立っている。ただし、Phi(n)はオイラー関数であり、整数nと互いに素な正整数の個数を表す。n=pqの場合は、

Phi(n) = (p-1)(q-1) (式3)

となる。式1、式2より、任意の整数zに対して、

zed = z mod n (式4)

という関係が成り立つ。この性質を利用することにより、暗号化・復号化等を達成することができる。すなわち、暗号化や署名の検証においては、

xe mod n (式5)

が計算され、復号化や署名の作成においては、

yd mod n (式6)

が計算される。ここでx,yは、入力データを表す整数である。この計算はべき乗剰余算と呼ばれる。

e=65537 (=216+1) (式7)

である。

p mod 4 = q mod 4 = 3となる素因数p,qを含み、上記ランダム化された平文uに変換するステップにおける上記秘密指数dより導出された値として

(p-3)/4および(q-3)/4を用い、上記ランダム化された平文uに変換するステップは、ランダム化された暗号文tの

(p-3)/4乗を計算するステップと、ランダム化された暗号文tの

(q-3)/4乗を計算するステップと、を含むように構成してもよい。

べき乗剰余c=me mod nを計算し、暗号化されたデータcを得る。コンピュータA101は暗号化処理部112で暗号化された1つ以上の部分データから暗号化された出力データを組み立てる。コンピュータA101は暗号化されたデータ141を入出力インタフェース110より出力し、ネットワーク142を介してコンピュータB121へ転送する。

べき乗剰余m'=cd mod nを計算し、暗号化される前の部分データmに相当するm'を得る。コンピュータB121は、復号化処理部132で復号化された部分データから平文データを組み立て、入出力インタフェース130を介して、ディスプレイ128などから出力する。

re-1 mod nを計算し、sに格納する(302)。モジュラー乗算部201は、

src mod nを計算し、tに格納する(303)。この計算は、モジュラー乗算部201がs, rからsr mod nを計算し、その後

(sr) c mod nを計算することにより達成できる。汎用べき乗剰余計算部203は、

td-1 modを計算し、uに格納する(304)。モジュラー乗算部201は、

us mod nを計算し、vに格納する(305)。モジュラー乗算部201は、

vc mod nを計算し、m'に格納する。復号化処理部132は、m'を暗号化される前の部分データである平文mとして出力する。平分mから平分データが組み立てられる。

td mod nを計算する。ここでp,qはnを割りきる素数である。

d mod p-1, d mod q-1 を計算し、dp, dqにそれぞれ格納する(501)。モジュラー剰余計算部403は

t mod p, t mod q を計算し、tp, tqにそれぞれ格納する(502)。べき乗剰余計算部404は、tp dp mod p, tq dq mod qを計算し、それぞれmp, mqに格納する(503)。モジュラー乗算部401およびモジュラー加減算部402は、

(mq-mp)pInv mod qを計算し、hに格納する(504)。この計算は、モジュラー加減算部402が

mq-mp mod qを計算し、モジュラー乗算部401が、その結果にpInvを乗ずる

(すなわち (mq-mp)pInv mod q)ことにより達成できる。加減乗算部405は、mp+phを計算し、mpqに格納する(505)。この計算は、加減乗算部405がphを計算し、その結果にmpを加える(すなわち mp+(ph))ことにより達成できる。ただし、pInvは、

pInv = p-1 mod q (式8)

をみたす整数である。pInvは定数406としてCRT計算部203に格納されている。CRT計算部203は、mpqを

td mod nとして出力する(506)。

m' = vc = usc = td-1sc

= (src)d-1sc = (rec)d-1re-1c

= cdred-e+e-1 = cd mod n (式9)

ここで、e,d の定義より、red-1 = 1が成り立つ。cはmを暗号化したものであるので、

cd = m mod n (式10)

が成り立つ。したがって、m'=mとなる。

n = pqr (式11)

ed = mod Phi(n) (式12)

という関係が成り立っている。ここでは、大きな素数を3つとしたが、4つやそれ以上でもよい。式12のnの場合、

Phi(n) = (p-1)(q-1)(r-1) (式13)

となる。multi-prime RSAにおいても、式4が成立し、そのため、暗号化や署名の検証においては式5が計算され、復号化や署名の作成においては式6が計算される。従って復号化処理を行なう場合、第1の計算方法を用いることにより、サイドチャネル攻撃に耐性を有し、さらに、逆元演算を用いないため、高速計算可能かつ小メモリとなる。

d mod p-1, d mod q-1, d mod r-1 を計算し、dp, dq, dr にそれぞれ格納する(601)。モジュラー剰余計算部403は

t mod p, t mod q, t mod r を計算し、tp, tq, trにそれぞれ格納する(602)。べき乗剰余計算部404は、

tp dp mod p, tq dq mod q, tr dr mod r を計算し、それぞれ mp, mq, mr に格納する(603)。モジュラー乗算部401およびモジュラー加減算部402は、

(mq-mp)pInv mod q を計算し、hに格納する(604)。この計算は、モジュラー加減算部402が

mq-mp mod q を計算し、モジュラー乗算部401が、その結果にpInvを乗ずる

(すなわち (mq-mp)pInv mod q)ことにより達成できる。ただし、pInvは、式*をみたす整数である。加減乗算部405は、mp+phを計算し、mpqに格納する(605)。この計算は、加減乗算部405がphを計算し、その結果にmpを加える(すなわち mp+(ph))ことにより達成できる。モジュラー乗算部401およびモジュラー加減算部402は、

(mr-mpq)pqInv mod r を計算し、hに格納する(606)。この計算は、モジュラー加減算部402が

mr-mpq mod r を計算し、モジュラー乗算部401が、その結果にpqInvを乗ずる

(すなわち (mr-mpq)pqInv mod r)ことにより達成できる。ただし、pqInvは、

pqInv = (pq)-1 mod r (式14)

をみたす整数である。pqInvは定数406として、CRT計算部203に格納されている。加減乗算部405は、mpq+pqhを計算し、mpqr に格納する(607)。この計算は、加減乗算部405がpqを計算し、その結果にhを乗じ、さらにその結果にmpqを加える(すなわち mpq+((pq)h))ことにより達成できる。CRT計算部203は、mpqr を

td mod n として出力する(608)。

n = p2q (式15)

ed = mod Phi(n) (式16)

という関係が成り立っている。ここでは、べき指数を2としたが、3やそれ以上でもよい。式16のnの場合、

Phi(n) = p(p-1)(q-1) (式17)

となる。multi-exponent RSAにおいても、式4が成立し、そのため、暗号化や署名の検証においては式5が計算され、復号化や署名の作成においては式6が計算される。従って復号化処理を行なう場合、第1の計算方法を用いることにより、サイドチャネル攻撃に耐性を有し、さらに、逆元演算を用いないため、高速計算可能かつ小メモリとなる。

d mod p-1, d mod q-1 を計算し、dp, dq にそれぞれ格納する(701)。モジュラー剰余計算部403は

t mod p, t mod q を計算し、tp, tq にそれぞれ格納する(702)。べき乗剰余計算部404は、

tp dp-1 mod pを計算し、kに格納する(703)。モジュラー剰余計算部403は、

tp k mod p を計算し、mp に格納する。べき乗剰余計算部404は、

tq dq mod q を計算し、mq に格納する(704)。べき乗剰余計算部404、モジュラー加減算部402、およびモジュラー剰余計算部403は、

c - mp e mod p2 を計算し、gに格納する。モジュラー乗算部401は、

g k eInv mod p2 を計算し、bに格納する。加減乗算部405は、mq +b を計算し、mp2 に格納する(705)。これらの計算は、べき乗剰余計算部404が

mp e mod p2 を計算し、モジュラー剰余計算部403が

c mod p2 を計算し、モジュラー加減算部402がそれらの差分をとる(すなわち

(c mod p2) (mp e) mod p2)ことによりgが計算できる。モジュラー乗算部401がg k mod p2 を計算し、その結果にeInv を乗ずる

(すなわち (gk)eInv mod p2)ことによりbが計算できる。その後、加減乗算部405が mq +b を計算することにより、達成できる。ただし、eInvは、

eInv = (e)-1 mod p (式18)

をみたす整数である。eInvは定数406としてCRT計算部203に格納されている。モジュラー乗算部401およびモジュラー加減算部402は、

(mq-mp2)p2Inv mod q を計算し、hに格納する(706)。この計算は、モジュラー加減算部402が

mq-mp2 mod q を計算し、モジュラー乗算部401が、その結果にp2Invを乗ずる

(すなわち (mq-mp2)p2Inv mod q)ことにより達成できる。ただし、p2Invは、

p2Inv = (p2)-1 mod r (式19)

をみたす整数である。p2Invは定数406としてCRT計算部203に格納されている。加減乗算部405は、mp2+p2hを計算し、mp2qに格納する(707)。この計算は、加減乗算部405が(p2)hを計算し、その結果にmp2を加える(すなわち mp+((p2)h))ことにより達成できる。CRT計算部203は、mp2q を

td mod n として出力する(708)。

e=2 (式20)

である。また素数p,qは、

p mod 4 = q mod 4 = 3 (式21)

をみたすように選ばれる。これらの数値の間には、

n = pq (式22)

という関係が成り立っている。Rabin暗号の場合、暗号化や署名の検証においては、xの平方

y = x2 mod n (式23)

を計算し、復号化や署名の作成においては、式23をみたすxを計算する。そのため、Rabin暗号では、式23をみたす整数が4つ存在し、そのうち適切なものを選択することとなる。

r2 mod nを計算し、sに格納する(902)。モジュラー乗算部801は、

s2c mod nを計算し、tに格納する(903)。この計算は、モジュラー乗算部801がsから

s2 mod nを計算し、その後

(s2) c mod nを計算することにより達成できる。汎用べき乗剰余計算部803は、

t(p-3)/4 mod p, t(q-3)/4 mod q を計算し、それぞれup, uq格納する(904)。モジュラー乗算部801およびモジュラー加減算部805は、

(uq-up)pInv mod q を計算し、h1に格納する。加減乗算部806は、

up+ph1を計算し、w1に格納する(905)。これらの計算は、モジュラー加減算部805が

uq-up mod q を計算し、モジュラー乗算部801が、その結果にpInvを乗ずる

(すなわち (uq-up)pInv mod q)ことによりh1が計算できる。その後、加減乗算部806がph1を計算し、その結果にupを加える

(すなわち up+(ph1))ことにより、達成できる。ただし、pInvは、式8をみたす整数である。モジュラー乗算部801およびモジュラー加減算部805は、

(uq+up)pInv mod q を計算し、h2に格納する。加減乗算部806は、

-up+ph2を計算し、w2に格納する(906)。これらの計算は、モジュラー加減算部805が

uq+up mod q を計算し、モジュラー乗算部801が、その結果にpInvを乗ずる

(すなわち (uq+up)pInv mod q)ことによりh2が計算できる。その後、加減乗算部806がph2を計算し、その結果からupを減ずる(すなわち -up+(ph2))ことにより、達成できる。加減乗算部806は、

n-w1, m-w2 を計算し、それぞれw3, w4 に格納する(907)。モジュラー乗算部801は、

w1 cs mod n, w2 cs mod n, w3 cs mod n, w4 cs mod nを計算し、それぞれm1, m2, m3, m4 に格納する(908)。これらの計算は、モジュラー乗算部801が cs mod n を計算し、その結果にそれぞれw1, w2, w3, w4 を乗ずることにより達成できる。復号化処理部132は、m1, m2, m3, m4 を平文mの候補として出力する(909)。

m1 2 = m2 2 = m3 2 = m4 2 = c mod n (式24)

をみたす。この理由は次の通りである。まず、upに関して次の式が成立する。

= (s2 c)(p-3)/2 = sp-3 mp-3 mod p (式25)

ここで、pは素数であるので、任意の整数zに対して、

zp = z mod p (式26)

が成り立つことに注意すると、

up 2 = s-2 m-2 mod p (式27)

が成り立つ。同様に、

uq 2 = s-2 m-2 mod q (式28)

も成り立つ。他方、w1に関して次の式が成立する。

w1 2 = (up +p(uq-up)pInv)2 mod q (式30)

pInvは式*をみたすので、

w1 2 = uq 2 mod q (式31)

が成り立つ。式22、式27、式28、式29、式31を考慮すると、

m1 2 = w1 2 c2 s2 mod n

= c mod n (式32)

が成り立つ。m2, m3, m4に対しても、同様にして示すことができる。

n = p2q (式33)

という関係が成り立っている。HIME(R)の場合、暗号化や署名の検証においては、xの平方

y = x2 mod n (式34)

を計算し、復号化や署名の作成においては、式34をみたすxを計算する。そのため、HIME(R)では、式34をみたす整数が4つ存在し、そのうち適切なものを選択することとなる。

r2 mod nを計算し、sに格納する(1002)。モジュラー乗算部801は、

s2c mod nを計算し、tに格納する(1003)。この計算は、モジュラー乗算部801がsから

s2 mod nを計算し、その後

(s2) c mod nを計算することにより達成できる。汎用べき乗剰余計算部803は、

t(p-3)/4 mod p, t(q-3)/4 mod q を計算し、それぞれup, uq格納する(1004)。モジュラー乗算部801は、

up t mod p を計算し、kに格納する(1005)。モジュラー乗算部801およびモジュラー加減算部805は、

(uq-up)pInv mod q を計算し、h1に格納する。加減乗算部806は、

up+ph1を計算し、upq,1に格納する(1006)。これらの計算は、モジュラー加減算部805がuq-up mod q を計算し、モジュラー乗算部801が、その結果にpInvを乗ずる

(すなわち (uq-up)pInv mod q)ことによりh1が計算できる。その後、加減乗算部806がph1を計算し、その結果にupを加える

(すなわち up+(ph1))ことにより、達成できる。ただし、pInvは、式8をみたす整数である。モジュラー乗算部801およびモジュラー加減算部805は、

t upq,1 2 mod n を計算し、g1に格納する。モジュラー乗算部801は、

g1 k (2Inv) mod n を計算し、b1に格納する。モジュラー加減乗算部805は、

upq,1+b1を計算し、u1に格納する(1007)。これらの計算は、モジュラー乗算部801が

upq,1 2 mod n を計算し、モジュラー加減算部805が、tからその結果を減ずる

(すなわち t (upq,1 2) mod n)ことにより、g1が計算できる。その後、モジュラー乗算部801が、

k (2Inv) mod n を計算し、その結果にg1を乗ずる

(すなわち g1 (k (2Inv)) mod n)ことにより、b1が計算できる。その後、加減乗算部806が、

upq,1 +b1 を計算することにより、達成できる。ただし、2Invは、

2Inv = 2-1 mod p (式35)

をみたす整数である。モジュラー乗算部801およびモジュラー加減算部805は、

(uq+up)pInv mod q を計算し、h2に格納する。加減乗算部806は、

p-up+ph2を計算し、upq,2に格納する(1008)。これらの計算は、モジュラー加減算部805が

uq+up mod q を計算し、モジュラー乗算部801が、その結果にpInvを乗ずる

(すなわち (uq+up)pInv mod q)ことによりh2が計算できる。その後、加減乗算部806がph2を計算し、その結果にpを加え、upを減ずる

(すなわち p-up+(ph2))ことにより、達成できる。

t upq,2 2 mod n を計算し、g2に格納する。モジュラー乗算部801は、

g2 k (2Inv) mod n を計算し、b2に格納する。モジュラー加減乗算部805は、

upq,2+b2を計算し、u2に格納する(1009)。これらの計算は、モジュラー乗算部801が

upq,2 2 mod n を計算し、モジュラー加減算部805が、tからその結果を減ずる

(すなわち t (upq,2 2) mod n)ことにより、g2が計算できる。その後、モジュラー乗算部801が、

k (2Inv) mod n を計算し、その結果にg2を乗ずる

(すなわち g2 (k (2Inv)) mod n)ことにより、b2が計算できる。その後、加減乗算部806が、

upq,2 +b2 を計算することにより、達成できる。ただし、2Invは、式35をみたす整数である。加減乗算部806は、

n-u1, m-u2 を計算し、それぞれu3, u4 に格納する(1010)。モジュラー乗算部801は、

u1 cs mod n, u2 cs mod n, u3 cs mod n, u4 cs mod nを計算し、それぞれm1, m2, m3, m4 に格納する(1011)。これらの計算は、モジュラー乗算部801が cs mod n を計算し、その結果にそれぞれu1, u2, u3, u4 を乗ずることにより達成できる。復号化処理部132は、m1, m2, m3, m4 を平文mの候補として出力する(1012)。

m1 2 = m2 2 = m3 2 = m4 2 = c mod n (式36)

をみたす。この理由は次の通りである。まず、upに関して次の式が成立する。

= (s2 c)(p-3)/2 = sp-3 mp-3 mod p (式37)

ここで、pは素数であるので、任意の整数zに対して、

zp = z mod p (式38)

が成り立つことに注意すると、

up 2 = s-2 m-2 mod p (式39)

が成り立つ。同様に、

uq 2 = s-2 m-2 mod q (式40)

も成り立つ。式39、式40を用いると、

upq,1 2 = s-2 m-2 mod p (式41)

upq,1 2 = s-2 m-2 mod q (式42)

を示すことができ、したがって、

upq,1 2 = s-2 m-2 mod pq (式43)

が成り立つ。u = (sm)-1 mod n, u = upq,1 + b と表すと、

t = u2 = upq,1 2 + 2upq,1 b mod n (式44)

となる。そのため、

b = (t upq,1 2)((2 upq,1)-1 mod p) mod n (式45)

となる。

であることに注意すれば、b = b1 が成り立つ。したがって、

m1 = (sm)-1 cs = m mod n (式47)

となる。m2, m3, m4 についても同様に示すことができる。

m = cd mod n (式48)

を計算し、mをデータcに対する署名として出力すればよい。

また、上記各実施形態におけるデータ処理部、CRT計算部は、専用のハードウェアを用いて行なってもよい。モジュラー乗算部、モジュラー加減算部、乱数生成部、汎用べき乗剰余計算部、モジュラー剰余計算部、加減乗算部をコプロセッサまたはそれ以外の専用ハードウェアで実現してもよい。

Claims (7)

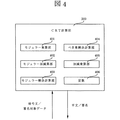

- 公開鍵暗号において,秘密指数dと, 公開鍵nと, 暗号文cとから,平文mを復号する,公開鍵暗号における復号装置であって,

前記暗号文cをランダム化された暗号文tに変換する処理部と,

ランダム化された暗号文tをランダム化された平文uに変換する処理部と,

ランダム化された平文uを平文mに変換する処理部と,

べき剰余計算部と,を有し,

前記ランダム化された暗号文tに変換する処理部は,

乱数rを生成する処理部と,

前記乱数rと前記乱数rより導出された整数sを用いてランダム化された暗号文tに変換する処理部とを含み,

前記ランダム化された平文uに変換する処理部は,

前記秘密指数dより導出された値を用いてランダム化された平文uを計算する処理部を含み,

前記平文mに変換する処理部は,

ランダム化された平文uに前記整数sを乗ずる処理部を含む

ことを特徴とする公開鍵暗号における復号装置。 - 請求項1記載の公開鍵暗号における復号装置であって,さらに,

モジュラー乗算部を備え,

前記乱数rより導出された前記整数sとして,前記べき剰余計算部により計算されるre-1を用い,

前記ランダム化された暗号文tに変換する処理部は,前記モジュラー乗算部を用いて,srを前記暗号文cに乗ずる処理部を含む

ことを特徴とする公開鍵暗号における復号装置。 - 請求項1または2に記載の公開鍵暗号における復号装置であって,さらに,

前記ランダム化された平文uを計算する処理部は,

前記べき剰余計算部を用いて,前記秘密指数dより導出された値としてd-1を用い,前記ランダム化された暗号文tのd-1乗を計算する処理部を含む

ことを特徴とする公開鍵暗号における復号装置。 - 請求項1記載の公開鍵暗号における復号装置であって,さらに,

モジュラー乗算部を備え,

前記暗号文tに変換する処理部は,

前記モジュラー乗算部を用いて,前記乱数rより導出された値としてr2を用い,r2を前記暗号文cに乗ずる処理部を含む

ことを特徴とする公開鍵暗号における復号装置。 - 請求項1記載の公開鍵暗号における復号装置であって,さらに,

前記公開鍵nは,p mod 4 = q mod 4 = 3となる素因数p,qを含み,

前記ランダム化された平文uを計算する処理部は,

前記べき剰余計算部を用いて前記秘密指数dから(p-3)/4および(q-3)/4を導出する処理部と,

ランダム化された暗号文tの(p-3)/4乗を計算する処理部と,

ランダム化された暗号文tの(q-3)/4乗を計算する処理部と,を含む

ことを特徴とする公開鍵暗号における復号装置。 - 請求項4に記載の公開鍵暗号における復号装置であって,さらに,

前記平文mに変換する処理部における前記整数sとして前記r2を用いる

ことを特徴とする公開鍵暗号における復号装置。 - 公開鍵暗号を用いた電子署名において,秘密指数dと, 公開鍵nと, データcとから,署名データmを生成する,公開鍵暗号を用いた署名作成装置であって,

前記データcをランダム化されたデータtに変換する処理部と,

ランダム化されたデータtをランダム化された署名uに変換する処理部と,

ランダム化された署名uを署名mに変換する処理部と,を有し,

前記ランダム化されたデータtに変換する処理部は,

乱数rを生成する処理部と,

前記乱数rと前記乱数rより導出された整数sを用いてランダム化されたデータtに変換する処理部とを含み,

前記ランダム化された署名uに変換する処理部は,

前記秘密指数dより導出された値を用いてランダム化された署名uを計算する処理部を含み,

前記署名mに変換する処理部は,

ランダム化された署名uに前記整数sを乗ずる処理部を含む

ことを特徴とする公開鍵暗号を用いた署名作成装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004001602A JP4626148B2 (ja) | 2004-01-07 | 2004-01-07 | 復号または署名作成におけるべき乗剰余算の計算方法 |

| DE602004023811T DE602004023811D1 (de) | 2004-01-07 | 2004-07-12 | Verfahren zur modularen Potenzierung zur Entschlüsselung bzw. zur Erzeugung von digitalen Signaturen |

| EP04016352A EP1553720B1 (en) | 2004-01-07 | 2004-07-12 | Modular exponentiation method in decryption or signature generation |

| US10/893,523 US7512231B2 (en) | 2004-01-07 | 2004-07-19 | Computation method for modular exponentiation operation in decryption or signature generation |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004001602A JP4626148B2 (ja) | 2004-01-07 | 2004-01-07 | 復号または署名作成におけるべき乗剰余算の計算方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005195829A JP2005195829A (ja) | 2005-07-21 |

| JP2005195829A5 JP2005195829A5 (ja) | 2007-02-22 |

| JP4626148B2 true JP4626148B2 (ja) | 2011-02-02 |

Family

ID=34587677

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004001602A Expired - Fee Related JP4626148B2 (ja) | 2004-01-07 | 2004-01-07 | 復号または署名作成におけるべき乗剰余算の計算方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7512231B2 (ja) |

| EP (1) | EP1553720B1 (ja) |

| JP (1) | JP4626148B2 (ja) |

| DE (1) | DE602004023811D1 (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2015171A1 (fr) * | 2007-06-29 | 2009-01-14 | Gemplus | Procédé cryptographique comprenant une exponentiation modulaire sécurisée contre les attaques à canaux cachés sans la connaissance de l'exposant public, cryptoprocesseur pour la mise en oeuvre du procédé et carte à puce associée |

| FR2977953A1 (fr) * | 2011-07-13 | 2013-01-18 | St Microelectronics Rousset | Protection d'un calcul d'exponentiation modulaire par addition d'une quantite aleatoire |

| FR3015079B1 (fr) * | 2013-12-17 | 2016-02-05 | Oberthur Technologies | Verification d'integrite de paire de cles cryptographiques |

| FR3015076B1 (fr) * | 2013-12-17 | 2016-02-05 | Oberthur Technologies | Generation de cles cryptographiques |

| CN105099684B (zh) * | 2014-05-08 | 2019-08-16 | 国民技术股份有限公司 | 一种模幂运算的处理方法、装置及密码设备 |

| WO2017135970A1 (en) * | 2016-02-05 | 2017-08-10 | Entit Software Llc | Extended ciphertexts |

| KR101982237B1 (ko) * | 2017-03-06 | 2019-05-24 | 고려대학교 산학협력단 | 클라우드 컴퓨팅 환경에서의 속성 기반 암호화를 이용한 데이터 공유 방법 및 시스템 |

| KR102003936B1 (ko) * | 2019-02-18 | 2019-07-29 | 주식회사 에이티이엔지 | 해킹방지용 데이터 전송 케이블 |

| US11249726B2 (en) | 2019-09-10 | 2022-02-15 | Intel Corporation | Integrated circuits with modular multiplication circuitry |

| CN111352609B (zh) * | 2020-03-05 | 2022-06-14 | 青岛大学 | 一种基于边缘计算的分布式外包模幂运算方法 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1999035782A1 (en) * | 1998-01-02 | 1999-07-15 | Cryptography Research, Inc. | Leak-resistant cryptographic method and apparatus |

| JP2000182012A (ja) * | 1998-12-14 | 2000-06-30 | Hitachi Ltd | 情報処理装置、端タンパ処理装置 |

| JP2001005731A (ja) * | 1999-06-24 | 2001-01-12 | Hitachi Ltd | 情報処理装置、カード部材および情報処理システム |

| JP2002247025A (ja) * | 2001-02-22 | 2002-08-30 | Hitachi Ltd | 情報処理装置 |

| JP2003208097A (ja) * | 2002-01-15 | 2003-07-25 | Fujitsu Ltd | サイドチャネルアタック耐性を有する暗号演算装置及び方法 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1995024708A1 (fr) * | 1994-03-07 | 1995-09-14 | Nippon Telegraph And Telephone Corporation | Procede et systeme d'emission d'informations a protocole d'authentification a base de connaissances nulles |

| US6411715B1 (en) * | 1997-11-10 | 2002-06-25 | Rsa Security, Inc. | Methods and apparatus for verifying the cryptographic security of a selected private and public key pair without knowing the private key |

| DE10143728B4 (de) * | 2001-09-06 | 2004-09-02 | Infineon Technologies Ag | Vorrichtung und Verfahren zum Berechnen eines Ergebnisses einer modularen Exponentiation |

| CN1682484B (zh) * | 2002-09-11 | 2012-03-21 | 德国捷德有限公司 | 受保护的密码计算 |

| TW586086B (en) * | 2002-12-27 | 2004-05-01 | Ind Tech Res Inst | Method and apparatus for protecting public key schemes from timing, power and fault attacks |

-

2004

- 2004-01-07 JP JP2004001602A patent/JP4626148B2/ja not_active Expired - Fee Related

- 2004-07-12 EP EP04016352A patent/EP1553720B1/en not_active Expired - Fee Related

- 2004-07-12 DE DE602004023811T patent/DE602004023811D1/de active Active

- 2004-07-19 US US10/893,523 patent/US7512231B2/en not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1999035782A1 (en) * | 1998-01-02 | 1999-07-15 | Cryptography Research, Inc. | Leak-resistant cryptographic method and apparatus |

| JP2000182012A (ja) * | 1998-12-14 | 2000-06-30 | Hitachi Ltd | 情報処理装置、端タンパ処理装置 |

| JP2001005731A (ja) * | 1999-06-24 | 2001-01-12 | Hitachi Ltd | 情報処理装置、カード部材および情報処理システム |

| JP2002247025A (ja) * | 2001-02-22 | 2002-08-30 | Hitachi Ltd | 情報処理装置 |

| JP2003208097A (ja) * | 2002-01-15 | 2003-07-25 | Fujitsu Ltd | サイドチャネルアタック耐性を有する暗号演算装置及び方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| DE602004023811D1 (de) | 2009-12-10 |

| US20050147241A1 (en) | 2005-07-07 |

| US7512231B2 (en) | 2009-03-31 |

| EP1553720B1 (en) | 2009-10-28 |

| JP2005195829A (ja) | 2005-07-21 |

| EP1553720A1 (en) | 2005-07-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP3566385B1 (en) | Homomorphic white box system and method for using same | |

| KR100891323B1 (ko) | 이진 필드 ecc에서 랜덤 포인트 표현을 이용하여 파워해독의 복잡도를 증가시키기 위한 암호화 방법 및 장치 | |

| CN109039640B (zh) | 一种基于rsa密码算法的加解密硬件系统及方法 | |

| JP4086503B2 (ja) | 暗号演算装置及び方法並びにプログラム | |

| JP2008252299A (ja) | 暗号処理システム及び暗号処理方法 | |

| Nagaraj et al. | Data encryption and authetication using public key approach | |

| JP5182364B2 (ja) | サイドチャネル攻撃に対する耐タンパ性を有する暗号処理方法 | |

| KR100652377B1 (ko) | 모듈라 지수승 알고리즘, 기록매체 및 시스템 | |

| JP2009500710A (ja) | 攻撃又は解析に対してデータ処理装置を保護するための装置及び方法 | |

| JP2004304800A (ja) | データ処理装置におけるサイドチャネル攻撃防止 | |

| EP0952697B1 (en) | Elliptic curve encryption method and system | |

| JP4626148B2 (ja) | 復号または署名作成におけるべき乗剰余算の計算方法 | |

| KR20120028432A (ko) | 타원곡선암호를 위한 연산 장치 및 방법 | |

| KR20030075146A (ko) | 암호 체계의 비밀 키 저장 및 복원 방법과 장치 | |

| Fadulilahi et al. | Efficient algorithm for RNS implementation of RSA | |

| JP2010139544A (ja) | 剰余演算装置、及び剰余演算方法 | |

| CN1985458B (zh) | 增强的自然蒙哥马利指数掩蔽和恢复的方法和装置 | |

| Kayode et al. | Efficient RSA cryptosystem decryption based on Chinese remainder theorem and strong prime | |

| KR100953715B1 (ko) | Crt-rsa 모듈라 지수승 알고리즘을 이용한 디지털서명 방법, 그 장치 및 이를 기록한 컴퓨터 판독가능 저장매체 | |

| KR101112570B1 (ko) | 전력 분석 및 오류 주입 공격에 안전한 디지털 서명 장치, 방법 및 그 기록 매체 | |

| Hwang et al. | Fast firmware implementation of RSA-like security protocol for mobile devices | |

| Somsuk | The alternative Method to Finish Modular Exponentiation and Point Multiplication Processes | |

| KR20090093141A (ko) | Crt-rsa 기반의 비트 연산을 이용한 디지털 서명방법, 그 장치 및 이를 기록한 기록 매체 | |

| Muhaya et al. | Applying hessian curves in parallel to improve elliptic curve scalar multiplication hardware | |

| Hung et al. | Compression-RSA: New approach of encryption and decryption method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20060424 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070109 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070109 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100330 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100413 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100611 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101012 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101025 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131119 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131119 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |