JP4547084B2 - Mobile communication device and transceiver - Google Patents

Mobile communication device and transceiver Download PDFInfo

- Publication number

- JP4547084B2 JP4547084B2 JP2000352553A JP2000352553A JP4547084B2 JP 4547084 B2 JP4547084 B2 JP 4547084B2 JP 2000352553 A JP2000352553 A JP 2000352553A JP 2000352553 A JP2000352553 A JP 2000352553A JP 4547084 B2 JP4547084 B2 JP 4547084B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- output

- variable gain

- low

- frequency

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Digital Transmission Methods That Use Modulated Carrier Waves (AREA)

- Transceivers (AREA)

- Mobile Radio Communication Systems (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は、部品点数を低減できる移動体通信機に係り、特に大規模集積化に適したダイレクトコンバージョン方式を適用した送受信機に関するものである。

【0002】

【従来の技術】

移動体通信機の爆発的な普及につれ、小型、低コスト化への要求が強まっている。そのため、VCO(電圧制御形発振器)や、フィルタ数を低減し、集積度を上げた集積回路の適用が望まれている。送受信機の従来例としては瀧川等によりアイ、イー、イー、イー、1999年、第25回、欧州集積回路会議予稿集278頁から281頁に発表された「GSM、DCS1800向けデュアルバンドトランシーバIC高周波技術 」(K. Takikawa et. al. RF Circuits Technique of Dual-Band Transceiver IC for GSM and DCS1800 applications, IEEE 25th European Solid-State Circuits Conference pp. 278-281, 1999)狽ェ挙げられる。構成図を図10(a)に示す。(1016)が集積回路で、他の構成部品(1001〜1015)は外付けとなる。本従来例は900MHz帯と1.8GHz帯の2つの周波数帯に対応するものである。また、受信機としてスーパーヘテロダイン方式を適用し、送信機にはオフセットPLL方式を採用している。スーパーヘテロダイン受信機では、帯域外妨害波を抑圧するRF(高周波)フィルタ(1001,1002)2個と、周波数変換に伴うイメージ周波数帯の妨害波を取り除くイメージ除去フィルタ(1003,1004)2個と、受信チャネル近傍の妨害波を除去するIF(中間周波)フィルタ(1005)が必要になる。また900MHz帯と1.8GHz帯の2つの周波数帯に対応するため局部発振器(1006,1007)が2個必要となる。

【0003】

外付け部品点数を削減できる受信方式に、ダイレクトコンバージョン方式がある。ダイレクトコンバージョン受信機の従来例としてはアイ、イー、イー、イー、1997年、VLSI回路シンポジウム予稿集113頁から114頁に発表された「900MHzダイレクトコンバージョン受信機」(Behzad Razavi, "A 900-MHz CMOS Direct Conversion Receiver," IEEE Symposium on VLSI Circuits,pp. 113-114, 1997)が挙げられる。構成図を図10(b)に示す。原理的にイメージ応答が存在しないので、ダイレクトコンバージョン方式にはイメージ除去フィルタが不要である。また、IFフィルタはICに集積化されたフィルタで代用できるため不要となる。本従来例では、VCO(1025)は受信機の入力周波数の2倍の周波数で発振し、その周波数は1850〜1920MHzである。この受信機をGSM,DCS1800のデュアルバンド受信機に適用する場合、VCO(1025)は1850〜1920MHz(GSM)と3610〜3760MHz(DCS1800)で発振する必要がある。しかし、これらの周波数帯を1つのVCOでカバーするのは困難でありVCOは2個必要となる。

【0004】

ダイレクトコンバージョン受信機の広く知られた欠点は、直流オフセット電圧である。これは、ミキサ(1019,1020)の入力信号と局発発振信号の周波数が等しいために生じる。例えば、局発発振信号が入力信号の入力端子にリークすると局発発振信号同士の掛け算が生じて直流オフセット電圧が発生する。直流オフセット電圧を校正する方式の従来例としてはアイ、イー、イー、イー、1995年、半導体素子回路ジャーナル1399頁から1410頁に発表された「デジタル通信向けダイレクトコンバージョントランシーバ」(Asad A. Abidi et. al., "Direct-Conversion Radio Transceivers for Digital Communications," IEEE Journal of Solid-State Circuits, pp. 1399-1410, vol. 30, no. 12,Dec.,1995)が挙げられる。構成図を図11に示す。可変利得増幅器(1102,1104)と低域通過フィルタ(1101,1103,1105)からなる可変利得増幅器の出力直流オフセット電圧は、DSP(1106)で検知される。その情報に基づいてDSP(1106)は、低域通過フィルタ(1101)の入力に直流オフセット電圧校正信号を出力する。

【0005】

【発明が解決しようとする課題】

上記の様に、ダイレクトコンバージョン受信機は外付けフィルタ数を削減することができる。しかし、図10(a)のGSM,DCS1800デュアルバンド送受信機でスーパーへテロダイン受信機の代わりにダイレクトコンバージョン受信機を使用すると、局発発信器の数が増加してしまう問題がある。なぜなら、局発発振周波数として送信機では1150〜1185MHz(GSM),1575〜1650MHz(DCS1800)が、受信機では1850〜1920MHz(GSM),3610〜3760MHz(DCS1800)が必要で、1つのVCOで複数の帯域をカバーするのは困難だからである。さらなるコスト削減のため、VCO数を削減することが第1の課題となる。

【0006】

また、GSMシステムで高速データ通信を実現するGPRS(GeneralPacket Radio Service)では受信または送信に複数のスロットが割り当てられる。そのため高速な直流オフセット電圧校正が要求される。また、直流オフセット電圧校正は動作フレーム毎に行う必要がある。まず高速なオフセット校正の必要性から図4を用いて説明する。GSMの1フレームは8スロットから構成され、1スロットの時間は577μsecである。直流オフセット電圧校正にとって厳しい条件、すなわち受信(RX)に4スロット、送信(TX)に1スロット割り当てられた場合を想定する。送信スロットTX1’はスロット7に割り当てられるが、基地局への伝播遅延を考慮してスロット7から237μsec前のTX1のタイミングで送信される。また、送受信以外に約500μsecのモニタ期間とPLLの同期期間が必要である。PLL同期期間に150μsec程度かかるとすると、送受信回路が動作せず直流オフセット電圧校正を行える時間は、1154−500−237−150*2=117μsecとなり、高速なDCオフセット校正が要求される。

【0007】

次に、フレーム毎にオフセット校正を行う必要性について図5を用いて説明する。図5に、ミキサの出力直流オフセット電圧の受信周波数依存性を測るための測定回路とその測定結果を示す。測定結果から、出力直流オフセット電圧には周波数依存性があることが分かる。したがって、GSM,DCS1800の様に通話中の受信周波数が固定でなく、受信帯域内で周波数ホッピングするシステムでは、前もって直流オフセット電圧を予見することは困難である。したがって、動作フレーム毎に直流オフセット電圧を校正する必要がある。

【0008】

従来例(図11)の方式はオフセット校正用の帰還ループ内にフィルタが介在するため高速なオフセット校正が困難で高速データ通信に不向きである。したがって、高速データ通信に適した高速なオフセット校正方式の実現が第2の課題である。

【0009】

【課題を解決するための手段】

上記第1の課題を実現するために、本発明では1つのVCOから分周器を利用して受信機と送信機にRF帯の局部発振信号を供給する。受信機用の局部発振信号生成には分周比固定の分周器を用い、送信機用の局部発振信号生成には分周比の切り替えが可能な分周器を用いる。

【0010】

上記第2の課題を実現するために、本発明ではベースバンド信号用の可変利得増幅器に直流オフセット電圧検出手段と、直流オフセット校正手段を設け、オフセット校正用の帰還ループ内にフィルタを介在させないことで高速に直流オフセットを校正する。

【0011】

【発明の実施の形態】

本発明の第1の実施形態を図1を用いて説明する。ここではアプリケーションとして欧州セルラ電話GSM(900MHz帯)、DCS1800(1800MHz帯)に対応する例を用いる。

【0012】

受信機にはRF信号を直接ベースバンド信号に変換するダイレクトコンバージョン方式を適用し、送信機には従来例ですでに示したオフセットPLL方式を採用している。受信機は低雑音増幅器(101,102)、ミキサ(103,104)、可変利得低域通過フィルタ(139)から構成される。ミキサでは信号周波数をRF帯からベースバンド帯へ変換するとともに、sin成分とcos成分に分離する復調も同時に行う。このためミキサ(103,104)に90°位相の異なる局部発振信号を加える必要があり、分周器(105,115)を用いて生成する。局部発振信号は、VCO(111)とPLL(112)でPLLループを組むことで発生させる。VCO(111)として3600MHz帯発振のものを用いれば、分周器(115)の出力は1800MHz帯となりDCS1800用の局部発振信号を得る。また、分周器(116)を分周器(105)の前段に配置することで、分周器(105)の出力周波数は900MHz帯となり、GSM用局部発振信号を得る。ミキサ(103,104)の出力ベースバンド信号は可変利得低域通過フィルタ(139)に入力され、レベル調整と妨害波除去が行われる。可変利得低域通過フィルタ(139)は、低域通過フィルタ(106,107,137,138)と可変利得増幅器(108,109)から構成される。また、可変利得低域通過フィルタ(139)出力での直流オフセット電圧を抑圧するため、直流オフセット電圧検出手段と直流オフセット校正手段をもった直流オフセット電圧校正回路(110)を設ける。

【0013】

外付け構成部品を減らすため、送信機でも受信機と同じVCO(111)を用いる。送信機で用いるIF周波数(fIF)の決め方を以下に説明する。アンテナ(136)で受信する受信周波数をfrG(GSM)とfrD(DCS1800)、送信する送信周波数をftG(GSM)とftD(DCS1800)とする。

前述の様に、VCO(111)の発振周波数はGSM受信周波数の4倍、DCS1800受信周波数の2倍だから、VCO(111)の発振周波数は、4・frG=2・frDと表すことができる。この発振周波数をm分周(GSM)、n分周(DCS1800)した信号をオフセットPLLのミキサ(126)の局部発振信号として用いると、GSM時のIF周波数fIFGは数式1の様に表せる。

【0014】

【数1】

【0015】

同様にDCS1800時のIF周波数fIFDは数式2の様に表せる。

【0016】

【数2】

【0017】

ここで、frG=925MHz,ftG=880MHz,frD=1805MHz,ftD=1710MHzとする。mに対してfIFGを計算したものを図12に、nに対してfIFDを計算したものを図13に示す。分周には2分周器を用いるので、m,nとして2のi乗(iは正の整数)を用いた。IF周波数生成のためのVCOを1個にするにはm,nは自由に選ぶことはできず、fIFGとfIFDはほぼ等しい必要がある。または、2分周器を使用した場合は、fIFGとfIFDの比が2のj乗(jは正の整数)にほぼ等しければよい。ここで、ほぼ等しいとは、2つの周波数が正確に一致しなくてもそれら2つがVCOの発振周波数範囲に含まれていればよいという意味である。図12、図13において、上記条件を満たすmとnの組み合わせは、例えば、(m,n)=(2,1)や(4,2)である。このm,nの組み合わせから、消費電力や不要スプリアス信号発生の有無等を考慮に入れて最終的にfIFを決定する。本実施例では(m,n)=(4,2)としてある。分周器(117,118)と切り替えスイッチ(121)をVCO(111)後段に設け、GSM時にはVCO(111)出力周波数を4分周、DCS1800時には2分周する様に制御する。次に、VCO(114)の発振周波数は、消費電力やICに内蔵する受動素子の規模等によって決定される。本実施例では発振周波数を300MHz帯とし、VCO(114)後段に分周器(119,120)と切り替えスイッチ(122)を設けることで、GSM時には8分周、DCS1800時には4分周してfIFG=45MHz、fIFD=95MHzが生成される。

【0018】

スプリアスの問題を更に具体的に説明する。図17,18にIF周波数を固定し、局部発振周波数を変化させた場合のスプリアスを示す。図17,18はGSM、DCS1800に対応し、送信信号を送信用発振器(128、129)から発生させた場合に、IF周波数の整数倍(m倍)と、局部発振周波数の差によって生じるスプリアスを示したものである。ここでfIFはIF周波数、fVCOは送信周波数を示す。各欄に記入した数値はスプリアス信号と送信周波数の差をMHzの単位で示したものである。ハッチをかけた部分は10MHz以内の近傍にスプリアスが発生する場合で、送信機のループフィルタ(127)で除去するのが困難なものである。図17,18より判るようにIF周波数を1つに固定すると、送信帯域内でスプリアスが送信周波数の近傍に現れる領域を避けることが困難であり、IF周波数を送信周波数に応じて変化させることの有効性が理解される。例えば図17に示すGSMの例では、880MHzから888MHzまで45MHzのIF周波数を選び、888MHzから914MHzまで46MHzのIF周波数を選ぶとスプリアスを回避できる。

【0019】

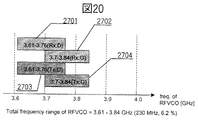

本実施例では送信機のミキサ回路(126)に印加される局部発振信号が受信帯域内に存在する。図16に本実施例の送信部を拡大して示す。(2309)で示す経路を通じて受信帯域内に有る局部発振信号は漏洩し、後段の増幅器により増幅され放射される。GSMのスプリアスのほうしゃに関する規格を図19にまとめる。受信帯域のスプリアスは、5点に限り-36 dBm以下のスプリアスが許容されるが、原則として-79dBm/100kHzに抑圧することが望まれる。図20にこれまでの実施例で説明したVCOの発振周波数をまとめる。DCS1800の受信用帯域(2701)と送信用帯域(2703)は一致しており、GSMの受信用帯域(2702)と送信用帯域(2704)も同様に一致している。これをずらせる為図21のような周波数配置を考える。DCS1800の受信用帯域(2701)とずらせた送信用帯域(2705)は重なることなく、送信時に受信帯域内の周波数を持つ局部発振漏洩は回避できる。GSMについても同様である。

【0020】

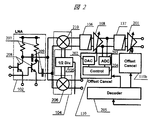

次に、本発明に係る受信機の第2の実施形態について図2を用いて説明する。

【0021】

受信機は、低雑音増幅器(102)、ミキサ(104)、分周器(105)、低域通過フィルタ(106,137)、可変利得増幅器(108,201)、直流オフセット電圧校正回路(110,110b)及びデコーダ(205)から構成される。また、低雑音増幅器は負荷抵抗(207)、トランジスタ(208)及び容量(209)から構成され、直流オフセット電圧校正回路(110)はデジタルアナログ変換器DAC(202)、アナログデジタル変換器ADC(203)及び制御回路(204)から構成される。ミキサ(104)は、ミキサ(210,206)から構成される。

【0022】

可変利得増幅器(108)の出力直流電圧はADC(203)でデジタル信号に変換され制御回路(204)へ入力される。制御回路(204)で、可変利得増幅器(108)出力での直流オフセット電圧が計測され、直流オフセット電圧を校正するための校正信号が出力される。該校正信号はDAC(202)でデジタル信号からアナログ信号に変換され、DAC(202)出力信号により可変利得増幅器(108)の直流オフセット電圧が校正される。また、直流オフセット電圧校正回路(110)はデコーダ(205)により選択され、選択された回路だけが動作を行う。この様に、可変利得増幅器と直流オフセット電圧校正回路からなる帰還ループ内にフィルタが介在しないためフィルタでの遅延がなくなり高速なオフセット校正が実現できる。ここでADCのビット数は1ビットつまり単純な比較器を適用することも可能である。

【0023】

本発明に係る可変利得増幅器と直流オフセット電圧校正回路の第3の実施形態について図3を用いて説明する。

【0024】

可変利得増幅器は、抵抗(307,308,312)とトランジスタ(309,310,311)から構成される。トランジスタ(309,310)のベースに入力電圧が入力され、コレクタから出力電圧が出力される。利得は、例えば、トランジスタ(311)のベース電圧により制御することができる。DAC(313)は、トランジスタ(301,302,303)と抵抗(304,305,306)から構成される。制御回路(204)の出力をトランジスタ(301,302,303)のベースに接続しているので、制御回路(204)でトランジスタ(301,302,303)のコレクタ直流電流を制御することができる。

該コレクタ直流電流はトランジスタ(309)のコレクタ電流と足し合わされ抵抗(307)で電圧に変換される。今、直流オフセット電圧ΔV(=V2−V1)があるとする。抵抗(307,308)の抵抗値がRL、DAC(313)の出力直流電流をIDAC1、DAC(314)の出力直流電流をIDAC2で表すことにする。この時、数式3の関係が成り立つ様に制御回路(204)はDAC(313,314)を制御する。

【0025】

【数3】

【0026】

本発明に係る可変利得増幅器の第4の実施形態について図6を用いて説明する。図6(a)に直流オフセット電圧のない理想的な可変利得増幅器(603)と可変利得増幅器(603)の入力換算直流オフセット電圧源(606)を示す。この場合、オフセット電圧を抑圧する手段がないので出力端子(604,605)の間にはオフセット電圧源(606)の出力電圧が可変利得増幅器(603)の利得倍されたオフセットが発生する。次に、本発明に係る第4の実施例である、切り替えスイッチ(607,608)を可変利得増幅器(603)の入出力に接続した構成を図6(b,c)に示す。切り替えスイッチ(607,608)の接続関係が図6(b)と(c)で逆になっているため、入出力端子間の接続関係は維持しつつオフセット電圧源(606)出力電圧の伝わる出力端子は逆になる。したがって、上記に示した切り替えスイッチ(607,608)の切り替えを周期的に行えば、オフセット電圧源(606)の出力電圧は出力端子(604)と(605)に同じ時間発生することになり、出力端子間のオフセット電圧は0になる。

【0027】

本発明に係る受信機の第5の実施形態について図7を用いて説明する。本実施例は、第2の実施例において、可変利得増幅器(201)と直流オフセット電圧校正回路(110b)の代わりに第4の実施例で示した可変利得増幅器(609)を用い、可変利得増幅器(609)後段に低域通過フィルタ(702)とバッファアンプ(701)を接続したことを特徴とする受信機である。

【0028】

本発明に係る受信機の第6の実施形態について図8を用いて説明する。本実施例は、第2の実施例において、低域通過フィルタ(140)と可変利得増幅器(201)の間にスイッチ(801)を接続したことを特徴とする受信機である。

直流オフセット電圧校正時には、スイッチ(801)をオンにして可変利得増幅器(201)の入力を短絡し、校正時以外にはスイッチ(801)をオフにする。校正時にスイッチ(801)をオンにすることで、可変利得増幅器(201)は前段からの直流オフセット電圧の影響を受けずに校正を行うことができる。

【0029】

本発明に係る移動体通信機の第7の実施形態について図9を用いて説明する。本実施例は、第1の実施例にベースバンド回路(901)を追加したことを特徴とする移動体通信機である。(907)には、第1の実施例においてアンテナ(136)とICに内蔵される回路(143)以外のすべての回路が含まれる。ベースバンド回路(901)では、受信ベースバンド信号(902,903)から音声信号への変換や、音声信号から送信ベースバンド信号(905,906)への変換等の信号処理を行う。さらに、ベースバンド回路(901)は、回路(143)での直流オフセット電圧の校正を開始するタイミングを決めるDCオフセットキャンセル開始信号(904)を出力し、回路(143)に入力する。この開始信号は受信機が信号を受信開始する前に送られ、信号を受信する前に(143)の回路で発生する直流オフセットを除去する。

【0030】

本発明に係る移動体通信機の第8の実施形態について図14を用いて説明する。フィルタ(140)の容量(1403)と抵抗(1404,1405)の間にスイッチ(1401,1402)を挿入し、直流オフセット校正時の時定数を小さくする。これによりフィルタ(140)での伝搬遅延を短縮できるので図8に示す入力短絡用スイッチ(801)を使うことなく高速で直流オフセット校正が出来る。また、各増幅器(108,201)が図3に示すようにバイポーラトランジスタで構成された場合は、フィルタ抵抗(1404,1405)を介してベースバイアスが行われる。このため、ベース電流ばらつき、フィルタ抵抗ばらつきによるバイアスオフセットも含めて直流オフセット電圧を校正できる。これに対して、短絡用スイッチ(801)を用いる第6の実施例では該バイアスオフセットを校正できない。また、直流オフセットを前段から順に除去すると、残留誤差は後段の直流オフセット校正機能が除去するため、より高精度の直流オフセット除去が達成できる。

【0031】

本発明に係る移動体通信機の第9の実施形態について図15を用いて説明する。第8の実施例の様にフィルタの伝搬遅延を低減した場合は、直流オフセット電圧校正のための帰還ループ内にフィルタを介在できる。そのため、第8の実施例に比べてADCの数を削減でき回路規模を低減出来る。

【0032】

【発明の効果】

本発明により従来のスーパーヘテロダイン形受信機を適用した場合に比べ、外付けフィルタ3個、外付けVCO1個削減することができる。さらにダイレクトコンバージョン受信機で問題となる直流オフセット電圧を高速で除去する方式をとることで、部品点数を削減しつつ、高速パケット伝送モードにも対応できる移動体通信機を実現できる。

【図面の簡単な説明】

【図1】本発明の第1の実施形態を示す移動体通信機構成図。

【図2】本発明の移動体通信機の受信機部分構成図。

【図3】本発明の受信機の直流オフセットを除去する回路の詳細図。

【図4】GSM規格における動作タイミング図。

【図5】ミキサ回路の発生する直流オフセット電圧測定方法と測定結果を示す図。

【図6】本発明に適用できるチョッパ形増幅器動作原理図。

【図7】本発明の受信機部分にチョッパ形増幅器を適用した場合の実施形態。

【図8】本発明の受信機に係る前段回路の影響なしに可変利得増幅器の直オフセット電圧校正を行う回路の構成図。

【図9】直流オフセット除去のためのタイミング信号がベースバンド回路から与えられることを示す図面。

【図10】(a)従来のスーパーヘテロダイン方式を適用した移動体通信機構成図。(b)従来のダイレクトコンバージョン受信機構成図。

【図11】従来の直流オフセット電圧校正手法。

【図12】GSM動作時の送信機IF周波数を示す図。

【図13】DCS1800動作時の送信機IF周波数を示す図。

【図14】フィルタ容量を切り離し直流オフセット除去動作を加速する方法を示す図。

【図15】フィルタ容量を切り離し直流オフセット除去回路を簡略化する方法を示す図。

【図16】GSM/DCS1800デュアルバンド送信回路を示す図。

【図17】GSM送信時スプリアス一覧を示す図。

【図18】DCS1800送信時スプリアス一覧を示す図。

【図19】GSMスプリアス規格を示す図。

【図20】送信、受信の局部発振周波数帯が一致したVCO発振周波数配置を示す図。

【図21】送信、受信の局部発振周波数帯が重ならないVCO発振周波数配置を示す図。

【符号の説明】

101、 102 低雑音増幅器

103、 104、 123、 126、 206、 210、 1019、 1020 ミキサ

105、 115、 116、 117、 118、 119、 120、 139 分周器

106、 107、 127、 131、 132、 137、 138、 702、 1012、 1013, 1021、 1022、 1101、 1103、 1105 低域通過フィルタ

108、 109、 201、 603、 1102、 1104 可変利得増幅器

110 直流オフセット電圧校正回路

111、 114、 128、 129、 1006、 1007、 1008、 1009 VCO

112、 113 PLL

121、 122 切り替えスイッチ

127 位相比較器

130、 1010、 1011 電力増幅器

133、 134、 1001、 1002、 1003、 1004、 1005 帯域通過フィルタ

135、 1014 アンテナスイッチ

136、 1015 アンテナ

139 可変利得低域通過フィルタ

140、 1016 IC内蔵回路

202 DAC

203 ADC

205 デコーダ

701 バッファアンプ

801、 1401、 1402、 スイッチ

901 ベースバンド回路

1403 容量

1404、 1405 抵抗

2301、 2302、 2305、 2306 リミッタ増幅器

2303、 2304、 2307、 2308 低域通過フィルタ

2309 送信用局部発振信号漏洩経路

2701、 2702 受信時VCO発振周波数帯

2703、 2704、 2705、 2706 送信時VCO発振周波数。[0001]

BACKGROUND OF THE INVENTION

The present invention relates to a mobile communication device capable of reducing the number of parts, and more particularly to a transceiver using a direct conversion method suitable for large-scale integration.

[0002]

[Prior art]

With the explosive spread of mobile communication devices, there is an increasing demand for miniaturization and cost reduction. Therefore, it is desired to apply a VCO (Voltage Controlled Oscillator) or an integrated circuit with a reduced number of filters and an increased degree of integration. As a conventional example of a transceiver, I. E., E. E., 1999, 25th, European Integrated Circuits Conference Proceedings, 278-281, “Dual Band Transceiver IC High Frequency for GSM, DCS1800” Technology '' (K. Takikawa et.al.RF Circuits Technique of Dual-Band Transceiver IC for GSM and DCS1800 applications, IEEE 25 th European Solid-State Circuits Conference pp. 278-281, 1999). A block diagram is shown in FIG. (1016) is an integrated circuit, and other components (1001 to 1015) are externally attached. This conventional example corresponds to two frequency bands of 900 MHz band and 1.8 GHz band. Further, a superheterodyne system is applied as a receiver, and an offset PLL system is employed as a transmitter. In the superheterodyne receiver, there are two RF (high frequency) filters (1001, 1002) for suppressing out-of-band jamming waves, and two image removal filters (1003, 1004) for removing jamming waves in the image frequency band accompanying frequency conversion In addition, an IF (intermediate frequency) filter (1005) for removing interference waves in the vicinity of the reception channel is required. Also, two local oscillators (1006, 1007) are required to support two frequency bands of 900 MHz band and 1.8 GHz band.

[0003]

There is a direct conversion method as a receiving method that can reduce the number of external parts. Conventional examples of direct conversion receivers include “900 MHz direct conversion receiver” (Behzad Razavi, “A 900-MHz”) published on pages 113 to 114 of the VLSI Circuit Symposium Proceedings in 1997. CMOS Direct Conversion Receiver, "IEEE Symposium on VLSI Circuits, pp. 113-114, 1997). A block diagram is shown in FIG. Since there is no image response in principle, the direct conversion method does not require an image removal filter. Further, the IF filter is unnecessary because it can be replaced by a filter integrated in the IC. Book Conventional In the example, the VCO (1025) oscillates at twice the receiver input frequency, which is between 1850 and 1920 MHz. When this receiver is applied to a dual band receiver of GSM and DCS1800, the VCO (1025) needs to oscillate at 1850 to 1920 MHz (GSM) and 3610 to 3760 MHz (DCS1800). However, it is difficult to cover these frequency bands with one VCO, and two VCOs are required.

[0004]

A widely known drawback of direct conversion receivers is the DC offset voltage. This occurs because the frequency of the input signal of the mixer (1019, 1020) is equal to the frequency of the local oscillation signal. For example, when the local oscillation signal leaks to the input terminal of the input signal, the local oscillation signals are multiplied together to generate a DC offset voltage. As a conventional example of a method for calibrating a DC offset voltage, “Direct Conversion Transceiver for Digital Communication” (Asad A. Abidi et al.) Published on pages 1399 to 1410 of Semiconductor Device Circuit Journal, I, E, E, E, 1995. al., “Direct-Conversion Radio Transceivers for Digital Communications,” IEEE Journal of Solid-State Circuits, pp. 1399-1410, vol. 30, no. 12, Dec., 1995). A block diagram is shown in FIG. Variable gain amplifier ( 1102, 1104 ) And low-pass filter ( 1101, 1103, 1105 ) Is detected by the DSP (1106). Based on the information, the DSP (1106) outputs a DC offset voltage calibration signal to the input of the low-pass filter (1101).

[0005]

[Problems to be solved by the invention]

As described above, the direct conversion receiver can reduce the number of external filters. However, if a direct conversion receiver is used instead of a superheterodyne receiver in the GSM / DCS1800 dual-band transceiver shown in FIG. 10A, there is a problem that the number of local oscillators increases. This is because the transmitter oscillation frequency requires 1150 to 1185 MHz (GSM) and 1575 to 1650 MHz (DCS1800), and the receiver requires 1850 to 1920 MHz (GSM) and 3610 to 3760 MHz (DCS1800). This is because it is difficult to cover this bandwidth. In order to further reduce the cost, the first problem is to reduce the number of VCOs.

[0006]

In GPRS (General Packet Radio Service) that realizes high-speed data communication in the GSM system, a plurality of slots are assigned to reception or transmission. Therefore, high-speed DC offset voltage calibration is required. Further, the DC offset voltage calibration needs to be performed for each operation frame. First, the necessity of high-speed offset calibration will be described with reference to FIG. One frame of GSM is composed of 8 slots, and the time of 1 slot is 577 μsec. Assume a strict condition for DC offset voltage calibration, that is, 4 slots for reception (RX) and 1 slot for transmission (TX). The transmission slot TX1 ′ is assigned to the

[0007]

Next, the necessity of performing offset calibration for each frame will be described with reference to FIG. FIG. 5 shows a measurement circuit for measuring the reception frequency dependence of the output DC offset voltage of the mixer and the measurement result. From the measurement results, it can be seen that the output DC offset voltage has frequency dependence. Therefore, it is difficult to predict the DC offset voltage in advance in a system in which the reception frequency during a call is not fixed, such as GSM and DCS1800, and frequency hopping is performed within the reception band. Therefore, it is necessary to calibrate the DC offset voltage for each operation frame.

[0008]

Conventional The method of FIG. 11 (FIG. 11) is not suitable for high-speed data communication because high-speed offset calibration is difficult because a filter is interposed in the feedback loop for offset calibration. Therefore, the realization of a high-speed offset calibration method suitable for high-speed data communication is a second problem.

[0009]

[Means for Solving the Problems]

In order to realize the first problem, in the present invention, a local oscillation signal in the RF band is supplied from one VCO to a receiver and a transmitter using a frequency divider. A frequency divider with a fixed division ratio is used for generating a local oscillation signal for a receiver, and a frequency divider capable of switching the frequency division ratio is used for generating a local oscillation signal for a transmitter.

[0010]

In order to realize the second problem, in the present invention, a variable gain amplifier for baseband signals is provided with DC offset voltage detection means and DC offset calibration means, and no filter is interposed in the feedback loop for offset calibration. To calibrate the DC offset at high speed.

[0011]

DETAILED DESCRIPTION OF THE INVENTION

A first embodiment of the present invention will be described with reference to FIG. Here, examples corresponding to European cellular telephone GSM (900 MHz band) and DCS1800 (1800 MHz band) are used as applications.

[0012]

A direct conversion method for directly converting an RF signal into a baseband signal is applied to the receiver, and the offset PLL method already shown in the conventional example is adopted for the transmitter. The receiver includes a low noise amplifier (101, 102), a mixer (103, 104), and a variable gain low pass filter (139). In the mixer, the signal frequency is converted from the RF band to the baseband band, and at the same time, the demodulation for separating into the sin component and the cos component is simultaneously performed. For this reason, it is necessary to add local oscillation signals having a phase difference of 90 ° to the mixers (103, 104), which are generated using the frequency dividers (105, 115). The local oscillation signal is generated by forming a PLL loop with the VCO (111) and the PLL (112). If a VCO (111) having a 3600 MHz band oscillation is used, the output of the frequency divider (115) becomes the 1800 MHz band, and a local oscillation signal for DCS 1800 is obtained. Further, by arranging the frequency divider (116) in the preceding stage of the frequency divider (105), the output frequency of the frequency divider (105) becomes the 900 MHz band, and a GSM local oscillation signal is obtained. The output baseband signal of the mixer (103, 104) is input to the variable gain low-pass filter (139), where level adjustment and interference wave removal are performed. The variable gain low-pass filter (139) includes a low-pass filter (106, 107, 137, 138) and a variable gain amplifier (108, 109). Further, in order to suppress the DC offset voltage at the output of the variable gain low-pass filter (139), a DC offset voltage calibration circuit (110) having a DC offset voltage detection means and a DC offset calibration means is provided.

[0013]

In order to reduce external components, the transmitter uses the same VCO (111) as the receiver. A method for determining the IF frequency (fIF) used in the transmitter will be described below. The reception frequency received by the antenna (136) is fr. G (GSM) and fr D (DCS1800), the transmission frequency to be transmitted is ft G (GSM) and ft D (DCS1800).

As described above, since the oscillation frequency of the VCO (111) is four times the GSM reception frequency and twice the DCS1800 reception frequency, the oscillation frequency of the VCO (111) is 4 · fr. G = 2 · fr D It can be expressed as. When a signal obtained by dividing the oscillation frequency by m (GSM) and by n (DCS1800) is used as a local oscillation signal of the mixer (126) of the offset PLL, the IF frequency fIF at the time of GSM G Can be expressed as

[0014]

[Expression 1]

[0015]

Similarly, IF frequency fIF at DCS1800 D Can be expressed as

[0016]

[Expression 2]

[0017]

Where fr G = 925 MHz, ft G = 880 MHz, fr D = 1805 MHz, ft D = 1710 MHz. for m F IF G FIG. 12 shows a calculation result of fIF with respect to n. D FIG. 13 shows the result of calculating. Since a frequency divider is used for frequency division, 2 to the power of i (i is a positive integer) is used as m and n. To make one VCO for generating IF frequency, m and n cannot be selected freely. G And fIF D Must be approximately equal. Or, if a divide-by-2 is used, fIF G And fIF D It is sufficient that the ratio of is substantially equal to 2 to the power of j (j is a positive integer). Here, “substantially equal” means that the two frequencies need only be included in the oscillation frequency range of the VCO even if the two frequencies do not exactly match. 12 and 13, the combinations of m and n satisfying the above conditions are, for example, (m, n) = (2, 1) or (4, 2). From the combination of m and n, the final result is taken into account the power consumption and the presence / absence of unnecessary spurious signals. F Determine IF. In this embodiment, (m, n) = (4, 2). A frequency divider (117, 118) and a changeover switch (121) are provided in the subsequent stage of the VCO (111), and control is performed so that the VCO (111) output frequency is divided by 4 during GSM and by 2 during DCS1800. Next, the oscillation frequency of the VCO (114) is determined by the power consumption, the scale of passive elements built in the IC, and the like. In this embodiment, the oscillation frequency is set to a 300 MHz band, and by providing a frequency divider (119, 120) and a changeover switch (122) after the VCO (114), the frequency is divided by 8 at GSM and divided by 4 at DCS1800. G = 45 MHz, fIF D = 95 MHz is generated.

[0018]

The problem of spurious will be explained more specifically. 17 and 18 show the spurious when the IF frequency is fixed and the local oscillation frequency is changed. 17 and 18 correspond to GSM and DCS1800, and transmit signals are transmitted to transmission oscillators (128, 12). 9 ) Where In addition, the spurious generated by the difference between the integral multiple (m times) of the IF frequency and the local oscillation frequency is shown. Here, fIF represents the IF frequency, and fVCO represents the transmission frequency. The numerical values entered in each column indicate the difference between the spurious signal and the transmission frequency in units of MHz. The hatched part is a case where spurious is generated in the vicinity of 10 MHz, and it is difficult to remove by the loop filter (127) of the transmitter. 17 and 18, when the IF frequency is fixed to one, it is difficult to avoid a region where spurious appears in the vicinity of the transmission frequency in the transmission band, and the IF frequency can be changed according to the transmission frequency. Effectiveness is understood. For example, in the example of GSM shown in FIG. 17, spurious can be avoided by selecting an IF frequency of 45 MHz from 880 MHz to 888 MHz and selecting an IF frequency of 46 MHz from 888 MHz to 914 MHz.

[0019]

In this embodiment, the local oscillation signal applied to the mixer circuit (126) of the transmitter is present in the reception band. FIG. 16 shows an enlargement of the transmission unit of this embodiment. The local oscillation signal in the reception band leaks through the path indicated by (2309) and is amplified and radiated by the amplifier at the subsequent stage. FIG. 19 summarizes the standards related to GSM spurious brushes. As for the spurious of the reception band, spurious of −36 dBm or less is allowed only for 5 points, but in principle, it is desirable to suppress it to −79 dBm / 100 kHz. FIG. 20 summarizes the oscillation frequency of the VCO described in the embodiments so far. The DCS 1800 reception band (2701) and transmission band (2703) match, and the GSM reception band (2702) and transmission band (2704) also match. In order to shift this, a frequency arrangement as shown in FIG. 21 is considered. The transmission band (2705) shifted from the reception band (2701) of DCS 1800 does not overlap, and local oscillation leakage having a frequency within the reception band can be avoided during transmission. The same applies to GSM.

[0020]

Next, a second embodiment of the receiver according to the present invention Using FIG. explain.

[0021]

The receiver includes a low noise amplifier (102), a mixer (104), a frequency divider (105), a low pass filter (106, 137 ), Variable gain amplifier (108, 201), DC offset voltage calibration circuit (110, 201) 110b ) And a decoder (205). The low noise amplifier includes a load resistor (207), a transistor (208), and a capacitor (209). A DC offset voltage calibration circuit (110) includes a digital / analog converter DAC (202) and an analog / digital converter ADC (203). ) And a control circuit (204). The mixer (104) is composed of mixers (210, 206).

[0022]

The output DC voltage of the variable gain amplifier (108) is converted into a digital signal by the ADC (203) and input to the control circuit (204). The control circuit (204) measures the DC offset voltage at the output of the variable gain amplifier (108), and outputs a calibration signal for calibrating the DC offset voltage. The calibration signal is converted from a digital signal to an analog signal by the DAC (202), and the DC offset voltage of the variable gain amplifier (108) is calibrated by the DAC (202) output signal. The DC offset voltage calibration circuit (110) is selected by the decoder (205), and only the selected circuit operates. In this way, since no filter is interposed in the feedback loop composed of the variable gain amplifier and the DC offset voltage calibration circuit, there is no delay in the filter and high-speed offset calibration can be realized. Here, the number of bits of the ADC is 1 bit, that is, a simple comparator can be applied.

[0023]

A third embodiment of the variable gain amplifier and DC offset voltage calibration circuit according to the present invention will be described with reference to FIG.

[0024]

The variable gain amplifier includes resistors (307, 308, 312) and transistors (309, 310, 311). An input voltage is input to the bases of the transistors (309, 310), and an output voltage is output from the collector. The gain can be controlled by, for example, the base voltage of the transistor (311). The DAC (313) includes transistors (301, 302, 303) and resistors (304, 305, 306). Since the output of the control circuit (204) is connected to the base of the transistor (301, 302, 303), the collector DC current of the transistor (301, 302, 303) can be controlled by the control circuit (204).

The collector direct current is added to the collector current of the transistor (309) and converted into a voltage by the resistor (307). Now, the DC offset voltage ΔV (= V 2 -V 1 ). The resistance value of the resistor (307, 308) is R L , The output DC current of the DAC (313) is I DAC1 , The output DC current of the DAC (314) is I DAC2 It will be expressed as At this time, the control circuit (204) controls the DAC (313, 314) so that the relationship of

[0025]

[Equation 3]

[0026]

A fourth embodiment of the variable gain amplifier according to the present invention will be described with reference to FIG. FIG. 6A shows an ideal variable gain amplifier (603) having no DC offset voltage and an input converted DC offset voltage source (606) of the variable gain amplifier (603). In this case, since there is no means for suppressing the offset voltage, an offset is generated between the output terminals (604, 605) by multiplying the output voltage of the offset voltage source (606) by the gain of the variable gain amplifier (603). Next, according to the present invention 4 A configuration in which the changeover switch (607, 608) is connected to the input / output of the variable gain amplifier (603) is shown in FIG. Since the connection relationship of the changeover switches (607, 608) is reversed in FIGS. 6B and 6C, the output from which the offset voltage source (606) output voltage is transmitted while maintaining the connection relationship between the input and output terminals. The terminals are reversed. Therefore, if the changeover switches (607, 608) described above are periodically switched, the output voltage of the offset voltage source (606) is generated at the output terminals (604) and (605) for the same time, The offset voltage between the output terminals becomes zero.

[0027]

A fifth embodiment of the receiver according to the present invention will be described with reference to FIG. This embodiment is different from the second embodiment in that the variable gain amplifier (201) and the DC offset voltage calibration circuit ( 110b ) 4 The receiver is characterized in that the variable gain amplifier (609) shown in the embodiment is used, and a low-pass filter (702) and a buffer amplifier (701) are connected to the subsequent stage of the variable gain amplifier (609).

[0028]

A sixth embodiment of the receiver according to the present invention will be described with reference to FIG. This embodiment is a receiver characterized in that a switch (801) is connected between a low-pass filter (140) and a variable gain amplifier (201) in the second embodiment.

At the time of DC offset voltage calibration, the switch (801) is turned on to short-circuit the input of the variable gain amplifier (201), and the switch (801) is turned off at times other than calibration. By turning on the switch (801) during calibration, the variable gain amplifier (201) can be calibrated without being affected by the DC offset voltage from the previous stage.

[0029]

A seventh embodiment of the mobile communication device according to the present invention will be described with reference to FIG. The present embodiment is a mobile communication device characterized in that a baseband circuit (901) is added to the first embodiment. (907) includes an antenna (13 in the first embodiment). 6 ) And a circuit (143) built in the IC. The baseband circuit (901) performs signal processing such as conversion from a reception baseband signal (902, 903) to an audio signal and conversion from an audio signal to a transmission baseband signal (905, 906). Further, the baseband circuit (901) outputs a DC offset cancel start signal (904) for determining the timing for starting calibration of the DC offset voltage in the circuit (143), and inputs it to the circuit (143). This start signal is sent before the receiver starts receiving the signal, and removes the DC offset generated in the circuit of (143) before receiving the signal.

[0030]

An eighth embodiment of a mobile communication device according to the present invention will be described with reference to FIG. Switches (1401, 1402) are inserted between the capacitor (1403) and the resistors (1404, 1405) of the filter (140) to reduce the time constant during DC offset calibration. As a result, the propagation delay in the filter (140) can be shortened, so that the DC offset calibration can be performed at high speed without using the input short-circuit switch (801) shown in FIG. Further, when each amplifier (108, 201) is composed of a bipolar transistor as shown in FIG. 3, a base bias is performed via a filter resistor (1404, 1405). Therefore, it is possible to calibrate the DC offset voltage including the bias offset due to the base current variation and the filter resistance variation. On the other hand, the bias offset cannot be calibrated in the sixth embodiment using the shorting switch (801). Further, when the DC offset is removed in order from the previous stage, the residual error is removed by the DC offset calibration function in the subsequent stage, so that more accurate DC offset removal can be achieved.

[0031]

A ninth embodiment of a mobile communication device according to the present invention will be described with reference to FIG. If the propagation delay of the filter is reduced as in the eighth embodiment, the filter can be interposed in the feedback loop for DC offset voltage calibration. The Therefore, the number of ADCs can be reduced and the circuit scale can be reduced as compared with the eighth embodiment.

[0032]

【The invention's effect】

According to the present invention, it is possible to reduce three external filters and one external VCO compared to the case where a conventional superheterodyne receiver is applied. Furthermore, by adopting a method for removing the DC offset voltage, which is a problem in the direct conversion receiver, at high speed, it is possible to realize a mobile communication device that can cope with the high-speed packet transmission mode while reducing the number of components.

[Brief description of the drawings]

FIG. 1 is a configuration diagram of a mobile communication device showing a first embodiment of the present invention.

FIG. 2 is a configuration diagram of a receiver part of the mobile communication device of the present invention.

FIG. 3 is a detailed diagram of a circuit for removing a DC offset of the receiver of the present invention.

FIG. 4 is an operation timing chart in the GSM standard.

FIG. 5 is a diagram illustrating a method for measuring a DC offset voltage generated by a mixer circuit and a measurement result.

FIG. 6 is an operation principle diagram of a chopper type amplifier applicable to the present invention.

FIG. 7 shows an embodiment in which a chopper amplifier is applied to the receiver portion of the present invention.

FIG. 8 is a configuration diagram of a circuit that performs direct offset voltage calibration of a variable gain amplifier without the influence of the preceding circuit according to the receiver of the present invention.

FIG. 9 is a diagram showing that a timing signal for removing a DC offset is supplied from a baseband circuit.

FIG. 10A is a configuration diagram of a mobile communication device to which a conventional superheterodyne method is applied. (B) Configuration diagram of a conventional direct conversion receiver.

FIG. 11 shows a conventional DC offset voltage calibration method.

FIG. 12 is a diagram showing a transmitter IF frequency during GSM operation.

FIG. 13 is a diagram showing a transmitter IF frequency during DCS1800 operation.

FIG. 14 is a diagram illustrating a method of accelerating a DC offset removal operation by disconnecting a filter capacitor.

FIG. 15 is a diagram illustrating a method for simplifying a DC offset removal circuit by cutting off a filter capacitor;

FIG. 16 is a diagram showing a GSM / DCS1800 dual-band transmission circuit.

FIG. 17 is a diagram showing a list of spurious during GSM transmission.

FIG. 18 is a diagram showing a list of spurious transmissions during DCS1800 transmission.

FIG. 19 is a diagram showing a GSM spurious standard.

FIG. 20 is a diagram showing a VCO oscillation frequency arrangement in which local oscillation frequency bands for transmission and reception match.

FIG. 21 is a diagram showing a VCO oscillation frequency arrangement in which local oscillation frequency bands for transmission and reception do not overlap.

[Explanation of symbols]

101, 102 Low noise amplifier

103, 104, 123, 126, 206, 210, 1019, 1020 Mixer

105, 115, 116, 117, 118, 119, 120, 139 Frequency divider

106, 107, 127, 131, 132, 137, 138, 702, 1012, 1013, 1021, 1022, 1101, 1103, 1105 Low-pass filter

108, 109, 201, 603, 1102, 1104 Variable gain amplifier

110 DC offset voltage calibration circuit

111, 114, 128, 129, 1006, 1007, 1008, 1009 VCO

112, 113 PLL

121, 122 selector switch

127 Phase comparator

130, 1010, 1011 Power amplifier

133, 134, 1001, 1002, 1003, 1004, 1005 Band pass filter

135, 1014 Antenna switch

136, 1015 antenna

139 Variable Gain Low-Pass Filter

140, 1016 IC built-in circuit

202 DAC

203 ADC

205 decoder

701 Buffer amplifier

801, 1401, 1402, switch

901 Baseband circuit

1403 capacity

1404, 1405 resistance

2301, 2302, 2305, 2306 Limiter amplifier

2303, 2304, 2307, 2308 Low-pass filter

2309 Local oscillation signal leakage path for transmission

2701, 2702 VCO oscillation frequency band at reception

2703, 2704, 2705, 2706 Transmission VCO oscillation frequency.

Claims (10)

該第1のVCOの出力に接続された第1の分周比と第2の分周比を切り替える手段を有する第3の分周器と、第2のVCOと、該第2のVCOの出力に接続された第3と第4の分周比を切り替える手段を有する第4の分周器と、該第4の分周器の出力信号とベースバンド信号とが入力される第3のミキサと、該第3の分周器の出力信号を第1の入力信号とし、該第3のミキサの出力信号を第2の入力信号とし、該第1と第2の入力信号の周波数を用いて周波数変換した信号を出力信号とする周波数変換回路と、を含む送信機と、

を有することを特徴とする送受信機。A first VCO; first and second frequency dividers connected to the output of the first VCO; an output signal of the first frequency divider and a first RF signal being input; A receiving circuit including a first mixer and a second mixer to which an output signal of the second frequency divider and a second RF signal are input;

A third divider having means for switching between a first divider ratio and a second divider ratio connected to the output of the first VCO; a second VCO; and an output of the second VCO A fourth frequency divider having means for switching between the third and fourth frequency division ratios, and a third mixer to which the output signal of the fourth frequency divider and the baseband signal are input. The output signal of the third frequency divider is the first input signal, the output signal of the third mixer is the second input signal, and the frequency using the frequencies of the first and second input signals is used. A transmitter including a frequency conversion circuit that uses the converted signal as an output signal ;

A transmitter / receiver characterized by comprising:

該第1の分周器の分周比が2で、該第2の分周器の分周比が4であることを特徴とする送受信機。The transceiver according to claim 1,

2. A transceiver according to claim 1, wherein the first frequency divider has a frequency division ratio of 2, and the second frequency divider has a frequency division ratio of 4.

該第1のRF信号の周波数をfrf1、該第2のRF信号の周波数をfrf2、該周波数変換回路の第1と第2の出力周波数をそれぞれftx1、ftx2とするとき、該第1の分周比mと該第2の分周比nは、該第2のVCOの発振可能な周波数範囲内で、該第4の分周器の分周比を切り替えることで該第3のミキサ出力周波数を

|(2・frf1)/n−ftx1|と

|(4・frf2)/m−ftx2|にすることができるという条件を満たし、該第1のVCOの発振可能な周波数範囲を、(2・frf1)もしくは(4・frf2)にすることができるという条件を満たす

ことを特徴とする送受信機。The transceiver according to claim 2,

When the frequency of the first RF signal is frf1, the frequency of the second RF signal is frf2, and the first and second output frequencies of the frequency conversion circuit are ftx1 and ftx2, respectively, the first frequency division The ratio m and the second division ratio n are obtained by switching the third mixer output frequency by switching the division ratio of the fourth divider within the frequency range in which the second VCO can oscillate. | (2 · frf1) / n -ftx1 | and | (4 · frf2) / m -ftx2 | to meet the condition of being able to, capable of oscillating frequency range of the VCO of the first, (2- A transmitter / receiver characterized by satisfying the condition that it can be frf1) or (4 · frf2) .

該周波数変換回路は、位相比較器と、第1の低域通過フィルタと、第3と第4のVCOと、第4のミキサを有し、

該位相比較器は該第3のミキサ出力信号と該第4のミキサ出力信号の位相差に比例した信号を出力し、該第1の低域通過フィルタは該位相比較器の出力に接続され、該第3と第4のVCOは該第1の低域通過フィルタの出力に接続され、該第4のミキサは該第3もしくは第4のVCO出力信号と該第3の分周器出力信号をミキシングするPLLを用いた周波数変換回路である

ことを特徴とする送受信機。The transceiver according to claim 3,

The frequency conversion circuit includes a phase comparator, a first low-pass filter, third and fourth VCOs, and a fourth mixer.

The phase comparator outputs a signal proportional to the phase difference between the third mixer output signal and the fourth mixer output signal, and the first low-pass filter is connected to the output of the phase comparator; The third and fourth VCOs are connected to the output of the first low pass filter, and the fourth mixer receives the third or fourth VCO output signal and the third divider output signal. A transceiver comprising a frequency conversion circuit using a PLL for mixing.

該可変利得低域通過フィルタは、複数の可変利得増幅器と複数の低域通過フィルタから構成され、

該オフセット電圧校正回路は、該可変利得増幅器出力信号が入力されるADCと、該ADC出力信号から該可変利得増幅器の直流オフセット電圧を検知し該直流オフセット電圧を校正する信号を出力する制御回路と、該制御回路出力信号が入力され該可変利得増幅器に信号を出力するDACとから構成され、

該可変利得増幅器は、互いのエミッタが接続した第1と第2のトランジスタと、該第1のトランジスタのコレクタと電源に接続した第1の抵抗と、該第2のトランジスタのコレクタと該電源に接続した第2の抵抗と、該エミッタに接続した可変電流源から構成され、信号が該第1と第2のトランジスタのベースから入力され、コレクタから信号が出力されることを特徴とする可変利得増幅器であり、

該DACは、第3のトランジスタと、該第3のトランジスタのエミッタとグランドに接続した第3の抵抗から構成される電圧電流変換回路を複数有し、該第3のトランジスタのコレクタは、該第1のトランジスタのコレクタと接続し、該第3のトランジスタのベースは該制御回路の出力に接続する

ことを特徴とする送受信機。A variable gain low-pass filter to which a baseband signal is input, and an offset voltage calibration circuit having means for calibrating a DC offset voltage of the low-pass filter;

The variable gain low-pass filter includes a plurality of variable gain amplifiers and a plurality of low-pass filters.

The offset voltage calibration circuit includes an ADC to which the variable gain amplifier output signal is input, and a control circuit that detects a DC offset voltage of the variable gain amplifier from the ADC output signal and outputs a signal for calibrating the DC offset voltage. A DAC that receives the control circuit output signal and outputs a signal to the variable gain amplifier,

The variable gain amplifier includes first and second transistors whose emitters are connected to each other, a first resistor connected to a collector and a power source of the first transistor, a collector of the second transistor, and a power source. A variable gain comprising a connected second resistor and a variable current source connected to the emitter, wherein a signal is input from the bases of the first and second transistors and a signal is output from the collector An amplifier,

The DAC includes a plurality of voltage-current conversion circuits including a third transistor and a third resistor connected to the emitter of the third transistor and a ground. The collector of the third transistor is the second transistor. A transceiver connected to the collector of one transistor and the base of the third transistor connected to the output of the control circuit.

該可変利得低域通過フィルタは、複数の可変利得増幅器と複数の低域通過フィルタから構成され、

該オフセット電圧校正回路は、該可変利得増幅器出力信号が入力されるADCと、該ADC出力信号から該可変利得増幅器の直流オフセット電圧を検知し該直流オフセット電圧を校正する信号を出力する制御回路と、該制御回路出力信号が入力され該可変利得増幅器に信号を出力するDACとから構成され、

該可変利得低域通過フィルタは差動回路により構成され、

該低域通過フィルタのうち少なくとも1つの第1の低域通過フィルタは、第2と第3のスイッチと第1の容量を含み、該第2のスイッチは該第1の低域通過フィルタの第1の信号線と該第1の容量に接続され、該第3のスイッチは該第1の低域通過フィルタの第2の信号線と該第1の容量に接続され、該第2と第3のスイッチは、スイッチ切り替え制御により同期して短絡状態または開放状態になる

ことを特徴とする送受信機。A variable gain low-pass filter to which a baseband signal is input, and an offset voltage calibration circuit having means for calibrating a DC offset voltage of the low-pass filter;

The variable gain low-pass filter includes a plurality of variable gain amplifiers and a plurality of low-pass filters.

The offset voltage calibration circuit includes an ADC to which the variable gain amplifier output signal is input, and a control circuit that detects a DC offset voltage of the variable gain amplifier from the ADC output signal and outputs a signal for calibrating the DC offset voltage. A DAC that receives the control circuit output signal and outputs a signal to the variable gain amplifier,

The variable gain low-pass filter is constituted by a differential circuit,

At least one first low-pass filter of the low-pass filters includes second and third switches and a first capacitor, and the second switch is the second low-pass filter of the first low-pass filter. One signal line and the first capacitor, and the third switch is connected to the second signal line and the first capacitor of the first low-pass filter, and the second and third capacitors. The transmitter / receiver is in a short circuit state or an open state in synchronization with switch switching control.

該第1の低域通過フィルタの前段に接続される第1の可変利得増幅器の直流オフセット電圧を校正する制御回路は、第1のDACと第1の制御回路から構成され、

該第1の制御回路は、該第1の低域通過フィルタの後段に接続される第2の可変利得増幅器の直流オフセット電圧を校正する制御回路と同一である

ことを特徴とする送受信機。The transceiver according to claim 6,

The control circuit for calibrating the DC offset voltage of the first variable gain amplifier connected to the previous stage of the first low-pass filter includes a first DAC and a first control circuit.

The transceiver is characterized in that the first control circuit is the same as a control circuit that calibrates a DC offset voltage of a second variable gain amplifier connected to a subsequent stage of the first low-pass filter.

該可変利得低域通過フィルタは、複数の可変利得増幅器と複数の低域通過フィルタから構成され、

該可変利得低域通過フィルタは差動回路により構成され、

該可変利得増幅器のうち少なくとも1つを第3と第4の入力端子と第1と第2の出力端子を有するチョッパ型増幅器に換えたことを特徴とする送受信機であって、

該チョッパ型増幅器は、第5と第6の入力端子と第3と第4の出力端子をもつ第3の可変利得増幅器と、第4のスイッチと、第5のスイッチを有し、

該第4と第5のスイッチの切り替え制御により、該第3の入力端子と該第5の入力端子、該第4の入力端子と該第6の入力端子、該第1の出力端子と該第3の出力端子、該第2の出力端子と該第4の出力端子が接続する第1の状態と、該第3の入力端子と該第6の入力端子、該第4の入力端子と該第5の入力端子、該第1の出力端子と該第4の出力端子、該第2の出力端子と該第3の出力端子が接続する第2の状態を切り替えることが可能であり、

該第1と第2の状態は周期的に切り替わる

ことを特徴とする送受信機。A variable gain low-pass filter to which a baseband signal is input, and an offset voltage calibration circuit having means for calibrating a DC offset voltage of the low-pass filter;

The variable gain low-pass filter includes a plurality of variable gain amplifiers and a plurality of low-pass filters.

The variable gain low-pass filter is constituted by a differential circuit,

A transmitter / receiver characterized in that at least one of the variable gain amplifiers is replaced with a chopper type amplifier having third and fourth input terminals and first and second output terminals,

The chopper type amplifier includes a third variable gain amplifier having fifth and sixth input terminals, third and fourth output terminals, a fourth switch, and a fifth switch.

By the switching control of the fourth and fifth switches, the third input terminal and the fifth input terminal, the fourth input terminal and the sixth input terminal, the first output terminal and the first input terminal 3 output terminals, the first state in which the second output terminal and the fourth output terminal are connected, the third input terminal, the sixth input terminal, the fourth input terminal, and the fourth output terminal. 5 input terminals, the first output terminal and the fourth output terminal, the second state where the second output terminal and the third output terminal are connected can be switched,

A transmitter / receiver characterized in that the first and second states are periodically switched.

該送受信機が、請求項1から8の何れかに記載の送受信機であって、

該ベースバンド回路から該送受信機に直流オフセット電圧校正動作を開始するタイミングを規定する信号が出力される

ことを特徴とする移動体通信機。An antenna, an antenna switch connected to the antenna, a plurality of power amplifiers that output signals to the antenna switch, a plurality of bandpass filters connected to the antenna switch, the bandpass filter, and the power amplifier A mobile communication device having a transceiver connected to a baseband circuit,

The transceiver is the transceiver according to any one of claims 1 to 8,

A mobile communication device characterized in that a signal defining a timing for starting a DC offset voltage calibration operation is output from the baseband circuit to the transceiver.

該アンテナスイッチの代わりにデュプレクサを用いることを特徴とする移動体通信機。The mobile communication device according to claim 9, wherein

A mobile communication device using a duplexer instead of the antenna switch.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000352553A JP4547084B2 (en) | 1999-11-15 | 2000-11-15 | Mobile communication device and transceiver |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP11-323656 | 1999-11-15 | ||

| JP32365699 | 1999-11-15 | ||

| JP2000352553A JP4547084B2 (en) | 1999-11-15 | 2000-11-15 | Mobile communication device and transceiver |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007295286A Division JP4566228B2 (en) | 1999-11-15 | 2007-11-14 | Transceiver |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001211098A JP2001211098A (en) | 2001-08-03 |

| JP2001211098A5 JP2001211098A5 (en) | 2007-12-27 |

| JP4547084B2 true JP4547084B2 (en) | 2010-09-22 |

Family

ID=26571262

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000352553A Expired - Lifetime JP4547084B2 (en) | 1999-11-15 | 2000-11-15 | Mobile communication device and transceiver |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4547084B2 (en) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3672189B2 (en) | 2001-07-13 | 2005-07-13 | ソニー株式会社 | Radio signal receiving apparatus and demodulation processing circuit |

| JP2003152815A (en) | 2001-11-14 | 2003-05-23 | Hitachi Ltd | Semiconductor integrated circuit for communication |

| WO2004002098A1 (en) * | 2002-06-19 | 2003-12-31 | Hitachi, Ltd. | Radio communication apparatus |

| WO2004040755A1 (en) | 2002-11-01 | 2004-05-13 | Matsushita Electric Industrial Co., Ltd. | Filter circuit and radio device |

| KR100461723B1 (en) * | 2002-12-05 | 2004-12-17 | 삼성전기주식회사 | Cordless phone rf module having in-line pin arrangement |

| JP4230762B2 (en) | 2002-12-20 | 2009-02-25 | 株式会社ルネサステクノロジ | Direct conversion receiver |

| KR100519806B1 (en) * | 2003-10-07 | 2005-10-11 | 한국전자통신연구원 | Method for Power Controlling of Received Signal in Ultra Wide Band Transmission System |

| US7907589B2 (en) | 2003-12-01 | 2011-03-15 | Panasonic Corporation | Reception apparatus and reception method |

| CN1886901B (en) | 2003-12-01 | 2013-12-18 | 松下电器产业株式会社 | Receiving device and semiconductor integrated circuit |

| JP4234026B2 (en) | 2004-01-26 | 2009-03-04 | パナソニック株式会社 | Receiver circuit |

| WO2006030513A1 (en) * | 2004-09-16 | 2006-03-23 | Fujitsu Limited | Unbalance-balance converter |

| EP1845626A1 (en) * | 2005-01-14 | 2007-10-17 | NEC Corporation | Communication device, multi-band reception device, and reception device |

| JP4692346B2 (en) * | 2006-03-23 | 2011-06-01 | パナソニック電工株式会社 | Receiver |

| US8731024B2 (en) | 2008-01-25 | 2014-05-20 | Nec Corporation | Noise suppression apparatus |

| DE102010030628A1 (en) * | 2010-06-29 | 2011-12-29 | Robert Bosch Gmbh | Radar sensor for motor vehicles |

| JP4883657B2 (en) * | 2010-08-18 | 2012-02-22 | ルネサスエレクトロニクス株式会社 | Semiconductor integrated circuit for communication |

| JP5623877B2 (en) | 2010-11-15 | 2014-11-12 | ルネサスエレクトロニクス株式会社 | Semiconductor integrated circuit and operation method thereof |

| JP5611070B2 (en) | 2011-01-28 | 2014-10-22 | ルネサスエレクトロニクス株式会社 | Semiconductor integrated circuit and operation method thereof |

| JP5624493B2 (en) * | 2011-02-16 | 2014-11-12 | キヤノン株式会社 | Differential amplifier |

| JP5778047B2 (en) * | 2012-01-18 | 2015-09-16 | ルネサスエレクトロニクス株式会社 | Semiconductor integrated circuit and operation method thereof |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0316349A (en) * | 1989-06-13 | 1991-01-24 | Nec Corp | Automatic gain control system |

| JPH0575495A (en) * | 1991-09-11 | 1993-03-26 | Hitachi Ltd | Mobile communication equipment |

| JPH06303137A (en) * | 1992-12-29 | 1994-10-28 | Hitachi Ltd | D/a converter, offset adjustment circuit and portable communication terminal equipment using them |

| JPH09261106A (en) * | 1996-03-22 | 1997-10-03 | Matsushita Electric Ind Co Ltd | Mobile radio equipment operated for plural frequency bands |

| JPH1032520A (en) * | 1996-04-01 | 1998-02-03 | Nokia Mobile Phones Ltd | Transmitter-receiver sending/receiving radio frequency signal for two frequency bands |

| JPH10200353A (en) * | 1997-01-14 | 1998-07-31 | Kokusai Electric Co Ltd | Burst agc circuit and burst agc control method |

| JP2000286742A (en) * | 1999-03-31 | 2000-10-13 | Toshiba Corp | Radio communication unit |

-

2000

- 2000-11-15 JP JP2000352553A patent/JP4547084B2/en not_active Expired - Lifetime

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0316349A (en) * | 1989-06-13 | 1991-01-24 | Nec Corp | Automatic gain control system |

| JPH0575495A (en) * | 1991-09-11 | 1993-03-26 | Hitachi Ltd | Mobile communication equipment |

| JPH06303137A (en) * | 1992-12-29 | 1994-10-28 | Hitachi Ltd | D/a converter, offset adjustment circuit and portable communication terminal equipment using them |

| JPH09261106A (en) * | 1996-03-22 | 1997-10-03 | Matsushita Electric Ind Co Ltd | Mobile radio equipment operated for plural frequency bands |

| JPH1032520A (en) * | 1996-04-01 | 1998-02-03 | Nokia Mobile Phones Ltd | Transmitter-receiver sending/receiving radio frequency signal for two frequency bands |

| JPH10200353A (en) * | 1997-01-14 | 1998-07-31 | Kokusai Electric Co Ltd | Burst agc circuit and burst agc control method |

| JP2000286742A (en) * | 1999-03-31 | 2000-10-13 | Toshiba Corp | Radio communication unit |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001211098A (en) | 2001-08-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4566228B2 (en) | Transceiver | |

| JP4547084B2 (en) | Mobile communication device and transceiver | |

| US7194242B2 (en) | Direct-conversion transmitter circuit and transceiver system | |

| KR100663104B1 (en) | Frequency conversion circuit, radio frequency wave receiver, and radio frequency wave transceiver | |

| US7062248B2 (en) | Direct conversion receiver having a low pass pole implemented with an active low pass filter | |

| US20150118980A1 (en) | Transmitter (tx) residual sideband (rsb) and local oscillator (lo) leakage calibration using a reconfigurable tone generator (tg) and lo paths | |

| JP5168148B2 (en) | Wireless communication device | |

| US20020049075A1 (en) | Multiband portable radio terminal | |

| JPH1032520A (en) | Transmitter-receiver sending/receiving radio frequency signal for two frequency bands | |

| JPH1065749A (en) | Receiving circuit | |

| JP2004534454A (en) | Low leakage local oscillator system | |

| JP2006020265A (en) | Wireless communication receiver | |

| US20040147238A1 (en) | Analog demodulator in a low-if receiver | |

| JP3672189B2 (en) | Radio signal receiving apparatus and demodulation processing circuit | |

| JP4385521B2 (en) | Transceiver | |

| JPH09252324A (en) | Frequency converter | |

| KR100553434B1 (en) | Apparatus for receiving rf signal | |

| Piazza | Low power RF-receiver front-end ICs for mobile communications |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071114 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071114 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090928 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091013 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100302 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100602 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100622 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100705 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130709 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4547084 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |