JP4276993B2 - エラー訂正符号装置、エラー訂正符号復号装置および伝送装置 - Google Patents

エラー訂正符号装置、エラー訂正符号復号装置および伝送装置 Download PDFInfo

- Publication number

- JP4276993B2 JP4276993B2 JP2004317475A JP2004317475A JP4276993B2 JP 4276993 B2 JP4276993 B2 JP 4276993B2 JP 2004317475 A JP2004317475 A JP 2004317475A JP 2004317475 A JP2004317475 A JP 2004317475A JP 4276993 B2 JP4276993 B2 JP 4276993B2

- Authority

- JP

- Japan

- Prior art keywords

- error correction

- data

- decoding

- encoding

- node

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Error Detection And Correction (AREA)

- Detection And Prevention Of Errors In Transmission (AREA)

Description

遅延が生じる。

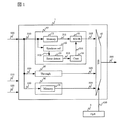

”後に、もとのデータ310と同一のデータ系列となるようにデータ311として読み出し、排他的論理和ゲート15に出力する。エラー訂正制御部14では入力されたエラー評価結果313にもとづいて、訂正データ314を排他的論理和ゲート15に出力する。訂正データ314は、メモリ11からエラーの存在する位置が出力されるタイミングでは該当するエラー値に論理的に等しく、エラーの存在しない位置が出力されるタイミングでは論理的に“ゼロ”である。排他的論理和ゲート15ではメモリ11からの出力データ311とエラー訂正制御部14からの訂正データ314との排他的論理和をデータ319として出力する。

がシンドローム計算部12に入力された時点から、符号化ブロックAに対する訂正データ314をエラー訂正制御部14が必ず出力できる時間であり、少なくとも符号化ブロックの周期以上であることが必要条件である。

、セレクタ内部では一切遅延を施さない。

では、この識別子を読み取ることで符号化されているか否かを判別することが可能となる。

場合、符号化されていると判定する。また、m回以上連続して“非符号化”に対応したパターン(上述の例では(00)hex)を検出した場合、符号化されてい

ないと判定する。そして上記のいづれでもない場合は直前迄の判定状態を維持するという具合である。ここでn、mは共に任意の自然数であり等しくてもよい。

ビットの計算は符号ブロック内の全ビットの値が入力された時点で完了する為、符号ブロックの最後の符号化対象ビット(図6では符号ブロックの末尾)を入力し終えた段階でチェックビットを出力開始するようにすれば符号化の遅延を最小にすることができる。

、符号ブロックの最後の符号化対象ビットがチェックビット領域の直前となる為

、“Tkmin”はゼロである。よって、 “Tk”はゼロでもよく、すなわちメモ

リ71、31は不要で、単なるスルー接続でよい。この“Tk”をゼロとする手法は一般的によく用いられる。

もよく、すなわちメモリ71、31は不要で、単なるスルー接続でよい。

、“Tk”がゼロの場合は、メモリ31も不要で、単なるスルー接続でよい。

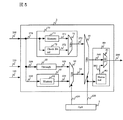

(AA)hexを発生し、符号化を行わない場合は(00)hexを発生する。セレクタ

81は、セレクタ40からの入力データ340が識別子の領域以外のタイミングでは入力データ340を選択して出力し、入力データ340が識別子の領域のタイミングでは識別パターン発生部82からのパターン信号382を選択して出力する。

ドと記す)と、符号化・復号化装置を具備しないノード(non−FECノードと記す

)とから構成される。また、エラー訂正はFECノード間でのみ可能であり、それ

以外のノード間では行えない。当然ではあるが、網を構成するノードが、全てFE

Cノードであってもよい。

と図1〜4のいづれかの復号化装置を適用できる。しかし、符号化装置、復号化装置は、これらの実施例に限られるわけではない。

延挿入と復号化オフ用の遅延挿入をオンに設定する。つまり、各FECノードが具

備する符号化装置及び復号化装置の各セレクタ50を、遅延出力部30からのデータ信号339を選択出力するように制御する。但し、図1の復号化装置を適用したFECノードに対してはセレクタ50が無い為、本設定は行えない。

手順を繰り返す。(S9−2,3)ノード番号iがFECノードかを判定し(S

9−4)、FECノードの場合符号化オフ用遅延および復号化オフ用遅延を挿入

し(S9−5)、符号化オフおよび復号化オフを設定する(S9−6)ことで、

初期設定する(S9−7)。

ドに対しては本設定は行えない。

。まず、エラー訂正を非実施から実施に切り替えるときは、まずノードiのノードjと対向する送信器の符号化をオンする(S10−1)。つぎにノードjのノ

ードiと対向する送信器の符号化をオンし(S10−2)、ノードiと対向する

受信器の復号化をオンする(S10−3)。この後、ノードiのノードjと対向

する受信器の復号化をオンする(S10−3)。

ノードiと対向する受信器の復号化をオフし(S10−6)、ノードiと対向す

る送信器の符号化をオフする(S10−7)。この後、ノードiのノードjと対

向する送信器の符号化をオフする(S10−8)。

すれば上記の一連の設定をプログラムが実行するという具合である。

入と共に全FECノードに対して符号化をオン状態に設定してもよい。このように

すれば、以降、各FECノードに対して復号化のオン・オフ切替のみを制御すれば

よく、符号化制御と復号化制御の順序考慮を必要とせず、網管理システムを簡易化することができる。

axになるまで以下の手順を繰り返す。(S11−2,3)ノード番号iがFE

Cノードかを判定し(S11−4)、FECノードの場合符号化オフ用遅延およ

び復号化オフ用遅延を挿入し(S11−5)、符号化オンおよび自動復号化オン

を設定する(S11−6)ことで、初期設定する(S11−7)。

この後、ノードjのノードiと対向する受信器の復号化をオンする(S12−2)

。この順序は逆でも良い。

ノードiと対向する受信器の復号化をオフする(S12−4)。この順序は逆で

も良い。

復号化装置を用いれば、網管理システムやオペレータが各FECノード毎に復号化

の選択を指定する必要もなくなり、初期設定のみの非常に簡易な網管理システムを実現できる。

、各FECノード毎に符号化のオン・オフ切替、復号化のオン・オフ切替を、該当

する伝送区間のエラーレートやエラー数にもとづいて設定してもよい。例えば予めエラーレートのしきい値を網管理システムに設定して記憶させておき、このしきい値に対して伝送区間のエラーレートが超過した場合にのみ、該当するFECノ

ードの復号をオン状態、あるいはオフ状態に設定するという具合にである。但し

、図3または図4に示した実施例の復号化装置を適用したFECノードに対しては

この制御は行えない。

)7と呼ばれるリングネットワークシステムに適用されるノードである。図で左側(West側)から伝送されてきた光信号は、受信器8−1で電気信号に変換されクロスコネクトスイッチ(Cross Connect Switch)500に送出される。同様に、右側(East側)から伝送されてきた光信号は、受信器8−2で電気信号に変換されクロスコネクト500に送出される。また、分配側から挿入される信号は、分配側インターフェース510からクロスコネクト500に送出される

。

、電気光変換部9−5とで構成されている。符号化装置2は、オペレーティングシステム3からの制御により、符号化の実施/非実施を切り替える。

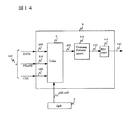

、200,310,311…データ信号、312…シンドローム,313…エラー評価結果、314…訂正データ、319…データ信号、320,329,330,339,340,360…データ信号、369…符号化識別結果、370,371…データ信号、372…チェックビット結果、379…データ信号、382…パターン信号、390…データ信号、391…検出エラーレート、395…セレクタ制御信号、400,410,420,430…外部制御信号、440…しきい値制御信号、500…多重分離スイッチ、510…被アッド・ドロップ信号インタフェース、Tm…復号化遅延時間、Tkmin…符号化遅延時間。

Claims (2)

- デジタル信号のエラー訂正が可能なエラー訂正装置において、

エラー訂正のため符号化されたデジタル信号を復号化して、前記デジタル信号のエラー訂正符号を生成するエラー訂正部と、

前記エラー訂正のため符号化されたデジタル信号を所定時間遅延させる遅延部と、

前記エラー訂正部および前記遅延部からそれぞれ出力されるエラー訂正符号およびデジタル信号を入力とし、一方を選択して出力する選択部と、

前記エラー訂正符号に含まれるエラーの数又は割合を検出し、前記エラーの数又は割合を

あらかじめ定められたしきい値と比較する計算部とを有し、

前記選択部は、前記計算部の比較の結果、前記検出されたエラーの数又は割合が前記しきい値よりも大きい場合に、前記エラー訂正符号を選択することを特徴とするエラー訂正装置。 - デジタル信号のエラー訂正が可能なエラー訂正装置において、

エラー訂正のため符号化されたデジタル信号を復号化して、前記デジタル信号のエラー訂正符号を生成するエラー訂正部と、

前記エラー訂正のため符号化されたデジタル信号を出力するスルー出力部と、

前記エラー訂正部および前記スルー出力部からそれぞれ出力されるエラー訂正符号およびデジタル信号を入力とし、一方を選択して出力する選択部と、

前記エラー訂正符号に含まれるエラーの数又は割合を検出し、前記エラーの数又は割合をあらかじめ定められたしきい値と比較する計算部とを有し、

前記選択部は、前記計算部の比較の結果、前記検出されたエラーの数又は割合が前記しきい値よりも大きい場合に、前記エラー訂正符号を選択することを特徴とするエラー訂正装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004317475A JP4276993B2 (ja) | 2004-11-01 | 2004-11-01 | エラー訂正符号装置、エラー訂正符号復号装置および伝送装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004317475A JP4276993B2 (ja) | 2004-11-01 | 2004-11-01 | エラー訂正符号装置、エラー訂正符号復号装置および伝送装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP19702399A Division JP3699863B2 (ja) | 1999-07-12 | 1999-07-12 | エラー訂正符号装置、エラー訂正符号復号装置および伝送装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005094793A JP2005094793A (ja) | 2005-04-07 |

| JP4276993B2 true JP4276993B2 (ja) | 2009-06-10 |

Family

ID=34464248

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004317475A Expired - Fee Related JP4276993B2 (ja) | 2004-11-01 | 2004-11-01 | エラー訂正符号装置、エラー訂正符号復号装置および伝送装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4276993B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4812546B2 (ja) * | 2005-06-30 | 2011-11-09 | 株式会社日立製作所 | 送信装置,受信装置及び通信システム |

| JP4749820B2 (ja) * | 2005-10-06 | 2011-08-17 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 誤りがない場合のレイテンシに影響を与えることなく誤り訂正機能を実装したインターコネクト通信 |

| US8122330B2 (en) * | 2007-08-06 | 2012-02-21 | Alcatel Lucent | Rate-adaptive forward error correction for optical transport systems |

| JP5698107B2 (ja) * | 2011-11-25 | 2015-04-08 | 株式会社日立製作所 | ネットワーク評価方法、および、ネットワーク評価システム |

-

2004

- 2004-11-01 JP JP2004317475A patent/JP4276993B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005094793A (ja) | 2005-04-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3699863B2 (ja) | エラー訂正符号装置、エラー訂正符号復号装置および伝送装置 | |

| US7512867B2 (en) | Method for encoding/decoding error correcting code, transmitting apparatus and network | |

| JP5378446B2 (ja) | 通信システム内のデータ通信方法 | |

| US6654562B1 (en) | Optical transmission system and optical transmission device | |

| US7957642B2 (en) | Efficient and simple bit error rate calculation on optical transport layer | |

| US6920603B2 (en) | Path error monitoring method and apparatus thereof | |

| JP4431113B2 (ja) | データ伝送方法及びデータ伝送装置 | |

| US10778570B2 (en) | Network protection method, network node and system | |

| US5204903A (en) | Secure communication equipment and secure transmission system | |

| US20030179783A1 (en) | Wavelength division multiplexing transmission system | |

| US20060098686A1 (en) | Frame transmitting apparatus and frame receiving apparatus | |

| JP4767676B2 (ja) | 光受信装置 | |

| JP4276993B2 (ja) | エラー訂正符号装置、エラー訂正符号復号装置および伝送装置 | |

| US6222892B1 (en) | Synchronization message reception processing apparatus | |

| US6961350B1 (en) | System and method for segmenting a multidimensional digital frame structure | |

| JP2005124194A (ja) | エラー訂正符号の構成方法、復号方法、伝送装置、ネットワーク | |

| GB2372337A (en) | Error checking circuit using selective connection of feedback nodes to perform error checks based on different mathematical functions | |

| GB2101852A (en) | Data transmission | |

| JP2001237815A (ja) | 伝送装置 | |

| JPH0321130A (ja) | 多重分離タイミング同期方式 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20060511 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20060511 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060703 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060703 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20081216 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090210 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090303 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090309 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120313 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120313 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |