JP4276258B2 - 速度とフレキシビリティを最大にするためにハードウエアとソフトウエアを用いてサンプルレートコンバータを実装するシステム及び方法 - Google Patents

速度とフレキシビリティを最大にするためにハードウエアとソフトウエアを用いてサンプルレートコンバータを実装するシステム及び方法 Download PDFInfo

- Publication number

- JP4276258B2 JP4276258B2 JP2006507404A JP2006507404A JP4276258B2 JP 4276258 B2 JP4276258 B2 JP 4276258B2 JP 2006507404 A JP2006507404 A JP 2006507404A JP 2006507404 A JP2006507404 A JP 2006507404A JP 4276258 B2 JP4276258 B2 JP 4276258B2

- Authority

- JP

- Japan

- Prior art keywords

- sample rate

- data stream

- sample

- input data

- rate converter

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F1/00—Details of amplifiers with only discharge tubes, only semiconductor devices or only unspecified devices as amplifying elements

- H03F1/52—Circuit arrangements for protecting such amplifiers

- H03F1/523—Circuit arrangements for protecting such amplifiers for amplifiers using field-effect devices

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/20—Power amplifiers, e.g. Class B amplifiers, Class C amplifiers

- H03F3/21—Power amplifiers, e.g. Class B amplifiers, Class C amplifiers with semiconductor devices only

- H03F3/217—Class D power amplifiers; Switching amplifiers

- H03F3/2171—Class D power amplifiers; Switching amplifiers with field-effect devices

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/20—Power amplifiers, e.g. Class B amplifiers, Class C amplifiers

- H03F3/21—Power amplifiers, e.g. Class B amplifiers, Class C amplifiers with semiconductor devices only

- H03F3/217—Class D power amplifiers; Switching amplifiers

- H03F3/2175—Class D power amplifiers; Switching amplifiers using analogue-digital or digital-analogue conversion

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03G—CONTROL OF AMPLIFICATION

- H03G7/00—Volume compression or expansion in amplifiers

- H03G7/007—Volume compression or expansion in amplifiers of digital or coded signals

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H17/00—Networks using digital techniques

- H03H17/02—Frequency selective networks

- H03H17/06—Non-recursive filters

- H03H17/0621—Non-recursive filters with input-sampling frequency and output-delivery frequency which differ, e.g. extrapolation; Anti-aliasing

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/0016—Arrangements for synchronising receiver with transmitter correction of synchronization errors

- H04L7/005—Correction by an elastic buffer

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/02—Speed or phase control by the received code signals, the signals containing no special synchronisation information

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/331—Sigma delta modulation being used in an amplifying circuit

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H2218/00—Indexing scheme relating to details of digital filters

- H03H2218/06—Multiple-input, multiple-output [MIMO]; Multiple-input, single-output [MISO]

Description

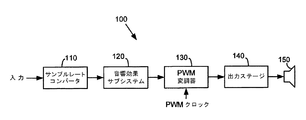

本発明は、一般的に音響増幅システムに関し、特に、第1のサンプルレートを有する入力データストリームを第2のデータレートを有する出力データストリームに変換するシステム及び方法に関する。

パルス幅変調(PWM)あるいはD級信号増幅技術は長年存在するが、スイッチドモード電源(SMPS)の増加に伴っていっそうポピュラーになってきている。この技術が現れてから、信号増幅アプリケーションにPWM技術を適用することへの関心が高まってきた。これは、少なくとも部分的に、昔の(リニアなAB級)電力出力トポロジィに代わるD級電力出力トポロジィの使用を通じて認識することができるかなりの効率改善の結果である。

上記に概要を説明した一又はそれ以上の問題点は、本発明の様々な実施例によって解決することができる。広く言えば、本発明は、ハードウエアとソフトウエア部品の組み合わせを用いてデジタル入力データストリームを第1のサンプルレートから第2のサンプルレートへ変換するシステムと方法を具える。一の実施例では、第1のサンプルレートから第2のサンプルレートへの変換が、デジタル音響システム用のサンプルレートコンバータ内で実行される。サンプルレートコンバータは複数の部品を有し、そのうちのいくつかはハードウエアに実装されており、いくつかはソフトウエアに実装されている。各部品をハードウエアに実装するかソフトウエアに実装するかは、部品の性能要求による。ソフトウエアでより優れた性能を実現する部品はソフトウエアに実装し、ハードウエアでより優れた性能を実現する部品はハードウエアに実装する。音響パフォーマンス手段の性能のみならず、コンピュータの複雑性、すなわちソフトウエアエンジンの部品の「適合性」における性能も改善することができる。

本発明の一又はそれ以上の実施例を以下に説明する。これらの実施例及び以下に述べるその他のすべての実施例は具体例であり、本発明を限定するものではなく明確化するためのものである。

各出力プットサイクルについて

ハードウエア係数計数器を初期化する

j=1 to Y について

o[Y] = 0; // アキュムレータを初期化する

p[Y] = start (N) // ポインタを初期化する

i=1 to X について // 各係数に対して

C=mem[coeff] // 係数を読み取る

j = 1 to Yについて // 各チャネルに対して

o[Y] += C*mem[p[Y]++]

Claims (20)

- サンプルレートコンバータにおいて:

2又はそれ以上のデータチャネルを処理する複数のサンプルレートコンバータ部品を具え;

前記部品の第1の部分がハードウエア部品を具え;

前記部品の第2の部分がソフトウエア部品を具え;

一又はそれ以上のサンプルレートコンバータ部品が2又はそれ以上のチャネル間で共用されており、一又はそれ以上のサンプルレートコンバータ部品が前記2又はそれ以上のチャネルによって共用されておらず;

前記2又はそれ以上のチャネルの各々が、他のチャネルによって処理される入力データストリームのサンプルレートから独立している可変のサンプルレートを有する入力データストリームを処理するように構成されていることを特徴とするサンプルレートコンバータ。 - 請求項1に記載のサンプルレートコンバータにおいて、各チャネルが独立したレートエスティメータを具えることを特徴とするサンプルレートコンバータ。

- 請求項2に記載のサンプルレートコンバータにおいて、各レートエスティメータが別々のサンプル周期カウンタを具えることを特徴とするサンプルレートコンバータ。

- 請求項3に記載のサンプルレートコンバータにおいて、各入力データストリームのサンプルレートが、共通のソフトウエア部品を用いて各サンプル期間カウンタを読み取ることによって決定されることを特徴とするサンプルレートコンバータ。

- 請求項3に記載のサンプルレートコンバータにおいて、前記チャネルのうちの一つが主チャネルであり、前記チャネルの残りが二次チャネルであり、サンプルレートが前記主チャネルについて予測され、各二次チャネルについては、前記主チャネルサンプル周期カウンタに対する対応サンプル期間カウンタの比が決定され、各二次チャネルのサンプルレートが前記主チャネルに前記比を掛けたものに対して予測されたサンプルレートであると決定されることを特徴とするサンプルレートコンバータ。

- 請求項1に記載のサンプルレートコンバータにおいて、各チャネルが多段階フィルタを実装しており、各多段階フィルタ実装の計数が共通のフィルタ係数セットから補間されることを特徴とするサンプルレートコンバータ。

- 請求項1に記載のサンプルレートコンバータにおいて、各チャネルについての前記部品が:

レートエスティメータと;

ローパスフィルタであって、前記エスティメータの出力が当該ローパスフィルタを通過するローパスフィルタと;

位相選択ユニットであって、前記ローパスフィルタの出力が当該位相選択ユニットに提供される位相選択ユニットと;

多相係数インターポレータであって、補間された多段階フィルタ係数セットを前記位相選択ユニットの出力に基づいて多相係数インターポレータによって発生する多相係数インターポレータと;

補間された多段階フィルタ係数に入力データストリームの対応するサンプルを重畳するように構成された重畳ユニットと;

入力データストリームのサンプルを受信して、入力データストリームのサンプルを前記重畳ユニットに提供するように構成された入力FIFOと;

前記重畳ユニットからの出力データストリームのサンプルを受信するように構成された出力FIFOと;

前記入力及び出力FIFOsに接続され、前記ローパスフィルタへフィードバックを提供するように構成されたFIFO管理ユニットと;

を具えることを特徴とするサンプルレートコンバータ。 - 請求項7に記載のサンプルレートコンバータにおいて、前記レートエスティメータと、前記ローパスフィルタと、前記多相係数インターポレータがハードウエアに実装されていることを特徴とするサンプルレートコンバータ。

- 請求項7に記載のサンプルレートコンバータにおいて、前記位相選択ユニットと、前記重畳ユニットと、前記FIFO管理ユニットがソフトウエアに実装されていることを特徴とするサンプルレートコンバータ。

- 請求項7に記載のサンプルレートコンバータにおいて、前記レートエスティメータが、前記入力データストリームのサンプル周期を計数するように構成されたカウンタを具え、入力サンプルレートが前記カウンタの値に基づいてソフトウエア部品で計算されることを特徴とするサンプルレートコンバータ。

- 請求項1に記載のサンプルレートコンバータにおいて、前記サンプルレートコンバータがパルス幅変調(PWM)音響増幅器に接続されており、各チャネルからの処理データをPWM変調器に提供するように構成されていることを特徴とするサンプルレートコンバータ。

- 独立した可変入力サンプルレートを有する2又はそれ以上の入力データストリームを予め決められた出力データレートを有する出力データストリームに変換する方法において、当該方法が:

複数の入力データストリームを受信するステップであって、各入力データストリームが、他の入力データストリームの入力サンプルレートから独立した可変の入力サンプルレートを有するステップと;

サンプルレートコンバータの少なくとも一のハードウエア部品と、サンプルレートコンバータの少なくとも一のソフトウエア部品を用いて前記入力データストリームを処理して、予め決められた出力サンプルレートを有する対応する出力データストリームを生成するステップであって、前記サンプルレートコンバータ部品の少なくともひとつが共用されており、前記サンプルレートコンバータ部品の少なくともひとつが共用されていないステップと;

を具えることを特徴とする方法。 - 請求項12に記載の方法が更に、前記各個別の入力サンプルレートを予測するステップを具えることを特徴とする方法。

- 請求項13に記載の方法において、前記入力サンプルレートを予測するステップが、前記第1の入力データストリーム中のサンプル周期のサイクル数を計数するステップと、このサンプル周期において計数したサイクル数から前記対応する入力サンプルレートを計算するステップとを具えることを特徴とする方法。

- 請求項14に記載の方法において、前記異なる入力データストリームについての入力サンプルレートの計算が単一のソフトウエア部品によって実行されることを特徴とする方法。

- 請求項12に記載の方法において、前記少なくとも一のハードウエア部品が多相係数インターポレータを具えることを特徴とする方法。

- 請求項12に記載の方法において、前記少なくとも一のソフトウエア部品が、多段階フィルタ係数セットを補間するための位相を選択する位相選択ユニットを具えることを特徴とする方法。

- 請求項12に記載の方法において、前記少なくとも一のソフトウエア部品が、補間した多段階フィルタ係数セットを前記第1の入力データストリームの対応するサンプルで重畳して前記第1の出力データストリームを生成する重畳ユニットを具えることを特徴とする方法。

- 請求項12に記載の方法において、各入力データストリームを処理するステップが:前記対応する入力サンプルレートを予測するステップと;多段階フィルタ係数セットの補間用の位相を選択するステップと;前記多段階フィルタ係数セットを補間するステップと;補間した多段階フィルタ係数セットを前記入力データストリームの一又はそれ以上のサンプルで重畳するステップと;前記対応する出力データストリームの結果としてのサンプルを提供するステップと;を具えることを特徴とする方法。

- 請求項19に記載の方法において、前記多段階フィルタ係数セットを補間するステップがハードウエアで実行され、前記補間した多段階フィルタ係数セットを各入力データストリームの一又はそれ以上のサンプルで重畳するステップがソフトウエアで実行されることを特徴とする方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US45642903P | 2003-03-21 | 2003-03-21 | |

| US46976103P | 2003-05-12 | 2003-05-12 | |

| PCT/US2004/008547 WO2004086611A2 (en) | 2003-03-21 | 2004-03-19 | Systems and methods for implementing a sample rate converter using hardware and software to maximize speed and flexibility |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007521716A JP2007521716A (ja) | 2007-08-02 |

| JP4276258B2 true JP4276258B2 (ja) | 2009-06-10 |

Family

ID=33101246

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006507404A Expired - Fee Related JP4276258B2 (ja) | 2003-03-21 | 2004-03-19 | 速度とフレキシビリティを最大にするためにハードウエアとソフトウエアを用いてサンプルレートコンバータを実装するシステム及び方法 |

Country Status (5)

| Country | Link |

|---|---|

| EP (1) | EP1609241B1 (ja) |

| JP (1) | JP4276258B2 (ja) |

| AT (1) | ATE381145T1 (ja) |

| DE (1) | DE602004010632T2 (ja) |

| WO (1) | WO2004086611A2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101433181B1 (ko) * | 2014-03-28 | 2014-08-27 | 삼성탈레스 주식회사 | 비등간격 채널에 적용 가능한 다상 채널 필터 구조의 위성 통신용 송/수신 방법 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2267193B (en) * | 1992-05-21 | 1995-09-27 | Sony Broadcast & Communication | Multi-tap oversampling filter |

| US5475628A (en) * | 1992-09-30 | 1995-12-12 | Analog Devices, Inc. | Asynchronous digital sample rate converter |

| US6061410A (en) * | 1997-02-27 | 2000-05-09 | Advanced Micro Devices | Frequency ratio estimation arrangement and method thereof |

| US5986589A (en) * | 1997-10-31 | 1999-11-16 | Ati Technologies, Inc. | Multi-stream audio sampling rate conversion circuit and method |

| US6134268A (en) * | 1998-10-19 | 2000-10-17 | Motorola, Inc. | Apparatus for performing a non-integer sampling rate change in a multichannel polyphase filter |

| US6531970B2 (en) * | 2001-06-07 | 2003-03-11 | Analog Devices, Inc. | Digital sample rate converters having matched group delay |

-

2004

- 2004-03-19 WO PCT/US2004/008547 patent/WO2004086611A2/en active IP Right Grant

- 2004-03-19 JP JP2006507404A patent/JP4276258B2/ja not_active Expired - Fee Related

- 2004-03-19 EP EP04757929A patent/EP1609241B1/en not_active Expired - Lifetime

- 2004-03-19 AT AT04757929T patent/ATE381145T1/de not_active IP Right Cessation

- 2004-03-19 DE DE602004010632T patent/DE602004010632T2/de not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| WO2004086611A2 (en) | 2004-10-07 |

| EP1609241A2 (en) | 2005-12-28 |

| DE602004010632D1 (de) | 2008-01-24 |

| JP2007521716A (ja) | 2007-08-02 |

| EP1609241B1 (en) | 2007-12-12 |

| ATE381145T1 (de) | 2007-12-15 |

| DE602004010632T2 (de) | 2008-12-11 |

| WO2004086611A3 (en) | 2005-01-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| USRE43489E1 (en) | Systems and methods for implementing a sample rate converter using hardware and software to maximize speed and flexibility | |

| US7970088B2 (en) | Systems and methods for sample rate conversion | |

| US7262716B2 (en) | Asynchronous sample rate converter and method | |

| US8405532B1 (en) | Asynchronous sample rate converter | |

| US5907295A (en) | Audio sample-rate conversion using a linear-interpolation stage with a multi-tap low-pass filter requiring reduced coefficient storage | |

| US7236110B2 (en) | Sample rate converter for reducing the sampling frequency of a signal by a fractional number | |

| US7411525B2 (en) | Sampling rate converting method and circuit | |

| WO1999050758A1 (en) | Efficient decimation filtering | |

| US20040263363A1 (en) | Rational sample rate conversion | |

| US9432043B2 (en) | Sample rate converter, an analog to digital converter including a sample rate converter and a method of converting a data stream from one data rate to another data rate | |

| JP2006197599A (ja) | 非同期サンプルレートコンバータ | |

| US7492848B2 (en) | Method and apparatus for efficient multi-stage FIR filters | |

| US20060212503A1 (en) | Multi-channel sample rate conversion method | |

| JP2006345508A (ja) | デジタル信号のサンプリング周波数を変換するための方法および装置 | |

| JPH07112144B2 (ja) | デジタル・フィルタ | |

| EP3704796B1 (en) | Low delay decimator and interpolator filters | |

| CN100511980C (zh) | 采样速率转换设备和方法 | |

| US7908306B1 (en) | SRC with multiple sets of filter coefficients in memory and a high order coefficient interpolator | |

| JP4276258B2 (ja) | 速度とフレキシビリティを最大にするためにハードウエアとソフトウエアを用いてサンプルレートコンバータを実装するシステム及び方法 | |

| US7292630B2 (en) | Limit-cycle-free FIR/IIR halfband digital filter with shared registers for high-speed sigma-delta A/D and D/A converters | |

| US6486813B1 (en) | Oversampling circuit digital/analog converter | |

| US7242326B1 (en) | Sample rate conversion combined with filter | |

| JP2009232079A (ja) | 補間フィルタ | |

| JP2002300007A (ja) | サンプリング周波数変換装置 | |

| US6778600B1 (en) | Method of filtering and apparatus therefore |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080826 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20081126 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20081203 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081212 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090203 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090305 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4276258 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120313 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120313 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130313 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130313 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140313 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |