以下、本発明の一実施形態を図面を参照して説明する。

まず、遊技機の一例であるパチンコ遊技機の全体の構成について説明する。図1はパチンコ遊技機1を正面からみた正面図、図2はパチンコ遊技機1の内部構造を示す全体背面図、図3はパチンコ遊技機1の機構盤を背面からみた背面図である。なお、ここでは、遊技機の一例としてパチンコ遊技機を示すが、本発明はパチンコ遊技機に限られず、例えばコイン遊技機等であってもよい。また、画像式の遊技機やスロット機に適用することもできる。

図1に示すように、パチンコ遊技機1は、額縁状に形成されたガラス扉枠2を有する。ガラス扉枠2の下部表面には打球供給皿3がある。打球供給皿3の下部には、打球供給皿3からあふれた景品玉を貯留する余剰玉受皿4と打球を発射する打球操作ハンドル(操作ノブ)5が設けられている。ガラス扉枠2の後方には、遊技盤6が着脱可能に取り付けられている。また、遊技盤6の前面には遊技領域7が設けられている。

遊技領域7の中央付近には、複数種類の図柄を可変表示するための可変表示部9と7セグメントLEDによる可変表示器10とを含む可変表示装置8が設けられている。この実施の形態では、可変表示部9には、「左」、「中」、「右」の3つの図柄表示エリアがある。可変表示装置8の側部には、打球を導く通過ゲート11が設けられている。通過ゲート11を通過した打球は、玉出口13を経て始動入賞口14の方に導かれる。通過ゲート11と玉出口13との間の通路には、通過ゲート11を通過した打球を検出するゲートスイッチ12がある。また、始動入賞口14に入った入賞球は、遊技盤6の背面に導かれ、始動口スイッチ17によって検出される。また、始動入賞口14の下部には開閉動作を行う可変入賞球装置15が設けられている。可変入賞球装置15は、ソレノイド16によって開状態とされる。

可変入賞球装置15の下部には、特定遊技状態(大当り状態)においてソレノイド21によって開状態とされる開閉板20が設けられている。この実施の形態では、開閉板20が大入賞口を開閉する手段となる。開閉板20から遊技盤6の背面に導かれた入賞球のうち一方(Vゾーン)に入った入賞球はVカウントスイッチ22で検出される。また、開閉板20からの入賞球はカウントスイッチ23で検出される。可変表示装置8の下部には、始動入賞口14に入った入賞球数を表示する4個の表示部を有する始動入賞記憶表示器18が設けられている。この例では、4個を上限として、始動入賞がある毎に、始動入賞記憶表示器18は点灯している表示部を1つずつ増やす。そして、可変表示部9の可変表示が開始される毎に、点灯している表示部を1つ減らす。

遊技盤6には、複数の入賞口19,24が設けられ、遊技球の入賞口19,24への入賞は入賞口スイッチ19a,24aによって検出される。遊技領域7の左右周辺には、遊技中に点滅表示される装飾ランプ25が設けられ、下部には、入賞しなかった打球を吸収するアウト口26がある。また、遊技領域7の外側の左右上部には、効果音を発する2つのスピーカ27が設けられている。遊技領域7の外周には、遊技効果LED28aおよび遊技効果ランプ28b,28cが設けられている。

そして、この例では、一方のスピーカ27の近傍に、景品玉払出時に点灯する賞球ランプ51が設けられ、他方のスピーカ27の近傍に、補給玉が切れたときに点灯する球切れランプ52が設けられている。さらに、図1には、パチンコ遊技台1に隣接して設置され、プリペイドカードが挿入されることによって球貸しを可能にするカードユニット50も示されている。

カードユニット50には、使用可能状態であるか否かを示す使用可表示ランプ151、カード内に記録された残額情報に端数(100円未満の数)が存在する場合にその端数を打球供給皿3の近傍に設けられる度数表示LEDに表示させるための端数表示スイッチ152、カードユニット50がいずれの側のパチンコ遊技機1に対応しているのかを示す連結台方向表示器153、カードユニット50内にカードが投入されていることを示すカード投入表示ランプ154、記録媒体としてのカードが挿入されるカード挿入口155、およびカード挿入口155の裏面に設けられているカードリーダライタの機構を点検する場合にカードユニット50を解放するためのカードユニット錠156が設けられている。

打球発射装置から発射された打球は、打球レールを通って遊技領域7に入り、その後、遊技領域7を下りてくる。打球が通過ゲート11を通ってゲートスイッチ12で検出されると、可変表示器10の表示数字が連続的に変化する状態になる。また、打球が始動入賞口14に入り始動口スイッチ17で検出されると、図柄の変動を開始できる状態であれば、可変表示部9内の図柄が回転を始める。図柄の変動を開始できる状態でなければ、始動入賞記憶を1増やす。

可変表示部9内の画像の回転は、一定時間が経過したときに停止する。停止時の画像の組み合わせが大当り図柄の組み合わせであると、大当り遊技状態に移行する。すなわち、開閉板20が、一定時間経過するまで、または、所定個数(例えば10個)の打球が入賞するまで開放する。そして、開閉板20の開放中に打球が特定入賞領域に入賞しVカウントスイッチ22で検出されると、継続権が発生し開閉板20の開放が再度行われる。継続権の発生は、所定回数(例えば15ラウンド)許容される。

停止時の可変表示部9内の画像の組み合わせが確率変動を伴う大当り図柄の組み合わせである場合には、次に大当りとなる確率が高くなる。すなわち、高確率状態という遊技者にとってさらに有利な状態となる。また、可変表示器10における停止図柄が所定の図柄(当り図柄)である場合に、可変入賞球装置15が所定時間だけ開状態になる。さらに、高確率状態では、可変表示器10における停止図柄が当り図柄になる確率が高められるとともに、可変入賞球装置15の開放時間と開放回数が高められる。

次に、パチンコ遊技機1の裏面の構造について図2を参照して説明する。

可変表示装置8の背面では、図2に示すように、機構板36の上部に景品玉タンク38が設けられ、パチンコ遊技機1が遊技機設置島に設置された状態でその上方から景品玉が景品玉タンク38に供給される。景品玉タンク38内の景品玉は、誘導樋39を通って玉払出装置に至る。

機構板36には、中継基板30を介して可変表示部9を制御する可変表示制御ユニット29、基板ケース32に覆われ遊技制御用マイクロコンピュータ等が搭載された遊技制御基板(主基板)31、可変表示制御ユニット29と主基板31との間の信号を中継するための中継基板33、および景品玉の払出制御を行う賞球制御用マイクロコンピュータ等が搭載された賞球制御基板(払出制御基板)37が設置されている。さらに、機構板36の下部には、モータの回転力を利用して打球を遊技領域7に発射する打球発射装置34と、遊技効果ランプ・LED28a,28b,28c、賞球ランプ51および球切れランプ52に信号を送るためのランプ制御基板35が設置されている。

また、図3はパチンコ遊技機1の機構盤を背面からみた背面図である。誘導樋39を通った玉は、図3に示されるように、球切れ検出器187a,187bを通過して玉供給樋186a,186bを経て玉払出装置97に至る。玉払出装置97から払い出された景品玉は、連絡口45を通ってパチンコ遊技機1の前面に設けられている打球供給皿3に供給される。連絡口45の側方には、パチンコ遊技機1の前面に設けられている余剰玉受皿4に連通する余剰玉通路46が形成されている。入賞にもとづく景品玉が多数払い出されて打球供給皿3が満杯になり、ついには景品玉が連絡口45に到達した後さらに景品玉が払い出されると景品玉は、余剰玉通路46を経て余剰玉受皿4に導かれる。さらに景品玉が払い出されると、感知レバー47が満タンスイッチ48を押圧して満タンスイッチ48がオンする。その状態では、玉払出装置97内のステッピングモータの回転が停止して玉払出装置97の動作が停止するとともに、必要に応じて打球発射装置34の駆動も停止する。

賞球払出制御を行うために、入賞口スイッチ19a,24a、始動口スイッチ17およびVカウントスイッチ22からの信号が、主基板31に送られる。主基板31のCPU56は、始動口スイッチ17がオンすると6個の賞球払出に対応した入賞が発生したことを知る。また、カウントスイッチ23がオンすると15個の賞球払出に対応した入賞が発生したことを知る。そして、入賞口スイッチがオンすると10個の賞球払出に対応した入賞が発生したことを知る。なお、この実施の形態では、例えば、入賞口24に入賞した遊技球は、入賞口24からの入賞球流路に設けられている入賞口スイッチ24aで検出され、入賞口19に入賞した遊技球は、入賞口19からの入賞球流路に設けられている入賞口スイッチ19aで検出される。

図4は、主基板31における回路構成の一例を示すブロック図である。なお、図4には、賞球制御基板37、ランプ制御基板35、音声制御基板70、発射制御基板91および表示制御基板80も示されている。主基板31には、プログラムに従ってパチンコ遊技機1を制御する基本回路53と、ゲートスイッチ12、始動口スイッチ17、Vカウントスイッチ22、カウントスイッチ23、満タンスイッチ48、玉切れスイッチ187a,187b(以下、玉切れスイッチ187と表現することがある。)および入賞口スイッチ19a,24aからの信号を基本回路53に与えるスイッチ回路58と、可変入賞球装置15を開閉するソレノイド16および開閉板20を開閉するソレノイド21を基本回路53からの指令に従って駆動するソレノイド回路59と、始動記憶表示器18の点灯および滅灯を行うとともに7セグメントLEDによる可変表示器10と装飾ランプ25とを駆動するランプ・LED回路60とが設けられている。

また、基本回路53から与えられるデータに従って、大当りの発生を示す大当り情報、可変表示部9の画像表示開始に利用された始動入賞球の個数を示す有効始動情報、確率変動が生じたことを示す確変情報等をホール管理コンピュータ等のホストコンピュータに対して出力する情報出力回路64を含む。

基本回路53は、ゲーム制御用のプログラム等を記憶するROM54、ワークメモリとして使用されるRAM55、制御用のプログラムに従って制御動作を行うCPU56およびI/Oポート部57を含む。この実施の形態では、ROM54,RAM55はCPU56に内蔵されている。すなわち、CPU56は、1チップマイクロコンピュータである。なお、1チップマイクロコンピュータは、少なくともRAM55が内蔵されていればよく、ROM54およびI/Oポート部57は外付けであってもよい。

さらに、主基板31には、電源投入時に基本回路53をリセットするための初期リセット回路65と、基本回路53から与えられるアドレス信号をデコードしてI/Oポート部57のうちのいずれかのI/Oポートを選択するための信号を出力するアドレスデコード回路67とが設けられている。

なお、玉払出装置97から主基板31に入力されるスイッチ情報もあるが、図4ではそれらは省略されている。

遊技球を打撃して発射する打球発射装置は発射制御基板91上の回路によって制御される駆動モータ94で駆動される。そして、駆動モータ94の駆動力は、操作ノブ5の操作量に従って調整される。すなわち、発射制御基板91上の回路によって、操作ノブ5の操作量に応じた速度で打球が発射されるように制御される。

図5は、表示制御基板80内の回路構成を、可変表示部9の一実現例であるCRT82および主基板31の出力ポート(ポートA,B)571,572および出力バッファ回路63とともに示すブロック図である。出力ポート571からは8ビットのデータが出力され、出力ポート572からは1ビットのストローブ信号(INT信号)が出力される。

表示制御用CPU101は、制御データROM102に格納されたプログラムに従って動作し、主基板31からノイズフィルタ107および入力バッファ回路105を介してストローブ信号が入力されると、入力バッファ回路105を介して表示制御コマンドを受信する。入力バッファ回路105として、例えば汎用ICである74HC244を使用することができる。なお、表示制御用CPU101がI/Oポートを内蔵していない場合には、入力バッファ回路105と表示制御用CPU101との間に、I/Oポートが設けられる。

そして、表示制御用CPU101は、受信した表示制御コマンドに従って、CRT82に表示される画面の表示制御を行う。具体的には、表示制御コマンドに応じた指令をVDP103に与える。VDP103は、キャラクタROM86から必要なデータを読み出す。VDP103は、入力したデータに従ってCRT82に表示するための画像データを生成し、その画像データをVRAM87に格納する。そして、VRAM87内の画像データは、R,G,B信号に変換され、D−A変換回路104でアナログ信号に変換されてCRT82に出力される。

なお、図5には、VDP103をリセットするためのリセット回路83、VDP103に動作クロックを与えるための発振回路85、および使用頻度の高い画像データを格納するキャラクタROM86も示されている。キャラクタROM86に格納される使用頻度の高い画像データとは、例えば、CRT82に表示される人物、動物、または、文字、図形もしくは記号等からなる画像などである。この実施の形態では、表示制御用CPU101は、1チップマイクロコンピュータであり、少なくともRAMが内蔵されている。

入力バッファ回路105は、主基板31から表示制御基板80へ向かう方向にのみ信号を通過させることができる。従って、表示制御基板80側から主基板31側に信号が伝わる余地はない。表示制御基板80内の回路に不正改造が加えられても、不正改造によって出力される信号が主基板31側に伝わることはない。なお、出力ポート571,572の出力をそのまま表示制御基板80に出力してもよいが、単方向にのみ信号伝達可能な出力バッファ回路63を設けることによって、主基板31から表示制御基板80への一方向性の信号伝達をより確実にすることができる。また、高周波信号を遮断するノイズフィルタ107として、例えば3端子コンデンサやフェライトビーズが使用されるが、ノイズフィルタ107の存在によって、表示制御コマンドに基板間でノイズが乗ったとしても、その影響は除去される。

図6は、主基板31における音声制御コマンドの信号送信部分および音声制御基板70の構成例を示すブロック図である。この実施の形態では、遊技進行に応じて、遊技領域7の外側に設けられているスピーカ27の音声出力を指示するための音声制御コマンドが、主基板31から音声制御基板70に出力される。

図6に示すように、音声制御コマンドは、基本回路53におけるI/Oポート部57の出力ポート(出力ポートC,D)573,574から出力される。出力ポート573からは8ビットのデータが出力され、出力ポート574からは1ビットのストローブ信号(INT信号)が出力される。音声制御基板70において、主基板31からの各信号は、入力バッファ回路705を介して音声制御用CPU701に入力する。なお、音声制御用CPU701がI/Oポートを内蔵していない場合には、入力バッファ回路705と音声制御用CPU701との間に、I/Oポートが設けられる。また、この実施の形態では、音声制御用CPU701は、1チップマイクロコンピュータであり、少なくともRAMが内蔵されている。

そして、例えばディジタルシグナルプロセッサによる音声合成回路702は、音声制御用CPU701の指示に応じた音声や効果音を発生し音量切替回路703に出力する。音量切替回路703は、音声制御用CPU701の出力レベルを、設定されている音量に応じたレベルにして音量増幅回路704に出力する。音量増幅回路704は、増幅した音声信号をスピーカ27に出力する。

入力バッファ回路705として、例えば、汎用のCMOS−ICである74HC244が用いられる。74HC244のイネーブル端子には、常にローレベル(GNDレベル)が与えられている。よって、各バッファの出力レベルは、入力レベルすなわち主基板31からの信号レベルに確定している。よって、音声制御基板70側から主基板31側に信号が伝わる余地はない。従って、音声制御基板70内の回路に不正改造が加えられても、不正改造によって出力される信号が主基板31側に伝わることはない。なお、入力バッファ回路705の入力側にノイズフィルタを設けてもよい。

また、主基板31において、出力ポート574,575の外側にバッファ回路67が設けられている。バッファ回路67として、例えば、汎用のCMOS−ICである74HC244が用いられる。イネーブル端子には常にローレベル(GNDレベル)が与えられている。このような構成によれば、外部から主基板31の内部に入力される信号が阻止されるので、音声制御基板70から主基板31に信号が与えられる可能性がある信号ラインをさらに確実になくすことができる。

図7は、主基板31およびランプ制御基板35における信号送受信部分を示すブロック図である。この実施の形態では、遊技領域7の外側に設けられている遊技効果LED28aおよび遊技効果ランプ28b,28cの点灯/消灯と、賞球ランプ51および球切れランプ52の点灯/消灯を示すランプ制御コマンドが出力される。

図7に示すように、ランプ制御に関するランプ制御コマンドは、基本回路53におけるI/Oポート部57の出力ポート(出力ポートE,F)575,576から出力される。出力ポート575は8ビットのデータを出力し、出力ポート576は1ビットのストローブ信号(INT信号)を出力する。ランプ制御基板35において、主基板31からの制御コマンドは、入力バッファ回路355を介してランプ制御用CPU351に入力する。なお、ランプ制御用CPU351がI/Oポートを内蔵していない場合には、入力バッファ回路355とランプ制御用CPU351との間に、I/Oポートが設けられる。また、この実施の形態では、ランプ制御用CPU351は、1チップマイクロコンピュータであり、少なくともRAMが内蔵されている。

ランプ制御基板35において、ランプ制御用CPU351は、各制御コマンドに応じて定義されている遊技効果LED28aおよび遊技効果ランプ28b,28cの点灯/消灯パターンに従って、遊技効果LED28aおよび遊技効果ランプ28b,28cに対して点灯/消灯信号を出力する。点灯/消灯信号は、遊技効果LED28aおよび遊技効果ランプ28b,28cに出力される。なお、点灯/消灯パターンは、ランプ制御用CPU351の内蔵ROMまたは外付けROMに記憶されている。

主基板31において、CPU56は、賞球時に賞球ランプ点灯を指示する制御コマンドを出力し、遊技盤裏面の遊技球補給路に設置されている球切れ検出センサがオンすると球切れランプ点灯を指示する制御コマンドを出力する。ランプ制御基板35において、各制御コマンドは、入力バッファ回路355を介してランプ制御用CPU351に入力する。ランプ制御用CPU351は、それらの制御コマンドに応じて、賞球ランプ51および球切れランプ52を点灯/消灯する。

入力バッファ回路355として、例えば、汎用のCMOS−ICである74HC244が用いられる。74HC244のイネーブル端子には、常にローレベル(GNDレベル)が与えられている。よって、各バッファの出力レベルは、入力レベルすなわち主基板31からの信号レベルに確定している。従って、ランプ制御基板35側から主基板31側に信号が伝わる余地はない。たとえ、ランプ制御基板35内の回路に不正改造が加えられても、不正改造によって出力される信号が主基板31側に伝わることはない。なお、入力バッファ回路355の入力側にノイズフィルタを設けてもよい。

図7に示された構成では、ランプ制御基板35から主基板31に信号が与えらる可能性がある信号ラインをなくすことができる。すなわち、主基板31からランプ制御基板35への信号の一方向性が確実になり、主基板31における遊技制御に対してランプ制御基板35が影響を及ぼす可能性がなくなる。この結果、例えば、ランプ制御基板35において、主基板31の基本回路53に大当りを生じさせるための不正信号を与えるような改造を行ったとしても、不正信号を主基板31に伝えることはできない。

さらに、主基板31において、出力ポート575,576の外側にバッファ回路62が設けられている。バッファ回路62として、例えば、汎用のCMOS−ICである74HC244が用いられる。イネーブル端子には常にローレベル(GNDレベル)が与えられている。このような構成によれば、外部から主基板31の内部に入力される信号が阻止されるので、ランプ制御基板35から主基板31に信号が与えらる可能性がある信号ラインをより確実になくすことができる。

なお、図7では、ランプ制御用CPU351の内蔵出力ポートから遊技効果LED28a、遊技効果ランプ28b,28c、賞球ランプ51および球切れランプ52に点灯または消灯を指示する信号が出力されているが、実際には、出力ポートと各ランプ・LEDとの間にドライバ回路が挿入されている。

図8は、賞球制御基板37および玉払出装置97の構成要素などの賞球に関連する構成要素を示すブロック図である。図8に示すように、満タンスイッチ48からの検出信号は、中継基板71を介して主基板31のI/Oポート57に入力される。満タンスイッチ48は、余剰玉受皿4の満タンを検出するスイッチである。なお、賞球制御基板37に搭載されている賞球制御用CPU371は、入賞にもとづく遊技球払出制御と玉貸し要求にもとづく遊技球払出制御とを行う払出制御手段を構成する。

球切れスイッチ187(187a,187b)からの検出信号は、中継基板72および中継基板71を介して主基板31のI/Oポート57に入力される。球切れ検出スイッチ167は景品玉タンク38内の補給玉の不足を検出するスイッチであり、球切れスイッチ187は、景品玉通路内の景品玉の有無を検出するスイッチである。

主基板31のCPU56は、球切れスイッチ187からの検出信号が球切れ状態を示しているか、または、満タンスイッチ48からの検出信号が満タン状態を示していると、球貸し禁止を指示する賞球制御コマンドを送出する。球貸し禁止を指示する賞球制御コマンドを受信すると、賞球制御基板37の賞球制御用CPU371は、球貸し処理を停止する。

さらに、賞球カウントスイッチ301Aからの検出信号も、中継基板72および中継基板71を介して主基板31のI/Oポート57に入力される。また、主基板31のI/Oポート57から入賞球排出ソレノイド127への駆動信号は、中継基板71を介して入賞球排出ソレノイド127に供給される。なお、賞球カウントスイッチ301Aは、玉払出装置97の賞球機構部分に設けられ、実際に払い出された賞球を検出する。

入賞があると、賞球制御基板37には、主基板31の出力ポート(ポートG,H)577,578から賞球個数を示す賞球制御コマンドが入力される。出力ポート577は8ビットのデータを出力し、出力ポート578は1ビットのストローブ信号(INT信号)を出力する。賞球個数を示す賞球制御コマンドは、入力バッファ回路373を介してI/Oポート372aに入力される。賞球制御用CPU371は、I/Oポート372aを介して賞球制御コマンドを入力し、賞球制御コマンドに応じて玉払出装置97を駆動して賞球払出を行う。なお、この実施の形態では、賞球制御用CPU371は、1チップマイクロコンピュータであり、少なくともRAMが内蔵されている。

入力バッファ回路373における各バッファは、主基板31から賞球制御基板37へ向かう方向にのみ信号を通過させることができる。従って、賞球制御基板37側から主基板31側に信号が伝わる余地はない。賞球制御基板37内の回路に不正改造が加えられても、不正改造によって出力される信号が主基板31側に伝わることはない。なお、入力バッファ回路373の入力側にノイズフィルタを設けてもよい。

また、主基板31において、賞球制御コマンドを出力する出力ポート577,578の外側にバッファ回路68が設けられている。このような構成によれば、外部から主基板31の内部に入力される信号が阻止されるので、賞球制御基板37から主基板31に信号が与えらる可能性がある信号ラインをより確実になくすことができる。

また、賞球制御用CPU371は、出力ポート372gを介して、貸し玉数を示す球貸し個数信号をターミナル基板160に出力し、ブザー駆動信号をブザー基板75に出力する。ブザー基板75にはブザーが搭載されている。さらに、出力ポート372eを介して、エラー表示用LED374にエラー信号を出力する。

さらに、賞球制御基板37の入力ポート372bには、中継基板72を介して、賞球カウントスイッチ301Aの検出信号および球貸しカウントスイッチ301Bの検出信号が入力される。球貸しカウントスイッチ301Bは、実際に貸し出された遊技球を検出する。賞球制御基板37からの払出モータ289への駆動信号は、出力ポート372cおよび中継基板72を介して玉払出装置97の賞球機構部分における払出モータ289に伝えられる。

カードユニット50には、カードユニット制御用マイクロコンピュータが搭載されている。また、カードユニット50には、端数表示スイッチ152、連結台方向表示器153、カード投入表示ランプ154およびカード挿入口155が設けられている(図1参照)。残高表示基板74には、打球供給皿3の近傍に設けられている度数表示LED、球貸しスイッチおよび返却スイッチが接続される。

残高表示基板74からカードユニット50には、遊技者の操作に応じて、球貸しスイッチ信号および返却スイッチ信号が賞球制御基板37を介して与えられる。また、カードユニット50から残高表示基板74には、プリペイドカードの残高を示すカード残高表示信号および球貸し可表示信号が賞球制御基板37を介して与えられる。カードユニット50と賞球制御基板37の間では、ユニット操作信号(BRDY信号)、球貸し要求信号(BRQ信号)、球貸し完了信号(EXS信号)およびパチンコ機動作信号(PRDY信号)がI/Oポート372fを介してやりとりされる。

パチンコ遊技機1の電源が投入されると、賞球制御基板37の賞球制御用CPU371は、カードユニット50にPRDY信号を出力する。カードユニット50においてカードが受け付けられ、球貸しスイッチが操作され球貸しスイッチ信号が入力されると、カードユニット制御用マイクロコンピュータは、賞球制御基板37にBRDY信号を出力する。この時点から所定の遅延時間が経過すると、カードユニット制御用マイクロコンピュータは、賞球制御基板37にBRQ信号を出力する。そして、賞球制御基板37の賞球制御用CPU371は、払出モータ289を駆動し、所定個の貸し玉を遊技者に払い出す。そして、払出が完了したら、賞球制御用CPU371は、カードユニット50にEXS信号を出力する。

以上のように、カードユニット50からの信号は全て賞球制御基板37に入力される構成になっている。従って、球貸し制御に関して、カードユニット50から主基板31に信号が入力されることはなく、主基板31の基本回路53にカードユニット50の側から不正に信号が入力される余地はない。なお、主基板31および賞球制御基板37には、ソレノイドおよびモータやランプを駆動するためのドライバ回路が搭載されているが、図8では、それらの回路は省略されている。

この実施の形態では、少なくとも主基板31において、RAMの一部が電源バックアップされている。すなわち、遊技機に対する電力供給が停止しても、バックアップRAM領域のデータは保存される。また、表示制御用CPU101、音声制御用CPU701、ランプ制御用CPU351および賞球制御用CPU371においても、RAMの一部が電源バックアップされるように構成されていてもよい。

図9は、主基板31、表示制御基板80、音声制御基板70、ランプ制御基板35および賞球制御基板37におけるCPU周りの構成を示すブロック図である。この例では、主基板31および賞球制御用CPU371において、CPU内蔵RAMの一部が、バックアップ端子にバックアップ電源が接続されることによって電源バックアップされている。

図9に示すように、主基板31において、電源監視用IC901は、+30V電圧を導入し、+30V電圧を監視することによって電源断の発生を検出する。具体的には、+30V電圧が所定値(例えば+22V)以下になったら、電源断が発生することを知らせるために、CPU56に割り込み信号を与える。CPU56において、この割り込みは、マスク不能割込(INT)端子に入力されている。また、NMI端子に入力される信号は、CPU56が内蔵する入力ポートにも入力されている。

電源監視用IC901が電源断を検知するための所定値は、通常時の電圧より低いが、CPU56が暫くの間動作しうる程度の電圧である。また、電源監視用IC901が、CPU56が必要とする電圧(この例では+5V)よりも高く、かつ、交流から直流に変換された直後の電圧を監視するように構成されているので、CPU56が必要とする電圧に対して監視範囲を広げることができる。従って、より精密な監視を行うことができる。さらに、監視電圧として+30Vを用いる場合には、遊技機の各種スイッチに供給される電圧が+12Vであることから、電源瞬断時のスイッチオン誤検出の防止も期待できる。すなわち、+30V電源の電圧を監視すると、+30V作成の以降に作られる+12Vが落ち始める以前の段階でそれの低下を検出できる。よって、+12V電源の電圧が低下するとスイッチ出力がオン状態を呈するようになるが、+12Vより早く低下する+30V電源電圧を監視して電源断を認識すれば、スイッチ出力がオン状態を呈する前に電源復旧待ちの状態に入ってスイッチ出力を検出しない状態となることができる。

賞球制御基板371において、電源監視用IC931は、+30V電圧を導入し、+30V電圧を監視することによって電源断の発生を検出する。具体的には、+30V電圧が上述した電源監視用IC901の検出時の電圧よりも低い電圧である所定値(例えば+22V)以下になったら、電源断が発生することを知らせるために、賞球制御用CPU371に割り込み信号を与える。賞球制御用CPU371において、この割り込みは、マスク不能割込(INT)端子に入力されている。また、NMI端子に入力される信号は、賞球制御用CPU371が内蔵する入力ポートにも入力されている。

なお、図9に示された構成では、電源監視用ICの出力がCPUのNMI端子に入力されているが、マスク可能割込端子(IRQ端子)に入力されていてもよい。また、電源監視用ICの出力はCPUの入力ポートにも入力されているが、割込端子にのみ入力されている構成であってもよい。さらに、音声制御基板70、ランプ制御基板35および表示制御基板80にも電源監視用IC901,931と同様のものが搭載され、+30V電圧が所定値以下になったら各CPUに信号を与えるように構成されていてもよい。

図9に示された構成において、電源監視用IC901が信号を出力することになる+30V電源の電圧は、電源監視用IC931が信号を出力することになる+30V電源の電圧と同じに設定されている。また、電源監視用IC901,931として同じ品種のICを用いる。従って、電源電圧が低下していくときに、賞球制御基板37の賞球制御用CPU371に対して、主基板31のCPU56にNMI割込がかかった時点と同じタイミングでNMI割込がかかる。後述するように、各CPUはNMIに応じて通常の制御を停止するので、遊技制御手段と払出制御手段とについて、電源状態に関する遊技進行制御の停止条件と払出制御の停止条件とは同じである。

従って、電源監視用IC901,931のばらつきに起因するタイミングのずれがないとした場合の実質的なNMI処理開始タイミングは、主基板31のCPU56と賞球制御用CPU371とで同じになる。すると、主基板31のCPU56と賞球制御用CPU371とは、実質的に同じ時期に、通常の制御処理を中断して電源断時の所定の処理(例えば、RAMの内容をバックアップ保存するための処理)を開始する。

よって、電源断の直前に主基板31のCPU56が送出した賞球制御コマンドが賞球制御用CPU371に受信されないといった不都合が生ずることはない。例えば、賞球制御用CPU371が早めに通常の制御処理を中断して電源断時の所定の処理を開始する場合には、電源断の直前に主基板31のCPU56が送出した賞球制御コマンドが賞球制御用CPU371に受信されなくなってしまう。しかし、この実施の形態では、そのような不都合は生じない。

さらに、主基板31には、リセットIC651を含む初期リセット回路65が搭載されている。初期リセット回路65は、電源投入時に、+5Vが立ち上がったことを検出すると、所定時間後(外付けの抵抗値とコンデンサ容量とで決まる時間)にリセット解除を示す信号を出力する。また、表示制御基板80、音声制御基板70、ランプ制御基板35および賞球制御基板37にも、同様の初期リセット回路が搭載されている。ただし、図9では、賞球制御基板37におけるリセットIC380を含む初期リセット回路のみが示されている。

なお、図9に示された構成において、主基板31の初期リセット回路65における抵抗およびコンデンサの抵抗値および容量は、他の制御基板におけるリセットIC380に外付けされている抵抗およびコンデンサの抵抗値および容量と等しい。すなわち、同一の構成となっている。従って、遊技機に電源投入されたときに、リセットIC651,380からのリセット信号は実質的に同時に立ち上がる。

主基板31において、初期リセット回路65の出力は、遅延回路655を介してCPU56のリセット端子に入力されている。従って、電源投入時に、主基板31のCPU56は、他の全ての基板におけるCPUよりも遅く立ち上がる。また、遅延回路655の出力は、2つのゲート回路656,657を介して出力ポート570のリセット端子に入力されている。出力ポート570は他の基板に対するコマンドを送出するポートであり、リセット信号がリセット解除状態を示すと、情報出力可能状態になる。なお、出力ポート570は、図5〜図8に示された出力ポート571〜578に対応したものである。

主基板31のCPU56が他の全ての基板におけるCPUよりも遅く立ち上がるので、他の基板におけるCPUの立ち上がりが完了してコマンド受信可能状態になってから、主基板31のCPU56は、コマンド送出可能状態になる。よって、電源投入後に遊技制御手段から直ちに他の電気部品制御手段に対してコマンドが送出されるように構成しても、そのコマンドは確実に他の制御手段において受信される。

なお、図9に示された構成では、電源断を監視するための電源監視手段が各基板に搭載されていたが、例えば後述する電源基板に電源監視手段を搭載し、そこから各基板に電圧低下を示す信号を供給するようにしてもよい。

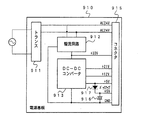

図10は、電源基板910の一構成例を示すブロック図である。電源基板910は、主基板31、表示制御基板80、音声制御基板70、ランプ制御基板35および賞球制御基板37等の制御基板と独立して設置され、遊技機内の各制御基板および機構部品が使用する電圧を生成する。この例では、AC24V、DC+30V、DC+21V、DC+12VおよびDC+5Vを生成する。また、バックアップ電源となるコンデンサ916は、DC+5Vすなわち各基板上のIC等を駆動する電源のラインから充電される。

トランス911は、交流電源からの交流電圧を24Vに変換する。AC24V電圧は、コネクタ915に出力される。また、整流回路912は、AC24Vから+30Vの直流電圧を生成し、DC−DCコンバータ913およびコネクタ915に出力する。DC−DCコンバータ913は、+21V、+12Vおよび+5Vを生成してコネクタ915に出力する。コネクタ915は例えば中継基板に接続され、中継基板から各制御基板および機構部品に必要な電圧の電力が供給される。

DC−DCコンバータ913からの+5Vラインは分岐してバックアップ+5Vラインを形成する。バックアップ+5Vラインとグラウンドレベルとの間には大容量のコンデンサ916が接続されている。コンデンサ916は、遊技機に対する電力供給が遮断されたときの各制御基板におけるバックアップRAM領域に対するバックアップ電源となる。また、+5Vラインとバックアップ+5Vラインとの間に、逆流防止用のダイオード917が挿入される。

なお、バックアップ電源として、+5V電源から充電可能な電池を用いてもよい。電池を用いる場合には、+5V電源から電力供給されない状態が所定時間継続すると容量がなくなるような充電池が用いられる。

主基板および電気部品制御基板に、第2の電源監視回路を搭載してもよい。第2の電源監視回路は、例えば、第1の電源監視回路(電源監視用IC901,931)が監視する電源電圧と等しい電源電圧である+30V電源電圧を監視して電圧値が所定値以下になるとローレベルの電圧低下信号を発生する。そして、例えば、第1の電源監視回路の検出電圧(電圧低下信号を出力することになる電圧)を+22Vとし、第2の電源監視回路の検出電圧を+9Vとする。

さらに、第2の電源監視回路からの電圧低下信号が、リセットIC651,380からの初期リセット信号と論理和をとられた後に、CPUのリセット端子に入力されるように構成する。従って、CPUは、初期リセット信号がローレベルを呈しているとき、または、第2の電源監視回路からの電圧低下信号がローレベルを呈しているときに、リセット状態(非動作状態)になる。

そのように構成した場合には、第1の電源監視回路からの検出信号に応じてCPUが所定の電力供給停止時処理を行った後に、CPUはシステムリセットされる。従って、電源電圧低下時の電圧不安定状態においてCPUはシステムリセットされ、CPU暴走等の危険が回避される。そして、同一の電圧を監視するので、第1の電圧監視回路が電圧低下信号を出力するタイミングと第2の電圧監視回路が電圧低下信号を出力するタイミングの差を所望の所定期間に確実に設定することができる。所望の所定期間とは、第1の電源監視回路からの電圧低下信号に応じて電力供給停止時処理を開始してから電力供給停止時処理が確実に完了するまでの期間である。

次に遊技機の動作について説明する。

遊技機に電源が投入されたときには、図9に示された主基板31の初期リセット回路65において、抵抗を介してコンデンサが充電されていく。従って、コンデンサの電位が上昇していく。コンデンサの電位が所定値を越えると、図9に示すように、リセットIC651は、出力レベルをローレベルからハイレベルに変化させる。遅延回路655は、リセットIC651の出力を遅延させてCPU56にリセット信号として供給する。従って、CPU56には、図11に示すように、初期リセット回路65の出力信号立ち上がり時点よりも遅れた時点までローレベルのリセット信号が与えられ、その後リセット信号はハイレベルに立ち上がる。すなわち、その時点でCPU56のリセットは解除される。

なお、遅延回路655における遅延量は、例えば、各制御基板におけるCPUが初期化プログラムの実行が完了しないうちに遊技制御手段からコマンドが送出されないような量に設定される。

主基板31以外の各電気部品制御基板において、遅延回路は設けられていないので、各CPUに入力されるリセット信号は早めに立ち上がっている。すなわち、各CPUは、主基板31のCPU56よりも早めに動作可能状態になっている。従って、遊技機の電源オン直後に主基板31のCPU56が送出したコマンドを各電気部品制御手段が受信できないという状況は生じない。

図12は、主基板31におけるCPU56の遊技制御処理を示すフローチャートである。図12(A)はCPU56が実行するメイン処理を示し、図12(B)は割込処理を示す。電源オン時のリセットが解けると、CPU56は、まず、クロックモニタ制御を動作可能状態にするために、内蔵されているクロックモニタレジスタをクロックモニタイネーブル状態に設定する(ステップS1)。クロックモニタ制御とは、入力されるクロック信号の低下または停止を検出すると、CPU56の内部で自動的にリセットを発生する制御である。次いで、CPU56は、初期化処理を行う(ステップS2)。なお、初期化処理では、所定期間後(例えば2ms後)にタイマ割込がかかるようにタイマの設定処理を行う。その後、停止図柄の種類を決定する乱数等の表示用乱数を更新する処理を繰り返し実行する(ステップS17)。

図12(B)に示された処理は、CPU56内部のタイマ割込によって起動される。割込処理において、CPU56は、まず、所定期間後(例えば2ms後)に再度タイマ割込がかかるようにタイマの設定処理を行う(ステップS20)。

次に、表示制御基板80に送出される表示制御コマンドをRAM55の所定の領域に設定する処理を行った後に(表示制御データ設定処理:ステップS4)、表示制御コマンドを出力する処理を行う(表示制御データ出力処理:ステップS5)。

次いで、各種出力データの格納領域の内容を各出力ポートに出力する処理を行う(データ出力処理:ステップS6)。また、ホール管理用コンピュータに出力される大当り情報、始動情報、確率変動情報などの出力データを格納領域に設定する出力データ設定処理を行う(ステップS8)。さらに、パチンコ遊技機1の内部に備えられている自己診断機能によって種々の異常診断処理が行われ、その結果に応じて必要ならば警報が発せられる(エラー処理:ステップS9)。

次に、遊技制御に用いられる大当り判定用の乱数等の各判定用乱数を示す各カウンタを更新する処理を行う(ステップS10)。

次に、CPU56は、特別図柄プロセス処理を行う(ステップS11)。特別図柄プロセス制御では、遊技状態に応じてパチンコ遊技機1を所定の順序で制御するための特別図柄プロセスフラグに従って該当する処理が選び出されて実行される。そして、特別図柄プロセスフラグの値は、遊技状態に応じて各処理中に更新される。また、普通図柄プロセス処理を行う(ステップS12)。普通図柄プロセス処理では、7セグメントLEDによる可変表示器10を所定の順序で制御するための普通図柄プロセスフラグに従って該当する処理が選び出されて実行される。そして、普通図柄プロセスフラグの値は、遊技状態に応じて各処理中に更新される。

さらに、CPU56は、スイッチ回路58を介して、ゲートセンサ12、始動口センサ17およびカウントセンサ23の状態を入力し、各入賞口や入賞装置に対する入賞があったか否か判定する(スイッチ処理:ステップS13)。CPU56は、さらに、停止図柄の種類を決定する乱数等の表示用乱数を更新する処理を行う(ステップS15)。

また、CPU56は、賞球制御基板37との間の信号処理を行う(ステップS16)。すなわち、所定の条件が成立すると賞球制御基板37に賞球制御コマンドを出力する。賞球制御基板37に搭載されている賞球制御用CPUは、賞球制御コマンドに応じて玉払出装置97を駆動する。

なお、この実施の形態では2msタイマ割込処理でステップS20およびS4〜S16の遊技制御処理が実行されるが、タイマ割込処理ではタイマ割込があったことを示すフラグセットのみを行い、メイン処理でそのフラグを監視してフラグがオンしたら遊技制御処理を実行するようにしてもよい。

図13は、CPU56のNMI割込処理を示すフローチャートである。上述したように、電源監視用IC901が電源電圧の低下を検出すると、CPU56にNMI割込がかかる。なお、この実施の形態では、図13に示す処理が電力供給停止時処理に相当する。

電源電圧の低下にもとづくNMI割込処理では、CPU56は、まず、レジスタの内容をバックアップRAMに転送する(ステップS31)。次いで、NMIフラグをセットする(ステップS32)。NMIフラグとは、電源電圧低下にもとづく割込が生じたことを示す内部フラグである。また、NMIフラグは、バックアップRAM領域に設定される。CPU56は、さらに、RAMアクセスを禁止状態にして(ステップS33)、電源監視用IC901の出力が導入されている入力ポートのレベルを監視し続ける(ステップS34)。この状態で、電源電圧はさらに低下していき、遂には、CPU56の動作が停止する。

しかし、入力ポートのレベルが通常時のレベルに復帰した場合には、CPU56は、RAMアクセスを許可状態にして(ステップS35)、バックアップRAMに保存されていたレジスタ値を本来のレジスタに復帰させる(ステップS36)。そして、NMIフラグをリセットし(ステップS37)、NMI割込がかかったアドレスに復帰する。

このように、CPU56は、電源電圧が正常に復帰したことを検出すると、レジスタの状態を元に戻してNMI割込がかかったアドレスに復帰する。従って、NMIラインにノイズ等がのった場合でも、制御を正常状態に復帰させることができる。

ただし、ステップS34の入力ポート監視処理を行わなくてもよい。その場合には、RAMアクセス禁止にした後にプログラムをループ状態とするか、またはHALT(ホールト)命令を発行する。また、入力ポート監視処理を行わない場合には、図9に示された構成において、NMI信号をCPUの入力ポートに接続する必要はない。

図11に示されているように、主基板31の電源監視用IC901が+30Vの電圧低下を検出する時点は、賞球制御基板における電源監視用IC931が+30Vの電圧低下を検出する時点と同じである。すなわち、主基板31のCPU56がNMI処理を開始する時点では、賞球制御用CPU371もNMI処理を開始する。そして、CPU56のNMI処理では、ステップS34でループしているので、新たなコマンド送出が開始されることはない。従って、賞球制御用CPU371は、電源が断するときに、主基板31からのコマンドが受信できなくなるという状況に陥ることはない。

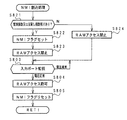

図14は、図12に示されたメイン処理における初期化処理(ステップS2)の一例を示すフローチャートである。遊技機への電力供給が再開されると、初期リセット回路65からCPU56にリセット信号が入力される。CPU56は、初期リセット信号に応じてメイン処理を開始するのであるが、システムチェック処理において、まず、NMIフラグがセットされているか否か確認する(ステップS42)。

NMIフラグがセットされていなければ、レジスタおよびRAM領域を全てクリアし(ステップS46)、必要な初期値を設定する(ステップS47)。そして、電源投入時画面表示コマンド送出要求をセットし(ステップS48)、スタックポインタを初期化して(ステップS49)、初期化処理を終了する。

なお、電源投入時画面表示コマンド送出要求がセットされると、例えば、図12に示された表示制御データ出力処理(ステップS5)によって電源投入時画面表示コマンドが表示制御基板80に送出される。表示制御基板80における表示制御用CPU101は、電源投入時画面表示コマンドを受信すると、可変表示部9に、電源投入時に表示される画面としてあらかじめ決められている画面を表示する。

ステップS42でNMIフラグがセットされていることが確認されると、CPU56は、バックアップRAMに保存されていたレジスタ値を本来のレジスタに復帰させる(ステップS43)。そして、NMIフラグをリセットし(ステップS44)、エラー画面表示コマンド送出要求をセットする(ステップS45)。

なお、エラー画面表示コマンド送出要求がセットされると、例えば、表示制御データ出力処理(ステップS5)によってエラー画面表示コマンドが表示制御基板80に送出される。表示制御基板80における表示制御用CPU101は、電源投入時画面表示コマンドを受信すると、可変表示部9にあらかじめ決められているエラー画面を表示する。

そして、CPU56は、スタックポインタが指すスタックエリアの値をジャンプ先としてそこにジャンプする。スタックポインタは、レジスタの一つであるから、ステップS43の処理によって、電源断したときの値に復元されている。また、この実施の形態では、スタックエリアはバックアップRAM領域に形成されている。すなわち、電源断中でも保存されている。従って、制御状態は、電源断時の状態に戻る。

例えば、電源断時に、表示制御基板80における表示制御用CPU101が可変表示部9において図柄変動表示を行っていたとする。すると、電源復旧時に、表示制御用CPU101は、エラー画面表示コマンドを受信するので、可変表示部9にエラー画面を表示する。一方、主基板31のCPU56は、電源断時の状態すなわち特別図柄変動中の遊技状態に戻る。そして、特別図柄変動中の遊技状態が終了すると、図柄停止を示すコマンドや大当り表示を示すコマンドを送出する。表示制御用CPU101は、その段階で、エラー表示を停止して、続く表示制御を続行することができる。

以上のように、CPU56は、復帰時にNMIフラグがセットされていたらデータ復帰処理を行い、NMIフラグがセットされていなければ通常の初期設定処理(ステップS46,S47)を行う。そして、データ復帰処理では、保存されていたレジスタの復帰処理とNMIフラグのリセット処理とが行われる。また、電源バックアップされているRAM領域におけるスタックエリアに保存されていた復帰アドレスに戻るので、遊技制御手段は、電源断時の遊技状態に復帰することができる。

なお、この実施の形態では、電源投入時に、NMIフラグがセットされているか否かによって初期化処理を行うのか状態復帰処理を行うのかを決定したが、電源断時のNMI処理においてパリティチェックデータを算出して電源バックアップされているRAM領域に格納し、電源投入時に、NMIフラグがオンしていたら、パリティチェックデータにもとづくチェックを行ってデータが正しく保存されていたら状態復帰処理を行うように構成してもよい。

また、上記の実施の形態では、主基板31の初期リセット回路65における抵抗およびコンデンサの抵抗値および容量は、他の電気部品制御基板におけるリセットIC380に外付けされている抵抗およびコンデンサの抵抗値および容量とは、等しい値に設定されていた。しかし、初期リセット回路65におけるコンデンサの容量を、他の電気部品制御基板におけるコンデンサの容量よりも大きくしてもよい。そのように構成した場合には、初期リセット回路65のリセットIC651からのリセット信号の立ち上がり時点は、他の電気部品制御基板におけるリセットIC380からのリセット信号の立ち上がり時点よりも遅くなる。従って、遅延回路655をなくして、初期リセット回路65の出力をそのままCPU56に供給しても、主基板31のCPU56が、他の全ての基板におけるCPUよりも遅く立ち上がるようにすることができる。

主基板31のCPU56は、リセット解除後に、遊技制御プログラムに先立って所定のセキュリティチェックプログラムを実行するように構成されることもある。セキュリティチェックプログラムの実行にある程度の時間がかかるのであれば、その時間を利用して電源投入時の他の電気部品制御基板における各CPUのリセット解除を早くすることができる。図15は、そのような考え方にもとづく他の実施の形態を示すブロック図である。

この場合には、主基板31において遅延回路655は設けられず、また、初期リセット回路65の出力は直接CPU56のリセット入力端子に接続される。そして、主基板31の初期リセット回路65における抵抗およびコンデンサの抵抗値および容量は、他の電気部品制御基板におけるリセットIC380に外付けされている抵抗およびコンデンサの抵抗値および容量と等しい値に設定される。ただし、主基板31のCPU56がセキュリティチェックプログラムの実行を完了するまでに、他の電気部品制御基板におけるCPUが立ち上がって初期化プログラムの実行を完了するのであれば、他の電気部品制御基板のコンデンサの抵抗値および容量は、主基板31のコンデンサの抵抗値および容量と等しくなくてもよい。

従って、図16に示すように、主基板31のCPU56と他の電気部品制御基板の各CPUとは、ほぼ同時にリセット解除される。CPU56は、リセット解除されると、まず、セキュリティチェックプログラムを実行する。セキュリティチェックプログラムが実行されている間、他の電気部品制御基板に対するコマンドがCPU56から出力されることはない。セキュリティチェックプログラムの実行に十分な時間がかかるのであれば、その間に、他の電気部品制御基板の各CPUは、初期化プログラムの実行を終えている。よって、コマンドを待っている状態になる。

この実施の形態では、図16に示すように、セキュリティチェックプログラムの実行完了時が実質的なCPU56のリセット解除タイミングとなっている。従って、この実施の形態でも、遊技機の電源投入後、各電気部品制御手段における各CPUのリセット解除のタイミングは、遊技制御手段におけるCPU56のリセット解除のタイミングよりも実質的に早くなっている。よって、各電気部品制御手段における初期化プログラムの実行が完了しないうちに遊技制御手段からコマンドが送出されて各電気部品制御手段がコマンドデータを取り損なうという事態は生じない。

以上のように、上記の各実施の形態では、電源投入時には、主基板31のCPU56が他の全ての電気部品制御手段の各CPUよりも遅く立ち上がるように構成したので、他の電気部品制御手段の各CPUが、主基板31からのコマンドを受信できなる可能性をなくすことができる。

なお、電源投入時に、主基板31のCPU56が、他の電気部品制御基板にコマンドを送出する前に、ソフトウェアで遅延時間を設けることによって、実質的に、主基板31のCPU56が他の電気部品制御手段の各CPUよりも遅く立ち上がるようにしてもよい。

また、少なくとも、遊技機の電源断時に、主基板31のCPU56に電源断を示す割込がかかるタイミングと賞球制御用CPU371に電源断を示す割込がかかるタイミングとを実質的に同じにしたので、電源断直前に送出されたコマンドが受信側で受信できない可能性が低減される。

以下、遊技制御手段以外の各電気部品制御手段における電力供給停止時処理について説明する。ここでは、賞球制御手段を例にするが、NMI割込処理を実行する他の制御手段も同様の処理を行う。なお、この実施の形態では、NMI割込処理が電力供給停止時処理に相当する。図17に示すように、賞球制御用CPU371は、まず、NMIフラグをセットする(ステップS801)。また、RAMアクセスを禁止状態にして(ステップS802)、電源監視用IC931の出力が導入されている入力ポートのレベルを監視し続ける(ステップS803)。

入力ポートのレベルが通常時のレベルに復帰した場合には、賞球制御用CPU371は、RAMアクセスを許可状態にして(ステップS804)、NMIフラグをリセットし(ステップS805)、NMI割込がかかったアドレスに復帰する。

このように、賞球制御用CPU371は、電源電圧が正常に復帰したことを検出すると、レジスタの状態を元に戻してNMI割込がかかったアドレスに復帰する。従って、NMIラインにノイズ等がのった場合でも、制御を正常状態に復帰させることができる。

ただし、ステップS803の入力ポート監視処理を行わなくてもよい。その場合には、RAMアクセス禁止にした後にプログラムをループ状態とするか、またはHALT(ホールト)命令を発行する。また、入力ポート監視処理を行わない場合には、図9や図15に示された構成において、NMI信号を賞球制御用CPU371の入力ポートに接続する必要はない。

図18は、賞球制御用CPU371が実行するメイン処理における初期化処理を示すフローチャートである。この場合には、賞球制御用CPU37は、まず、NMIフラグがセットされているか否か確認する(ステップS812)。セットされていなければ、レジスタおよびRAM領域を全てクリアし(ステップS814)、必要な初期値を設定する(ステップS815)。そして、スタックポインタを初期化して(ステップS816)、初期化処理を終了する。

ステップS812でNMIフラグがセットされていることが確認されると、CPU56は、NMIフラグをリセットし(ステップS813)、スタックポインタが指すスタックエリアの値をジャンプ先としてそこにジャンプする。なお、この実施の形態では、汎用の各レジスタの値を電源断時にバックアップRAMに保存する必要はないが、少なくともスタックポインタは保存される必要がある。また、スタックエリアはバックアップRAM領域に形成されているので、賞球制御用CPU371は、電源投入時にNMIフラグがセットされていることを検出することによって、確実に電源断時の制御状態に戻ることができる。

例えば、賞球中フラグがバックアップRAM領域に形成されていれば、賞球中を示すフラグが設定されていることを検知して、賞球制御用CPU371は、直ちに、バックアップRAM領域に保存されている各個数カウンタの値にもとづいて賞球払出処理を再開することができる。

フラグ類がバックアップRAM領域に設定されていなくても、個数カウンタがバックアップRAM領域に設定されていれば、賞球制御用CPU371は、電源復旧時に、遊技状態記憶の読み出し処理を行って、すなわち、各個数カウンタの設定値を読み出して、未払出賞球があるか否かを検出することができる。そして、未払出賞球があることを検出した場合には、例えば、賞球払出中フラグをセットすることによって賞球払出処理を再開することができる。

図19は、賞球制御用CPU371が実行するNMI割込処理の他の例を示すフローチャートである。この場合には、賞球制御用CPU371は、まず、未払出賞球個数または未払出玉貸し個数が記憶されているか否か確認する(ステップS821)。そのような記憶があれば、NMIフラグをセットする(ステップS822)。また、RAMアクセスを禁止状態にして(ステップS823)、電源監視用IC931の出力が導入されている入力ポートのレベルを監視し続ける(ステップS803)。

入力ポートのレベルが通常時のレベルに復帰した場合には、賞球制御用CPU371は、RAMアクセスを許可状態にして(ステップS804)、NMIフラグをリセットし(ステップS805)、NMI割込がかかったアドレスに復帰する。

未払出賞球個数または未払出玉貸し個数の記憶がない場合には、RAMアクセスを禁止状態にして(ステップS823)、ステップS803に移行する。このような制御によれば、未払出状態のときに電源断が生じた場合にのみ、すなわち、必要な場合にのみ、電源復旧時の制御状態復帰のための準備が行われる。

なお、上記の各実施の形態では、電源断時に、各電気部品制御手段において電源監視用ICからのNMI割込にもとづく処理が行われる場合を例示したが、必要な電気部品制御基板においてのみ電源監視用ICが搭載されるように構成してもよい。また、上記の各実施の形態では、NMI割込を例示したが、マスク不能でない外部割込(INT)端子に電源電圧低下を示す信号を導入して、INT端子の割込信号にもとづく割込処理を行ってもよい。

また、賞球制御手段におけるRAMと同様に、音声制御手段、ランプ制御手段および表示制御手段におけるRAMも、電源バックアップされる部分があるようにしてもよい。

なお、上記の各実施の形態に開示されているように、遊技機は、以下のように構成されていてもよい。

遊技制御手段と払出制御手段とは、電力供給が停止する際に所定の電力供給停止時処理を行い、遊技制御手段に電力供給停止時処理を開始させるための電源状態と払出制御手段に電力供給停止時処理を開始させるための電源状態とは同じであるように構成されていてもよい。

遊技機で使用される所定電位電源を監視し検出条件が成立した場合に検出信号を出力する電源監視手段を備え、遊技制御手段および払出制御手段が、電源監視手段からの検出信号に応じて電力供給停止時処理を行うように構成されていてもよい。

遊技制御手段および払出制御手段は、電源監視手段の検出信号を受けた場合に、割込処理で電力供給停止時処理を実行するように構成されていてもよい。

遊技制御基板には、バックアップ用電源によって電力供給断時でも所定時間電力供給停止直前の内容を保持することが可能な記憶手段が設けられ、記憶手段には電力供給が復旧したときに遊技状態を復元するために必要な情報が保持されるように構成されていてもよい。

電力供給停止直前の内容を保持することが可能な記憶手段は、遊技制御手段に含まれている構成であってもよい。すなわち、記憶手段は、例えば、遊技制御マイクロコンピュータに内蔵されているメモリ(RAM)であってもよい。

払出制御手段が搭載された払出制御基板には、バックアップ用電源によって電力供給断時でも所定時間電力供給停止直前の内容を保持することが可能な記憶手段が設けられ、記憶手段には電力供給が復旧したときに払出状態を復元するために必要な情報が保持されるように構成されていてもよい。

電力供給停止直前の内容を保持することが可能な記憶手段は、払出制御手段に含まれている構成であってもよい。すなわち、記憶手段は、例えば、払出制御マイクロコンピュータに内蔵されているメモリ(RAM)であってもよい。

遊技制御基板および払出制御基板には、遊技制御手段および払出制御手段に対してリセット信号を出力する初期リセット手段が搭載され、初期リセット手段からのリセット信号を遅延させて遊技制御手段に供給する遅延手段を備えていてもよい。

遊技制御基板および払出制御基板には、遊技制御手段および払出制御手段に対してリセット信号を出力する初期リセット手段が搭載され、遊技制御基板の初期リセット手段におけるリセット信号を作成するためのコンデンサの容量は、払出制御基板の初期リセット手段におけるリセット信号を作成するためのコンデンサの容量よりも大きい構成であってもよい。

遊技制御基板および払出制御基板には、遊技制御手段および払出制御手段に対してリセット信号を出力する初期リセット手段が搭載され、遊技制御手段はパワーオンリセット解除時に所定のプログラムを実行するものであって、遊技制御基板における初期リセット手段と払出制御基板における初期リセット手段とは同一構成であるように構成されていてもよい。

遊技制御手段に電力供給停止時処理を開始させるための電源状態と払出制御手段に電力供給停止時処理を開始させるための電源状態とは同じであるように構成されている場合には、電力供給停止時処理が同時に開始されることによって、遊技制御手段と払出制御手段とを、同時に立ち下げることができる。

所定電位電源を監視し検出条件が成立した場合に検出信号を出力する電源監視手段を備え、遊技制御手段および払出制御手段が、電源監視手段からの検出信号に応じて電力供給停止時処理を行うように構成されている場合には、払出制御手段が遊技制御手段からのコマンドを確実に受信することができる上に、遊技制御手段および払出制御手段は、データ保存のための処理などの電力供給停止時処理を行うタイミングを確実に把握できる。

電源監視手段の検出信号を受けた遊技制御手段および払出制御手段が、割込処理で電力供給停止時処理を実行するように構成されている場合には、優先度の高い処理によって、確実に電源断処理が実行される。

遊技制御基板にある記憶手段が電源バックアップされ、遊技機の電源が復旧したときに遊技状態を復元するために必要な情報を保持するように構成されている場合には、不測の停電等による電源断が生じても、電源復旧時に電源断時の状態に復帰でき、遊技者に不利益を与えない等の効果がある。

電力供給停止直前の内容を保持することが可能な記憶手段が遊技制御手段に含まれている場合には、記憶手段が遊技制御手段と一体化されることによって、遊技制御手段のコストを低減することができる。

払出制御手段が搭載された払出制御基板にある記憶手段が電源バックアップされ、遊技機の電源が復旧したときに払出状態を復元するために必要な情報を保持するように構成されている場合には、不測の停電等による電源断が生じても、電源復旧時に電源断時の払出状態に復帰でき、遊技者に不利益を与えないという効果がある。

電力供給停止直前の内容を保持することが可能な記憶手段が払出制御手段に含まれている場合には、記憶手段が払出制御手段と一体化されることによって、払出制御手段のコストを低減することができる。

初期リセット手段からのリセット信号を遅延させて遊技制御手段に供給する遅延手段を備えている場合には、遊技制御基板の初期リセット手段と払出制御基板の初期リセット手段とを同一構成にすることができる。

遊技制御基板の初期リセット手段におけるリセット信号を作成するためのコンデンサの容量が、払出制御基板の初期リセット手段におけるリセット信号を作成するためのコンデンサの容量よりも大きい場合には、遅延回路等が不要になるので回路構成が簡略化されるという効果がある。

遊技制御手段はパワーオンリセット解除時に所定のプログラムを実行するものであって、遊技制御基板における初期リセット手段と払出制御基板における初期リセット手段とが同一構成である場合には、同一設計を行うことができるので設計コストが低減し、その結果、遊技機コストが低減される効果がある。