JP4221473B2 - Game machine - Google Patents

Game machine Download PDFInfo

- Publication number

- JP4221473B2 JP4221473B2 JP2007137259A JP2007137259A JP4221473B2 JP 4221473 B2 JP4221473 B2 JP 4221473B2 JP 2007137259 A JP2007137259 A JP 2007137259A JP 2007137259 A JP2007137259 A JP 2007137259A JP 4221473 B2 JP4221473 B2 JP 4221473B2

- Authority

- JP

- Japan

- Prior art keywords

- command

- payout

- game

- ball

- control

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

本発明は、遊技者が遊技媒体を用いて遊技を行うパチンコ遊技機やスロット機等の遊技機に関する。 The present invention relates to a gaming machine such as a pachinko gaming machine or a slot machine in which a player plays a game using a gaming medium.

遊技機として、遊技球などの遊技媒体を発射装置によって遊技領域に発射し、遊技領域に設けられている入賞口などの入賞領域に遊技媒体が入賞すると、所定個の遊技媒体が賞球として遊技者に払い出されるものがある。さらに、表示状態が変化可能な可変表示装置が設けられ、可変表示装置における表示結果があらかじめ定められた特定の表示態様となった場合に所定の遊技価値を遊技者に与えるように構成されたものがある。 As a gaming machine, a game medium such as a game ball is launched into a game area by a launching device, and when a game medium wins a prize area such as a prize opening provided in the game area, a predetermined number of game media are played as prize balls. Is paid out to the person. Further, a variable display device capable of changing the display state is provided, and is configured to give a predetermined game value to a player when a display result on the variable display device becomes a predetermined specific display mode There is.

特別図柄を表示する可変表示装置における表示結果があらかじめ定められた特定の表示態様の組合せとなることを、通常、「大当り」という。なお、遊技価値とは、遊技機の遊技領域に設けられた可変入賞球装置の状態が打球が入賞しやすい遊技者にとって有利な状態になることや、遊技者にとって有利な状態となるための権利を発生させたりすることである。 That the display result in the variable display device that displays the special symbol is a combination of specific display modes determined in advance is usually referred to as “big hit”. Note that the game value is the right that the state of the variable winning ball device provided in the gaming area of the gaming machine is advantageous for a player who is likely to win a ball, or the advantageous state for a player. It is to generate.

大当りが発生すると、例えば、大入賞口が所定回数開放して打球が入賞しやすい大当り遊技状態に移行する。そして、各開放期間において、所定個(例えば10個)の大入賞口への入賞があると大入賞口は閉成する。そして、大入賞口の開放回数は、所定回数(例えば16ラウンド)に固定されている。なお、各開放について開放時間(例えば29.5秒)が決められ、入賞数が所定個に達しなくても開放時間が経過すると大入賞口は閉成する。また、大入賞口が閉成した時点で所定の条件(例えば、大入賞口内に設けられているVゾーンへの入賞)が成立していない場合には、大当り遊技状態は終了する。 When the big hit occurs, for example, the big winning opening is opened a predetermined number of times, and the game shifts to a big hit gaming state where the hit ball is easy to win. And in each open period, if there is a prize for a predetermined number (for example, 10) of the big prize opening, the big prize opening is closed. And the number of times the special winning opening is opened is fixed to a predetermined number (for example, 16 rounds). An opening time (for example, 29.5 seconds) is determined for each opening, and even if the number of winnings does not reach a predetermined number, the big winning opening is closed when the opening time elapses. Further, when a predetermined condition (for example, winning in the V zone provided in the big prize opening) is not established at the time when the big prize opening is closed, the big hit gaming state is ended.

遊技機における遊技進行はマイクロコンピュータ等による遊技制御手段によって制御される。そして、可変表示装置に表示される識別情報は、遊技制御手段の遊技制御マイクロコンピュータとは別の表示制御用のマイクロコンピュータを含む表示制御手段によって制御される。さらに、遊技機において、スピーカ等の音発生手段が設けられ、遊技効果を増進するために遊技の進行に伴ってスピーカから種々の効果音や音声が発せられる。また、遊技盤や枠側にランプやLED等の発光体が設けられ、遊技効果を増進するために遊技の進行に伴ってそれらの発光体が点灯されたり消灯されたりする。そして、音発生手段や発光体を制御するために、音制御手段を搭載した音制御基板を遊技制御手段とは別に設けたり、発光体制御手段を搭載した発光体制御基板を遊技制御手段とは別に設けた構成が採用されることがある。 The game progress in the gaming machine is controlled by game control means such as a microcomputer. The identification information displayed on the variable display device is controlled by display control means including a display control microcomputer different from the game control microcomputer of the game control means. Furthermore, in the gaming machine, sound generating means such as a speaker is provided, and various sound effects and sounds are emitted from the speaker as the game progresses in order to enhance the gaming effect. In addition, light emitters such as lamps and LEDs are provided on the game board and the frame side, and these light emitters are turned on and off as the game progresses in order to enhance the game effect. And in order to control the sound generating means and the light emitter, a sound control board equipped with a sound control means is provided separately from the game control means, or a light emitter control board equipped with the light emitter control means is a game control means. A separately provided configuration may be employed.

賞球払出の制御を行う払出制御手段が、遊技制御手段が搭載されている遊技制御基板とは別の払出制御基板に搭載されている場合、遊技の進行は遊技制御基板に搭載された遊技制御手段によって制御されるので、入賞にもとづく賞球個数は、遊技制御手段によって決定され、払出制御基板に送信される。一方、遊技媒体の貸し出しは、遊技の進行とは無関係であるから、一般に、遊技制御手段を介さず払出制御手段によって制御される。 When the payout control means for controlling the prize ball payout is mounted on a payout control board different from the game control board on which the game control means is mounted, the progress of the game is controlled by the game control mounted on the game control board. Since it is controlled by the means, the number of winning balls based on the winning is determined by the game control means and transmitted to the payout control board. On the other hand, the rental of game media is irrelevant to the progress of the game, and is generally controlled by the payout control means without going through the game control means.

以上のように、遊技機には、遊技制御手段の他に種々の制御手段が搭載されている。そして、遊技の進行を制御する遊技制御手段は、遊技状況に応じて動作指示を示す各コマンドを、各制御基板に搭載された各制御手段に送信する。以下、遊技機に設けられている制御手段を電気部品制御手段といい、電気部品制御手段が搭載された基板を電気部品制御基板ということがある。 As described above, various control means are mounted on the gaming machine in addition to the game control means. Then, the game control means for controlling the progress of the game transmits each command indicating an operation instruction according to the game situation to each control means mounted on each control board. Hereinafter, the control means provided in the gaming machine may be referred to as electrical component control means, and the board on which the electrical component control means is mounted may be referred to as an electrical component control board.

上記のような遊技機において、遊技機に対する電力供給を開始する場合に、遊技店員がRAMクリア等の遊技機の初期化作業を容易に行えるようにすることが望ましい。In the gaming machine as described above, it is desirable that the game shop clerk can easily perform initialization work of the gaming machine such as RAM clearing when the power supply to the gaming machine is started.

そこで、本発明は、クリアスイッチをオン状態にしながら遊技機に対する電力供給を開始することによって、容易に初期化処理を実行させることができる遊技機を提供することを目的とする。 Accordingly, an object of the present invention is to provide a gaming machine that can easily execute an initialization process by starting power supply to the gaming machine while turning on a clear switch .

本発明による遊技機は、遊技者が所定の遊技を行うことが可能な遊技機であって、制御を行う際に発生する変動データを記憶する遊技制御用変動データ記憶手段を有し、遊技の進行を制御する遊技制御用マイクロコンピュータと、遊技機への電力供給が停止していても遊技制御用変動データ記憶手段の記憶内容を所定期間保持させることが可能な記憶内容保持手段と、遊技媒体を検出するための遊技媒体検出手段に供給される電圧よりも高い所定電源電圧の電圧低下を検出して、電源断の発生を検出したときに検出信号を出力する電源監視手段と、操作に応じて操作信号を出力する初期化操作手段とを備え、遊技制御用マイクロコンピュータは、検出信号の入力に応じて、遊技制御用変動データ記憶手段の記憶内容が正常か否かの判定に用いるチェックデータの作成処理を含む遊技制御用電力供給停止時処理を実行し、電力供給が開始されたときに、初期化操作手段から操作信号が入力されているか否かを判定し、初期化操作手段からの操作信号が入力されていれば、チェックデータにもとづく遊技制御用変動データ記憶手段の記憶内容が正常か否かの判定を行うことなく、遊技制御用変動データ記憶手段の記憶内容を初期化し、初期化操作手段から操作信号が入力されていないと判定されたときに、チェックデータにもとづいて遊技制御用変動データ記憶手段の記憶内容が正常か否かの判定を実行し、遊技制御用変動データ記憶手段の記憶内容が正常であると判定されたことを条件に、遊技制御用変動データ記憶手段に保存されていた記憶内容にもとづいて制御状態を遊技制御用電力供給停止時処理を開始したときの状態に復旧させる遊技制御用状態復帰制御を実行し、初期化操作手段からの操作信号が入力されているか否かを、遊技媒体検出手段から出力される信号が有効と判定される遊技媒体検出判定期間よりも短い要求検出判定期間で判定することを特徴とする。

また、本発明による遊技機の他の態様は、遊技者が所定の遊技を行うことが可能な遊技機であって、制御を行う際に発生する変動データを記憶する払出制御用変動データ記憶手段を有し、遊技媒体の払出の制御を行う払出制御用マイクロコンピュータと、遊技機への電力供給が停止していても払出制御用変動データ記憶手段の記憶内容を所定期間保持させることが可能な記憶内容保持手段と、遊技媒体を検出するための遊技媒体検出手段に供給される電圧よりも高い所定電源電圧の電圧低下を検出して、電源断の発生を検出したときに検出信号を出力する電源監視手段と、操作に応じて操作信号を出力する初期化操作手段とを備え、払出制御用マイクロコンピュータは、検出信号の入力に応じて、払出制御用変動データ記憶手段の記憶内容が正常か否かの判定に用いるチェックデータの作成処理を含む払出制御用電力供給停止時処理を実行し、電力供給が開始されたときに、初期化操作手段から操作信号が入力されているか否かを判定し、初期化操作手段からの操作信号が入力されていれば、チェックデータにもとづく払出制御用変動データ記憶手段の記憶内容が正常か否かの判定を行うことなく、払出制御用変動データ記憶手段の記憶内容を初期化し、初期化操作手段から操作信号が入力されていないと判定されたときに、チェックデータにもとづいて払出制御用変動データ記憶手段の記憶内容が正常か否かの判定を実行し、払出制御用変動データ記憶手段の記憶内容が正常であると判定されたことを条件に、払出制御用変動データ記憶手段に保存されていた記憶内容にもとづいて制御状態を払出制御用電力供給停止時処理を開始したときの状態に復旧させる払出制御用状態復帰制御を実行し、初期化操作手段からの操作信号が入力されているか否かを、遊技媒体検出手段から出力される信号が有効と判定される遊技媒体検出判定期間よりも短い要求検出判定期間で判定することを特徴とする。

A gaming machine according to the present invention is a gaming machine in which a player can play a predetermined game, and has a game control variation data storage means for storing variation data generated when control is performed . A game control microcomputer for controlling the progress, a storage content holding means capable of holding the storage contents of the game control variation data storage means for a predetermined period even when power supply to the gaming machine is stopped, and a game medium A power supply monitoring means for detecting a voltage drop of a predetermined power supply voltage higher than the voltage supplied to the game medium detecting means for detecting the power supply, and outputting a detection signal when the occurrence of power interruption is detected, and depending on the operation The game control microcomputer is used to determine whether or not the stored content of the game control variation data storage means is normal according to the input of the detection signal. A process for stopping power supply for game control including a process for creating check data is executed, and when power supply is started, it is determined whether or not an operation signal is input from the initialization operation means, and the initialization operation means If the operation signal is input, the memory content of the game control variation data storage means is initialized without determining whether the memory content of the game control variation data storage means is normal based on the check data. When it is determined that the operation signal is not input from the initialization operation means, it is determined whether or not the stored content of the game control variation data storage means is normal based on the check data, and the game control variation On the condition that the stored contents of the data storage means are normal, the control state is set for game control based on the stored contents stored in the variation data storage means for game control. A signal output from the game medium detection means for executing whether or not an operation signal from the initialization operation means is input, executing a state return control for game control to restore the state at the time of starting the power supply stop process Is determined in a request detection determination period shorter than the game medium detection determination period in which it is determined to be valid .

Further, another aspect of the gaming machine according to the present invention is a gaming machine in which a player can play a predetermined game, and a variation data storage means for payout control that stores variation data generated when control is performed. And the storage contents of the payout control variation data storage means can be held for a predetermined period even when the power supply to the gaming machine is stopped. A voltage drop of a predetermined power supply voltage higher than the voltage supplied to the stored content holding means and the game medium detection means for detecting a game medium is detected, and a detection signal is output when the occurrence of power interruption is detected. Power supply monitoring means and initialization operation means for outputting an operation signal in response to an operation, and the payout control microcomputer stores the contents of the payout control variation data storage means in response to the input of the detection signal. Whether or not an operation signal is input from the initialization operation means when the power supply stop process for payout control including the process of creating check data used to determine whether or not it is normal is executed and the power supply is started If the operation signal from the initialization operation means is input, the payout control variation data is determined without determining whether the storage content of the payout control variation data storage means based on the check data is normal or not. Initializing the storage contents of the storage means and determining whether or not the storage contents of the payout control variation data storage means are normal based on the check data when it is determined that no operation signal is input from the initialization operation means On the basis of the stored contents stored in the payout control variable data storage means on the condition that the storage contents of the payout control variable data storage means are determined to be normal. Executes payout control state return control that restores the control state to the state at the start of payout control power supply stop processing, and detects whether an operation signal is input from the initialization operation means. The determination is made in a request detection determination period shorter than the game medium detection determination period in which the signal output from the means is determined to be valid.

本発明によれば、初期化操作手段からの操作信号が入力されているか否かを、遊技媒体検出手段から出力される信号が有効と判定される遊技媒体検出判定期間よりも短い要求検出判定期間で判定するように構成したので、初期化操作手段をオン状態にしながら遊技機に対する電力供給を開始することによって、容易に初期化処理を実行させることができる効果がある。 According to the present invention, the request detection determination period shorter than the game medium detection determination period in which the signal output from the game medium detection means is determined to be valid, whether or not the operation signal from the initialization operation means is input. since it is configured so to determine in, by starting the power supply to the gaming machine while the initializing operation means to the oN state, there is an effect that it is possible to easily perform the initialization process.

以下、本発明の一実施形態を図面を参照して説明する。

まず、遊技機の一例であるパチンコ遊技機の全体の構成について説明する。図1はパチンコ遊技機を正面からみた正面図、図2はガラス扉枠を取り外した状態での遊技盤の前面を示す正面図である。なお、以下の実施の形態では、パチンコ遊技機を例に説明を行うが、本発明による遊技機はパチンコ遊技機に限られず、例えばスロット機等であってもよい。また、画像式の遊技機に適用することもできる。

Hereinafter, an embodiment of the present invention will be described with reference to the drawings.

First, the overall configuration of a pachinko gaming machine that is an example of a gaming machine will be described. FIG. 1 is a front view of the pachinko gaming machine as viewed from the front, and FIG. 2 is a front view showing the front of the game board with the glass door frame removed. In the following embodiments, a pachinko gaming machine will be described as an example. However, the gaming machine according to the present invention is not limited to a pachinko gaming machine, and may be, for example, a slot machine. It can also be applied to image-type gaming machines.

パチンコ遊技機1は、縦長の方形状に形成された外枠(図示せず)と、外枠の内側に開閉可能に取り付けられた遊技枠とで構成される。また、パチンコ遊技機1は、遊技枠に開閉可能に設けられている額縁状に形成されたガラス扉枠2を有する。遊技枠は、外枠に対して開閉自在に設置される前面枠(図示せず)と、機構部品等が取り付けられる機構板と、それらに取り付けられる種々の部品(後述する遊技盤を除く。)とを含む構造体である。

The

図1に示すように、パチンコ遊技機1は、額縁状に形成されたガラス扉枠2を有する。ガラス扉枠2の下部表面には打球供給皿(上皿)3がある。打球供給皿3の下部には、打球供給皿3に収容しきれない遊技球を貯留する余剰球受皿4と打球を発射する打球操作ハンドル(操作ノブ)5が設けられている。ガラス扉枠2の背面には、遊技盤6が着脱可能に取り付けられている。なお、遊技盤6は、それを構成する板状体と、その板状体に取り付けられた種々の部品とを含む構造体である。また、遊技盤6の前面には遊技領域7が形成されている。

As shown in FIG. 1, the

遊技領域7の中央付近には、それぞれが識別情報としての図柄を可変表示する複数の可変表示部を含む可変表示装置(特別図柄表示装置)9が設けられている。可変表示装置9には、例えば「左」、「中」、「右」の3つの可変表示部(図柄表示エリア)がある。可変表示装置9の下方には、始動入賞口14が設けられている。始動入賞口14に入った入賞球は、遊技盤6の背面に導かれ、始動口スイッチ14aによって検出される。また、始動入賞口14の下部には開閉動作を行う可変入賞球装置15が設けられている。可変入賞球装置15は、ソレノイド16によって開状態とされる。

Near the center of the

可変入賞球装置15の下部には、特定遊技状態(大当り状態)においてソレノイド21によって開状態とされる開閉板20が設けられている。開閉板20は大入賞口を開閉する手段である。開閉板20から遊技盤6の背面に導かれた入賞球のうち一方(V入賞領域)に入った入賞球はV入賞スイッチ22で検出され、開閉板20からの入賞球はカウントスイッチ23で検出される。遊技盤6の背面には、大入賞口内の経路を切り換えるためのソレノイド21Aも設けられている。また、可変表示装置9の下部には、始動入賞口14に入った有効入賞球数すなわち始動記憶数を表示する4個の表示部を有する始動記憶表示器18が設けられている。この例では、4個を上限として、有効始動入賞がある毎に、始動記憶表示器18は点灯している表示部を1つずつ増やす。そして、可変表示装置9の可変表示が開始される毎に、点灯している表示部を1つ減らす。

An open /

ゲート32に遊技球が入賞すると、7セグメントLEDによる普通図柄表示器10の表示の可変表示が開始される。そして、普通図柄表示器10における停止図柄が所定の図柄(当り図柄)である場合に、可変入賞球装置15が所定回数、所定時間だけ開状態になる。普通図柄表示器10の近傍には、ゲート32に入った入賞球数を表示する4個の表示部を有する普通図柄始動記憶表示器41が設けられている。この例では、4個を上限として、ゲート32への入賞がある毎に、普通図柄始動記憶表示器41は点灯している表示部を1つずつ増やす。そして、可変入賞球装置15の開放制御がなされる毎に、点灯している表示部を1つ減らす。

When a game ball wins the

遊技盤6には、複数の入賞口24,29,30,33が設けられ、遊技球の入賞口24,29,30,33への入賞は、それぞれ入賞口スイッチ24a,29a,30a,33aによって検出される。遊技領域7の左右周辺には、遊技中に点滅表示される装飾ランプ25が設けられ、下部には、入賞しなかった打球を吸収するアウト口26がある。また、遊技領域7の外側の左右上部には、効果音を発する2つのスピーカ27が設けられている。遊技領域7の外周には、天枠ランプ28a、左枠ランプ28bおよび右枠ランプ28cが設けられている。さらに、遊技領域7における各構造物(大入賞口等)の周囲には装飾LEDが設置されている。

The

そして、この例では、左枠ランプ28bの近傍に、賞球残数があるときに点灯する賞球ランプ51が設けられ、天枠ランプ28aの近傍に、補給球が切れたときに点灯する球切れランプ52が設けられている。さらに、図1には、パチンコ遊技機1に隣接して設置され、プリペイドカードが挿入されることによって球貸しを可能にするカードユニット50も示されている。

In this example, a

カードユニット50には、使用可能状態であるか否かを示す使用可表示ランプ151、カード内に記録された残額情報に端数(100円未満の数)が存在する場合にその端数を打球供給皿3の近傍に設けられる度数表示LEDに表示させるための端数表示スイッチ152、カードユニット50がいずれの側のパチンコ遊技機1に対応しているのかを示す連結台方向表示器153、カードユニット50内にカードが投入されていることを示すカード投入表示ランプ154、記録媒体としてのカードが挿入されるカード挿入口155、およびカード挿入口155の裏面に設けられているカードリーダライタの機構を点検する場合にカードユニット50を解放するためのカードユニット錠156が設けられている。

The

打球発射装置から発射された遊技球は、打球レールを通って遊技領域7に入り、その後、遊技領域7を下りてくる。打球が始動入賞口14に入り始動口スイッチ14aで検出されると、図柄の可変表示を開始できる状態であれば、可変表示装置9において特別図柄が可変表示(変動)を始める。図柄の可変表示を開始できる状態でなければ、始動記憶数を1増やす。

The game balls launched from the hit ball launching device enter the

可変表示装置9における特別図柄の可変表示は、一定時間が経過したときに停止する。停止時の特別図柄の組み合わせが大当り図柄の組み合わせであると、大当り遊技状態に移行する。すなわち、開閉板20が、一定時間経過するまで、または、所定個数(例えば10個)の打球が入賞するまで開放する。そして、開閉板20の開放中に打球がV入賞領域に入賞しV入賞スイッチ22で検出されると、継続権が発生し開閉板20の開放が再度行われる。継続権の発生は、所定回数(例えば15ラウンド)許容される。

The variable display of the special symbol on the

停止時の可変表示装置9における特別図柄の組み合わせが確率変動を伴う大当り図柄の組み合わせである場合には、次に大当りとなる確率が高くなる。すなわち、高確率状態という遊技者にとってさらに有利な状態となる。

When the combination of special symbols in the

打球がゲート32に入賞すると、普通図柄表示器10において普通図柄としての表示数字が連続的に変化する状態になる。また、普通図柄表示器10における停止図柄が所定の図柄(当り図柄)である場合に、可変入賞球装置15が所定時間だけ開状態になる。さらに、高確率状態では、普通図柄表示器10における停止図柄が当り図柄になる確率が高められるとともに、可変入賞球装置15の開放時間と開放回数が高められる。

When the hit ball wins the

次に、パチンコ遊技機1の裏面の構造について図3および図4を参照して説明する。図3は、遊技機を裏面から見た背面図である。図4は、各種部材が取り付けられた機構板を遊技機背面側から見た背面図である。

Next, the structure of the back surface of the

図3に示すように、遊技機裏面側では、可変表示装置9を制御する図柄制御基板80を含む可変表示制御ユニット49、遊技制御用マイクロコンピュータ等が搭載された遊技制御基板(主基板)31が設置されている。また、球払出制御を行う払出制御用マイクロコンピュータ等が搭載された払出制御基板37が設置されている。さらに、遊技盤6に設けられている各種装飾LED、特別図柄始動記憶表示器18および普通図柄始動記憶表示器41、装飾ランプ25、枠側に設けられている天枠ランプ28a、左枠ランプ28b、右枠ランプ28c、賞球ランプ51および球切れランプ52を点灯制御するランプ制御手段が搭載されたランプ制御基板35、スピーカ27からの音発生を制御する音制御手段が搭載された音制御基板70も設けられている。また、DC30V、DC21V、DC12VおよびDC5Vを作成する電源回路が搭載された電源基板910や発射制御基板91が設けられている。

As shown in FIG. 3, on the back side of the gaming machine, a game control board (main board) 31 on which a variable

遊技機裏面において、上方には、各種情報を遊技機外部に出力するための各端子を備えたターミナル基板160が設置されている。ターミナル基板160には、少なくとも、球切れ検出スイッチの出力を導入して外部出力するための球切れ用端子、賞球個数信号を外部出力するための賞球用端子および球貸し個数信号を外部出力するための球貸し用端子が設けられている。また、中央付近には、主基板31からの各種情報を遊技機外部に出力するための各端子を備えた情報端子盤34が設置されている。

On the back side of the gaming machine, a

さらに、各基板(主基板31や払出制御基板37等)に含まれる記憶内容保持手段(例えば、電力供給停止時にもその内容を保持可能なバックアップRAM)に記憶されたバックアップデータをクリアするための初期化操作手段としてのクリアスイッチ921が搭載されたスイッチ基板190が設けられている。スイッチ基板190には、クリアスイッチ921と、主基板31等の他の基板と接続されるコネクタ922が設けられている。

Furthermore, for clearing backup data stored in storage content holding means (for example, a backup RAM capable of holding the contents even when power supply is stopped) included in each board (

貯留タンク38に貯留された遊技球は誘導レール39を通り、図4に示されるように、カーブ樋186を経て賞球ケース40Aで覆われた球払出装置に至る。球払出装置の上部には、遊技媒体切れ検出手段としての球切れスイッチ187が設けられている。球切れスイッチ187が球切れを検出すると、球払出装置の払出動作が停止する。球切れスイッチ187は遊技球通路内の遊技球の有無を検出するスイッチであるが、貯留タンク38内の補給球の不足を検出する球切れ検出スイッチ167も誘導レール39における上流部分(貯留タンク38に近接する部分)に設けられている。球切れ検出スイッチ167が遊技球の不足を検知すると、遊技機設置島に設けられている補給機構から遊技機に対して遊技球の補給が行われる。

The game balls stored in the

なお、球切れスイッチ187は、球払出装置に至る払出球通路に27〜28個程度の遊技球が存在することを検出できるような位置に係止されている。すなわち、球切れスイッチ187は、賞球の一単位の最大払出量(この実施の形態では15個)および球貸しの一単位の最大払出量(この実施の形態では100円:25個)以上が確保されていることが確認できるような位置に設置されている。

The ball break

球払出装置から払い出された遊技球は、連絡口45を通ってパチンコ遊技機1の前面に設けられている打球供給皿3に誘導される。連絡口45の側方には、パチンコ遊技機1の前面に設けられている余剰球受皿4に連通する余剰球通路46が形成されている。

The game ball paid out from the ball payout device is guided to the hitting

入賞にもとづく景品としての遊技球や球貸し要求にもとづく遊技球が多数払い出されて打球供給皿3が満杯になり、ついには遊技球が連絡口45に到達した後さらに遊技球が払い出されると、遊技球は、余剰球通路46を経て余剰球受皿4に導かれる。さらに遊技球が払い出されると、感知レバー47が貯留状態検出手段としての満タンスイッチ48を押圧して、貯留状態検出手段としての満タンスイッチ48がオンする。すなわち、遊技者側貯留手段としての余剰球受皿4における貯留量が貯留許容量を越えたことが、満タンスイッチ48で検出される。その状態では、球払出装置内の払出モータの回転が停止して球払出装置の動作が停止するとともに発射装置の駆動も停止する。

A large number of game balls as prizes based on winning prizes and game balls based on ball lending requests are paid out and the hitting

図4に示すように、球払出装置の側方には、カーブ樋186から遊技機下部の排出口192に至る球抜き通路191が形成されている。球抜き通路191の上部には球抜きレバー193が設けられ、球抜きレバー193が遊技店員等によって操作されると、誘導レール39から球抜き通路191への遊技球通路が形成され、貯留タンク38内に貯留されている遊技球は、排出口192から遊技機外に排出される。

As shown in FIG. 4, a

図5は、球払出装置97の構成例を示す分解斜視図である。この例では、賞球ケース40Aとしての3つのケース140,141,142の内部に球払出装置97が形成されている。ケース140,141の上部には、球切れスイッチ187の下部の球通路と連通する穴170,171が設けられ、遊技球は、穴170,171から球払出装置97に流入する。

FIG. 5 is an exploded perspective view showing a configuration example of the

球払出装置97は駆動源となる払出モータ(例えばステッピングモータ)289を含む。払出モータ289の回転力は、払出モータ289の回転軸に嵌合しているギア290に伝えられ、さらに、ギア290と噛み合うギア291に伝えられる。ギア291の中心軸には、凹部を有するスプロケット292が嵌合している。穴170,171から流入した遊技球は、スプロケット292の凹部によって、スプロケット292の下方の球通路293に1個ずつ落下させられる。

The

球通路293には遊技球の流下路を切り替えるための振分部材311が設けられている。振分部材311はソレノイド310によって駆動され、賞球払出時には、球通路293における一方の流下路を遊技球が流下するように倒れ、球貸し時には球通路293における他方の流下路を遊技球が流下するように倒れる。なお、払出モータ289およびソレノイド310は、払出制御基板37に搭載されている払出制御用CPUによって制御される。また、払出制御用CPUは、主基板31に搭載されている遊技制御用のCPUからの指令に応じて払出モータ289およびソレノイド310を制御する。

The

賞球払出時に選択される流下路の下方には球払出装置によって払い出された遊技球を検出する賞球センサ(賞球カウントスイッチ)301Aが設けられ、球貸し時に選択される流下路の下方には球払出装置によって払い出された遊技球を検出する球貸しセンサ(球貸しカウントスイッチ)301Bが設けられている。賞球カウントスイッチ301Aの検出信号と球貸しカウントスイッチ301Bの検出信号は払出制御基板37の払出制御用CPUに入力される。払出制御用CPUは、それらの検出信号にもとづいて、実際に払い出された遊技球の個数を計数する。

A prize ball sensor (prize ball count switch) 301A for detecting a game ball paid out by the ball payout device is provided below the flow path selected at the time of paying out the winning ball, and below the flow path selected at the time of lending the ball. Is provided with a ball lending sensor (ball lending count switch) 301B for detecting a game ball paid out by the ball paying device. The detection signal of the winning

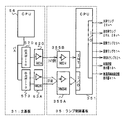

図6は、主基板31における回路構成の一例を示すブロック図である。なお、図6には、払出制御基板37、ランプ制御基板35、音制御基板70、発射制御基板91および図柄制御基板80も示されている。主基板31には、プログラムに従ってパチンコ遊技機1を制御する基本回路53と、ゲートスイッチ32a、始動口スイッチ14a、V入賞スイッチ22、カウントスイッチ23、入賞口スイッチ24a,29a,30a,33a、満タンスイッチ48、球切れスイッチ187、賞球カウントスイッチ301Aおよびクリアスイッチ921からの信号を基本回路53に与えるスイッチ回路58と、可変入賞球装置15を開閉するソレノイド16、開閉板20を開閉するソレノイド21および大入賞口内の経路を切り換えるためのソレノイド21Aを基本回路53からの指令に従って駆動するソレノイド回路59とが搭載されている。

FIG. 6 is a block diagram illustrating an example of a circuit configuration in the

なお、図6には示されていないが、カウントスイッチ短絡信号もスイッチ回路58を介して基本回路53に伝達される。また、ゲートスイッチ32a、始動口スイッチ14a、V入賞スイッチ22、カウントスイッチ23、入賞口スイッチ24a,29a,30a,33a、満タンスイッチ48、球切れスイッチ187、賞球カウントスイッチ301A等のスイッチは、センサと称されているものでもよい。すなわち、遊技球を検出できる遊技媒体検出手段(この例では遊技球検出手段)であれば、その名称を問わない。

Although not shown in FIG. 6, the count switch short-circuit signal is also transmitted to the

また、基本回路53から与えられるデータに従って、大当りの発生を示す大当り情報、可変表示装置9における図柄の可変表示開始に利用された始動入賞球の個数を示す有効始動情報、確率変動が生じたことを示す確変情報等の情報出力信号をホールコンピュータ等の外部機器に対して出力する情報出力回路64が搭載されている。

Further, according to the data given from the

基本回路53は、ゲーム制御用のプログラム等を記憶するROM54、ワークメモリとして使用される記憶手段(変動データを記憶する手段)としてのRAM55、プログラムに従って制御動作を行うCPU56およびI/Oポート部57を含む。この実施の形態では、ROM54,RAM55はCPU56に内蔵されている。すなわち、CPU56は、1チップマイクロコンピュータである。なお、1チップマイクロコンピュータは、少なくともRAM55が内蔵されていればよく、ROM54およびI/Oポート部57は外付けであっても内蔵されていてもよい。

The

また、RAM(CPU内蔵RAMであってもよい。)55の一部または全部が、電源基板910において作成されるバックアップ電源よってバックアップされているバックアップRAMである。すなわち、遊技機に対する電力供給が停止しても、所定期間は、RAM55の一部または全部の内容は保存される。

Further, a part or all of the RAM (may be a CPU built-in RAM) 55 is a backup RAM that is backed up by a backup power source created in the

遊技球を打撃して発射する打球発射装置は発射制御基板91上の回路によって制御される駆動モータ94で駆動される。そして、駆動モータ94の駆動力は、操作ノブ5の操作量に従って調整される。すなわち、発射制御基板91上の回路によって、操作ノブ5の操作量に応じた速度で打球が発射されるように制御される。

A ball hitting device for hitting and launching a game ball is driven by a

なお、この実施の形態では、ランプ制御基板35に搭載されているランプ制御手段が、遊技盤に設けられている始動記憶表示器18、普通図柄始動記憶表示器41および装飾ランプ25の表示制御を行うとともに、枠側に設けられている天枠ランプ28a、左枠ランプ28b、右枠ランプ28c、賞球ランプ51および球切れランプ52の表示制御を行う。また、特別図柄を可変表示する可変表示装置9および普通図柄を可変表示する普通図柄表示器10の表示制御は、図柄制御基板80に搭載されている表示制御手段によって行われる。

In this embodiment, the lamp control means mounted on the

図7は、図柄制御基板80内の回路構成を、可変表示装置9の一実現例であるLCD(液晶表示装置)82、普通図柄表示器10、主基板31の出力ポート(ポート0,2)570,572および出力バッファ回路620,62Aとともに示すブロック図である。出力ポート(出力ポート2)572からは8ビットの表示制御コマンドを構成するコマンドデータが出力され、出力ポート570からは1ビットのストローブ信号(INT信号)が出力される。INT信号は、コマンドデータの取り込みを指令する取込信号である

FIG. 7 shows the circuit configuration in the

表示制御用CPU101は、制御データROM102に格納されたプログラムに従って動作し、主基板31からノイズフィルタ107および入力バッファ回路105Bを介してINT信号が入力されると、入力バッファ回路105Aを介して表示制御コマンドを受信する。入力バッファ回路105A,105Bとして、例えば汎用ICである74HC540,74HC14を使用することができる。なお、表示制御用CPU101がI/Oポートを内蔵していない場合には、入力バッファ回路105A,105Bと表示制御用CPU101との間に、I/Oポートが設けられる。

The display control CPU 101 operates in accordance with a program stored in the

そして、表示制御用CPU101は、受信した表示制御コマンドに従って、LCD82に表示される画面の表示制御を行う。具体的には、表示制御コマンドに応じた指令をVDP103に与える。VDP103は、キャラクタROM86から必要なデータを読み出す。VDP103は、入力したデータに従ってLCD82に表示するための画像データを生成し、R,G,B信号および同期信号をLCD82に出力する。

Then, the display control CPU 101 performs display control of the screen displayed on the

なお、図7には、VDP103をリセットするためのリセット回路83、VDP103に動作クロックを与えるための発振回路85、および使用頻度の高い画像データを格納するキャラクタROM86も示されている。キャラクタROM86に格納される使用頻度の高い画像データとは、例えば、LCD82に表示される人物、動物、または、文字、図形もしくは記号等からなる画像などである。

7 also shows a reset circuit 83 for resetting the

入力バッファ回路105A,105Bは、主基板31から図柄制御基板80へ向かう方向にのみ信号を通過させることができる。従って、図柄制御基板80側から主基板31側に信号が伝わる余地はない。すなわち、入力バッファ回路105A,105Bは、入力ポートともに不可逆性情報入力手段を構成する。図柄制御基板80内の回路に不正改造が加えられても、不正改造によって出力される信号が主基板31側に伝わることはない。

The input buffer circuits 105A and 105B can pass signals only in the direction from the

高周波信号を遮断するノイズフィルタ107として、例えば3端子コンデンサやフェライトビーズが使用されるが、ノイズフィルタ107の存在によって、表示制御コマンドに基板間でノイズが乗ったとしても、その影響は除去される。また、主基板31のバッファ回路620,62Aの出力側にもノイズフィルタを設けてもよい。

For example, a three-terminal capacitor or a ferrite bead is used as the

図8は、主基板31およびランプ制御基板35における信号送受信部分を示すブロック図である。この実施の形態では、遊技盤6に設けられている各種装飾LED、特別図柄始動記憶表示器18および普通図柄始動記憶表示器41、装飾ランプ25、枠側に設けられている天枠ランプ28a、左枠ランプ28b、右枠ランプ28c、賞球ランプ51および球切れランプ52の点灯/消灯とを示すランプ制御コマンドが主基板31からランプ制御基板35に出力される。

FIG. 8 is a block diagram showing signal transmission / reception portions in the

図8に示すように、ランプ制御に関するランプ制御コマンドは、基本回路53におけるI/Oポート部57の出力ポート(出力ポート0,3)570,573から出力される。出力ポート(出力ポート3)573は8ビットのランプ制御コマンドを構成するコマンドデータを出力し、出力ポート570は1ビットのINT信号を出力する。ランプ制御基板35において、主基板31からの制御コマンドは、入力バッファ回路355A,355Bを介してランプ制御用CPU351に入力する。なお、ランプ制御用CPU351がI/Oポートを内蔵していない場合には、入力バッファ回路355A,355Bとランプ制御用CPU351との間に、I/Oポートが設けられる。

As shown in FIG. 8, the lamp control command related to the lamp control is output from the output ports (

ランプ制御基板35において、ランプ制御用CPU351は、各制御コマンドに応じて定義されている各種装飾LED、装飾ランプ25、枠側に設けられている天枠ランプ28a、左枠ランプ28b、右枠ランプ28cに対して点灯/消灯信号を出力する。点灯/消灯信号は、各ランプ・LEDに出力される。なお、点灯/消灯パターンは、ランプ制御用CPU351の内蔵ROMまたは外付けROMに記憶されている。

In the

主基板31において、CPU56は、RAM55の記憶内容に未払出の賞球残数があるときに賞球ランプ51の点灯を指示するランプ制御コマンドを出力し、遊技盤裏面の補給球通路に設置されている球切れスイッチ187(図4参照)が遊技球を検出しなくなると球切れランプ52の点灯を指示するランプ制御コマンドを出力する。ランプ制御基板35において、各ランプ制御コマンドは、入力バッファ回路355A,355Bを介してランプ制御用CPU351に入力する。ランプ制御用CPU351は、それらの制御コマンドに応じて、賞球ランプ51および球切れランプ52を点灯/消灯する。なお、点灯/消灯パターンは、ランプ制御用CPU351の内蔵ROMまたは外付けROMに記憶されている。

In the

さらに、ランプ制御用CPU351は、ランプ制御コマンドに応じて始動記憶表示器18および普通図柄始動記憶表示器41に対して点灯/消灯信号を出力する。

Further, the lamp control CPU 351 outputs a light on / off signal to the

入力バッファ回路355A,355Bとして、例えば、汎用のCMOS−ICである74HC540,74HC14が用いられる。入力バッファ回路355A,355Bは、主基板31からランプ制御基板35へ向かう方向にのみ信号を通過させることができる。従って、ランプ制御基板35側から主基板31側に信号が伝わる余地はない。たとえ、ランプ制御基板35内の回路に不正改造が加えられても、不正改造によって出力される信号がメイン基板31側に伝わることはない。なお、入力バッファ回路355A,355Bの入力側にノイズフィルタを設けてもよい。

As the

また、主基板31において、出力ポート570,573の外側にバッファ回路620,63Aが設けられている。バッファ回路620,63Aとして、例えば、汎用のCMOS−ICである74HC250,74HC14が用いられる。このような構成によれば、外部から主基板31の内部に入力される信号が阻止されるので、ランプ制御基板70から主基板31に信号が与えられる可能性がある信号ラインをさらに確実になくすことができる。なお、バッファ回路620,63Aの出力側にノイズフィルタを設けてもよい。

In the

図9は、主基板31における音制御コマンドの信号送信部分および音制御基板70の構成例を示すブロック図である。この実施の形態では、遊技進行に応じて、遊技領域7の外側に設けられているスピーカ27の音声出力を指示するための音制御コマンドが、主基板31から音制御基板70に出力される。

FIG. 9 is a block diagram showing a configuration example of the sound control command signal transmission part of the

図9に示すように、音制御コマンドは、基本回路53におけるI/Oポート部57の出力ポート(出力ポート0,4)570,574から出力される。出力ポート(出力ポート4)574からは8ビットのデータが出力され、出力ポート570からは1ビットのINT信号が出力される。音制御基板70において、主基板31からの各信号は、入力バッファ回路705A,705Bを介して音制御用CPU701に入力する。なお、音制御用CPU701がI/Oポートを内蔵していない場合には、入力バッファ回路705A,705Bと音制御用CPU701との間に、I/Oポートが設けられる。

As shown in FIG. 9, the sound control command is output from the output ports (

そして、例えばディジタルシグナルプロセッサによる音声合成回路702は、音制御用CPU701の指示に応じた音声や効果音を発生し音量切替回路703に出力する。音量切替回路703は、音制御用CPU701の出力レベルを、設定されている音量に応じたレベルにして音量増幅回路704に出力する。音量増幅回路704は、増幅した音声信号をスピーカ27に出力する。

Then, for example, a

入力バッファ回路705A,705Bとして、例えば、汎用のCMOS−ICである74HC540,74HC14が用いられる。入力バッファ回路705A,705Bは、主基板31から音制御基板70へ向かう方向にのみ信号を通過させることができる。よって、音制御基板70側から主基板31側に信号が伝わる余地はない。従って、音制御基板70内の回路に不正改造が加えられても、不正改造によって出力される信号が主基板31側に伝わることはない。なお、入力バッファ回路705A,705Bの入力側にノイズフィルタを設けてもよい。

As the

また、主基板31において、出力ポート570,574の外側にバッファ回路620,67Aが設けられている。バッファ回路620,67Aとして、例えば、汎用のCMOS−ICである74HC250,74HC14が用いられる。このような構成によれば、外部から主基板31の内部に入力される信号が阻止されるので、音制御基板70から主基板31に信号が与えられる可能性がある信号ラインをさらに確実になくすことができる。なお、バッファ回路620,67Aの出力側にノイズフィルタを設けてもよい。

In the

図10は、払出制御基板37および球払出装置97の構成要素などの払出に関連する構成要素を示すブロック図である。図10に示すように、満タンスイッチ48からの検出信号は、中継基板71を介して主基板31のI/Oポート部57に入力される。また、球切れスイッチ187からの検出信号も、中継基板72および中継基板71を介して主基板31のI/Oポート部57に入力される。

FIG. 10 is a block diagram showing components related to payout, such as components of the

主基板31のCPU56は、球切れスイッチ187からの検出信号が球切れ状態を示しているか、または、満タンスイッチ48からの検出信号が満タン状態を示していると、払出を停止すべき状態であることを指示する払出制御コマンドを送信する。払出を停止すべき状態であることを指示する払出制御コマンドを受信すると、払出制御基板37の払出制御用CPU371は球払出処理を停止する。

The

さらに、賞球カウントスイッチ301Aからの検出信号は、中継基板72および中継基板71を介して主基板31のI/Oポート部57に入力されるとともに、中継基板72を介して払出制御基板37の入力ポート372bに入力される。賞球カウントスイッチ301Aは、球払出装置97の払出機構部分に設けられ、実際に払い出された賞球払出球を検出する。

Further, the detection signal from the prize

入賞があると、払出制御基板37には、主基板31の出力ポート(ポート0,1)570,571から賞球個数を示す払出制御コマンドが入力される。出力ポート(出力ポート1)571は8ビットのデータを出力し、出力ポート570は1ビットのINT信号を出力する。賞球個数を示す払出制御コマンドは、入力バッファ回路373Aを介してI/Oポート372aに入力される。INT信号は、入力バッファ回路373Bを介して払出制御用CPU371の割込端子に入力されている。払出制御用CPU371は、I/Oポート372aを介して払出制御コマンドを入力し、払出制御コマンドに応じて球払出装置97を駆動して賞球払出を行う。なお、この実施の形態では、払出制御用CPU371は、1チップマイクロコンピュータであり、少なくともRAMが内蔵されている。

When there is a winning, a payout control command indicating the number of winning balls is input to the

また、主基板31において、出力ポート570,571の外側にバッファ回路620,68Aが設けられている。バッファ回路620,68Aとして、例えば、汎用のCMOS−ICである74HC250,74HC14が用いられる。このような構成によれば、外部から主基板31の内部に入力される信号が阻止されるので、払出制御基板37から主基板31に信号が与えられる可能性がある信号ラインをさらに確実になくすことができる。なお、バッファ回路620,68Aの出力側にノイズフィルタを設けてもよい。

In the

払出制御用CPU371は、出力ポート372cを介して、貸し球数を示す球貸し個数信号をターミナル基板160に出力する。さらに、出力ポート372dを介して、エラー表示用LED374にエラー信号を出力する。

The payout control CPU 371 outputs a ball lending number signal indicating the number of lending balls to the

さらに、払出制御基板37の入力ポート372bには、中継基板72を介して、球貸しカウントスイッチ301B、および払出モータ289の回転位置を検出するための払出モータ位置センサからの検出信号が入力される。球貸しカウントスイッチ301Bは、球払出装置97の払出機構部分に設けられ、実際に払い出された貸し球を検出する。払出制御基板37からの払出モータ289への駆動信号はあ、出力ポート372cおよび中継基板72を介して球払出装置97の払出機構部分における払出モータ289に伝えられ、振分ソレノイド310への駆動信号は、出力ポート372eおよび中継基板72を介して球払出装置97の払出機構部分における振分ソレノイド310に伝えられる。また、クリアスイッチ921の出力も、入力ポート372bに入力される。

Further, a detection signal from the payout motor position sensor for detecting the rotational position of the ball lending

カードユニット50には、カードユニット制御用マイクロコンピュータが搭載されている。また、カードユニット50には、端数表示スイッチ152、連結台方向表示器153、カード投入表示ランプ154およびカード挿入口155が設けられている(図1参照)。残高表示基板74には、打球供給皿3の近傍に設けられている度数表示LED、球貸しスイッチおよび返却スイッチが接続される。

The

残高表示基板74からカードユニット50には、遊技者の操作に応じて、球貸しスイッチ信号および返却スイッチ信号が払出制御基板37を介して与えられる。また、カードユニット50から残高表示基板74には、プリペイドカードの残高を示すカード残高表示信号および球貸し可表示信号が払出制御基板37を介して与えられる。カードユニット50と払出制御基板37の間では、接続信号(VL信号)、ユニット操作信号(BRDY信号)、球貸し要求信号(BRQ信号)、球貸し完了信号(EXS信号)およびパチンコ機動作信号(PRDY信号)が入力ポート372bおよび出力ポート372eを介してやりとりされる。

A ball lending switch signal and a return switch signal are given from the

パチンコ遊技機1の電源が投入されると、払出制御基板37の払出制御用CPU371は、カードユニット50にPRDY信号を出力する。また、カードユニット制御用マイクロコンピュータは、VL信号を出力する。払出制御用CPU371は、VL信号の入力状態により接続状態/未接続状態を判定する。カードユニット50においてカードが受け付けられ、球貸しスイッチが操作され球貸しスイッチ信号が入力されると、カードユニット制御用マイクロコンピュータは、払出制御基板37にBRDY信号を出力する。この時点から所定の遅延時間が経過すると、カードユニット制御用マイクロコンピュータは、払出制御基板37にBRQ信号を出力する。

When the power of the

そして、払出制御基板37の払出制御用CPU371は、カードユニット50に対するEXS信号を立ち上げ、カードユニット50からのBRQ信号の立ち下がりを検出すると、払出モータ289を駆動し、所定個の貸し球を遊技者に払い出す。このとき、振分ソレノイド310は駆動状態とされている。すなわち、球振分部材311を球貸し側に向ける。そして、払出が完了したら、払出制御用CPU371は、カードユニット50に対するEXS信号を立ち下げる。その後、カードユニット50からのBRDY信号がオン状態でなければ、賞球払出制御を実行する。

Then, the payout control CPU 371 of the

以上のように、カードユニット50からの信号は全て払出制御基板37に入力される構成になっている。従って、球貸し制御に関して、カードユニット50から主基板31に信号が入力されることはなく、主基板31の基本回路53にカードユニット50の側から不正に信号が入力される余地はない。また、カードユニット50で用いられる電源電圧AC24Vは払出制御基板37から供給される。

As described above, all signals from the

この実施の形態では、電源基板910から払出制御基板37に対して電源断信号も入力される。電源断信号は、払出制御用CPU371のマスク不能割込(NMI)端子に入力される。さらに、払出制御基板37に存在するRAM(CPU内蔵RAMであってもよい。)の少なくとも一部は、電源基板910において作成されるバックアップ電源によって、バックアップされている。すなわち、遊技機に対する電力供給が停止しても、所定期間は、RAMの少なくとも一部の内容は保存される。

In this embodiment, a power-off signal is also input from the

なお、この実施の形態では、カードユニット50が遊技機とは別体として遊技機に隣接して設置されている場合を例にするが、カードユニット50は遊技機と一体化されていてもよい。また、コイン投入に応じてその金額に応じた遊技球が貸し出されるような場合でも本発明を適用できる。

In this embodiment, the case where the

図11は、電源基板910の一構成例を示すブロック図である。電源基板910は、主基板31、図柄制御基板80、音制御基板70、ランプ制御基板35および払出制御基板37等の電気部品制御基板と独立して設置され、遊技機内の各電気部品制御基板および機構部品が使用する電圧を生成する。この例では、AC24V、VSL(DC+30V)、DC+21V、DC+12VおよびDC+5Vを生成する。また、バックアップ電源すなわち記憶保持手段となるコンデンサ916は、DC+5Vすなわち各基板上のIC等を駆動する電源のラインから充電される。なお、VSLは、整流回路912において、整流素子でAC24Vを整流昇圧することによって生成される。VSLは、ソレノイド駆動電源となる。

FIG. 11 is a block diagram illustrating a configuration example of the

トランス911は、交流電源からの交流電圧を24Vに変換する。AC24V電圧は、コネクタ915に出力される。また、整流回路912は、AC24Vから+30Vの直流電圧を生成し、DC−DCコンバータ913およびコネクタ915に出力する。DC−DCコンバータ913は、1つまたは複数のコンバータIC922(図11では1つのみを示す。)を有し、VSLにもとづいて+21V、+12Vおよび+5Vを生成してコネクタ915に出力する。コンバータIC922の入力側には、比較的大容量のコンデンサ923が接続されている。従って、外部からの遊技機に対する電力供給が停止したときに、+30V、+12V、+5V等の直流電圧は、比較的緩やかに低下する。コネクタ915は例えば中継基板に接続され、中継基板から各電気部品制御基板および機構部品に必要な電圧の電力が供給される。

The transformer 911 converts AC voltage from the AC power source into 24V. The AC 24V voltage is output to the

ただし、電源基板910に各電気部品制御基板に至る各コネクタを設け、電源基板910から、中継基板を介さずにそれぞれの基板に至る各電圧を供給するようにしてもよい。また、図11には1つのコネクタ915が代表して示されているが、コネクタは、各電気部品制御基板対応に設けられている。

However, each connector reaching each electric component control board may be provided on the

DC−DCコンバータ913からの+5Vラインは分岐してバックアップ+5Vラインを形成する。バックアップ+5Vラインとグラウンドレベルとの間には大容量のコンデンサ916が接続されている。コンデンサ916は、遊技機に対する電力供給が停止したときの電気部品制御基板のバックアップRAM(電源バックアップされているRAMすなわち電力供給停止時にも記憶内容保持状態となりうるバックアップ記憶手段)に対して記憶状態を保持できるように電力を供給するバックアップ電源となる。また、+5Vラインとバックアップ+5Vラインとの間に、逆流防止用のダイオード917が挿入される。なお、この実施の形態では、バックアップ用の+5Vは、主基板31および払出制御基板37に供給される。

The + 5V line from the DC-

また、電源基板910には、電源監視回路としての電源監視用IC902が搭載されている。電源監視用IC902は、VSL電圧を導入し、VSL電圧を監視することによって遊技機への電力供給停止の発生を検出する。具体的には、VSL電圧が所定値(この例では+22V)以下になったら、電力供給の停止が生ずるとして電源断信号を出力する。なお、監視対象の電源電圧は、各電気部品制御基板に搭載されている回路素子の電源電圧(この例では+5V)よりも高い電圧であることが好ましい。この例では、交流から直流に変換された直後の電圧であるVSLが用いられている。電源監視用IC902からの電源断信号は、主基板31や払出制御基板37等に供給される。主基板31に搭載されている遊技制御手段や払出制御基板37に搭載されている払出制御手段は、電源断信号の入力に応じて、バックアップRAMの記憶内容を保護するための処理である電力供給停止時処理を実行する。

The

電源監視用IC902が電力供給の停止を検知するための所定値は、通常時の電圧より低いが、各電気部品制御基板上のCPUが暫くの間動作しうる程度の電圧である。また、電源監視用IC902が、CPU等の回路素子を駆動するための電圧(この例では+5V)よりも高く、また、交流から直流に変換された直後の電圧を監視するように構成されているので、CPUが必要とする電圧に対して監視範囲を広げることができる。従って、より精密な監視を行うことができる。さらに、監視電圧としてVSL(+30V)を用いる場合には、遊技機の各種スイッチに供給される電圧が+12Vであることから、電源瞬断時のスイッチオン誤検出の防止も期待できる。すなわち、+30V電源の電圧を監視すると、+30V作成の以降に作られる+12Vが落ち始める以前の段階でそれの低下を検出できる。 The predetermined value for the power monitoring IC 902 to detect the stop of power supply is lower than the normal voltage, but is a voltage that allows the CPU on each electrical component control board to operate for a while. Further, the power monitoring IC 902 is configured to monitor a voltage that is higher than a voltage for driving a circuit element such as a CPU (+5 V in this example) and immediately after being converted from AC to DC. Therefore, the monitoring range can be expanded for the voltage required by the CPU. Therefore, more precise monitoring can be performed. Furthermore, when VSL (+ 30V) is used as the monitoring voltage, the voltage supplied to the various switches of the gaming machine is + 12V, so that it can be expected to prevent erroneous switch-on detection at the time of instantaneous power interruption. That is, when the voltage of the + 30V power supply is monitored, it is possible to detect a decrease in the level before + 12V created after the creation of + 30V starts to drop.

+12V電源の電圧が低下するとスイッチ出力がオン状態を呈するようになるが、+12Vより早く低下する+30V電源電圧を監視して電力供給の停止を認識すれば、スイッチ出力がオン状態を呈する前に電力供給回復待ちの状態に入ってスイッチ出力を検出しない状態となることができる。 When the voltage of the + 12V power supply decreases, the switch output becomes on. However, if the power supply voltage is monitored by monitoring the + 30V power supply voltage, which decreases faster than + 12V, and the power supply is stopped, the switch output is turned on. It is possible to enter a supply recovery waiting state and not detect the switch output.

また、電源監視用IC902は、電気部品制御基板とは別個の電源基板910に搭載されているので、電源監視回路から複数の電気部品制御基板に電源断信号を供給することができる。電源断信号を必要とする電気部品制御基板が幾つあっても電源監視手段は1つ設けられていればよいので、各電気部品制御基板における各電気部品制御手段が後述する復旧制御を行っても、遊技機のコストはさほど上昇しない。

Further, since the power monitoring IC 902 is mounted on the

なお、図11に示された構成では、電源監視用IC902の検出信号(電源断信号)は、バッファ回路918,919を介してそれぞれの電気部品制御基板(例えば主基板31と払出制御基板37)に伝達されるが、例えば、1つの検出信号を中継基板に伝達し、中継基板から各電気部品制御基板に同じ信号を分配する構成でもよい。また、電源断信号を必要とする基板数に応じたバッファ回路を設けてもよい。さらに、主基板31と払出制御基板37とに出力される電源断信号について、電源断信号を出力することになる電源監視回路の監視電圧を異ならせてもよい。

In the configuration shown in FIG. 11, the detection signal (power cut-off signal) of the power monitoring IC 902 is sent to the respective electric component control boards (for example, the

図12および図13は、この実施の形態における出力ポートの割り当てを示す説明図である。図12に示すように、出力ポート0は各電気部品制御基板に送信される制御コマンドのINT信号の出力ポートである。また、払出制御基板37に送信される払出制御コマンドの8ビットのデータは出力ポート1から出力され、図柄制御基板80に送信される表示制御コマンドの8ビットのデータは出力ポート2から出力され、ランプ制御基板35に送信されるランプ制御コマンドの8ビットのデータは出力ポート3から出力される。そして、図13に示すように、音制御基板70に送信される音制御コマンドの8ビットのデータは出力ポート4から出力される。

12 and 13 are explanatory diagrams showing output port assignment in this embodiment. As shown in FIG. 12, the

また、出力ポート5から、情報出力回路64を介して情報端子板34やターミナル基板160に至る各種情報出力用信号すなわち制御に関わる情報の出力データが出力される。そして、出力ポート6から、可変入賞球装置15を開閉するためのソレノイド16、大入賞口の開閉板2を開閉するためのソレノイド21、および大入賞口内の経路を切り換えるためのソレノイド21Aに対する駆動信号が出力される。

Further, various information output signals from the

図13に示すように、払出制御基板37、図柄制御基板80、ランプ制御基板35および音制御基板70に対して出力される各INT信号(払出制御信号INT、表示制御信号INT、ランプ制御信号INTおよび音制御信号INT)を出力する出力ポート(出力ポート0)と、払出制御コマンドのコマンドデータとしての払出制御信号CD0〜CD7、表示制御コマンドのコマンドデータとしての表示制御信号CD0〜CD7、ランプ制御コマンドのコマンドデータとしてのランプ制御信号CD0〜CD7および音制御コマンドのコマンドデータとしての音制御信号CD0〜CD7を出力する出力ポート(出力ポート1〜4)とは、別ポートである。

As shown in FIG. 13, each INT signal (payout control signal INT, display control signal INT, lamp control signal INT) output to the

従って、INT信号を出力する際に、誤って払出制御信号CD0〜CD7、表示制御信号CD0〜CD7、ランプ制御信号CD0〜CD7および音制御信号CD0〜CD7を変化させてしまう可能性が低減する。また、払出制御信号CD0〜CD7、表示制御信号CD0〜CD7、ランプ制御信号CD0〜CD7または音制御信号CD0〜CD7を出力する際に、誤ってINT信号を変化させてしまう可能性が低減する。その結果、主基板31の遊技制御手段から各電気部品制御基板に対するコマンドは、より確実に送信されることになる。さらに、各INT信号は、全て出力ポート0から出力されるように構成されているので、遊技制御手段のINT信号出力処理の負担が軽減される。

Therefore, when outputting the INT signal, the possibility that the payout control signals CD0 to CD7, the display control signals CD0 to CD7, the ramp control signals CD0 to CD7, and the sound control signals CD0 to CD7 are erroneously changed is reduced. Further, when outputting the payout control signals CD0 to CD7, the display control signals CD0 to CD7, the ramp control signals CD0 to CD7, or the sound control signals CD0 to CD7, the possibility of erroneously changing the INT signal is reduced. As a result, a command for each electric component control board is more reliably transmitted from the game control means of the

図14は、この実施の形態における入力ポートのビット割り当てを示す説明図である。図14に示すように、入力ポート0のビット0〜7には、それぞれ、入賞口スイッチ33a、24a,29a,30a、始動口スイッチ14a、カウントスイッチ23、V入賞スイッチ22、ゲートスイッチ32aの検出信号が入力される。また、入力ポート1のビット0〜4には、それぞれ、賞球カウントスイッチ301A、満タンスイッチ48、球切れスイッチ187の検出信号、カウントスイッチ短絡信号およびクリアスイッチ921の検出信号が入力される。なお、各スイッチからの検出信号は、スイッチ回路58において論理反転されている。このように、クリアスイッチ921の検出信号は、遊技球を検出するためのスイッチの検出信号が入力される入力ポート(8ビット)と同一の入力ポートに入力されている。

FIG. 14 is an explanatory diagram showing bit assignment of input ports in this embodiment. As shown in FIG. 14,

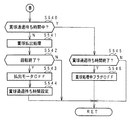

次に遊技機の動作について説明する。図15は、主基板31における遊技制御手段(CPU56およびROM,RAM等の周辺回路)が実行するメイン処理を示すフローチャートである。遊技機に対して電源が投入され、リセット端子の入力レベルがハイレベルになると、CPU56は、ステップS1以降のメイン処理を開始する。メイン処理において、CPU56は、まず、必要な初期設定を行う。

Next, the operation of the gaming machine will be described. FIG. 15 is a flowchart showing main processing executed by game control means (

初期設定処理において、CPU56は、まず、割込禁止に設定する(ステップS1)。次に、割込モードを割込モード2に設定し(ステップS2)、スタックポインタにスタックポインタ指定アドレスを設定する(ステップS3)。そして、内蔵デバイスレジスタの初期化を行う(ステップS4)。また、内蔵デバイス(内蔵周辺回路)であるCTC(カウンタ/タイマ)およびPIO(パラレル入出力ポート)の初期化(ステップS5)を行った後、RAMをアクセス可能状態に設定する(ステップS6)。

In the initial setting process, the

この実施の形態で用いられるCPU56は、I/Oポート(PIO)およびタイマ/カウンタ回路(CTC)も内蔵している。また、CTCは、2本の外部クロック/タイマトリガ入力CLK/TRG2,3と2本のタイマ出力ZC/TO0,1を備えている。

The

この実施の形態で用いられているCPU56には、マスク可能な割込のモードとして以下の3種類のモードが用意されている。なお、マスク可能な割込が発生すると、CPU56は、自動的に割込禁止状態に設定するとともに、プログラムカウンタの内容をスタックにセーブする。

The

割込モード0:割込要求を行った内蔵デバイスがRST命令(1バイト)またはCALL命令(3バイト)をCPUの内部データバス上に出力する。よって、CPU56は、RST命令に対応したアドレスまたはCALL命令で指定されるアドレスの命令を実行する。リセット時に、CPU56は自動的に割込モード0になる。よって、割込モード1または割込モード2に設定したい場合には、初期設定処理において、割込モード1または割込モード2に設定するための処理を行う必要がある。

Interrupt mode 0: The built-in device that issued the interrupt request outputs an RST instruction (1 byte) or a CALL instruction (3 bytes) on the internal data bus of the CPU. Therefore, the

割込モード1:割込が受け付けられると、常に0038(h)番地に飛ぶモードである。 Interrupt mode 1: In this mode, when an interrupt is accepted, the mode always jumps to address 0038 (h).

割込モード2:CPU56の特定レジスタ(Iレジスタ)の値(1バイト)と内蔵デバイスが出力する割込ベクタ(1バイト:最下位ビット0)から合成されるアドレスが、割込番地を示すモードである。すなわち、割込番地は、上位アドレスが特定レジスタの値とされ下位アドレスが割込ベクタとされた2バイトで示されるアドレスである。従って、任意の(飛び飛びではあるが)偶数番地に割込処理を設置することができる。各内蔵デバイスは割込要求を行うときに割込ベクタを送信する機能を有している。

Interrupt mode 2: A mode in which the address synthesized from the value (1 byte) of the specific register (I register) of the

よって、割込モード2に設定されると、各内蔵デバイスからの割込要求を容易に処理することが可能になり、また、プログラムにおける任意の位置に割込処理を設置することが可能になる。さらに、割込モード1とは異なり、割込発生要因毎のそれぞれの割込処理を用意しておくことも容易である。上述したように、この実施の形態では、初期設定処理のステップS2において、CPU56は割込モード2に設定される。

Therefore, when the interrupt

次いで、CPU56は、入力ポート1を介して入力されるクリアスイッチ921の出力信号の状態を1回だけ確認する(ステップS7)。その確認においてオンを検出した場合には、CPU56は、通常の初期化処理を実行する(ステップS11〜ステップS15)。クリアスイッチ921がオンである場合(押下されている場合)には、ローレベルのクリアスイッチ信号が出力されている。なお、入力ポート1では、クリアスイッチ信号のオン状態はハイレベルである(図14参照)。また、例えば、遊技店員は、クリアスイッチ921をオン状態にしながら遊技機に対する電力供給を開始することによって、容易に初期化処理を実行させることができる。すなわち、RAMクリア等を行うことができる。

Next, the

クリアスイッチ921がオンの状態でない場合には、遊技機への電力供給が停止したときにバックアップRAM領域のデータ保護処理(例えばパリティデータの付加等の電力供給停止時処理)が行われたか否か確認する(ステップS8)。この実施の形態では、電力供給の停止が生じた場合には、バックアップRAM領域のデータを保護するための処理が行われている。そのような保護処理が行われていた場合をバックアップありとする。そのような保護処理が行われていないことを確認したら、CPU56は初期化処理を実行する。

If the

この実施の形態では、バックアップRAM領域にバックアップデータがあるか否かは、電力供給停止時処理においてバックアップRAM領域に設定されるバックアップフラグの状態によって確認される。例えば、バックアップフラグ領域に「55H」が設定されていればバックアップあり(オン状態)を意味し、「55H」以外の値が設定されていればバックアップなし(オフ状態)を意味する。 In this embodiment, whether or not there is backup data in the backup RAM area is confirmed by the state of the backup flag set in the backup RAM area in the power supply stop process. For example, if “55H” is set in the backup flag area, it means that there is a backup (ON state), and if a value other than “55H” is set, it means that there is no backup (OFF state).

バックアップありを確認したら、CPU56は、バックアップRAM領域のデータチェック(この例ではパリティチェック)を行う(ステップS9)。この実施の形態では、クリアデータ(00)をチェックサムデータエリアにセットし、チェックサム算出開始アドレスをポインタにセットする。また、チェックサムの対象となるデータ数に対応するチェックサム算出回数をセットする。そして、チェックサムデータエリアの内容とポインタが指すRAM領域の内容との排他的論理和を演算する。演算結果をチェックサムデータエリアにストアするとともに、ポインタの値を1増やし、チェックサム算出回数の値を1減算する。以上の処理が、チェックサム算出回数の値が0になるまで繰り返される。チェックサム算出回数の値が0になったら、CPU56は、チェックサムデータエリアの内容の各ビットの値を反転し、反転後のデータをチェックサムとする。

After confirming that there is a backup, the

電力供給停止時処理において、上記の処理と同様の処理によってチェックサムが算出され、チェックサムはバックアップRAM領域に保存されている。ステップS9では、算出したチェックサムと保存されているチェックサムとを比較する。不測の停電等の電力供給停止が生じた後に復旧した場合には、バックアップRAM領域のデータは保存されているはずであるから、チェック結果(比較結果)は正常(一致)になる。チェック結果が正常でないということは、バックアップRAM領域のデータが、電力供給停止時のデータとは異なっていることを意味する。そのような場合には、内部状態を電力供給停止時の状態に戻すことができないので、電力供給の停止からの復旧時でない電源投入時に実行される初期化処理を実行する。 In the power supply stop process, a checksum is calculated by the same process as described above, and the checksum is stored in the backup RAM area. In step S9, the calculated checksum is compared with the stored checksum. When the power supply is stopped after an unexpected power outage or the like, the data in the backup RAM area should be saved, so the check result (comparison result) is normal (matched). That the check result is not normal means that the data in the backup RAM area is different from the data when the power supply is stopped. In such a case, since the internal state cannot be returned to the state when the power supply is stopped, an initialization process that is executed when the power is turned on is not performed when the power supply is stopped.

チェック結果が正常であれば、CPU56は、遊技制御手段の内部状態と表示制御手段等の電気部品制御手段の制御状態を電力供給停止時の状態に戻すための遊技状態復旧処理を行う(ステップS10)。そして、バックアップRAM領域に保存されていたPC(プログラムカウンタ)の退避値がPCに設定され、そのアドレスに復帰する。

If the check result is normal, the

このように、バックアップフラグとチェックサム等のチェックデータとを用いてバックアップRAM領域のデータが保存されているか否かを確認することによって、遊技状態を電力供給停止時の状態に正確に戻すことができる。すなわち、バックアップRAM領域のデータにもとづく状態復旧処理の確実性が向上する。なお、この実施の形態では、バックアップフラグとチェックデータとの双方を用いてバックアップRAM領域のデータが保存されているか否かを確認しているが、いずれか一方のみを用いてもよい。すなわち、バックアップフラグとチェックデータとのいずれかを、状態復旧処理を実行するための契機としてもよい。 In this way, it is possible to accurately return the gaming state to the state when the power supply is stopped by checking whether the data in the backup RAM area is stored using the backup flag and check data such as a checksum. it can. That is, the certainty of the state restoration process based on the data in the backup RAM area is improved. In this embodiment, it is confirmed whether or not the data in the backup RAM area is stored by using both the backup flag and the check data, but only one of them may be used. That is, either the backup flag or the check data may be used as an opportunity for executing the state recovery process.

初期化処理では、CPU56は、まず、RAMクリア処理を行う(ステップS11)。また、所定の作業領域(例えば、普通図柄判定用乱数カウンタ、普通図柄判定用バッファ、特別図柄左中右図柄バッファ、特別図柄プロセスフラグ、払出コマンド格納ポインタ、賞球中フラグ、球切れフラグ、払出停止フラグなど制御状態に応じて選択的に処理を行うためのフラグ)に初期値を設定する作業領域設定設定処理を行う(ステップS12)。さらに、球払出装置97からの払出が可能であることを指示する払出停止解除コマンド(払出可能状態指定コマンド)を払出制御基板37に対して送信する処理を行う(ステップS13)。また、他のサブ基板(ランプ制御基板35、音制御基板70、図柄制御基板80)を初期化するための初期化コマンドを各サブ基板に送信する処理を実行する(ステップS14)。初期化コマンドとして、可変表示装置9に表示される初期図柄を示すコマンド(図柄制御基板80に対して)や賞球ランプ51および球切れランプ52の消灯を指示するコマンド(ランプ制御基板35に対して)等がある。

In the initialization process, the

初期化処理では、払出制御基板37に対して常に払出可能状態指定コマンドが送信される。仮に、遊技機の状態が球払出装置97からの払出が可能でない状態であったとしても、直後に実行される遊技制御処理において、その旨が検出され、払出が可能でない状態であることを指示する払出停止コマンド(払出停止状態指定コマンド)が送信されるので問題はない。なお、払出可能状態指定コマンドおよび他のサブ基板に対する初期化コマンドの送信処理において、例えば、各コマンドが設定されているテーブル(ROM領域)のアドレスをポインタにセットし、後述するコマンドセット処理のような処理ルーチンをコールすればよい。

In the initialization process, a payout enable state designation command is always transmitted to the

そして、2ms毎に定期的にタイマ割込がかかるようにCPU56に設けられているCTCのレジスタの設定が行われる(ステップS15)。すなわち、初期値として2msに相当する値が所定のレジスタ(時間定数レジスタ)に設定される。

Then, a CTC register set in the

初期化処理の実行(ステップS11〜S15)が完了すると、メイン処理で、表示用乱数更新処理(ステップS17)および初期値用乱数更新処理(ステップS18)が繰り返し実行される。表示用乱数更新処理および初期値用乱数更新処理が実行されるときには割込禁止状態とされ(ステップS16)、表示用乱数更新処理および初期値用乱数更新処理の実行が終了すると割込許可状態とされる(ステップS19)。表示用乱数とは、可変表示装置9に表示される図柄を決定するための乱数であり、表示用乱数更新処理とは、表示用乱数を発生するためのカウンタのカウント値を更新する処理である。また、初期値用乱数更新処理とは、

初期値用乱数を発生するためのカウンタのカウント値を更新する処理である。初期値用乱数とは、大当りとするか否かを決定するための乱数を発生するためのカウンタ(大当り決定用乱数発生カウンタ)等のカウント値の初期値を決定するための乱数である。後述する遊技制御処理において、大当り決定用乱数発生カウンタのカウント値が1周すると、そのカウンタに初期値が設定される。

When the execution of the initialization process (steps S11 to S15) is completed, the display random number update process (step S17) and the initial value random number update process (step S18) are repeatedly executed in the main process. When the display random number update process and the initial value random number update process are executed, the interrupt disabled state is set (step S16). When the display random number update process and the initial value random number update process are finished, the interrupt enabled state is set. (Step S19). The display random number is a random number for determining a symbol displayed on the

This is a process for updating the count value of the counter for generating the initial value random number. The initial value random number is a random number for determining an initial value of a count value such as a counter for generating a random number for determining whether or not to make a jackpot (a jackpot determining random number generation counter). In a game control process to be described later, when the count value of the jackpot determination random number generation counter makes one round, an initial value is set in the counter.

なお、表示用乱数更新処理が実行されるときには割込禁止状態とされるのは、表示用乱数更新処理が後述するタイマ割込処理でも実行されることから、タイマ割込処理における処理と競合してしまうのを避けるためである。すなわち、ステップS17の処理中にタイマ割込が発生してタイマ割込処理中で表示用乱数を発生するためのカウンタのカウント値を更新してしまったのでは、カウント値の連続性が損なわれる場合がある。しかし、ステップS17の処理中では割込禁止状態にしておけば、そのような不都合が生ずることはない。 Note that when the display random number update process is executed, the interrupt is prohibited. The display random number update process is also executed in the timer interrupt process described later, and thus conflicts with the process in the timer interrupt process. This is to avoid that. That is, if the timer interrupt is generated during the process of step S17 and the counter value for generating the display random number is updated during the timer interrupt process, the continuity of the count value is impaired. There is a case. However, such an inconvenience does not occur if the interrupt is prohibited during the process of step S17.

タイマ割込が発生すると、CPU56は、レジスタの退避処理(ステップS20)を行った後、図16に示すステップS21〜S32の遊技制御処理を実行する。遊技制御処理において、CPU56は、まず、スイッチ回路58を介して、ゲートスイッチ32a、始動口スイッチ14a、カウントスイッチ23および入賞口スイッチ33a,24a,29a,30a等のスイッチの検出信号を入力し、それらの状態判定を行う(スイッチ処理:ステップS21)。

When the timer interrupt occurs, the

次いで、パチンコ遊技機1の内部に備えられている自己診断機能によって種々の異常診断処理が行われ、その結果に応じて必要ならば警報が発せられる(エラー処理:ステップS22)。

Next, various abnormality diagnosis processes are performed by the self-diagnosis function provided in the

次に、遊技制御に用いられる大当り判定用の乱数等の各判定用乱数を生成するための各カウンタのカウント値を更新する処理を行う(ステップS23)。CPU56は、さらに、表示用乱数および初期値用乱数を生成するためのカウンタのカウント値を更新する処理を行う(ステップS24,S25)。

Next, a process of updating the count value of each counter for generating each determination random number such as a big hit determination random number used for game control is performed (step S23). The

さらに、CPU56は、特別図柄プロセス処理を行う(ステップS26)。特別図柄プロセス制御では、遊技状態に応じてパチンコ遊技機1を所定の順序で制御するための特別図柄プロセスフラグに従って該当する処理が選び出されて実行される。そして、特別図柄プロセスフラグの値は、遊技状態に応じて各処理中に更新される。また、普通図柄プロセス処理を行う(ステップS27)。普通図柄プロセス処理では、普通図柄表示器10の表示状態を所定の順序で制御するための普通図柄プロセスフラグに従って該当する処理が選び出されて実行される。そして、普通図柄プロセスフラグの値は、遊技状態に応じて各処理中に更新される。

Further, the

次いで、CPU56は、特別図柄に関する表示制御コマンドをRAM55の所定の領域に設定して表示制御コマンドを送信する処理を行う(特別図柄コマンド制御処理:ステップS28)。また、普通図柄に関する表示制御コマンドをRAM55の所定の領域に設定して表示制御コマンドを送信する処理を行う(普通図柄コマンド制御処理:ステップS29)。

Next, the

さらに、CPU56は、例えばホール管理用コンピュータに供給される大当り情報、始動情報、確率変動情報などのデータを出力する情報出力処理を行う(ステップS30)。

Further, the

また、CPU56は、所定の条件が成立したときにソレノイド回路59に駆動指令を行う(ステップS31)。可変入賞球装置15または開閉板20を開状態または閉状態としたり、大入賞口内の遊技球通路を切り替えたりするために、ソレノイド回路59は、駆動指令に応じてソレノイド16,21,21Aを駆動する。

Further, the

そして、CPU56は、入賞口スイッチ33a,24a,29a,30aの検出信号にもとづく賞球個数の設定などを行う賞球処理を実行する(ステップS32)。具体的には、入賞口スイッチ33a,24a,29a,30aがオンしたことにもとづく入賞検出に応じて、払出制御基板37に賞球個数を示す払出制御コマンドを出力する。払出制御基板37に搭載されている払出制御用CPU371は、賞球個数を示す払出制御コマンドに応じて球払出装置97を駆動する。その後、レジスタの内容を復帰させ(ステップS33)、割込許可状態に設定する(ステップS34)。

Then, the

以上の制御によって、この実施の形態では、遊技制御処理は2ms毎に起動されることになる。なお、この実施の形態では、タイマ割込処理で遊技制御処理が実行されているが、タイマ割込処理では例えば割込が発生したことを示すフラグのセットのみがなされ、遊技制御処理はメイン処理において実行されるようにしてもよい。 With the above control, in this embodiment, the game control process is started every 2 ms. In this embodiment, the game control process is executed by the timer interrupt process. However, in the timer interrupt process, for example, only a flag indicating that an interrupt has occurred is set, and the game control process is performed by the main process. May be executed.

図17は、CPU56が実行する特別図柄プロセス処理のプログラムの一例を示すフローチャートである。図17に示す特別図柄プロセス処理は、図16のフローチャートにおけるステップS26の具体的な処理である。CPU56は、特別図柄プロセス処理を行う際に、変動短縮タイマ減算処理(ステップS310)を行った後に、内部状態に応じて、ステップS300〜S309のうちのいずれかの処理を行う。変動短縮タイマは、特別図柄の変動時間が短縮される場合に、変動時間を設定するためのタイマである。

FIG. 17 is a flowchart showing an example of a special symbol process processing program executed by the

特別図柄変動待ち処理(ステップS300):始動入賞口14に打球入賞して始動口スイッチ17がオンするのを待つ。始動口スイッチ14がオンすると、始動入賞記憶数が満タンでなければ、始動入賞記憶数を+1するとともに大当り決定用乱数等を抽出する。

Special symbol change waiting process (step S300): The start winning

特別図柄判定処理(ステップS301):特別図柄の可変表示が開始できる状態になると、始動入賞記憶数を確認する。始動入賞記憶数が0でなければ、抽出されている大当り決定用乱数の値に応じて大当りとするかはずれとするか決定する。 Special symbol determination process (step S301): When variable symbol special display can be started, the number of start winning memories is confirmed. If the start winning memorized number is not 0, it is determined whether to win or not according to the extracted value of the big hit determination random number.

停止図柄設定処理(ステップS302):左右中図柄の停止図柄を決定する。 Stop symbol setting process (step S302): The stop symbol of the middle left and right symbols is determined.

リーチ動作設定処理(ステップS303):左右中の停止図柄の組み合わせにもとづいてリーチ動作するか否か決定するとともに、リーチとすることに決定した場合には、変動パターン決定用乱数の値に応じてリーチ時の変動時間を決定する。 Reach operation setting process (step S303): It is determined whether or not to perform a reach operation based on a combination of left and right stop symbols, and when it is determined to reach, depending on the value of the random number for determining the variation pattern Determine the time of change at reach.

全図柄変動開始処理(ステップS304):可変表示部9において全図柄が変動開始されるように制御する。このとき、図柄制御基板80に対して、左右中最終停止図柄と変動態様を指令する情報とが送信される。処理を終えると、内部状態(プロセスフラグ)をステップS305に移行するように更新する。

All symbol variation start processing (step S304): Control is performed so that the

全図柄停止待ち処理(ステップS305):所定時間(ステップS310の変動短縮タイマで示された時間)が経過すると、可変表示部9において表示される全図柄が停止される。そして、停止図柄が大当り図柄の組み合わせである場合には、内部状態(プロセスフラグ)をステップS306に移行するように更新する。そうでない場合には、内部状態をステップS300に移行するように更新する。

All symbol stop waiting process (step S305): When a predetermined time (the time indicated by the fluctuation shortening timer in step S310) elapses, all symbols displayed on the

大入賞口開放開始処理(ステップS306):大入賞口を開放する制御を開始する。具体的には、カウンタやフラグを初期化するとともに、ソレノイド21を駆動して大入賞口を開放する。また、大当りフラグ(大当り中であることを示すフラグ)のセットを行う。処理を終えると、内部状態(プロセスフラグ)をステップS307に移行するように更新する。

Big winning opening opening process (step S306): Control for opening the big winning opening is started. Specifically, the counter and the flag are initialized, and the

大入賞口開放中処理(ステップS307):大入賞口ラウンド表示の表示制御コマンドを図柄制御基板80に送信する制御や大入賞口の閉成条件の成立を確認する処理等を行う。最終的な大入賞口の閉成条件が成立したら、内部状態をステップS308に移行するように更新する。

Processing for opening a special prize opening (step S307): A process for transmitting a display control command for displaying a special prize round to the

特定領域有効時間処理(ステップS308):V入賞スイッチ22の通過の有無を監視して、大当り遊技状態継続条件の成立を確認する処理を行う。大当り遊技状態継続の条件が成立し、かつ、まだ残りラウンドがある場合には、内部状態をステップS306に移行するように更新する。また、所定の有効時間内に大当り遊技状態継続条件が成立しなかった場合、または、全てのラウンドを終えた場合には、内部状態をステップS309に移行するように更新する。

Specific area valid time process (step S308): The presence / absence of passing of the

大当り終了処理(ステップS309):大当り遊技状態が終了したことを遊技者に報知するための表示を行う。その表示が終了したら、内部状態をステップS300に移行するように更新する。 Big hit end process (step S309): A display for notifying the player that the big hit gaming state has ended is performed. When the display is completed, the internal state is updated to shift to step S300.

図18は、CPU56が実行する普通図柄プロセス処理のプログラムの一例を示すフローチャートである。図18に示す普通図柄プロセス処理は、図16のフローチャートにおけるステップS27の具体的な処理である。CPU56は、普通図柄プロセス処理を行う際に、ゲートスイッチ通過確認処理(ステップS75)を行った後に、内部状態(この例では普通図柄プロセスフラグ)に応じて、ステップS70〜S74のうちのいずれかの処理を行う。

FIG. 18 is a flowchart showing an example of a normal symbol process processing program executed by the

ゲートスイッチ通過確認処理は、普通図柄の変動開始の条件となる遊技球のゲート32の通過を検出する処理である。ゲートスイッチ通過確認処理において、CPOU56は、ゲートスイッチ32aがオンしたことを確認すると、所定の乱数値(この例ではランダム5)を取得して記憶する。また、ゲートスイッチ32aがオンしたことは、普通図柄始動記憶として最大4個記憶可能である。

The gate switch passage confirmation process is a process for detecting the passage of the game ball through the

ステップS70〜S74において、以下のような処理が行われる。 In steps S70 to S74, the following processing is performed.

普通図柄通常処理(ステップS70):普通図柄始動記憶数を確認し、普通図柄始動記憶数が0でなければ、ステップS71に移行するように普通図柄プロセスフラグの値を変更する。 Normal symbol normal processing (step S70): The normal symbol start memory number is confirmed. If the normal symbol start memory number is not 0, the value of the normal symbol process flag is changed so as to proceed to step S71.

普通図柄当り判定処理(ステップS71):遊技球のゲート32の通過があったときに記憶された乱数を格納するバッファの内容をシフトする。シフトの結果、押し出されたバッファの内容にもとづいて当りとするか否かを決定する。その後、ステップS72に移行するように特別図柄プロセスフラグの値を変更する。なお、この実施の形態では、3〜13の範囲の値をとりうる乱数の値が3〜12のうちのいずれかであれば当りと決定され、乱数の値が13であればはずれに決定される。また、当りと決定されると普通図柄表示器10において変動する普通図柄の変動後の停止図柄が当り図柄となり、はずれと決定されると停止図柄がはずれ図柄となるように制御される。

Normal symbol determination process (step S71): The contents of the buffer for storing the random number stored when the game ball passes through the

普通図柄変動処理(ステップS72):普通図柄の変動時間が経過したか否か確認する。経過していれば、ステップS73に移行するように普通図柄プロセスフラグの値を変更する。 Normal symbol variation processing (step S72): It is confirmed whether or not the variation time of the regular symbol has elapsed. If it has elapsed, the value of the normal symbol process flag is changed so as to proceed to step S73.

普通図柄図柄停止処理(ステップS73):当りとすることに決定されている場合には、ステップS74に移行するように普通図柄プロセスフラグの値を変更する。そうでなければ、ステップS70に移行するように普通図柄プロセスフラグの値を変更する。 Normal symbol stop process (step S73): If it is determined to win, the value of the normal symbol process flag is changed so as to proceed to step S74. Otherwise, the value of the normal symbol process flag is changed so as to proceed to step S70.

普通電動役物作動処理(ステップS74):可変入賞球装置15を所定時間開放する処理を所定回行う。ソレノイド16を駆動して可変入賞球装置15を開放する。そして、ステップS70に移行するように普通図柄プロセスフラグの値を変更する。

Ordinary electric accessory operating process (step S74): A process of releasing the variable winning

図19は、主基板31から他の電気部品制御基板に送信される制御コマンドのコマンド形態の一例を示す説明図である。この実施の形態では、制御コマンドのコマンドデータは2バイト構成であり、1バイト目はMODE(コマンドの分類)を表し、2バイト目はEXT(コマンドの種類)を表す。MODEデータの先頭ビット(ビット7)は必ず「1」とされ、EXTデータの先頭ビット(ビット7)は必ず「0」とされる。このように、電気部品制御基板に送信される制御コマンドは、複数のコマンドデータで構成され、先頭ビットによってそれぞれを区別可能な態様になっている。なお、図19に示されたコマンド形態は一例であって他のコマンド形態を用いてもよい。例えば、1バイトや3バイト以上で構成される制御コマンドを用いてもよい。

FIG. 19 is an explanatory diagram showing an example of a command form of a control command transmitted from the

図20は、各電気部品制御手段に対する制御コマンドを構成する8ビットの制御信号CD0〜CD7(コマンドデータ)とINT信号(取込信号)との関係を示すタイミング図である。図20に示すように、MODEまたはEXTのデータが出力ポート(出力ポート1〜出力ポート4のうちのいずれか)に出力されてから、Aで示される期間が経過すると、CPU56は、データ出力を示す信号であるINT信号をハイレベル(オンデータ)にする。また、そこからBで示される期間が経過するとINT信号をローレベル(オフデータ)にする。さらに、次に送信すべきデータがある場合には、すなわち、MODEデータ送信後では、Cで示される期間をおいてから2バイト目のデータを出力ポートに出力する。2バイト目のデータに関して、A,Bの期間は、1バイト目の場合と同様である。このように、取込信号はMODEおよびEXTのデータのそれぞれについて出力される。

FIG. 20 is a timing chart showing a relationship between 8-bit control signals CD0 to CD7 (command data) and an INT signal (capture signal) that constitute a control command for each electric component control means. As shown in FIG. 20, after the MODE or EXT data is output to the output port (any one of the

Aの期間は、CPU56が、コマンドの送信準備の期間すなわちバッファに制御コマンドを設定する処理に要する期間であるとともに、制御信号線におけるデータの安定化のための期間である。すなわち、制御信号線において制御信号CD0〜CD7が出力された後、所定期間(Aの期間:オフ出力期間の一部)経過後に、取込信号としてのINT信号が出力される。また、Bの期間(オン出力期間)は、INT信号安定化のための期間である。そして、Cの期間(オフ出力期間の一部)は、電気部品制御手段が確実にデータを取り込めるように設定されている期間である。B,Cの期間では、信号線上のデータは変化しない。すなわち、B,Cの期間が経過するまでデータ出力が維持される。

The period A is a period required for the

この実施の形態では、払出制御基板37への払出制御コマンド、図柄制御基板80への表示制御コマンド、ランプ制御基板35へのランプ制御コマンドおよび音制御基板70への音制御コマンドは、同一のコマンド送信処理ルーチン(共通モジュール)を用いて送信される。そこで、B,Cの期間すなわち1バイト目に関するINT信号が立ち上がってから2バイト目のデータが送信開始されるまでの期間は、コマンド受信処理に最も時間がかかる電気部品制御手段における受信処理時間よりも長くなるように設定される。

In this embodiment, the payout control command to the

なお、各電気部品制御手段は、INT信号が立ち上がったことを検知して、例えば割込処理によって1バイトのデータの取り込み処理を開始する。 Each electrical component control means detects that the INT signal has risen, and starts a 1-byte data capture process, for example, by an interrupt process.

B,Cの期間が、コマンド受信処理に最も時間がかかる電気部品制御手段における受信処理時間よりも長いので、遊技制御手段が、各電気部品制御手段に対するコマンド送信処理を共通モジュールで制御しても、いずれの電気部品制御手段でも遊技制御手段からの制御コマンドを確実に受信することができる。 Since the period of B and C is longer than the reception processing time in the electrical component control means that takes the longest time for command reception processing, even if the game control means controls the command transmission processing for each electrical component control means with the common module Any electric component control means can reliably receive a control command from the game control means.

CPU56は、INT信号出力処理を実行した後に所定期間が経過すると次のデータを送信できる状態になるが、その所定期間(B,Cの期間)は、INT信号出力処理の前にデータを送信してからINT信号を出力開始するまでの期間(Aの期間)よりも長い。上述したように、Aの期間はコマンドの信号線における安定化期間であり、B,Cの期間は受信側がデータを取り込むのに要する時間を確保するための期間である。従って、Aの期間をB,Cの期間よりも短くすることによって、受信側の電気部品制御手段が確実にコマンドを受信できる状態になるという効果を得ることができるとともに、1つのコマンドの送信完了に要する期間が短縮される効果もある。

The

図21は、電気部品制御基板のうちの図柄制御基板80に送信される表示制御コマンドの内容の一例を示す説明図である。図22に示すように、表示制御コマンドは2バイト構成である。図21に示す例において、コマンド8000(H)〜8031(H)は、特別図柄を可変表示する可変表示装置9における特別図柄の変動パターンを指定する表示制御コマンドである。なお、変動パターンを指定するコマンド(変動パターンコマンド)は変動開始指示も兼ねている。

FIG. 21 is an explanatory diagram showing an example of the contents of a display control command transmitted to the

コマンド88XX(X=4ビットの任意の値)は、普通図柄表示器10で可変表示される普通図柄の変動パターンに関する表示制御コマンドである。コマンド89XXは、普通図柄の停止図柄を指定する表示制御コマンドである。コマンド8AXX(X=4ビットの任意の値)は、普通図柄の可変表示の停止を指示する表示制御コマンドである。

The command 88XX (X = any value of 4 bits) is a display control command relating to a variation pattern of a normal symbol variably displayed on the

コマンド91XX、92XXおよび93XXは、特別図柄の左中右の停止図柄を指定する表示制御コマンドである。また、コマンドA0XXは、特別図柄の可変表示の停止を指示する表示制御コマンドである。コマンドBXXXは、大当り遊技開始から大当り遊技終了までの間に送信される表示制御コマンドである。そして、コマンドC000〜EXXXは、特別図柄の変動および大当り遊技に関わらない可変表示装置9の表示状態に関する表示制御コマンドである。

Commands 91XX, 92XX, and 93XX are display control commands for designating a stop symbol in the middle left of the special symbol. The command A0XX is a display control command for instructing to stop the special symbol variable display. The command BXXX is a display control command transmitted from the start of the big hit game to the end of the big hit game. The commands C000 to EXXXX are display control commands relating to the display state of the

表示制御コマンドは、遊技制御処理(図16参照)における特別図柄コマンド制御処理や普通図柄コマンド制御処理において、変化後の制御状態を示すコマンドとして表示制御手段に送信される。制御状態が変化したか否かは、特別図柄プロセス処理や普通図柄プロセス処理で判定される。図柄制御基板80の表示制御手段は、主基板31の遊技制御手段から上述した表示制御コマンドを受信すると図21に示された内容に応じて可変表示装置9および普通図柄表示器10の表示状態を変更する制御を行う。

The display control command is transmitted to the display control means as a command indicating the control state after the change in the special symbol command control processing or the normal symbol command control processing in the game control processing (see FIG. 16). Whether or not the control state has changed is determined by a special symbol process or a normal symbol process. When the display control means of the

図22は、ランプ制御コマンドの内容の一例を示す説明図である。ランプ制御コマンドもMODEとEXTの2バイト構成である。図22に示す例において、コマンド8000(H)〜8031(H)は、可変表示装置9における特別図柄の変動パターンに対応したランプ・LED表示制御パターンを指定するランプ制御コマンドである。また、コマンドA0XX(X=4ビットの任意の値)は、特別図柄の可変表示の停止時のランプ・LED表示制御パターンを指示するランプ制御コマンドである。コマンドBXXXは、大当り遊技開始から大当り遊技終了までの間のランプ・LED表示制御パターンを指示するランプ制御コマンドである。そして、コマンドC000は、客待ちデモンストレーション時のランプ・LED表示制御パターンを指示するランプ制御コマンドである。

FIG. 22 is an explanatory diagram showing an example of the content of the lamp control command. The lamp control command also has a 2-byte configuration of MODE and EXT. In the example shown in FIG. 22, commands 8000 (H) to 8031 (H) are lamp control commands for designating a lamp / LED display control pattern corresponding to a special symbol variation pattern in the

なお、コマンド8XXX、AXXX、BXXXおよびCXXXは、遊技進行状況に応じて遊技制御手段から送信されるランプ制御コマンドである。ランプ制御手段は、主基板31の遊技制御手段から上述したランプ制御コマンドを受信すると図22に示された内容に応じてランプ・LEDの表示状態を変更する。

The commands 8XXX, AXXX, BXXX and CXXX are ramp control commands transmitted from the game control means in accordance with the game progress status. When the lamp control means receives the lamp control command described above from the game control means of the

コマンドE0XXは、始動記憶表示器18の点灯個数を示すランプ制御コマンドである。例えば、ランプ制御手段は、始動記憶表示器18における「XX」で指定される個数の表示器を点灯状態とする。また、コマンドE1XXは、普通図柄始動記憶表示器41の点灯個数を示すランプ制御コマンドである。例えば、ランプ制御手段は、普通図柄始動記憶表示器41における「XX」で指定される個数の表示器を点灯状態とする。すなわち、それらのコマンドは、保留個数という情報を報知するために設けられている発光体の制御を指示するコマンドである。なお、始動記憶表示器18および普通図柄始動記憶表示器41の点灯個数に関するコマンドが点灯個数の増減を示すように構成されていてもよい。

The command E0XX is a lamp control command indicating the number of lighting of the

コマンドE200およびE201は、賞球ランプ51の表示状態に関するランプ制御コマンドであり、コマンドE300およびE301は、球切れランプ52の表示状態に関するランプ制御コマンドである。ランプ制御手段は、主基板31の遊技制御手段から「E201」のランプ制御コマンドを受信すると賞球ランプ51の表示状態を賞球残がある場合としてあらかじめ定められた表示状態とし、「E200」のランプ制御コマンドを受信すると賞球ランプ51の表示状態を賞球残がない場合としてあらかじめ定められた表示状態とする。

The commands E200 and E201 are lamp control commands related to the display state of the winning

また、主基板31の遊技制御手段から「E300」のランプ制御コマンドを受信すると球切れランプ52の表示状態を球あり中の表示状態とし、「E301」のランプ制御コマンドを受信すると球切れランプ52の表示状態を球切れ中の表示状態とする。すなわち、コマンドE200およびE201は、未賞球の遊技球があることを遊技者等に報知するために設けられている発光体を制御することを示すコマンドであり、コマンドE300およびE301は、補給球が切れていることを遊技者や遊技店員に報知するために設けられている発光体を制御することを示すコマンドである。

When the lamp control command “E300” is received from the game control means of the

コマンドE400は、遊技機の電源投入時、または特別遊技状態(高確率状態や時短状態、この例では高確率状態)から通常状態(低確率状態や非時短状態、この例では低確率状態)に移行したときのランプ・LED表示制御パターンを指示するランプ制御コマンドである。コマンドE401は、通常状態(低確率状態や非時短状態、この例では低確率状態)から特別遊技状態(高確率状態や時短状態、この例では高確率状態)に移行したときのランプ・LED表示制御パターンを指示するランプ制御コマンドである。コマンドE402は、大当り遊技中に発生したエラーが解除されたときのランプ・LED表示制御パターンを指示するランプ制御コマンドである。そして、コマンドE403は、カウントスイッチ23のエラーが発生したときのランプ・LED表示制御パターンを指示するランプ制御コマンドである。

The command E400 is changed from a special gaming state (high probability state or short time state, high probability state in this example) to a normal state (low probability state or non-time short state, low probability state in this example) when the gaming machine is turned on. This is a lamp control command for instructing a lamp / LED display control pattern at the time of transition. The command E401 is a lamp / LED display when a transition is made from a normal state (low probability state or non-time-short state, low probability state in this example) to a special game state (high probability state or time-short state, high probability state in this example). This is a lamp control command for designating a control pattern. The command E402 is a lamp control command for instructing a lamp / LED display control pattern when an error occurring during the big hit game is canceled. The command E403 is a lamp control command for instructing a lamp / LED display control pattern when an error of the

ランプ制御コマンドは、例えば、遊技制御処理(図16参照)における特別図柄プロセス処理や賞球処理において、変化後の制御状態を示すコマンドとしてランプ制御手段に送信される。制御状態が変化したか否かは、特別図柄プロセス処理や賞球処理等で判定される。 The lamp control command is transmitted to the lamp control means as a command indicating the control state after the change in, for example, a special symbol process or a prize ball process in the game control process (see FIG. 16). Whether the control state has changed is determined by special symbol process processing, prize ball processing, or the like.

図23は、音制御コマンドの内容の一例を示す説明図である。音制御コマンドもMODEとEXTの2バイト構成である。図23に示す例において、コマンド8XXX(X=4ビットの任意の値)は、特別図柄の変動期間における音発生パターンを指定する音制御コマンドである。コマンドBXXX(X=4ビットの任意の値)は、大当り遊技開始から大当り遊技終了までの間における音発生パターンを指定する音制御コマンドである。その他のコマンドは、特別図柄の変動および大当り遊技に関わらない音制御コマンドである。音制御基板70に搭載されている音制御手段は、主基板31の遊技制御手段から上述した音制御コマンドを受信すると図23に示された内容に応じて音声出力状態を変更する。

FIG. 23 is an explanatory diagram showing an example of the contents of a sound control command. The sound control command also has a 2-byte structure of MODE and EXT. In the example shown in FIG. 23, a command 8XXX (X = any value of 4 bits) is a sound control command for designating a sound generation pattern in a special symbol variation period. The command BXXX (arbitrary value of X = 4 bits) is a sound control command for designating a sound generation pattern from the start of the big hit game to the end of the big hit game. The other commands are sound control commands that are not related to special symbol changes and jackpot games. When the sound control means mounted on the

音制御コマンドは、例えば、遊技制御処理(図16参照)における特別図柄プロセス処理において、変化後の制御状態を示すコマンドとして音制御手段に送信される。制御状態が変化したか否かは、特別図柄プロセス処理等で判定される。 For example, in the special symbol process in the game control process (see FIG. 16), the sound control command is transmitted to the sound control means as a command indicating the control state after the change. Whether or not the control state has changed is determined by special symbol process processing or the like.

図24は、払出制御コマンドの内容の一例を示す説明図である。図24に示された例において、MODE=FF(H),EXT=00(H)のコマンドFF00(H)は、払出が可能であることを指示する払出制御コマンド(払出可能状態指定コマンド)である。MODE=FF(H),EXT=01(H)のコマンドFF01(H)は、払出を停止すべき状態であることを指示する払出制御コマンド(払出停止状態指定コマンド)である。また、MODE=F0(H)のコマンドF0XX(H)は、賞球個数を指定する払出制御コマンドである。EXTである「XX」が払出個数を示す。 FIG. 24 is an explanatory diagram showing an example of the contents of the payout control command. In the example shown in FIG. 24, the command FF00 (H) with MODE = FF (H) and EXT = 00 (H) is a payout control command (payout enable state designation command) for instructing that payout is possible. is there. A command FF01 (H) with MODE = FF (H) and EXT = 01 (H) is a payout control command (payout stop state designation command) for instructing that payout should be stopped. A command F0XX (H) with MODE = F0 (H) is a payout control command for designating the number of winning balls. “XX”, which is EXT, indicates the number of payouts.

払出制御手段は、主基板31の遊技制御手段からFF01(H)の払出制御コマンドを受信すると賞球払出および球貸しを停止する状態となり、FF00(H)の払出制御コマンドを受信すると賞球払出および球貸しができる状態になる。また、賞球個数を指定する払出制御コマンドを受信すると、受信したコマンドで指定された個数に応じた賞球払出制御を行う。

When the payout control means receives the payout control command of FF01 (H) from the game control means of the

表示制御コマンド、ランプ制御コマンド、音制御コマンドおよび払出制御コマンドは共通のコマンド形態になっている。すなわち、いずれの制御コマンドも、8ビットのコマンドデータと、コマンドデータの取り込みを指示する1ビットのINT信号(ストローブ信号)とで構成されている。従って、遊技制御手段におけるコマンドの作成ルーチンおよび送信ルーチンを、各制御コマンドについて共通化することができる。その結果、コマンドの作成と送信とに関するプログラム容量が減少する。なお、この実施の形態では、コマンドの分類を表すMODEデータとコマンドの種類を表すEXTデータとからなる2バイトのコマンドデータで構成されているが、コマンドデータは、1バイトまたは3バイト以上の構成であってもよい。また、図21〜図24に示された各制御コマンドは一例であって制御内容と制御コマンドの割り当て方は任意である。 The display control command, the lamp control command, the sound control command, and the payout control command are in a common command form. In other words, each control command is composed of 8-bit command data and a 1-bit INT signal (strobe signal) for instructing the capture of the command data. Therefore, the command creation routine and the transmission routine in the game control means can be made common for each control command. As a result, the program capacity for command creation and transmission is reduced. In this embodiment, the command data is composed of 2-byte command data composed of MODE data representing the classification of the command and EXT data representing the command type, but the command data is composed of 1 byte or 3 bytes or more. It may be. Moreover, each control command shown in FIGS. 21 to 24 is an example, and the control content and the method of assigning the control command are arbitrary.

さらに、表示制御コマンド、ランプ制御コマンドおよび音制御コマンドに関して、コマンド8XXX、AXXX、BXXXおよびCXXXは、遊技進行状況に応じて遊技制御手段から同時期に送信される。例えば、変動パターン1で可変表示装置9において図柄の変動が開始されるときには、図柄制御基板80、ランプ制御基板35および音制御基板70に対して、同一のコマンド8000(H)が送信される。つまり、遊技制御手段は、複数の電気部品制御基板に対して、1種類の制御コマンドを送信するだけでよい。このように、この実施の形態では、遊技の進行に応じて、制御状態が変化したときに、複数の電気部品制御基板に対して同じコマンドを送信することができる。この結果、制御コマンドの種類数を削減することができる。

Further, regarding the display control command, the lamp control command, and the sound control command, commands 8XXX, AXXX, BXXX, and CXXX are transmitted from the game control means at the same time according to the game progress status. For example, when the variation of the symbol is started in the

なお、制御状態の変化とは、例えば、電気部品制御手段が、制御対象の動作(例えば、可変表示装置9の表示状態、各種ランプ・LEDの点灯パターン、スピーカ27からの音発生パターン)を変更する必要があると判断することである。

The change in the control state means, for example, that the electrical component control means changes the operation to be controlled (for example, the display state of the

また、各制御コマンドは、電気部品制御基板に搭載されている電気部品制御手段が認識可能に1回だけ送信される。認識可能とは、この例では、INT信号のレベルが変化することであり、認識可能に1回だけ送信されるとは、この例では、コマンドデータの1バイト目および2バイト目のそれぞれに応じてINT信号が1回だけパルス状(矩形波状)に出力されることである。 Each control command is transmitted only once so that the electric component control means mounted on the electric component control board can be recognized. In this example, “recognizable” means that the level of the INT signal changes. In this example, “recognizable to be transmitted only once” corresponds to each of the first and second bytes of command data. Thus, the INT signal is output in a pulse shape (rectangular wave shape) only once.

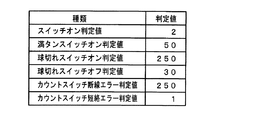

次に、メイン処理におけるスイッチ処理(ステップS21)の具体例を説明する。この実施の形態では、各スイッチの検出信号のオン状態が所定時間継続すると、確かにスイッチがオンしたと判定されスイッチオンに対応した処理が開始される。所定時間を計測するために、スイッチタイマが用いられる。スイッチタイマは、バックアップRAM領域に形成された1バイトのカウンタであり、検出信号がオン状態を示している場合に2ms毎に+1される。図25に示すように、スイッチタイマは検出信号の数N(クリアスイッチ921の検出信号を除く)だけ設けられている。この実施の形態ではN=12である。また、RAM55において、各スイッチタイマのアドレスは、入力ポートのビット配列順(図14に示された上から下への順)と同じ順序で並んでいる。

Next, a specific example of the switch process (step S21) in the main process will be described. In this embodiment, when the ON state of the detection signal of each switch continues for a predetermined time, it is determined that the switch has been turned ON, and processing corresponding to the switch ON is started. A switch timer is used to measure the predetermined time. The switch timer is a 1-byte counter formed in the backup RAM area, and is incremented by 1 every 2 ms when the detection signal indicates an ON state. As shown in FIG. 25, the switch timer is provided for the number N of detection signals (excluding the detection signal of the clear switch 921). In this embodiment, N = 12. Further, in the

図26は、遊技制御処理におけるステップS21のスイッチ処理の処理例を示すフローチャートである。なお、スイッチ処理は、図16に示すように遊技制御処理において最初に実行される。スイッチ処理において、CPU56は、まず、入力ポート0に入力されているデータを入力する(ステップS101)。次いで、処理数として「8」を設定し(ステップS102)、入賞口スイッチ33aのためのスイッチタイマのアドレスをポインタにセットする(ステップS103)。そして、スイッチチェック処理サブルーチンをコールする(ステップS104)。

FIG. 26 is a flowchart illustrating a processing example of the switch process in step S21 in the game control process. The switch process is first executed in the game control process as shown in FIG. In the switch process, the

図27は、スイッチチェック処理サブルーチンを示すフローチャートである。スイッチチェック処理サブルーチンにおいて、CPU56は、ポート入力データ、この場合には入力ポート0からの入力データを「比較値」として設定する(ステップS121)。また、クリアデータ(00)をセットする(ステップS122)。そして、ポインタ(スイッチタイマのアドレスが設定されている)が指すスイッチタイマをロードするとともに(ステップS123)、比較値を右(上位ビットから下位ビットへの方向)にシフトする(ステップS124)。比較値には入力ポート0のデータ設定されている。そして、この場合には、入賞口スイッチ33aの検出信号がキャリーフラグに押し出される。

FIG. 27 is a flowchart showing a switch check processing subroutine. In the switch check processing subroutine, the

キャリーフラグの値が「1」であれば(ステップS125)、すなわち入賞口スイッチ33aの検出信号がオン状態であれば、スイッチタイマの値を1加算する(ステップS127)。加算後の値が0でなければ加算値をスイッチタイマに戻す(ステップS128,S129)。加算後の値が0になった場合には加算値をスイッチタイマに戻さない。すなわち、スイッチタイマの値が既に最大値(255)に達している場合には、それよりも値を増やさない。

If the value of the carry flag is “1” (step S125), that is, if the detection signal of the winning

キャリーフラグの値が「0」であれば、すなわち入賞口スイッチ33aの検出信号がオフ状態であれば、スイッチタイマにクリアデータをセットする(ステップS126)。すなわち、スイッチがオフ状態であれば、スイッチタイマの値が0に戻る。

If the value of the carry flag is “0”, that is, if the detection signal of the winning

その後、CPU56は、ポインタ(スイッチタイマのアドレス)を1加算するとともに(ステップS130)、処理数を1減算する(ステップS131)。処理数が0になっていなければステップS122に戻る。そして、ステップS122〜S132の処理が繰り返される。

Thereafter, the

ステップS122〜S132の処理は、処理数分すなわち8回繰り返され、その間に、入力ポート0の8ビットに入力されるスイッチの検出信号について、順次、オン状態かオフ状態か否かのチェック処理が行われ、オン状態であれば、対応するスイッチタイマの値が1増やされる。

The processes in steps S122 to S132 are repeated for the number of processes, that is, eight times, and during that time, the detection signal of the switch input to the 8 bits of the

CPU56は、スイッチ処理のステップS105において、入力ポート1に入力されているデータを入力する。次いで、処理数として「4」を設定し(ステップS106)、賞球カウントスイッチ301Aのためのスイッチタイマのアドレスをポインタにセットする(ステップS107)。そして、スイッチチェック処理サブルーチンをコールする(ステップS108)。

The

スイッチチェック処理サブルーチンでは、上述した処理が実行されるので、ステップS122〜S132の処理が、処理数分すなわち4回繰り返され、その間に、入力ポート1の4ビットに入力されるスイッチの検出信号について、順次、オン状態かオフ状態か否かのチェック処理が行われ、オン状態であれば、対応するスイッチタイマの値が1増やされる。

In the switch check processing subroutine, since the above-described processing is executed, the processing in steps S122 to S132 is repeated for the number of processing, that is, four times, and the detection signal of the switch input to the 4 bits of the

なお、この実施の形態では、遊技制御処理が2ms毎に起動されるので、スイッチ処理も2msに1回実行される。従って、スイッチタイマは、2ms毎に+1される。 In this embodiment, since the game control process is started every 2 ms, the switch process is also executed once every 2 ms. Therefore, the switch timer is incremented by 1 every 2 ms.

図28〜図30は、遊技制御処理におけるステップS32の賞球処理の一例を示すフローチャートである。この実施の形態では、賞球処理では、賞球払出の対象となる入賞口スイッチ33a,24a,29a,30a、カウントスイッチ23および始動口スイッチ14aが確実にオンしたか否か判定されるとともに、オンしたら賞球個数を示す払出制御コマンドが払出制御基板37に送信されるように制御し、また、満タンスイッチ48および球切れスイッチ187が確実にオンしたか否か判定されるとともに、オンしたら所定の払出制御コマンドが払出制御基板37に送信されるように制御する等の処理が行われる。

28 to 30 are flowcharts showing an example of the prize ball process in step S32 in the game control process. In this embodiment, in the prize ball processing, it is determined whether or not the

賞球処理において、CPU56は、入力判定値テーブルのオフセットとして「1」を設定し(ステップS150)、スイッチタイマのアドレスのオフセットとして「9」を設定する(ステップS151)。入力判定値テーブル(図32参照)のオフセット「1」は、入力判定値テーブルの2番目のデータ「50」を使用することを意味する。また、各スイッチタイマは、図15に示された入力ポートのビット順と同順に並んでいるので、スイッチタイマのアドレスのオフセット「9」は満タンスイッチ48に対応したスイッチタイマが指定されることを意味する。そして、スイッチオンチェックルーチンがコールされる(ステップS152)。

In the prize ball process, the

入力判定値テーブルとは、各スイッチについて、連続何回のオンが検出されたら確かにスイッチがオンしたと判定するための判定値が設定されているROM領域である。入力判定値テーブルの構成例は図32に示されている。図32に示すように、入力判定値テーブルには、上から順に、すなわちアドレス値が小さい領域から順に、「2」、「50」、「250」、「30」、「250」、「1」の判定値が設定されている。また、スイッチオンチェックルーチンでは、入力判定値テーブルの先頭アドレスとオフセット値とで決まるアドレスに設定されている判定値と、スイッチタイマの先頭アドレスとオフセット値とで決まるスイッチタイマの値とが比較され、一致した場合には、例えばスイッチオンフラグがセットされる。 The input determination value table is a ROM area in which a determination value for determining that the switch has been turned on when it is detected how many times it is continuously turned on is set for each switch. A configuration example of the input determination value table is shown in FIG. As shown in FIG. 32, the input determination value table includes “2”, “50”, “250”, “30”, “250”, “1” in order from the top, that is, in order from the smallest address value. The judgment value is set. In the switch-on check routine, the judgment value set at the address determined by the head address and the offset value in the input judgment value table is compared with the value of the switch timer determined by the head address and the offset value of the switch timer. If they match, for example, a switch-on flag is set.