JP4163499B2 - 複数の機能を実施するために複数のリアセンブリ・メモリを使用する方法および装置 - Google Patents

複数の機能を実施するために複数のリアセンブリ・メモリを使用する方法および装置 Download PDFInfo

- Publication number

- JP4163499B2 JP4163499B2 JP2002367651A JP2002367651A JP4163499B2 JP 4163499 B2 JP4163499 B2 JP 4163499B2 JP 2002367651 A JP2002367651 A JP 2002367651A JP 2002367651 A JP2002367651 A JP 2002367651A JP 4163499 B2 JP4163499 B2 JP 4163499B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- memory

- packet

- reassembled

- reassembly

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000015654 memory Effects 0.000 title claims description 85

- 230000006870 function Effects 0.000 title claims description 43

- 238000000034 method Methods 0.000 title claims description 9

- 238000012545 processing Methods 0.000 claims description 68

- 239000004744 fabric Substances 0.000 description 6

- 238000013461 design Methods 0.000 description 5

- 238000004458 analytical method Methods 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 239000000872 buffer Substances 0.000 description 2

- 238000009432 framing Methods 0.000 description 2

- 238000003672 processing method Methods 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- 238000013459 approach Methods 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000011218 segmentation Effects 0.000 description 1

- 238000000638 solvent extraction Methods 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L49/00—Packet switching elements

- H04L49/90—Buffering arrangements

- H04L49/9084—Reactions to storage capacity overflow

- H04L49/9089—Reactions to storage capacity overflow replacing packets in a storage arrangement, e.g. pushout

- H04L49/9094—Arrangements for simultaneous transmit and receive, e.g. simultaneous reading/writing from/to the storage element

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L45/00—Routing or path finding of packets in data switching networks

- H04L45/56—Routing software

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L45/00—Routing or path finding of packets in data switching networks

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L45/00—Routing or path finding of packets in data switching networks

- H04L45/60—Router architectures

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L47/00—Traffic control in data switching networks

- H04L47/50—Queue scheduling

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L49/00—Packet switching elements

- H04L49/90—Buffering arrangements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L49/00—Packet switching elements

- H04L49/90—Buffering arrangements

- H04L49/9042—Separate storage for different parts of the packet, e.g. header and payload

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

Description

【発明の属する技術分野】

本発明は一般にパケット処理システムに関し、より詳細には、このようなパケット処理システムに関連する複数の機能を実施するために複数のリアセンブリ・メモリを使用することに関する。

【0002】

【従来の技術】

周知のように、パケット処理システムのルータまたは他のタイプのパケット・スイッチ内で実施されるある種のプロセスの間は、パケットが「セル」と呼ばれるデータ・サブセットまたはデータ部分にセグメント化されることがある。例えば、ルータ・フレーミング動作中に、パケットがセルにセグメント化されることがある。しかし、これらのデータ・セルは、ルータ内で実施される他のプロセスまたは機能によって使用されるように、再びパケットまたはプロトコル・データ・ユニット(PDU)にリアセンブルしなければならない。

【0003】

従来のルータは通常、パケットをリアセンブルし、これらを、ルータが実施する複数の機能に後で使用するために共通のリアセンブリ・メモリに記憶する。このような機能には、例えばパケット分類やパケット・スケジューリングを含めることができる。しかし周知のように、このような複数の機能によって使用するためにパケットをリアセンブルすることは、非常に高い入出力帯域幅を必要とする。

【0004】

共通の高帯域幅メモリを使用して複数の機能を実施することには、多くの重大な欠点がある。第1に、このような高帯域幅メモリは、非常に高価である可能性がある。また通常、追加ピンや特殊なバッファや特殊な制御機構などが必要になるので、関連するメモリ・インタフェース・デバイスも高価となる。さらに、共通の高帯域幅リアセンブリ・メモリを使用すると、メモリ区分化設計の作業が非常に困難になり、特に、設計を複数の集積回路中に実装する場合は困難である。

【0005】

【発明が解決しようとする課題】

したがって、リアセンブルしたパケットを、パケット処理システム内で実施する複数の機能において後で使用できるように、共通の高帯域幅メモリを使用して記憶することに関連するこれらおよび他の欠点に対処する技法が必要とされていることは明らかである。

【0006】

【課題を解決するための手段】

本発明は、パケット処理システムに関連する複数の機能を実施するために複数のリアセンブリ・メモリを利用し、それにより従来の共通の高帯域幅メモリの使用に起因する欠点を回避する、パケット処理技法を提供する。

【0007】

本発明の一態様では、処理システムが、第1の機能を実施するための第1の処理回路と、第1の処理回路に結合された、受信パケットを記憶するための第1のメモリ回路とを備え、第1のメモリ回路によって記憶されたパケットの少なくとも一部は、第1の処理回路が第1の機能に従って使用可能である。処理システムはさらに、第2の機能を実施するための少なくとも第2の処理回路と、第2の処理回路に結合された、第1のメモリ回路に記憶されるのと同じパケットの少なくとも一部を記憶するための少なくとも第2のメモリ回路とを備え、第2のメモリ回路に記憶されたパケットの少なくとも一部は、第2の処理回路が第2の機能に従って使用可能である。

【0008】

したがって本発明は、第1の機能および少なくとも第2の機能を実施するのに必要なメモリが、第1のメモリと少なくとも第2のメモリとに別々に区分化され、これらのメモリがそれぞれ、同じデータをまたは必要なデータの少なくともサブセットを記憶するのに十分な、かつ対応する機能を実施可能にするのに十分な帯域幅を備える、パケット処理システムを提供する。

【0009】

第1の処理回路、第1のメモリ回路、第2の処理回路、および第2のメモリ回路は、同じ集積回路上に実装できることを理解されたい。あるいは、第1の処理回路および第1のメモリ回路は第1の集積回路上に実装し、第2の処理回路および第2のメモリ回路は第2の集積回路上に実装することもできる。

【0010】

処理システムはまた、第1のメモリ回路に結合された第1のリアセンブリ回路であって、受信パケットを第1のメモリ回路に記憶する前にパケット・サブセットをリアセンブルするための第1のリアセンブリ回路と、第2のメモリ回路に結合された少なくとも第2のリアセンブリ回路であって、パケットを第2のメモリ回路に記憶する前に、第1のリアセンブリ回路によってリアセンブルされるのと同じパケット・サブセットの少なくとも一部をリアセンブルするための少なくとも第2のリアセンブリ回路とを備えることもできる。パケット・サブセットはセルであることが好ましい。

【0011】

処理システムはまた、第1のリアセンブリ回路および第2のリアセンブリ回路に結合された解析回路であって、第1のリアセンブリ回路および第2のリアセンブリ回路によってそれぞれ受信パケットがリアセンブルされる際に使用されるようにパケットからの情報を解析するための解析回路を備えることもできる。

【0012】

例示的な一実施形態では、第1の処理回路および第1のメモリ回路は、ネットワーク・プロセッサを構成する。このような場合、第1の機能はパケット分類動作とすることができる。さらに、第2の処理回路および第2のメモリ回路は、トラフィック・マネージャを構成することができる。このような場合、第2の機能はパケット・スケジューリング動作とすることができる。

【0013】

別の例示的な実施形態では、第1の処理回路および第2の処理回路は、ルータなどのパケット交換デバイス内で動作する。このような場合、第1の処理回路および第2の処理回路は、パケット交換デバイスのパケット・ネットワーク・インタフェースとスイッチ・ファブリックとの間で動作する。

【0014】

有利にも、本発明のパケット処理技法では、複数の機能を実施することに関連する必要メモリ帯域幅が低減することにより、かつ処理システム設計全体が単純化される関連影響により、システム性能が向上し、システム・コストが削減される。

【0015】

本発明のこれらおよび他の目的、特徴、および利点は、添付の図面と共に読む以下の本発明の例示的な実施形態の詳細な説明から明らかになるであろう。

【0016】

【発明の実施の形態】

本発明を、パケット・リアセンブリ動作を含む例示的なパケット処理システムとの関連で以下に例示する。ただし本発明は、共通の高帯域幅メモリの使用に起因する欠点を回避するのが望ましい任意のパケット処理システムに対して、より一般的に適用可能であることを理解されたい。

【0017】

本明細書で使用する用語「プロセッサ」は、限定ではなく例としてマイクロプロセッサ、中央処理装置(CPU)、ディジタル信号プロセッサ(DSP)、特定用途向け集積回路(ASIC)、あるいは他のタイプのデータ処理デバイスまたは処理回路、ならびに、これらあるいは他のデバイスまたは回路の一部および組合せを利用して実装できることを理解されたい。

【0018】

例示的な一実施形態における本発明は、パケット処理システムの複数のプロセッサに関連する複数の機能をそれぞれ実施するために複数のリアセンブリ・メモリを利用することにより、共通の高帯域幅リアセンブリ・メモリの使用に起因する欠点を回避する。本発明は、利点の中でもとりわけ、システム性能の向上および設計費用の削減をもたらす。本発明はまた、システム費用の削減ももたらす。これは、所与の帯域幅のメモリを2つ有する方が、2倍の帯域幅のメモリを1つ有するよりも安価であることが多いからであり、後者は従来の手法で必要とされるものである。

【0019】

図1に、本発明の一実施形態による、複数のリアセンブリ・メモリを利用するパケット処理システム100を示す。システム100は、セル・パーサ102と、N個のパケット・プロセッサ104−1〜104−Nを備え、Nは、処理システム100がサポートするようになっているプロセッサの数に等しい整数とすることができる。各パケット・プロセッサ104は、パケット・リアセンブラまたはPDUリアセンブラ106(106−1〜106−N)と、PDUメモリ108(108−1〜108−N)を備える。各プロセッサはまた、それに関連する少なくとも1つのパケット関連機能110(110−1〜110−N)も有する。

【0020】

各プロセッサが複数の機能を実施することができ、任意の2つのプロセッサが同じ機能の異なる部分を実施することができることを理解されたい。また、N個のプロセッサはそれぞれ、N個の、N個より多い、またはN個より少ない集積回路または処理デバイス(1つの集積回路または処理デバイスを含めて)上に実装することができる。

【0021】

さらに、パケット処理システム100は、ルータまたは他のタイプのパケット・スイッチ内に実装することができる。このような場合、各プロセッサがそれぞれのリアセンブリ・メモリに従って実施する機能は、限定ではなく例として、パケット分類やパケット・スケジューリングなどとすることができる。

【0022】

有利にも、図示のように、パケット処理システム100は、N個の機能を実施するのに必要なメモリがN個のメモリ(108−1〜108−N)に区分化されるように設計され、各メモリは、対応する機能を実施するために同じデータを、または少なくとも選択された必要データをリアセンブルするのに十分な帯域幅を提供する。したがって、データをリアセンブルして、N個のメモリのそれぞれに並行して記憶することができる。並行動作は、同時、またはほぼ同時(例えばいくらかの時間だけ遅延する)とすることができる。したがって、共通の高帯域幅リアセンブリ・メモリに関連する前述の欠点は、有利にも回避される。

【0023】

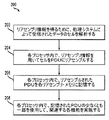

図2に、本発明の一実施形態による、複数のリアセンブリ・メモリを利用するパケット処理方法200を示す。具体的には、図2は、図1に示した複数のリアセンブリ・メモリ構成に関して以下に述べる。

【0024】

前述のように、ある種のルータ・プロセス(例えばルータ・フレーミング動作)の間、パケットが「セル」と呼ばれるデータ・サブセットまたはデータ部分にセグメント化されることがある。したがって、セルは通常、パケットのサブセットであり、ヘッダおよびペイロードを含むことがある。例えばセルは、完全なパケットの最初、中間、または最後(あるいはこれらの何らかの組合せ)を含むことがある。しかし、これらのセルのすべてまたはいくつかは、機能110−1〜110−Nによってそれぞれ使用されるように、再びパケットまたはPDUにリアセンブルしなければならない。

【0025】

したがって、ステップ202で、データ処理システム100によって受信されたセルをパーサ102によって解析する。解析動作は、セルからリアセンブリ情報を抽出することを含む。周知のように、リアセンブリ情報は、パケットに関連するデータを、パケットがセルにセグメント化された以前の元の順序またはシーケンスにどのようにリアセンブルするかをリアセンブラ106に指示するデータである。

【0026】

ステップ204で、リアセンブリ情報およびセルを、パーサ102から各プロセッサ104の各リアセンブラ106に渡す。次いで、リアセンブラはそれぞれ、リアセンブリ情報を用いて周知のようにセルをPDUにリアセンブルする。

すべてのリアセンブラが同じデータをリアセンブルすることもできるが、このことは必須ではないことを理解されたい。すなわち、各リアセンブラは、それに関連するプロセッサによって実施される機能に特有のデータをリアセンブルするだけでよい。したがって、各リアセンブリ・メモリの帯域幅およびサイズは、機能の処理要件に合わせることができる。

【0027】

次にステップ206で、リアセンブルされたPDUを、各プロセッサ104の各PDUメモリ108に記憶する。最後にステップ208で、各メモリ108に記憶されたリアセンブル済みPDU(またはこのような記憶済みPDUの少なくとも一部)を、各プロセッサが利用して各機能110を実施する。

【0028】

前述のように、図2のステップ204〜208は、パケット処理システム100の全体設計に応じて、各プロセッサ内で同時またはほぼ同時に実施することができる。ただしこのことは必須ではない。

【0029】

次に図3を参照すると、本発明による、パケット分類機能およびパケット・スケジューリング機能をそれぞれ実施するために2つのリアセンブリ・メモリを利用するパケット処理システム300が示されている。より具体的には、図3は、図1の処理システム100の特定の例(Nが2に等しい場合)を表すことを理解されたい。

【0030】

パケット処理システム300は、メモリ304を備えるネットワーク・プロセッサ302と、メモリ308を備えるトラフィック・マネージャ306を含む。この例示的な実施形態では、メモリ304を備えるネットワーク・プロセッサ302は、対応するリアセンブリ・メモリ回路を備える1つのプロセッサまたは処理回路を表し、トラフィック・マネージャ306およびメモリ308は、対応するリアセンブリ・メモリ回路を備える他のプロセッサまたは処理回路を表すことを理解されたい。

【0031】

周知のように、図3に示すようなネットワーク・プロセッサは一般に、非同期転送モード(ATM)ネットワークまたは光同期伝送網(SONET)の物理層部分など物理転送媒体と、ルータ内または他のタイプのパケット・スイッチ内のスイッチ・ファブリックとの間で、パケットのフローを制御する。ネットワーク・プロセッサの機能の1つは、パケット分類である。図3に示すようなトラフィック・マネージャは一般に、ネットワーク・プロセッサと共に動作し、機能の中でもとりわけ、バッファ管理およびパケット・スケジューリングを実施する。

【0032】

したがって図示のように、ネットワーク・プロセッサ302およびトラフィック・マネージャ306は、これらのプロセッサとネットワーク312(例えばATMやSONETなど)との間のインタフェース(例えば物理層インタフェースやフレーマ)を提供するネットワーク・インタフェース310と、スイッチ・ファブリック314との間に機能的に位置する。ネットワーク312は、パケットまたはその他のパケット・データを送ってくるネットワークである。スイッチ・ファブリック314は、パケットの交換を制御する。2つのプロセッサはまた、この2つのプロセッサに対する制御全体を提供するホストCPU316に応答する。

【0033】

周知のように、ルータおよびスイッチは一般に複数のプロセッサを備え、これらのプロセッサは、例えば各ライン・カードに1つまたは複数のプロセッサが関連付けられたライン・カード・アレイの形で構成される。したがって、この実施形態では、ネットワーク・プロセッサ302およびトラフィック・マネージャ306は、ルータまたは他のタイプのパケット・スイッチのライン・カードまたはポート・カード上に実装されたプロセッサを表すことができることを理解されたい。ネットワーク・プロセッサおよびトラフィック・マネージャは、同じ集積回路上に実装することもでき、異なる集積回路上に実装することもできる。

【0034】

したがって、この特定の実施形態にかんがみて図2の各ステップを再び参照すると、システム300内のセル(例えばネットワーク・インタフェース300および/またはスイッチ・ファブリック314に関連するセグメント化によって生成されたもの)を、リアセンブリ情報を得るために解析する(ステップ202)。パーサは、ネットワーク・プロセッサ302内またはトラフィック・マネージャ306内のいずれかに実装することができる。次いで、各プロセッサ302および306によって、セルを同時またはほぼ同時に元のパケットにリアセンブルし(ステップ204)、関連するメモリ304および308に記憶する(ステップ206)ことができる。次いで、各メモリに記憶されたリアセンブル済みパケットを、各プロセッサが利用して各機能を実施する(ステップ208)。例えば、ネットワーク・プロセッサ302内でのパケット分類や、トラフィック・マネージャ306内でのパケット・スケジューリングを実施する。

【0035】

本発明の例示的な実施形態について、添付の図面を参照しながら本明細書に述べたが、本発明は、これらの厳密な実施形態に限定するものではなく、当業者なら本発明の範囲および趣旨を逸脱することなくその他様々な変更および修正を加えることができることを理解されたい。

【図面の簡単な説明】

【図1】本発明の一実施形態による、複数のリアセンブリ・メモリを利用するパケット処理システムを示すブロック図である。

【図2】本発明の一実施形態による、複数のリアセンブリ・メモリを利用するパケット処理方法を示す流れ図である。

【図3】本発明の一実施形態による、パケット分類およびパケット・スケジューリングをそれぞれ実施するために2つのリアセンブリ・メモリを利用するパケット処理システムを示すブロック図である。

Claims (9)

- 処理システムであって、

第1の処理回路に関連づけられた、受信されたパケットのサブセットをリアセンブルされたパケットにリアセンブルするための第1のリアセンブリ回路と、

第1の機能を実施するための第1の処理回路と、

第1の処理回路に関連づけられた、第1のリアセンブリ回路によりリアセンブルされたパケットを記憶するための第1のメモリ回路であって、第1のメモリ回路によって記憶されたリアセンブルされたパケットの少なくとも一部は第1の処理回路が第1の機能に従って使用可能である、第1のメモリ回路と、

第2の機能を実施するための少なくとも第2の処理回路と、

第2の処理回路に関連づけられた、第1のリアセンブリ回路によりリアセンブルされたパケットと同じサブセットの少なくとも一部分をリアセンブルされたパケットにリアセンブルするための少なくとも第2のリアセンブリ回路と、

第2の処理回路に関連づけられた、第2のリアセンブリ回路によってリアセンブルされたパケットを記憶するための少なくとも第2のメモリ回路であって、第1のメモリ回路および第2のメモリ回路に記憶された、リアセンブルされたパケットの少なくとも一部分が同じになるようにし、第2のメモリ回路に記憶されたリアセンブルされたパケットの少なくとも一部分は第2の処理回路が第2の機能に従って使用可能である、第2のメモリ回路とを備える処理システム。 - 第1の処理回路、第1のリアセンブリ回路、第1のメモリ回路、第2の処理回路、第2のリアセンブリ回路および第2のメモリ回路が1つの集積回路上に実装される、請求項1に記載のシステム。

- 第1の処理回路、第1のリアセンブリ回路および第1のメモリ回路が第1の集積回路上に実装され、第2の処理回路、第2のリアセンブリ回路および第2のメモリ回路が第2の集積回路上に実装される、請求項1に記載のシステム。

- 第1の機能と第2の機能が1つの集積回路によって実施される、請求項1に記載のシステム。

- 第1の機能と第2の機能が、異なる集積回路によって実施される、請求項1に記載のシステム。

- 第1の処理回路、第1のリアセンブリ回路および第1のメモリ回路がネットワーク・プロセッサを構成する、請求項1に記載のシステム。

- 第2の処理回路、第2のリアセンブリ回路および第2のメモリ回路がトラフィック・マネージャを構成する、請求項1に記載のシステム。

- パケットに応答する処理システム内で使用するための方法であって、

受信パケットのサブセットを第1のリアセンブラ内でリアセンブル済みパケットにリアセンブルするステップと、

リアセンブル済みパケットを第1のメモリに記憶するステップとを含み、第1のメモリによって記憶されたリアセンブル済みパケットの少なくとも一部は、第1のプロセッサが第1の機能に従って使用可能であり、

第1のリアセンブラによってリアセンブルされる受信パケットのサブセットの少なくとも一部は、少なくとも第2のプロセッサが第2の機能に従って使用可能な少なくとも第2のメモリに記憶されるように、少なくとも第2のリアセンブラ内でリアセンブルすることができ、これにより、第1のメモリおよび第2のメモリに記憶されたリアセンブルされたパケットの少なくとも一部分が同じものになり得る方法。 - パケットに応答する処理システム内で使用するための装置であって、

第1のメモリと、

(i)受信パケットのサブセットをリアセンブル済みパケットにリアセンブルするように、かつ(ii)リアセンブル済みパケットを第1のメモリに記憶させるように動作可能な第1のプロセッサとを備え、第1のメモリによって記憶されたリアセンブル済みパケットの少なくとも一部は第1の機能に従って使用可能であり、

第1のプロセッサによってリアセンブルされる受信パケットのサブセットの少なくとも一部は、第2の機能に従って使用可能な少なくとも第2のメモリに記憶されるように、少なくとも第2のプロセッサによってリアセンブルすることができ、これにより、第1のメモリおよび第2のメモリに記憶されたリアセンブルされたパケットの少なくとも一部分が同じものになり得る装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/029679 | 2001-12-21 | ||

| US10/029,679 US8782287B2 (en) | 2001-12-21 | 2001-12-21 | Methods and apparatus for using multiple reassembly memories for performing multiple functions |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003218908A JP2003218908A (ja) | 2003-07-31 |

| JP2003218908A5 JP2003218908A5 (ja) | 2006-02-09 |

| JP4163499B2 true JP4163499B2 (ja) | 2008-10-08 |

Family

ID=21850300

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002367651A Expired - Fee Related JP4163499B2 (ja) | 2001-12-21 | 2002-12-19 | 複数の機能を実施するために複数のリアセンブリ・メモリを使用する方法および装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8782287B2 (ja) |

| EP (1) | EP1326475A1 (ja) |

| JP (1) | JP4163499B2 (ja) |

| KR (1) | KR100941569B1 (ja) |

| TW (1) | TWI254529B (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7280527B2 (en) * | 2002-05-13 | 2007-10-09 | International Business Machines Corporation | Logically grouping physical ports into logical interfaces to expand bandwidth |

| US7379467B1 (en) * | 2003-05-08 | 2008-05-27 | Cypress Semiconductor Corporation | Scheduling store-forwarding of back-to-back multi-channel packet fragments |

| KR100970989B1 (ko) * | 2008-04-28 | 2010-07-21 | 김상현 | 다목적 가위 |

| JP6369175B2 (ja) * | 2014-07-04 | 2018-08-08 | 富士通株式会社 | パケット処理装置、制御プログラム、及びパケット処理装置の制御方法 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5317034A (en) * | 1976-07-30 | 1978-02-16 | Sharp Corp | Image sensor output correcting system |

| US4149243A (en) * | 1977-10-20 | 1979-04-10 | International Business Machines Corporation | Distributed control architecture with post and wait logic |

| US4593357A (en) * | 1982-02-19 | 1986-06-03 | Laboratory Equipment Corp. | Motor vehicle performance monitoring system |

| US4885684A (en) * | 1987-12-07 | 1989-12-05 | International Business Machines Corporation | Method for compiling a master task definition data set for defining the logical data flow of a distributed processing network |

| US5179530A (en) * | 1989-11-03 | 1993-01-12 | Zoran Corporation | Architecture for integrated concurrent vector signal processor |

| US5396490A (en) * | 1992-03-23 | 1995-03-07 | Motorola, Inc. | Packet reassembly method and apparatus |

| US5623494A (en) * | 1995-06-07 | 1997-04-22 | Lsi Logic Corporation | Asynchronous transfer mode (ATM) interconnection system for multiple hosts including advanced programmable interrupt controller (APIC) |

| US6058114A (en) * | 1996-05-20 | 2000-05-02 | Cisco Systems, Inc. | Unified network cell scheduler and flow controller |

| FI974020A0 (fi) | 1997-10-21 | 1997-10-21 | Nokia Telecommunications Oy | Optimering av resurser i ett paketnaetsflerprocessorsystem |

| US6249528B1 (en) * | 1998-03-12 | 2001-06-19 | I-Cube, Inc. | Network switch providing per virtual channel queuing for segmentation and reassembly |

| US6483839B1 (en) * | 1998-03-18 | 2002-11-19 | Conexant Systems, Inc. | Apparatus and method for scheduling multiple and simultaneous traffic in guaranteed frame rate in ATM communication system |

| US6330584B1 (en) * | 1998-04-03 | 2001-12-11 | Mmc Networks, Inc. | Systems and methods for multi-tasking, resource sharing and execution of computer instructions |

| JP3742250B2 (ja) * | 1999-06-04 | 2006-02-01 | 富士通株式会社 | パケットデータ処理装置及びそれを用いたパケット中継装置 |

| US6766381B1 (en) | 1999-08-27 | 2004-07-20 | International Business Machines Corporation | VLSI network processor and methods |

| US6771652B1 (en) * | 1999-11-23 | 2004-08-03 | International Business Machines Corporation | Method and system for controlling transmission of packets in computer networks |

| US6944153B1 (en) * | 1999-12-01 | 2005-09-13 | Cisco Technology, Inc. | Time slot interchanger (TSI) and method for a telecommunications node |

| US6629147B1 (en) * | 2000-03-31 | 2003-09-30 | Intel Corporation | Segmentation and reassembly of data frames |

| US7092393B1 (en) * | 2001-02-04 | 2006-08-15 | Cisco Technology, Inc. | Method and apparatus for distributed reassembly of subdivided packets using multiple reassembly components |

| US6934760B1 (en) * | 2001-02-04 | 2005-08-23 | Cisco Technology, Inc. | Method and apparatus for resequencing of packets into an original ordering using multiple resequencing components |

-

2001

- 2001-12-21 US US10/029,679 patent/US8782287B2/en not_active Expired - Fee Related

-

2002

- 2002-11-29 EP EP02258237A patent/EP1326475A1/en not_active Ceased

- 2002-12-04 TW TW091135163A patent/TWI254529B/zh not_active IP Right Cessation

- 2002-12-19 JP JP2002367651A patent/JP4163499B2/ja not_active Expired - Fee Related

- 2002-12-20 KR KR1020020081687A patent/KR100941569B1/ko not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| KR100941569B1 (ko) | 2010-02-10 |

| TWI254529B (en) | 2006-05-01 |

| JP2003218908A (ja) | 2003-07-31 |

| EP1326475A1 (en) | 2003-07-09 |

| KR20030053050A (ko) | 2003-06-27 |

| TW200304302A (en) | 2003-09-16 |

| EP1326475A8 (en) | 2003-11-12 |

| US8782287B2 (en) | 2014-07-15 |

| US20030120798A1 (en) | 2003-06-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4066382B2 (ja) | ネットワーク・スイッチ及びコンポーネント及び操作方法 | |

| JP3872342B2 (ja) | ネットワークのための装置およびスケーラブル・ネットワーク・プロセッサ | |

| JP3832816B2 (ja) | ネットワーク・プロセッサ、メモリ構成及び方法 | |

| US5959994A (en) | ATM/SONET network enhanced as a universal computer system interconnect | |

| US7100020B1 (en) | Digital communications processor | |

| US5311509A (en) | Configurable gigabits switch adapter | |

| JP3817477B2 (ja) | Vlsiネットワーク・プロセッサ及び方法 | |

| EP1568172B1 (en) | Method for verifying function of redundant standby packet forwarder | |

| CN1543149B (zh) | 网络环境中的流控制 | |

| US6988235B2 (en) | Checksum engine and a method of operation thereof | |

| JP2003508957A (ja) | ネットワーク・プロセッサ処理コンプレックス及び方法 | |

| WO2007149206A2 (en) | Communicating packets between forwarding contexts using virtual interfaces | |

| WO2000001121A9 (en) | Two-dimensional queuing/de-queuing methods and systems for implementing the same | |

| US7912069B2 (en) | Virtual segmentation system and method of operation thereof | |

| US6925514B1 (en) | Multi-protocol bus system and method of operation thereof | |

| US7079539B2 (en) | Method and apparatus for classification of packet data prior to storage in processor buffer memory | |

| JP4163499B2 (ja) | 複数の機能を実施するために複数のリアセンブリ・メモリを使用する方法および装置 | |

| US7379467B1 (en) | Scheduling store-forwarding of back-to-back multi-channel packet fragments | |

| JPH10285173A (ja) | Atmセル処理装置 | |

| US7043544B2 (en) | Processor with multiple-pass non-sequential packet classification feature | |

| US7590056B2 (en) | Processor configured for efficient processing of single-cell protocol data units | |

| JP2003218907A (ja) | パケットの高速ルーティング及びスイッチングに対するメモリ要件を低減するように構成されたプロセッサ | |

| McKeown et al. | Architecture and Performance of the BayBridge: A High Speed Bridge/router Between FDDI and SMDS | |

| WO2002023823A1 (en) | Apparatus and methods for processing packets in a broadband data stream |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051216 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20051216 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071121 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20080221 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20080226 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080521 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080630 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080724 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110801 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110801 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120801 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130801 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |