JP3885262B2 - テクスチャマップ上の複数画素を混合する方法及び、これを用いた複数画素混合回路と画像処理装置 - Google Patents

テクスチャマップ上の複数画素を混合する方法及び、これを用いた複数画素混合回路と画像処理装置 Download PDFInfo

- Publication number

- JP3885262B2 JP3885262B2 JP33682396A JP33682396A JP3885262B2 JP 3885262 B2 JP3885262 B2 JP 3885262B2 JP 33682396 A JP33682396 A JP 33682396A JP 33682396 A JP33682396 A JP 33682396A JP 3885262 B2 JP3885262 B2 JP 3885262B2

- Authority

- JP

- Japan

- Prior art keywords

- pixels

- transparent

- pixel

- texture

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06T—IMAGE DATA PROCESSING OR GENERATION, IN GENERAL

- G06T11/00—2D [Two Dimensional] image generation

- G06T11/001—Texturing; Colouring; Generation of texture or colour

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2340/00—Aspects of display data processing

- G09G2340/10—Mixing of images, i.e. displayed pixel being the result of an operation, e.g. adding, on the corresponding input pixels

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Image Generation (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は、テクスチャマップ上の複数画素を混合する方法及び、これを用いた複数画素混合回路と画像処理装置に関する。

【0002】

【従来の技術】

近年、コンピュータグラフィック技術を用い、仮想3次元空間内に配置された物体を複数のポリゴンで画像表示する画像処理装置が普及している。更に、表示される物体をより現実に近いものとすべく研究開発が進められている。

【0003】

かかるコンピュータグラフィック技術において、表示される物体の表面の細部はテクスチャと呼ばれる。該当ポリゴンを構成するポリゴンの画素(ピクセル)毎にテクスチャデータをテクスチャマップから読み出し貼り付けることにより、物体の表面に色肌、材質感等が形成される。

【0004】

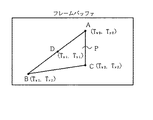

図8、図9は、かかるテクスチャデータの貼り付けを説明する図である。即ち、図8は、CRTディスプレー等の表示装置に表示するために、二次元座標平面に展開され、フレームバッファに格納されたポリゴンの一例である。

【0005】

図示されるかかるポリゴンPは、3頂点A、B、Cを有し、それぞれの頂点は貼り付けられるテクスチャデータを格納するテクスチャマップ上のX、Y2軸の座標を頂点データとして有する。

【0006】

例えば、頂点Aの画素に貼り付けられるテクスチャデータの格納位置として、図8に示されるように図9のテクスチャマップ上の座標データ(Tx0,Ty0)を有する。同様に、頂点Bは座標データ(Tx1,Ty1)を有し、頂点Cは座標データ(Tx2,Ty2)を有する。

【0007】

更に、例えば頂点Aと頂点Bの稜線上の点Dの画素に対しては、頂点Aの座標データ(Tx0,Ty0)と頂点Bの座標データ(Tx1,Ty1)を線型もしくはパースペクティブ補間をして、図9に示されるように、テクスチャマップ上の座標Dのデータ(Txi,Tyi)が求められる。

【0008】

ポリゴンPを構成する他の全ての画素に対しても、同様に線型もしくはパースペクティブ補間によりテクスチャマップ上の座標データが求められる。

【0009】

一方、テクスチャマップは、物体のテクスチャ種類毎に例えば、物体が岩であれば岩肌を表現するデータ、木材であれば木肌等を表現するデータがマップ状に展開され、メモリ装置に格納される。即ち、一つの岩における岩肌、一本の樹の木肌等は、1つのデータで定義できるようには均一ではなく、また連続性を持って変化する。

【0010】

従って、テクスチャマップは、岩肌、木肌等のテクスチャをX、Y2軸座標平面に展開したものであり、X、Y2軸座標位置を特定することにより、対応する特定位置の岩肌、木肌等のテクスチャが求められる。

【0011】

ここで、図10に示されるテクスチャマップの2軸平面とポリゴンの一画素との関係を考察する。図10において、太線で囲われた領域70は、ポリゴンを構成する1画素に対応してテクスチャマップの座標を指定した範囲である。領域71〜74は、テクスチャマップ上の複数の画素である。従って、この領域70に対し、テクスチャマップから読み出されるテクスチャデータに基づきテクスチャが該当の画素に貼り付けられる。

【0012】

しかし、上記のようにポリゴンを構成する1画素とテクスチャマップの画素とは必ずしも対応せず、ポリゴンを構成する1画素で指定される領域70は、テクスチャマップの隣接する複数の画素に跨る。図10の例では、領域70は、テクスチャマップの隣接する4つの画素71〜74に跨って重なる。

【0013】

このために、領域70に対応するポリゴンを構成する1画素に対するテクスチャは、隣接する4つの画素71〜74のデータを領域70の重なる面積に応じて混合して、対応するテクスチャデータを求めることが行われる。

【0014】

しかし、ポリゴンの中には、一部に穴の開いた部分を表現するものがある。この開いた部分に対応するテクスチャデータは透明色となる。従って、かかる場合は、ポリゴンに対しテクスチャを貼り付ける際に混合されるテクスチャマップ上の当該ポリゴンに対応する複数の画素の中に、透明であるテクスチャ画素が存在することになる。

【0015】

かかる場合は、混合に際し留意が必要である。なぜならば、透明色を隣接する画素に混合する場合は、色合いが異質になる恐れがあるからである。

【0016】

ここで上記したように、面積に応じて複数画素のテクスチャデータを混合する場合、図10でのテクスチャの画素71〜74の色をそれぞれ color0、 color1、 color2、 color3 とし、更に color1 が透明であるとする時、関係する面積に応じた寄与分から正規化した想定される計算式として数1または数2のように表わされる。

【0017】

【数1】

【0018】

または、

【0019】

【数2】

color=color0(1-x)(1-y)+color1x(1-y)+color2(1-x)y+color3xy

即ち、数1では透明である color1 の画素72のデータを除外して計算する。一方、数2は、透明である color1 の画素72のデータも含めて計算している。

【0020】

【発明が解決しようとする課題】

上記数1、数2のいずれの計算方法においても問題がある。前者の場合は透明である画素の色は、無視することが出来る。しかし、除算を行うために回路構成が複雑となる。

【0021】

一方、後者の場合は、除算を行うための回路構成は必要でなくなるが、透明であるはずの画素72の色が混合されてしまう。この場合、透明な画素72にもテクスチャマップ上の隣接の画素の色と整合性を与える色を与えておくことが必要となり、データ処理上煩雑となる。

【0022】

したがって、本発明の目的は、かかる問題を解決するために、テクスチャマップ上の透明である画素の色を混合しない回路構成であって、構成が簡易な複数画素混合方法及び回路を提供することにある。

【0023】

更に本発明の目的は、上記の本発明に従う複数画素混合方法及び回路を用いた画像処理装置を提供することにある。

【0024】

【課題を解決するための手段】

上記の本発明の課題を達成する複数画素混合方法の第1の構成は、ポリゴンを構成する画素に対応するテクスチャマップ上の複数画素を混合して、該ポリゴンを構成する画素に貼り付けるテクスチャデータを求める複数画素混合方法において、該テクスチャマップ上の複数画素の中に透明画素があるか否かを判断し、透明画素がない場合は、該テクスチャマップ上の複数画素を該ポリゴンを構成する画素が対応する割合に応じて混合し、該テクスチャマップ上の複数画素の一部が透明画素である場合は、該透明画素を他の隣接する透明でない画素で置き換え、更に、該テクスチャマップ上の複数画素の全てが透明画素である場合は、該テクスチャマップ上の複数画素を無視するようにする。

【0025】

更に、本発明に従う複数画素混合方法の第2の構成は、ポリゴンを構成する画素に対応するテクスチャマップ上の複数画素を混合して、該ポリゴンを構成する画素に貼り付けるテクスチャデータを求める複数画素混合方法において、該テクスチャマップ上の一の行アドレス方向に隣接する第1の複数画素に透明画素があるか否かを判断し、該一の行アドレス方向に隣接する第1の複数画素に透明画素がない場合は、該第1の複数画素を該ポリゴンを構成する画素が対応する割合に応じて混合し、該一の行アドレス方向に隣接する第1の複数画素の一部の画素が透明画素である場合は、該透明画素を隣接する透明でない画素で置き換え、該一の行アドレス方向に隣接する第1の複数画素の全てが透明画素である場合は、該複数画素を無視する第1の工程と、

該テクスチャマップ上の該一の行に隣接する行アドレス方向に隣接する第2の複数画素に透明画素があるか否かを判断し、該一の行に隣接する行アドレス方向に隣接する第2の複数画素に透明画素がない場合は、該第2の複数画素を該ポリゴンを構成する画素が対応する割合に応じて混合し、該一の行に隣接する行アドレス方向に隣接する第2の複数画素の一部の画素が透明画素である場合は、該透明画素を隣接する透明でない画素で置き換え、該一の行に隣接する行アドレス方向に隣接する第2の複数画素の全てが透明画素である場合は、該第2の複数画素を無視する第2の工程と、

該第1の工程により得られる第1のテクスチャ画素データと該第2の工程により得られる第2のテクスチャ画素データを比較し、該第1、第2のテクスチャ画素データのいずれも透明でない場合は、該第1、第2のテクスチャ画素データを該ポリゴンを構成する画素が対応する割合に応じて混合し、該第1、第2のテクスチャ画素データのいずれかが透明である場合は、透明であるテクスチャ画素データを他方の透明でないテクスチャ画素データで置き換え、いずれも透明である場合は、該第1及び第2のテクスチャ画素データを無視する第3の工程を有する。

【0026】

また、本発明に従う複数画素混合回路の第1の構成は、ポリゴンを構成する画素に対応するテクスチャマップ上の複数画素を混合して、該ポリゴンを構成する画素に貼り付けるテクスチャデータを求める複数画素混合回路において、テクスチャマップ上の隣接する複数画素を、該ポリゴンを構成する画素が対応する割合に応じて混合する補間演算回路と、該補間演算回路の出力及び、該隣接する複数画素と、該複数画素のそれぞれが透明であるか否かを示すフラグを選択信号として入力し、該選択信号により、該複数画素のいずれもが透明でない場合は、該補間演算回路の出力を有効とし、該複数画素のいずれかが透明である場合は、該複数画素の透明で無い画素を有効とし、該複数画素のいずれもが透明である場合は、出力を無効とする選択回路を有して構成される。

【0027】

更にまた、本発明に従う複数画素混合回路の第2の構成は、第1の複数画素混合回路の構成において、更に、前記隣接する複数画素のアンド論理を出力するアンドゲートを有する。

【0028】

更に、本発明に従う複数画素混合回路の第3の構成は、第2の構成の複数画素混合回路を3組有し、第1及び第2の組の複数画素混合回路の出力を、第3の組の複数画素混合回路の前記補間演算回路の2つの入力とする。

【0029】

また、本発明に従う画像処理装置の第1の構成は、仮想3次元空間内に配置された物体を複数のポリゴンで構成して画像表示する画像処理装置において、X,Y2軸で特定される複数の座標位置にテクスチャデータを格納するテクスチャマップを格納するメモリ装置と、該複数のポリゴンのそれぞれを構成するピクセル毎に、該テクスチャマップから読み出したテクスチャデータを貼り付けるテクスチャ貼り付け回路を有し、該テクスチャ貼り付け回路は、テクスチャマップ上の隣接する複数画素を、該ポリゴンを構成する画素が対応する割合に応じて混合する補間演算回路と、該補間演算回路の出力及び、該隣接する複数画素と、該複数画素のそれぞれが透明であるか否かを示すフラグを選択信号として入力し、該選択信号により、該複数画素のいずれもが透明でない場合は、該補間演算回路の出力を有効とし、該複数画素のいずれかが透明である場合は、該複数画素の透明で無い画素を有効とし、該複数画素のいずれもが透明である場合は、出力を無効とする選択回路を備えた複数画素混合回路を含む。

【0030】

更に、本発明に従う画像処理装置の第2の構成は、第1の構成において、前記複数画素混合回路は、前記隣接する複数画素のアンド論理を出力するアンドゲートを有する。

【0031】

また、本発明に従う画像処理装置の第3の構成は、第1の構成において、前記複数画素混合回路を3組有し、第1及び第2の組の複数画素混合回路の出力を、第3の組の複数画素混合回路の前記補間演算回路の2つの入力とする。

【0032】

【発明の実施の形態】

以下本発明の実施の形態を図面に従い説明する。尚、図面において、同一または類似のものには、同一の参照番号または参照記号を付して説明する。

【0033】

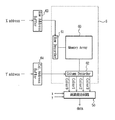

図1は、本発明の複数画素混合方法を用いた画像処理装置の構成ブロック図である。

【0034】

図1において、CPU1は、ポリゴンを使用した画像を処理するためのプログラムの実行を制御するものである。CPU1にはプログラムの進行に伴いディスプレー装置12上に表示するポリゴンの頂点データやレジスタセットファンクションを一次的に蓄えておくメモリであるデータバッファ2が接続されている。

【0035】

このデータバッファ2には、前記データに従って、3次元空間内にポリゴンを配置し、これをディスプレー装置12上に表示するために2次元座標系に変換するためのジオメトリ処理部3が接続されている。

【0036】

更に、表示する各ポリゴンに対し、着色、シェーディング、テクスチャの貼り付けを行うレンダリング処理部10が接続されている。レンダリング処理部10の出力側には、フレームバッファ11が接続され、表示される一画面分のデータが格納される。フレームバッファ11にCRT等のディスプレー装置12が接続され、フレームバッファ11の内容が順次表示される。

【0037】

ここで、上記ジオメトリ処理部3は、データバッファ2からプログラムの進行及び処理速度に対応して、ポリゴンの頂点データ(頂点座標、頂点カラー、テクスチャマップ座標、頂点透明度及び頂点の法線ベクトル等を有する)やレジスタセットファンクションを読み出す。

【0038】

ジオメトリ処理部3は、頂点座標データに基づき3次元空間にポリゴンを配置し、3次元空間のどの領域まで表示対象とするかのビューポートの決定、法線ベクトルに基づき各頂点の輝度の計算等を行う。また、ビューポートよりはみ出すポリゴンの頂点除去即ち、クリッピングを行う。更に、ビューポートに配置されたポリゴンを所定の視点を基準に2次平面に投影して3次元から2次元への座標変換を行う。

【0039】

2次元座標に座標変換されたポリゴンデータは、レンダリング処理部10に送られる。レンダリング処理部10は、塗り潰し回路4、テクスチャ貼り付け回路5、デプステスト回路7、ブレンディング回路9から構成されている。

【0040】

塗り潰し回路4は、ポリゴンの各頂点で囲まれた範囲にある画素(ピクセル)の情報を計算し、他のレンダリング処理部10内の各回路に渡す機能を有する。上記計算は、ポリゴンの各頂点間にあるピクセルの情報を対応の両頂点の情報を基に、例えば線型補間または、パースペクティブ補間等の補間を行うものである。先に図8において説明した頂点A,Bの頂点データからピクセルDのデータを求める如くである。

【0041】

テクスチャ貼り付け回路5は、ピクセルに対応したテクスチャをテクスチャマップ6から読み出し、ピクセルのカラーを計算して求める回路である。ピクセルのカラーを計算して求める回路の構成に本発明の複数画素混合方法及び回路の構成が適用されている。

【0042】

従って、かかる部分の方法及び回路構成については、本発明の実施例として後に詳細に説明する。

【0043】

デプステスト回路7は、複数のポリゴンの前後関係を比較して、最も手前に配置されたポリゴンのデータをデプスバッファ8に記憶させる回路である。即ち、デプスバッファ8には、先に描いた図形(ポリゴン)のピクセルのZ値が記憶されている。

【0044】

そして、画面上の先に描かれたポリゴンと重なる位置に、新しくポリゴンを表示する場合、新しいポリゴンを構成する各ピクセルのZ値と、デプスバッファ8から読み出される先に描かれたポリゴンのピクセルのZ値とを比較する。比較の結果、新しいポリゴンのピクセルが手前の場合は、デプスバッファ8に当該ピクセルのZ値が書き込まれる。

【0045】

ブレンディング回路9は、フレームバッファ11から読み込んだ、先に描かれているポリゴンのピクセルのカラー情報と、新しく処理するポリゴンのピクセルのカラー情報とを混合し、フレームバッファ11に書き込む。このフレームバッファ11の情報が1画面分ずつディスプレー装置12に送られ表示される。

【0046】

次に、上記のような構成の画像処理装置における本発明を適用した複数画素混合方法及び回路の実施例構成を説明する。

【0047】

先に説明したように、ポリゴンを構成する1画素のテクスチャデータを求める場合、当該1画素のテクスチャマップ上の座標データ位置において、画素は面積を持つので、テクスチャマップの隣接する複数の画素と重なる。従って、テクスチャマップの隣接する複数の画素データを組み合わせて、当該ポリゴンを構成する1画素に対するテクスチャデータを生成することが行われる。

【0048】

図2は、図1のテクスチャ貼り付け回路5に含まれる主機能回路としての画素混合回路50と、テクスチャマップ6の詳細を示すブロック図である。

【0049】

テクスチャマップ6は、テクスチャデータがポリゴン対応に展開格納されるメモリアレー60、行アドレスデコーダ61及び列アドレスデコーダ62を有する。更に、テクスチャ貼り付け回路5には、テクスチャマップ6の行アドレスデコーダ61及び列アドレスデコーダ62にそれぞれ行アドレス、列アドレスを送るアドレスバッファ63、64を有する。

【0050】

テクスチャ貼り付け回路5は、塗り潰し回路4から入力されるポリゴンの画素データからテクスチャマップ6の座標位置データを抜き出し、前記行アドレスデコーダ61及び列アドレスデコーダ62に送る。

【0051】

メモリアレー60は、テクスチャ貼り付け回路5から入力した4組の行アドレスと列アドレスにより対応する座標位置にある4画素71〜74のcolor0,color1,color2,color3 のデータを読み出し、複数画素混合回路50に入力する。

【0052】

更に、複数画素混合回路50には、テクスチャ貼り付け回路5において求めたポリゴンの画素を特定する座標とテクスチャマップ60の画素位置とのずれ(x及びy)の値が入力される。

【0053】

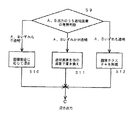

かかる複数画素混合回路50における動作フローが図3〜図5に示される。

【0054】

図10に示す例を用い、テクスチャメモリの画素71から74のテクスチャ(カラー:color0, color1, color2, color3)を混合し、ポリゴンの画素70に貼り付けるテクスチャデータ(カラー:color)を求める場合を考える。

【0055】

図3において、一の行アドレス方向の隣接画素のうち透明画素の有無を判断する(ステップS1)。この判断の結果、隣接画素のいずれも透明画素がない場合は、ポリゴンの画素の占める面積に応じた割合で混合する(ステップS2)。

【0056】

隣接画素のいずれかが、透明である場合は、他の画素で当該透明画素を置き換える(ステップS3)。更に、隣接画素のいずれも透明画素である場合は、画素テクスチャを無視する(ステップS4)。

【0057】

かかる処理を図10に当てはめると、一の行アドレス方向の隣接画素は画素71、72が対応し、画素72が透明であるので、ステップS3の処理が対応し、画素72の透明部分を不透明な画素71の画素で置き換える。即ち、画素71(color0)そのものが出力A(color01) となる。

【0058】

更に、図4において、一の行アドレスに隣接する行アドレス方向の隣接画素のうち透明画素の有無を判断する(ステップS5)。この判断結果による処理は、透明画素が無い場合は(ステップS6)の処理、一部の画素が透明である場合は(ステップS7)の処理、そして全てが透明画素である場合は(ステップS8)の処理となり、これらはそれぞれ図3の(ステップS2)、(ステップS3)、(ステップS4)に対応する。

【0059】

従って、図4の処理を図10に対応させると、隣接する行アドレス方向の隣接画素は画素73、74となる。そして、いずれの画素も透明では無いので画素73、74に対するポリゴンの画素70の占める割合に応じて混合され、出力B(color23) となる。

【0060】

更に、図5は、図3、図4の出力A,Bに基づく処理である。出力A,Bのうち透明画素の有無を判断する(ステップS9)。この判断結果による処理は、透明画素が無い場合は(ステップS10)の処理、一部の画素が透明である場合は(ステップS11)の処理、そして全てが透明画素である場合は(ステップS12)の処理となり、これらはそれぞれ図3、図4の(ステップS2、S6)、(ステップS3、S7)、(ステップS4、S8)に対応する。

【0061】

従って、図5の処理を図10に対応させると、出力A(color01) ,B(color23) のいずれも透明でないので、一の行アドレス方向の隣接画素71、72に対するポリゴンの画素70の占める大きさと、隣接する行アドレス方向の隣接画素73、74に対するポリゴンの画素70の占める大きさとの割合に応じて混合され、出力C(color) となる。

【0062】

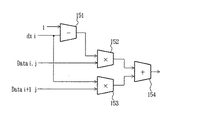

図6は、かかる本発明の複数補画素混合方法を適用する複数画素混合回路50の実施例回路である。上記図3から図5の処理に対応して、3組の同様の回路で構成されている。補間演算回路501、選択回路502及びアンドゲート503により、図10に示す画素71と72を混合したデータ即ち、color0とcolor1を混合した出力color01 を得る。

【0063】

このために補間演算回路501、選択回路502及びアンドゲート503による第1の回路は、数3の計算を行う。

【0064】

【数3】

color01 = color0(1-x) + color1・x

同様に、補間演算回路504、選択回路505及びアンドゲート506による第2の回路は、数4の計算を行い、color2とcolor3を混合した出力color23 を得る。

【0065】

【数4】

color23 = color2(1-x) + color3・x

更に、補間演算回路507、選択回路508及びアンドゲート509による第3の回路は、数5の計算を行い、上記に求めたcolor02 とcolor23 を混合した最終出力としてcolor を得る。

【0066】

【数5】

color = color01(1-y) + color23・y

上記第1〜3の回路の計算原理は同様であるので、補間演算回路501、選択回路502及びアンドゲート503による第1の回路を代表例にして、回路の動作原理を説明する。

【0067】

上記第1の回路において、先ず補間演算回路501によりcolor0とcolor1の二つの画素71、72を混合する。補間演算回路501、504、507の構成例が図7に示される。

【0068】

図7において、入力信号の記号を一般化して示しているが、第1の回路に対応させると、dxi は、xであり、Datai,j 、 Datai,jは、それぞれ画素71、72のcolor0、 color1である。

【0069】

したがって、差回路151は、(1−x)を出力する。次いで、掛け算回路152、153からは、それぞれ(1−x)とcolor0の積color0・(1−x)、xとcolor1との積color1・xを出力する。

【0070】

和回路154は、掛け算回路152、153の出力の和を求め、color0・(1−x)+color1・xを出力し、選択回路502のA入力端に入力する。更に、選択回路502のB,C入力端にはそれぞれcolor0、color1が入力される。

【0071】

一方、それぞれのテクスチャマップの画素データには、画素が透明であるか否かの透明フラグ情報(画素が透明であれば、H論理を有する)が付加されている。従って、 選択回路502にはこのフラグ情報が端子S0 、S1 にセレクタ信号として入力される。

【0072】

選択回路502では、これら端子S0 、S1 に入力されるセレクタ信号の論理に基づき、補間演算回路501の混合出力color01 、または混合前の元の入力であるcolor0、color1が選択され、出力される。

【0073】

即ち、color0及びcolor1がともに透明でない(S0 =S1 =L論理)時、補間演算回路501の混合出力color01 が出力される。color0のみが透明である(S0 =H、S1 =L論理)時、color01 =color1として出力される。

【0074】

更に、color1のみが透明である(S0 =L、S1 =H論理)時、color01 =color0として出力される。color0、color1ともに透明である(S0 =H、S1 =H論理)時、混合の結果は特定されない。この時、選択回路502の出力color01 に対する透明フラグは、アンドゲート503の出力であり、H論理となる。この時、color01 の画素の色は無視される。

【0075】

上記の様にして、第1の回路により、数3の計算式に対応する出力color01 が得られる。更に、補間演算回路504、選択回路505及びアンドゲート506による第2の回路、補間演算回路507、選択回路508及びアンドゲート509による第3の回路の動作も第1の回路と同様である。

【0076】

即ち、第2の回路は、color2とcolor3を入力して、数4の計算に対応する出力color23 を出力する。第3の回路は、第1の回路の出力color01 と第2の回路の出力color23 を入力して数5の計算に対応する出力color を出力する。

【0077】

【発明の効果】

以上、図にしたがい実施例を説明したように、本発明に従う画素混合回路は、簡易な論理構成で実現でき且つ、透明な画素も考慮することが可能である。

【0078】

透明な画素の色は、隣接する他の色を適用することになるが、通常テクスチャマップにおいて、隣接する画素はある程度の相関を持った連続性があるために、画像品質に対し、影響を与えることがない。

【0079】

従って、本発明の適用により画像処理装置の低コスト化と、画像データの取り扱いを簡易にすることが可能である。

【図面の簡単な説明】

【図1】本発明の画素混合回路をテクスチャ貼り付け回路に用いた画像処理装置の構成ブロック図である。

【図2】本発明を適用したテクスチャ貼り付け回路とテクスチャマップメモリの関係を説明する図である。

【図3】複数画素混合回路50における動作のうち1の行の隣接画素の混合を説明するフロー図である。

【図4】複数画素混合回路50における動作のうち1の行に隣接する行の隣接画素の混合を説明するフロー図である。

【図5】複数画素混合回路50における動作のうち図3、図4のフローによる結果を混合を説明するフロー図である。

【図6】本発明の画素混合回路の一実施の形態の構成ブロック図である。

【図7】図3の実施の形態における相関演算回路の実施の形態の構成ブロック図である。

【図8】CRTディスプレー等の表示装置に表示するために、二次座標平面に展開され、フレームバッファに格納されたポリゴンの一例である。

【図9】ポリゴンの各ピクセルに対するテクスチャデータの貼り付けを説明する図である。

【図10】ポリゴンの各ピクセルを複数のテクスチャ画素データを組み合わせ求める計算を説明するための図である。

【符号の説明】

1 CPU

2 データバッファ

3 ジオメトリ処理部

4 塗り潰し回路

5 テクスチャ貼り付け回路

6 テクスチャマップ

7 デプステスト回路

8 デプスバッファ

9 ブレンディング回路

10 レンダリング処理部

11 フレームバッファ

12 ディスプレー装置

60 メモリセル

61 行アドレスデコード回路

62 列アドレスデコード回路

63、64 アドレスバッファ

50 画素混合回路

501、504、507 相関演算回路

502、505、508 選択回路

503、506、509 アンドゲート

【発明の属する技術分野】

本発明は、テクスチャマップ上の複数画素を混合する方法及び、これを用いた複数画素混合回路と画像処理装置に関する。

【0002】

【従来の技術】

近年、コンピュータグラフィック技術を用い、仮想3次元空間内に配置された物体を複数のポリゴンで画像表示する画像処理装置が普及している。更に、表示される物体をより現実に近いものとすべく研究開発が進められている。

【0003】

かかるコンピュータグラフィック技術において、表示される物体の表面の細部はテクスチャと呼ばれる。該当ポリゴンを構成するポリゴンの画素(ピクセル)毎にテクスチャデータをテクスチャマップから読み出し貼り付けることにより、物体の表面に色肌、材質感等が形成される。

【0004】

図8、図9は、かかるテクスチャデータの貼り付けを説明する図である。即ち、図8は、CRTディスプレー等の表示装置に表示するために、二次元座標平面に展開され、フレームバッファに格納されたポリゴンの一例である。

【0005】

図示されるかかるポリゴンPは、3頂点A、B、Cを有し、それぞれの頂点は貼り付けられるテクスチャデータを格納するテクスチャマップ上のX、Y2軸の座標を頂点データとして有する。

【0006】

例えば、頂点Aの画素に貼り付けられるテクスチャデータの格納位置として、図8に示されるように図9のテクスチャマップ上の座標データ(Tx0,Ty0)を有する。同様に、頂点Bは座標データ(Tx1,Ty1)を有し、頂点Cは座標データ(Tx2,Ty2)を有する。

【0007】

更に、例えば頂点Aと頂点Bの稜線上の点Dの画素に対しては、頂点Aの座標データ(Tx0,Ty0)と頂点Bの座標データ(Tx1,Ty1)を線型もしくはパースペクティブ補間をして、図9に示されるように、テクスチャマップ上の座標Dのデータ(Txi,Tyi)が求められる。

【0008】

ポリゴンPを構成する他の全ての画素に対しても、同様に線型もしくはパースペクティブ補間によりテクスチャマップ上の座標データが求められる。

【0009】

一方、テクスチャマップは、物体のテクスチャ種類毎に例えば、物体が岩であれば岩肌を表現するデータ、木材であれば木肌等を表現するデータがマップ状に展開され、メモリ装置に格納される。即ち、一つの岩における岩肌、一本の樹の木肌等は、1つのデータで定義できるようには均一ではなく、また連続性を持って変化する。

【0010】

従って、テクスチャマップは、岩肌、木肌等のテクスチャをX、Y2軸座標平面に展開したものであり、X、Y2軸座標位置を特定することにより、対応する特定位置の岩肌、木肌等のテクスチャが求められる。

【0011】

ここで、図10に示されるテクスチャマップの2軸平面とポリゴンの一画素との関係を考察する。図10において、太線で囲われた領域70は、ポリゴンを構成する1画素に対応してテクスチャマップの座標を指定した範囲である。領域71〜74は、テクスチャマップ上の複数の画素である。従って、この領域70に対し、テクスチャマップから読み出されるテクスチャデータに基づきテクスチャが該当の画素に貼り付けられる。

【0012】

しかし、上記のようにポリゴンを構成する1画素とテクスチャマップの画素とは必ずしも対応せず、ポリゴンを構成する1画素で指定される領域70は、テクスチャマップの隣接する複数の画素に跨る。図10の例では、領域70は、テクスチャマップの隣接する4つの画素71〜74に跨って重なる。

【0013】

このために、領域70に対応するポリゴンを構成する1画素に対するテクスチャは、隣接する4つの画素71〜74のデータを領域70の重なる面積に応じて混合して、対応するテクスチャデータを求めることが行われる。

【0014】

しかし、ポリゴンの中には、一部に穴の開いた部分を表現するものがある。この開いた部分に対応するテクスチャデータは透明色となる。従って、かかる場合は、ポリゴンに対しテクスチャを貼り付ける際に混合されるテクスチャマップ上の当該ポリゴンに対応する複数の画素の中に、透明であるテクスチャ画素が存在することになる。

【0015】

かかる場合は、混合に際し留意が必要である。なぜならば、透明色を隣接する画素に混合する場合は、色合いが異質になる恐れがあるからである。

【0016】

ここで上記したように、面積に応じて複数画素のテクスチャデータを混合する場合、図10でのテクスチャの画素71〜74の色をそれぞれ color0、 color1、 color2、 color3 とし、更に color1 が透明であるとする時、関係する面積に応じた寄与分から正規化した想定される計算式として数1または数2のように表わされる。

【0017】

【数1】

【0018】

または、

【0019】

【数2】

color=color0(1-x)(1-y)+color1x(1-y)+color2(1-x)y+color3xy

即ち、数1では透明である color1 の画素72のデータを除外して計算する。一方、数2は、透明である color1 の画素72のデータも含めて計算している。

【0020】

【発明が解決しようとする課題】

上記数1、数2のいずれの計算方法においても問題がある。前者の場合は透明である画素の色は、無視することが出来る。しかし、除算を行うために回路構成が複雑となる。

【0021】

一方、後者の場合は、除算を行うための回路構成は必要でなくなるが、透明であるはずの画素72の色が混合されてしまう。この場合、透明な画素72にもテクスチャマップ上の隣接の画素の色と整合性を与える色を与えておくことが必要となり、データ処理上煩雑となる。

【0022】

したがって、本発明の目的は、かかる問題を解決するために、テクスチャマップ上の透明である画素の色を混合しない回路構成であって、構成が簡易な複数画素混合方法及び回路を提供することにある。

【0023】

更に本発明の目的は、上記の本発明に従う複数画素混合方法及び回路を用いた画像処理装置を提供することにある。

【0024】

【課題を解決するための手段】

上記の本発明の課題を達成する複数画素混合方法の第1の構成は、ポリゴンを構成する画素に対応するテクスチャマップ上の複数画素を混合して、該ポリゴンを構成する画素に貼り付けるテクスチャデータを求める複数画素混合方法において、該テクスチャマップ上の複数画素の中に透明画素があるか否かを判断し、透明画素がない場合は、該テクスチャマップ上の複数画素を該ポリゴンを構成する画素が対応する割合に応じて混合し、該テクスチャマップ上の複数画素の一部が透明画素である場合は、該透明画素を他の隣接する透明でない画素で置き換え、更に、該テクスチャマップ上の複数画素の全てが透明画素である場合は、該テクスチャマップ上の複数画素を無視するようにする。

【0025】

更に、本発明に従う複数画素混合方法の第2の構成は、ポリゴンを構成する画素に対応するテクスチャマップ上の複数画素を混合して、該ポリゴンを構成する画素に貼り付けるテクスチャデータを求める複数画素混合方法において、該テクスチャマップ上の一の行アドレス方向に隣接する第1の複数画素に透明画素があるか否かを判断し、該一の行アドレス方向に隣接する第1の複数画素に透明画素がない場合は、該第1の複数画素を該ポリゴンを構成する画素が対応する割合に応じて混合し、該一の行アドレス方向に隣接する第1の複数画素の一部の画素が透明画素である場合は、該透明画素を隣接する透明でない画素で置き換え、該一の行アドレス方向に隣接する第1の複数画素の全てが透明画素である場合は、該複数画素を無視する第1の工程と、

該テクスチャマップ上の該一の行に隣接する行アドレス方向に隣接する第2の複数画素に透明画素があるか否かを判断し、該一の行に隣接する行アドレス方向に隣接する第2の複数画素に透明画素がない場合は、該第2の複数画素を該ポリゴンを構成する画素が対応する割合に応じて混合し、該一の行に隣接する行アドレス方向に隣接する第2の複数画素の一部の画素が透明画素である場合は、該透明画素を隣接する透明でない画素で置き換え、該一の行に隣接する行アドレス方向に隣接する第2の複数画素の全てが透明画素である場合は、該第2の複数画素を無視する第2の工程と、

該第1の工程により得られる第1のテクスチャ画素データと該第2の工程により得られる第2のテクスチャ画素データを比較し、該第1、第2のテクスチャ画素データのいずれも透明でない場合は、該第1、第2のテクスチャ画素データを該ポリゴンを構成する画素が対応する割合に応じて混合し、該第1、第2のテクスチャ画素データのいずれかが透明である場合は、透明であるテクスチャ画素データを他方の透明でないテクスチャ画素データで置き換え、いずれも透明である場合は、該第1及び第2のテクスチャ画素データを無視する第3の工程を有する。

【0026】

また、本発明に従う複数画素混合回路の第1の構成は、ポリゴンを構成する画素に対応するテクスチャマップ上の複数画素を混合して、該ポリゴンを構成する画素に貼り付けるテクスチャデータを求める複数画素混合回路において、テクスチャマップ上の隣接する複数画素を、該ポリゴンを構成する画素が対応する割合に応じて混合する補間演算回路と、該補間演算回路の出力及び、該隣接する複数画素と、該複数画素のそれぞれが透明であるか否かを示すフラグを選択信号として入力し、該選択信号により、該複数画素のいずれもが透明でない場合は、該補間演算回路の出力を有効とし、該複数画素のいずれかが透明である場合は、該複数画素の透明で無い画素を有効とし、該複数画素のいずれもが透明である場合は、出力を無効とする選択回路を有して構成される。

【0027】

更にまた、本発明に従う複数画素混合回路の第2の構成は、第1の複数画素混合回路の構成において、更に、前記隣接する複数画素のアンド論理を出力するアンドゲートを有する。

【0028】

更に、本発明に従う複数画素混合回路の第3の構成は、第2の構成の複数画素混合回路を3組有し、第1及び第2の組の複数画素混合回路の出力を、第3の組の複数画素混合回路の前記補間演算回路の2つの入力とする。

【0029】

また、本発明に従う画像処理装置の第1の構成は、仮想3次元空間内に配置された物体を複数のポリゴンで構成して画像表示する画像処理装置において、X,Y2軸で特定される複数の座標位置にテクスチャデータを格納するテクスチャマップを格納するメモリ装置と、該複数のポリゴンのそれぞれを構成するピクセル毎に、該テクスチャマップから読み出したテクスチャデータを貼り付けるテクスチャ貼り付け回路を有し、該テクスチャ貼り付け回路は、テクスチャマップ上の隣接する複数画素を、該ポリゴンを構成する画素が対応する割合に応じて混合する補間演算回路と、該補間演算回路の出力及び、該隣接する複数画素と、該複数画素のそれぞれが透明であるか否かを示すフラグを選択信号として入力し、該選択信号により、該複数画素のいずれもが透明でない場合は、該補間演算回路の出力を有効とし、該複数画素のいずれかが透明である場合は、該複数画素の透明で無い画素を有効とし、該複数画素のいずれもが透明である場合は、出力を無効とする選択回路を備えた複数画素混合回路を含む。

【0030】

更に、本発明に従う画像処理装置の第2の構成は、第1の構成において、前記複数画素混合回路は、前記隣接する複数画素のアンド論理を出力するアンドゲートを有する。

【0031】

また、本発明に従う画像処理装置の第3の構成は、第1の構成において、前記複数画素混合回路を3組有し、第1及び第2の組の複数画素混合回路の出力を、第3の組の複数画素混合回路の前記補間演算回路の2つの入力とする。

【0032】

【発明の実施の形態】

以下本発明の実施の形態を図面に従い説明する。尚、図面において、同一または類似のものには、同一の参照番号または参照記号を付して説明する。

【0033】

図1は、本発明の複数画素混合方法を用いた画像処理装置の構成ブロック図である。

【0034】

図1において、CPU1は、ポリゴンを使用した画像を処理するためのプログラムの実行を制御するものである。CPU1にはプログラムの進行に伴いディスプレー装置12上に表示するポリゴンの頂点データやレジスタセットファンクションを一次的に蓄えておくメモリであるデータバッファ2が接続されている。

【0035】

このデータバッファ2には、前記データに従って、3次元空間内にポリゴンを配置し、これをディスプレー装置12上に表示するために2次元座標系に変換するためのジオメトリ処理部3が接続されている。

【0036】

更に、表示する各ポリゴンに対し、着色、シェーディング、テクスチャの貼り付けを行うレンダリング処理部10が接続されている。レンダリング処理部10の出力側には、フレームバッファ11が接続され、表示される一画面分のデータが格納される。フレームバッファ11にCRT等のディスプレー装置12が接続され、フレームバッファ11の内容が順次表示される。

【0037】

ここで、上記ジオメトリ処理部3は、データバッファ2からプログラムの進行及び処理速度に対応して、ポリゴンの頂点データ(頂点座標、頂点カラー、テクスチャマップ座標、頂点透明度及び頂点の法線ベクトル等を有する)やレジスタセットファンクションを読み出す。

【0038】

ジオメトリ処理部3は、頂点座標データに基づき3次元空間にポリゴンを配置し、3次元空間のどの領域まで表示対象とするかのビューポートの決定、法線ベクトルに基づき各頂点の輝度の計算等を行う。また、ビューポートよりはみ出すポリゴンの頂点除去即ち、クリッピングを行う。更に、ビューポートに配置されたポリゴンを所定の視点を基準に2次平面に投影して3次元から2次元への座標変換を行う。

【0039】

2次元座標に座標変換されたポリゴンデータは、レンダリング処理部10に送られる。レンダリング処理部10は、塗り潰し回路4、テクスチャ貼り付け回路5、デプステスト回路7、ブレンディング回路9から構成されている。

【0040】

塗り潰し回路4は、ポリゴンの各頂点で囲まれた範囲にある画素(ピクセル)の情報を計算し、他のレンダリング処理部10内の各回路に渡す機能を有する。上記計算は、ポリゴンの各頂点間にあるピクセルの情報を対応の両頂点の情報を基に、例えば線型補間または、パースペクティブ補間等の補間を行うものである。先に図8において説明した頂点A,Bの頂点データからピクセルDのデータを求める如くである。

【0041】

テクスチャ貼り付け回路5は、ピクセルに対応したテクスチャをテクスチャマップ6から読み出し、ピクセルのカラーを計算して求める回路である。ピクセルのカラーを計算して求める回路の構成に本発明の複数画素混合方法及び回路の構成が適用されている。

【0042】

従って、かかる部分の方法及び回路構成については、本発明の実施例として後に詳細に説明する。

【0043】

デプステスト回路7は、複数のポリゴンの前後関係を比較して、最も手前に配置されたポリゴンのデータをデプスバッファ8に記憶させる回路である。即ち、デプスバッファ8には、先に描いた図形(ポリゴン)のピクセルのZ値が記憶されている。

【0044】

そして、画面上の先に描かれたポリゴンと重なる位置に、新しくポリゴンを表示する場合、新しいポリゴンを構成する各ピクセルのZ値と、デプスバッファ8から読み出される先に描かれたポリゴンのピクセルのZ値とを比較する。比較の結果、新しいポリゴンのピクセルが手前の場合は、デプスバッファ8に当該ピクセルのZ値が書き込まれる。

【0045】

ブレンディング回路9は、フレームバッファ11から読み込んだ、先に描かれているポリゴンのピクセルのカラー情報と、新しく処理するポリゴンのピクセルのカラー情報とを混合し、フレームバッファ11に書き込む。このフレームバッファ11の情報が1画面分ずつディスプレー装置12に送られ表示される。

【0046】

次に、上記のような構成の画像処理装置における本発明を適用した複数画素混合方法及び回路の実施例構成を説明する。

【0047】

先に説明したように、ポリゴンを構成する1画素のテクスチャデータを求める場合、当該1画素のテクスチャマップ上の座標データ位置において、画素は面積を持つので、テクスチャマップの隣接する複数の画素と重なる。従って、テクスチャマップの隣接する複数の画素データを組み合わせて、当該ポリゴンを構成する1画素に対するテクスチャデータを生成することが行われる。

【0048】

図2は、図1のテクスチャ貼り付け回路5に含まれる主機能回路としての画素混合回路50と、テクスチャマップ6の詳細を示すブロック図である。

【0049】

テクスチャマップ6は、テクスチャデータがポリゴン対応に展開格納されるメモリアレー60、行アドレスデコーダ61及び列アドレスデコーダ62を有する。更に、テクスチャ貼り付け回路5には、テクスチャマップ6の行アドレスデコーダ61及び列アドレスデコーダ62にそれぞれ行アドレス、列アドレスを送るアドレスバッファ63、64を有する。

【0050】

テクスチャ貼り付け回路5は、塗り潰し回路4から入力されるポリゴンの画素データからテクスチャマップ6の座標位置データを抜き出し、前記行アドレスデコーダ61及び列アドレスデコーダ62に送る。

【0051】

メモリアレー60は、テクスチャ貼り付け回路5から入力した4組の行アドレスと列アドレスにより対応する座標位置にある4画素71〜74のcolor0,color1,color2,color3 のデータを読み出し、複数画素混合回路50に入力する。

【0052】

更に、複数画素混合回路50には、テクスチャ貼り付け回路5において求めたポリゴンの画素を特定する座標とテクスチャマップ60の画素位置とのずれ(x及びy)の値が入力される。

【0053】

かかる複数画素混合回路50における動作フローが図3〜図5に示される。

【0054】

図10に示す例を用い、テクスチャメモリの画素71から74のテクスチャ(カラー:color0, color1, color2, color3)を混合し、ポリゴンの画素70に貼り付けるテクスチャデータ(カラー:color)を求める場合を考える。

【0055】

図3において、一の行アドレス方向の隣接画素のうち透明画素の有無を判断する(ステップS1)。この判断の結果、隣接画素のいずれも透明画素がない場合は、ポリゴンの画素の占める面積に応じた割合で混合する(ステップS2)。

【0056】

隣接画素のいずれかが、透明である場合は、他の画素で当該透明画素を置き換える(ステップS3)。更に、隣接画素のいずれも透明画素である場合は、画素テクスチャを無視する(ステップS4)。

【0057】

かかる処理を図10に当てはめると、一の行アドレス方向の隣接画素は画素71、72が対応し、画素72が透明であるので、ステップS3の処理が対応し、画素72の透明部分を不透明な画素71の画素で置き換える。即ち、画素71(color0)そのものが出力A(color01) となる。

【0058】

更に、図4において、一の行アドレスに隣接する行アドレス方向の隣接画素のうち透明画素の有無を判断する(ステップS5)。この判断結果による処理は、透明画素が無い場合は(ステップS6)の処理、一部の画素が透明である場合は(ステップS7)の処理、そして全てが透明画素である場合は(ステップS8)の処理となり、これらはそれぞれ図3の(ステップS2)、(ステップS3)、(ステップS4)に対応する。

【0059】

従って、図4の処理を図10に対応させると、隣接する行アドレス方向の隣接画素は画素73、74となる。そして、いずれの画素も透明では無いので画素73、74に対するポリゴンの画素70の占める割合に応じて混合され、出力B(color23) となる。

【0060】

更に、図5は、図3、図4の出力A,Bに基づく処理である。出力A,Bのうち透明画素の有無を判断する(ステップS9)。この判断結果による処理は、透明画素が無い場合は(ステップS10)の処理、一部の画素が透明である場合は(ステップS11)の処理、そして全てが透明画素である場合は(ステップS12)の処理となり、これらはそれぞれ図3、図4の(ステップS2、S6)、(ステップS3、S7)、(ステップS4、S8)に対応する。

【0061】

従って、図5の処理を図10に対応させると、出力A(color01) ,B(color23) のいずれも透明でないので、一の行アドレス方向の隣接画素71、72に対するポリゴンの画素70の占める大きさと、隣接する行アドレス方向の隣接画素73、74に対するポリゴンの画素70の占める大きさとの割合に応じて混合され、出力C(color) となる。

【0062】

図6は、かかる本発明の複数補画素混合方法を適用する複数画素混合回路50の実施例回路である。上記図3から図5の処理に対応して、3組の同様の回路で構成されている。補間演算回路501、選択回路502及びアンドゲート503により、図10に示す画素71と72を混合したデータ即ち、color0とcolor1を混合した出力color01 を得る。

【0063】

このために補間演算回路501、選択回路502及びアンドゲート503による第1の回路は、数3の計算を行う。

【0064】

【数3】

color01 = color0(1-x) + color1・x

同様に、補間演算回路504、選択回路505及びアンドゲート506による第2の回路は、数4の計算を行い、color2とcolor3を混合した出力color23 を得る。

【0065】

【数4】

color23 = color2(1-x) + color3・x

更に、補間演算回路507、選択回路508及びアンドゲート509による第3の回路は、数5の計算を行い、上記に求めたcolor02 とcolor23 を混合した最終出力としてcolor を得る。

【0066】

【数5】

color = color01(1-y) + color23・y

上記第1〜3の回路の計算原理は同様であるので、補間演算回路501、選択回路502及びアンドゲート503による第1の回路を代表例にして、回路の動作原理を説明する。

【0067】

上記第1の回路において、先ず補間演算回路501によりcolor0とcolor1の二つの画素71、72を混合する。補間演算回路501、504、507の構成例が図7に示される。

【0068】

図7において、入力信号の記号を一般化して示しているが、第1の回路に対応させると、dxi は、xであり、Datai,j 、 Datai,jは、それぞれ画素71、72のcolor0、 color1である。

【0069】

したがって、差回路151は、(1−x)を出力する。次いで、掛け算回路152、153からは、それぞれ(1−x)とcolor0の積color0・(1−x)、xとcolor1との積color1・xを出力する。

【0070】

和回路154は、掛け算回路152、153の出力の和を求め、color0・(1−x)+color1・xを出力し、選択回路502のA入力端に入力する。更に、選択回路502のB,C入力端にはそれぞれcolor0、color1が入力される。

【0071】

一方、それぞれのテクスチャマップの画素データには、画素が透明であるか否かの透明フラグ情報(画素が透明であれば、H論理を有する)が付加されている。従って、 選択回路502にはこのフラグ情報が端子S0 、S1 にセレクタ信号として入力される。

【0072】

選択回路502では、これら端子S0 、S1 に入力されるセレクタ信号の論理に基づき、補間演算回路501の混合出力color01 、または混合前の元の入力であるcolor0、color1が選択され、出力される。

【0073】

即ち、color0及びcolor1がともに透明でない(S0 =S1 =L論理)時、補間演算回路501の混合出力color01 が出力される。color0のみが透明である(S0 =H、S1 =L論理)時、color01 =color1として出力される。

【0074】

更に、color1のみが透明である(S0 =L、S1 =H論理)時、color01 =color0として出力される。color0、color1ともに透明である(S0 =H、S1 =H論理)時、混合の結果は特定されない。この時、選択回路502の出力color01 に対する透明フラグは、アンドゲート503の出力であり、H論理となる。この時、color01 の画素の色は無視される。

【0075】

上記の様にして、第1の回路により、数3の計算式に対応する出力color01 が得られる。更に、補間演算回路504、選択回路505及びアンドゲート506による第2の回路、補間演算回路507、選択回路508及びアンドゲート509による第3の回路の動作も第1の回路と同様である。

【0076】

即ち、第2の回路は、color2とcolor3を入力して、数4の計算に対応する出力color23 を出力する。第3の回路は、第1の回路の出力color01 と第2の回路の出力color23 を入力して数5の計算に対応する出力color を出力する。

【0077】

【発明の効果】

以上、図にしたがい実施例を説明したように、本発明に従う画素混合回路は、簡易な論理構成で実現でき且つ、透明な画素も考慮することが可能である。

【0078】

透明な画素の色は、隣接する他の色を適用することになるが、通常テクスチャマップにおいて、隣接する画素はある程度の相関を持った連続性があるために、画像品質に対し、影響を与えることがない。

【0079】

従って、本発明の適用により画像処理装置の低コスト化と、画像データの取り扱いを簡易にすることが可能である。

【図面の簡単な説明】

【図1】本発明の画素混合回路をテクスチャ貼り付け回路に用いた画像処理装置の構成ブロック図である。

【図2】本発明を適用したテクスチャ貼り付け回路とテクスチャマップメモリの関係を説明する図である。

【図3】複数画素混合回路50における動作のうち1の行の隣接画素の混合を説明するフロー図である。

【図4】複数画素混合回路50における動作のうち1の行に隣接する行の隣接画素の混合を説明するフロー図である。

【図5】複数画素混合回路50における動作のうち図3、図4のフローによる結果を混合を説明するフロー図である。

【図6】本発明の画素混合回路の一実施の形態の構成ブロック図である。

【図7】図3の実施の形態における相関演算回路の実施の形態の構成ブロック図である。

【図8】CRTディスプレー等の表示装置に表示するために、二次座標平面に展開され、フレームバッファに格納されたポリゴンの一例である。

【図9】ポリゴンの各ピクセルに対するテクスチャデータの貼り付けを説明する図である。

【図10】ポリゴンの各ピクセルを複数のテクスチャ画素データを組み合わせ求める計算を説明するための図である。

【符号の説明】

1 CPU

2 データバッファ

3 ジオメトリ処理部

4 塗り潰し回路

5 テクスチャ貼り付け回路

6 テクスチャマップ

7 デプステスト回路

8 デプスバッファ

9 ブレンディング回路

10 レンダリング処理部

11 フレームバッファ

12 ディスプレー装置

60 メモリセル

61 行アドレスデコード回路

62 列アドレスデコード回路

63、64 アドレスバッファ

50 画素混合回路

501、504、507 相関演算回路

502、505、508 選択回路

503、506、509 アンドゲート

Claims (8)

- ポリゴンを構成する画素に対応するテクスチャマップ上の複数画素を混合して、該ポリゴンを構成する画素に貼り付けるテクスチャデータを求める複数画素混合方法において、

該テクスチャマップ上の複数画素の中に透明画素があるか否かを判断し、

透明画素がない場合は、該テクスチャマップ上の複数画素を該ポリゴンを構成する画素が対応する割合に応じて混合し、

該テクスチャマップ上の複数画素の一部が透明画素である場合は、該透明画素を他の隣接する透明でない画素で置き換え、

更に、該テクスチャマップ上の複数画素の全てが透明画素である場合は、該テクスチャマップ上の複数画素を無視するようにしたことを特徴とするテクスチャマップ上の複数画素を混合する方法。 - ポリゴンを構成する画素に対応するテクスチャマップ上の複数画素を混合して、該ポリゴンを構成する画素に貼り付けるテクスチャデータを求める複数画素混合方法において、

該テクスチャマップ上の一の行アドレス方向に隣接する第1の複数画素に透明画素があるか否かを判断し、該一の行アドレス方向に隣接する第1の複数画素に透明画素がない場合は、該第1の複数画素を該ポリゴンを構成する画素が対応する割合に応じて混合し、該一の行アドレス方向に隣接する第1の複数画素の一部の画素が透明画素である場合は、該透明画素を隣接する透明でない画素で置き換え、該一の行アドレス方向に隣接する第1の複数画素の全てが透明画素である場合は、該複数画素を無視する第1の工程と、

該テクスチャマップ上の該一の行に隣接する行アドレス方向に隣接する第2の複数画素に透明画素があるか否かを判断し、該一の行に隣接する行アドレス方向に隣接する第2の複数画素に透明画素がない場合は、該第2の複数画素を該ポリゴンを構成する画素が対応する割合に応じて混合し、該一の行に隣接する行アドレス方向に隣接する第2の複数画素の一部の画素が透明画素である場合は、該透明画素を隣接する透明でない画素で置き換え、該一の行に隣接する行アドレス方向に隣接する第2の複数画素の全てが透明画素である場合は、該第2の複数画素を無視する第2の工程と、

該第1の工程により得られる第1のテクスチャ画素データと該第2の工程により得られる第2のテクスチャ画素データを比較し、該第1、第2のテクスチャ画素データのいずれも透明でない場合は、該第1、第2のテクスチャ画素データを該ポリゴンを構成する画素が対応する割合に応じて混合し、該第1、第2のテクスチャ画素データのいずれかが透明である場合は、透明であるテクスチャ画素データを他方の透明でないテクスチャ画素データで置き換え、いずれも透明である場合は、該第1及び第2のテクスチャ画素データを無視する第3の工程を有することを特徴とするテクスチャマップ上の複数画素を混合する方法。 - ポリゴンを構成する画素に対応するテクスチャマップ上の複数画素を混合して、該ポリゴンを構成する画素に貼り付けるテクスチャデータを求める複数画素混合回路において、

テクスチャマップ上の隣接する複数画素を該ポリゴンを構成する画素が対応する割合に応じて混合する補間演算回路と、

該補間演算回路の出力及び、該隣接する複数画素と、該複数画素のそれぞれが透明であるか否かを示すフラグを選択信号として入力し、該選択信号により、該複数画素のいずれもが透明でない場合は、該補間演算回路の出力を有効とし、該複数画素のいずれかが透明である場合は、該複数画素の透明で無い画素を有効とし、該複数画素のいずれもが透明である場合は、出力を無効とする選択回路を

有して構成されることを特徴とする複数画素混合回路。 - 請求項3において、

更に、前記隣接する複数画素のアンド論理を出力するアンドゲートを有することを特徴とする複数画素混合回路。 - 請求項3の構成の複数画素混合回路を3組有し、第1及び第2の組の複数画素混合回路の出力を、第3の組の複数画素混合回路の前記補間演算回路の2つの入力とすることを特徴とする複数画素混合回路。

- 仮想3次元空間内に配置された物体を複数のポリゴンで構成して画像表示する画像処理装置において、

X,Y2軸で特定される複数の座標位置にテクスチャデータを格納するテクスチャマップを格納するメモリ装置と、

該複数のポリゴンのそれぞれを構成するピクセル毎に、該テクスチャマップから読み出したテクスチャデータを貼り付けるテクスチャ貼り付け回路を有し、

該テクスチャ貼り付け回路は、テクスチャマップ上の隣接する複数画素を該ポリゴンを構成する画素が対応する割合に応じて混合する補間演算回路と、

該補間演算回路の出力及び、該隣接する複数画素と、該複数画素のそれぞれが透明であるか否かを示すフラグを選択信号として入力し、該選択信号により、該複数画素のいずれもが透明でない場合は、該補間演算回路の出力を有効とし、該複数画素のいずれかが透明である場合は、該複数画素の透明で無い画素を有効とし、該複数画素のいずれもが透明である場合は、出力を無効とする選択回路を

備えた複数画素混合回路を含むことを特徴とする画像処理装置。 - 請求項6において、

更に、前記複数画素混合回路は、前記隣接する複数画素のアンド論理を出力するアンドゲートを有することを特徴とする画像処理装置。 - 請求項6において、

前記複数画素混合回路を3組有し、第1及び第2の組の複数画素混合回路の出力を、第3の組の複数画素混合回路の前記補間演算回路の2つの入力とすることを特徴とする画像処理装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP33682396A JP3885262B2 (ja) | 1996-12-17 | 1996-12-17 | テクスチャマップ上の複数画素を混合する方法及び、これを用いた複数画素混合回路と画像処理装置 |

| US08/986,192 US6005584A (en) | 1996-12-17 | 1997-12-05 | Method of blending a plurality of pixels on a texture map and a plural pixel blending circuit and image processing device using the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP33682396A JP3885262B2 (ja) | 1996-12-17 | 1996-12-17 | テクスチャマップ上の複数画素を混合する方法及び、これを用いた複数画素混合回路と画像処理装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH10177656A JPH10177656A (ja) | 1998-06-30 |

| JP3885262B2 true JP3885262B2 (ja) | 2007-02-21 |

Family

ID=18303012

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP33682396A Expired - Fee Related JP3885262B2 (ja) | 1996-12-17 | 1996-12-17 | テクスチャマップ上の複数画素を混合する方法及び、これを用いた複数画素混合回路と画像処理装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6005584A (ja) |

| JP (1) | JP3885262B2 (ja) |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6078335A (en) * | 1998-06-01 | 2000-06-20 | Ati Technologies, Inc. | Method and apparatus for determining level of detail for texture filtering |

| US6297852B1 (en) * | 1998-12-30 | 2001-10-02 | Ati International Srl | Video display method and apparatus with synchronized video playback and weighted frame creation |

| US6181352B1 (en) | 1999-03-22 | 2001-01-30 | Nvidia Corporation | Graphics pipeline selectively providing multiple pixels or multiple textures |

| US6297833B1 (en) * | 1999-03-23 | 2001-10-02 | Nvidia Corporation | Bump mapping in a computer graphics pipeline |

| US6618048B1 (en) | 1999-10-28 | 2003-09-09 | Nintendo Co., Ltd. | 3D graphics rendering system for performing Z value clamping in near-Z range to maximize scene resolution of visually important Z components |

| US6717577B1 (en) | 1999-10-28 | 2004-04-06 | Nintendo Co., Ltd. | Vertex cache for 3D computer graphics |

| JP2001250115A (ja) * | 2000-03-03 | 2001-09-14 | Sony Computer Entertainment Inc | ディジタルフィルタ |

| US7119813B1 (en) * | 2000-06-02 | 2006-10-10 | Nintendo Co., Ltd. | Variable bit field encoding |

| US6707458B1 (en) | 2000-08-23 | 2004-03-16 | Nintendo Co., Ltd. | Method and apparatus for texture tiling in a graphics system |

| US6636214B1 (en) | 2000-08-23 | 2003-10-21 | Nintendo Co., Ltd. | Method and apparatus for dynamically reconfiguring the order of hidden surface processing based on rendering mode |

| US6700586B1 (en) | 2000-08-23 | 2004-03-02 | Nintendo Co., Ltd. | Low cost graphics with stitching processing hardware support for skeletal animation |

| US7196710B1 (en) | 2000-08-23 | 2007-03-27 | Nintendo Co., Ltd. | Method and apparatus for buffering graphics data in a graphics system |

| US7576748B2 (en) | 2000-11-28 | 2009-08-18 | Nintendo Co. Ltd. | Graphics system with embedded frame butter having reconfigurable pixel formats |

| US7538772B1 (en) | 2000-08-23 | 2009-05-26 | Nintendo Co., Ltd. | Graphics processing system with enhanced memory controller |

| US6811489B1 (en) | 2000-08-23 | 2004-11-02 | Nintendo Co., Ltd. | Controller interface for a graphics system |

| US6784895B1 (en) | 2000-10-17 | 2004-08-31 | Micron Technology, Inc. | Programmable multiple texture combine circuit for a graphics processing system and method for use thereof |

| US7061507B1 (en) * | 2000-11-12 | 2006-06-13 | Bitboys, Inc. | Antialiasing method and apparatus for video applications |

| US6853373B2 (en) * | 2001-04-25 | 2005-02-08 | Raindrop Geomagic, Inc. | Methods, apparatus and computer program products for modeling three-dimensional colored objects |

| US20070109314A1 (en) * | 2003-05-23 | 2007-05-17 | Via Technologies, Inc. | Adaptive pixel-based blending method and system |

| US20050226087A1 (en) * | 2004-04-12 | 2005-10-13 | Kuo-Chang Wang | Protocol structure to accelerate memory transmission |

| US7573599B2 (en) * | 2004-05-20 | 2009-08-11 | Primax Electronics Ltd. | Method of printing geometric figures |

| US7852339B2 (en) * | 2006-10-23 | 2010-12-14 | Intel Corporation | Video composition optimization by the identification of transparent and opaque regions |

| JP4921113B2 (ja) * | 2006-10-25 | 2012-04-25 | キヤノン株式会社 | 接触提示装置及び方法 |

| US7928992B2 (en) * | 2007-05-30 | 2011-04-19 | Kabushiki Kaisha Toshiba | System and method for transparent object rendering |

| WO2012147303A1 (ja) * | 2011-04-25 | 2012-11-01 | Hayashi Mitsuo | 全方位画像編集プログラム及び全方位画像編集装置 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5889526A (en) * | 1994-11-25 | 1999-03-30 | Matsushita Electric Industrial Co., Ltd. | Interpolation apparatus and method, and image generation apparatus including such an apparatus |

| US5892516A (en) * | 1996-03-29 | 1999-04-06 | Alliance Semiconductor Corporation | Perspective texture mapping circuit having pixel color interpolation mode and method thereof |

| US5903270A (en) * | 1997-04-15 | 1999-05-11 | Modacad, Inc. | Method and apparatus for mapping a two-dimensional texture onto a three-dimensional surface |

| US5781197A (en) * | 1996-07-26 | 1998-07-14 | Hewlett-Packard Company | Method for maintaining contiguous texture memory for cache coherency |

| US5900882A (en) * | 1996-11-15 | 1999-05-04 | Samsung Electronics Co., Ltd. | Determining texture coordinates in computer graphics |

-

1996

- 1996-12-17 JP JP33682396A patent/JP3885262B2/ja not_active Expired - Fee Related

-

1997

- 1997-12-05 US US08/986,192 patent/US6005584A/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH10177656A (ja) | 1998-06-30 |

| US6005584A (en) | 1999-12-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3885262B2 (ja) | テクスチャマップ上の複数画素を混合する方法及び、これを用いた複数画素混合回路と画像処理装置 | |

| US5877769A (en) | Image processing apparatus and method | |

| JP3203160B2 (ja) | ボリューム・レンダリング装置及び方法 | |

| US6172687B1 (en) | Memory device and video image processing apparatus using the same | |

| JP2002304636A (ja) | 画像生成方法及び装置、画像処理プログラムを記録した記録媒体、画像処理プログラム | |

| JPH05307610A (ja) | テクスチャマッピング方法およびその装置 | |

| WO2000002165A1 (fr) | Procede permettant de produire des donnees de polygone et afficheur d'images utilisant lesdites donnees | |

| JPH0771936A (ja) | 画像処理装置及びその方法 | |

| JP2612221B2 (ja) | 図形画像を生成する装置及び方法 | |

| JPS6380375A (ja) | テクスチヤマツピング装置 | |

| KR100277803B1 (ko) | 3차원 그래픽 표시장치 | |

| WO2023173728A1 (zh) | 图形渲染方法、装置及存储介质 | |

| JPH11259671A (ja) | 画像表示方法及びそれを実行する画像表示装置 | |

| JP3649478B2 (ja) | 画像情報処理装置及び画像情報処理方法 | |

| US6373494B1 (en) | Signal processing apparatus and image processing apparatus | |

| JPH09245191A (ja) | 透明度変換方法及びその装置、画像処理装置 | |

| US20050275733A1 (en) | Method and apparatus of rendering a video image by polynomial evaluation | |

| JP3052839B2 (ja) | 画像処理装置及びその処理方法 | |

| US20030169272A1 (en) | Image generation apparatus and method thereof | |

| JPH06266852A (ja) | 画像合成装置 | |

| US6476818B1 (en) | Storage circuit control device and graphic computation device | |

| JP4622165B2 (ja) | 画像メモリ制御装置、グラフィック演算装置およびレンダリング処理方法 | |

| JPH11185052A (ja) | 3次元コンピュータグラフィックスのテクスチャマッピング座標計算装置および方法 | |

| JP2001134777A (ja) | 3次元グラフィックスシステム、演算処理装置及び記録媒体 | |

| JP4042204B2 (ja) | グラフィック演算装置およびその方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20031209 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20031209 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20061031 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20061113 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |