JP3557774B2 - Semiconductor storage device - Google Patents

Semiconductor storage device Download PDFInfo

- Publication number

- JP3557774B2 JP3557774B2 JP04509296A JP4509296A JP3557774B2 JP 3557774 B2 JP3557774 B2 JP 3557774B2 JP 04509296 A JP04509296 A JP 04509296A JP 4509296 A JP4509296 A JP 4509296A JP 3557774 B2 JP3557774 B2 JP 3557774B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- input

- output

- column

- control signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Tests Of Electronic Circuits (AREA)

- For Increasing The Reliability Of Semiconductor Memories (AREA)

- Dram (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は、半導体記憶装置に関するものである。

【0002】

【従来の技術】

従来のロジックICチップに内蔵されたメモリコアに対して試験を行うとき、外部に取り出されたメモリコアの各動作を制御する制御信号端子およびデータの入出力端子を介してデータの入出力が行われる。

【0003】

図7はこのようなメモリコアの構成を示すブロック図である。

図7において、10はロウアドレスバッファ、20はロウプリデコーダ、30はロウデコーダ、40aはカラムアドレスバッファ、50aはカラムプリデコーダ、60aはカラムセレクタ、70は入出力バッファ、100はメモリアレイ、DINおよびDOUT はデータ入力端子およびデータ出力端子をそれぞれ示している。

【0004】

図示のように、ロウアドレスROWADRがロウアドレスバッファ10に入力され、ロウアドレスバッファ10を介してロウプリデコーダ20に入力され、そして、ロウデコーダ30に入力される。ロウプリデコーダ20およびロウデコーダ30によって、入力されたロウアドレスROWADRに応じて、所定のワード線が選択されアクティブ状態に設定される。

【0005】

一方、カラムアドレスCLMADRがカラムアドレスバッファ40aに入力され、カラムアドレスバッファ40aを介してカラムプリデコーダ50aに入力され、さらに、カラムセレクタ60aに入力される。カラムプリデコーダ50aおよびカラムセレクタ60aによって、入力されたカラムアドレスCLMADRに応じて、所定のビット線が選択され、アクティブ状態に設定される。

【0006】

上述したように、アクティブ状態に設定された選択ワード線および選択ビット線によって、これらの信号線の交差点に配置されたメモリセルが選択され、入出力バッファ70aを介して、データの入出力が行われる。

たとえば、データ入力、すなわち、メモリ書き込み時に、データ入力端子DINに入力されたデータが入出力バッファ70aおよび選択されたビット線を介して、選択されたメモリセルに書き込まれる。

一方、データ出力、すなわち、メモリ読み出し時に、選択されたメモリセルから記憶データが読み出され、選択されたビット線および入出力バッファ70aを介してデータ出力端子DOUT に出力される。

【0007】

【発明が解決しようとする課題】

ところで、上述した従来のメモリコアにおいては、アプリケーションによってメモリコアの信号端子およびデータ入出力端子数が決まっており、メモリコアの容量が増加していくと、試験時間の増大が問題となる。

また、アプリケーション毎にデータ入出力端子数を変更すると、テストパターンも別途に作成しなければならなく、メモリコア自体もアプリケーション毎に新たに開発しなければならないという問題がある。

【0008】

本発明は、かかる事情に鑑みてなされたものであり、その目的は、データ入出力端子数が外部信号によって容易に変更でき、アプリケーションによらず多ビットが同時に試験でき、試験時間および試験パターンの開発工数を短縮でき、アプリケーションの依存性を低減できる半導体記憶装置を提供することにある。

【0009】

【課題を解決するための手段】

上記目的を達成するため、本発明は、複数のメモリセルが配列されたメモリアレイを有し、ロウアドレスおよびカラムアドレスに応じて、アクティブ状態に設定された選択ワード線および選択ビット線によってアドレス指定されたメモリセルを選択し、入出力回路を介して上記メモリアレイに対して、データの書き込みまたは読み出しを行う半導体記憶装置であって、入力された複数のカラムアドレスデータをそれぞれ同相信号および反転信号として出力する複数のアドレスバッファ回路を有し、当該複数のアドレスバッファ回路のうち、最下位のカラムアドレスデータが入力されるアドレスバッファ回路は、ビット幅制御信号が第1のレベルで入力されると入力された最下位のカラムアドレスデータの同相信号および反転信号の2つの信号を出力し、上記ビット幅制御信号が第2のレベルで入力されると上記最下位のカラムアドレスデータの入力レベルにかかわらず所定の同レベルの2つの信号を出力するカラムアドレスバッファと、上記カラムアドレスバッファ回路の上記複数のアドレスバッファ回路から出力された複数の信号に基づいて複数のカラム線のうち所定のカラム線をアクティブ状態に設定するカラムプリデコーダと、それぞれが異なる上記カラム線に接続され、上記ビット線とデータバスとを当該カラム線がアクティブ状態のときに導通状態とする複数のスイッチ回路を有するカラムセレクタと、を有し、上記入出力回路は、上記ビット幅制御信号および上記カラムアドレスバッファの最下位のアドレスバッファ回路の2つの出力信号を受けて、当該ビット幅制御信号が第1のレベルのときは、1つのデータバスの読み出しデータを出力し、上記ビット幅制御信号が第2のレベルのときは2つのデータバスの読み出しデータを出力する出力バッファと、上記ビット幅制御信号および上記カラムアドレスバッファの最下位のアドレスバッファ回路の2つの出力信号を受けて、当該ビット幅制御信号が第1のレベルのときは、2つのデータ入力端子の入力データを書き込みデータとして2つのデータバスに出力し、上記ビット幅制御信号が第2のレベルのときは1つのデータ入力端子の入力データを書き込みデータとして1つのデータバスに出力する入力バッファと、を有する。

【0010】

さらに、本発明の半導体装置がASICメモリに組み込まれている。

【0011】

本発明によれば、半導体記憶装置に外部からのビット幅制御信号の入力端子が設けられ、当該入力端子に入力されたビット幅制御信号によってデータ入出力回路の入出力のビット数が設定される。

たとえば、入出力回路にある複数の入出力端子の内、前記ビット幅制御信号に応じて、所定の数の入出力端子が選択され、これら選択された入出力端子を介してデータの入出力が行われる。

この結果、データの入出力の端子数が外部信号によって容易に変更でき、アプリケーションの依存性が低減できる。

【0012】

また、ASICメモリに上述したようなメモリコアが組み込まれることによって、アプリケーションによらず多ビットが同時に試験でき、試験時間および試験パターンの開発工数の短縮を図れる。

【0013】

【発明の実施の形態】

図1は、本発明に係る半導体記憶装置の一実施形態を示すブロック図である。

図1において、10はロウアドレスバッファ、20はロウプリデコーダ、30はロウデコーダ、40はカラムアドレスバッファ、50はカラムプリデコーダ、60はカラムセレクタ、70は入出力バッファ、100はメモリアレイ、DINおよびDOUT はデータ入力端子およびデータ出力端子をそれぞれ示している。

さらに、ROWADRはロウアドレス、CLMADRはカラムアドレス、BWCはビット幅制御信号をそれぞれ示している。

【0014】

図示のように、ロウアドレスROWADRはロウアドレスバッファ10に、カラムアドレスCLMADRはカラムアドレスバッファ40に、ビット幅制御信号BWCはカラムアドレスバッファ40および入出力バッファ70にそれぞれ入力される。

【0015】

ロウアドレスバッファ10に入力されたロウアドレスROWADRは、ロウアドレスバッファ10を介して、ロウプリデコーダ20に入力され、さらにロウデコーダ30に入力される。ロウプリデコーダ20およびロウデコーダ30によって、入力されたロウアドレスROWADRに応じて、所定のワード線が選択され、アクティブ状態に設定される。

【0016】

カラムアドレスバッファ40に入力されたカラムアドレスCLMADRは、カラムアドレスバッファ40を介して、カラムプリデコーダ50に入力され、さらにカラムセレクタ60に入力される。カラムプリデコーダ50およびカラムセレクタ60によって、入力されたカラムアドレスCLMADRに応じて、所定のビット線が選択され、アクティブ状態に設定される。

【0017】

そして、アクティブ状態に設定された選択ワード線および選択ビット線の交差点に配置されたメモリセルが選択され、データの入出力が行われる。

たとえば、書き込み時に、入力端子DINに入力されたデータが入出力バッファ70によって読み込まれ、選択ビット線を介して、選択されたメモリセルに書き込まれる。読み出し時に、選択されたメモリセルに記憶されたデータが選択ビット線に読み出され、入出力バッファ70を介して、出力端子DOUT に出力される。

【0018】

なお、ここで、カラムアドレスバッファ40および入出力バッファ70にそれぞれビット幅制御信号BWCが入力され、このビット幅制御信号BWCに応じて、入出力データのビット数が設定される。

以下、メモリコアを構成するカラムアドレスバッファ40、カラムプリデコーダ50、カラムセレクタ60、入出力バッファ70およびメモリアレイ100の各部分の構成およびそれらの動作について説明する。

【0019】

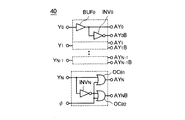

図2はカラムアドレスバッファ40の構成を示す回路図である。

図2において、Y0 ,Y1 ,…,YN−1 ,YN はカラムアドレスCLMADRの入力端子、φはビット幅制御信号BWC入力端子、AY0 は入力端子Y0 に入力されたアドレスデータの同相信号、AY0 Bは入力端子Y0 に入力されたアドレスデータの反転信号、AY1 は入力端子Y1 に入力されたアドレスデータの同相信号、AY1 Bは入力端子Y1 に入力されたアドレスデータの反転信号、AYN−1 は入力端子YN−1 に入力されたアドレスデータの同相信号、AYN−1 Bは入力端子YN−1 に入力されたアドレスデータの反転信号、AYN は入力端子YN に入力されたアドレスデータの同相信号、AYN Bは入力端子YN に入力されたアドレスデータの反転信号の出力端子をそれぞれ示している。

【0020】

図示のように、カラムアドレス入力端子Y0 ,Y1 ,…,YN−1 に入力されたカラムアドレスデータがそれぞれバッファ回路を介して、同相信号の出力端子AY0 ,AY1 ,…,AYN−1 に出力され、さらにインバータを介して、反転信号出力端子AY0 B,AY1 B,…,AYN−1 Bに出力される。

たとえば、図示のように入力端子Y0 に入力されたカラムアドレスデータがバッファ回路BUF0 を介して、同相信号出力端子AY0 に出力され、さらにインバータINV0 を介して反転信号出力端子AY0 Bに出力される。

【0021】

そして、カラムアドレスバッファ40の最下位のアドレスのバッファ回路が他のバッファ回路とは構造が異なる。このバッファ回路は入力端子φに入力されたビット幅制御信号BWCによって動作が制御される。

最下位アドレスの入力端子YN がオア回路OCB1の一方の入力端子およびインバータINVN の入力端子に接続され、インバータINVN の出力端子がオア回路OCB2の一方の入力端子に接続されている。さらに、ビット幅制御信号BWCの入力端子φがオア回路OCB1およびオア回路OCB2の他方の入力端子に接続されている。

【0022】

入力端子φにローレベル(第1のレベル)のビット幅制御信号BWCが入力されるとき、入力端子YN に入力された最下位アドレスの同相信号の同相信号出力端子AYN に出力され、その反転信号が反転信号出力端子AYN Bに出力される。

一方、入力端子φにハイレベル(第2のレベル)のビット幅制御信号BWCが入力されるとき、オア回路OCB1およびオア回路OCB2がともにハイレベルの信号が出力され、すなわち、最下位アドレスデータの同相信号出力端子AYN および反転信号出力端子AYN

Bにハイレベルの信号が出力される。

【0023】

図3はカラムプリデコーダ50の構成を示す回路図である。

図3において、AC0 ,AC1 ,…,AC2N,AC2N+1はアンド回路、CL0 ,CL1 ,…,CL2N,CL2N+1はカラム線をそれぞれ示している。

図示のように、カラムプリデコーダ50は複数個のアンド回路AC0 ,AC1 ,…,AC2N,AC2N+1によって構成され、これらのアンド回路AC0 ,AC1 ,…,AC2N,AC2N+1の入力端子にカラムアドレスバッファ40からのアドレスデータの同相信号および反転信号がそれぞれ異なる組み合わせで入力されている。

なお、これらのアンド回路AC0 ,AC1 ,…,AC2N,AC2N+1にはカラムプリデコーダのイネーブル信号YDEがそれぞれ入力され、このイネーブル信号YDEによってカラムプリデコーダ50の動作が制御される。

【0024】

たとえば、イネーブル信号YDEがハイレベルのとき、アンド回路AC0 ,AC1 ,…,AC2N,AC2N+1がそれぞれの入力端子に入力されたアドレスデータの同相信号またはそれらの反転信号に応じて、カラム線CL0 ,CL1 ,…,CL2N,CL2N+1の内所定のカラム線がアクティブ状態に設定される。

たとえば、最下位のアドレスデータ入力端子YN にローレベルの信号が入力されたとき、偶数番目のカラム線がアクティブ状態に設定され、最下位のアドレスデータ入力端子YN にハイレベルの信号が入力されたとき、奇数番目のカラム線がアクティブ状態に設定される。

【0025】

図4はメモリアレイ100とカラムセレクタ60との構成を示す回路図である。

図4において、WL0 ,WL1 ,…,WLN はワード線、CL0 ,CL1 ,…,CL2N,CL2N+1はカラム線、BL0 ,/BL0 ,BL1 ,/BL1 ,…,BL2N+1,/BL2N+1はビット線、MC00,MC01,…,MC2N+1,Nはメモリセル、BUS0 ,/BUS0 ,BUS1 ,/BUS1 はデータバス、SW0A,SW0B,SW1A,SW1B,…,SW2N+1A ,SW2N+1B はスイッチング回路をそれぞれ示している。

【0026】

メモリアレイ100において、メモリセルMC00,MC01,,MC2N+1,Nが行列状に配置され、2N+2行、N+1列のメモリアレイが構成されている。各列に配置されたメモリセルがそれぞれワード線WL0 ,WL1 ,…,WLN+1 に接続され、各行に配置されたメモリセルがそれぞれペアを成しているビット線BL0 ,/BL0 ,BL1 ,/BL1 ,…,BL2N+1,/BL2N+1に接続されている。ビット線BL0 ,/BL0 ,BL1 ,/BL1 ,…,BL2N+1,/BL2N+1がそれぞれペアを成しているスイッチング回路SW0A,SW0B,SW1A,SW1B,…,SW2N+1A ,SW2N+1B を介してデータバスBUS0 ,/BUS0 ,BUS1 ,/BUS1 に接続されている。

【0027】

スイッチング回路SW0A,SW0B,SW1A,SW1B,…,SW2N+1A ,SW2N+1B は、たとえば、nMOSトランジスタによって構成され、これらのnMOSトランジスタのゲート電極がそれぞれカラム線CL0 ,CL1 ,…,CL2N,CL2N+1に接続されている。

たとえば、入力されたカラムアドレスCLMADRに応じて、所定のカラム線CLi がハイレベル状態、すなわち、アクティブ状態に設定されているとき、ペアを成しているスイッチング回路SWiA,SWiBがともに導通状態に設定され、奇数番目のビット線BLi ,/BLi がデータバスBUS0 ,/BUS0 に接続され、偶数番目のビット線BLi ,/BLi がデータバスBUS1 ,/BUS1 にそれぞれ接続される。

【0028】

ワード線WL0 ,WL1 ,…,WLN+1 がそれぞれロウデコーダ30に接続され、ロウデコーダ30によって、入力されたロウアドレスROWADRに応じて、所定ワード線WLj がアクティブ状態に設定されたとき、選択されたワード線WLj および選択されたビット線BLi ,/BLi の交点に配置されているメモリセルMCjiが選択され、当該メモリセルMCijに対して、データの書き込みまたは読み出しが行われる。

【0029】

たとえば、データの読み出しが行われるとき、選択されたメモリセルMCijに記憶されているデータがビット線BLi に、記憶されているデータの反転データがビット線/BLi にそれぞれ出力され、スイッチング回路SWiA,SWiBを介してデータバスBUSi ,/BUSi に出力される。

一方、データの書き込みが行われるとき、データバスBUSi ,/BUSi に印加された書き込みデータおよびその反転データがそれぞれスイッチング回路SWiA,SWiBを介してビット線BLi ,/BLi に入力され、さらに選択されたメモリセルMCijに書き込まれる。

【0030】

図5は入出力バッファ70の構成を示す回路図である。

図5において、201,202,…,207はアンド回路、208,209はオア回路、210,211,…,215はインバータ、216,217,218,219は出力バッファ、DOUT0,DOUT1はデータ出力端子、DIN0 ,DIN1 はデータ入力端子、DBUS0 ,/DBUS0 ,DBUS1 ,/DBUS1 はデータバスへの入力端子をそれぞれ示している。

なお、図5(a)はデータの出力バッファの回路図であり、図5(b)はデータの入力バッファの回路図である。

【0031】

図5(a)に示すように、データの出力バッファはアンド回路201,202,203、オア回路208およびインバータ210によって構成されている。

アンド回路201の入力端子がそれぞれデータバスBUS0 、カラムアドレスの反転信号出力端子AY N Bに接続され、アンド回路202の入力端子がそれぞれデータバスBUS1 、カラムアドレスの同相信号出力端子AY N およびおインバータ210の出力端子に接続されている。

インバータ210の入力端子がビット幅制御信号BWCの入力端子φに接続され、また、アンド回路203の入力端子がそれぞれデータバスBUS1 およびビット幅制御信号BWCの入力端子φに接続されている。

オア回路208の入力端子がそれぞれアンド回路201、202の出力端子に接続され、オア回路208の出力端子がデータ出力端子DOUT0に接続され、アンド回路203の出力端子がデータ出力端子DOUT1に接続されている。

【0032】

このような構成におけるデータの出力バッファはビット幅制御信号BWCに応じて、データ出力ビット数が制御される。

たとえば、ハイレベルのビット幅制御信号BWCが入力端子φに印加されている場合は、データバスBUS1 に印加されているデータ信号がアンド回路203を介してデータ出力端子DOUT1に出力される。また、このとき、インバータ210の出力端子にローレベルの信号が出力されるため、アンド回路202の出力端子にローレベルの信号が出力される。

【0033】

また、図2に示すように、ビット幅制御信号BWCがハイレベルに設定されているとき、カラムアドレスデータの反転信号出力端子AYN Bにハイレベルの信号が出力されるため、データバスの出力端子BUS0 に印加されている信号がアンド回路201を介して、オア回路208の入力端子に入力され、さらにオア回路208を介してデータ出力端子DOUT0に出力される。

【0034】

一方、ローレベルのビット幅制御信号BWCが入力端子φに印加されている場合は、アンド回路203がローレベルの信号が出力され、すなわち、データ出力端子DOUT1にローレベルの信号が出力される。

また、インバータ210の出力端子にハイレベルの信号が出力されるため、データ出力端子DOUT0の出力信号がカラムアドレス入力端子YN に印加されたカラムデータの最下位データによって決まる。

【0035】

たとえば、カラムデータの最下位データがハイレベルの場合、カラムアドレス端子AYN にハイレベルの信号が印加され、カラムアドレス端子AYN Bにローレベルの信号が印加されるため、データバスBUS1 の出力端子に印加されたデータがアンド回路202およびオア回路208を介してデータ出力端子DOUT0に出力される。

カラムデータの最下位データがローレベルの場合、カラムアドレス端子AYN Bにハイレベルの信号が印加され、カラムアドレス端子AYN にローレベルの信号が印加されるため、データバスBUS0 の出力端子に印加されたデータがアンド回路201およびオア回路208を介してデータ出力端子DOUT0に出力される。

【0036】

図5(b)に示すように、データの入力バッファはアンド回路204,205…,207、オア回路209およびインバータ211,212,…,215および出力バッファ216,217,218,219によって構成されている。

【0037】

インバータ211の入力端子がビット幅制御信号BWCの入力端子φに接続され、インバータ211の出力端子がアンド回路207の一方の入力端子に接続され、アンド回路207の他方の入力端子がデータ入力端子DIN1 に接続されている。

アンド回路206の一方の入力端子がデータ入力端子DIN0 に接続され、他方の入力端子がビット幅制御信号BWCの入力端子φに接続されている。

【0038】

アンド回路204の一方の入力端子がカラムアドレス端子AYN Bに接続され、他方の入力端子が入力イネーブル信号入力端子WEに接続されている。

アンド回路204の出力端子がインバータ212の入力端子に接続され、さらに出力バッファ216、217の正のイネーブル信号端子に接続されている。出力バッファ216の入力端子がデータ入力端子DIN0 に接続され、出力端子がデータバスの入力端子DBUS0 に接続されている。インバータ213の入力端子がデータ入力端子DIN0 に接続され、出力端子が出力バッファ217の入力端子に接続されている。出力バッファ217の出力端子がデータバスの入力端子/DBUS0 に接続されている。

また、インバータ212の出力端子が出力バッファ216、217の負のイネーブル信号入力端子に接続されている。

【0039】

アンド回路205の一方の入力端子がカラムアドレス端子AYN に接続され、他方の入力端子が入力イネーブル信号入力端子WEに接続されている。

アンド回路205の出力端子がインバータ214の入力端子に接続され、さらに出力バッファ218、219の正のイネーブル信号端子に接続されている。出力バッファ218の入力端子がオア回路209の出力端子に接続され、出力端子がデータバスの入力端子DBUS1 に接続されている。インバータ215の入力端子がオア回路209の出力端子に接続され、出力端子が出力バッファ219の入力端子に接続されている。出力バッファ219の出力端子がデータバスの入力端子/DBUS1 に接続されている。

また、インバータ214の出力端子が出力バッファ218、219の負のイネーブル信号入力端子に接続されている。

【0040】

データ入力バッファが上述した構成において、入力端子φに入力されたビット幅制御信号BWCによって入力データのビット幅が制御される。

入力端子φにハイレベルのビット幅制御信号BWCが入力された場合は、データ入力端子DIN0 の信号がアンド回路206を介して、オア回路209の入力端子に入力され、さらにオア回路209を介して、出力バッファ218、インバータ215に入力される。また、図2に示すように、入力端子φにハイレベルのビット幅制御信号BWCが入力されたとき、カラムアドレス端子AYN がハイレベルに設定されるため、イネーブル信号入力端子WEにローレベルの信号が印加されているとき、アンド回路205の出力端子にローレベルの信号が出力され、出力バッファ218、219がともに非導通状態に設定されており、データバスへのデータの出力が行われず、そして、イネーブル信号入力端子WEの立ち上がりエッジにおいて、アンド回路205の出力端子の信号がローレベルからハイレベルへと切り換えられ、出力バッファ218、219がともに導通状態に切り換わる。

【0041】

このため、データ入力端子DIN0 に入力された入力データがアンド回路206およびオア回路209を介して出力バッファ218の入力端子に入力され、さらにインバータ215を介して反転され、出力バッファ219の入力端子に入力される。そして、イネーブル信号入力端子WEの立ち上がりエッジで、出力バッファ218、219がともに導通状態に切り換えられ、これらの出力バッファの入力端子に入力されたデータがそれぞれデータバス入力端子DBUS1 ,/DBUS1 に出力される。

【0042】

これと同時に、データ入力端子DIN0 に入力されたデータが出力バッファ216の入力端子に出力され、さらにインバータ213を介して反転され、出力バッファ217の入力端子に出力される。イネーブル信号入力端子WEの立ち上がりエッジにおいて、アンド回路204の出力端子に出力された信号のレベルがローレベルからハイレベルに切り換わり、出力バッファ216、217がともに非導通状態から導通状態に切り換えられるため、これらの出力バッファの入力端子に入力されたデータがそれぞれデータバス入力端子DBUS0 ,/DBUS0 に出力される。

【0043】

一方、ビット幅制御信号BWC入力端子φにローレベルの信号が印加された場合、インバータ211の出力端子にハイレベルの信号が出力されるため、データ入力端子DIN1 に入力された信号がアンド回路207およびオア回路209を介して出力バッファ218の入力端子に入力され、さらにインバータ215を介して反転され、出力バッファ219の入力端子に入力される。

【0044】

また、これと同時に、データ入力端子DIN0 に入力された信号が出力バッファ216の入力端子に入力され、さらにインバータ213を介して反転され、出力バッファ217の入力端子に入力される。

【0045】

カラムアドレス入力端子YN にハイレベルのカラムアドレスデータが入力された場合、カラムアドレス端子AYN にハイレベル、カラムアドレス端子AYN Bにローレベルの信号がそれぞれ出力されるため、イネーブル信号入力端子WEの信号がローレベルからハイレベルに切り換えられるとき、アンド回路205の出力端子に出力された信号がローレベルからハイレベルに切り換えられ、出力バッファ218、219が導通状態に切り換えられ、データ入力端子DIN1 に入力されたデータがアンド回路207およびオア回路209を介して、さらに出力バッファ218を介してデータバス入力端子DBUS1 に出力され、また、オア回路209の出力端子の信号がインバータ215を介して反転され、出力バッファ219を介してデータバス入力端子/DBUS1 に出力される。

【0046】

また、イネーブル信号入力端子WEの立ち上がりエッジにおいて、出力バッファ216および217が導通状態に切り換えられるため、データ入力端子DIN0 に入力されたデータが出力バッファ216を介してデータバス入力端子DBUS0 に出力され、さらにデータ入力端子DIN0 に入力されたデータがインバータ213を介して反転され、出力バッファ217を介してデータバス入力端子/DBUS0 に出力される。

【0047】

上述したように、ビット幅制御信号BWCがハイレベルに設定されているとき、イネーブル信号入力端子WEの立ち上がりエッジにおいて、データ入力端子DIN0 に入力されたデータおよびその反転されたデータがそれぞれデータバス入力端子DBUS0 ,/DBUS0 ,DBUS1 ,/DBUS1 に出力される。

一方、ビット幅制御信号BWCがローレベルに設定されているとき、イネーブル信号入力端子WEの立ち上がりエッジにおいて、カラムアドレスの最下位データYN に応じて、データ入力端子DIN0 に入力されたデータおよびその反転されたデータがそれぞれデータバス入力端子DBUS0 ,/DBUS0 に出力され、データ入力端子DIN1 に入力されたデータおよびその反転されたデータがそれぞれデータバス入力端子DBUS1 ,/DBUS1 に出力される。

【0048】

図6は上述した入出力バッファ70におけるデータ出力時のタイミングチャートである。

図6に示すように、チップイネーブル信号/CEがアクティブ状態(ローレベル)に設定されたとき、カラムプリデコーダイネーブル信号YDEがハイレベルに設定される。そして、ビット幅制御信号BWCの入力端子φにローレベルの信号が入力されたとき、カラムプリデコーダイネーブル信号YDEと同期して、カラム線CL2Nもハイレベルに設定され、カラム線CL2N+1 がローレベルに保持され、カラム線CL2Nの電位変化に同期して、データバスBUS0 のデータがデータ出力端子DOUT0に出力され、データ出力端子DOUT1がもとの状態に保持される。

【0049】

一方、ビット幅制御信号BWCの入力端子φにハイレベルの信号が入力されたとき、カラムプリデコーダイネーブル信号YDEと同期して、カラム線CL2N,CL2N+1 がともにハイレベルに設定される。そして、これらのカラム線の電位変化に同期して、データ出力端子DOUT0,DOUT1にそれぞれデータバスBUS0 ,BUS1 のデータが出力される。すなわち、ビット幅制御信号BWCによって、出力データの幅が変化する。

すなわち、ビット幅制御信号BWCがローレベルに設定されたとき、出力データが1ビットとなり、出力データが出力端子DOUT0に出力される。ビット幅制御信号BWCがハイレベルに設定されたとき、出力データが2ビットとなり、出力データが出力端子DOUT0,DOUT1にそれぞれ出力される。

【0050】

以上説明したように、本実施形態によれば、半導体記憶装置にビット幅制御信号BWCの入力端子φを設け、当該入力端子φに入力された信号をカラムアドレスバッファ40、入出力バッファ70にそれぞれ入力し、入力端子φにローレベルの信号が入力されたとき、半導体記憶装置の入出力端子のビット数が通常より1ビット増え、データの入出力の幅がビット幅制御信号BWCによって制御されるので、データ入出力のビット幅が外部入力ピンに入力された制御信号のレベルによって容易に変更でき、アプリケーションによらずに多ビット同時試験が可能となり、試験時間の短縮および試験パターンの開発工数が短縮できる。

【0051】

なお、ASICメモリに本発明の半導体記憶装置が組み込まれることによって、ASICメモリにおける試験時間および試験パターンの開発工数の短縮を図れる。

【0052】

【発明の効果】

以上説明したように、本発明の半導体記憶装置によれば、アプリケーションによらずに多ビット同時試験が可能となり、試験時間の短縮および試験パターンの開発工数が短縮できる利点がある。

【図面の簡単な説明】

【図1】本発明に係る半導体記憶装置の一実施形態を示すブロック図である。

【図2】カラムアドレスバッファの構成を示す回路図である。

【図3】カラムプリデコーダの構成を示す回路図である。

【図4】メモリアレイおよびカラムセレクタの構成を示す回路図である。

【図5】入出力バッファの構成を示す回路図である。

【図6】入出力バッファにおけるデータ出力のタイミングチャートである。

【図7】従来の半導体記憶装置の構成を示すブロック図である。

【符号の説明】

10…ロウアドレスバッファ、20…ロウプリデコーダ、30…ロウデコーダ、40…カラムアドレスバッファ、50…カラムプリデコーダ、60…カラムセレクタ、70…入出力バッファ、100…メモリアレイ、DIN,DIN0 ,DIN1 …データ入力端子、DOUT ,DOUT0,DOUT1…データ出力端子、Y0 ,Y1 ,…,YN−1 ,YN …カラムアドレス入力端子、φ…ビット幅制御信号入力端子、AC0 ,AC1 ,…,AC2N,AC2N+1…アンド回路、201,202,…,207…アンド回路、208,209…オア回路、210,211,…,215…インバータ、216,217,218,219…出力バッファ、WL0 ,WL1 ,…,WLN …ワード線、BL0 ,/BL0 ,BL1 ,/BL1 ,…,BL2N+1,/BL2N+1…ビット線、CL0 ,CL1 ,…,CL2N,CL2N+1…カラム線、MC00,MC01,…,MC2N+1,N…メモリセル、SW0A,SW0B,SW1A,SW1B,…,SW2N+1A ,SW2N+1B …スイッチング回路、BUS0 ,/BUS0 ,BUS1 ,/BUS1 …データバス、DBUS0 ,/DBUS0 ,DBUS1 ,/DBUS1 …データバス入力端子[0001]

TECHNICAL FIELD OF THE INVENTION

The present invention relates to a semiconductor memory device.

[0002]

[Prior art]

When a test is performed on a memory core built in a conventional logic IC chip, data input / output is performed via a control signal terminal for controlling each operation of the memory core taken out and a data input / output terminal. Be done.

[0003]

FIG. 7 is a block diagram showing a configuration of such a memory core.

7, 10 is a row address buffer, 20 is a row predecoder, 30 is a row decoder, 40a is a column address buffer, 50a is a column predecoder, 60a is a column selector, 70 is an input / output buffer, 100 is a memory array, DINAnd DOUTIndicates a data input terminal and a data output terminal, respectively.

[0004]

As shown, the row address ROWADR is input to the

[0005]

On the other hand, the column address CLMADR is input to the

[0006]

As described above, the memory cells arranged at the intersections of these signal lines are selected by the selected word line and the selected bit line set to the active state, and data input / output is performed via the input /

For example, at the time of data input, that is, at the time of memory writing, the data input terminal DINIs written to the selected memory cell via the input /

On the other hand, at the time of data output, that is, at the time of memory reading, storage data is read from the selected memory cell, and the data output terminal D is output via the selected bit line and the input / output buffer 70a.OUTIs output to

[0007]

[Problems to be solved by the invention]

By the way, in the above-mentioned conventional memory core, the number of signal terminals and data input / output terminals of the memory core is determined depending on the application. As the capacity of the memory core increases, the test time increases.

Data input / output for each applicationPowerIf the number of terminals is changed, there is a problem that a test pattern must be created separately, and the memory core itself must be newly developed for each application.

[0008]

The present invention has been made in view of such circumstances, and has as its object the number of data input / output terminals can be easily changed by an external signal, multiple bits can be tested simultaneously regardless of the application, and the test time and test pattern can be adjusted. It is an object of the present invention to provide a semiconductor memory device that can reduce the number of development steps and reduce application dependency.

[0009]

[Means for Solving the Problems]

In order to achieve the above object, the present invention providesA memory array in which a plurality of memory cells are arranged, and selecting a memory cell addressed by a selected word line and a selected bit line set to an active state according to a row address and a column address; Through the aboveA semiconductor memory device for writing or reading data to or from a memory array,An address buffer circuit having a plurality of address buffer circuits for outputting the inputted plurality of column address data as an in-phase signal and an inverted signal, respectively, and receiving the lowest one of the plurality of address buffer circuits; When the bit width control signal is inputted at the first level, two signals, ie, an in-phase signal and an inverted signal of the inputted least significant column address data, are outputted, and the bit width control signal is outputted at the second level. And a column address buffer that outputs two signals of a predetermined same level irrespective of the input level of the least significant column address data, and output from the plurality of address buffer circuits of the column address buffer circuit. Set a predetermined column line among a plurality of column lines to an active state based on a plurality of signals. A column predecoder and a column selector having a plurality of switch circuits each connected to a different one of the column lines and making the bit line and the data bus conductive when the column line is in an active state; The input / output circuit receives the bit width control signal and the two output signals of the lowermost address buffer circuit of the column address buffer, and when the bit width control signal is at the first level, provides one data bus. An output buffer for outputting read data of two data buses when the bit width control signal is at the second level, and a lowermost address buffer of the bit width control signal and the column address buffer In response to the two output signals of the circuit, when the bit width control signal is at the first level, two data signals are output. The input data of the data input terminal is output to two data buses as write data, and when the bit width control signal is at the second level, the input data of one data input terminal is output to one data bus as write data. With an input buffer.

[0010]

Further, the semiconductor device of the present invention is incorporated in an ASIC memory.

[0011]

According to the present invention, an input terminal for an external bit width control signal is provided in the semiconductor memory device, and the number of input / output bits of the data input / output circuit is set by the bit width control signal input to the input terminal. .

For example, among a plurality of input / output terminals in the input / output circuit, a predetermined number of input / output terminals are selected according to the bit width control signal, and data input / output is performed through the selected input / output terminals. Done.

As a result, the number of data input / output terminals can be easily changed by an external signal, and application dependency can be reduced.

[0012]

In addition, by incorporating the above-described memory core into the ASIC memory, multiple bits can be tested simultaneously regardless of the application, and the test time and the number of test pattern development steps can be reduced.

[0013]

BEST MODE FOR CARRYING OUT THE INVENTION

FIG. 1 is a block diagram showing one embodiment of a semiconductor memory device according to the present invention.

In FIG. 1, 10 is a row address buffer, 20 is a row predecoder, 30 is a row decoder, 40 is a column address buffer, 50 is a column predecoder, 60 is a column selector, 70 is an input / output buffer, 100 is a memory array,INAnd DOUTIndicates a data input terminal and a data output terminal, respectively.

Further, ROWADR indicates a row address, CLMADR indicates a column address, and BWC indicates a bit width control signal.

[0014]

As shown, the row address ROWADR is input to the

[0015]

The row address ROWADR input to the

[0016]

The column address CLMADR input to the

[0017]

Then, the memory cell arranged at the intersection of the selected word line and the selected bit line set in the active state is selected, and data is input / output.

For example, when writing, the input terminal DINIs read by the input /

[0018]

Here, the bit width control signal BWC is input to each of the

Hereinafter, the configuration and operation of each part of the

[0019]

FIG. 2 is a circuit diagram showing a configuration of the

In FIG. 2, Y0, Y1, ..., YN-1, YNIs an input terminal of a column address CLMADR, φ is a bit width control signal BWC input terminal, AY0Is the input terminal Y0AY, the in-phase signal of the address data input to0B is input terminal Y0AY, the inverted signal of the address data input to AY1Is the input terminal Y1AY, the in-phase signal of the address data input to1B is input terminal Y1AY, the inverted signal of the address data input to AYN-1Is the input terminal YN-1AY, the in-phase signal of the address data input toN-1B is input terminal YN-1AY, the inverted signal of the address data input to AYNIs the input terminal YNAY, the in-phase signal of the address data input toNB is input terminal YN, The output terminals of the inversion signal of the address data input to are shown.

[0020]

As shown, the column address input terminal Y0, Y1, ..., YN-1The column address data input to the input terminals A and Y are output via a buffer circuit to the output terminal AY of the in-phase signal.0, AY1, ..., AYN-1And an inverted signal output terminal AY via an inverter.0B, AY1B, ..., AYN-1B.

For example, as shown in FIG.0The column address data input to the buffer circuit BUF0Through an in-phase signal output terminal AY0To the inverter INV0Signal output terminal AY via0B.

[0021]

The buffer circuit of the lowest address of the

Input terminal Y of lowest addressNIs the OR circuit OCB1One input terminal and the inverter INVNOf the inverter INVNOutput terminal is OR circuit OCB2Connected to one of the input terminals. Further, the input terminal φ of the bit width control signal BWC is connected to the OR circuit OC.B1And OR circuit OCB2Is connected to the other input terminal.

[0022]

Low level on input terminal φ(First level)When the bit width control signal BWC is input, the input terminal YN Signal output terminal AY of the in-phase signal of the lowest address input toN And the inverted signal is output to an inverted signal output terminal AYN B.

On the other hand, input terminal φ is high level(2nd level)When the bit width control signal BWC is input, the OR circuit OCB1And OR circuit OCB2Output a high-level signal, that is, the in-phase signal output terminal AY of the lowest address data.N And inverted signal output terminal AYN

A high level signal is output to B.

[0023]

FIG. 3 is a circuit diagram showing a configuration of the

In FIG. 3, AC0, AC1, ..., AC2N, AC2N + 1Is the AND circuit, CL0, CL1, ..., CL2N, CL2N + 1Indicates a column line.

As shown, the

Note that these AND circuits AC0, AC1, ..., AC2N, AC2N + 1Is supplied with a column predecoder enable signal YDE, and the operation of the

[0024]

For example, when the enable signal YDE is at a high level, the AND circuit AC0, AC1, ..., AC2N, AC2N + 1Corresponds to the in-phase signal of the address data input to each input terminal or the inverted signal thereof, and the column line CL0, CL1, ..., CL2N, CL2N + 1Are set to the active state.

For example, the lowest address data input terminal YNWhen a low-level signal is input to the even-numbered column line, the even-numbered column line is set to the active state, and the lowest address data input terminal YNWhen a high-level signal is input to the first column, the odd-numbered column lines are set to the active state.

[0025]

FIG. 4 is a circuit diagram showing a configuration of the

In FIG. 4, WL0, WL1, ..., WLNIs the word line, CL0, CL1, ..., CL2N, CL2N + 1Is the column line, BL0, / BL0, BL1, / BL1, ..., BL2N + 1, / BL2N + 1Is the bit line, MC00, MC01, ..., MC2N + 1, NIs a memory cell, BUS0, / BUS0, BUS1, / BUS1Is the data bus, SW0A, SW0B, SW1A, SW1B, ..., SW2N + 1A, SW2N + 1BIndicates a switching circuit.

[0026]

In

[0027]

Switching circuit SW0A, SW0B, SW1A, SW1B, ..., SW2N + 1A, SW2N + 1BIs formed of, for example, nMOS transistors, and the gate electrodes of these nMOS transistors are connected to column lines CL, respectively.0, CL1, ..., CL2N, CL2N + 1It is connected to the.

For example, according to the input column address CLMADR, a predetermined column line CLiAre set to the high level state, that is, the active state, the paired switching circuits SWiA, SWiBAre set to the conductive state, and the odd-numbered bit lines BLi, / BLiIs the data bus BUS0, / BUS0And the even-numbered bit lines BLi, / BLiIs the data bus BUS1, / BUS1Connected to each other.

[0028]

Word line WL0, WL1, ..., WLN + 1Are respectively connected to the

[0029]

For example, when data is read, the selected memory cell MCijIs stored in the bit line BLiAnd the inverted data of the stored data isiAnd the switching circuit SWiA, SWiBVia the data bus BUSi, / BUSiIs output to

On the other hand, when data is written, the data bus BUSi, / BUSiIs applied to the switching circuit SW, respectively.iA, SWiBThrough the bit line BLi, / BLi, And further selected memory cell MCijIs written to.

[0030]

FIG. 5 is a circuit diagram showing a configuration of the input /

5, 207 are AND circuits, 208, 209 are OR circuits, 210, 211,..., 215 are inverters, 216, 217, 218, 219 are output buffers, DOUT0, DOUT1Is the data output terminal, DIN0, DIN1Is the data input terminal, DBUS0, / DBUS0, DBUS1, / DBUS1Indicates input terminals to the data bus.

FIG. 5A is a circuit diagram of a data output buffer, and FIG. 5B is a circuit diagram of a data input buffer.

[0031]

As shown in FIG. 5A, the data output buffer includes AND

The input terminals of the AND

An input terminal of

The input terminal of the

[0032]

In the data output buffer having such a configuration, the number of data output bits is controlled according to the bit width control signal BWC.

For example, when the high-level bit width control signal BWC is applied to the input terminal φ, the data bus BUS1Is applied to the data output terminal D via the AND circuit 203.OUT1Is output to At this time, since a low-level signal is output to the output terminal of the

[0033]

As shown in FIG. 2, when the bit width control signal BWC is set to a high level, the inverted signal output terminal AY of the column address data is output.NSince a high-level signal is output to B, the output terminal BUS of the data bus0Is input to the input terminal of the

[0034]

On the other hand, when the low-level bit width control signal BWC is applied to the input terminal φ, the AND

Further, since a high-level signal is output to the output terminal of the

[0035]

For example, when the least significant data of the column data is at the high level, the column address terminal AYNTo the column address terminal AYNSince a low level signal is applied to B, the data bus BUS1Is applied to the output terminal of the data output terminal D via the AND

When the least significant data of the column data is low level, the column address terminal AYNB, a high level signal is applied to the column address terminal AY.NIs applied to the data bus BUS.0Applied to the output terminal of the data output terminal D via the AND

[0036]

As shown in FIG. 5B, the data input buffer includes AND

[0037]

The input terminal of

One input terminal of the AND

[0038]

One input terminal of the AND

The output terminal of the AND

The output terminal of the

[0039]

One input terminal of the AND

The output terminal of the AND

The output terminal of the

[0040]

In the configuration of the data input buffer described above, the bit width of the input data is controlled by the bit width control signal BWC input to the input terminal φ.

When the high-level bit width control signal BWC is input to the input terminal φ, the data input terminal DIN0 Is input to the input terminal of the

[0041]

Therefore, the data input terminal DIN0Is input to the input terminal of the

[0042]

At the same time, the data input terminal DIN0Is output to the input terminal of the

[0043]

On the other hand, when a low-level signal is applied to the bit width control signal BWC input terminal φ, a high-level signal is output to the output terminal of the inverter 211.IN1Is input to the input terminal of the

[0044]

At the same time, the data input terminal DIN0Is input to the input terminal of the

[0045]

Column address input terminal YNWhen high-level column address data is input to the column address terminal AYNHigh level, column address terminal AYNSince a low level signal is output to B, when the signal at the enable signal input terminal WE is switched from low level to high level, the signal output to the output terminal of the AND

[0046]

Further, at the rising edge of enable signal input terminal WE,

[0047]

As described above, when the bit width control signal BWC is set to the high level, the data input terminal D is at the rising edge of the enable signal input terminal WE.IN0Are input to the data bus input terminal DBUS, respectively.0, / DBUS0, DBUS1, / DBUS1Is output to

On the other hand, when the bit width control signal BWC is set to the low level, the least significant data Y of the column address at the rising edge of the enable signal input terminal WE.NAccording to the data input terminal DIN0Are input to the data bus input terminal DBUS, respectively.0, / DBUS0To the data input terminal DIN1Are input to the data bus input terminal DBUS, respectively.1, / DBUS1Is output to

[0048]

FIG. 6 is a timing chart when data is output from the input /

As shown in FIG. 6, when the chip enable signal / CE is set to the active state (low level), the column predecoder enable signal YDE is set to high level. When a low level signal is input to the input terminal φ of the bit width control signal BWC, the column line CL is synchronized with the column predecoder enable signal YDE.2NIs also set to the high level, and the column line CL2N +1 Is held at the low level, and the column line CL2NData bus BUS in synchronization with the potential change of0 Is the data output terminal DOUT0To the data output terminal DOUT1Is kept in its original state.

[0049]

On the other hand, the input terminal φ of the bit width control signal BWC isYesWhen a level signal is input, the column line CL is synchronized with the column predecoder enable signal YDE.2N, CL2N +1 Are both set to the high level. Then, in synchronization with the potential change of these column lines, the data output terminal DOUT0, DOUT1Data bus BUS0 , BUS1 Is output. That is, the width of the output data changes according to the bit width control signal BWC.

That is, the bit width control signal BWC isLowWhen set to the level, the output data becomes 1 bit and the output dataOUT0Is output to The bit width control signal BWC isYesWhen set to the level, the output data becomes 2 bits and the output dataOUT0, DOUT1Respectively.

[0050]

As described above, according to the present embodiment, the semiconductor memory device is provided with the input terminal φ of the bit width control signal BWC, and the signal input to the input terminal φ is supplied to the

[0051]

By incorporating the semiconductor memory device of the present invention into the ASIC memory, the test time and test pattern development man-hour for the ASIC memory can be reduced.

[0052]

【The invention's effect】

As described above, according to the semiconductor memory device of the present invention, a multi-bit simultaneous test can be performed regardless of the application, and there is an advantage that the test time and the number of test pattern development steps can be reduced.

[Brief description of the drawings]

FIG. 1 is a block diagram showing one embodiment of a semiconductor memory device according to the present invention.

FIG. 2 is a circuit diagram showing a configuration of a column address buffer.

FIG. 3 is a circuit diagram showing a configuration of a column predecoder.

FIG. 4 is a circuit diagram showing a configuration of a memory array and a column selector.

FIG. 5 is a circuit diagram showing a configuration of an input / output buffer.

FIG. 6 is a timing chart of data output in the input / output buffer.

FIG. 7 is a block diagram showing a configuration of a conventional semiconductor memory device.

[Explanation of symbols]

10 row address buffer, 20 row predecoder, 30 row decoder, 40 column address buffer, 50 column predecoder, 60 column selector, 70 input / output buffer, 100 memory array, DIN, DIN0, DIN1... Data input terminal, DOUT, DOUT0, DOUT1... Data output terminal, Y0, Y1, ..., YN-1, YN... column address input terminal, φ ... bit width control signal input terminal, AC0, AC1, ..., AC2N, AC2N + 1... AND circuits, 201, 202, ..., 207 AND circuits, 208, 209 OR circuits, 210, 211, ..., 215 ... inverters, 216, 217, 218, 219 ... output buffers, WL0, WL1, ..., WLN... word line, BL0, / BL0, BL1, / BL1, ..., BL2N + 1, / BL2N + 1... bit line, CL0, CL1, ..., CL2N, CL2N + 1… Column line, MC00, MC01, ..., MC2N + 1, N... Memory cell, SW0A, SW0B, SW1A, SW1B, ..., SW2N + 1A, SW2N + 1B... Switching circuit, BUS0, / BUS0, BUS1, / BUS1... Data bus, DBUS0, / DBUS0, DBUS1, / DBUS1… Data bus input terminal

Claims (2)

入力された複数のカラムアドレスデータをそれぞれ同相信号および反転信号として出力する複数のアドレスバッファ回路を有し、当該複数のアドレスバッファ回路のうち、最下位のカラムアドレスデータが入力されるアドレスバッファ回路は、ビット幅制御信号が第1のレベルで入力されると入力された最下位のカラムアドレスデータの同相信号および反転信号の2つの信号を出力し、上記ビット幅制御信号が第2のレベルで入力されると上記最下位のカラムアドレスデータの入力レベルにかかわらず所定の同レベルの2つの信号を出力するカラムアドレスバッファと、

上記カラムアドレスバッファ回路の上記複数のアドレスバッファ回路から出力された複数の信号に基づいて複数のカラム線のうち所定のカラム線をアクティブ状態に設定するカラムプリデコーダと、

それぞれが異なる上記カラム線に接続され、上記ビット線とデータバスとを当該カラム線がアクティブ状態のときに導通状態とする複数のスイッチ回路を有するカラムセレクタと、を有し、

上記入出力回路は、

上記ビット幅制御信号および上記カラムアドレスバッファの最下位のアドレスバッファ回路の2つの出力信号を受けて、当該ビット幅制御信号が第1のレベルのときは、1つのデータバスの読み出しデータを出力し、上記ビット幅制御信号が第2のレベルのときは2つのデータバスの読み出しデータを出力する出力バッファと、

上記ビット幅制御信号および上記カラムアドレスバッファの最下位のアドレスバッファ回路の2つの出力信号を受けて、当該ビット幅制御信号が第1のレベルのときは、2つのデータ入力端子の入力データを書き込みデータとして2つのデータバスに出力し、上記ビット幅制御信号が第2のレベルのときは1つのデータ入力端子の入力データを書き込みデータとして1つのデータバスに出力する入力バッファと、を有する

半導体記憶装置。 A memory array in which a plurality of memory cells are arranged, and selecting a memory cell addressed by a selected word line and a selected bit line set to an active state according to a row address and a column address; A semiconductor memory device for writing or reading data to or from the memory array via

An address buffer circuit having a plurality of address buffer circuits for outputting the inputted plurality of column address data as an in-phase signal and an inverted signal, respectively, and receiving the lowest one of the plurality of address buffer circuits; When the bit width control signal is inputted at the first level, two signals, ie, an in-phase signal and an inverted signal of the inputted least significant column address data, are outputted, and the bit width control signal is outputted at the second level. A column address buffer that outputs two signals of a predetermined same level regardless of the input level of the lowest column address data when

A column predecoder that sets a predetermined column line among a plurality of column lines to an active state based on a plurality of signals output from the plurality of address buffer circuits of the column address buffer circuit;

A column selector having a plurality of switch circuits each connected to a different one of the column lines, and making the bit line and the data bus conductive when the column line is in an active state;

The input / output circuit is

Upon receiving the bit width control signal and the two output signals of the lowermost address buffer circuit of the column address buffer, when the bit width control signal is at the first level, the read data of one data bus is output. An output buffer for outputting read data of two data buses when the bit width control signal is at a second level;

Receiving the bit width control signal and the two output signals of the lowermost address buffer circuit of the column address buffer, and when the bit width control signal is at the first level, writes the input data of two data input terminals. An input buffer that outputs data to two data buses as data, and outputs input data of one data input terminal to one data bus as write data when the bit width control signal is at the second level. /> Semiconductor storage device.

請求項1に記載の半導体記憶装置。2. The semiconductor memory device according to claim 1, wherein the semiconductor memory device is incorporated in an ASIC memory.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP04509296A JP3557774B2 (en) | 1996-03-01 | 1996-03-01 | Semiconductor storage device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP04509296A JP3557774B2 (en) | 1996-03-01 | 1996-03-01 | Semiconductor storage device |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH09237498A JPH09237498A (en) | 1997-09-09 |

| JP3557774B2 true JP3557774B2 (en) | 2004-08-25 |

Family

ID=12709677

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP04509296A Expired - Fee Related JP3557774B2 (en) | 1996-03-01 | 1996-03-01 | Semiconductor storage device |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3557774B2 (en) |

-

1996

- 1996-03-01 JP JP04509296A patent/JP3557774B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH09237498A (en) | 1997-09-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US4365319A (en) | Semiconductor memory device | |

| US6999371B2 (en) | Semiconductor memory device capable of reducing power consumption during reading and standby | |

| KR100386442B1 (en) | Memory device circuit and method of simultaneous addressing of multi-bank columns of a multi-bank memory array | |

| US6490210B2 (en) | Semiconductor memory integrated circuit employing a redundant circuit system for compensating for defectiveness | |

| JPS63106998A (en) | Semiconductor memory with test circuit | |

| EP0622803B1 (en) | Address buffer | |

| EP0881571A1 (en) | Semiconductor memory device with redundancy | |

| US4962327A (en) | Decoder circuit having selective transfer circuit for decoded output signal | |

| EP0172112B1 (en) | Semiconductor memory device | |

| US6515927B2 (en) | Semiconductor memory having a wide bus-bandwidth for input/output data | |

| US7605434B2 (en) | Semiconductor memory device to which test data is written | |

| EP0953912B1 (en) | Semiconductor memory device with redundancy | |

| KR970023369A (en) | Semiconductor memories and their test circuits, memory systems and data transfer systems | |

| US6363027B1 (en) | Semiconductor memory device | |

| US6781917B2 (en) | Semiconductor memory device with dual port memory cells | |

| KR100336955B1 (en) | Semiconductor storage device | |

| JP3557774B2 (en) | Semiconductor storage device | |

| US6538941B2 (en) | Semiconductor memory device and method of pre-charging I/O lines | |

| US6201741B1 (en) | Storage device and a control method of the storage device | |

| JP2003196985A (en) | Semiconductor memory, bit-write method or byte-write method for semiconductor memory | |

| US5337287A (en) | Dual port semiconductor memory device | |

| KR100311571B1 (en) | Semiconductor memory device | |

| JP2590701B2 (en) | Semiconductor storage device | |

| CN112581998B (en) | Memory device and method of operating the same | |

| JPH01178199A (en) | Static type semiconductor storage device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20040427 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20040510 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090528 Year of fee payment: 5 |

|

| LAPS | Cancellation because of no payment of annual fees |