JP2023047330A - 表示パネルにおける焼き付きの領域ベースでの可変補償のためのシステム及び方法 - Google Patents

表示パネルにおける焼き付きの領域ベースでの可変補償のためのシステム及び方法 Download PDFInfo

- Publication number

- JP2023047330A JP2023047330A JP2022149724A JP2022149724A JP2023047330A JP 2023047330 A JP2023047330 A JP 2023047330A JP 2022149724 A JP2022149724 A JP 2022149724A JP 2022149724 A JP2022149724 A JP 2022149724A JP 2023047330 A JP2023047330 A JP 2023047330A

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- luminance value

- value

- compensation

- region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000000034 method Methods 0.000 title claims abstract description 24

- 230000001186 cumulative effect Effects 0.000 claims description 95

- 230000015556 catabolic process Effects 0.000 description 10

- 238000006731 degradation reaction Methods 0.000 description 10

- 230000007774 longterm Effects 0.000 description 10

- 238000013481 data capture Methods 0.000 description 4

- 238000009825 accumulation Methods 0.000 description 3

- 241000907513 Dakar bat virus Species 0.000 description 2

- 230000006399 behavior Effects 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 238000012512 characterization method Methods 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000003384 imaging method Methods 0.000 description 2

- 230000003466 anti-cipated effect Effects 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

- 230000001960 triggered effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/10—Intensity circuits

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0233—Improving the luminance or brightness uniformity across the screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0271—Adjustment of the gradation levels within the range of the gradation scale, e.g. by redistribution or clipping

- G09G2320/0276—Adjustment of the gradation levels within the range of the gradation scale, e.g. by redistribution or clipping for the purpose of adaptation to the characteristics of a display device, i.e. gamma correction

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0285—Improving the quality of display appearance using tables for spatial correction of display data

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/043—Preventing or counteracting the effects of ageing

- G09G2320/046—Dealing with screen burn-in prevention or compensation of the effects thereof

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2360/00—Aspects of the architecture of display systems

- G09G2360/16—Calculation or use of calculated indices related to luminance levels in display data

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Electroluminescent Light Sources (AREA)

- Chemical & Material Sciences (AREA)

- Inorganic Chemistry (AREA)

- Life Sciences & Earth Sciences (AREA)

- Sustainable Development (AREA)

- Liquid Crystal Display Device Control (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Control Of El Displays (AREA)

Abstract

【課題】撮像素子の上方に配置された画素について、ディスプレイの他の領域にある画素と異なる態様で補償するバーンイン補償システム及び方法。【解決手段】表示ドライバが画像処理回路部とソースドライバとを備えている。画像処理回路部は、表示パネルの第1領域にある第1画素の第1累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って第1画素の第1補償後輝度値を決定するように構成されている。第1領域は、第1画素レイアウトを有している。画像処理回路部は、更に、表示パネルの第2領域にある第2画素の第2累積輝度値をスケーリングしてスケーリング後累積輝度値を決定するように構成されている。第2領域は、第1画素レイアウトと異なる第2画素レイアウトを有している。画像処理回路部は、更に、スケーリング後累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って第2画素の第2補償後輝度値を決定するように構成されている。【選択図】図2

Description

本願は、2021年9月24日に出願された米国特許出願第63/248,394号の非仮出願であり、よって、米国特許出願第63/248,394号への米国特許法第119条(e)による利益を主張する。米国特許出願第63/248,394号は、参照することによりそのまま組み込まれる。

本開示は、全体としては表示パネルの分野に関しており、特に、焼き付き(burn-in)の効果の補償に関している。

有機発光ダイオード(OLED)ディスプレイ、マイクロ発光ダイオード(LED)ディスプレイ、液晶ディスプレイ(LCD)のような表示装置は、画素素子の過度の使用による焼き付きアーティファクトの影響を受けやすいことがある。これらの焼き付きアーティファクトは、パネルの個々の画素の生涯使用に依存している。多用された画素は、使用が限定された画素よりも早く劣化することがある。焼き付きを補償するために固有の画素補償が付加されることがある。基板に取り付けられたメモリが、各画素について長期使用データを格納することがある。補償により、多用された画素には大きなゲイン係数が印加され、使用が少ない画素には小さなゲイン係数が印加されることがある。

近年の表示システムは、ディスプレイの下にカメラのような撮像素子が設けられることがある。これらの撮像素子の上方に配置される画素は、十分な光が画素を通過して撮像素子に到達できるように他の領域にある画素とは異なる画素レイアウトで配置されることがある。この場合、撮像素子の上方の当該画素は、ディスプレイを均一に保つためにより明るい信号で駆動されることがある。これにより、撮像素子の情報に配置される画素には、ディスプレイの他の領域にある画素よりも早い劣化が生じることがある。

撮像素子の上方に配置された画素について、ディスプレイの他の領域にある画素と異なる態様で補償するバーンイン補償システム及び方法のニーズが存在する。

この要約は、以下において発明の詳細の説明において更に説明する概念の選択を簡潔な形態で紹介するために提供されている。この要約は、請求された主題の主要な特徴又は不可欠な特徴を特定することを意図しておらず、請求された主題の範囲を限定することも意図していない。

一般に、一の態様では、一以上の実施形態が画像処理回路部とソースドライバとを備える表示ドライバに関している。画像処理回路部は、表示パネルの第1領域にある第1画素の第1累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って第1画素の第1補償後輝度値を決定するように構成されている。第1領域は、第1画素レイアウトを有している。画像処理回路部は、更に、表示パネルの第2領域にある第2画素の第2累積輝度値をスケーリングしてスケーリング後累積輝度値を決定するように構成されている。第2領域は、第1画素レイアウトと異なる第2画素レイアウトを有している。画像処理回路部は、更に、スケーリング後累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って第2画素の第2補償後輝度値を決定するように構成されている。ソースドライバは、第1補償後輝度値に少なくとも部分的に基づいて第1画素を更新し、第2補償後輝度値に少なくとも部分的に基づいて第2画素を更新するように構成されている。

一以上の実施形態では、表示画素の長期累積輝度がメモリ装置に記録されてもよい。表示パネルへの出力階調レベルは、累積輝度値と個別の表示パネルの焼き付きプロファイルとに基づいて補償され得る。一以上の実施形態では、異なる密度又は構成の画素を用いる表示パネルの複数の領域について異なる補償値が使用され得る。

一般に、一の態様では、一以上の実施形態が表示パネルと表示ドライバとを備える表示装置に関している。表示パネルは、第1画素レイアウトを有する第1領域と、第1画素レイアウトと異なる第2画素レイアウトを有する第2領域とを備えている。表示ドライバは、表示パネルの第1領域にある第1画素の第1累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って第1画素の第1補償後輝度値を決定するように構成されている。表示ドライバは、更に、表示パネルの第2領域にある第2画素の第2累積輝度値をスケーリングしてスケーリング後累積輝度値を決定するように構成されている。表示ドライバは、更に、スケーリング後累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って第2画素の第2補償後輝度値を決定するように構成されている。表示ドライバは、第1補償後輝度値に少なくとも部分的に基づいて第1画素を更新し、第2補償後輝度値に少なくとも部分的に基づいて第2画素を更新するように構成されている。

一般に、一の態様では、一以上の実施形態が第1領域と第2領域とを備える表示パネルを駆動する方法に関している。第1領域は第1画素レイアウトを有しており、第2領域は第1画素レイアウトと異なる第2画素レイアウトを有している。当該方法は、表示パネルの第1領域にある第1画素の第1累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って第1画素の第1補償後輝度値を決定することを含む。当該方法は、更に、表示パネルの第2領域にある第2画素の第2累積輝度値をスケーリングしてスケーリング後累積輝度値を決定することを含む。当該方法は、更に、スケーリング後累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って第2画素の第2補償後輝度値を決定することを含む。当該方法は、更に、第1補償後輝度値に少なくとも部分的に基づいて第1画素を更新することと、第2補償後輝度値に少なくとも部分的に基づいて第2画素を更新することとを含む。

実施形態の他の観点は、以下の説明と添付された特許請求の範囲から明らかであろう。

本開示の上記された特徴が詳細に理解可能なように、上記に簡潔に要約されている本開示のより具体的な説明が、実施形態を参照してなされることがある。実施形態のうちのいくつかは添付図面に図示されている。しかしながら、添付図面は、例示的な実施形態を図示しているにすぎず、本開示は他の同様に有効な実施形態を認めているのであるから、発明の範囲を限定していると考えるべきでないことに留意すべきである。

理解を容易にするために、可能であれば、図面に共通の同一の要素を指し示すために同一の参照符号が用いられている。一の実施形態に開示された要素は、特に記載しなくとも他の実施形態に有益に使用され得ることが予期されている。同一の要素を互いに区別するために、参照符号に添字が付されることがある。本明細書で参照する図面は、特に言及がない限り、寸法通りに描かれていると理解されるべきではない。また、提示及び説明の明確性のために、図面は、しばしば、詳細又は構成部品が省略されて簡単化される。図面及び議論は、以下に議論する原理を説明するために役立つものであり、類似の符号は類似の要素を示している。

下記の詳細な説明は、本質的に単に例示的なものであり、本開示や本開示の用途及び使用法について限定する意図はない。更に、前述した技術分野、背景又は下記の詳細な説明において提示されている明示的な又は暗示的な理論によって拘束される意図もない。

下記の実施形態の詳細な説明では、開示された技術のより深い理解を提供するために、多くの具体的な詳細が記述されている。しかしながら、これらの具体的な詳細がなくとも開示された技術が実施され得ることは、当業者には自明であろう。他の例としては、記載を不必要に複雑化することを避けるために、周知の構成は詳細には説明していない。

出願全体にわたり、序数(例えば、第1、第2、第3、等)が、要素(即ち、出願における任意の名詞)のための形容詞として使用されることがある。序数の使用は、「前」、「後」、「単一の」という用語及び他の同様な術語の使用によって明文で開示されていない限り、要素の如何なる特定の順序付けを示唆又は生成するためのものではなく、如何なる要素が単一の要素のみであると限定するものでもない。むしろ、序数の使用は、要素を区別するためのものである。例えば、第1要素は第2要素とは別途のものであり、第1要素は、一より多い要素を包含することがあり、要素の順序付けにおいて第2要素に後続する(又は先行する)ことがある。

OLEDディスプレイ、マイクロLEDディスプレイ及びLCDのような表示装置は、画素の過度の使用からの焼き付きアーティファクトの影響を受けやすいことがある。これらの焼き付きアーティファクトは、画素の生涯の間、個々の画素がパネルにおいてどれだけ使用されたかに依存する。多用された画素は、使用が限定された画素よりも早く劣化することがある。個々の画素の累積輝度値が、焼き付きを補償するために使用されることがある。

ディスプレイの領域は、長期の焼き付きプロファイルが相違し得る異なる画素レイアウトの画素を含むことがある。画素レイアウトの相違は、(ピクセルパーインチ(PPI)を指標とすることがある)画素密度、構成、大きさ及び配置のうちの一以上における相違を含むことがある。例えば、低画素密度の画素は、それぞれ、その低密度を補償するために多く使用されることがある。その結果、高密度領域の画素と比較して、焼き付きアーティファクトのリスクが高くなる。ある所与の表示パネルは、ディスプレイの異なる領域における長期の劣化を補正するために、画素要素の劣化とディスプレイに加えられる補償のために特徴付けられることがある。

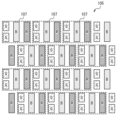

図1Aは、一以上の実施形態による、異なる画素レイアウトを有する複数の領域を含む表示パネル102を備える表示装置100の例示的な構成を図示している。表示パネル102の例としては、OLED表示パネル、マイクロLED表示パネル及びLCDパネルが挙げられる。図示された実施形態では、表示パネル102が、第1画素レイアウトを有する第1領域105と、第1画素レイアウトと異なる第2画素レイアウトを有する第2領域106とを備えている。2つの領域のみが図示されているが、一以上の実施形態の範囲から逸脱することなく2つより多い領域が存在し得る。表示パネル102は、表示パネル102を更新するように構成された表示ドライバ104に接続されることがある。

表示パネル102の第1領域105及び第2領域106の形状及び/又は配置は、様々に変更され得る。図1Bは、一以上の実施形態による、表示パネル102の他の例示的な構成を図示している。図示された実施形態では、第2領域106が表示パネル102に規定された矩形の領域であり、第1領域105が残りの領域として規定されている。第2領域106は、アンダーディスプレイカメラ(UDC)領域として使用されてもよい。UDC150は、UDC領域の背後に設けられてUDC領域を通じて画像を撮像するように設けられる。このような実施形態では、第2領域106は、第1領域105よりも低い画素密度を有している。

図1Cは、一以上の実施形態による、第1領域105の例示的な画素レイアウトを図示している。図示された実施形態では、第1領域105は、それぞれが赤(R)画素、2つの緑(G)画素及び青(B)画素を有する画素セット107を備えている。図1C(及び図1D)において、“R”、“G”及び“B”は、それぞれ、赤画素、緑画素及び青画素を示している。画素セット107のR、G及びB画素は、それぞれ、表示ドライバ104から受け取ったデータ信号で更新され、該データ信号に対応する輝度の光を発するように構成されている。

図1Dは、一以上の実施形態による、第2領域106における例示的な画素レイアウトを図示している。図示された実施形態では、第2領域106は、それぞれが1つのR画素、1つのG画素及び1つのB画素を備える複数の画素セット108を備えることがある。画素は、第2領域106の画素密度が第1領域105の画素密度より低くなるように配置されている。一の実装では、第2領域106における隣接する2つの画素の間隔が、第1領域105よりも大きい。画素セット108のR、G及びB画素は、それぞれ、表示ドライバ104から受け取ったデータ信号で更新され、該データ信号に対応する輝度の光を発するように構成されている。

図1Eは、一以上の実施形態による、表示パネル102の第1領域105と第2領域106の画素レイアウトの他の例を図示している。図示された実施形態では、第1領域105は、それぞれが1つの赤(R)画素、2つの緑(G)画素及び1つの青(B)画素を備える画素セット107A及び107Bを備えている。画素セット107A及び107Bは、2つの緑サブピクセルに対する赤及び青画素の相対位置が相違している。第2領域106は、画素セット107Aと同一に構成された画素セット108Aを備えている。図示された実施形態では、画素セット107A及び107Bは、第1領域105において互いに隣接して設けられる一方、画素セット108Aは、第2領域106において互いに離間している。従って、第2領域106の画素密度は第1領域105の画素密度よりも低い。図示された実施形態では、第2領域106の画素密度は、第1領域105の画素密度の4分の1である。

異なる画素レイアウトを有する第1領域105及び第2領域106にわたって連続する画像を表示するために、画素を更新するために使用されるデータ信号の信号レベル(例えば、電圧レベル)は、同一の階調であっても第1領域105と第2領域106の間で相違する。データ信号の信号レベルの相違により、長期の焼き付きプロファイルは相違し得る。一以上の実施形態では、エリア、即ち、画素レイアウトに依存してバーンイン補償が実施される。

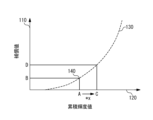

図1Fは、x軸120に沿った累積輝度値に対するy軸110に沿った補償値のグラフを図示している。一の実装では、ある画素の累積輝度値は、当該画素の輝度値の積算である場合がある。当該画素の輝度値は、当該画素を更新するために当該画素について指定された対応する階調値に基づいてそれぞれに算出されてもよい。所与の階調値についての、ある画素の算出された輝度値は該画素の輝度に対応していることがある。一の実施形態では、画素の累積輝度値が方向120において増加するほど、必要な補償値が方向110において増加する。この例で描かれた趨勢線130は、例示の目的のものである。他の実施形態では、趨勢線130は負の勾配を有していてもよく、線形の関係を有していてもよく、図1Fで図示した関係と異なる非線形の関係を有していてもよい。

一実施形態では、システムが、補償値を適用することによって累積輝度値を補償するように構成されることがある。位置140で示された例では、累積輝度値が値Aとして記録されることがあり、対応する補償値が値Bである場合がある。一以上の実施形態では、システムが、メモリ素子にアクセスすることによって累積輝度値を受け取ることがあり、ルックアップテーブルに基づいて対応する補償値を算出することがある。他の実施形態では、システムは、レジスタから累積輝度値を受け取り、趨勢線130の形状に基づいた計算を適用することにより対応する補償値を算出することがある。

累積輝度値Aと対応する補償値Bとで表される組は、表示パネルの第1領域(例えば、図1A~1Eに図示されている第1領域105)にある画素に適用される補償を表すことがある。表示パネルの第2領域(例えば、図1A~1Eに図示されている第2領域106)は、累積輝度に第1領域と異なる態様で応答する画素を含んでいることがある。一実施形態では、第2領域の画素は、表示パネルの下に、カメラを含むがそれに限定されない撮像素子(例えば、カメラ)を収容するために、異なる密度及び/又は構成を有している。第2領域の画素は、第1領域にある標準の画素と同一の輝度を生成するために、より強い輝度の駆動にさらされることがあり、第1領域にある画素よりも早く劣化し得る。位置Aにおける累積輝度値がスケーリング係数xによってスケーリング又は調節されて位置Cにおいてスケーリング後累積輝度値を得るようにスケーリング係数(又は補正係数)xが第2領域の画素に適用されることがある。この調節後の累積輝度値Cは、値Dの補償値をもたらす。スケーリング係数xは、第1領域と第2領域の画素レイアウトに依存することがある。一以上の実施形態では、スケーリング係数xは、第1領域と第2領域の画素密度に基づいている。第1領域が第1画素密度を有しており、第2領域が第2画素密度を有する実施形態では、スケーリング係数が、第1画素密度の第2画素密度に対する比に基づいていてもよい。

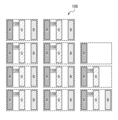

図2は、開示されたシステムの一実施形態のブロック図である。表示ドライバ200は、ホスト装置210に通信可能に結合されることがある。ホスト装置210は、表示ドライバ200に画像情報を送信することがあり、表示ドライバ200は、該画像情報に基づいて表示パネル270を更新するように構成されることがある。一の実装では、表示ドライバ200は、表示ドライバ集積回路(DDIC)であってもよい。

図示された実施形態では、表示パネル270が第1領域271と第2領域272とを備えている。図示された実施形態では、第1領域271は、第2領域272の外側の領域である。第1領域271と第2領域272とは異なる画素レイアウトを有している。第1領域271は、図1A~図1Eに図示されている第1領域105の一実施形態であってもよく、第2領域272は、図1A~図1Eに図示されている第2領域106の一実施形態であってもよい。第2領域272は、第1領域271にある画素と異なる光学的応答を有する画素を備えていてもよい。例えば、第2領域272にある画素のガンマ特性は、第1領域271にある画素のガンマ特性と異なる場合がある。ここでいうガンマ特性とは、画素輝度の階調レベルに対する依存性である。アンダーディスプレイカメラ(UDC)を収容するために、第2領域272の画素は、第1領域271にある画素と異なる密度及び/又は構成を有していることがある。第2領域272にある画素が第1領域271にある画素よりも大きく離間され、第2領域272の画素密度が第1領域271の画素密度よりも低い場合がある。第2領域272にある画素は、第1領域271にある画素と異なる長期焼き付きプロファイルを有していることがある。第2領域272にある画素は、第1領域271にある画素よりも大きい又は小さい補償値を必要とすることがある。

図示された実施形態では、表示ドライバ200が、画像データレシーバ220と、輝度制御ブロック221と、画像処理回路部230と、デバーンランダムアクセスメモリ(RAM)250と、ソースドライバ260とを備えている。画像データレシーバ220は、ホスト装置210から画像情報を受け取り、受け取った画像情報を画像データ225にデコードするように構成されている。画像データ225は、原階調値226と、それに対応する固有の画素位置227とを含んでいる。

輝度制御ブロック221は、ホスト装置210から輝度情報を受け取り、輝度情報に少なくとも部分的に基づいて輝度設定222を生成するように構成されている。輝度設定222は、表示パネル270の所望のディスプレイ輝度レベルを指定するディスプレイ輝度値(DBV)を含むことがある。所望のディスプレイ輝度レベルは、表示パネル270に表示される画像全体の所望の輝度レベルであってもよい。

デバーンRAM250は、表示パネル270の各画素について累積輝度値を格納するように構成されている。ある画素の累積輝度値は、当該画素について決定又は算出された輝度値の累積であってもよい。該画素の輝度値は、当該画素を更新するために該画素について指定された階調値に基づいて算出されることがある。累積輝度値は、個々の画素毎にデバーンRAM250に格納されてもよく、デバーンRAM250におけるメモリ帯域及び大きさを節約するためにM×N画素の寸法のより大きな矩形領域について実施されてよい。ここで、MとNは、2以上の整数である。矩形領域の大きさは、第1領域271と第2領域272とで異なっていてもよい。

画像処理回路部230は、画像データ225と輝度設定222とを受け取り、輝度設定222に基づいて画像データ225を処理するように構成される。図示された実施形態では、画像処理回路部230は、デバーンRAM250から受け取った累積輝度値251に少なくとも部分的に基づいて画像データ225に対してバーンイン補償を行って表示パネル270の各画素について補償後輝度値を生成するように構成される。

ソースドライバ260は、表示パネル270の画素について生成された対応する補償後輝度値に少なくとも部分的に基づいて当該画素を更新するように構成されている。ソースドライバ260は、データ信号が、表示パネル270の各画素について生成された補償後輝度値に対応する信号レベル(例えば、電圧レベル)を有するように各画素についてデータ信号を生成するように構成されてもよい。ソースドライバ260は、更に、生成したデータ信号を対応する画素に供給し、これにより各画素を更新するように構成されてもよい。

図示された実施形態では、画像処理回路部230は、ガンマ補正ブロック235とデバーンコントローラ240と加算器280とを備えている。ガンマ補正ブロック235は、画像データ225と輝度設定222とを受け取り、輝度設定222に基づいて画像データ225に対してガンマ補正を行って表示パネル270の各画素についてガンマ補正後輝度値を出力するように構成されている。輝度設定222がDBVを含む実施形態では、ガンマ補正ブロック235の入出力特性(即ち、画像データ225に記述された原階調値226とガンマ補正ブロック235から出力されるガンマ補正後輝度値との間の対応関係)が、表示パネル270においてDBVによって指定された通りのディスプレイ輝度レベルを実現するようにDBVに基づいて調節される。

デバーンコントローラ240は、デバーンRAM250から表示パネル270の各画素について累積輝度値251を読み出し、累積輝度値251に少なくとも部分的に基づいて各画素について補償値245を計算するように構成されている。一の実装では、補償値245は、対応する累積輝度値251が増加すると共に増加する。補償値245は、値を含むルックアップテーブルに基づいて計算されてもよく、累積輝度値251を補償値245に変換するための格納された数式に基づいて計算されてもよい。各画素についての補償値245は、更に、各画素に対応する画像データ225内の原階調値226に依存していてもよい。このようにして計算された補償値245は、加算器280に供給される。

加算器280は、ガンマ補正後輝度値に対してバーンイン補償を適用して表示パネル270の各画素について補償後輝度値を生成するために使用される。加算器280は、累積輝度値251に基づいて決定された補償値245をガンマ補正後輝度値に適用して補償後輝度値を生成するように構成されてもよい。補償後輝度値は、個別の画素位置の長期の焼き付きに対処するものとなっている。一の実装では、加算器280は、対応するガンマ補正後輝度値に補償値245を加算して、対応する補償後輝度値を各画素について生成するように構成されてもよい。補償後輝度値は、ソースドライバ260に供給され、各画素の更新に用いられるデータ信号を生成するために使用される。

一以上の実施形態では、デバーンコントローラ240が、更に、画像データ225を受け取り、原階調値226と輝度設定222とを用いてデバーンRAM250内の累積輝度値251を更新するように構成されてもよい。より高い輝度値で画素が駆動されるにつれ、当該画素の累積輝度値251が増加し、デバーンRAM250において更新され、格納される。周期的に、デバーンRAM250の内容が不揮発性メモリ255に書き込まれてもよい。デバーンRAM250の内容が、表示ドライバ200の電源ダウンのシーケンスの一部として不揮発性メモリ255に書き込まれてもよく、不揮発性メモリ255の内容を更新するためのタイマー起因又はユーザによって開始された動作の一部として不揮発性メモリ255に書き込まれてもよい。

動作時、表示システムは、デバーンRAM250から累積輝度値251を読み出すことがある。累積輝度値251の読み出しは、画像データ225内の個別の画素位置227に基づいていてもよい。デバーンコントローラ240は、読み出した累積輝度値251に基づいて補償値245を生成するように構成されてもよい。焼き付きに対する感受性が高い第2領域272の画素を補償するために、第2領域272の画素位置は、第1領域271の画素位置よりも大きな補償値245を生成することがある。

動作時では、表示ドライバ200の電源がオンされると、不揮発性メモリ255の内容がデバーンRAM250に書き込まれることがある。このようにして、累積輝度値251について最も新しく格納された値が、補償値245を計算する際に用いられ得る。

図3は、デバーンコントローラ240の内部の詳細の一実施形態である。デバーンコントローラ240は、画像データ225内の原階調値226と輝度設定222とを入力として受け取り、又は、取得するように構成されてもよい。デバーンコントローラ240は、更に、デバーンRAM250から累積輝度値251を読み出し、累積輝度値251と原階調値226とに基づいて補償値245を生成するように構成されてもよい。デバーンコントローラ240は、更に、原階調値226と輝度設定222とに基づいてデバーンRAM250内の累積輝度値251を更新するように構成されてもよい。図示された実施形態では、デバーンコントローラ240は、階調調節ブロック320と補償ブロック350とデータキャプチャブロック370とを備えている。加えて、デバーンコントローラ240は、領域情報330を入力として受け取り又は取得してもよい。領域情報330は、個々の原階調値226が表示パネル270の第2領域272に位置する画素に対応していることを示すことがあり、第2領域272は、第1領域271と異なる長期の焼き付きプロファイルを発現する。

階調調節ブロック320は、入力された原階調値226と輝度設定222とを用いて各画素について調節後階調値340を算出するように構成されることがある。調節後階調値340は、原階調値226を輝度設定222に基づいて決定された調節係数で乗算することによって計算されてもよく、原階調値226と輝度設定222とを用いる他の数値演算を用いて算出されてもよい。調節後階調値340の算出は、図3に図示されない一定のパラメータを含んでいてもよい。調節後階調値340の算出は、原階調値226と輝度設定222との少なくとも一方に基づいたルックアップテーブルを介していてもよい。

輝度設定222がDBVを含む実施形態では、DBVが調節後階調値340を算出するために使用されてもよい。図4Aは、このような実施形態による、階調調節ブロック320の例示的な構成を図示している。図示された実施形態では、階調調節ブロック320が、DBVルックアップテーブル(LUT)322と乗算器324とを備えている。DBV LUT322は、DBVを入力として受け取り又は取得して、DBVに基づくテーブルルックアップにより、DBVに対応する調節係数326を決定するように構成されている。乗算器324は、原階調値226を調節係数326で乗算することにより調節後階調値340を算出するように構成されている。

図4Bは、一以上の実施形態による、対応する調節係数326を介して関係付けられた原階調値226と調節後階調値340との間の例示的な関係を図示している。調節係数326は、輝度設定222によって指定されたDBVについて原階調値226によって生じる画素輝度が、最大DBVについて調節後階調値340によって生じる画素輝度と同じであるように決定される。図示されている実施形態では、DBVがパーセンテージを尺度としており、最大DBVが100%であることに留意されたい。一実施形態では、原階調値226が255であり、かつ、DBVが50%である場合、調節後階調値340が186となるように調節係数326が0.73(≒186/255)として決定される。他の実施形態では、原階調値226が255であり、かつ、DBVが20%である場合、調節後階調値340が128となるように調節係数326が0.50(≒128/255)として決定される。

図3に戻り、データキャプチャブロック370は、調節後階調値340と領域情報330とを入力として受け取り又は取得するように構成されている。データキャプチャブロック370は、各画素に適用される調節後階調値340をキャプチャし、各画素について、デバーンRAM250に格納されている累積輝度値251を更新するように構成されている。一以上の実施形態では、データキャプチャブロック370は、調節後階調値340に基づいて、表示パネル270の生涯にわたって各画素に適用される累積輝度値251の更新値を算出し、デバーンRAM250に格納されている累積輝度値251を算出された更新値に更新するように構成されてもよい。更新された累積輝度値は、表示パネル270の各走査時にデバーンRAM250に書き込まれてもよいし、更新された値は、演算の負荷と帯域幅の要求を低減するために、所定のサブサンプルレートで書き込まれてもよい。

図5は、補償ブロック350の一実施形態を図示している。補償ブロック350は、調節後階調値340を入力として受け取り又は取得することがある。加えて、デバーンRAM250からの累積輝度値251が補償ブロック350に入力されることがある。加えて、領域情報330が補償ブロック350に入力されることがある。図示された実施形態では、補償ブロック350がロジック回路420と乗算器435と補償値生成ブロック450とを備えている。

動作では、ロジック回路420が、領域情報330を入力として受け取り、スケーリング係数430を選択するように構成されてもよい。ロジック回路420はマルチプレクサであってもよいが、これは、限定的な例として解釈されるべきではない。ロジック回路420は、他のロジックゲート、同期回路又はメモリ素子を備えていてもよい。

動作では、領域情報330が、第2領域272にある画素について累積輝度値251に対して調節がなされることを指示する第1極性に設定され得る。一以上の実施形態では、正極性により、第2領域272にある画素について劣化補正係数470をスケーリング係数430として選択することがある。スケーリング係数430は、表示パネル270の第2領域272にある画素の加速された焼き付きを補償すべきである場合がある。劣化補正係数470は、レジスタ又は記憶素子に格納され、ロジック回路420に入力されてもよい。劣化補正係数470は、表示パネル270の長期的挙動の特性評価に基づく長期劣化情報を表していることがある。劣化補正係数470の値は、表示パネル270の特性評価に基づいていてもよく、また、長期劣化の振る舞いのモデリングに基づいていてもよい。劣化補正係数470(即ち、第2領域272にある画素のスケーリング係数430)は、第1領域271と第2領域272の画素密度に基づいて決定される。一の実装では、劣化補正係数470は、第1領域271の画素密度の第2領域272の画素密度に対する比に基づいている。

領域情報330は、第1領域271にある画素についての累積輝度値251について調節が行われないことを指示する反対極性をとることがある。該反対極性により、第1領域271にある画素についてスケーリング係数430として1又は単位元の値を選択する。他の実施形態では、領域情報330の反対極性が、1よりも大きい又は小さい一定値がスケーリング係数430として選択されることをもたらすことがある。

スケーリング係数430は乗算器435に供給される。乗算器435は、各画素について累積輝度値251をスケーリング係数430で乗算して各画素について調節後累積輝度値440を生成するように構成される。第1領域271にある画素についての調節後累積輝度値440は累積輝度値251と同一である一方、第2領域272にある画素についての調節後累積輝度値440は、累積輝度値251を(スケーリング係数430として選択される)劣化補正係数470でスケーリングすることで得られるスケーリング後累積輝度値である。

補償値生成ブロック450は、各画素について調節後階調値340と調節後累積輝度値440とを入力として受け取り又は取得するように構成されている。補償値生成ブロック450は、更に、各画素について、調節後階調値340と調節後累積輝度値440とに少なくとも部分的に基づいて補償値245を出力するように構成されている。補償値生成ブロック450は、図1Fに図示されているような補償値と累積輝度値の間の関係に基づいて補償値245を出力するように構成されてもよい。スケーリング係数430が1又は単位元である第1領域271の各画素については、補償値生成ブロック450は、累積輝度値251を入力として受け取り、累積輝度値251に対応する補償値245を出力する。第2領域272の各画素については、ロジック回路420と乗算器435の機能により、補償値生成ブロック450は、劣化補正係数470を用いて累積輝度値251をスケーリングすることで得られたスケーリング後累積輝度値を入力として受け取り、スケーリング後累積輝度値に対応する補償値245を出力する。一の実装では、補償値生成ブロック450は、補償値生成ブロック450の入出力特性を記述したLUT452を備えている。該入出力特性は、(例えば、図1Fに図示されているような)調節後累積輝度値440と補償値245との間の関係を表していることがある。補償値生成ブロック450は、調節後累積輝度値440をインデックスとして用いたLUT452のテーブルルックアップにより補償値245を生成するように構成されてもよい。

図6は、一以上の実施形態による、例示的な方法600を表現するフローチャートを図示している。フローチャートの様々なステップが順に提示され、説明されるが、当業者は、ステップの一部又は全部が異なる順序で実行されることがあり、組み合わされ又は省略されることがあり、ステップの一部又は全部が並行して実行されることがあると理解するであろう。追加のステップが更に実行されてもよい。したがって、開示の範囲は、図6に図示されている特定のステップの配列に限定されると考えるべきではない。

一以上の実施形態において、方法600は、第1領域(例えば、図1A~1C、1E及び図2の第1領域105及び271)と第2領域(例えば、図1A、1B、1D、1E及び図2の第2領域106及び272)とを備える表示パネル(例えば、図1A~図1E及び図2に図示されている表示パネル102)を駆動するための方法である。第1領域は第1画素レイアウトを有しており、第2領域は第1画素レイアウトと異なる第2画素レイアウトを有している。第1領域と第2領域とは、異なる画素密度を有していてもよい。いくつかの実施形態では、第2領域の画素密度が第1領域の画素密度よりも低くてもよく、第2領域が背後にカメラが設けられるアンダーディスプレイカメラ(UDC)領域として使用されてもよい。第2領域の画素密度が低いことにより、第2領域を通じた画像のキャプチャが容易になることがある。

方法600は、ステップ602において、表示パネルの第1領域にある第1画素の第1累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って第1画素の第1補償後輝度値を決定することを含む。第1画素の第1累積輝度値は、該第1画素の輝度値の累積であってもよい。第1画素の輝度値は、該第1画素を更新するために第1画素について指定された対応する階調値に基づいて、それぞれに算出されてもよい。一実施形態では、第1画素についてのバーンイン補償は、図1Fに図示されている補償値と累積輝度値との間の関係に基づいて、第1累積輝度値に対応する第1補償値を決定することと、第1補償値を用いて第1画素についての第1補償後輝度値を決定することとを含んでいる。

方法600は、更に、ステップ604において、表示パネルの第2領域にある第2画素の第2累積輝度値をスケーリングしてスケーリング後累積輝度値を決定することを含む。第2画素の第2累積輝度値は、該第2画素の輝度値の累積であってもよい。第2画素の輝度値は、該第2画素を更新するために第2画素について指定された対応する階調値に基づいて、それぞれに算出されてもよい。第2累積輝度値のスケーリングは、第1領域と第2領域の画素密度に基づいていてもよい。一以上の実施形態では、第1領域が第1画素密度を有しており、第2領域が第2画素密度を有している。このような実施形態では、第2累積輝度値が第1画素密度の第2画素密度に対する比に基づいて決定されたスケーリング係数でスケーリングされてもよい。

方法600は、更に、ステップ606において、スケーリング後累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って第2画素の第2補償後輝度値を決定することを含む。一実施形態では、第2画素についてのバーンイン補償は、図1Fに図示されている補償値と累積輝度値との間の関係に基づいて、スケーリング後累積輝度値に対応する第2補償値を決定することと、第2補償値を用いて第2画素についての第2補償後輝度値を決定することとを含んでいる。

方法600は、更に、ステップ608において第1補償後輝度値に少なくとも部分的に基づいて第1画素を更新することと、ステップ610において第2補償後輝度値に少なくとも部分的に基づいて第2画素を更新することとを含む。

多くの実施形態を説明したが、本開示に利益がある当業者は、範囲を外れない他の実施形態を考案可能であると評価するであろう。従って、本発明の技術的範囲は、添付のクレームのみによってのみ限定されるべきである。

Claims (20)

- 表示パネルの第1画素レイアウトを有する第1領域にある第1画素の第1累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って前記第1画素の第1補償後輝度値を決定し、

前記表示パネルの、前記第1画素レイアウトと異なる第2画素レイアウトを有する第2領域にある第2画素の第2累積輝度値をスケーリングしてスケーリング後累積輝度値を決定し、

前記スケーリング後累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って前記第2画素の第2補償後輝度値を決定するように構成された画像処理回路部と、

前記第1補償後輝度値に少なくとも部分的に基づいて前記第1画素を更新し、前記第2補償後輝度値に少なくとも部分的に基づいて前記第2画素を更新するように構成されたソースドライバと、

を備える表示ドライバ。 - 前記第2累積輝度値のスケーリングが前記第1領域及び前記第2領域の画素密度に基づいている

請求項1に記載の表示ドライバ。 - 前記第1領域が第1画素密度を有しており、

前記第2領域が第2画素密度を有しており、

前記第2累積輝度値をスケーリングすることが、前記第1画素密度の前記第2画素密度に対する比に基づいて決定されたスケーリング係数で前記第2累積輝度値をスケーリングすることを含む

請求項1に記載の表示ドライバ。 - 前記第2領域がアンダーディスプレイカメラ(UDC)領域を備えており、

前記UDC領域の背後に前記UDC領域を介して画像をキャプチャするようにカメラが設けられている

請求項1に記載の表示ドライバ。 - 前記画像処理回路部が、前記第1累積輝度値を入力として取得して前記第1累積輝度値に対応する第1補償値を出力し、前記スケーリング後累積輝度値を入力として取得して前記スケーリング後累積輝度値に対応する第2補償値を出力するように構成された補償値生成ブロックを備えており、

前記第1補償後輝度値を決定することが、前記第1補償値に少なくとも部分的に基づいており、

前記第2補償後輝度値を決定することが、前記第2補償値に少なくとも部分的に基づいている

請求項1に記載の表示ドライバ。 - 前記補償値生成ブロックが前記補償値生成ブロックの入出力特性を記述したルックアップテーブルを備えている

請求項5に記載の表示ドライバ。 - 前記画像処理回路部が、前記第1画素の第1階調値に少なくとも部分的に基づいて第1ガンマ補正後輝度値を出力し、前記第2画素の第2階調値に少なくとも部分的に基づいて第2ガンマ補正後輝度値を出力するように構成されたガンマ補正ブロックを備えており、

前記第1画素の前記第1補償後輝度値を決定することが、前記第1累積輝度値に少なくとも部分的に基づいて前記第1ガンマ補正後輝度値に対してバーンイン補償を行うことを含み、

前記第2画素の前記第2補償後輝度値を決定することが、前記第2累積輝度値に少なくとも部分的に基づいて前記第2ガンマ補正後輝度値に対してバーンイン補償を行うことを含む、

請求項1に記載の表示ドライバ。 - 前記画像処理回路部が、更に、

前記第1画素の第1階調値に少なくとも部分的に基づいて前記第1累積輝度値を更新し、

前記第2画素の第2階調値に少なくとも部分的に基づいて前記第2累積輝度値を更新するように構成された

請求項1に記載の表示ドライバ。 - 第1画素レイアウトを有する第1領域と、前記第1画素レイアウトと異なる第2画素レイアウトを有する第2領域とを備える表示パネルと、

前記表示パネルの前記第1領域にある第1画素の第1累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って前記第1画素の第1補償後輝度値を決定し、

前記表示パネルの前記第2領域にある第2画素の第2累積輝度値をスケーリングしてスケーリング後累積輝度値を決定し、

前記スケーリング後累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って前記第2画素の第2補償後輝度値を決定し、

第1補償後輝度値に少なくとも部分的に基づいて第1画素を更新し、

第2補償後輝度値に少なくとも部分的に基づいて第2画素を更新するように構成された表示ドライバと、

を備える表示装置。 - 前記第2累積輝度値のスケーリングが前記第1領域及び前記第2領域の画素密度に基づいている

請求項9に記載の表示装置。 - 前記第1領域が第1画素密度を有しており、

前記第2領域が第2画素密度を有しており、

前記第2累積輝度値をスケーリングすることが、前記第1画素密度の前記第2画素密度に対する比に基づいて決定されたスケーリング係数で前記第2累積輝度値をスケーリングすることを含む

請求項9に記載の表示装置。 - 前記第2領域がアンダーディスプレイカメラ(UDC)領域を備えており、

前記UDC領域の背後に前記UDC領域を介して画像をキャプチャするようにカメラが設けられている

請求項9に記載の表示装置。 - 前記表示ドライバが、前記第1累積輝度値を入力として取得して前記第1累積輝度値に対応する第1補償値を出力し、前記スケーリング後累積輝度値を入力として取得して前記スケーリング後累積輝度値に対応する第2補償値を出力するように構成された補償値生成ブロックを備えており、

前記第1補償後輝度値を決定することが、前記第1補償値に少なくとも部分的に基づいており、

前記第2補償後輝度値を決定することが、前記第2補償値に少なくとも部分的に基づいている

請求項9に記載の表示装置。 - 前記補償値生成ブロックが前記補償値生成ブロックの入出力特性を記述したルックアップテーブルを備えている

請求項13に記載の表示装置。 - 前記表示ドライバが、前記第1画素の第1階調値に少なくとも部分的に基づいて第1ガンマ補正後輝度値を出力し、前記第2画素の第2階調値に少なくとも部分的に基づいて第2ガンマ補正後輝度値を出力するように構成され、

前記第1画素の前記第1補償後輝度値を決定することが、前記第1累積輝度値に少なくとも部分的に基づいて前記第1ガンマ補正後輝度値に対してバーンイン補償を行うことを含み、

前記第2画素の前記第2補償後輝度値を決定することが、前記第2累積輝度値に少なくとも部分的に基づいて前記第2ガンマ補正後輝度値に対してバーンイン補償を行うことを含む、

請求項9に記載の表示装置。 - 前記表示ドライバが、更に、

前記第1画素の第1階調値に少なくとも部分的に基づいて前記第1累積輝度値を更新し、

前記第2画素の第2階調値に少なくとも部分的に基づいて前記第2累積輝度値を更新するように構成された

請求項9に記載の表示装置。 - 表示パネルの第1画素レイアウトを有する第1領域にある第1画素の第1累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って前記第1画素の第1補償後輝度値を決定することと、

前記表示パネルの、前記第1画素レイアウトと異なる第2画素レイアウトを有する第2領域にある第2画素の第2累積輝度値をスケーリングしてスケーリング後累積輝度値を決定することと、

前記スケーリング後累積輝度値に少なくとも部分的に基づいてバーンイン補償を行って前記第2画素の第2補償後輝度値を決定することと、

前記第1補償後輝度値に少なくとも部分的に基づいて前記第1画素を更新することと、

前記第2補償後輝度値に少なくとも部分的に基づいて前記第2画素を更新することと、

を含む

方法。 - 前記第2累積輝度値のスケーリングが前記第1領域及び前記第2領域の画素密度に基づいている

請求項17に記載の方法。 - 前記第1領域が第1画素密度を有しており、

前記第2領域が第2画素密度を有しており、

前記第2累積輝度値をスケーリングすることが、前記第1画素密度の前記第2画素密度に対する比に基づいて決定されたスケーリング係数で前記第2累積輝度値をスケーリングすることを含む

請求項17に記載の方法。 - 更に、

補償値生成ブロックによって前記第1累積輝度値を入力として取得して前記第1累積輝度値に対応する第1補償値を出力することと、

前記補償値生成ブロックによって前記スケーリング後累積輝度値を入力として取得して前記スケーリング後累積輝度値に対応する第2補償値を出力することと、

を含み、

前記第1補償後輝度値を決定することが、前記第1補償値に少なくとも部分的に基づいており、

前記第2補償後輝度値を決定することが、前記第2補償値に少なくとも部分的に基づいている

請求項17に記載の方法。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US202163248394P | 2021-09-24 | 2021-09-24 | |

| US63/248,394 | 2021-09-24 | ||

| US17/876,780 US12020666B2 (en) | 2021-09-24 | 2022-07-29 | System and method for variable area-based compensation of burn-in in display panels |

| US17/876,780 | 2022-07-29 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2023047330A true JP2023047330A (ja) | 2023-04-05 |

Family

ID=85661108

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2022149724A Pending JP2023047330A (ja) | 2021-09-24 | 2022-09-21 | 表示パネルにおける焼き付きの領域ベースでの可変補償のためのシステム及び方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US12020666B2 (ja) |

| JP (1) | JP2023047330A (ja) |

| KR (1) | KR20230043752A (ja) |

| CN (1) | CN115862508A (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US12020666B2 (en) * | 2021-09-24 | 2024-06-25 | Synaptics Incorporated | System and method for variable area-based compensation of burn-in in display panels |

| KR20230102214A (ko) * | 2021-12-30 | 2023-07-07 | 엘지디스플레이 주식회사 | 입력영상데이터 보정 방법 및 이를 이용한 발광표시장치 |

| US20250006102A1 (en) * | 2023-06-28 | 2025-01-02 | Intel Corporation | Brightness compensation for camera under display subpixels |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102139698B1 (ko) * | 2013-11-14 | 2020-07-31 | 삼성디스플레이 주식회사 | 표시 패널의 영상 보정 방법 |

| CN109872670B (zh) * | 2017-12-05 | 2021-11-05 | 京东方科技集团股份有限公司 | 显示屏、显示装置、显示电路及其亮度补偿方法 |

| KR20210134150A (ko) * | 2020-04-29 | 2021-11-09 | 삼성디스플레이 주식회사 | 표시 장치 및 이의 감마 보정 방법 |

| US11620933B2 (en) * | 2020-10-13 | 2023-04-04 | Synaptics Incorporated | IR-drop compensation for a display panel including areas of different pixel layouts |

| US12020666B2 (en) * | 2021-09-24 | 2024-06-25 | Synaptics Incorporated | System and method for variable area-based compensation of burn-in in display panels |

-

2022

- 2022-07-29 US US17/876,780 patent/US12020666B2/en active Active

- 2022-09-21 JP JP2022149724A patent/JP2023047330A/ja active Pending

- 2022-09-22 KR KR1020220120175A patent/KR20230043752A/ko unknown

- 2022-09-23 CN CN202211164042.XA patent/CN115862508A/zh active Pending

-

2024

- 2024-05-23 US US18/672,326 patent/US20240312436A1/en active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| CN115862508A (zh) | 2023-03-28 |

| KR20230043752A (ko) | 2023-03-31 |

| US12020666B2 (en) | 2024-06-25 |

| US20240312436A1 (en) | 2024-09-19 |

| US20230102440A1 (en) | 2023-03-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10283071B2 (en) | Driving apparatus and method | |

| US10699662B2 (en) | Integrated circuit for driving display panel and method thereof | |

| CN112767867B (zh) | 显示面板及其亮度补偿方法、装置 | |

| KR100887304B1 (ko) | 디스플레이장치 및 디스플레이패널드라이버 | |

| JP2023047330A (ja) | 表示パネルにおける焼き付きの領域ベースでの可変補償のためのシステム及び方法 | |

| KR101443371B1 (ko) | 액정표시장치 및 그의 구동방법 | |

| JP4073949B2 (ja) | 表示装置 | |

| JP6309777B2 (ja) | 表示装置、表示パネルドライバ、及び、表示パネルの駆動方法 | |

| JP5666163B2 (ja) | 光源駆動方法 | |

| JP2009139470A (ja) | 画像表示装置および画像表示方法 | |

| KR101073006B1 (ko) | 표시장치 및 표시장치의 이미지 밝기조절방법 | |

| KR100753318B1 (ko) | 표시 장치 | |

| KR102510573B1 (ko) | 투명 표시 장치 및 그 구동 방법 | |

| JP6347957B2 (ja) | 表示装置、表示パネルドライバ、及び、表示パネルの駆動方法 | |

| KR20120076059A (ko) | 액정 표시 장치 및 그 구동 방법 | |

| KR102566785B1 (ko) | 표시 장치 및 이의 구동 방법 | |

| US10419708B2 (en) | Image processing circuit and image contrast enhancement method thereof | |

| KR102746914B1 (ko) | 전자 장치, 디스플레이 장치 및 그 제어 방법 | |

| WO2018154728A1 (ja) | 表示装置 | |

| KR20160031597A (ko) | 표시 장치의 검사 방법 및 이에 의해 검사되는 표시 장치 | |

| US20150332642A1 (en) | Display device | |

| KR20080073821A (ko) | 액정 표시 장치 및 이의 구동 방법 | |

| KR102666134B1 (ko) | 표시 장치 | |

| KR20170036936A (ko) | 표시 장치 및 이의 구동 방법 | |

| KR102771110B1 (ko) | 광학 보상 장치 및 이를 포함하는 광학 보상 시스템 |