以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる形態で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。また、以下に示される複数の実施の形態は、適宜組み合わせることが可能である。

なお、実施の形態において説明するゲームシステムは、携帯型情報端末と、据置型表示装置と、情報処理装置等によって構成される。本明細書等において、本発明の一形態である携帯型情報端末、据置型表示装置および情報処理装置は、信号処理部、カメラ部、表示部等によって構成された半導体装置である。したがって、携帯型情報端末、据置型表示装置および情報処理装置を半導体装置、電子機器などと言い換える場合がある。

また、図面等において、大きさ、層の厚さ、領域等は、明瞭化のため誇張されている場合がある。よって、必ずしもそのスケールに限定されない。図面は、理想的な例を模式的に示したものであり、図面に示す形状または値などに限定されない。

また、図面等において、同一の要素または同様な機能を有する要素、同一の材質の要素、あるいは同時に形成される要素等には同一の符号を付す場合があり、その繰り返しの説明は省略する場合がある。

また、本明細書等において、「膜」という用語と、「層」という用語とは、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

また、本明細書等において、「上」や「下」などの配置を示す用語は、構成要素の位置関係が、「直上」または「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極」の表現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除外しない。

また、本明細書等において、「平行」とは、二つの直線が−10°以上10°以下の角度で配置されている状態をいう。したがって、−5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。

また、本明細書等において、「第1」、「第2」、「第3」などの序数詞は、構成要素の混同を避けるために付したものであり、数的に限定するものではない。

また、本明細書等において、「電気的に接続」とは、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、容量素子、その他の各種機能を有する素子などが含まれる。

また、本明細書等において、「電圧」とは、ある電位と基準の電位(例えば、グラウンド電位)との電位差のことを示す場合が多い。よって、電圧と電位差とは言い換えることができる。

また、本明細書等において、トランジスタとは、ゲートと、ドレインと、ソースとを含む、少なくとも三つの端子を有する素子である。そして、ドレイン(ドレイン端子、ドレイン領域、またはドレイン電極)とソース(ソース端子、ソース領域、またはソース電極)の間にチャネル領域を有しており、チャネル領域を介して、ソースとドレインとの間に電流を流すことができるものである。なお、本明細書等において、チャネル領域とは、電流が主として流れる領域をいう。

また、ソースやドレインの機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、ソースやドレインの用語は、入れ替えて用いることができるものとする。

また、本明細書等において、特に断りがない場合、オフ電流とは、トランジスタがオフ状態(非導通状態、遮断状態、ともいう)にあるときのドレイン電流をいう。オフ状態とは、特に断りがない場合、nチャネル型トランジスタでは、ゲートとソースの間の電圧Vgsがしきい値電圧Vthよりも低い状態、pチャネル型トランジスタでは、ゲートとソースの間の電圧Vgsがしきい値電圧Vthよりも高い状態をいう。つまり、nチャネル型のトランジスタのオフ電流とは、ゲートとソースの間の電圧Vgsがしきい値電圧Vthよりも低いときのドレイン電流、という場合がある。

上記オフ電流の説明において、ドレインをソースと読み替えてもよい。つまり、オフ電流は、トランジスタがオフ状態にあるときのソース電流をいう場合がある。

また、本明細書等では、オフ電流と同じ意味で、リーク電流と記載する場合がある。また、本明細書等において、オフ電流とは、トランジスタがオフ状態にあるときに、ソースとドレインの間に流れる電流を指す場合がある。

また、本明細書等において、金属酸化物(metal oxide)とは、広い表現での金属の酸化物である。金属酸化物は、酸化物絶縁体、酸化物導電体(透明酸化物導電体を含む)、酸化物半導体(Oxide Semiconductorまたは単にOSともいう)などに分類される。例えば、トランジスタの活性層に金属酸化物を用いた場合、当該金属酸化物を酸化物半導体と呼称する場合がある。つまり、金属酸化物が増幅作用、整流作用、及びスイッチング作用の少なくとも1つを有する場合、当該金属酸化物を、金属酸化物半導体(metal oxide semiconductor)、略してOSと呼ぶことができる。また、OSトランジスタ、またはOS FETと記載する場合においては、金属酸化物または酸化物半導体を有するトランジスタと換言することができる。

(実施の形態1)

本実施の形態では、携帯型情報端末と、据置型表示装置と、情報処理装置とを有するゲームシステムについて説明する。

<ゲームシステム>

図1は、ゲームシステムの構成例を説明する外観図である。

ゲームシステムは、携帯型情報端末10A乃至10C、据置型表示装置30、情報処理装置50を有する。図1では、ゲームのプレイヤとして、携帯型情報端末10A乃至10Cを操作するユーザー13A乃至13Cを図示している。図1では、ユーザーが3人の場合を示しているが、1人や2人であってもよいし、3人より多人数であってもよい。

携帯型情報端末10A乃至10Cは、それぞれ、表示部11A乃至11C、カメラ部12A乃至12Cを有する。また、据置型表示装置30は、表示部31、カメラ部32を有する。

携帯型情報端末10A乃至10Cと、情報処理装置50とは、無線通信により接続されている。無線通信には、例えば、通信プロトコル又は通信技術として、LTE(Long Term Evolution)、GSM(Global System for Mobile Communication:登録商標)、EDGE(Enhanced Data Rates for GSM Evolution)、CDMA2000(Code Division Multiple Access 2000)、W−CDMA(Wideband Code Division Multiple Access)などの通信規格、またはWi−Fi(Wireless Fidelity:登録商標)、Bluetooth(登録商標)、ZigBee(登録商標)等のIEEEにより規格化された仕様、またはIrDA(Infrared Data Association)等の光無線通信を用いることができる。

情報処理装置50と、据置型表示装置30とは、有線通信により接続されている。情報処理装置50は、据置型表示装置30で表示を行うための画像データを生成し、据置型表示装置30へ出力する機能を有する。

図2は、ゲームシステムの構成例を説明するブロック図である。

<携帯型情報端末>

携帯型情報端末10A乃至10Cは、それぞれ、カメラ部12A乃至12Cに加えて、表示装置14A乃至14C、信号処理部15A乃至15C、通信部16A乃至16C、タッチセンサ17A乃至17C、操作部18A乃至18C、バッテリ19A乃至19C、アンテナ20A乃至20Cを有する。

表示装置14A乃至14Cは、それぞれ、タッチセンサ17A乃至17Cと重畳する領域を有し、表示部11A乃至11Cを形成する。表示装置14A乃至14Cは、表示部11A乃至11Cに画像を表示する機能を有する。また、表示装置14A乃至14Cは、それぞれ、ディスプレイコントローラ等制御部を有し、信号処理部15A乃至15Cと、画像データや制御信号等について通信を行っている。

表示装置14A乃至14Cを構成する表示素子には、例えば、液晶素子、電子ペーパー、有機EL(Electro Luminescent)素子、無機EL素子、QLED(Quantum−dot Light Emitting Diode)、LED(Light Emitting Diode)等を適用することができる。

タッチセンサ17A乃至17Cは、タッチを検出できる領域を形成し、ユーザー13A乃至13Cは、この領域に指やスタイラス等を用いて入力を行うことができる。タッチセンサ17A乃至17Cとして、投影型静電容量方式(相互容量方式)、表面型静電容量方式、抵抗膜方式、超音波表面弾性波方式、光学方式、電磁誘導方式など、任意の検出方式を利用することができる。

タッチセンサ17A乃至17Cは、それぞれ、タッチセンサコントローラ等制御部を有し、信号処理部15A乃至15Cと、タッチの有無、タッチ位置の情報等について通信を行っている。信号処理部15A乃至15Cは、ユーザー13A乃至13Cがどの位置をタッチしたかを情報として得ることができる。なお、タッチセンサ17A乃至17Cの構成例については、実施の形態2にて説明する。

カメラ部12A乃至12Cは、それぞれ、表示装置14A乃至14Cの表示方向を撮影する機能を有する。カメラ部12A乃至12Cを用いて、携帯型情報端末10A乃至10Cのユーザー13A乃至13Cを撮影することができる。

操作部18A乃至18Cは、ハードウェアボタン、ポインティングデバイス、キーボード、マウス、キーパッド等の入力装置である。また、操作部18A乃至18Cに、音声入力装置、視線入力装置などを用いてもよい。

通信部16A乃至16Cは、アンテナ20A乃至20Cを介して、他の電子機器または通信網と無線接続し、情報を送受信する機能を備える。アンテナ20A乃至20Cは、図1では携帯型情報端末10A乃至10C内に内蔵されている。また、場合によっては、アンテナ20A乃至20Cを使用せず、有線通信を行ってもよい。

携帯型情報端末10A乃至10Cは、バッテリ19A乃至19Cを有する。図2では、主な情報の流れを矢印で図示しているが、各機能ブロックに電力を供給する流れは省略している。また、バッテリ19A乃至19Cは、バッテリコントローラ等を有し、信号処理部15A乃至15Cと、バッテリ19A乃至19Cの充電状態、充放電回数、温度等について通信を行っている。

信号処理部15A乃至15Cには、CPU(Central Processing Unit)やメモリ等を適用することができる。信号処理部15A乃至15Cは、ユーザー13A乃至13Cによる、操作部18A乃至18Cやタッチセンサ17A乃至17Cの操作データを取得し、ゲームのプログラムに応じた画像データを生成する機能、および表示装置14A乃至14Cの制御信号を生成する機能を有する。画像データは、表示装置14A乃至14Cに送られ、表示部11A乃至11Cに表示される。

信号処理部15Aは、通信部16Aおよびアンテナ20Aを介して、ユーザー13Aによる操作データやユーザー13Aのパラメータ等を、情報処理装置50、携帯型情報端末10Bおよび携帯型情報端末10Cに送信する。また、信号処理部15Aは、通信部16Aおよびアンテナ20Aを介して、ユーザー13Bおよび13Cによる操作データ、ユーザー13Bおよび13Cのパラメータ等、および、情報処理装置50が有するゲームのプログラムやデータ等を受信する。信号処理部15Bおよび15Cについても同様である。また、ユーザー13A乃至13Cのパラメータには、ゲーム内での位置情報、ステータス情報、装備品情報、および行動の経緯情報等がある。

また、信号処理部15A乃至15Cは、カメラ部12A乃至12Cを用いて撮影した画像データを解析する機能を有する。信号処理部15A乃至15Cは、撮影した画像データから、ユーザー13A乃至13Cが表示部11A乃至11Cを注視しているか否かを判断する機能を有する。ユーザー13A乃至13Cが表示部11A乃至11Cを注視しているか否かに応じて、表示装置14A乃至14Cの制御信号を変更することができる。

例えば、信号処理部15A乃至15Cは、撮影した画像データからユーザー13A乃至13Cの頭に対する眼の位置を認知し、顔の向きを推測する。さらに、眼の中の黒眼の位置を認知し、視線の方向を推測する。また、視線の方向が通過した程度の一時的なものなのか、しばらくとどまって注視しているものなのかを推測し、ユーザー13A乃至13Cの注視方向を判断する。

信号処理部15A乃至15Cには、CPUに加えて、DSP(Digital Signal Processor)やGPU(Graphics Processing Unit)等、他のマイクロプロセッサを併用してもよい。さらに、画像データを生成または解析するために、GPUやFPGA(Field Programmable Gate Array)等を利用することができる。

また、カメラ部12A乃至12Cを用いて撮影した画像データから、ユーザー13A乃至13Cが表示部11A乃至11Cを注視するか否かを予測するために、人工知能(Artificial Intelligence:AI)を利用することができる。

例えば、ゲームの内容に応じて異なるが、ある特定の動作やイベントがあるとき、もしくはあったときに、ユーザー13A乃至13Cが表示部11A乃至11Cを注視すると予測することができる。例えば、個人プレイ型のゲームの場合、難易度が高くタイミングが重要な局面では表示部11A乃至11Cが注視されると予測でき、その後、ゲームを最初にクリアしたユーザーは据置型表示装置30の表示部31を注視し、他のユーザーの状況を確認すると予測できる。

ユーザー13A乃至13Cの注視方向を判断し、さらに予測することで、ユーザーに画質の低下を認識させることなく、携帯型情報端末10A乃至10Cや据置型表示装置30を、低消費電力化することができる。低消費電力化の方法については、後述する。

人工知能とは、人工ニューラルネットワーク(Artificial Neural Network:ANN。以下、ニューラルネットワークと略記する)等を利用した、人間の知能を模した計算機のことである。ニューラルネットワークは、ニューロンとシナプスで構成する神経網を模した回路構成のことであり、人工知能は、ニューラルネットワークを利用することで学習に応じた演算を行うことができる。なお、ニューラルネットワークの構成例については、実施の形態4にて説明する。

また、信号処理部15A乃至15Cに適用できるメモリには、DRAM(Dynamic Random Access Memory)やSRAM(Static RAM)などの揮発性の記憶素子を用いた記憶装置、フラッシュメモリ、MRAM(Magnetoresistive RAM)、PRAM(Phase change RAM)、ReRAM(Resistance RAM)、FeRAM(Ferroelectric RAM)などの不揮発性の記憶素子を用いた記憶装置、または、ハードディスクドライブ(Hard Disc Drive:HDD)やソリッドステートドライブ(Solid State Drive:SSD)などの記憶装置等がある。

<情報処理装置>

情報処理装置50は、信号処理部55、通信部56、操作部58、アンテナ60、映像出力部61、情報入出力部63を有する。

通信部56、操作部58、アンテナ60は、携帯型情報端末10A乃至10Cが有する、通信部16A乃至16C、操作部18A乃至18C、アンテナ20A乃至20Cと同様のため、説明を援用する。

映像出力部61は、据置型表示装置30で表示を行うための画像データを出力する機能を有する。図1では、情報処理装置50と据置型表示装置30とは、映像出力部61を介して有線通信により接続されている例を示したが、無線通信によって接続してもよい。

情報入出力部63には、CD−ROM、DVD(Digital Versatile Disk)、ブルーレイディスク、フラッシュメモリ、または、外部インターフェースを介してコネクタにより脱着可能なハードディスクドライブやソリッドステートドライブ等の記憶装置を適用することができる。

信号処理部55には、信号処理部15A乃至15Cと同様、CPUやメモリ等を適用することができる。信号処理部55は、信号処理部55が有する不揮発性の記憶素子を用いた記憶装置、ハードディスクドライブ、ソリッドステートドライブ、または情報入出力部63等から、ゲームのプログラムを読み込み、実行する機能、および、据置型表示装置30で表示を行うための画像データを生成する機能を有する。

信号処理部55は、通信部56およびアンテナ60を介して、ユーザー13A乃至13Cによる操作データやユーザー13A乃至13Cのパラメータ等を受信し、随時、ゲームのプログラムに反映する。そして、ゲームのプログラムに反映した結果は、必要に応じて、携帯型情報端末10A乃至10Cに送信される。

また、信号処理部55は、ゲームの内容に応じて、表示部11A乃至11Cおよび表示部31に表示する表示内容を調整する機能を有する。例えば、個人プレイ型のゲームの場合、表示部11A乃至11Cにはユーザー13A乃至13Cそれぞれの画像を表示し、表示部31にはユーザー13A乃至13C全員分の画像を表示することができる。

例えば、ユーザー13A乃至13Cが協力して問題を解決するゲームの場合、表示部11A乃至11Cにはユーザー13A乃至13Cそれぞれの視点からの画像を表示し、表示部31にはユーザー13A乃至13C全員分の位置情報、ステータス情報、および装備品情報を表示して、お互いの状況を確認することができる。

逆に、ユーザー13A乃至13Cがお互いライバルとなるゲームの場合、表示部11A乃至11Cにはユーザー13A乃至13Cそれぞれの視点からの画像を表示するが、ユーザー13Aが仕掛けた罠については表示部11Aのみに表示し、表示部11B、11C、および31には表示しないといったことができる。

<据置型表示装置>

据置型表示装置30は、カメラ部32に加えて、表示装置34、信号処理部35、映像入力部42を有する。

表示装置34は表示部31を形成し、表示装置34は表示部31に画像を表示する機能を有する。また、表示装置34は、ディスプレイコントローラ等制御部を有し、信号処理部35と画像データや制御信号等について通信を行っている。表示装置34を構成する表示素子には、表示装置14A乃至14Cと同様、例えば、液晶素子、電子ペーパー、有機EL素子、無機EL素子、QLED、LED等を適用することができる。

カメラ部32は、表示装置34の表示方向を撮影する機能を有する。カメラ部32を用いて、表示部31を見ることができるユーザーを撮影することができる。

映像入力部42には、表示装置34が表示を行う画像データが入力される。映像入力部42に入力された画像データは、信号処理部35を経て、表示装置34に出力される。

信号処理部35には、信号処理部15A乃至15Cと同様、CPUやメモリ等を適用することができる。信号処理部35は、表示装置34の制御信号を生成する機能、カメラ部32を用いて撮影した画像データを解析する機能、および、映像入力部42に入力された画像データを解析する機能を有する。

信号処理部35は、カメラ部32を用いて撮影した画像データから、表示部31を見ることができるユーザーが表示部31を注視しているか否かを判断する機能を有する。ユーザーが表示部31を注視しているか否かに応じて、表示装置34の制御信号を変更することができる。注視方向を判断する方法の例に関しては、信号処理部15A乃至15Cと同様のため、省略する。

同様に、カメラ部32を用いて撮影した画像データから、表示部31を見ることができるユーザーが表示部31を注視するか否かを予測するために、人工知能を利用することができる。

また、信号処理部35は、映像入力部42に入力された画像データの内容から、ユーザーが注目しやすい領域(非特許文献2)が存在するかを解析する機能を有する。画像データの内容に、ユーザーが注目しやすい領域が存在するか否かに応じて、表示装置34の制御信号を変更することができる。

信号処理部35には、CPUに加えてDSPやGPU等他のマイクロプロセッサを併用してもよく、また、画像データを解析するためにGPUやFPGA等を利用することができる。さらに、カメラ部32を用いて撮影した画像データから、表示部31を見ることができるユーザーが表示部31を注視するか否かを予測するために、人工知能を利用することができる。

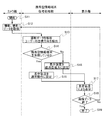

<フローチャート>

ゲームの開始から終了まで、携帯型情報端末10A乃至10Cの表示装置14A乃至14Cに関するフローチャートを、図3に示す。

ゲームが開始(ステップS11)されると、カメラ部12A乃至12Cは、それぞれ、ユーザー13A乃至13Cを撮影する(ステップS12)。なお、図3では、撮影した画像データを、「撮影データ」と表現している。

信号処理部15A乃至15Cは、それぞれ、撮影データを解析し、ユーザー13A乃至13Cの注視方向を検出する(ステップS13)。携帯型情報端末10Aについて、ユーザー13Aが、携帯型情報端末10Aの表示部11Aを注視していると判断された場合(ステップS14)、信号処理部15Aは表示装置14Aの動作モードを通常動作に設定する(ステップS16)。ユーザー13Aが、携帯型情報端末10Aの表示部11Aを注視していないと判断された場合(ステップS14)、信号処理部15Aは表示装置14Aの動作モードを低消費電力に設定する(ステップS15)。

携帯型情報端末10Bおよび10Cに対しても、同様にステップS14乃至S16が行われる。

表示装置14A乃至14Cは、それぞれ、信号処理部15A乃至15Cから送られる画像データを表示する(ステップS17)。引き続き、表示する画像データが存在する場合(ステップS18)、ステップS12に戻って、カメラ部12A乃至12Cは撮影する。表示する画像データが存在せず(ステップS18)、ゲーム終了の場合(ステップS19)、一連の動作が終了する。

次に、ゲームの開始から終了まで、据置型表示装置30の表示装置34に関するフローチャートを、図4に示す。

ゲームが開始(ステップS21)されると、カメラ部32は、表示部31を見ることができるユーザーを撮影する(ステップS22)。図4では、撮影した画像データを、「撮影データ」と表現している。

信号処理部35は、撮影データを解析し、表示部31を見ることができるユーザーの注視方向を検出する(ステップS23)。ユーザーが表示部31を注視していると判断された場合(ステップS24)、信号処理部35は、映像入力部42に入力された画像データを解析する(ステップS26)。画像データの内容に、ユーザーが注目しやすい領域が存在しないと判断された場合(ステップS27)、信号処理部35は表示装置34の動作モードを通常動作に設定する(ステップS29)。

ステップS24において、ユーザーが表示部31を注視していないと判断された場合、信号処理部35は表示装置34の動作モードを低消費電力に設定する(ステップS25)。また、ステップS27において、画像データの内容に、ユーザーが注目しやすい領域が存在すると判断された場合(ステップS27)、ユーザーが注目しやすい領域以外の領域を低消費電力に設定する(ステップS28)。

表示装置34は、信号処理部35から送られる画像データを表示する(ステップS30)。引き続き、表示する画像データが存在する場合(ステップS31)、ステップS22に戻って、カメラ部32は撮影する。表示する画像データが存在せず(ステップS31)、ゲーム終了の場合(ステップS32)、一連の動作が終了する。

なお、表示装置14A乃至14Cおよび表示装置34において、動作モードが低消費電力に設定されると、表示装置14A乃至14Cおよび表示装置34は表示輝度を暗くする、IDS駆動を行う等の方法で消費電力を低減する。また、表示装置34において、ユーザーが注目しやすい領域以外の領域を低消費電力に設定されると、表示装置34は表示部31の一部領域の表示輝度を暗くする、部分IDS駆動を行う等の方法で消費電力を低減する。

表示装置14A乃至14Cおよび表示装置34の構成例と、IDS駆動および部分IDS駆動については、実施の形態3にて説明する。

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせて実施することができる。

(実施の形態2)

本実施の形態では、上記実施の形態に記載のタッチセンサ17A乃至17Cに適用可能なタッチセンサユニット400について、図5乃至図7を用いて説明を行う。

<タッチセンサユニット>

図5は、タッチセンサユニット400の構成例を示すブロック図である。ここでは、タッチセンサユニット400が投影型静電容量方式のタッチセンサユニットである例を示す。

センサアレイ401は、配線CLおよび配線MLを有し、配線CLおよび配線MLが重畳すること、または、配線CLおよび配線MLが近接して配置されること、で形成される複数の容量404を有する。

図5は、一例として、配線CLをCL(1)乃至CL(6)の6本の配線、配線MLをML(1)乃至ML(6)の6本の配線として示しているが、配線の数はこれに限定されない。なお、配線CLはパルス電圧が与えられる配線であり、配線MLは電流の変化を検知する配線である。

センサアレイ401に、被検知体(指やスタイラス等)の近接または接触を検知すると、容量404の容量値が変化し、タッチセンサユニット400はタッチを検出する。

センサアレイ401は、配線CLおよび配線MLを介して、タッチセンサIC402に電気的に接続されている。タッチセンサIC402は、駆動回路405と検出回路406を有する。

駆動回路405は、配線CLを介して、センサアレイ401に電気的に接続される。駆動回路405は、信号Txを出力する機能を有する。駆動回路405としては、例えばシフトレジスタ回路とバッファ回路を組み合わせた構成を用いることができる。

検出回路406は、配線MLを介して、センサアレイ401に電気的に接続される。検出回路406は、信号Rxを検出し、タッチセンサユニット400でタッチが行われたことを検出する。例えば、検出回路406として、増幅回路と、アナログデジタル変換回路(Analog−Digital Converter:ADC)を有する構成を用いることができる。検出回路406は、センサアレイ401から出力されるアナログ信号を、デジタル信号に変換して、信号処理部15A乃至15Cに出力する機能を有する(図2参照)。

次に、タッチセンサユニット400のより具体的な構成例について、図6および図7を用いて説明する。

図6(A)はタッチセンサユニット400の上面図である。図6(B)および図6(C)は、図6(A)の一部を説明する投影図である。

図7(A)は、制御線および検知信号線の隣接部の上面図である。図7(B)は、隣接部に生じる電界を模式的に説明する投影図である。

タッチセンサユニット400はセンサアレイ401を有する。センサアレイ401は、配線CL(g)、配線ML(h)および導電膜を備える(図6(A)参照)。なお、gおよびhは2以上の整数である。

例えば、複数の領域に分割された導電膜をセンサアレイ401に用いることができる(図6(A)参照)。これにより、同一の電位または異なる電位を、複数の領域のそれぞれに供給することができる。

具体的には、配線CL(g)に用いることができる導電膜と、配線ML(h)に用いることができる導電膜と、に分割された導電膜をセンサアレイ401に用いることができる。また、複数の領域に分割された導電膜のそれぞれに、例えば、櫛歯状の形状を備える導電膜を用いることができる(図7、電極CE(1)、電極ME(1)および電極ME(2)参照)。これにより、分割された導電膜を検知素子の電極に用いることができる。

例えば、配線CL(1)に用いることができる導電膜と、配線ML(1)に用いることができる導電膜と、配線ML(2)に用いることができる導電膜と、に分割された導電膜は、隣接部X0において互いに隣接する(図6(A)、図6(C)、または図7参照)。

検知素子475(g,h)は、配線CL(g)および配線ML(h)と電気的に接続される(図6(A)参照)。

配線CL(g)は信号Txを供給する機能を備え、配線ML(h)は信号Rxを供給される機能を備える。

配線ML(h)は、導電膜BR(g,h)を含む(図6(B)参照)。導電膜BR(g,h)は、配線CL(g)と重なる領域を備える。

なお、検知素子475(g,h)は絶縁膜を備える。絶縁膜は、配線ML(h)および導電膜BR(g,h)の間に挟まれる領域を備える。これにより、配線ML(h)および導電膜BR(g,h)の短絡を防止することができる。

電極CE(1)は、配線CL(1)に電気的に接続され、電極ME(1)は、配線ML(1)に電気的に接続される(図7参照)。

同様に、電極CE(g)は、配線CL(g)に電気的に接続され、電極ME(h)は、配線ML(h)に電気的に接続される。

検知素子475(1、1)は、電極CE(1)と電極ME(1)の間に形成される容量値の変化を読み取ることで、タッチを検出する(図6及び図7参照)。

同様に、検知素子475(g、h)は、電極CE(g)と電極ME(h)の間に形成される容量値の変化を読み取ることで、タッチを検出する。

同一の工程で形成することができる導電膜を、配線CL(1)および電極CE(1)に用いることができる。同一の工程で形成することができる導電膜を、配線ML(1)および電極ME(1)に用いることができる(図7参照)。

同様に、同一の工程で形成することができる導電膜を、配線CL(g)および電極CE(g)に用いることができる。同一の工程で形成することができる導電膜を、配線ML(h)および電極ME(h)に用いることができる。

例えば、透光性を備える導電膜を、電極CE(g)および電極ME(h)に用いることができる。または、画素と重なる領域に開口部や櫛歯状の形状を備える導電膜を、電極CE(g)および電極ME(h)に用いることができる。これにより、表示パネルの表示を遮ることなく、表示パネルと重なる領域に近接するものを検知することができる。

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせて実施することができる。

(実施の形態3)

本実施の形態では、上記実施の形態に記載の表示装置14A乃至14Cおよび表示装置34に適用可能な、表示ユニット200について、図8乃至図21を用いて説明を行う。

<表示ユニット>

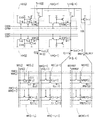

図8は、表示ユニットの構成例を示すブロック図である。表示ユニット200は、画素アレイ201、ゲートドライバ202、ゲートドライバ203、およびコントローラIC204を有する。

画素アレイ201は、複数の画素210を有し、それぞれの画素210はトランジスタを用いて駆動されるアクティブ型の素子である。また、画素アレイ201は、表示ユニット200の表示部を形成し、画像を表示する機能を有する。

ゲートドライバ202およびゲートドライバ203(以下、「ゲートドライバ202、203」と表記する)は、画素210を選択するためのゲート線を駆動する機能を有する。ゲートドライバ202、203は、どちらか一方のみでもよい。なお、図8の例では、ゲートドライバ202、203は、画素アレイ201と共に同一基板上に設けられている例を示しているが、ゲートドライバ202、203を専用ICとすることもできる。

コントローラIC204は、画素210にデータ信号を供給するためのソース線を駆動する、ソースドライバの機能を有する。ここでは、コントローラIC204の実装方式は、COG(Chip on Glass)方式としているが、実装方式に特段の制約はなく、COF(Chip on Flexible)方式、TAB(Tape Automated Bonding)方式などでもよい。

なお、画素210に使用されるトランジスタはOSトランジスタであり、Siトランジスタに比べてオフ電流が低いトランジスタである。

OSトランジスタは、チャネル形成領域に金属酸化物を有することが好ましい。また、OSトランジスタに適用される金属酸化物は、インジウム(In)および亜鉛(Zn)の少なくとも一方を含む酸化物であることが好ましい。

このような酸化物としては、In−M−Zn酸化物、In−M酸化物、Zn−M酸化物、In−Zn酸化物(元素Mは、例えば、アルミニウム(Al)、ガリウム(Ga)、イットリウム(Y)、スズ(Sn)、ホウ素(B)、シリコン(Si)、チタン(Ti)、鉄(Fe)、ニッケル(Ni)、ゲルマニウム(Ge)、ジルコニウム(Zr)、モリブデン(Mo)、ランタン(La)、セリウム(Ce)、ネオジム(Nd)、バナジウム(V)、ベリリウム(Be)、ハフニウム(Hf)、タンタル(Ta)またはタングステン(W)など)が代表的である。

OSトランジスタは、チャネル幅1μmあたりのオフ電流を1yA/μm(y;ヨクト、10−24)以上1zA/μm(z;ゼプト、10−21)以下程度に低くすることができる。

また、OSトランジスタには、CAC(Cloud−Aligned Composite)−OSを用いることが好ましい。CAC−OSの詳細については、実施の形態5で説明する。

もしくは、画素210に使用されるトランジスタとして、オフ電流が低ければOSトランジスタを適用しないことができる。例えば、バンドギャップが大きい半導体を用いたトランジスタを適用してもよい。バンドギャップが大きい半導体とは、バンドギャップが2.2eV以上の半導体を指す場合がある。例えば、炭化ケイ素、窒化ガリウム、ダイヤモンドなどが挙げられる。

画素210に、オフ電流が低いトランジスタを用いることで、表示部を書き換える必要がない場合(すなわち静止画を表示する場合)、一時的にゲートドライバ202、203、およびソースドライバの機能を停止することができる(「アイドリングストップ」または「IDS駆動」)。IDS駆動によって、表示ユニット200の消費電力を低減することができる。

すなわち、例えば、通常動作時に表示部を1秒間に60回書き換えていたものを、IDS駆動時には1秒間に1回とすることができる。さらに好ましくは、1分間に1回の書き換えとすることができる。このように表示部の書き換え(リフレッシュ、ともいう)頻度を少なくすることで、表示ユニット200の消費電力を低減することができる。

図9は、表示ユニット200の構成例を示すブロック図である。

画素アレイ201は、複数の画素210(1,1)乃至画素210(m,n)と、ソース線SL(1)乃至ソース線SL(m)と、ゲート線GL(1)乃至ゲート線GL(n)を有する。ここで、mおよびnは1以上の整数であり、iは1以上m以下の整数であり、jは1以上n以下の整数である。なお、図9において、電源線や容量を形成するための定電位線等は省略している。

ゲートドライバ202、203は、ゲート線GL(1)乃至ゲート線GL(n)を介して画素アレイ201と電気的に接続され、コントローラIC204は、ソース線SL(1)乃至ソース線SL(m)を介して画素アレイ201と電気的に接続される。

また、矢印C1で示す方向に配設される一群の画素210(i,1)乃至画素210(i,n)は、ソース線SL(i)と電気的に接続され、矢印R1で示す方向に配設される一群の画素210(1,j)乃至画素210(m,j)は、ゲート線GL(j)と電気的に接続される。

ゲートドライバ202、203は、ゲート線GL(j)を駆動し、画素210(1,j)乃至画素210(m,j)を選択する。コントローラIC204は、ソース線SL(1)乃至ソース線SL(m)を介して、信号処理部15A乃至15Cおよび信号処理部35から供給された画像データのデータ信号を、画素210(1,j)乃至画素210(m,j)に供給する。この動作を、ゲート線GL(1)からゲート線GL(n)まで繰り返すことで、表示ユニット200は、画素アレイ201に画像を表示することができる。

なお、画素210には、上述した、液晶素子、電子ペーパー、有機EL素子、無機EL素子、QLED、LED等、様々な表示素子を適用することができる。

<ゲートドライバ>

部分IDS駆動は、表示部の一部領域に対して、上述のIDS駆動を行う駆動方法である。ここでは、部分IDS駆動を行うために、表示ユニット200の表示部を複数の領域に分割して駆動することができるゲートドライバの構成例について説明する。

ゲートドライバ202、203は、表示ユニット200の表示部を複数の領域に分割して駆動する機能を有する。すなわち、ゲートドライバ202、203は、画素アレイ201を複数の画素群に分割して駆動する機能を有する。

ゲートドライバ202、203は、第1の回路と、第2の回路を有する。第2の回路は、第1乃至第N(Nは2以上の整数)のシフトレジスタを有し、第K(Kは1以上N以下の整数)のシフトレジスタは、第Kの画素群と電気的に接続されるゲート線GLに信号を出力する。

第2の回路において、第Kのシフトレジスタのみゲート線GLに信号を出力すること、および、第1乃至第Nのシフトレジスタを1つのシフトレジスタとしてゲート線GLに信号を出力することが可能である。第2の回路において、第Kのシフトレジスタのみゲート線GLに信号を出力する場合、Kの値は、第1の回路が出力する信号に従って決定される。

なお、説明をわかりやすくするため、図9においてn=1024、m=768とし、矢印C1で示す方向に16の画素群に分割して駆動する例を説明する。また、16の画素群は均等であり、それぞれ64×768個の画素210を有する。

ここで、第1の画素群はゲート線GL(1)乃至ゲート線GL(64)と電気的に接続され、第2の画素群はゲート線GL(65)乃至ゲート線GL(128)と電気的に接続され、以下同様であり、第16の画素群はゲート線GL(961)乃至ゲート線GL(1024)と電気的に接続される。

図10は、ゲートドライバ202、203に適用可能な、ゲートドライバの構成例を示すブロック図である。ゲートドライバ202、203は、シフトレジスタ71を15個と、シフトレジスタ72、およびシフトレジスタ73を有する。ここで、15個のシフトレジスタ71とシフトレジスタ72は、前述の第2の回路に相当し、シフトレジスタ73は第1の回路に相当する。

ゲートドライバ202、203には、スタートパルスG_SP、クロック信号G_CLK[1:4]、パルス幅制御信号G_PWC[1:4]、リセット信号G_INI_RES、選択制御信号G_SEL、スタートパルスU_SP、クロック信号U_CLK[1:2]が入力される。なお、本明細書等において、G_CLK[1:4]のように、コロンで区切られた角括弧内の2つの数字は、配列の範囲を表す。例えば、G_CLK[1:4]は、G_CLK[1]乃至G_CLK[4]と同義である。同様に、コロンで区切られた丸括弧内の2つの数字も、配列の範囲を表す。例えば、GL(1:64)は、GL(1)乃至GL(64)と同義である。

また、ゲートドライバ202、203は、上述したゲート線GL(1)乃至ゲート線GL(1024)に信号を出力し、ゲート線GLを駆動する。なお、ゲートドライバ202、203に入出力される信号はデジタル信号であり、HighまたはLowのどちらかの状態をとる。

シフトレジスタ73には、スタートパルスU_SP、クロック信号U_CLK[1:2]、リセット信号G_INI_RESが入力される。シフトレジスタ73は、シフトレジスタ71およびシフトレジスタ72に、信号U[01]乃至U[16]を出力する。

シフトレジスタ71およびシフトレジスタ72には、スタートパルスG_SP、クロック信号G_CLK[1:4]、パルス幅制御信号G_PWC[1:4]、リセット信号G_INI_RES、選択制御信号G_SEL、および、信号U[01]乃至U[16]が入力される。シフトレジスタ71およびシフトレジスタ72は、それぞれ64本のゲート線GLに電気的に接続され、ゲート線GLを駆動する。

15個のシフトレジスタ71とシフトレジスタ72は、スタートパルスG_SPをトリガーとして、1つのシフトレジスタとして動作することが可能である。すなわち、後述する図18に示すように、スタートパルスG_SPをトリガーに、ゲート線GL(1)乃至ゲート線GL(1024)に信号を出力し、ゲート線GLを駆動することができる。

また、15個のシフトレジスタ71とシフトレジスタ72のうち、いずれか1つのシフトレジスタのみゲート線GLに信号を出力することが可能である。この場合、どのシフトレジスタが信号を出力するかは、シフトレジスタ73が出力する信号U[01]乃至U[16]に従って決定される。

図11乃至図13は、シフトレジスタの構成例を示す回路図である。図11はシフトレジスタ71の構成例を、図12はシフトレジスタ72の構成例を、図13はシフトレジスタ73の構成例を、それぞれ示している。

図11(A)は、シフトレジスタ71のシンボルであり、シフトレジスタ71の入出力の様子を示している。シフトレジスタ71は、入力端子U_IN、SP_IN、CLK_IN[1:4]、PWC_IN[1:4]、INI_RES_IN、SEL_IN、R_IN[1:2]を有し、出力端子SP_OUT、CLK_OUT[1:4]、PWC_OUT[1:4]、INI_RES_OUT、SEL_OUT、R_OUT[1:2]、および、SR_OUT[1:64]を有する。ここで、SR_OUT[1:64]からは、64本のゲート線GLに信号が出力される。

図11(B)は、シフトレジスタ71のシンボルに対する回路図である。シフトレジスタ71は、レジスタ81と63個のレジスタ82を有する。レジスタ81と63個のレジスタ82は、それぞれ、CLK_IN[1]乃至CLK_IN[4]のいずれか3つ、PWC_IN[1]乃至PWC_IN[4]のいずれか1つ、およびINI_RES_INと電気的に接続され、信号が入力される。また、SR_OUT[1]はレジスタ81と電気的に接続され、SR_OUT[2]乃至SR_OUT[64]は、それぞれ、63個のレジスタ82の1つと、順に電気的に接続される。レジスタ81は、U_IN、SP_IN、SEL_INと電気的に接続され、信号が入力される。

図12(A)は、シフトレジスタ72のシンボルであり、シフトレジスタ72の入出力の様子を示している。シフトレジスタ72は、入力端子U_IN、SP_IN、CLK_IN[1:4]、PWC_IN[1:4]、INI_RES_IN、SEL_INを有し、出力端子R_OUT[1:2]、および、SR_OUT[1:64]を有する。

図12(B)は、シフトレジスタ72のシンボルに対する回路図である。シフトレジスタ72は、レジスタ81と63個のレジスタ82、および2個のレジスタ83を有する。レジスタ81とレジスタ82およびレジスタ83は、それぞれ、CLK_IN[1]乃至CLK_IN[4]のいずれか3つ、PWC_IN[1]乃至PWC_IN[4]のいずれか1つ、およびINI_RES_INと電気的に接続され、信号が入力される。また、SR_OUT[1]はレジスタ81と電気的に接続され、SR_OUT[2]乃至SR_OUT[64]は、それぞれ、63個のレジスタ82の1つと、順に電気的に接続される。レジスタ81は、U_IN、SP_IN、SEL_INと電気的に接続され、信号が入力される。

図13(A)は、シフトレジスタ73のシンボルであり、シフトレジスタ73の入出力の様子を示している。シフトレジスタ73は、入力端子SP_IN、CLK_IN[1:2]、INI_RES_INを有し、出力端子SR_OUT[1]乃至SR_OUT[16]を有する。

図13(B)は、シフトレジスタ73のシンボルに対する回路図である。シフトレジスタ73は、16個のレジスタ85を有する。レジスタ85は、それぞれ、CLK_IN[1]またはCLK_IN[2]、およびINI_RES_INと電気的に接続され、信号が入力される。また、レジスタ85は、それぞれ、SR_OUT[1]乃至SR_OUT[16]のいずれかと電気的に接続され、信号を出力する。

図14乃至図17は、レジスタの構成例を示す回路図である。図14はレジスタ81の構成例を、図15はレジスタ82の構成例を、図16はレジスタ83の構成例を、図17はレジスタ85の構成例を、それぞれ示している。

図14(A)は、レジスタ81のシンボルであり、レジスタ81の入出力の様子を示している。レジスタ81は、入力端子U_IN、L_IN、CLK_IN[1]乃至CLK_IN[3]、PWC_IN、RES_IN、SEL_IN、R_INを有し、出力端子R_OUT[1]、R_OUT[2]を有する。ここで、L_INにはスタートパルスが入力され、R_INには2つ後段のレジスタの出力が入力され、U_INにはシフトレジスタ73が出力する信号U[01]乃至U[16]のいずれかが入力される(図10乃至図12、参照)。

図14(B)は、レジスタ81のシンボルに対する回路図である。レジスタ81は、トランジスタTr1乃至トランジスタTr19と、容量素子C3を有する。なお、VDDは高電位電源であり、VSSは低電位電源である。

図15(A)は、レジスタ82のシンボルであり、レジスタ82の入出力の様子を示している。レジスタ82は、入力端子L_IN、CLK_IN[1]乃至CLK_IN[3]、PWC_IN、RES_IN、R_INを有し、出力端子R_OUT[1]、R_OUT[2]を有する。ここで、L_INには前段のレジスタの出力が入力され、R_INには2つ後段のレジスタの出力が入力される(図11および図12、参照)。

図15(B)は、レジスタ82のシンボルに対する回路図である。レジスタ82は、トランジスタTr20乃至トランジスタTr34と、容量素子C4を有する。なお、VDDは高電位電源であり、VSSは低電位電源である。

図16(A)は、レジスタ83のシンボルであり、レジスタ83の入出力の様子を示している。レジスタ83は、入力端子L_IN、CLK_IN[1]乃至CLK_IN[3]、PWC_IN、RES_INを有し、出力端子R_OUT[1]、R_OUT[2]を有する。L_INには前段のレジスタの出力が入力される。なお、レジスタ83は、シフトレジスタ72の最後の2段に使用されるため、入力端子R_INは有さない(図12参照)。

図16(B)は、レジスタ83のシンボルに対する回路図である。レジスタ83は、トランジスタTr35乃至トランジスタTr48と、容量素子C5を有する。なお、VDDは高電位電源であり、VSSは低電位電源である。

図17(A)は、レジスタ85のシンボルであり、レジスタ85の入出力の様子を示している。レジスタ85は、入力端子L_IN、CLK_IN、RES_IN、R_INを有し、出力端子R_OUTを有する。ここで、L_INには前段のレジスタの出力またはスタートパルスが入力され、R_INには後段のレジスタの出力が入力される(図13参照)。

図17(B)は、レジスタ85のシンボルに対する回路図である。レジスタ85は、トランジスタTr49乃至トランジスタTr58と、容量素子C6を有する。なお、VDDは高電位電源であり、VSSは低電位電源である。

なお、トランジスタTr1乃至トランジスタTr58はOSトランジスタを用いることが好ましい。トランジスタTr1乃至トランジスタTr58は、図14乃至図17ではシングルゲートトランジスタとして図示したが、バックゲートを有するデュアルゲートトランジスタでもよい。トランジスタTr1乃至トランジスタTr58がOSトランジスタであることで、トランジスタのオフ電流が低くなり、ゲートドライバの消費電流を低減することができる。

<タイミングチャート>

図18乃至図21は、ゲートドライバ202、203の動作に関するタイミングチャートである。

なお、上述したように、表示ユニット200が設定される動作モードに通常動作と低消費電力があり、動作モードが低消費電力の場合、表示ユニット200はIDS駆動、または部分IDS駆動を行うことができる。IDS駆動は、表示部の全領域の書き換え頻度を少なくする駆動方法であり、部分IDS駆動は、表示部の一部領域の書き換え頻度を少なくする駆動方法である。以下、通常動作と部分IDS駆動のタイミングチャートについて説明する。

図18は、通常動作におけるタイミングチャートであり、ゲートドライバ202、203に入力されるスタートパルスG_SP、クロック信号G_CLK[1]乃至G_CLK[4]、パルス幅制御信号G_PWC[1]乃至G_PWC[4]と、ゲートドライバ202、203が信号を出力するゲート線GL(1)乃至ゲート線GL(1024)の関係を示している。

図18において、ゲートドライバ202、203は、スタートパルスG_SPをトリガーとして、クロック信号G_CLK[1]乃至G_CLK[4]に従い、ゲート線GL(1)乃至ゲート線GL(1024)に順に信号を出力する。ゲートドライバ202、203が、ゲート線GL(1)乃至ゲート線GL(1024)に順に信号を出力することで、表示ユニット200は、表示部の全領域を書き換えることができる。

図19乃至図21は、部分IDS駆動におけるタイミングチャートである。部分IDS駆動では、15個のシフトレジスタ71とシフトレジスタ72のうち、いずれか1つのシフトレジスタのみゲート線GLに信号を出力することが可能である。この場合、どのシフトレジスタが信号を出力するかは、シフトレジスタ73が出力する信号U[01]乃至U[16]に従って決定される。

図19および図20は、スタートパルスU_SP、クロック信号U_CLK[1]乃至U_CLK[2]、リセット信号G_INI_RESと、シフトレジスタ73が出力する信号U[01]乃至U[16]の関係を示している。さらに、図19は、一部領域として第2の画素群(ゲート線GL(65)乃至ゲート線GL(128)と電気的に接続されている)を書き換える場合、図20は、第9の画素群(ゲート線GL(513)乃至ゲート線GL(576)と電気的に接続されている)を書き換える場合のタイミングチャートである。

図19においては、シフトレジスタ73は、スタートパルスU_SPをトリガーとして、クロック信号U_CLK[1]乃至U_CLK[2]に従い動作を開始するが、信号U[02]にHighの信号を出力したタイミングで、クロック信号U_CLK[1]乃至U_CLK[2]は停止する。クロック信号U_CLK[1]乃至U_CLK[2]が停止することで、シフトレジスタ73は、信号U[02]をHighの状態に保持している。

図20においては、シフトレジスタ73は、スタートパルスU_SPをトリガーとして、クロック信号U_CLK[1]乃至U_CLK[2]に従い、信号U[01]乃至信号U[08]に順に信号を出力するが、信号U[09]にHighの信号を出力したタイミングで、クロック信号U_CLK[1]乃至U_CLK[2]は停止する。クロック信号U_CLK[1]乃至U_CLK[2]が停止することで、シフトレジスタ73は、信号U[09]をHighの状態に保持している。

図21は、第2の画素群を書き換える場合であり、信号U[02]、選択制御信号G_SEL、クロック信号G_CLK[1]乃至G_CLK[4]、パルス幅制御信号G_PWC[1]乃至G_PWC[4]と、ゲート線GL(64)乃至ゲート線GL(129)の関係を示している。

信号U[02]は、図19におけるシフトレジスタ73の動作により、Highの状態を保持している。そこへ、選択制御信号G_SELに信号が入力されると、シフトレジスタ71およびシフトレジスタ72のうち、信号U[02]が入力されるシフトレジスタへ、スタートパルスが入力されたのと、同じ状態とすることができる。すなわち、ゲート線GL(65)乃至ゲート線GL(128)に電気的に接続されたシフトレジスタ71が、動作を開始する。

ゲート線GL(65)乃至ゲート線GL(128)に電気的に接続されたシフトレジスタ71は、選択制御信号G_SELをトリガーとして、クロック信号G_CLK[1]乃至G_CLK[4]に従い、ゲート線GL(65)乃至ゲート線GL(128)に順に信号を出力する。ゲート線GL(65)乃至ゲート線GL(128)に順に信号を出力することで、表示ユニット200は、第2の画素群を書き換えることができる。

なお、シフトレジスタ71が有するレジスタ82は、入力端子R_INに2つ後段のレジスタの出力が入力されるため、図21において、ゲート線GL(129)乃至ゲート線GL(192)に電気的に接続されたシフトレジスタ71が有する最初の2つのレジスタが、動作を行うためのクロック信号G_CLK[1]乃至G_CLK[4]も入力する必要がある。前記クロック信号G_CLK[1]乃至G_CLK[4]が入力されることによって、ゲート線GL(129)乃至ゲート線GL(192)に電気的に接続されたシフトレジスタ71も一部動作を行うが、パルス幅制御信号G_PWC[1]乃至G_PWC[4]をLowの状態に保持することで、ゲート線GL(129)乃至ゲート線GL(192)に信号を出力することはない。

第9の画素群を書き換える場合も、シフトレジスタ71の動作は同様のため、説明を省略する。なお、図19および図20に示すシフトレジスタ73が動作する期間を「期間Fa」とし、図21に示すシフトレジスタ71またはシフトレジスタ72が動作する期間を「期間Fb」とすると、期間Faで一部領域を選択し、選択した領域を期間Fbで書き換えることで、表示部の一部領域を書き換えることができる。また、シフトレジスタ73が有するレジスタ85は16個であり、シフトレジスタ71やシフトレジスタ72が有するレジスタの個数よりも少ないため、期間Faは期間Fbより短く、シフトレジスタ73を配置するためのレイアウト面積も小さくすることができる。

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせて実施することができる。

(実施の形態4)

本実施の形態では、上記実施の形態に記載の信号処理部15A乃至15Cおよび信号処理部35に適用可能な、ニューラルネットワークの構成例について図22乃至図28を用いて説明を行う。

なお、ここでは、ニューラルネットワークの演算処理や、画像データの画像処理に用いられる、積和演算回路の説明から行う。

<積和演算回路>

積和演算回路の構成の一例を図22に示す。図22に示す積和演算回路100は、記憶回路101、参照用記憶回路102、電流ソース回路103、電流シンク回路104、および電流源回路105を有する。

記憶回路101は、メモリセルMC[i、j]、メモリセルMC[i+1、j]で例示されるメモリセルMCを有する。また、各メモリセルMCは、入力された電位を電流に変換する機能を有する素子を有する。上記機能を有する素子として、例えばトランジスタなどの能動素子を用いることができる。図22では、各メモリセルMCがトランジスタTr1を有する場合を例示している。

メモリセルMCには、配線WD[j]で例示される配線WDから第1のアナログ電位が入力される。そして、メモリセルMCは、第1のアナログ電位に応じた第1のアナログ電流を生成する機能を有する。具体的には、トランジスタTr1のゲートに第1のアナログ電位を供給したときに得られるトランジスタTr1のドレイン電流を、第1のアナログ電流とすることができる。なお、以下、メモリセルMC[i、j]に流れる電流をI[i、j]とし、メモリセルMC[i+1、j]に流れる電流をI[i+1、j]とする。

なお、トランジスタTr1が飽和領域で動作する場合、そのドレイン電流はソースとドレイン間の電圧に依存せず、ゲート電圧と閾値電圧の差分によって制御される。よって、トランジスタTr1は飽和領域で動作させることが望ましい。トランジスタTr1を飽和領域で動作させるために、そのゲート電圧、ソースとドレイン間の電圧は、飽和領域で動作する範囲の電圧に適切に設定されているものとする。

具体的に、図22に示す積和演算回路100では、メモリセルMC[i、j]に配線WD[j]から第1のアナログ電位Vx[i、j]または第1のアナログ電位Vx[i、j]に応じた電位が入力される。メモリセルMC[i、j]は、第1のアナログ電位Vx[i、j]に応じた第1のアナログ電流を生成する機能を有する。すなわち、この場合、メモリセルMC[i、j]の電流I[i、j]は、第1のアナログ電流に相当する。

また、具体的に、図22に示す積和演算回路100では、メモリセルMC[i+1、j]に配線WD[j]から第1のアナログ電位Vx[i+1、j]または第1のアナログ電位Vx[i+1、j]に応じた電位が入力される。メモリセルMC[i+1、j]は、第1のアナログ電位Vx[i+1、j]に応じた第1のアナログ電流を生成する機能を有する。すなわち、この場合、メモリセルMC[i+1、j]の電流I[i+1、j]は、第1のアナログ電流に相当する。

メモリセルMCは、第1のアナログ電位を保持する機能を有する。すなわち、メモリセルMCは、第1のアナログ電位を保持することで、第1のアナログ電位に応じた第1のアナログ電流を保持する機能を有すると言える。

また、メモリセルMCには、配線RW[i]、配線RW[i+1]で例示される配線RWから第2のアナログ電位が入力される。メモリセルMCは、既に保持されている第1のアナログ電位に、第2のアナログ電位或いは第2のアナログ電位に応じた電位を加算する機能と、加算することで得られる第3のアナログ電位を保持する機能とを有する。そして、メモリセルMCは、第3のアナログ電位に応じた第2のアナログ電流を生成する機能を有する。すなわち、メモリセルMCは、第3のアナログ電位を保持することで、第3のアナログ電位に応じた第2のアナログ電流を保持する機能を有すると言える。

具体的に、図22に示す積和演算回路100では、メモリセルMC[i、j]に配線RW[i]から第2のアナログ電位Vw[i、j]が入力される。そして、メモリセルMC[i、j]は、第1のアナログ電位Vx[i、j]及び第2のアナログ電位Vw[i、j]に応じた第3のアナログ電位を保持する機能を有する。そして、メモリセルMC[i、j]は、第3のアナログ電位に応じた第2のアナログ電流を生成する機能を有する。すなわち、この場合、メモリセルMC[i、j]の電流I[i、j]は、第2のアナログ電流に相当する。

また、図22に示す積和演算回路100では、メモリセルMC[i+1、j]に配線RW[i+1]から第2のアナログ電位Vw[i+1、j]が入力される。そして、メモリセルMC[i+1、j]は、第1のアナログ電位Vx[i+1、j]及び第2のアナログ電位Vw[i+1、j]に応じた第3のアナログ電位を保持する機能を有する。そして、メモリセルMC[i+1、j]は、第3のアナログ電位に応じた第2のアナログ電流を生成する機能を有する。すなわち、この場合、メモリセルMC[i+1、j]の電流I[i+1、j]は、第2のアナログ電流に相当する。

そして、電流I[i、j]は、メモリセルMC[i、j]を介して配線BL[j]と配線VR[j]の間を流れる。電流I[i+1、j]は、メモリセルMC[i+1、j]を介して配線BL[j]と配線VR[j]の間を流れる。よって、電流I[i、j]と電流I[i+1、j]との和に相当する電流I[j]が、メモリセルMC[i、j]及びメモリセルMC[i+1、j]を介して配線BL[j]と配線VR[j]の間を流れることとなる。

参照用記憶回路102は、メモリセルMCR[i]、メモリセルMCR[i+1]で例示されるメモリセルMCRを有する。メモリセルMCRには、配線WDREFから第1の参照電位VPRが入力される。そして、メモリセルMCRは、第1の参照電位VPRに応じた第1の参照電流を生成する機能を有する。なお、以下、メモリセルMCR[i]に流れる電流をIREF[i]とし、メモリセルMCR[i+1]に流れる電流をIREF[i+1]とする。

そして、具体的に、図22に示す積和演算回路100では、メモリセルMCR[i]に配線WDREF[i]から第1の参照電位VPRが入力される。メモリセルMCR[i]は、第1の参照電位VPRに応じた第1の参照電流を生成する機能を有する。すなわち、この場合、メモリセルMCR[i]の電流IREF[i]は、第1の参照電流に相当する。

また、図22に示す積和演算回路100では、メモリセルMCR[i+1]に配線WDREFから第1の参照電位VPRが入力される。メモリセルMCR[i+1]は、第1の参照電位VPRに応じた第1の参照電流を生成する機能を有する。すなわち、この場合、メモリセルMCR[i+1]の電流IREF[i+1]は、第1の参照電流に相当する。

そして、メモリセルMCRは、第1の参照電位VPRを保持する機能を有する。すなわち、メモリセルMCRは、第1の参照電位VPRを保持することで、第1の参照電位VPRに応じた第1の参照電流を保持する機能を有すると言える。

また、メモリセルMCRには、配線RW[i]、配線RW[i+1]で例示される配線RWから第2のアナログ電位が入力される。メモリセルMCRは、既に保持されている第1の参照電位VPRに、第2のアナログ電位或いは第2のアナログ電位に応じた電位を加算し、加算することで得られる第2の参照電位を保持する機能を有する。そして、メモリセルMCRは、第2の参照電位に応じた第2の参照電流を生成する機能を有する。すなわち、メモリセルMCRは、第2の参照電位を保持することで、第2の参照電位に応じた第2の参照電流を保持する機能を有すると言える。

具体的に、図22に示す積和演算回路100では、メモリセルMCR[i]に配線RW[i]から第2のアナログ電位Vw[i、j]が入力される。そして、メモリセルMCR[i]は、第1の参照電位VPR及び第2のアナログ電位Vw[i、j]に応じた第2の参照電位を保持する機能を有する。そして、メモリセルMCR[i]は、第2の参照電位に応じた第2の参照電流を生成する機能を有する。すなわち、この場合、メモリセルMCR[i]の電流IREF[i]は、第2の参照電流に相当する。

また、図22に示す積和演算回路100では、メモリセルMCR[i+1]に配線RW[i+1]から第2のアナログ電位Vw[i+1、j]が入力される。そして、メモリセルMCR[i+1]は、第1の参照電位VPR及び第2のアナログ電位Vw[i+1、j]に応じた第2の参照電位を保持する機能を有する。そして、メモリセルMCR[i+1]は、第2の参照電位に応じた第2の参照電流を生成する機能を有する。すなわち、この場合、メモリセルMCR[i+1]の電流IREF[i+1]は、第2の参照電流に相当する。

そして、電流IREF[i]は、メモリセルMCR[i]を介して配線BLREFと配線VRREFの間を流れる。電流IREF[i+1]は、メモリセルMCR[i+1]を介して配線BLREFと配線VRREFの間を流れる。よって、電流IREF[i]と電流IREF[i+1]との和に相当する電流IREFが、メモリセルMCR[i]及びメモリセルMCR[i+1]を介して配線BLREFと配線VRREFの間を流れることとなる。

電流源回路105は、配線BLREFに流れる電流IREFと同じ値の電流、もしくは電流IREFに対応する電流を、配線BLに供給する機能を有する。そして、後述するオフセットの電流を設定する際には、メモリセルMC[i、j]及びメモリセルMC[i+1、j]を介して配線BL[j]と配線VR[j]の間を流れる電流I[j]が、メモリセルMCR[i]及びメモリセルMCR[i+1]を介して配線BLREFと配線VRREFの間を流れる電流IREFと異なる場合、差分の電流は電流ソース回路103または電流シンク回路104に流れる。

具体的に、電流I[j]が電流IREFよりも大きい場合、電流ソース回路103は、電流I[j]と電流IREFの差分に相当する電流ΔI[j]を生成する機能を有する。また、電流ソース回路103は、生成した電流ΔI[j]を配線BL[j]に供給する機能を有する。すなわち、電流ソース回路103は、電流ΔI[j]を保持する機能を有すると言える。

また、電流I[j]が電流IREFよりも小さい場合、電流シンク回路104は、電流I[j]と電流IREFの差分に相当する電流ΔI[j]を生成する機能を有する。また、電流シンク回路104は、生成した電流ΔI[j]を配線BL[j]から引き込む機能を有する。すなわち、電流シンク回路104は、電流ΔI[j]を保持する機能を有すると言える。

次いで、図22に示す積和演算回路100の動作の一例について説明する。

まず、メモリセルMC[i、j]に第1のアナログ電位に応じた電位を格納する。具体的には、第1の参照電位VPRから第1のアナログ電位Vx[i、j]を差し引いた電位VPR−Vx[i、j]が、配線WD[j]を介してメモリセルMC[i、j]に入力される。メモリセルMC[i、j]では、電位VPR−Vx[i、j]が保持される。また、メモリセルMC[i、j]では、電位VPR−Vx[i、j]に応じた電流I[i、j]が生成される。例えば第1の参照電位VPRは、接地電位よりも高いハイレベルの電位とする。具体的には、接地電位よりも高く、電流源回路105に供給されるハイレベルの電位VDDと同程度か、それ以下の電位であることが望ましい。

また、メモリセルMCR[i]に第1の参照電位VPRを格納する。具体的には、電位VPRが、配線WDREFを介してメモリセルMCR[i]に入力される。メモリセルMCR[i]では、電位VPRが保持される。また、メモリセルMCR[i]では、電位VPRに応じた電流IREF[i]が生成される。

また、メモリセルMC[i+1、j]に第1のアナログ電位に応じた電位を格納する。具体的には、第1の参照電位VPRから第1のアナログ電位Vx[i+1、j]を差し引いた電位VPR−Vx[i+1、j]が、配線WD[j]を介してメモリセルMC[i+1、j]に入力される。メモリセルMC[i+1、j]では、電位VPR−Vx[i+1、j]が保持される。また、メモリセルMC[i+1、j]では、電位VPR−Vx[i+1、j]に応じた電流I[i+1、j]が生成される。

また、メモリセルMCR[i+1]に第1の参照電位VPRを格納する。具体的には、電位VPRが、配線WDREFを介してメモリセルMCR[i+1]に入力される。モリセルMCR[i+1]では、電位VPRが保持される。また、メモリセルMCR[i+1]では、電位VPRに応じた電流IREF[i+1]が生成される。

上記動作において、配線RW[i]及び配線RW[i+1]は基準電位とする。例えば、基準電位として接地電位、基準電位よりも低いローレベルの電位VSSなどを用いることができる。或いは、基準電位として電位VSSと電位VDDの間の電位を用いると、第2のアナログ電位Vwを正負にしても、配線RWの電位を接地電位よりも高くできるので信号の生成を容易にすることができ、正負の電位に対する積演算が可能になるので好ましい。

上記動作により、配線BL[j]には、配線BL[j]に接続されたメモリセルMCにおいてそれぞれ生成される電流を合わせた電流が、流れることとなる。具体的に図22では、メモリセルMC[i、j]で生成される電流I[i、j]と、メモリセルMC[i+1、j]で生成される電流I[i+1、j]とを合わせた電流I[j]が流れる。また、上記動作により、配線BLREFには、配線BLREFに接続されたメモリセルMCRにおいてそれぞれ生成される電流を合わせた電流が、流れることとなる。具体的に図22では、メモリセルMCR[i]で生成される電流IREF[i]と、メモリセルMCR[i+1]で生成される電流IREF[i+1]とを合わせた電流IREFが流れる。

次いで、配線RW[i]及び配線RW[i+1]の電位を基準電位としたまま、第1のアナログ電位によって得られる電流I[j]と第1の参照電位によって得られる電流IREFとの差分から得られるオフセットの電流Ioffset[j]を、電流ソース回路103または電流シンク回路104において保持する。

具体的に、電流I[j]が電流IREFよりも大きい場合、電流ソース回路103は電流Ioffset[j]を配線BL[j]に供給する。すなわち、電流ソース回路103に流れる電流ICM[j]は電流Ioffset[j]に相当することとなる。そして、当該電流ICM[j]の値は電流ソース回路103において保持される。また、電流I[j]が電流IREFよりも小さい場合、電流シンク回路104は電流Ioffset[j]を配線BL[j]から引き込む。すなわち、電流シンク回路104に流れる電流ICP[j]は電流Ioffset[j]に相当することとなる。そして、当該電流ICP[j]の値は電流シンク回路104において保持される。

次いで、既にメモリセルMC[i、j]において保持されている第1のアナログ電位または第1のアナログ電位に応じた電位に加算するように、第2のアナログ電位または第2のアナログ電位に応じた電位をメモリセルMC[i、j]に格納する。具体的には、配線RW[i]の電位を基準電位に対してVw[i]だけ高い電位とすることで、第2のアナログ電位Vw[i]が、配線RW[i]を介してメモリセルMC[i、j]に入力される。メモリセルMC[i、j]では、電位VPR−Vx[i、j]+Vw[i]が保持される。また、メモリセルMC[i、j]では、電位VPR−Vx[i、j]+Vw[i]に応じた電流I[i、j]が生成される。

また、既にメモリセルMC[i+1、j]において保持されている第1のアナログ電位または第1のアナログ電位に応じた電位に加算するように、第2のアナログ電位または第2のアナログ電位に応じた電位をメモリセルMC[i+1、j]に格納する。具体的には、配線RW[i+1]の電位を基準電位に対してVw[i+1]だけ高い電位とすることで、第2のアナログ電位Vw[i+1]が、配線RW[i+1]を介してメモリセルMC[i+1、j]に入力される。メモリセルMC[i+1、j]では、電位VPR−Vx[i+1、j]+Vw[i+1]が保持される。また、メモリセルMC[i+1、j]では、電位VPR−Vx[i+1、j]+Vw[i+1]に応じた電流I[i+1、j]が生成される。

なお、電位を電流に変換する素子として飽和領域で動作するトランジスタTr1を用いる場合、配線RW[i]の電位がVw[i]であり、配線RW[i+1]の電位がVw[i+1]であると仮定すると、メモリセルMC[i、j]が有するトランジスタTr1のドレイン電流が電流I[i、j]に相当するので、第2のアナログ電流は以下の式1で表される。なお、kは係数、VthはトランジスタTr1の閾値電圧である。

I[i、j]=k(Vw[i]−Vth+VPR−Vx[i、j])2・・・(1)

また、メモリセルMCR[i]が有するトランジスタTr1のドレイン電流が電流IREF[i]に相当するので、第2の参照電流は以下の式2で表される。

IREF[i]=k(Vw[i]−Vth+VPR)2・・・(2)

そして、メモリセルMC[i、j]に流れる電流I[i、j]と、メモリセルMC[i+1、j]に流れる電流I[i+1、j]の和に相当する電流I[j]は、I[j]=ΣiI[i、j]であり、メモリセルMCR[i]に流れる電流IREF[i]と、メモリセルMCR[i+1]に流れる電流IREF[i+1]の和に相当する電流IREFは、IREF=ΣiIREF[i]となり、その差分に相当する電流ΔI[j]は以下の式3で表される。

ΔI[j]=IREF−I[j]=ΣiIREF[i]−ΣiI[i、j]・・・(3)

式1、式2、式3から、電流ΔI[j]は以下の式4のように導き出される。

ΔI[j]

=Σi{k(Vw[i]−Vth+VPR)2−k(Vw[i]−Vth+VPR−Vx[i、j])2}

=2kΣi(Vw[i]・Vx[i、j])−2kΣi(Vth−VPR)・Vx[i、j]−kΣiVx[i、j]2・・・(4)

式4において、2kΣi(Vw[i]・Vx[i、j])で示される項は、第1のアナログ電位Vx[i、j]及び第2のアナログ電位Vw[i]の積と、第1のアナログ電位Vx[i+1、j]及び第2のアナログ電位Vw[i+1]の積と、の和に相当する。

また、Ioffset[j]は、配線RW[i]の電位を全て基準電位としたとき、すなわち第2のアナログ電位Vw[i]を0、第2のアナログ電位Vw[i+1]を0としたときの電流ΔI[j]とすると、式4から、以下の式5が導き出される。

Ioffset[j]=−2kΣi(Vth−VPR)・Vx[i、j]−kΣiVx[i、j]2・・・(5)

したがって、式3乃至式5から、第1のアナログ電流と第2のアナログ電流の積和値に相当する2kΣi(Vw[i]・Vx[i、j])は、以下の式6で表されることが分かる。

2kΣi(Vw[i]・Vx[i、j])=IREF−I[j]−Ioffset[j]・・・(6)

そして、メモリセルMCに流れる電流の和を電流I[j]、メモリセルMCRに流れる電流の和を電流IREF、電流ソース回路103または電流シンク回路104に流れる電流を電流Ioffset[j]とすると、配線RW[i]の電位をVw[i]、配線RW[i+1]の電位をVw[i+1]としたときに配線BL[j]から流れ出る電流Iout[j]は、IREF−I[j]−Ioffset[j]で表される。式6から、電流Iout[j]は、2kΣi(Vw[i]・Vx[i、j])であり、第1のアナログ電位Vx[i、j]及び第2のアナログ電位Vw[i]の積と、第1のアナログ電位Vx[i+1、j]及び第2のアナログ電位Vw[i+1]の積と、の和に相当することが分かる。

なお、トランジスタTr1は飽和領域で動作させることが望ましいが、トランジスタTr1の動作領域が理想的な飽和領域と異なっていたとしても、第1のアナログ電位Vx[i、j]及び第2のアナログ電位Vw[i]の積と、第1のアナログ電位Vx[i+1、j]及び第2のアナログ電位Vw[i+1]の積との和に相当する電流を、所望の範囲内の精度で問題なく得ることができる場合は、トランジスタTr1は飽和領域で動作しているものとみなせる。

図22に示す積和演算回路の構成とすることにより、演算処理をデジタルデータに変換せずとも実行することができるので、半導体装置の回路規模を小さく抑えることができる。或いは、図22に示す積和演算回路の構成とすることにより、演算処理をデジタルデータに変換せずとも実行することができるので、演算処理に要する時間を抑えることができる。或いは、図22に示す積和演算回路の構成とすることにより、演算処理に要する時間を抑えつつ、低消費電力化を実現することができる。

次いで、記憶回路101、参照用記憶回路102、電流ソース回路103、電流シンク回路104、および電流源回路105の具体的な構成の一例について、図23を用いて説明する。

図23では、一例として、任意の2行2列のメモリセルMCと、任意の2行1列のメモリセルMCRとの、具体的な回路構成と接続関係とを示している。具体的に図23では、i行j列目のメモリセルMC[i、j]と、i+1行j列目のメモリセルMC[i+1、j]と、i行j+1列目のメモリセルMC[i、j+1]と、i+1行j+1列目のメモリセルMC[i+1、j+1]とを図示している。また、具体的に図23では、i行目のメモリセルMCR[i]と、i+1行目のメモリセルMCR[i+1]とを図示している。

i行目のメモリセルMC[i、j]と、メモリセルMC[i、j+1]と、メモリセルMCR[i]とは、配線RW[i]及び配線WW[i]に接続されている。また、i+1行目のメモリセルMC[i+1、j]と、メモリセルMC[i+1、j+1]と、メモリセルMCR[i+1]とは、配線RW[i+1]及び配線WW[i+1]に接続されている。

j列目のメモリセルMC[i、j]と、メモリセルMC[i+1、j]とは、配線WD[j]、配線VR[j]、及び配線BL[j]に接続されている。また、j+1列目のメモリセルMC[i、j+1]と、メモリセルMC[i+1、j+1]とは、配線WD[j+1]、配線VR[j+1]、及び配線BL[j+1]に接続されている。また、メモリセルMCR[i]と、i+1行目のメモリセルMCR[i+1]とは、配線WDREF、配線VRREF、及び配線BLREFに接続されている。

そして、各メモリセルMCと各メモリセルMCRとは、トランジスタTr1と、トランジスタTr2と、容量素子C11と、を有する。トランジスタTr2は、メモリセルMCまたはメモリセルMCRへの第1のアナログ電位の入力を制御する機能を有する。トランジスタTr1は、ゲートに入力された電位に従って、アナログ電流を生成する機能を有する。容量素子C11は、メモリセルMCまたはメモリセルMCRにおいて保持されている第1のアナログ電位または第1のアナログ電位に応じた電位に、第2のアナログ電位或いは第2のアナログ電位に応じた電位を加算する機能を有する。

具体的に、図23に示すメモリセルMCでは、トランジスタTr2は、ゲートが配線WWに接続され、ソース又はドレインの一方が配線WDに接続され、ソース又はドレインの他方がトランジスタTr1のゲートに接続されている。また、トランジスタTr1は、ソース又はドレインの一方が配線VRに接続され、ソース又はドレインの他方が配線BLに接続されている。容量素子C11は、第1の電極が配線RWに接続され、第2の電極がトランジスタTr1のゲートに接続されている。

また、図23に示すメモリセルMCRでは、トランジスタTr2は、ゲートが配線WWに接続され、ソース又はドレインの一方が配線WDREFに接続され、ソース又はドレインの他方がトランジスタTr1のゲートに接続されている。また、トランジスタTr1は、ソース又はドレインの一方が配線VRREFに接続され、ソース又はドレインの他方が配線BLREFに接続されている。容量素子C11は、第1の電極が配線RWに接続され、第2の電極がトランジスタTr1のゲートに接続されている。

メモリセルMCにおいてトランジスタTr1のゲートをノードNとすると、メモリセルMCでは、トランジスタTr2を介してノードNに第1のアナログ電位が入力され、次いでトランジスタTr2がオフになるとノードNが浮遊状態になり、ノードNにおいて第1のアナログ電位または第1のアナログ電位に応じた電位が保持される。また、メモリセルMCでは、ノードNが浮遊状態になると、容量素子C11の第1の電極に入力された第2のアナログ電位がノードNに与えられる。上記動作により、ノードNは、第1のアナログ電位または第1のアナログ電位に応じた電位に、第2のアナログ電位または第2のアナログ電位に応じた電位が加算されることで得られる電位となる。

なお、容量素子C11の第1の電極の電位は容量素子C11を介してノードNに与えられるため、実際には、第1の電極の電位の変化量がそのままノードNの電位の変化量に反映されるわけではない。具体的には、容量素子C11の容量値と、トランジスタTr1のゲート容量の容量値と、寄生容量の容量値とから一意に決まる結合係数を、第1の電極の電位の変化量に乗ずることで、ノードNの電位の変化量を正確に算出することができる。以下、説明を分かり易くするために、第1の電極の電位の変化量がほぼノードNの電位の変化量に反映されるものとして説明を行う。

トランジスタTr1は、ノードNの電位にしたがってそのドレイン電流が定まる。よって、トランジスタTr2がオフになることでノードNの電位が保持されると、トランジスタTr1のドレイン電流の値も保持される。上記ドレイン電流には第1のアナログ電位と第2のアナログ電位が反映されている。

また、メモリセルMCRにおいてトランジスタTr1のゲートをノードNREFとすると、メモリセルMCRでは、トランジスタTr2を介してノードNREFに第1の参照電位または第1の参照電位に応じた電位が入力され、次いでトランジスタTr2がオフになるとノードNREFが浮遊状態になり、ノードNREFにおいて第1の参照電位または第1の参照電位に応じた電位が保持される。また、メモリセルMCRでは、ノードNREFが浮遊状態になると、容量素子C11の第1の電極に入力された第2のアナログ電位がノードNREFに与えられる。上記動作により、ノードNREFは、第1の参照電位または第1の参照電位に応じた電位に、第2のアナログ電位または第2のアナログ電位に応じた電位が加算されることで得られる電位となる。

トランジスタTr1は、ノードNREFの電位にしたがってそのドレイン電流が定まる。よって、トランジスタTr2がオフになることでノードNREFの電位が保持されると、トランジスタTr1のドレイン電流の値も保持される。上記ドレイン電流には第1の参照電位と第2のアナログ電位が反映されている。

メモリセルMC[i、j]のトランジスタTr1に流れるドレイン電流を電流I[i、j]とし、メモリセルMC[i+1、j]のトランジスタTr1に流れるドレイン電流を電流I[i+1、j]とすると、配線BL[j]からメモリセルMC[i、j]及びメモリセルMC[i+1、j]に供給される電流の和は、電流I[j]となる。また、メモリセルMC[i、j+1]のトランジスタTr1に流れるドレイン電流を電流I[i、j+1]とし、メモリセルMC[i+1、j+1]のトランジスタTr1に流れるドレイン電流を電流I[i+1、j+1]とすると、配線BL[j+1]からメモリセルMC[i、j+1]及びメモリセルMC[i+1、j+1]に供給される電流の和は、電流I[j+1]となる。また、メモリセルMCR[i]のトランジスタTr1に流れるドレイン電流を電流IREF[i]とし、メモリセルMCR[i+1]のトランジスタTr1に流れるドレイン電流を電流IREF[i+1]とすると、配線BLREFからメモリセルMCR[i]及びメモリセルMCR[i+1]に供給される電流の和は、電流IREFとなる。

また、図23に示す電流ソース回路103は、j列目のメモリセルMCに対応した電流ソース回路103[j]と、j+1列目のメモリセルMCに対応した電流ソース回路103[j+1]とを有する。また、図23に示す電流シンク回路104は、j列目のメモリセルMCに対応した電流シンク回路104[j]と、j+1列目のメモリセルMCに対応した電流シンク回路104[j+1]とを有する。

電流ソース回路103[j]及び電流シンク回路104[j]は、配線BL[j]に接続されている。また、電流ソース回路103[j+1]及び電流シンク回路104[j+1]は、配線BL[j+1]に接続されている。

電流源回路105は、配線BL[j]、配線BL[j+1]、配線BLREFに接続されている。そして、電流源回路105は、配線BLREFに電流IREFを供給する機能と、電流IREFと同じ電流または電流IREFに応じた電流を、配線BL[j]及び配線BL[j+1]のそれぞれに供給する機能を有する。

具体的に、電流ソース回路103[j]及び電流ソース回路103[j+1]は、トランジスタTr7乃至Tr9と、容量素子C13とをそれぞれ有する。オフセットの電流を設定する際に、電流ソース回路103[j]において、トランジスタTr7は、電流I[j]が電流IREFよりも大きい場合に、電流I[j]と電流IREFの差分に相当する電流ICM[j]を生成する機能を有する。また、電流ソース回路103[j+1]において、トランジスタTr7は、電流I[j+1]が電流IREFよりも大きい場合に、電流I[j+1]と電流IREFの差分に相当する電流ICM[j+1]を生成する機能を有する。電流ICM[j]及び電流ICM[j+1]は、電流ソース回路103[j]及び電流ソース回路103[j+1]から配線BL[j]及び配線BL[j+1]に供給される。

電流ソース回路103[j]及び電流ソース回路103[j+1]において、トランジスタTr7は、ソース又はドレインの一方が対応する配線BLに接続されており、ソース又はドレインの他方が所定の電位が供給される配線に接続されている。トランジスタTr8は、ソース又はドレインの一方が配線BLに接続されており、ソース又はドレインの他方がトランジスタTr7のゲートに接続されている。トランジスタTr9は、ソース又はドレインの一方がトランジスタTr7のゲートに接続されており、ソース又はドレインの他方が所定の電位が供給される配線に接続されている。容量素子C13は、第1の電極がトランジスタTr7のゲートに接続されており、第2の電極が所定の電位が供給される配線に接続されている。

トランジスタTr8のゲートは配線OSMに接続されており、トランジスタTr9のゲートは配線ORMに接続されている。

なお、図23では、トランジスタTr7がpチャネル型であり、トランジスタTr8及びTr9がnチャネル型である場合を例示している。

また、電流シンク回路104[j]及び電流シンク回路104[j+1]は、トランジスタTr4乃至Tr6と、容量素子C14とをそれぞれ有する。オフセットの電流を設定する際に、電流シンク回路104[j]において、トランジスタTr4は、電流I[j]が電流IREFよりも小さい場合に、電流I[j]と電流IREFの差分に相当する電流ICP[j]を生成する機能を有する。また、電流シンク回路104[j+1]において、トランジスタTr4は、電流I[j+1]が電流IREFよりも小さい場合に、電流I[j+1]と電流IREFの差分に相当する電流ICP[j+1]を生成する機能を有する。電流ICP[j]及び電流ICP[j+1]は、配線BL[j]及び配線BL[j+1]から電流シンク回路104[j]及び電流シンク回路104[j+1]に引き込まれる。

なお、電流ICM[j]と電流ICP[j]とが、Ioffset[j]に相当する。また、なお、電流ICM[j+1]と電流ICP[j+1]とが、Ioffset[j+1]に相当する。

そして、電流シンク回路104[j]及び電流シンク回路104[j+1]において、トランジスタTr4は、ソース又はドレインの一方が対応する配線BLに接続されており、ソース又はドレインの他方が所定の電位が供給される配線に接続されている。トランジスタTr5は、ソース又はドレインの一方が配線BLに接続されており、ソース又はドレインの他方がトランジスタTr4のゲートに接続されている。トランジスタTr6は、ソース又はドレインの一方がトランジスタTr4のゲートに接続されており、ソース又はドレインの他方が所定の電位が供給される配線に接続されている。容量素子C14は、第1の電極がトランジスタTr4のゲートに接続されており、第2の電極が所定の電位が供給される配線に接続されている。

トランジスタTr5のゲートは配線OSPに接続されており、トランジスタTr6のゲートは配線ORPに接続されている。

なお、図23では、トランジスタTr4乃至Tr6がnチャネル型である場合を例示している。

また、電流源回路105は、配線BLに対応したトランジスタTr10と、配線BLREFに対応したトランジスタTr11とを有する。具体的に、図23に示す電流源回路105は、トランジスタTr10として、配線BL[j]に対応したトランジスタTr10[j]と、配線BL[j+1]に対応したトランジスタTr10[j+1]とを有する場合を例示している。

トランジスタTr10のゲートは、トランジスタTr11のゲートに接続されている。また、トランジスタTr10は、ソース又はドレインの一方が対応する配線BLに接続されており、ソース又はドレインの他方が所定の電位が供給される配線に接続されている。トランジスタTr11は、ソース又はドレインの一方が配線BLREFに接続されており、ソース又はドレインの他方が所定の電位が供給される配線に接続されている。

トランジスタTr10とトランジスタTr11とは、同じ極性を有している。図23では、トランジスタTr10とトランジスタTr11とが、共にpチャネル型を有する場合を例示している。

トランジスタTr11のドレイン電流は電流IREFに相当する。そして、トランジスタTr10とトランジスタTr11とはカレントミラー回路としての機能を有するため、トランジスタTr10のドレイン電流は、トランジスタTr11のドレイン電流とほぼ同じ値、またはトランジスタTr11のドレイン電流に応じた値となる。

次いで、図24を用いて、積和演算回路100の具体的な動作の一例について説明する。

図24は、図23に示すメモリセルMC、メモリセルMCR、電流ソース回路103、電流シンク回路104、および電流源回路105の動作を示すタイミングチャートの一例に相当する。図24では、時刻T01乃至時刻T04において、メモリセルMC及びメモリセルMCRに第1のアナログ電流を格納する動作が行われる。時刻T05乃至時刻T10において、電流ソース回路103及び電流シンク回路104にオフセットの電流Ioffsetを設定する動作が行われる。時刻T11乃至時刻T16において、第1のアナログ電流と第2のアナログ電流との積和値に対応したデータを取得する動作が行われる。

なお、電源線VR[j]及び電源線VR[j+1]にはローレベルの電位が供給されるものとする。また、電流ソース回路103に接続される所定の電位を有する配線は、全てハイレベルの電位VDDが供給されるものとする。また、電流シンク回路104に接続される所定の電位を有する配線は、全てローレベルの電位VSSが供給されるものとする。また、電流源回路105に接続される所定の電位を有する配線は、全てハイレベルの電位VDDが供給されるものとする。

また、トランジスタTr1、Tr4、Tr7、Tr10[j]、Tr10[j+1]、Tr11は飽和領域で動作するものとする。

まず、時刻T01乃至時刻T02において、配線WW[i]にハイレベルの電位が与えられ、配線WW[i+1]にローレベルの電位が与えられる。上記動作により、図23に示すメモリセルMC[i、j]、メモリセルMC[i、j+1]、メモリセルMCR[i]においてトランジスタTr2がオンになる。また、メモリセルMC[i+1、j]、メモリセルMC[i+1、j+1]、メモリセルMCR[i+1]においてトランジスタTr2がオフの状態を維持する。

また、時刻T01乃至時刻T02では、図23に示す配線WD[j]と配線WD[j+1]とに、第1の参照電位VPRから第1のアナログ電位を差し引いた電位がそれぞれ与えられる。具体的に、配線WD[j]には電位VPR−Vx[i、j]が与えられ、配線WD[j+1]には電位VPR−Vx[i、j+1]が与えられる。また、配線WDREFには第1の参照電位VPRが与えられ、配線RW[i]及び配線RW[i+1]には基準電位として電位VSSと電位VDDの間の電位、例えば電位(VDD+VSS)/2が与えられる。

よって、図23に示すメモリセルMC[i、j]のノードN[i、j]にはトランジスタTr2を介して電位VPR−Vx[i、j]が与えられ、メモリセルMC[i、j+1]のノードN[i、j+1]にはトランジスタTr2を介して電位VPR−Vx[i、j+1]が与えられ、メモリセルMCR[i]のノードNREF[i]にはトランジスタTr2を介して電位VPRが与えられる。

時刻T02が終了すると、図23に示す配線WW[i]に与えられる電位はハイレベルからローレベルに変化し、メモリセルMC[i、j]、メモリセルMC[i、j+1]、メモリセルMCR[i]においてトランジスタTr2がオフになる。上記動作により、ノードN[i、j]には電位VPR−Vx[i、j]が保持され、ノードN[i、j+1]には電位VPR−Vx[i、j+1]が保持され、ノードNREF[i]には電位VPRが保持される。

次いで、時刻T03乃至時刻T04において、図23に示す配線WW[i]の電位はローレベルに維持され、配線WW[i+1]にハイレベルの電位が与えられる。上記動作により、図23に示すメモリセルMC[i+1、j]、メモリセルMC[i+1、j+1]、メモリセルMCR[i+1]においてトランジスタTr2がオンになる。また、メモリセルMC[i、j]、メモリセルMC[i、j+1]、メモリセルMCR[i]においてトランジスタTr2がオフの状態を維持する。

また、時刻T03乃至時刻T04では、図23に示す配線WD[j]と配線WD[j+1]とに、第1の参照電位VPRから第1のアナログ電位を差し引いた電位がそれぞれ与えられる。具体的に、配線WD[j]には電位VPR−Vx[i+1、j]が与えられ、配線WD[j+1]には電位VPR−Vx[i+1、j+1]が与えられる。また、配線WDREFには第1の参照電位VPRが与えられ、配線RW[i]及び配線RW[i+1]には基準電位として電位VSSと電位VDDの間の電位、例えば電位(VDD+VSS)/2が与えられる。

よって、図23に示すメモリセルMC[i+1、j]のノードN[i+1、j]にはトランジスタTr2を介して電位VPR−Vx[i+1、j]が与えられ、メモリセルMC[i+1、j+1]のノードN[i+1、j+1]にはトランジスタTr2を介して電位VPR−Vx[i+1、j+1]が与えられ、メモリセルMCR[i+1]のノードNREF[i+1]にはトランジスタTr2を介して電位VPRが与えられる。

時刻T04が終了すると、図23に示す配線WW[i+1]に与えられる電位はハイレベルからローレベルに変化し、メモリセルMC[i+1、j]、メモリセルMC[i+1、j+1]、メモリセルMCR[i+1]においてトランジスタTr2がオフになる。上記動作により、ノードN[i+1、j]には電位VPR−Vx[i+1、j]が保持され、ノードN[i+1、j+1]には電位VPR−Vx[i+1、j+1]が保持され、ノードNREF[i+1]には電位VPRが保持される。

次いで、時刻T05乃至時刻T06において、図23に示す配線ORP及び配線ORMにハイレベルの電位が与えられる。図23に示す電流ソース回路103[j]及び電流ソース回路103[j+1]では、配線ORMにハイレベルの電位が与えられることで、トランジスタTr9がオンになり、トランジスタTr7のゲートは電位VDDが与えられることでリセットされる。また、図23に示す電流シンク回路104[j]及び電流シンク回路104[j+1]では、配線ORPにハイレベルの電位が与えられることで、トランジスタTr6がオンになり、トランジスタTr4のゲートは電位VSSが与えられることでリセットされる。

時刻T06が終了すると、図23に示す配線ORP及び配線ORMに与えられる電位はハイレベルからローレベルに変化し、電流ソース回路103[j]及び電流ソース回路103[j+1]においてトランジスタTr9がオフになり、電流シンク回路104[j]及び電流シンク回路104[j+1]においてトランジスタTr6がオフになる。上記動作により、電流ソース回路103[j]及び電流ソース回路103[j+1]においてトランジスタTr7のゲートに電位VDDが保持され、電流シンク回路104[j]及び電流シンク回路104[j+1]においてトランジスタTr4のゲートに電位VSSが保持される。

次いで、時刻T07乃至時刻T08において、図23に示す配線OSPにハイレベルの電位が与えられる。また、図23に示す配線RW[i]及び配線RW[i+1]には基準電位として電位VSSと電位VDDの間の電位、例えば電位(VDD+VSS)/2が与えられる。配線OSPにハイレベルの電位が与えられることにより、電流シンク回路104[j]及び電流シンク回路104[j+1]においてトランジスタTr5がオンになる。

配線BL[j]に流れる電流I[j]が配線BLREFに流れる電流IREFよりも小さい場合、すなわち電流ΔI[j]が正の場合、図23に示すメモリセルMC[i、j]のトランジスタTr1が引き込むことのできる電流と、メモリセルMC[i+1、j]のトランジスタTr1が引き込むことのできる電流との和が、トランジスタTr10[j]のドレイン電流より小さいことを意味する。よって、電流ΔI[j]が正の場合、電流シンク回路104[j]においてトランジスタTr5がオンになると、トランジスタTr10[j]のドレイン電流の一部がトランジスタTr4のゲートに流れ込み、当該ゲートの電位が上昇し始める。そして、トランジスタTr4のドレイン電流が電流ΔI[j]とほぼ等しくなると、トランジスタTr4のゲートの電位は所定の値に収束する。このときのトランジスタTr4のゲートの電位は、トランジスタTr4のドレイン電流が電流ΔI[j]、すなわちIoffset[j](=ICP[j])となるような電位に相当する。つまり、電流シンク回路104[j]のトランジスタTr4は、電流ICP[j]を流し得る電流源に設定された状態であると言える。

同様に、配線BL[j+1]に流れる電流I[j+1]が配線BLREFに流れる電流IREFよりも小さい場合、つまり電流ΔI[j+1]が正の場合、電流シンク回路104[j+1]においてトランジスタTr5がオンになると、トランジスタTr10[j+1]のドレイン電流の一部がトランジスタTr4のゲートに流れ込み、当該ゲートの電位が上昇し始める。そして、トランジスタTr4のドレイン電流が電流ΔI[j+1]とほぼ等しくなると、トランジスタTr4のゲートの電位は所定の値に収束する。このときのトランジスタTr4のゲートの電位は、トランジスタTr4のドレイン電流が電流ΔI[j+1]、すなわちIoffset[j+1](=ICP[j+1])となるような電位に相当する。つまり、電流シンク回路104[j+1]のトランジスタTr4は、電流ICP[j+1]を流し得る電流源に設定された状態であると言える。

時刻T08が終了すると、図23に示す配線OSPに与えられる電位はハイレベルからローレベルに変化し、電流シンク回路104[j]及び電流シンク回路104[j+1]においてトランジスタTr5がオフになる。上記動作により、トランジスタTr4のゲートの電位は保持される。よって、電流シンク回路104[j]は電流ICP[j]を流し得る電流源に設定された状態を維持し、電流シンク回路104[j+1]は電流ICP[j+1]を流し得る電流源に設定された状態を維持する。

次いで、時刻T09乃至時刻T10において、図23に示す配線OSMにハイレベルの電位が与えられる。また、図23に示す配線RW[i]及び配線RW[i+1]には基準電位として電位VSSと電位VDDの間の電位、例えば電位(VDD+VSS)/2が与えられる。配線OSMにハイレベルの電位が与えられることにより、電流ソース回路103[j]及び電流ソース回路103[j+1]においてトランジスタTr8がオンになる。

配線BL[j]に流れる電流I[j]が配線BLREFに流れる電流IREFよりも大きい場合、すなわち電流ΔI[j]が負の場合、図23に示すメモリセルMC[i、j]のトランジスタTr1が引き込むことのできる電流と、メモリセルMC[i+1、j]のトランジスタTr1が引き込むことのできる電流との和が、トランジスタTr10[j]のドレイン電流より大きいことを意味する。よって、電流ΔI[j]が負の場合、電流ソース回路103[j]においてトランジスタTr8がオンになると、トランジスタTr7のゲートから配線BL[j]に電流が流れ出し、当該ゲートの電位が下降し始める。そして、トランジスタTr7のドレイン電流が電流ΔI[j]の絶対値とほぼ等しくなると、トランジスタTr7のゲートの電位は所定の値に収束する。このときのトランジスタTr7のゲートの電位は、トランジスタTr7のドレイン電流が電流ΔI[j]の絶対値、すなわちIoffset[j](=ICM[j])となるような電位に相当する。つまり、電流ソース回路103[j]のトランジスタTr7は、電流ICM[j]を流し得る電流源に設定された状態であると言える。

同様に、配線BL[j+1]に流れる電流I[j+1]が配線BLREFに流れる電流IREFよりも大きい場合、つまり電流ΔI[j+1]が負の場合、電流ソース回路103[j+1]においてトランジスタTr8がオンになると、トランジスタTr7のゲートから配線BL[j+1]に電流が流れ出し、当該ゲートの電位が下降し始める。そして、トランジスタTr7のドレイン電流が電流ΔI[j+1]の絶対値とほぼ等しくなると、トランジスタTr7のゲートの電位は所定の値に収束する。このときのトランジスタTr7のゲートの電位は、トランジスタTr7のドレイン電流が電流ΔI[j+1]の絶対値、すなわちIoffset[j+1](=ICM[j+1])となるような電位に相当する。つまり、電流ソース回路103[j+1]のトランジスタTr7は、電流ICM[j+1]を流し得る電流源に設定された状態であると言える。

時刻T08が終了すると、図23に示す配線OSMに与えられる電位はハイレベルからローレベルに変化し、電流ソース回路103[j]及び電流ソース回路103[j+1]においてトランジスタTr8がオフになる。上記動作により、トランジスタTr7のゲートの電位は保持される。よって、電流ソース回路103[j]は電流ICM[j]を流し得る電流源に設定された状態を維持し、電流ソース回路103[j+1]は電流ICM[j+1]を流し得る電流源に設定された状態を維持する。

なお、電流シンク回路104[j]及び電流シンク回路104[j+1]において、トランジスタTr4は電流を引き込む機能を有する。そのため、時刻T07乃至時刻T08において配線BL[j]に流れる電流I[j]が配線BLREFに流れる電流IREFよりも大きく電流ΔI[j]が負の場合、或いは、配線BL[j+1]に流れる電流I[j+1]が配線BLREFに流れる電流IREFよりも大きく電流ΔI[j+1]が負の場合、電流シンク回路104[j]または電流シンク回路104[j+1]から過不足なく配線BL[j]または配線BL[j+1]に電流を供給するのが難しくなる恐れがある。この場合、配線BL[j]または配線BL[j+1]に流れる電流と、配線BLREFに流れる電流とのバランスを取るために、メモリセルMCのトランジスタTr1と、電流シンク回路104[j]または電流シンク回路104[j+1]のトランジスタTr4と、トランジスタTr10[j]またはTr10[j+1]とが、共に飽和領域で動作することが困難になる可能性がある。

時刻T07乃至時刻T08において電流ΔI[j]が負の場合でも、トランジスタTr1、Tr4、Tr10[j]またはTr10[j+1]における飽和領域での動作を確保するために、時刻T05乃至時刻T06において、トランジスタTr7のゲートを電位VDDにリセットするのではなく、トランジスタTr7のゲートの電位を所定のドレイン電流が得られる程度の高さに設定しておいても良い。上記構成により、トランジスタTr10[j]またはTr10[j+1]のドレイン電流に加えてトランジスタTr7から電流が供給されるため、トランジスタTr1において引き込めない分の電流を、トランジスタTr4においてある程度引き込むことができるため、トランジスタTr1、Tr4、Tr10[j]またはTr10[j+1]における飽和領域での動作を確保することができる。

なお、時刻T09乃至時刻T10において、配線BL[j]に流れる電流I[j]が配線BLREFに流れる電流IREFよりも小さい場合、すなわち電流ΔI[j]が正の場合、時刻T07乃至時刻T08において電流シンク回路104[j]が電流ICP[j]を流し得る電流源に既に設定されているため、電流ソース回路103[j]においてトランジスタTr7のゲートの電位はほぼ電位VDDのままとなる。同様に、配線BL[j+1]に流れる電流I[j+1]が配線BLREFに流れる電流IREFよりも小さい場合、すなわち電流ΔI[j+1]が正の場合、時刻T07乃至時刻T08において電流シンク回路104[j+1]が電流ICP[j+1]を流し得る電流源に既に設定されているため、電流ソース回路103[j+1]においてトランジスタTr7のゲートの電位はほぼ電位VDDのままとなる。

次いで、時刻T11乃至時刻T12において、図23に示す配線RW[i]に第2のアナログ電位Vw[i]が与えられる。また、配線RW[i+1]には、基準電位として電位VSSと電位VDDの間の電位、例えば電位(VDD+VSS)/2が与えられたままである。具体的に、配線RW[i]の電位は、基準電位である電位VSSと電位VDDの間の電位、例えば電位(VDD+VSS)/2に対して電位差Vw[i]だけ高い電位となるが、以下説明を分かり易くするために、配線RW[i]の電位は電位Vw[i]であると仮定する。

配線RW[i]が電位Vw[i]になると、容量素子C11の第1の電極の電位の変化量がほぼノードNの電位の変化量に反映されるものと仮定すると、図23に示すメモリセルMC[i、j]におけるノードNの電位はVPR−Vx[i、j]+Vw[i]となり、メモリセルMC[i、j+1]におけるノードNの電位はVPR−Vx[i、j+1]+Vw[i]となる。そして、上記の式6から、メモリセルMC[i、j]に対応する第1のアナログ電流と第2のアナログ電流の積和値は、電流ΔI[j]からIoffset[j]を差し引いた電流、すなわち、配線BL[j]から流れ出る電流Iout[j]に反映されることが分かる。また、メモリセルMC[i、j+1]に対応する第1のアナログ電流と第2のアナログ電流の積和値は、電流ΔI[j+1]からIoffset[j+1]を差し引いた電流、すなわち、配線BL[j+1]から流れ出る電流Iout[j+1]に反映されることが分かる。

時刻T12が終了すると、配線RW[i]には、再度、基準電位である電位VSSと電位VDDの間の電位、例えば電位(VDD+VSS)/2が与えられる。

次いで、時刻T13乃至時刻T14において、図23に示す配線RW[i+1]に第2のアナログ電位Vw[i+1]が与えられる。また、配線RW[i]には、基準電位として電位VSSと電位VDDの間の電位、例えば電位(VDD+VSS)/2が与えられたままである。具体的に、配線RW[i+1]の電位は、基準電位である電位VSSと電位VDDの間の電位、例えば電位(VDD+VSS)/2に対して電位差Vw[i+1]だけ高い電位となるが、以下説明を分かり易くするために、配線RW[i+1]の電位は電位Vw[i+1]であると仮定する。

配線RW[i+1]が電位Vw[i+1]になると、容量素子C11の第1の電極の電位の変化量がほぼノードNの電位の変化量に反映されるものと仮定すると、図23に示すメモリセルMC[i+1、j]におけるノードNの電位はVPR−Vx[i+1、j]+Vw[i+1]となり、メモリセルMC[i+1、j+1]におけるノードNの電位はVPR−Vx[i+1、j+1]+Vw[i+1]となる。そして、上記の式6から、メモリセルMC[i+1、j]に対応する第1のアナログ電流と第2のアナログ電流の積和値は、電流ΔI[j]からIoffset[j]を差し引いた電流、すなわち、Iout[j]に反映されることが分かる。また、メモリセルMC[i+1、j+1]に対応する第1のアナログ電流と第2のアナログ電流の積和値は、電流ΔI[j+1]からIoffset[j+1]を差し引いた電流、すなわち、Iout[j+1]に反映されることが分かる。

時刻T14が終了すると、配線RW[i+1]には、再度、基準電位である電位VSSと電位VDDの間の電位、例えば電位(VDD+VSS)/2が与えられる。

次いで、時刻T15乃至時刻T16において、図23に示す配線RW[i]に第2のアナログ電位Vw[i]が与えられ、配線RW[i+1]に第2のアナログ電位Vw[i+1]が与えられる。具体的に、配線RW[i]の電位は、基準電位である電位VSSと電位VDDの間の電位、例えば電位(VDD+VSS)/2に対して電位差Vw[i]だけ高い電位となり、配線RW[i+1]の電位は、基準電位である電位VSSと電位VDDの間の電位、例えば電位(VDD+VSS)/2に対して電位差Vw[i+1]だけ高い電位となるが、以下説明を分かり易くするために、配線RW[i]の電位は電位Vw[i]であり、配線RW[i+1]の電位は電位Vw[i+1]であると仮定する。

配線RW[i]の電位が電位Vw[i]になると、容量素子C11の第1の電極の電位の変化量がほぼノードNの電位の変化量に反映されるものと仮定すると、図23に示すメモリセルMC[i、j]におけるノードNの電位はVPR−Vx[i、j]+Vw[i]となり、メモリセルMC[i、j+1]におけるノードNの電位はVPR−Vx[i、j+1]+Vw[i]となる。また、配線RW[i+1]の電位が電位Vw[i+1]になると、容量素子C11の第1の電極の電位の変化量がほぼノードNの電位の変化量に反映されるものと仮定すると、図23に示すメモリセルMC[i+1、j]におけるノードNの電位はVPR−Vx[i+1、j]+Vw[i+1]となり、メモリセルMC[i+1、j+1]におけるノードNの電位はVPR−Vx[i+1、j+1]+Vw[i+1]となる。

そして、上記の式6から、メモリセルMC[i、j]とメモリセルMC[i+1、j]とに対応する第1のアナログ電流と第2のアナログ電流の積和値は、電流ΔI[j]からIoffset[j]を差し引いた電流、すなわち、電流Iout[j]に反映されることが分かる。また、メモリセルMC[i、j+1]とメモリセルMC[i+1、j+1]とに対応する第1のアナログ電流と第2のアナログ電流の積和値は、電流ΔI[j+1]からIoffset[j+1]を差し引いた電流、すなわち、電流Iout[j+1]に反映されることが分かる。

時刻T16が終了すると、配線RW[i]及び配線RW[i+1]には、再度、基準電位である電位VSSと電位VDDの間の電位、例えば電位(VDD+VSS)/2が与えられる。

上記構成により、積和演算を小さな回路規模で行うことができる。また、上記構成により、積和演算を高速で行うことができる。また、上記構成により、低消費電力で積和演算を行うことができる。

なお図22乃至図24で説明した積和演算回路の回路構成はあくまで一例であり、本発明の一態様を実現可能であれば任意の構成とすることができる。

なお、トランジスタTr2、Tr5、Tr6、Tr8、またはTr9は、オフ電流の著しく低いトランジスタを用いることが望ましい。トランジスタTr2にオフ電流の著しく低いトランジスタを用いることにより、ノードNの電位の保持を長時間に渡って行うことができる。また、トランジスタTr5及びTr6にオフ電流の著しく低いトランジスタを用いることにより、トランジスタTr4のゲートの電位の保持を、長時間に渡って行うことができる。また、トランジスタTr8及びTr9にオフ電流の著しく低いトランジスタを用いることにより、トランジスタTr7のゲートの電位の保持を、長時間に渡って行うことができる。

トランジスタのオフ電流を下げるには、例えば、チャネル形成領域をエネルギーギャップが広い半導体で形成すればよい。半導体のエネルギーギャップは、2.5eV以上、または2.7eV以上、または3eV以上であることが好ましい。このような半導体材料として酸化物半導体が挙げられる。トランジスタTr2、Tr5、Tr6、Tr8、またはTr9として、チャネル形成領域に酸化物半導体を含むトランジスタを用いればよい。チャネル幅で規格化したOSトランジスタのリーク電流は、ソースドレイン電圧が10V、室温(25℃程度)の状態で10×10−21A/μm(10ゼプトA/μm)以下とすることが可能である。トランジスタTr2、Tr5、Tr6、Tr8、またはTr9に適用されるOSトランジスタのリーク電流は、室温(25℃程度)にて1×10−18A以下、または、1×10−21A以下、または1×10−24A以下が好ましい。または、リーク電流は85℃にて1×10−15A以下、または1×10−18A以下、または1×10−21A以下であることが好ましい。

酸化物半導体はエネルギーギャップが大きく、電子が励起されにくく、ホールの有効質量が大きい半導体である。このため、チャネル形成領域に酸化物半導体を含むトランジスタは、シリコン等を用いた一般的なトランジスタと比較して、アバランシェ崩壊等が生じにくい場合がある。アバランシェ崩壊に起因するホットキャリア劣化等が抑制されることで、チャネル形成領域に酸化物半導体を含むトランジスタは高いドレイン耐圧を有することとなり、高いドレイン電圧で駆動することが可能である。

トランジスタのチャネル形成領域に含まれる酸化物半導体は、インジウム(In)および亜鉛(Zn)の少なくとも一方を含む酸化物半導体であることが好ましい。このような酸化物半導体としては、In酸化物、Zn酸化物、In−Zn酸化物、In−M−Zn酸化物(元素Mは、Ga、Al、Ti、Y、Zr、La、Ce、Nd、またはHf)が代表的である。これら酸化物半導体は、電子供与体(ドナー)となる水素などの不純物を低減し、かつ酸素欠損も低減することで、酸化物半導体をi型半導体(真性半導体)にする、あるいはi型半導体に限りなく近づけることができる。このような酸化物半導体は、高純度化された酸化物半導体と呼ぶことができる。

チャネル形成領域を、キャリア密度の低い酸化物半導体で形成することが好ましい。酸化物半導体のキャリア密度は、例えば、8×1011/cm3未満1×10−9/cm3以上であるとよい。キャリア密度は、1×1011/cm3未満が好ましく、1×1010/cm3未満がさらに好ましい。

<ニューラルネットワーク>

次に、ニューラルネットワークの構成例について説明を行う。ここでは、ニューラルネットワークの種類の一つである、階層型ニューラルネットワークについて説明する。

図25は、階層型ニューラルネットワークの一例を示した図である。第(k−1)層(kは2以上の整数である)は、ニューロンをP個(Pは1以上の整数である)有し、第k層は、ニューロンをQ個(Qは1以上の整数である)有し、第(k+1)層は、ニューロンをR個(Rは1以上の整数である)有する。

第(k−1)層の第pニューロン(pは1以上P以下の整数である)の出力信号zp (k−1)と重み係数wqp (k)と、の積が第k層の第qニューロン(qは1以上Q以下の整数である)に入力されるものとし、第k層の第qニューロンの出力信号zq (k)と重み係数wrq (k+1)と、の積が第(k+1)層の第rニューロン(rは1以上R以下の整数である)に入力されるものとし、第(k+1)層の第rニューロンの出力信号をzr (k+1)とする。

このとき、第k層の第qニューロンへ入力される信号の総和は、次の式(D1)で表される。

また、第k層の第qニューロンからの出力信号zq (k)を次の式(D2)で定義する。

関数f(uq (k))は、ニューロンの出力関数であり、ステップ関数、線形ランプ関数、又はシグモイド関数などを用いることができる。なお、式(D1)の積和演算は、先述した積和演算回路によって実現できる。なお、式(D2)の演算は、例えば、図28(A)に示す回路411によって実現できる。

なお、ニューロンの出力関数は、全てのニューロンにおいて同一でもよいし、又は異なっていてもよい。加えて、ニューロンの出力関数は、層毎において、同一でもよいし、異なっていてもよい。

ここで、図26に示す、全L層からなる階層型ニューラルネットワークを考える(つまり、ここでのkは2以上(L−1)以下の整数とする)。第1層は、階層型ニューラルネットワークの入力層となり、第L層は、階層型ニューラルネットワークの出力層となり、第2層乃至第(L−1)層は、隠れ層となる。

第1層(入力層)は、ニューロンをP個有し、第k層(隠れ層)は、ニューロンをQ[k]個(Q[k]は1以上の整数である)有し、第L層(出力層)は、ニューロンをR個有する。

第1層の第s[1]ニューロン(s[1]は1以上P以下の整数である)の出力信号をzs[1] (1)とし、第k層の第s[k]ニューロン(s[k]は1以上Q[k]以下の整数である)の出力信号をzs[k] (k)とし、第L層の第s[L]ニューロン(s[L]は1以上R以下の整数である)の出力信号をzs[L] (L)とする。

また、第(k−1)層の第s[k−1]ニューロン(s[k−1]は1以上Q[k−1]以下の整数である)の出力信号zs[k−1] (k−1)と重み係数ws[k]s[k−1] (k)と、の積us[k] (k)が第k層の第s[k]ニューロンに入力されるものとし、第(L−1)層の第s[L−1]ニューロン(s[L−1]は1以上Q[L−1]以下の整数である)の出力信号zs[L−1] (L−1)と重み係数ws[L]s[L−1] (L)と、の積us[L] (L)が第L層の第s[L]ニューロンに入力されるものとする。

次に、教師付き学習について説明する。教師付き学習とは、上述の階層型ニューラルネットワークの機能において、出力した結果と、所望の結果(教師データ、又は教師信号という場合がある)が異なったときに、階層型ニューラルネットワークの全ての重み係数を、出力した結果と所望の結果とに基づいて、更新する動作をいう。

教師付き学習の具体例として、逆伝播誤差方式による学習方法について説明する。図27は、逆伝播誤差方式による学習方法を説明する図である。逆伝播誤差方式は、階層型ニューラルネットワークの出力と教師データとの誤差が小さくなるように、重み係数を変更する方式である。

例えば、第1層の第s[1]ニューロンに入力データを入力し、第L層の第s[L]ニューロンから出力データzs[L] (L)が出力されたとする。ここで、出力データzs[L] (L)に対する教師信号をts[L]としたとき、誤差エネルギーEは、出力データzs[L] (L)及び教師信号ts[L]によって表すことができる。

誤差エネルギーEに対して、第k層の第s[k]ニューロンの重み係数ws[k]s[k−1] (k)の更新量を∂E/∂ws[k]s[k−1] (k)とすることで、新たに重み係数を変更することができる。ここで、第k層の第s[k]ニューロンの出力値zs[k] (k)の誤差δs[k] (k)を∂E/∂us[k] (k)と定義すると、δs[k] (k)及び∂E/∂ws[k]s[k−1] (k)は、それぞれ次の式(D3)、(D4)で表すことができる。

f’(us[k] (k))は、ニューロン回路の出力関数の導関数である。なお、式(D3)の演算は、例えば、図28(B)に示す回路413によって実現できる。また、式(D4)の演算は、例えば、図28(C)に示す回路414によって実現できる。出力関数の導関数は、例えば、オペアンプの出力端子に所望の導関数に対応した演算回路を接続することによって実現できる。

また、例えば、式(D3)のΣws[k+1]・s[k] (k+1)・δs[k+1] (k+1)の部分の演算は、前述した積和演算回路によって実現できる。

ここで、第(k+1)層が出力層のとき、すなわち、第(k+1)層が第L層であるとき、δs[L] (L)及び∂E/∂ws[L]s[L−1] (L)は、それぞれ次の式(D5)、(D6)で表すことができる。

式(D5)の演算は、図28(D)に示す回路415によって実現できる。また、式(D6)の演算は、図28(C)に示す回路414によって実現できる。

つまり、式(D1)乃至式(D6)により、全てのニューロン回路の誤差δs[k] (k)及びδs[L] (L)を求めることができる。なお、重み係数の更新は、誤差δs[k] (k)、δs[L] (L)及び所望のパラメータなどに基づいて、設定される。

以上のように、図22および図23に示す積和演算回路を用いることによって、教師付き学習を適用した階層型ニューラルネットワークの計算を行うことができる。

具体的には、図22および図23に示す積和演算回路において、第1アナログデータを重み係数として、複数の第2アナログデータをニューロン出力に対応することで、各ニューロン出力の重み付け和演算を並列して行うことができ、当該出力信号として重み付け演算の結果に対応したデータ、すなわちシナプス入力を取得することができる。具体的には、メモリセルMC[1,j]乃至メモリセルMC[m,j]に、第k層の第s[k]ニューロンの重み係数ws[k]・1 (k)乃至ws[k]・Q[k−1] (k)を第1アナログデータとして格納し、配線RW[1]乃至配線RW[m]にそれぞれ第(k−1)層の各ニューロンの出力信号z1・s[k] (k−1)乃至zQ[k−1]・s[k] (k−1)を第2アナログデータとして供給することで、第k層の第s[k]ニューロンに入力される信号の総和us[k] (k)を計算することができる。つまり、式(D1)に示した積和演算を積和演算回路によって実現することができる。

また、教師付き学習で重み係数の更新を行うとき、メモリセルMC[1,j]乃至メモリセルMC[m,j]に、第k層の第s[k]ニューロンから第(k+1)層の各ニューロンに信号が送られるときに掛かる重み係数w1・s[k] (k+1)乃至wQ[k+1]s[k] (k+1)を第1アナログデータとして格納し、配線RW[1]乃至配線RW[m]に第(k+1)層の各ニューロンの誤差δ1 (k+1)乃至δQ[k+1] (k+1)を第2アナログデータとして供給すると、式(D3)におけるΣws[k+1]・s[k] (k+1)・δs[k+1] (k+1)の値を、配線BL[j]に流れる差分電流ΔI[j]から得ることができる。つまり、式(D3)に示した演算の一部を積和演算回路によって実現することができる。

(実施の形態5)

以下では、本発明の一態様で開示されるトランジスタに用いることができるCAC−OSの構成について説明する。

<CAC−OSの構成>

CAC−OSとは、例えば、酸化物半導体を構成する元素が、0.5nm以上10nm以下、好ましくは、1nm以上2nm以下、またはその近傍のサイズで偏在した材料の一構成である。なお、以下では、酸化物半導体において、一つあるいはそれ以上の金属元素が偏在し、該金属元素を有する領域が、0.5nm以上10nm以下、好ましくは、1nm以上2nm以下、またはその近傍のサイズで混合した状態をモザイク状、またはパッチ状ともいう。

なお、酸化物半導体は、少なくともインジウムを含むことが好ましい。特にインジウムおよび亜鉛を含むことが好ましい。また、それらに加えて、アルミニウム、ガリウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種が含まれていてもよい。

例えば、In−Ga−Zn酸化物におけるCAC−OS(CAC−OSの中でもIn−Ga−Zn酸化物を、特にCAC−IGZOと呼称してもよい)とは、インジウム酸化物(以下、InOX1(X1は0よりも大きい実数)とする)、またはインジウム亜鉛酸化物(以下、InX2ZnY2OZ2(X2、Y2、およびZ2は0よりも大きい実数)とする)と、ガリウム酸化物(以下、GaOX3(X3は0よりも大きい実数)とする)、またはガリウム亜鉛酸化物(以下、GaX4ZnY4OZ4(X4、Y4、およびZ4は0よりも大きい実数)とする)などと、に材料が分離することでモザイク状となり、モザイク状のInOX1、またはInX2ZnY2OZ2が、膜中に均一に分布した構成(以下、クラウド状ともいう)である。

つまり、CAC−OSは、GaOX3が主成分である領域と、InX2ZnY2OZ2、またはInOX1が主成分である領域とが、混合している構成を有する複合酸化物半導体である。なお、本明細書において、例えば、第1の領域の元素Mに対するInの原子数比が、第2の領域の元素Mに対するInの原子数比よりも大きいことを、第1の領域は、第2の領域と比較して、Inの濃度が高いとする。

なお、IGZOは通称であり、In、Ga、Zn、およびOによる1つの化合物をいう場合がある。代表例として、InGaO3(ZnO)m1(m1は自然数)、またはIn(1+x0)Ga(1−x0)O3(ZnO)m0(−1≦x0≦1、m0は任意数)で表される結晶性の化合物が挙げられる。

上記結晶性の化合物は、単結晶構造、多結晶構造、またはCAAC(C−Axis Aligned Crystalline Oxide Semiconductor、または、C−Axis Aligned and A−B−plane Anchored Crystalline Oxide Semiconductor)構造を有する。なお、CAAC構造とは、複数のIGZOのナノ結晶がc軸配向を有し、かつa−b面においては配向せずに連結した結晶構造である。

一方、CAC−OSは、酸化物半導体の材料構成に関する。CAC−OSとは、In、Ga、Zn、およびOを含む材料構成において、一部にGaを主成分とするナノ粒子状に観察される領域と、一部にInを主成分とするナノ粒子状に観察される領域とが、それぞれモザイク状にランダムに分散している構成をいう。従って、CAC−OSにおいて、結晶構造は副次的な要素である。

なお、CAC−OSは、組成の異なる二種類以上の膜の積層構造は含まないものとする。例えば、Inを主成分とする膜と、Gaを主成分とする膜との2層からなる構造は、含まない。

なお、GaOX3が主成分である領域と、InX2ZnY2OZ2、またはInOX1が主成分である領域とは、明確な境界が観察できない場合がある。

なお、ガリウムの代わりに、アルミニウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種が含まれている場合、CAC−OSは、一部に該金属元素を主成分とするナノ粒子状に観察される領域と、一部にInを主成分とするナノ粒子状に観察される領域とが、それぞれモザイク状にランダムに分散している構成をいう。

CAC−OSは、例えば基板を意図的に加熱しない条件で、スパッタリング法により形成することができる。また、CAC−OSをスパッタリング法で形成する場合、成膜ガスとして、不活性ガス(代表的にはアルゴン)、酸素ガス、及び窒素ガスの中から選ばれたいずれか一つまたは複数を用いればよい。また、成膜時の成膜ガスの総流量に対する酸素ガスの流量比は低いほど好ましく、例えば酸素ガスの流量比を0%以上30%未満、好ましくは0%以上10%以下とすることが好ましい。

CAC−OSは、X線回折(XRD:X−ray diffraction)測定法のひとつであるOut−of−plane法によるθ/2θスキャンを用いて測定したときに、明確なピークが観察されないという特徴を有する。すなわち、X線回折から、測定領域のa−b面方向、およびc軸方向の配向は見られないことが分かる。

またCAC−OSは、プローブ径が1nmの電子線(ナノビーム電子線ともいう)を照射することで得られる電子線回折パターンにおいて、リング状に輝度の高い領域と、該リング領域に複数の輝点が観測される。従って、電子線回折パターンから、CAC−OSの結晶構造が、平面方向、および断面方向において、配向性を有さないnc(nano−crystal)構造を有することがわかる。

また例えば、In−Ga−Zn酸化物におけるCAC−OSでは、エネルギー分散型X線分光法(EDX:Energy Dispersive X−ray spectroscopy)を用いて取得したEDXマッピングにより、GaOX3が主成分である領域と、InX2ZnY2OZ2、またはInOX1が主成分である領域とが、偏在し、混合している構造を有することが確認できる。

CAC−OSは、金属元素が均一に分布したIGZO化合物とは異なる構造であり、IGZO化合物と異なる性質を有する。つまり、CAC−OSは、GaOX3などが主成分である領域と、InX2ZnY2OZ2、またはInOX1が主成分である領域と、に互いに相分離し、各元素を主成分とする領域がモザイク状である構造を有する。

ここで、InX2ZnY2OZ2、またはInOX1が主成分である領域は、GaOX3などが主成分である領域と比較して、導電性が高い領域である。つまり、InX2ZnY2OZ2、またはInOX1が主成分である領域を、キャリアが流れることにより、酸化物半導体としての導電性が発現する。従って、InX2ZnY2OZ2、またはInOX1が主成分である領域が、酸化物半導体中にクラウド状に分布することで、高い電界効果移動度(μ)が実現できる。

一方、GaOX3などが主成分である領域は、InX2ZnY2OZ2、またはInOX1が主成分である領域と比較して、絶縁性が高い領域である。つまり、GaOX3などが主成分である領域が、酸化物半導体中に分布することで、リーク電流を抑制し、良好なスイッチング動作を実現できる。

従って、CAC−OSを半導体素子に用いた場合、GaOX3などに起因する絶縁性と、InX2ZnY2OZ2、またはInOX1に起因する導電性とが、相補的に作用することにより、高いオン電流(Ion)、および高い電界効果移動度(μ)を実現することができる。

また、CAC−OSを用いた半導体素子は、信頼性が高い。従って、CAC−OSは、ディスプレイをはじめとするさまざまな半導体装置に最適である。

なお、本実施の形態は、少なくともその一部を本明細書で示す他の実施の形態と適宜組み合わせて実施することができる。