JP2014170110A - 制御装置、電気光学装置、電子機器および制御方法 - Google Patents

制御装置、電気光学装置、電子機器および制御方法 Download PDFInfo

- Publication number

- JP2014170110A JP2014170110A JP2013041813A JP2013041813A JP2014170110A JP 2014170110 A JP2014170110 A JP 2014170110A JP 2013041813 A JP2013041813 A JP 2013041813A JP 2013041813 A JP2013041813 A JP 2013041813A JP 2014170110 A JP2014170110 A JP 2014170110A

- Authority

- JP

- Japan

- Prior art keywords

- gradation

- voltage

- display element

- period

- memory display

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/3433—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using light modulating elements actuated by an electric field and being other than liquid crystal devices and electrochromic devices

- G09G3/344—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using light modulating elements actuated by an electric field and being other than liquid crystal devices and electrochromic devices based on particles moving in a fluid or in a gas, e.g. electrophoretic devices

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/06—Details of flat display driving waveforms

- G09G2310/061—Details of flat display driving waveforms for resetting or blanking

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2340/00—Aspects of display data processing

- G09G2340/16—Determination of a pixel data signal depending on the signal applied in the previous frame

Abstract

【解決手段】画像データに従った電圧を記憶性表示素子に印加させるように、記憶性表示素子を駆動する駆動回路を制御する。記憶性表示素子の光学状態を画像データにより示される階調とするために、消去期間、リセット期間、および書き込み期間を含む複数の単位期間における電圧印加のパターンに従った電圧を印加させ、パターンは、各単位期間において第1電圧および第2電圧のうち第1階調から第2階調を経て第1階調に戻る方向に階調変化させる電圧を印加するパターンであり、当該階調が第1階調および第2階調の中間階調である場合には、書き込み期間において第1階調から第2階調への遷移により当該記憶性表示素子に当該階調を表示させる。

【選択図】図3

Description

これに対し本発明は、記憶性表示素子において3階調以上の多階調表示を行う場合に、中間階調の再現性を改善する技術を提供する。

この制御装置によれば、記憶性表示素子において3階調以上の多階調表示を行う場合に、中間階調の再現性を改善することができる。

この電気光学装置によれば、記憶性表示素子において3階調以上の多階調表示を行う場合に、中間階調の再現性を改善することができる。

この電子機器によれば、記憶性表示素子において3階調以上の多階調表示を行う場合に、中間階調の再現性を改善することができる。

この制御方法によれば、記憶性表示素子において3階調以上の多階調表示を行う場合に、中間階調の再現性を改善することができる。

1−1.概要

一実施形態に係る装置の具体的構成および動作の説明に先立ち、駆動原理を説明する。ここでは、電気光学素子としてEPD(Electro Phoretic Display)が用いられ、各画素で4階調表示を行う例を説明する。

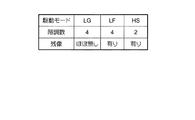

EPDは、素子そのものの応答速度が本質的に(液晶ディスプレイなどと比較して)遅いという問題を抱えている。残像が出ないように高品質の書き換えを行うと、10インチ程度の大きさの画面を書き換えるのに数秒オーダーの時間がかかってしまう。書き換えを高速化する種々の技術が開発されているが、書き換えを高速化すると残像が出てしまう。このように、EPDの駆動において書き換え速度と残像とはトレードオフの関係にあり、書き換え速度が速くかつ残像が無い駆動を行うことは非常に困難である。そこで、本実施形態においては、それぞれ書き換え速度が異なる3つの駆動モードが用意され、状況に応じてこれらが使い分けられる。

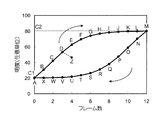

図4は、LGモードにおける駆動波形および階調変化を例示する図である。図4(A)はLGモードにおける階調変化を示している。図4(B)は、LGモードの駆動波形のうち、現階調および次階調がダークグレーおよびライトグレーである場合の駆動波形を示している。図4(A)および(B)において、横軸はともにフレーム数を表している。図4(A)の縦軸はEPDの明度を表している。図4(B)の縦軸は印加電圧を表している。

図5は、LFモードにおける駆動波形および階調変化を例示する図である。図5(A)はLFモードにおける階調変化を示している。図5(B)は、LFモードの駆動波形のうち、現階調および次階調がダークグレーおよびライトグレーである場合の駆動波形を示している。縦軸および横軸は図4と同様である。

図6は、HSモードにおける駆動波形および階調変化を例示する図である。図6(A)はHSモードにおける階調変化を示している。図6(B)は、HSモードの駆動波形のうち、現階調および次階調が白および黒である場合の駆動波形を示している。縦軸および横軸は図4および図5と同様である。

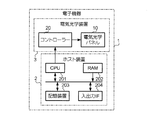

図7は、一実施形態に係る電子機器1の構成を示す図である。電子機器1は、ホスト装置2と、電気光学装置3とを有する。電気光学装置3は、ホスト装置2の制御下で画像を表示する装置であり、電気光学パネル10およびコントローラー20を有する。この例で、電気光学パネル10は、電圧の印加等によりエネルギーを与えなくても表示を保持する記憶性の表示素子として、電気泳動粒子を用いた表示素子を有する。この表示素子により、電気光学パネル10は、モノクロ複数階調(この例では黒、ダークグレー、ライトグレー、および白の4階調)の像を表示する。コントローラー20は、電気光学パネル10を制御する制御装置である。ホスト装置2は、電気光学装置3を制御する装置であり、CPU(Central Processing Unit)201、RAM(Random Access Memory)202、記憶装置203、および入出力インターフェース204を有する。CPU201は、RAM202をワークエリアとして、ROM(Read Only Memory、図示略)または記憶装置203に記憶されているプログラムを実行する。RAM202は、データを記憶する揮発性のメモリーである。記憶装置203は、各種のデータおよびアプリケーションプログラムを記憶する記憶装置であり、フラッシュメモリーなど不揮発性のメモリーを有する。入出力インターフェース204は、各種の入力装置または電気光学装置3などの出力装置との間でデータを入力または出力するためのインターフェースである。電子機器1は、例えば、電子書籍リーダー、計測器、電子POP装置などである。

図13は、電子機器1の一実施形態に係る動作を示すフローチャートである。電子機器1において、CPU201はプログラムを実行しており、このプログラムの実行において所定のイベントが発生したことを契機として、図12のフローが開始される。

本発明は上述の実施形態に限定されるものではなく、種々の変形実施が可能である。以下、変形例をいくつか説明する。以下の変形例のうち2つ以上のものが組み合わせて用いられてもよい。

コントローラー20に実装される駆動モードの数は3つに限定されない。コントローラー20には、実施形態で説明したLGモードおよびLFモードのうち少なくとも1つが実装されていればよい。また、実施形態で説明した3つの駆動モードに加え、さらに別の駆動モードが追加されてもよい。

消去期間の終期におけるEPDの階調は第2階調(実施形態では黒)に限定されない。消去期間は、EPDの階調を第1階調にする期間であってもよい。

LGモードおよびLFモードにおいて実施形態で説明したループの回転数はあくまで例示であって、ループの回転数はこれに限定されない。LFモードにおけるループの回転数は少なくとも0.5回転あれば、これ以上であってもよい。

実施形態においては、基本フレーム数および階調フレーム数がすべての駆動モードにおいて共通である例を説明したが、基本フレーム数および階調フレーム数のうち少なくとも一方は、駆動モード毎に定義されていてもよい。

実施形態においては、第1階調が白であり第2階調が黒である例を説明したが、第1階調および第2階調はこれに限定されない。この場合において、第1階調から第2階調への遷移が、第2階調から第1階調への遷移よりも遅い(応答速度が遅い)ことが好ましい。実施形態においては、書き込み期間においては、第1階調(白)から第2階調(黒)への遷移を使って中間階調の表現をする例を説明した。応答速度が遅い遷移を使って階調表現をすることにより、中間階調の合わせ込みをより高精度で行うことができる。

コントローラー20の構成は図11で例示したものに限定されない。例えば、コントローラー20はVRAM21およびVRAM22を有しておらず、VRAM21およびVRAM22はコントローラー20の外部に設けられてもよい。LUT24、レジスター23、およびレジスター27についても同様である。

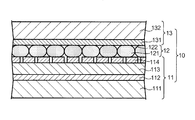

画素14の等価回路は、実施形態で説明されたものに限定されない。画素電極114と共通電極131との間に制御された電圧を印加できる構成であれば、スイッチング素子および容量素子はどのように組み合わせられてもよい。また、この画素を駆動する方法は、単一のフレームにおいて、印加電圧の極性が異なる電気泳動素子143が存在する両極駆動、または、単一のフレームにおいてはすべての電気泳動素子143において同一の極性の電圧が印加される片極駆動のいずれであってもよい。

Claims (11)

- 第1電圧の印加によって第1階調から第2階調に光学状態が遷移し、第2電圧の印加によって前記第2階調から前記第1階調に光学状態が遷移する記憶性表示素子に表示させる画像を示す画像データを取得する取得手段と、

前記画像データに従った電圧を前記記憶性表示素子に印加させるように、当該記憶性表示素子を駆動する駆動回路を制御する制御手段であって、当該記憶性表示素子の光学状態を前記画像データにより示される階調とするために、消去期間、リセット期間、および書き込み期間を含む複数の期間における電圧印加のパターンに従った電圧を印加させ、前記パターンは、単位期間において前記第1電圧および前記第2電圧のうち前記第2階調から前記第1階調を経て前記第2階調に戻るループに沿って階調変化させる電圧を印加するパターンであり、当該階調が前記第1階調および前記第2階調の中間階調である場合には、前記書き込み期間において前記第1階調から前記第2階調への遷移により当該記憶性表示素子に当該階調を表示させる制御手段と

を有する制御装置。 - 前記消去期間は、当該消去期間の終期において前記記憶性表示素子が前記第2階調となる電圧を印加する期間である

ことを特徴とする請求項1に記載の制御装置。 - 前記リセット期間は、前記ループを0.5回以上実現させる電圧を印加する期間である

ことを特徴とする請求項1または2に記載の制御装置。 - 前記パターンは、一の階調について、前記ループの回数が異なる複数の駆動モードに応じたパターンを含む

ことを特徴とする請求項3に記載の制御装置。 - 前記パターンは、前記記憶性表示素子に前記第1階調または前記第2階調のどちらかを表示させるため、前記第1階調から前記第2階調に、または前記第2階調から前記第1階調に直接遷移させる電圧を印加する駆動モードを含む複数の駆動モードに応じたパターンを含む

ことを特徴とする請求項1ないし4のいずれか一項に記載の制御装置。 - 前記第1階調から前記第2階調へ遷移させる期間の時間長および前記第2階調から前記第1階調へ遷移させる期間の時間長が、それぞれ、前記複数の駆動モードにおいて共通である

ことを特徴とする請求項4または5に記載の制御装置。 - 前記第1階調から前記第2階調への遷移が、前記第2階調から前記第1階調への遷移よりも遅い

ことを特徴とする請求項1ないし6のいずれか一項に記載の制御装置。 - 前記記憶性表示素子に現在表示されている画像を示す現データを記憶する第1記憶手段と、

前記記憶性表示素子に次に表示させる画像を示す次データを記憶する第2記憶手段と、

前記パターンに含まれる複数の単位期間のうち電圧印加が終了した単位期間の数をカウントするカウント手段と、

書き換え前の階調値、書き換え後の階調値、並びに当該書き換え前の階調値および当該書き換え後の階調値に対応する電圧印加のパターンを、複数の階調値の各々について記憶した第3記憶手段と

を有し、

前記取得手段は、前記第1記憶手段から前記現データを、前記第2記憶手段から次データをそれぞれ取得し、

前記制御手段は、前記第3記憶手段に記憶されている複数のパターンにより示される電圧のうち、前記取得手段により取得された前記現データおよび前記次データ、並びに前記カウント手段によりカウントされている数に相当する単位期間に印加すべき電圧を前記記憶性表示素子に印加させるように、前記記憶性表示素子を駆動する駆動回路を制御する

ことを特徴とする請求項1ないし7のいずれか一項に記載の制御装置。 - 第1電圧の印加によって第1階調から第2階調に光学状態が遷移し、第2電圧の印加によって前記第2階調から前記第1階調に光学状態が遷移する記憶性表示素子と、

前記記憶性表示素子に表示させる画像を示す画像データを取得する取得手段と、

前記画像データに従った電圧を前記記憶性表示素子に印加させるように、当該記憶性表示素子を駆動する駆動回路を制御する制御手段であって、当該記憶性表示素子の光学状態を前記画像データにより示される階調とするために、消去期間、リセット期間、および書き込み期間を含む複数の期間における電圧印加のパターンに従った電圧を印加させ、前記パターンは、単位期間において前記第1電圧および前記第2電圧のうち前記第2階調から前記第1階調を経て前記第2階調に戻るループ沿って階調変化させる電圧を印加するパターンであり、当該階調が前記第1階調および前記第2階調の中間階調である場合には、前記書き込み期間において前記第1階調から前記第2階調への遷移により当該記憶性表示素子に当該階調を表示させる制御手段と

を有する電気光学装置。 - 請求項9に記載の電気光学装置を有する電子機器。

- 第1電圧の印加によって第1階調から第2階調に光学状態が遷移し、第2電圧の印加によって前記第2階調から前記第1階調に光学状態が遷移する記憶性表示素子に表示させる画像を示す画像データを取得するステップと、

前記画像データに従った電圧を前記記憶性表示素子に印加させるように、当該記憶性表示素子を駆動する駆動回路を制御するステップと、

当該記憶性表示素子の光学状態を前記画像データにより示される階調とするために、消去期間、リセット期間、および書き込み期間を含む複数の期間における電圧印加のパターンに従った電圧を印加させ、前記パターンは、単位期間において前記第1電圧および前記第2電圧のうち前記第2階調から前記第1階調を経て前記第2階調に戻るループに沿って階調変化させる電圧を印加するパターンであり、当該階調が前記第1階調および前記第2階調の中間階調である場合には、前記書き込み期間において前記第1階調から前記第2階調への遷移により当該記憶性表示素子に当該階調を表示させるステップと

を有する電気光学装置の制御方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013041813A JP2014170110A (ja) | 2013-03-04 | 2013-03-04 | 制御装置、電気光学装置、電子機器および制御方法 |

| US14/193,942 US20140247290A1 (en) | 2013-03-04 | 2014-02-28 | Control apparatus, electro-optical apparatus, electronic device, and control method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013041813A JP2014170110A (ja) | 2013-03-04 | 2013-03-04 | 制御装置、電気光学装置、電子機器および制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014170110A true JP2014170110A (ja) | 2014-09-18 |

| JP2014170110A5 JP2014170110A5 (ja) | 2016-04-21 |

Family

ID=51420768

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013041813A Withdrawn JP2014170110A (ja) | 2013-03-04 | 2013-03-04 | 制御装置、電気光学装置、電子機器および制御方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20140247290A1 (ja) |

| JP (1) | JP2014170110A (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN111508440B (zh) * | 2020-03-25 | 2021-05-25 | 广州奥翼材料与器件研究院有限公司 | 一种电泳显示器的驱动方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005509925A (ja) * | 2001-11-20 | 2005-04-14 | イー−インク コーポレイション | 双安定電子光学ディスプレイの駆動方法 |

| JP2008158488A (ja) * | 2006-12-23 | 2008-07-10 | Lg Display Co Ltd | 電気泳動表示装置とその駆動方法 |

| JP2009237543A (ja) * | 2008-03-05 | 2009-10-15 | Seiko Epson Corp | 電気泳動装置、電気泳動装置の駆動方法、電子機器 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7012600B2 (en) * | 1999-04-30 | 2006-03-14 | E Ink Corporation | Methods for driving bistable electro-optic displays, and apparatus for use therein |

-

2013

- 2013-03-04 JP JP2013041813A patent/JP2014170110A/ja not_active Withdrawn

-

2014

- 2014-02-28 US US14/193,942 patent/US20140247290A1/en not_active Abandoned

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005509925A (ja) * | 2001-11-20 | 2005-04-14 | イー−インク コーポレイション | 双安定電子光学ディスプレイの駆動方法 |

| JP2008158488A (ja) * | 2006-12-23 | 2008-07-10 | Lg Display Co Ltd | 電気泳動表示装置とその駆動方法 |

| JP2009237543A (ja) * | 2008-03-05 | 2009-10-15 | Seiko Epson Corp | 電気泳動装置、電気泳動装置の駆動方法、電子機器 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20140247290A1 (en) | 2014-09-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6033901B2 (ja) | 電気光学ディスプレイを駆動する方法 | |

| JP6256822B2 (ja) | 電気泳動表示装置及びその駆動方法 | |

| WO2012026078A1 (ja) | 制御装置、表示装置及び表示装置の制御方法 | |

| JP7079845B2 (ja) | 電気光学ディスプレイを駆動する方法 | |

| JP6186781B2 (ja) | 制御装置、電気光学装置、電子機器および制御方法 | |

| US20100271377A1 (en) | Electrophoretic Display Controller Providing PIP And Cursor Support | |

| US9842548B2 (en) | Device for controlling display device, method of controlling display device, display device, and electronic apparatus | |

| JP2015057637A (ja) | 集積回路、表示装置、電子機器および表示制御方法 | |

| CN102693691B (zh) | 驱动方法、控制装置、显示装置以及电子设备 | |

| JP5948811B2 (ja) | 制御装置、電気光学装置、電子機器および制御方法 | |

| JP5754194B2 (ja) | 集積回路装置、電気光学装置及び電子機器 | |

| JP2014170110A (ja) | 制御装置、電気光学装置、電子機器および制御方法 | |

| KR101991744B1 (ko) | 전기영동 디스플레이 장치와 이의 구동방법 | |

| RU2754485C1 (ru) | Электрооптические дисплеи и способы их возбуждения | |

| KR20130143361A (ko) | 전기영동 디스플레이 장치와 이의 구동방법 | |

| US9240134B2 (en) | Device for controlling electro-optic device including write section that executes first and second write operations during which different voltages are applied to pixels, method for controlling electro-optic device electro-optic device, and electronic apparatus | |

| JP2015158530A (ja) | 制御装置、表示装置、制御方法およびプログラム | |

| US20230213832A1 (en) | Methods for driving electro-optic displays | |

| JP2012194344A (ja) | 電気光学装置の駆動方法、電気光学装置の制御装置、電気光学装置および電子機器 | |

| JP6146055B2 (ja) | 制御装置、電気光学装置、電子機器及び制御方法 | |

| JP2016133622A (ja) | 記憶型表示装置、記憶型表示装置の駆動方法、及び電子機器 | |

| JP2024019719A (ja) | 電気光学ディスプレイを駆動する方法 | |

| KR20140015040A (ko) | 전기영동 디스플레이 장치와 이의 구동방법 | |

| JP2013231776A (ja) | 制御装置、表示装置、電子機器および制御方法 | |

| JP2015156028A (ja) | 集積回路装置、電気光学装置及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160303 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160303 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170116 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170124 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20170327 |