JP2012199664A - Differential amplifier circuit and integrated circuit device - Google Patents

Differential amplifier circuit and integrated circuit device Download PDFInfo

- Publication number

- JP2012199664A JP2012199664A JP2011061231A JP2011061231A JP2012199664A JP 2012199664 A JP2012199664 A JP 2012199664A JP 2011061231 A JP2011061231 A JP 2011061231A JP 2011061231 A JP2011061231 A JP 2011061231A JP 2012199664 A JP2012199664 A JP 2012199664A

- Authority

- JP

- Japan

- Prior art keywords

- pmos transistor

- gate

- signal

- control signal

- differential amplifier

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- DYCJFJRCWPVDHY-LSCFUAHRSA-N NBMPR Chemical compound O[C@@H]1[C@H](O)[C@@H](CO)O[C@H]1N1C2=NC=NC(SCC=3C=CC(=CC=3)[N+]([O-])=O)=C2N=C1 DYCJFJRCWPVDHY-LSCFUAHRSA-N 0.000 abstract 1

- 238000001514 detection method Methods 0.000 description 37

- 238000010586 diagram Methods 0.000 description 11

- 238000005452 bending Methods 0.000 description 10

- 230000004048 modification Effects 0.000 description 10

- 238000012986 modification Methods 0.000 description 10

- 238000006243 chemical reaction Methods 0.000 description 8

- 230000000694 effects Effects 0.000 description 8

- 230000001360 synchronised effect Effects 0.000 description 7

- 230000006866 deterioration Effects 0.000 description 5

- 238000000034 method Methods 0.000 description 5

- 239000013078 crystal Substances 0.000 description 4

- 230000005284 excitation Effects 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 2

- 239000000758 substrate Substances 0.000 description 2

- 230000002238 attenuated effect Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000010355 oscillation Effects 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 230000009466 transformation Effects 0.000 description 1

Images

Landscapes

- Amplifiers (AREA)

Abstract

【課題】差動対を構成する2つのPMOSトランジスターにおけるNBTIの発生を可能な限り防ぐことにより出力オフセット電圧の発生を抑制可能な差動増幅回路及び集積回路装置を提供すること。

【解決手段】差動増幅回路1は、第1の信号が入力されるPMOSトランジスター10(第1のPMOSトランジスターの一例)と、第2の信号が入力されるPMOSトランジスター20(第2のPMOSトランジスターの一例)と、制御信号XSTBに基づいて、PMOSトランジスター10のゲートとバックゲートを同電位にするか否かを選択するPMOSトランジスター14(第1のスイッチ部の一例)と、制御信号XSTBに基づいて、PMOSトランジスター20のゲートとバックゲートを同電位にするか否かを選択するPMOSトランジスター24(第2のスイッチ部の一例)と、を含む。

【選択図】図1To provide a differential amplifier circuit and an integrated circuit device capable of suppressing generation of an output offset voltage by preventing occurrence of NBTI in two PMOS transistors constituting a differential pair as much as possible.

A differential amplifier circuit includes a PMOS transistor (an example of a first PMOS transistor) to which a first signal is input, and a PMOS transistor (a second PMOS transistor) to which a second signal is input. 1), a PMOS transistor 14 (an example of a first switch unit) that selects whether the gate and back gate of the PMOS transistor 10 are set to the same potential based on the control signal XSTB, and a control signal XSTB A PMOS transistor 24 (an example of a second switch unit) that selects whether or not the gate and back gate of the PMOS transistor 20 have the same potential.

[Selection] Figure 1

Description

本発明は、差動増幅回路及び集積回路装置に関する。 The present invention relates to a differential amplifier circuit and an integrated circuit device.

差動信号を増幅して出力する差動増幅回路(オペアンプ)は、基本回路として様々なアナログ回路に使用されている。特に、集積回路装置(IC)の設計では、MOSトランジスターを用いて差動増幅回路を構成する場合が多いが、MOSトランジスターの劣化により差動増幅回路としての正常な機能が失われるおそれがあり、その対策が重要になる。MOSトランジスターの劣化要因の1つとしてNBTI(Negative Bias Temperature Instability)が知られている。これは、ゲートに印加される電圧や温度の影響により、長時間にわたってチャネルが形成されることでPMOSトランジスターのしきい値電圧が時間の経過とともに変化する現象である。 A differential amplifier circuit (op-amp) that amplifies and outputs a differential signal is used in various analog circuits as a basic circuit. In particular, in the design of an integrated circuit device (IC), a differential amplifier circuit is often configured using a MOS transistor. However, the normal function as a differential amplifier circuit may be lost due to deterioration of the MOS transistor, Countermeasures are important. NBTI (Negative Bias Temperature Instability) is known as one of the deterioration factors of MOS transistors. This is a phenomenon in which the threshold voltage of the PMOS transistor changes with time due to the formation of a channel over a long period of time due to the influence of the voltage and temperature applied to the gate.

特許文献1では、ある製造プロセスで試作されたLSIにおいて、PMOSトランジスターが、NBTIモードよりもPBTI(Positive Bias Temperature Instability)モードにおいて、しきい値電圧の経時変化がより大きく生じることが実験上で判明したため、スタンバイモード時には、PMOSトランジスターのバックゲートに所定の電位を印加することでNBTIモードに設定するというものである。これにより、スタンバイモード時に発生するスタビリティ特性に起因するMOSトランジスターの劣化が抑制され、オペアンプ回路の特性劣化を回避することが可能になるとしている。なお、NBTIモードとPBTIモードの違いは、PMOSトランジスターのゲート電界の方向の違いによる。

In

しかしながら、特許文献1の手法では、スタンバイモード時に、入力用の差動対を構成する2つのPMOSトランジスターのゲート電圧の値によっては、NBTIを発生させるため、2つの差動入力信号の電位に差があると2つのPMOSトランジスターのしきい値電圧のシフト量が異なる可能性がある。2つのPMOSトランジスターのしきい値電圧のシフト量が異なると、オペアンプ回路の出力にオフセット電圧が発生し、差動増幅回路としての正常な機能が失われる。従って、特許文献1の手法は、オペアンプ回路の特性劣化を確実に回避できるものではない。

However, in the method of

本発明は、以上のような問題点に鑑みてなされたものであり、本発明のいくつかの態様によれば、差動対を構成する2つのPMOSトランジスターにおけるNBTIの発生を防ぐことにより出力オフセット電圧の発生を抑制可能な差動増幅回路及び集積回路装置を提供することができる。 The present invention has been made in view of the above problems, and according to some aspects of the present invention, output offset is prevented by preventing occurrence of NBTI in two PMOS transistors constituting a differential pair. A differential amplifier circuit and an integrated circuit device that can suppress voltage generation can be provided.

(1)本発明は、第1の信号と第2の信号を差動増幅する差動増幅回路であって、前記第1の信号が入力される第1のPMOSトランジスターと、前記第2の信号が入力される第2のPMOSトランジスターと、制御信号に基づいて、前記第1のPMOSトランジスターのゲートとバックゲートを同電位にするか否かを選択する第1のスイッチ部と、前記制御信号に基づいて、前記第2のPMOSトランジスターのゲートとバックゲートを同電位にするか否かを選択する第2のスイッチ部と、を含む、差動増幅回路である。 (1) The present invention is a differential amplifier circuit that differentially amplifies a first signal and a second signal, wherein the first PMOS transistor to which the first signal is input, and the second signal Is input to the second PMOS transistor, a first switch unit for selecting whether the gate and the back gate of the first PMOS transistor have the same potential based on the control signal, and the control signal And a second switch unit for selecting whether or not the gate and the back gate of the second PMOS transistor have the same potential.

本発明によれば、制御信号に基づいて、第1のPMOSトランジスターのゲートとバックゲートを同電位にするとともに、第2のPMOSトランジスターのゲートとバックゲートを同電位にすることができる。つまり、本実施形態によれば、制御信号に基づいて、第1のPMOSトランジスターと第2のPMOSトランジスターにともにチャネルが形成されないようにすることができるので、これらのPMOSトランジスターにおけるNBTIの発生を抑制することができる。これにより、NBTIに起因する差動増幅回路の出力オフセット電圧の発生を抑制することができる。 According to the present invention, based on the control signal, the gate and back gate of the first PMOS transistor can be set to the same potential, and the gate and back gate of the second PMOS transistor can be set to the same potential. In other words, according to the present embodiment, it is possible to prevent channels from being formed in both the first PMOS transistor and the second PMOS transistor based on the control signal, thereby suppressing the occurrence of NBTI in these PMOS transistors. can do. Thereby, generation | occurrence | production of the output offset voltage of the differential amplifier circuit resulting from NBTI can be suppressed.

(2)この差動増幅回路において、前記制御信号は、スタンバイモードか否かを示す信号であり、前記第1のスイッチ部は、前記制御信号がスタンバイモードを示す時、前記第1のPMOSトランジスターのゲートとバックゲートを同電位にし、前記第2のスイッチ部は、前記制御信号がスタンバイモードを示す時、前記第2のPMOSトランジスターのゲートとバックゲートを同電位にするようにしてもよい。 (2) In the differential amplifier circuit, the control signal is a signal indicating whether or not the standby mode is set, and the first switch unit is configured to output the first PMOS transistor when the control signal indicates the standby mode. The gate and back gate of the second PMOS transistor may be set to the same potential, and the second switch unit may set the gate and back gate of the second PMOS transistor to the same potential when the control signal indicates a standby mode.

一般に、通常動作モードでは、仮想短絡により第1の信号の電位と第2の信号の電位が同じになるため、NBTIが発生しても第1のPMOSトランジスターのしきい値電圧のシフト量と第2のPMOSトランジスターのしきい値電圧のシフト量が同じになるため、差動増幅回路の出力にオフセット電圧は発生しない。一方、スタンバイモードでは、第1のPMOSトランジスターのゲートとバックゲートが同電位になるとともに、第2のPMOSトランジスターのゲートとバックゲートが同電位になるので、これらのPMOSトランジスターにはともにチャネルが形成されない。従って、スタンバイモードにおいて、これらのPMOSトランジスターにおけるNBTIの発生を防ぎ、差動増幅回路の出力オフセット電圧の発生を抑制することができる。 In general, in the normal operation mode, the potential of the first signal and the potential of the second signal become the same due to a virtual short circuit. Therefore, even if NBTI occurs, the shift amount of the threshold voltage of the first PMOS transistor Since the threshold voltage shift amounts of the two PMOS transistors are the same, no offset voltage is generated at the output of the differential amplifier circuit. On the other hand, in the standby mode, the gate and back gate of the first PMOS transistor have the same potential, and the gate and back gate of the second PMOS transistor have the same potential. Therefore, a channel is formed in both of these PMOS transistors. Not. Therefore, in the standby mode, the occurrence of NBTI in these PMOS transistors can be prevented, and the generation of the output offset voltage of the differential amplifier circuit can be suppressed.

(3)この差動増幅回路において、前記第1のPMOSトランジスターのバックゲート及び前記第2のPMOSトランジスターのバックゲートに第1の電位が供給され、前記第1のスイッチ部は、前記制御信号に基づいて、前記第1のPMOSトランジスターのゲートに前記第1の電位を供給するか否かを選択し、前記第2のスイッチ部は、前記制御信号に基づいて、前記第2のPMOSトランジスターのゲートに前記第1の電位を供給するか否かを選択するようにしてもよい。 (3) In this differential amplifier circuit, a first potential is supplied to the back gate of the first PMOS transistor and the back gate of the second PMOS transistor, and the first switch unit outputs the control signal to the control signal. Based on the control signal, the second switch unit selects whether to supply the first potential to the gate of the first PMOS transistor based on the control signal. Whether to supply the first potential may be selected.

このようにすれば、制御信号に基づいて、第1のPMOSトランジスターのゲートとバックゲート、第2のPMOSトランジスターのゲートとバックゲートをすべて第1の電位にすることができる。これにより、これらのPMOSトランジスターにはともにチャネルが形成されないので、NBTIに起因する差動増幅回路の出力オフセット電圧の発生を抑制することができる。 In this way, the gate and back gate of the first PMOS transistor and the gate and back gate of the second PMOS transistor can all be set to the first potential based on the control signal. Thereby, since a channel is not formed in these PMOS transistors, it is possible to suppress the generation of the output offset voltage of the differential amplifier circuit due to NBTI.

(4)この差動増幅回路において、前記第1のスイッチ部は、前記制御信号に基づいて、前記第1のPMOSトランジスターのゲートとバックゲートを接続するか否かを選択し、前記第2のスイッチ部は、前記制御信号に基づいて、前記第2のPMOSトランジスターのゲートとバックゲートを接続するか否かを選択するようにしてもよい。 (4) In the differential amplifier circuit, the first switch unit selects whether to connect a gate and a back gate of the first PMOS transistor based on the control signal, and The switch unit may select whether to connect the gate and the back gate of the second PMOS transistor based on the control signal.

このようにすれば、制御信号に基づいて、第1のPMOSトランジスターのゲートとバックゲートを同電位にするとともに、第2のPMOSトランジスターのゲートとバックゲートを同電位にすることができる。これにより、これらのPMOSトランジスターにはともにチャネルが形成されないので、NBTIに起因する差動増幅回路の出力オフセット電圧の発生を抑制することができる。 According to this configuration, the gate and back gate of the first PMOS transistor can be set to the same potential, and the gate and back gate of the second PMOS transistor can be set to the same potential based on the control signal. Thereby, since a channel is not formed in these PMOS transistors, it is possible to suppress the generation of the output offset voltage of the differential amplifier circuit due to NBTI.

(5)この差動増幅回路は、前記制御信号に基づいて、前記第1のPMOSトランジスターのバックゲートとソースを接続するとともに前記第2のPMOSトランジスターのバックゲートとソースを接続するか、前記第1のPMOSトランジスターのバックゲート及び前記第2のPMOSトランジスターのバックゲートに第1の電位を供給するかを選択する第3のスイッチ部をさらに含み、前記第1のスイッチ部は、前記制御信号に基づいて、前記第1のPMOSトランジスターのゲートに前記第1の電位を供給するか否かを選択し、前記第2のスイッチ部は、前記制御信号に基づいて、前記第2のPMOSトランジスターのゲートに前記第1の電位を供給するか否かを選択するようにしてもよい。 (5) The differential amplifier circuit connects the back gate and the source of the first PMOS transistor and connects the back gate and the source of the second PMOS transistor based on the control signal. A third switch for selecting whether to supply a first potential to the back gate of the first PMOS transistor and the back gate of the second PMOS transistor; Based on the control signal, the second switch unit selects whether to supply the first potential to the gate of the first PMOS transistor based on the control signal. Whether to supply the first potential may be selected.

このようにすれば、制御信号に基づいて、第1のPMOSトランジスターのゲートとバックゲートを第1の電位にするとともに、第2のPMOSトランジスターのゲートとバックゲートを第1の電位にすることができる。これにより、これらのPMOSトランジスターにはともにチャネルが形成されないので、NBTIに起因する差動増幅回路の出力オフセット電圧の発生を抑制することができる。 In this way, based on the control signal, the gate and back gate of the first PMOS transistor can be set to the first potential, and the gate and back gate of the second PMOS transistor can be set to the first potential. it can. Thereby, since a channel is not formed in these PMOS transistors, it is possible to suppress the generation of the output offset voltage of the differential amplifier circuit due to NBTI.

また、このようにすれば、制御信号に基づいて、第1のPMOSトランジスターのバックゲートとソースを同電位にするとともに第2のPMOSトランジスターのバックゲートとソースを同電位にすることができる。これにより、第1のPMOSトランジスターと第2のPMOSトランジスターにおけるバックゲートバイアス効果(基板効果)を発生させず、入力電圧範囲の上限を高くすることができる。 In this way, the back gate and source of the first PMOS transistor can be set to the same potential and the back gate and source of the second PMOS transistor can be set to the same potential based on the control signal. Thereby, the back gate bias effect (substrate effect) in the first PMOS transistor and the second PMOS transistor is not generated, and the upper limit of the input voltage range can be increased.

(6)この差動増幅回路は、前記制御信号に基づいて、前記第1のPMOSトランジスターのゲートに前記第1の信号を供給するか否かを選択する第4のスイッチ部と、前記制御信号に基づいて、前記第2のPMOSトランジスターのゲートに前記第2の信号を供給するか否かを選択する第5のスイッチ部と、をさらに含むようにしてもよい。 (6) The differential amplifier circuit includes a fourth switch unit that selects whether to supply the first signal to the gate of the first PMOS transistor based on the control signal, and the control signal. And a fifth switch unit for selecting whether or not to supply the second signal to the gate of the second PMOS transistor.

このようにすれば、制御信号に基づいて、第1のPMOSトランジスターのゲートに第1の信号が入力されないようにするとともに、第2のPMOSトランジスターのゲートに第2の信号が入力されないようにすることができる。従って、第1の信号の電位や第2の信号の電位に関係なく、第1のPMOSトランジスターのゲートとバックゲートを確実に同電位にするとともに、第2のPMOSトランジスターのゲートとバックゲートを確実に同電位にすることができる。これにより、これらのPMOSトランジスターにはともにチャネルが形成されないので、NBTIに起因する差動増幅回路の出力オフセット電圧の発生を抑制することができる。 In this way, based on the control signal, the first signal is prevented from being input to the gate of the first PMOS transistor, and the second signal is prevented from being input to the gate of the second PMOS transistor. be able to. Therefore, regardless of the potential of the first signal or the potential of the second signal, the gate and back gate of the first PMOS transistor are surely set to the same potential, and the gate and back gate of the second PMOS transistor are surely set. To the same potential. Thereby, since a channel is not formed in these PMOS transistors, it is possible to suppress the generation of the output offset voltage of the differential amplifier circuit due to NBTI.

(7)本発明は、上記のいずれかの差動増幅回路を含む、集積回路装置である。 (7) The present invention is an integrated circuit device including any of the differential amplifier circuits described above.

以下、本発明の好適な実施形態について図面を用いて詳細に説明する。なお、以下に説明する実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではない。また以下で説明される構成の全てが本発明の必須構成要件であるとは限らない。 DESCRIPTION OF EMBODIMENTS Hereinafter, preferred embodiments of the present invention will be described in detail with reference to the drawings. The embodiments described below do not unduly limit the contents of the present invention described in the claims. Also, not all of the configurations described below are essential constituent requirements of the present invention.

1.差動増幅回路

(1)第1実施形態

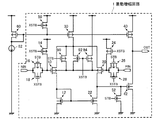

図1は、第1実施形態の差動増幅回路の構成図である。第1実施形態の差動増幅回路1は、PMOSトランジスター10,14,20,24,30,40,50とNMOSトランジスター12,22,42,52を含んで構成されている。

1. Differential Amplifier Circuit (1) First Embodiment FIG. 1 is a configuration diagram of a differential amplifier circuit according to a first embodiment. The

PMOSトランジスター30のソースとPMOSトランジスター40のソースは電源に接続されている。PMOSトランジスター30のゲートとPMOSトランジスター40のゲートには、PMOSトランジスター60のゲート及びドレインが接続されており、PMOSトランジスター60のドレインとグランドの間に定電流源62が接続されている。また、PMOSトランジスター30のゲート(PMOSトランジスター40のゲート)と電源の間に、PMOSトランジスター50が接続されている。

The source of the

PMOSトランジスター10(第1のPMOSトランジスターの一例)のゲートは、NIN入力端子に接続されている。また、PMOSトランジスター10のゲートと電源の間に、PMOSトランジスター14(第1のスイッチ部の一例)が接続されている。

The gate of the PMOS transistor 10 (an example of the first PMOS transistor) is connected to the NIN input terminal. Further, a PMOS transistor 14 (an example of a first switch unit) is connected between the gate of the

PMOSトランジスター20(第2のPMOSトランジスターの一例)のゲートは、PIN入力端子に接続されている。また、PMOSトランジスター20のゲートと電源の間に、PMOSトランジスター24(第2のスイッチ部の一例)が接続されている。

The gate of the PMOS transistor 20 (an example of a second PMOS transistor) is connected to the PIN input terminal. A PMOS transistor 24 (an example of a second switch unit) is connected between the gate of the

PMOSトランジスター10のバックゲートとPMOSトランジスター20のバックゲートは、ともに電源に接続されており、電源電位(第1の電位の一例)が供給されている。

Both the back gate of the

PMOSトランジスター10のソースとPMOSトランジスター20のソースは、PMOSトランジスター30のドレインに共通接続されている。

The source of the

PMOSトランジスター10のドレインは、NMOSトランジスター12のゲート及びドレインとNMOSトランジスター22のゲートに接続されており、PMOSトランジスター20のドレインは、NMOSトランジスター22のドレインとNMOSトランジスター42のゲートに接続されている。また、NMOSトランジスター12のソースとNMOSトランジスター22のソースはグランドに接続されている。

The drain of the

NMOSトランジスター42のソースはグランドに接続され、NMOSトランジスター42のドレインとPMOSトランジスター40のドレインはOUT出力端子に共通接続されている。また、NMOSトランジスター42のゲートとグランドの間に、NMOSトランジスター52が接続されている。

The source of the

本実施形態の差動増幅回路1は、スタンバイモードか否かを示す制御信号STBとXSTBが入力され、通常動作モード(非スタンバイモード)かスタンバイモードのいずれかに設定される。制御信号STBは、スタンバイモード時にハイレベル、通常動作モード時にローレベルに設定される信号であり、制御信号XSTBは、スタンバイモード時にローレベル、通常動作モード時にハイレベルに設定される信号である。

The

制御信号STBは、NMOSトランジスター52のゲートに入力され、制御信号XSTBは、PMOSトランジスター14,24,50の各ゲートに入力される。

The control signal STB is input to the gate of the

通常動作モードでは、制御信号STBがローレベル、制御信号XSTBがハイレベルなので、NMOSトランジスター52、PMOSトランジスター14,24,50はすべてオフしている。従って、PMOSトランジスター60とPMOSトランジスター30により電流ミラー回路が構成され、PMOSトランジスター30には定電流が流れる。同様に、PMOSトランジスター60とPMOSトランジスター40により電流ミラー回路が構成され、PMOSトランジスター40には定電流が流れる。

In the normal operation mode, since the control signal STB is at a low level and the control signal XSTB is at a high level, the

また、通常動作モード時は、PMOSトランジスター10のゲートにはNIN入力端子を介して第1の信号が入力され、PMOSトランジスター20のゲートにはPIN入力端子を介して第2の信号が入力される。そして、PMOSトランジスター10とPMOSトランジスター20には、PMOSトランジスター30を流れる定電流が第1の信号と第2の信号の電位差に応じて分配された各電流が流れる。すなわち、PMOSトランジスター10とPMOSトランジスター20は、第1の信号と第2の信号の電位差を検知する差動対として機能する。また、NMOSトランジスター12とNMOSトランジスター22は電流ミラー対として機能し、PMOSトランジスター40とNMOSトランジスター42は、出力段を構成する。これにより、出力端子OUTには、第1の信号と第2の信号を差動増幅した信号が出力される。

In the normal operation mode, the first signal is input to the gate of the

一方、スタンバイモードでは、制御信号XSTBがローレベルなので、PMOSトランジスター50がオンする。そのため、PMOSトランジスター30のゲートには強制的に電源電位が供給される。これにより、PMOSトランジスター30がオフし、PMOSトランジスター10とPMOSトランジスター20への電流の供給が停止される。PMOSトランジスター50がオンすることで、PMOSトランジスター40のゲートにも強制的に電源電位が供給される。また、スタンバイモード時は、制御信号STBがハイレベルなので、NMOSトランジスター42のゲートには強制的にグランド電位が供給される。これにより、PMOSトランジスター40とNMOSトランジスター42がともにオフし、電源からグランドに流れる電流が停止される。従って、スタンバイモード時は、差動増幅回路1の消費電力が低減される。

On the other hand, in the standby mode, since the control signal XSTB is at a low level, the

さらに、スタンバイモード時は、制御信号XSTBがローレベルなので、PMOSトランジスター14がオンし、PMOSトランジスター10のゲートには強制的に電源電位が供給される。その結果、PMOSトランジスター10のゲートとバックゲートが同電位(電源電位)になり、PMOSトランジスター10にはチャネルが形成されない。同様に、PMOSトランジスター24がオンし、PMOSトランジスター20のゲートには強制的に電源電位が供給される。その結果、PMOSトランジスター20のゲートとバックゲートが同電位(電源電位)になり、PMOSトランジスター20にはチャネルが形成されない。

Further, in the standby mode, since the control signal XSTB is at a low level, the

従って、本実施形態によれば、スタンバイモードにおいて、PMOSトランジスター10とPMOSトランジスター20におけるNBTIの発生を抑制することができる。これにより、本実施形態の差動増幅回路1は、PMOSトランジスター10又はPMOSトランジスター20におけるNBTIに起因する出力オフセット電圧の発生を防ぐことができる。

Therefore, according to the present embodiment, occurrence of NBTI in the

なお、一般に、通常動作モード時は、NIN入力端子とPIN入力端子が仮想短絡の状態で使用されるので、PMOSトランジスター10のバックゲートとゲートの電位差とPMOSトランジスター20のバックゲートとゲートの電位差は等しい。そのため、PMOSトランジスター10とPMOSトランジスター20にともにNBTIが発生しても、しきい値電圧のシフト量は同じになるため、差動増幅回路1に出力オフセット電圧は発生しない。

In general, in the normal operation mode, since the NIN input terminal and the PIN input terminal are used in a virtual short-circuit state, the potential difference between the back gate and the gate of the

[変形例]

図2は、第1実施形態の変形例の差動増幅回路の構成図である。第1実施形態の変形例の差動増幅回路1は、図1の構成に対して、PMOSトランジスター16とNMOSトランジスター18によるスイッチと、PMOSトランジスター26とNMOSトランジスター28によるスイッチが追加されている。図2において、図1と同じ構成(要素)には同じ符号を付しており、図1との相違点のみ説明する。

[Modification]

FIG. 2 is a configuration diagram of a differential amplifier circuit according to a modification of the first embodiment. The

PMOSトランジスター16とNMOSトランジスター18によるスイッチ(第4のスイッチ部の一例)は、NIN端子とPMOSトランジスター10のゲートとの間に接続されている。PMOSトランジスター16のゲートには制御信号STBが入力され、NMOSトランジスター18のゲートには制御信号XSTBが入力される。

A switch (an example of a fourth switch unit) by the PMOS transistor 16 and the

PMOSトランジスター26とNMOSトランジスター28によるスイッチ(第5のスイッチ部の一例)は、PIN端子とPMOSトランジスター20のゲートとの間に接続されている。PMOSトランジスター26のゲートには制御信号STBが入力され、NMOSトランジスター28のゲートには制御信号XSTBが入力される。

A switch (an example of a fifth switch unit) formed by the

通常動作モードでは、STBがローレベル、XSTBがハイレベルなので、PMOSトランジスター16とNMOSトランジスター18がともにオンし、PMOSトランジスター10のゲートにはNIN端子から第1の信号が入力される。同様に、PMOSトランジスター26とNMOSトランジスター28がともにオンし、PMOSトランジスター20のゲートにはPIN端子から第2の信号が入力される。

In the normal operation mode, since STB is at a low level and XSTB is at a high level, both the PMOS transistor 16 and the

一方、スタンバイモードでは、STBがハイレベル、XSTBがローレベルなので、PMOSトランジスター16とNMOSトランジスター18がともにオフし、PMOSトランジスター14がオンするので、NIN入力端子の電位によらず、PMOSトランジスター10のゲートは電源電位になる。同様に、PMOSトランジスター26とNMOSトランジスター28がともにオフし、PMOSトランジスター24がオンするので、PIN入力端子の電位によらず、PMOSトランジスター20のゲートは電源電位になる。その結果、スタンバイモードでは、PMOSトランジスター10のゲートとバックゲートが必ず同電位(電源電位)になるため、PMOSトランジスター10にはチャネルが形成されない。同様に、PMOSトランジスター20のゲートとバックゲートが必ず同電位(電源電位)になるため、PMOSトランジスター20にはチャネルが形成されない。

On the other hand, in the standby mode, since STB is high level and XSTB is low level, both the PMOS transistor 16 and the

従って、本実施形態によれば、スタンバイモードにおいて、PMOSトランジスター10とPMOSトランジスター20におけるNBTIの発生を確実に抑制することができる。そのため、本変形例の差動増幅回路1は、PMOSトランジスター10又はPMOSトランジスター20におけるNBTIに起因する出力オフセット電圧の発生を確実に防ぐことができる。

Therefore, according to the present embodiment, occurrence of NBTI in the

(2)第2実施形態

図3は、第2実施形態の差動増幅回路の構成図である。第2実施形態の差動増幅回路1は、図1の構成に対して、PMOSトランジスター14とPMOSトランジスター24が削除されるとともに、PMOSトランジスター70とNMOSトランジスター72によるスイッチと、PMOSトランジスター80とNMOSトランジスター82によるスイッチが追加されている。図3において、図1と同じ構成(要素)には同じ符号を付しており、図1との相違点のみ説明する。

(2) Second Embodiment FIG. 3 is a configuration diagram of a differential amplifier circuit according to a second embodiment. The

PMOSトランジスター70とNMOSトランジスター72によるスイッチ(第1のスイッチ部の一例)は、PMOSトランジスター10のゲートとバックゲートの間に接続されている。PMOSトランジスター70のゲートには制御信号XSTBが入力され、NMOSトランジスター72のゲートには制御信号STBが入力される。また、PMOSトランジスター10のバックゲートとソースが接続されている。

A switch (an example of a first switch unit) formed by the

PMOSトランジスター80とNMOSトランジスター82によるスイッチ(第2のスイッチ部の一例)は、PMOSトランジスター20のゲートとバックゲートの間に接続されている。PMOSトランジスター80のゲートには制御信号XSTBが入力され、NMOSトランジスター82のゲートには制御信号STBが入力される。また、PMOSトランジスター20のバックゲートとソースが接続されている。

A switch (an example of a second switch unit) constituted by the

通常動作モードでは、STBがローレベル、XSTBがハイレベルなので、PMOSトランジスター70とNMOSトランジスター72がともにオフである。同様に、PMOSトランジスター80とNMOSトランジスター82もともにオフである。そのため、PMOSトランジスター10とPMOSトランジスター20は、NIN端子から入力される第1の信号とPIN端子から入力される第2の信号の電位差を検知する差動対として機能する。また、NMOSトランジスター12とNMOSトランジスター22は電流ミラー対として機能し、PMOSトランジスター40とNMOSトランジスター42は、出力段を構成する。これにより、出力端子OUTには、第1の信号と第2の信号を差動増幅した信号が出力される。

In the normal operation mode, since the STB is low level and the XSTB is high level, both the

ところで、NMOSトランジスター12のゲート−ソース間の電圧をvgsn1、PMOSトランジスター10のドレイン−ソース間の電圧をvdsp1、PMOSトランジスター10のゲート−ソース間の電圧をvgsp1、PMOSトランジスター30のドレイン−ソース間の電圧をvdsp2、電源電位をvddとすると、NIN入力端子を介して入力される第1の信号の最小入力電圧VinLと最大入力電圧VinHは、それぞれ式(1)と式(2)で表される。

By the way, the voltage between the gate and the source of the

図1に示した第1実施形態の差動増幅回路では、PMOSトランジスター10は、バックゲートが電源に接続され、ソースがPMOSトランジスター30のドレインと接続されているのに対して、図3に示した第2実施形態の差動増幅回路では、PMOSトランジスター10は、バックゲートとソースが接続されている。図1の回路では、PMOSトランジスター10のバックゲートの電位がソースの電位よりも高くなっており、バックゲートバイアス効果(基板効果)により、PMOSトランジスター10の閾値の絶対値が図2の回路よりも高くなっている。つまり、図1の回路のほうが、PMOSトランジスター10のゲート−ソース間電圧の絶対値|vgsp1|が高くなるため、式(1)、式(2)より、VinLとVinHがより低くなる。逆に言えば、図3の回路構成にすることで、VinLとVinHがより高くなるので、第1の信号の入力範囲を上側にシフトすることができる。PIN入力端子を介して入力される第2の信号の入力範囲についても同様である。

In the differential amplifier circuit of the first embodiment shown in FIG. 1, the

一方、スタンバイモードでは、STBがハイレベル、XSTBがローレベルなので、PMOSトランジスター70とNMOSトランジスター72がともにオンし、PMOSトランジスター10のゲートとバックゲートが同電位になる。同様に、PMOSトランジスター80とNMOSトランジスター82がともにオンし、PMOSトランジスター20のゲートとバックゲートが同電位になる。その結果、スタンバイモードでは、PMOSトランジスター10とPMOSトランジスター20にはともにチャネルが形成されない。

On the other hand, in the standby mode, since STB is at a high level and XSTB is at a low level, both the

従って、本実施形態によれば、スタンバイモードにおいて、PMOSトランジスター10とPMOSトランジスター20におけるNBTIの発生を確実に抑制することができる。そのため、本実施形態の差動増幅回路1は、PMOSトランジスター10又はPMOSトランジスター20におけるNBTIに起因する出力オフセット電圧の発生を防ぐことができる。

Therefore, according to the present embodiment, occurrence of NBTI in the

(3)第3実施形態

図4は、第3実施形態の差動増幅回路の構成図である。第3実施形態の差動増幅回路1は、図1の構成に対して、PMOSトランジスター90、NMOSトランジスター92及びPMOSトランジスター94によるスイッチ(第3のスイッチ部の一例)が追加されている。図4において、図1と同じ構成(要素)には同じ符号を付しており、図1との相違点のみ説明する。

(3) Third Embodiment FIG. 4 is a configuration diagram of a differential amplifier circuit according to a third embodiment. In the

本実施形態では、PMOSトランジスター10のバックゲートとPMOSトランジスター20のバックゲートが接続されている。PMOSトランジスター90とNMOSトランジスター92は、PMOSトランジスター10のバックゲートとソース(PMOSトランジスター20のバックゲートとソース)の間に接続されている。PMOSトランジスター90のゲートには制御信号STBが入力され、NMOSトランジスター92のゲートには制御信号XSTBが入力される。

In this embodiment, the back gate of the

PMOSトランジスター94は、PMOSトランジスター10のバックゲート(PMOSトランジスター20のバックゲート)と電源の間に接続されている。PMOSトランジスター94のゲートには制御信号XSTBが入力される。

The

通常動作モードでは、STBがローレベル、XSTBがハイレベルなので、PMOSトランジスター90とNMOSトランジスター92がともにオンであり、PMOSトランジスター94がオフである。その結果、PMOSトランジスター10のバックゲートとソースは同電位になり、PMOSトランジスター20のバックゲートとソースも同電位になる。そのため、PMOSトランジスター10とPMOSトランジスター20は、NIN端子から入力される第1の信号とPIN端子から入力される第2の信号の電位差を検知する差動対として機能する。また、NMOSトランジスター12とNMOSトランジスター22は電流ミラー対として機能し、PMOSトランジスター40とNMOSトランジスター42は、出力段を構成する。これにより、出力端子OUTには、第1の信号と第2の信号を差動増幅した信号が出力される。

In the normal operation mode, since STB is at a low level and XSTB is at a high level, both the PMOS transistor 90 and the

なお、図4の差動増幅回路は、図3の差動増幅回路と同様に、PMOSトランジスター10のバックゲートとソースを同電位にし、PMOSトランジスター20のバックゲートとソースを同電位にすることで、第1の信号と第2の信号の入力範囲を上側にシフトすることができる。

4, the back gate and the source of the

一方、スタンバイモードでは、STBがハイレベル、XSTBがローレベルなので、PMOSトランジスター90とNMOSトランジスター92がともにオフし、PMOSトランジスター94がオンするので、PMOSトランジスター10のバックゲートとPMOSトランジスター20のバックゲートには強制的に電源電位が供給される。

On the other hand, in the standby mode, since STB is high level and XSTB is low level, both the PMOS transistor 90 and the

さらに、スタンバイモード時は、制御信号XSTBがローレベルなので、PMOSトランジスター14がオンし、PMOSトランジスター10のゲートには強制的に電源電位が供給される。同様に、PMOSトランジスター24がオンし、PMOSトランジスター20のゲートには強制的に電源電位が供給される。その結果、スタンバイモードでは、PMOSトランジスター10のゲートとバックゲートが同電位(電源電位)になるため、PMOSトランジスター10にはチャネルが形成されない。同様に、PMOSトランジスター20のゲートとバックゲートが同電位(電源電位)になるため、PMOSトランジスター20にはチャネルが形成されない。

Further, in the standby mode, since the control signal XSTB is at a low level, the

従って、本実施形態によれば、スタンバイモードにおいて、PMOSトランジスター10とPMOSトランジスター20におけるNBTIの発生を抑制することができる。そのため、本実施形態の差動増幅回路1は、PMOSトランジスター10又はPMOSトランジスター20におけるNBTIに起因する出力オフセット電圧の発生を防ぐことができる。

Therefore, according to the present embodiment, occurrence of NBTI in the

[変形例]

図5は、第3実施形態の変形例の差動増幅回路の構成図である。第3実施形態の変形例の差動増幅回路1は、図4の構成に対して、PMOSトランジスター16とNMOSトランジスター18によるスイッチと、PMOSトランジスター26とNMOSトランジスター28によるスイッチが追加されている。図5において、図4と同じ構成(要素)には同じ符号を付しており、図1との相違点のみ説明する。

[Modification]

FIG. 5 is a configuration diagram of a differential amplifier circuit according to a modification of the third embodiment. In the

PMOSトランジスター16とNMOSトランジスター18によるスイッチ(第4のスイッチ部の一例)は、NIN端子とPMOSトランジスター10のゲートとの間に接続されている。PMOSトランジスター16のゲートには制御信号STBが入力され、NMOSトランジスター18のゲートには制御信号XSTBが入力される。

A switch (an example of a fourth switch unit) by the PMOS transistor 16 and the

PMOSトランジスター26とNMOSトランジスター28によるスイッチ(第5のスイッチ部の一例)は、PIN端子とPMOSトランジスター20のゲートとの間に接続されている。PMOSトランジスター26のゲートには制御信号STBが入力され、NMOSトランジスター28のゲートには制御信号XSTBが入力される。

A switch (an example of a fifth switch unit) formed by the

通常動作モードでは、STBがローレベル、XSTBがハイレベルなので、PMOSトランジスター16とNMOSトランジスター18がともにオンし、PMOSトランジスター10のゲートにはNIN端子から第1の信号が入力される。同様に、PMOSトランジスター26とNMOSトランジスター28がともにオンし、PMOSトランジスター20のゲートにはPIN端子から第2の信号が入力される。

In the normal operation mode, since STB is at a low level and XSTB is at a high level, both the PMOS transistor 16 and the

一方、スタンバイモードでは、STBがハイレベル、XSTBがローレベルなので、PMOSトランジスター16とNMOSトランジスター18がともにオフし、PMOSトランジスター14がオンするので、NIN入力端子の電位によらず、PMOSトランジスター10のゲートは電源電位になる。同様に、PMOSトランジスター26とNMOSトランジスター28がともにオフし、PMOSトランジスター24がオンするので、PIN入力端子の電位によらず、PMOSトランジスター20のゲートは電源電位になる。また、PMOSトランジスター94がオンするので、PMOSトランジスター10のバックゲートとPMOSトランジスター20のバックゲートはともに電源電位になる。その結果、スタンバイモードでは、PMOSトランジスター10のゲートとバックゲートが必ず同電位(電源電位)になるため、PMOSトランジスター10にはチャネルが形成されない。同様に、PMOSトランジスター20のゲートとバックゲートが必ず同電位(電源電位)になるため、PMOSトランジスター20にはチャネルが形成されない。

On the other hand, in the standby mode, since STB is high level and XSTB is low level, both the PMOS transistor 16 and the

従って、本実施形態によれば、スタンバイモードにおいて、PMOSトランジスター10とPMOSトランジスター20におけるNBTIの発生を確実に抑制することができる。そのため、本変形例の差動増幅回路1は、PMOSトランジスター10又はPMOSトランジスター20におけるNBTIに起因する出力オフセット電圧の発生を確実に防ぐことができる。

Therefore, according to the present embodiment, occurrence of NBTI in the

2.集積回路装置

図6は、集積回路装置の一例である角速度検出用ICを用いた角速度検出装置(ジャイロセンサー)の構成例を示す図である。本実施形態の角速度検出装置2は、角速度検出用IC100とセンサー素子110を含んで構成されている。

2. Integrated Circuit Device FIG. 6 is a diagram illustrating a configuration example of an angular velocity detection device (gyro sensor) using an angular velocity detection IC which is an example of an integrated circuit device. The angular

本実施形態のセンサー素子110は、2本の駆動振動腕とともにその間に1本の検出振動腕を有するいわゆるダブルT型の水晶振動片に2つの駆動電極と2つの検出電極が形成され、不図示のパッケージに封止されている。

In the

センサー素子110の2本の駆動振動腕は、駆動信号として交流電圧信号が与えられると、逆圧電効果によって、互いの先端が接近と離間を繰り返す屈曲振動(励振振動)をする。この2本の駆動振動腕の屈曲振動の振幅が等しければ、2本の駆動振動腕は検出振動腕に対して常に線対称な関係で屈曲振動をするので、検出振動腕は振動を起こさない。

When an AC voltage signal is given as a drive signal, the two drive vibration arms of the

この状態で、センサー素子110の励振振動面に垂直な軸を回転軸とする角速度が加わると、2本の駆動振動腕は、屈曲振動の方向と回転軸の両方に垂直な方向にコリオリの力を得る。その結果、2本の駆動振動腕の屈曲振動の対称性が崩れ、検出振動腕は、バランスを保つように屈曲振動をする。このコリオリ力に伴う検出振動腕の屈曲振動と駆動振動腕の屈曲振動(励振振動)とは位相が90°ずれている。

In this state, when an angular velocity having an axis perpendicular to the excitation vibration surface of the

ただし、実際には、コリオリ力が加わっていなくても2本の駆動振動腕の屈曲振動の振幅がわずかに異なるため、検出振動腕はバランスを保つようにわずかに屈曲振動をする。この屈曲振動は漏れ振動と呼ばれ、駆動信号とは同位相である。そして、圧電効果によってこれらの屈曲振動に基づく逆位相(位相が180°異なる)の交流電荷が2つの検出電極に発生する。コリオリ力に基づいて発生する交流電荷は、コリオリ力の大きさ(言い換えれば、センサー素子110に加わる角速度の大きさ)に応じて変化するのに対して、漏れ振動に基づいて発生する交流電荷は、センサー素子110に加わる角速度の大きさに関係せず一定である。

However, actually, even if no Coriolis force is applied, the amplitudes of the bending vibrations of the two drive vibrating arms are slightly different, so that the detection vibrating arms slightly bend and vibrate so as to maintain a balance. This bending vibration is called leakage vibration and is in phase with the drive signal. Then, AC charges having opposite phases (phases differ by 180 °) based on these bending vibrations are generated in the two detection electrodes by the piezoelectric effect. The AC charge generated based on the Coriolis force changes according to the magnitude of the Coriolis force (in other words, the angular velocity applied to the sensor element 110), whereas the AC charge generated based on the leakage vibration is It is constant irrespective of the magnitude of the angular velocity applied to the

センサー素子110の2つの駆動電極は、それぞれ角速度検出用IC100の外部出力端子101と外部入力端子102に接続されている。また、センサー素子110の2つの検出電極は、それぞれ角速度検出用IC100の外部入力端子103,104と接続されている。

The two drive electrodes of the

角速度検出用IC100は、駆動回路200、検出回路300、電源回路400、基準回路500を含んで構成されており、センサー素子110を発振駆動するとともに、センサー素子110の検出信号に基づいて、角速度の大きさに応じた電圧の信号(角速度信号)を生成する処理を行う。

The angular velocity detection IC 100 includes a drive circuit 200, a detection circuit 300, a

電源回路400は、外部入力端子105から供給される電源電圧から、角速度検出用IC100の内部の電源電圧を生成する。

The

基準回路500は、電源回路400が生成する電源電圧から基準電圧や定電流を生成し、駆動回路200と検出回路300に供給する。

The

駆動回路200は、I/V変換回路(電流電圧変換回路)210、コンパレーター220及びAGC(Automatic Gain Control)回路230及を含んで構成されている。

The drive circuit 200 includes an I / V conversion circuit (current / voltage conversion circuit) 210, a

I/V変換回路210は、センサー素子110の励振振動により一方の駆動電極に発生した水晶電流が外部入力端子102を介して入力され、この水晶電流を交流電圧信号に変換する。

The I /

I/V変換回路210から出力された交流電圧信号は、コンパレーター220及びAGC回路230に入力される。コンパレーター220は、入力された交流電圧信号の電圧を2値化信号(方形波電圧信号)に変換して出力する。

The AC voltage signal output from the I /

AGC回路230は、I/V変換回路210が出力する交流電圧信号の振幅に応じて、コンパレーター220が出力する2値化信号の振幅を変化させ、水晶電流が一定に保持されるように制御する。コンパレーター220が出力する2値化信号は、外部出力端子101を介してセンサー素子110の他方の駆動電極に供給される。

The

このように、駆動回路200を介する発振ループにより、センサー素子110は所定の駆動振動を継続して励振している。

As described above, the

検出回路300は、チャージアンプ310,312、差動アンプ314、ハイパスフィルター316、アンプ318、同期検波回路320、アンプ322、ローパスフィルター324、アンプ326を含んで構成されている。

The detection circuit 300 includes

チャージアンプ310には、外部入力端子103を介してセンサー素子110の一方の検出電極から角速度成分と振動漏れ成分を含む交流電荷が入力される。同様に、チャージアンプ312には、外部入力端子104を介してセンサー素子110の他方の検出電極から角速度成分と振動漏れ成分を含む交流電荷が入力される。このチャージアンプ310及び312は、それぞれ入力された交流電荷を交流電圧信号に変換する。チャージアンプ310の出力信号とチャージアンプ312の出力信号の位相は互いに逆位相である(180°ずれている)。

An AC charge including an angular velocity component and a vibration leakage component is input to the

差動アンプ314は、チャージアンプ310の出力信号とチャージアンプ312の出力信号を差動増幅する。差動アンプ314により、同相成分はキャンセルされ、逆相成分は加算増幅される。

The

ハイパスフィルター316は、差動アンプ314の出力信号に含まれる直流成分をキャンセルし、アンプ318は、ハイパスフィルター316の出力信号を増幅する。

The

同期検波回路320は、アンプ318の出力信号をコンパレーター220が出力する2値化信号で同期検波する。同期検波回路320は、例えば、2値化信号の電圧レベルが基準電圧よりも高い時はアンプ318の出力信号をそのまま選択し、2値化信号の電圧レベルが基準電圧よりも低い時はアンプ318の出力信号を基準電圧に対して反転した信号を選択するスイッチ回路として構成することができる。

The

アンプ318の出力信号には角速度成分と振動漏れ成分が含まれているが、この角速度成分はコンパレーター220が出力する2値化信号と同位相であるのに対して、振動漏れ成分は逆位相である。そのため、同期検波回路320により角速度成分は検波されるが、振動漏れ成分は検波されないようになっている。

The output signal of the

アンプ322は同期検波回路320の出力信号を増幅又は減衰させて所望の電圧レベルの信号を出力し、ローパスフィルター324はアンプ322の出力信号に含まれる高周波成分を除去するとともに仕様で決められる周波数範囲の信号を抽出する。

The

ローパスフィルター324の出力信号は、アンプ326で所望の電圧レベルの信号に増幅又は減衰される。このアンプ326の出力信号は、角速度に応じた電圧レベルの信号(角速度信号)であり、外部出力端子106を介して外部に出力される。

The output signal of the low-

例えば、I/V変換回路210、チャージアンプ310,312、差動アンプ314、アンプ318,322,326などに本実施形態の差動増幅回路を用いることにより、長期間にわたり安定した検出動作が可能な信頼性の高い集積回路装置及び角速度検出装置を実現することができる。

For example, by using the differential amplifier circuit of this embodiment for the I /

なお、本発明は本実施形態に限定されず、本発明の要旨の範囲内で種々の変形実施が可能である。 In addition, this invention is not limited to this embodiment, A various deformation | transformation implementation is possible within the range of the summary of this invention.

本発明は、実施の形態で説明した構成と実質的に同一の構成(例えば、機能、方法及び結果が同一の構成、あるいは目的及び効果が同一の構成)を含む。また、本発明は、実施の形態で説明した構成の本質的でない部分を置き換えた構成を含む。また、本発明は、実施の形態で説明した構成と同一の作用効果を奏する構成又は同一の目的を達成することができる構成を含む。また、本発明は、実施の形態で説明した構成に公知技術を付加した構成を含む。 The present invention includes configurations that are substantially the same as the configurations described in the embodiments (for example, configurations that have the same functions, methods, and results, or configurations that have the same objects and effects). In addition, the invention includes a configuration in which a non-essential part of the configuration described in the embodiment is replaced. In addition, the present invention includes a configuration that exhibits the same operational effects as the configuration described in the embodiment or a configuration that can achieve the same object. Further, the invention includes a configuration in which a known technique is added to the configuration described in the embodiment.

1 差動増幅回路、2 角速度検出装置、10 PMOSトランジスター、12 NMOSトランジスター、14 PMOSトランジスター、16 PMOSトランジスター、18 NMOSトランジスター、20 PMOSトランジスター、22 NMOSトランジスター、24 PMOSトランジスター、26 PMOSトランジスター、28 NMOSトランジスター、30 PMOSトランジスター、40 PMOSトランジスター、42 NMOSトランジスター、50 PMOSトランジスター、52 NMOSトランジスター、60 PMOSトランジスター、62 定電流源、70 PMOSトランジスター、72 NMOSトランジスター、80 PMOSトランジスター、82 NMOSトランジスター、90 PMOSトランジスター、92 NMOSトランジスター、94 PMOSトランジスター、100 角速度検出用IC、110 センサー素子、101 外部出力端子、102,103,104,105 外部入力端子、106 外部出力端子、200 駆動回路、210 I/V変換回路(電流電圧変換回路)、220 コンパレーター、230 AGC回路、300 検出回路、310,312 チャージアンプ、314 差動アンプ、316 ハイパスフィルター、318 アンプ、320 同期検波回路、322 アンプ、324 ローパスフィルター、326 アンプ、400 基準回路、500 電源回路

DESCRIPTION OF

Claims (7)

前記第1の信号が入力される第1のPMOSトランジスターと、

前記第2の信号が入力される第2のPMOSトランジスターと、

制御信号に基づいて、前記第1のPMOSトランジスターのゲートとバックゲートを同電位にするか否かを選択する第1のスイッチ部と、

前記制御信号に基づいて、前記第2のPMOSトランジスターのゲートとバックゲートを同電位にするか否かを選択する第2のスイッチ部と、を含む、差動増幅回路。 A differential amplifier circuit for differentially amplifying a first signal and a second signal,

A first PMOS transistor to which the first signal is input;

A second PMOS transistor to which the second signal is input;

A first switch unit that selects whether or not the gate and the back gate of the first PMOS transistor have the same potential based on a control signal;

And a second switch unit that selects whether or not the gate and back gate of the second PMOS transistor have the same potential based on the control signal.

前記制御信号は、

スタンバイモードか否かを示す信号であり、

前記第1のスイッチ部は、

前記制御信号がスタンバイモードを示す時、前記第1のPMOSトランジスターのゲートとバックゲートを同電位にし、

前記第2のスイッチ部は、

前記制御信号がスタンバイモードを示す時、前記第2のPMOSトランジスターのゲートとバックゲートを同電位にする、差動増幅回路。 In claim 1,

The control signal is

It is a signal indicating whether it is in standby mode,

The first switch unit includes:

When the control signal indicates a standby mode, the gate and back gate of the first PMOS transistor are set to the same potential,

The second switch unit includes:

A differential amplifier circuit for setting the gate and back gate of the second PMOS transistor to the same potential when the control signal indicates a standby mode.

前記第1のPMOSトランジスターのバックゲート及び前記第2のPMOSトランジスターのバックゲートに第1の電位が供給され、

前記第1のスイッチ部は、

前記制御信号に基づいて、前記第1のPMOSトランジスターのゲートに前記第1の電位を供給するか否かを選択し、

前記第2のスイッチ部は、

前記制御信号に基づいて、前記第2のPMOSトランジスターのゲートに前記第1の電位を供給するか否かを選択する、差動増幅回路。 In claim 1 or 2,

A first potential is supplied to a back gate of the first PMOS transistor and a back gate of the second PMOS transistor;

The first switch unit includes:

Selecting whether to supply the first potential to the gate of the first PMOS transistor based on the control signal;

The second switch unit includes:

A differential amplifier circuit that selects whether to supply the first potential to the gate of the second PMOS transistor based on the control signal.

前記第1のスイッチ部は、

前記制御信号に基づいて、前記第1のPMOSトランジスターのゲートとバックゲートを接続するか否かを選択し、

前記第2のスイッチ部は、

前記制御信号に基づいて、前記第2のPMOSトランジスターのゲートとバックゲートを接続するか否かを選択する、差動増幅回路。 In claim 1 or 2,

The first switch unit includes:

Based on the control signal, selecting whether to connect the gate and back gate of the first PMOS transistor,

The second switch unit includes:

A differential amplifier circuit that selects whether to connect a gate and a back gate of the second PMOS transistor based on the control signal.

前記制御信号に基づいて、前記第1のPMOSトランジスターのバックゲートとソースを接続するとともに前記第2のPMOSトランジスターのバックゲートとソースを接続するか、前記第1のPMOSトランジスターのバックゲート及び前記第2のPMOSトランジスターのバックゲートに第1の電位を供給するかを選択する第3のスイッチ部をさらに含み、

前記第1のスイッチ部は、

前記制御信号に基づいて、前記第1のPMOSトランジスターのゲートに前記第1の電位を供給するか否かを選択し、

前記第2のスイッチ部は、

前記制御信号に基づいて、前記第2のPMOSトランジスターのゲートに前記第1の電位を供給するか否かを選択する、差動増幅回路。 In claim 1 or 2,

Based on the control signal, the back gate and the source of the first PMOS transistor are connected and the back gate and the source of the second PMOS transistor are connected, or the back gate and the first of the first PMOS transistor are connected. A third switch for selecting whether to supply the first potential to the back gate of the two PMOS transistors;

The first switch unit includes:

Selecting whether to supply the first potential to the gate of the first PMOS transistor based on the control signal;

The second switch unit includes:

A differential amplifier circuit that selects whether to supply the first potential to the gate of the second PMOS transistor based on the control signal.

前記制御信号に基づいて、前記第1のPMOSトランジスターのゲートに前記第1の信号を供給するか否かを選択する第4のスイッチ部と、

前記制御信号に基づいて、前記第2のPMOSトランジスターのゲートに前記第2の信号を供給するか否かを選択する第5のスイッチ部と、をさらに含む、差動増幅回路。 In claim 3 or 5,

A fourth switch unit for selecting whether to supply the first signal to the gate of the first PMOS transistor based on the control signal;

And a fifth switch section for selecting whether to supply the second signal to the gate of the second PMOS transistor based on the control signal.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011061231A JP2012199664A (en) | 2011-03-18 | 2011-03-18 | Differential amplifier circuit and integrated circuit device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011061231A JP2012199664A (en) | 2011-03-18 | 2011-03-18 | Differential amplifier circuit and integrated circuit device |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2012199664A true JP2012199664A (en) | 2012-10-18 |

Family

ID=47181482

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011061231A Withdrawn JP2012199664A (en) | 2011-03-18 | 2011-03-18 | Differential amplifier circuit and integrated circuit device |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2012199664A (en) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10601411B2 (en) | 2017-02-07 | 2020-03-24 | Kabushiki Kaisha Toshiba | Comparator |

| US10658984B2 (en) | 2017-08-08 | 2020-05-19 | Murata Manufacturing Co., Ltd. | Differential amplifier circuit |

| US11101780B2 (en) | 2019-01-25 | 2021-08-24 | Kabushiki Kaisha Toshiba | Comparator circuit |

-

2011

- 2011-03-18 JP JP2011061231A patent/JP2012199664A/en not_active Withdrawn

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10601411B2 (en) | 2017-02-07 | 2020-03-24 | Kabushiki Kaisha Toshiba | Comparator |

| US10658984B2 (en) | 2017-08-08 | 2020-05-19 | Murata Manufacturing Co., Ltd. | Differential amplifier circuit |

| US10979000B2 (en) | 2017-08-08 | 2021-04-13 | Murata Manufacturing Co., Ltd. | Differential amplifier circuit |

| US11101780B2 (en) | 2019-01-25 | 2021-08-24 | Kabushiki Kaisha Toshiba | Comparator circuit |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI481818B (en) | A detection circuit, a physical quantity detection device, an angular velocity detection device, an integrated circuit device, and an electronic device | |

| US9046366B2 (en) | Signal processing circuit, physical quantity detection apparatus, angular velocity detection apparatus, integrated circuit device, and electronic instrument | |

| US10288426B2 (en) | Circuit device, physical-quantity detecting apparatus, electronic apparatus, and moving object | |

| JP6303411B2 (en) | Detection device, sensor, electronic device, and moving object | |

| US20140174148A1 (en) | Angular velocity detection circuit | |

| WO2010150736A1 (en) | Angular velocity sensor, and synchronous detection circuit used therein | |

| US7812681B2 (en) | Driver device, physical quantity measuring device, and electronic instrument | |

| JP4668407B2 (en) | Angular velocity sensor | |

| JP2005227234A (en) | Angular velocity sensor | |

| US10031176B2 (en) | Circuit device, physical quantity detection device, electronic apparatus, and moving object | |

| US8525591B2 (en) | Signal level conversion circuit, physical quantity detection device and electronic apparatus | |

| JP2012149904A (en) | Temperature detection circuit and sensor device | |

| JP2012199664A (en) | Differential amplifier circuit and integrated circuit device | |

| JP4867385B2 (en) | Oscillation circuit and physical quantity transducer | |

| JP2006313084A (en) | Capacity type physical quantity sensor | |

| CN104634336B (en) | Detection device, sensor, electronic equipment and moving body | |

| JP2006220454A (en) | Sensor circuit for capacitance type physical quantity sensor | |

| JP2008241330A (en) | Detection circuit of piezoelectric vibrator and gyro sensor | |

| JP2007057340A (en) | Oscillation circuit and angular velocity sensor | |

| JP2007057262A (en) | Sensor circuit | |

| JP5360676B2 (en) | Manufacturing method of angular velocity detection device | |

| JP5700090B2 (en) | Manufacturing method of angular velocity detection device | |

| JP2004228625A (en) | Hysteresis comparator | |

| Aaltonen et al. | Upconverting capacitance-to-voltage converter for readout of a micromechanical gyroscope | |

| JP2009098081A (en) | Vibrator driving circuit |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A300 | Withdrawal of application because of no request for examination |

Free format text: JAPANESE INTERMEDIATE CODE: A300 Effective date: 20140603 |